# NAU83G20 DataSheet

#### **Table of Contents** LIST OF FIGURES......5 1.1 1.2 Features .......8 2.1 Pin Diagrams......9 2.2 3 BLOCK DIAGRAM......12 4 ELECTRICAL CHARACTERISTICS ......13 4.1 4.2 4.3 4.4 4.5 4.6 4.7 4.8 4.9 Power Plots 19 5 5.1 5.2 5.3 ADC, DAC and Digital Signal Processing......21 5.4 5.5 5.6 5.7 5.8 59 5.10 5.10.1 5 10 2 5.11

5.12

5.13

5.11.1

5.11.2

5.11.3

| 5.   | .13.1    | ALC Operation                                                 | 33  |

|------|----------|---------------------------------------------------------------|-----|

| 5.   | .13.1.1  | Clip Limiting Mode                                            | 34  |

| 5.   | .13.1.2  | Low VBAT Clip Limiting Mode                                   | 36  |

| 5.   | .13.1.3  | Normal Limiting Mode                                          | 37  |

| 5.   | .13.1.4  | Low Battery Limiting Mode                                     | 38  |

| 5.   | .13.1.5  | Low Battery Limiting Mode with Pre-programmed VBAT Ratio      | 40  |

| 5.   | .13.1.6  | Under Voltage Lock Out Prevention Limiter                     | 42  |

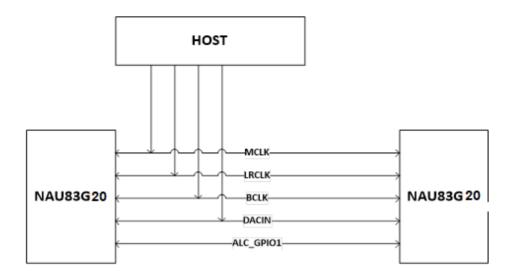

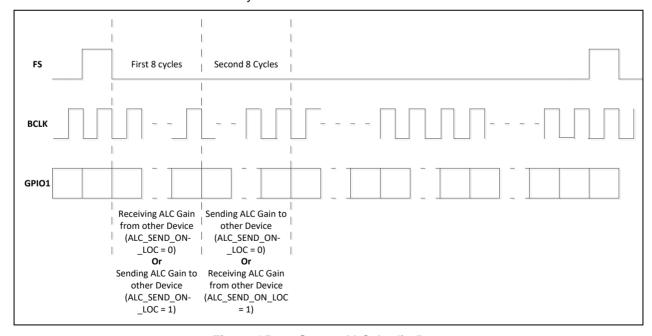

| 5.   | .13.1.7  | Stereo ALC Gain Tracking Operation                            | 43  |

| 5.   | .13.2    | Example ALC Values ALC Hold Time                              | 44  |

| 5.14 | Dev      | rice Protection                                               | 45  |

| 5.15 | Pov      | ver-up and Power-Down Control                                 | 46  |

| 5.16 | Вур      | ass Capacitors                                                | 46  |

| 5.17 | Prin     | nted Circuit Board Layout Considerations                      | 46  |

| 5.   | .17.1    | Recommended PCB Footprint                                     | 46  |

| 5.   | .17.2    | PCB Layout Notes                                              | 47  |

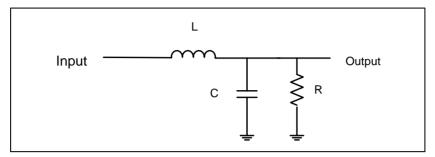

| 5.18 | Filte    | ers                                                           | 48  |

| 5.   | .18.1    | Class D without Filters                                       | 48  |

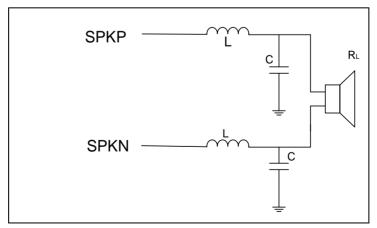

| 5.   | .18.2    | Class D with Filters                                          | 49  |

| 5.19 | Cor      | ntrol Interfaces                                              | 50  |

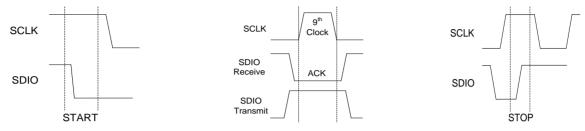

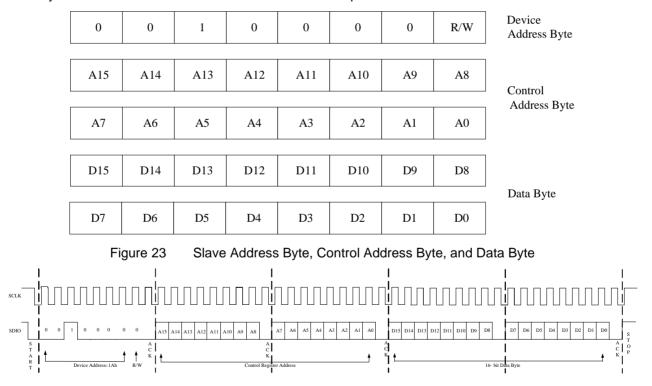

| 5.   | .19.1    | 2-Wire-Serial Control Mode (I <sup>2</sup> C Style Interface) | 50  |

| 5.   | .19.2    | 2-Wire Protocol Convention                                    | 50  |

| 5.   | .19.3    | 2-Wire Write Operation                                        | 51  |

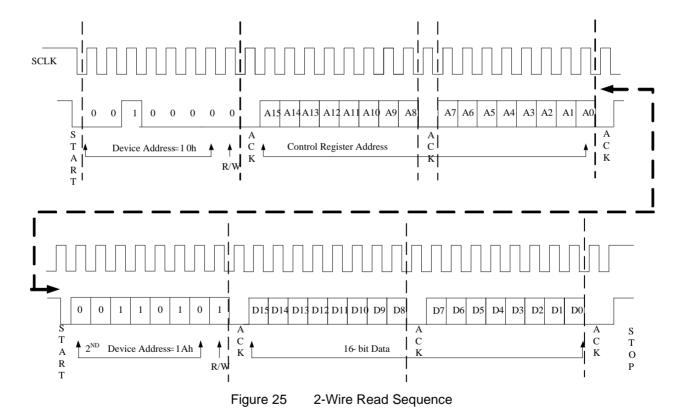

| 5.   | .19.4    | 2-Wire Read Operation                                         | 51  |

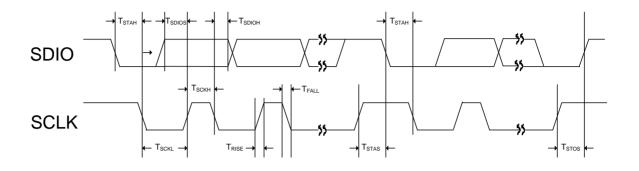

| 5.   | .19.5    | Digital Serial Interface Timing                               | 52  |

| 5.   | .19.6    | Software Reset                                                | 53  |

| 5.20 | Digi     | ital Audio Control Interface                                  | 53  |

| 5.   | .20.1    | Digital Control Interface                                     | 53  |

| 5.   | .20.2    | Digital Audio Interface                                       | 54  |

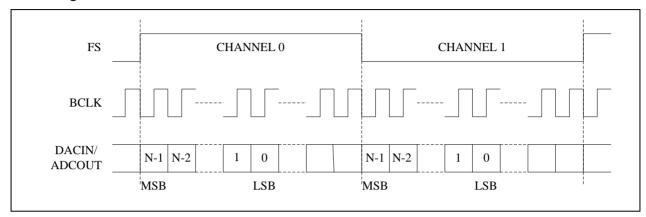

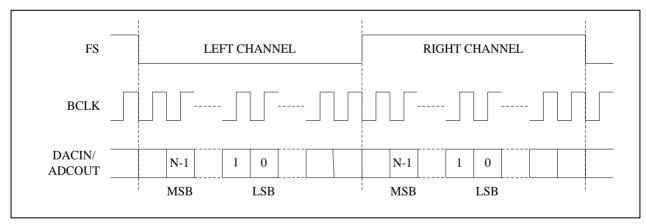

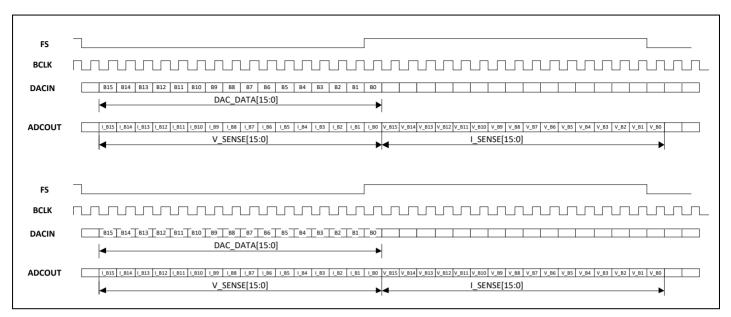

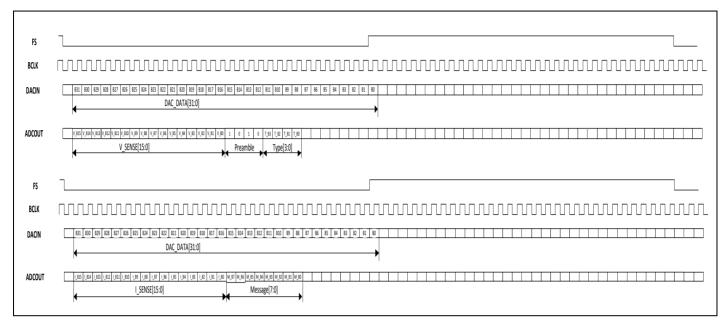

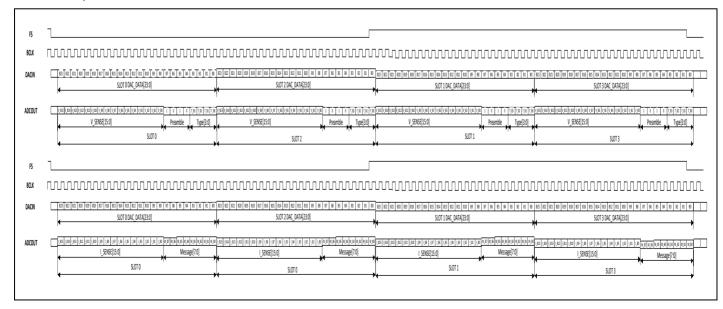

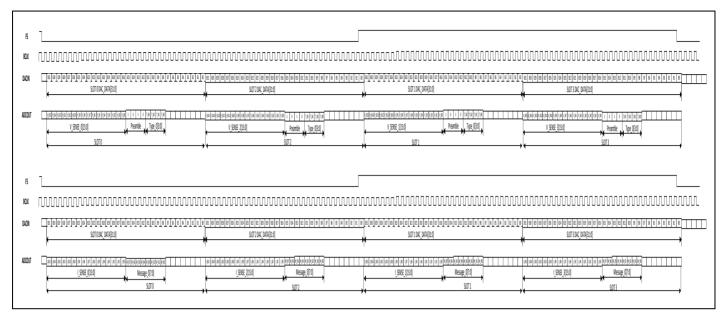

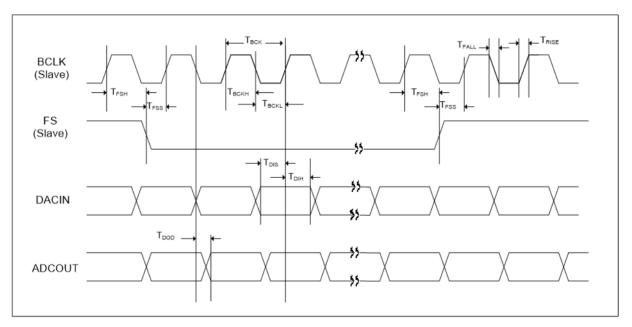

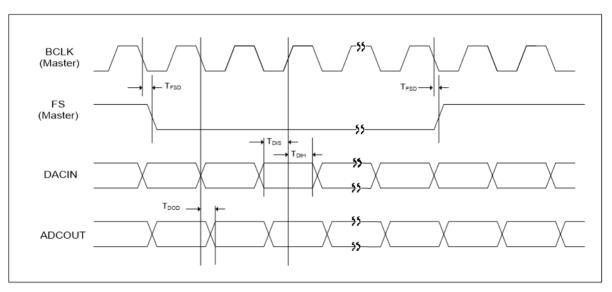

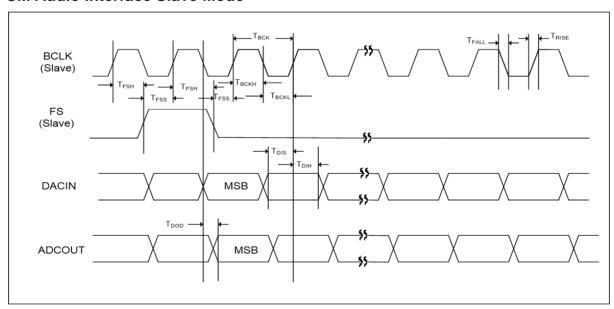

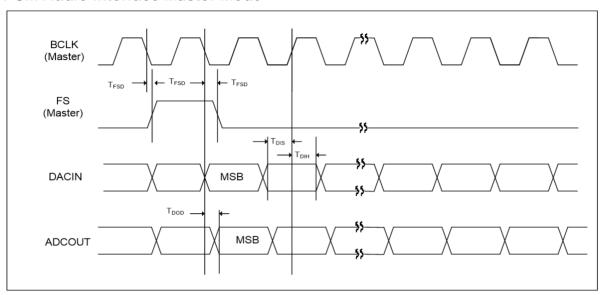

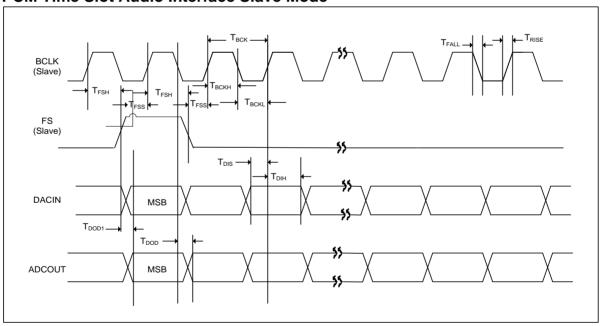

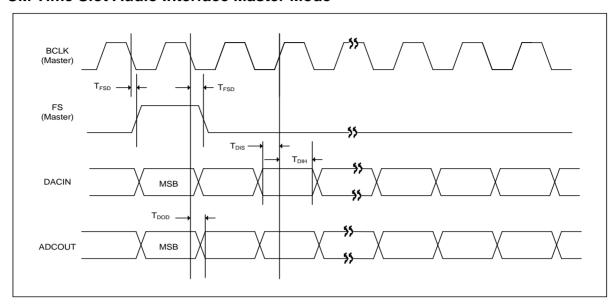

| 5.   | .20.3    | Digital Audio Interface Timing Diagrams                       | 65  |

| Α    | udio Int | erface Master Mode                                            | 65  |

| 5.   | .20.4    | Digital Audio Interface Timing Parameters                     | 68  |

| 5.21 | Inte     | rrupt Request                                                 | 69  |

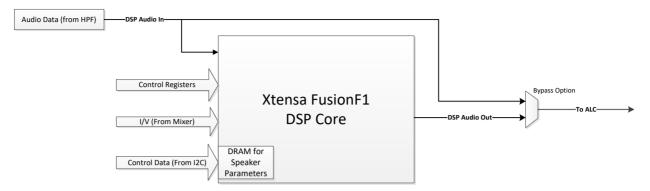

| 5.22 | Digi     | ital Signal Processor (DSP)                                   | 70  |

| 5.   | .22.1    | DSP Core Control and Usage                                    | 70  |

| 5.   | .22.2    | Base Register Initialization for DSP                          | 71  |

| 5.   | .22.2.1  | Supported Commands                                            | 72  |

| 5.23 | Cor      | ntrol Registers                                               | 74  |

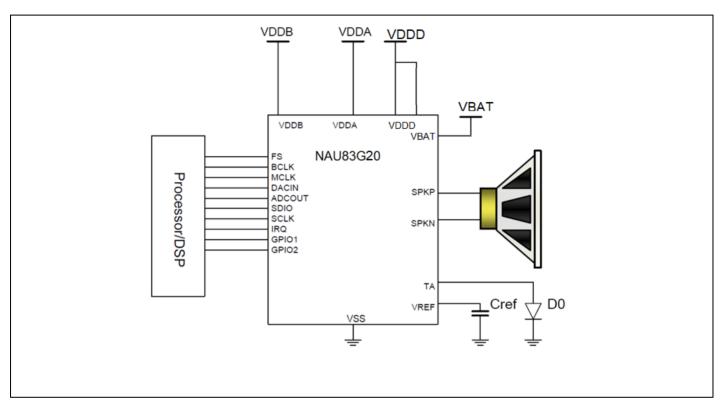

| 5    | SYSTE    | M DIAGRAM                                                     | 100 |

| 6.1  | Ref      | erence System Diagram                                         | 100 |

| E    | EXAMF    | PLE OF REGISTER SETTING                                       | 101 |

|      |          |                                                               |     |

6

7

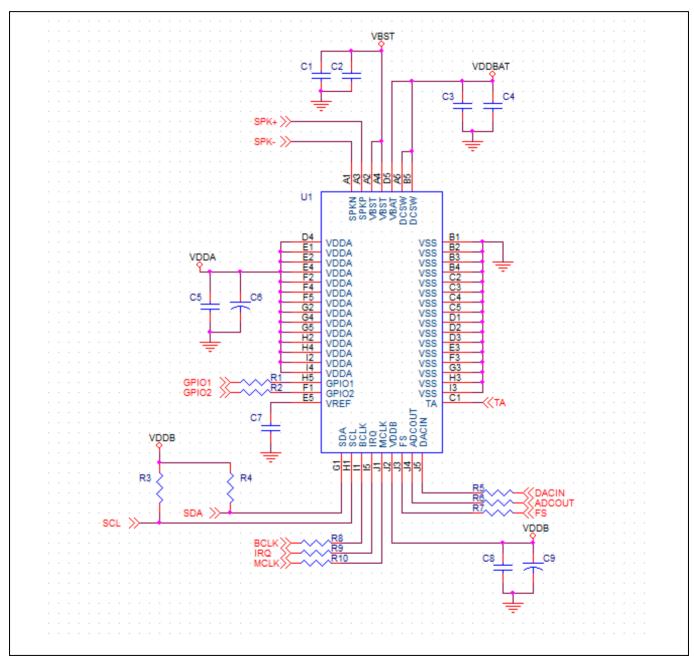

| 8  | APPLICATION REFERENCE CIRCUIT | .102 |

|----|-------------------------------|------|

| 9  | PACKAGE SPECIFICATION         | .104 |

| 10 | ORDERING INFORMATION          | .106 |

| 11 | REVISION HISTORY              | .107 |

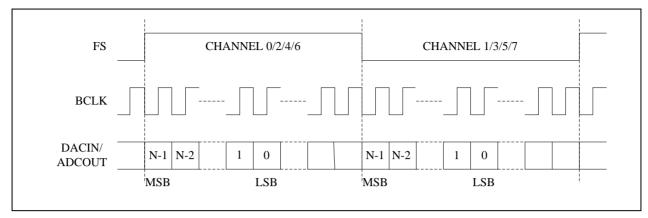

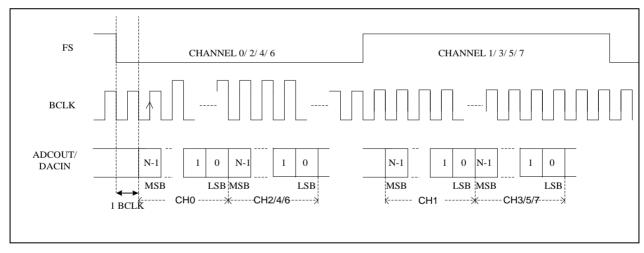

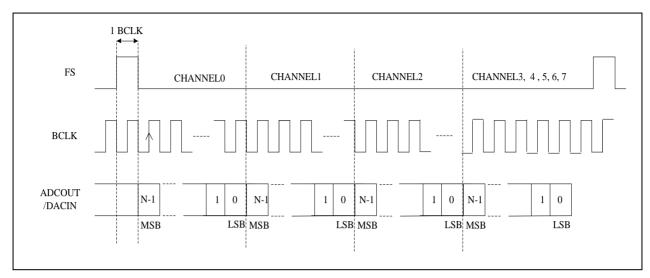

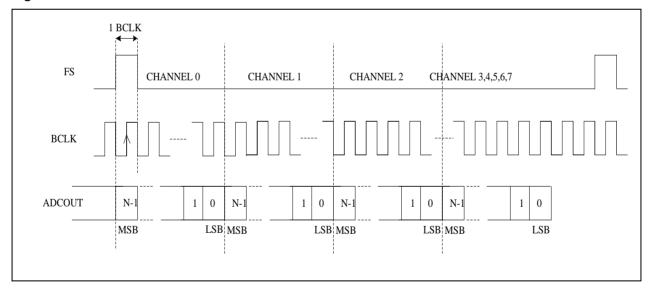

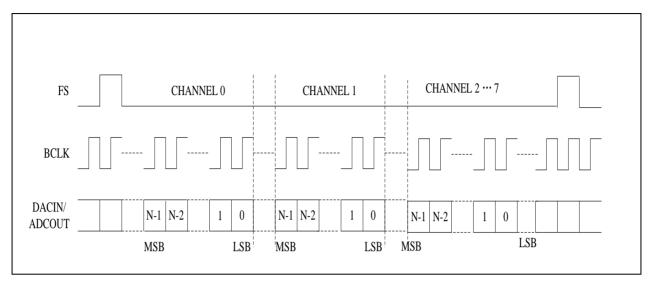

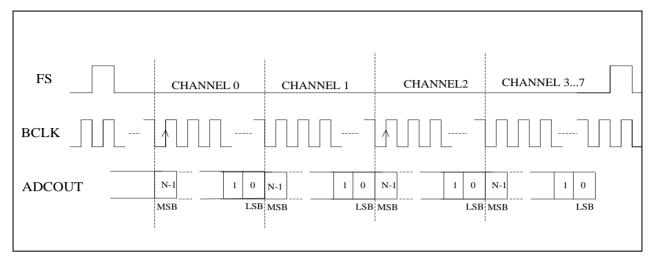

#### **List of Figures** Figure 1 Pin Diagram of NAU83G20 (Top View)......9 Figure 2 Figure 3 THD vs Po 18 Figure 4 Figure 5 Figure 6 Figure 7 Figure 8 SAR ADC Control 25 Figure 9 Figure 10 Automatic Level Control 33 Figure 11 Figure 12 Figure 13 Figure 14 Figure 15 Figure 16 Figure 17 Figure 18 Figure 19 Figure 20 Figure 21 Figure 22 Figure 23 Figure 24 Figure 25 Figure 26 Figure 27 Figure 28 Figure 29 Figure 30 Figure 31 Figure 32 Figure 33 Figure 34 Figure 35 Figure 36 16-Bit I2S Stereo Mode Timing Diagram ......61 Figure 37 24-Bit I2S Stereo Mode Timing Diagram .......61 Figure 38 Figure 39 16-Bit I2S PingPong Mode Timing Diagram .......63

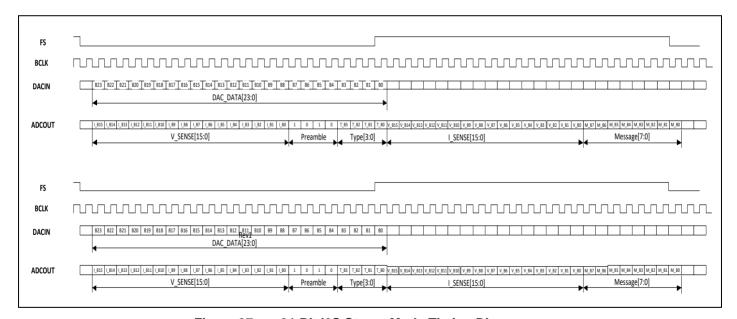

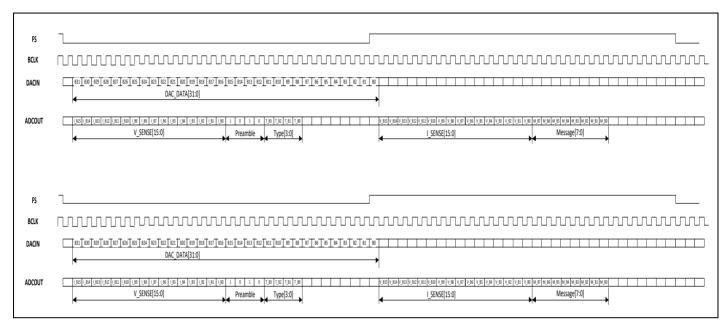

| Figure 40   | 24-Bit I2S PingPong Mode Timing Diagram         | 63  |

|-------------|-------------------------------------------------|-----|

| Figure 41   | 32-Bit I2S PingPong Mode Timing Diagram         | 64  |

| Figure 42   | 24-Bits I2S PingPong Mode in TDM Timing Diagram | 64  |

| Figure 43   | 32-Bits I2S PingPong Mode in TDM Timing Diagram | 65  |

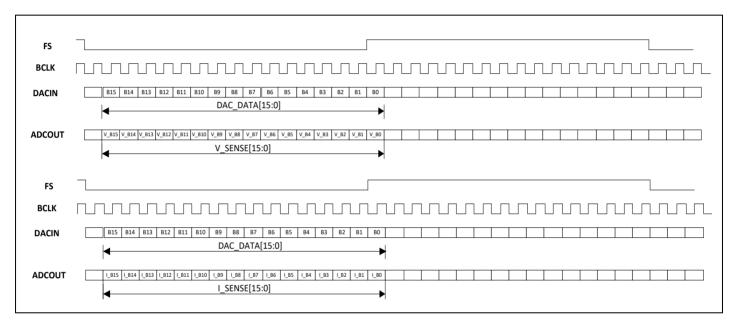

| Figure 44   | Audio Interface Slave Mode                      | 65  |

| Figure 45 / | Audio Interface Master Mode                     | 66  |

| Figure 46 I | PCM Audio Interface Slave Mode                  | 66  |

| Figure 47   | PCM Audio Interface Master Mode                 | 67  |

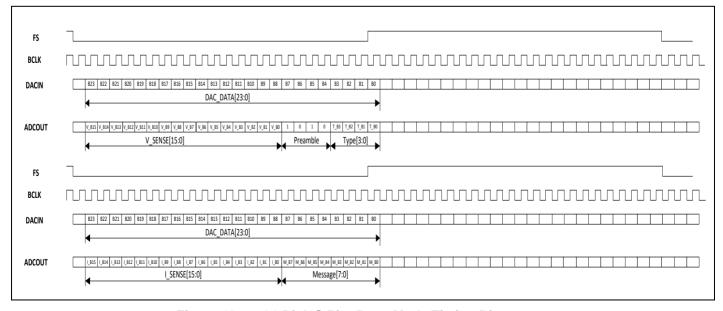

| Figure 48   | PCM Time Slot Audio Interface Slave Mode        | 67  |

| Figure 49   | PCM Time Slot Audio Interface Master Mode       | 68  |

| Figure 50   | DSP Connection Diagram                          | 71  |

| Figure 51   | NAU83G20 Simplified System Diagram              | 100 |

| Figure 52   | Application Reference Circuit Diagram           | 102 |

| Figure 53   | NAU83G20 Package Specification                  | 105 |

**List of Tables**

#### Table 1 Table 2 Table 3 Table 4 Table 5 Table 6 Table 7 Table 8 Table 9 Table 10 Table 11 Table 12 Table 13 Table 14 Table 15 Table 16 Table 17 Table 18 Table 19

Table 20

Table 21

Table 22

Table 23

Table 24

Table 25

#### 1 GENERAL DESCRIPTION

#### 1.1 Overview

The NAU83G20 is a monophonic amplifier device with DSP and V/I sense. The DSP ROM is programmed with a speaker excursion control algorithm. The target application for this device is mobile phone, tablet, and laptop market, where small speaker is used. Compared to traditional Class D amp, the NAU83G20 has 2 ADCs integrated such that speaker voltage and current can be sensed and sent back to the DSP for speaker excursion control. This speaker excursion control can prevent the speaker membrane excursion from exceeding its rated limit and provide ample headroom for overall loudness and sound quality.

#### 1.2 Features

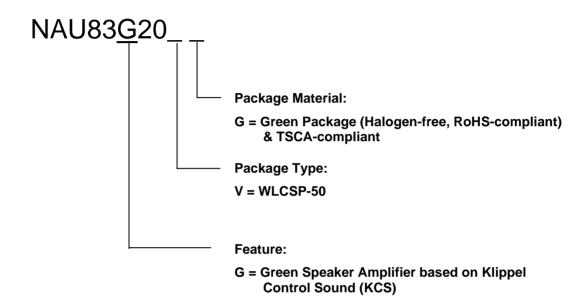

The NAU83G20 Monophonic Amplifier, with DSP and I/V Sense, and utilizes a powerful Class-D Amplifier. The chip features high output power capability, low-current shutdown mode, and click-and-pop suppression. Equipped with a DSP Core, numerous types of device protection schemes are supported, as well as speaker protection schemes, including ambient temperature monitoring input for enhanced speaker module design. The temperature monitoring in the NAU83G20 protects both the chip and the speaker from overheating. The chip is available in a 50-ball Wafer Level Chip Scale Package (WLCSP).

#### **Key Feature List**

- Powerful Class-D Amplifier:

- Up to 10.8 Watts into an 8 Ohm load at 10% Total Harmonic Distortion and Noise (THD+N)

- Up to 20 Watts into an 4 Ohm load at max. power

- ≥ 90 dB Power Supply Rejection Ratio (PSRR)

- Low Current Shutdown Mode

- Click-and-Pop Suppression (30 µVRMS)

- Programmable Serial Interfaces:

- I2C Interface

- I2S Interface

- PCM Interface

- Device Protection:

- Over Current Protection (OCP),

- Over Voltage Protection (OVP)

- Under Voltage Lock Out (UVLO)

- Over Temperature Protection (OTP)

- Clock Termination Protection (CTP)

- Speaker Protection:

- Current & Voltage Sensing

- Anti-Clip Protection (ACP)

- Speaker Module Temperature Sense Input

- Battery Protection: Limiter

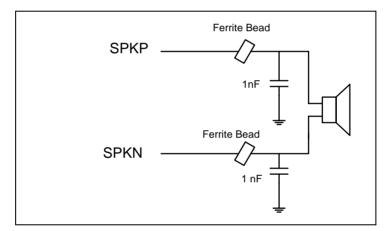

- Filter-less Electro Magnetic Interference (EMI) mitigation

- 50-Ball Wafer Level Chip Scale Package (WLCSP) (0.5 mm Pitch)

- Package is Halogen-free, RoHS-compliant and TSCA-compliant

#### **Applications**

- Smartphones

- Notebooks /Tablets/ Personal Computers

- Personal Media Players/Portable Televisions

- MP3 Lossless Standard Audio Compression Format Players

- Portable Game Players

- Digital Camcorders

## 2 PIN CONFIGURATIONS

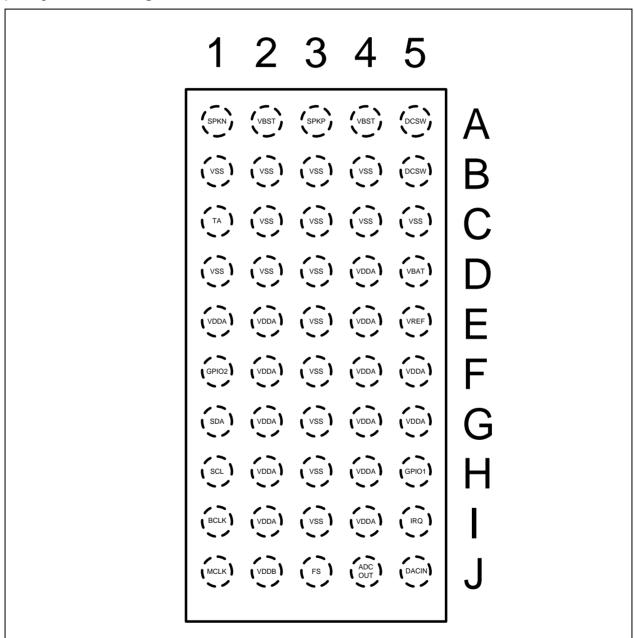

## 2.1 Pin Diagrams

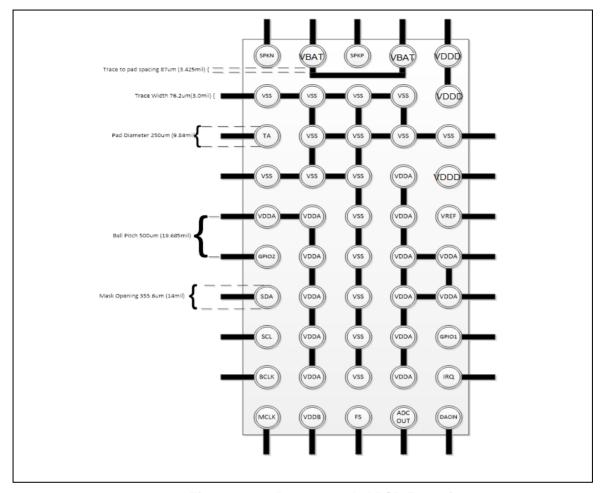

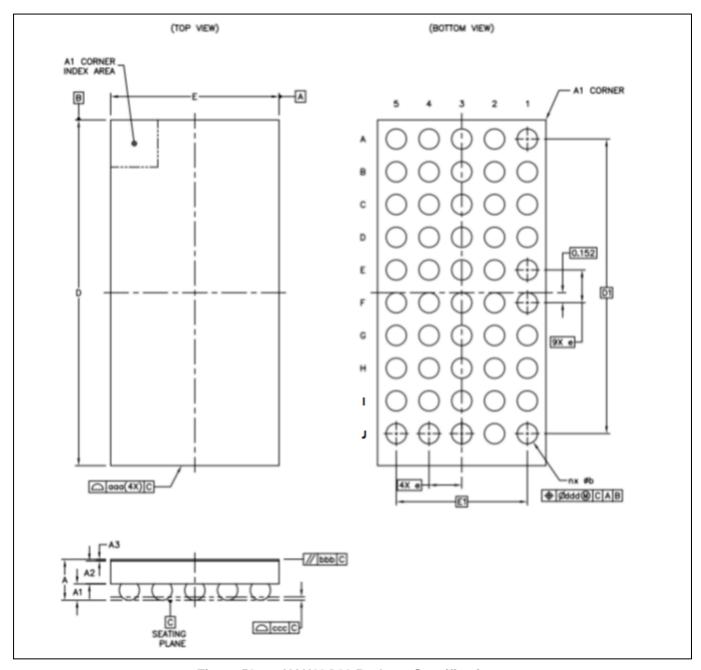

The NAU83G20 Monophonic Class-D Amplifier with DSP and I/V-Sense is available in a 50-Ball WLCSP package as shown in **Figure 1**.

Figure 1 Pin Diagram of NAU83G20 (Top View)

## 2.2 PIN DESCRIPTIONS

Pin descriptions for the NAU83G20 Mono Class-D Amplifier with DSP and I/V Sense are provided in Table 1.

Table 1 Pin Descriptions for the NAU83G20

| Pin # | Name  | Type, (Supply Domain) | Description                                             |

|-------|-------|-----------------------|---------------------------------------------------------|

| A1    | SPKN  | Analog Output (VBAT)  | Class-D Negative Speaker Output Terminal                |

| A2    | VBAT  | Supply                | Battery Supply                                          |

| А3    | SPKP  | Analog Output (VBAT)  | Class-D Positive Speaker Output Terminal                |

| A4    | VBAT  | Supply                | Battery Supply                                          |

| A5    | VDDD  | Supply                | Analog Supply Voltage                                   |

| B1    | VSS   | Ground                | Supply Ground                                           |

| B2    | VSS   | Ground                | Supply Ground                                           |

| B3    | VSS   | Ground                | Supply Ground                                           |

| B4    | VSS   | Ground                | Supply Ground                                           |

| B5    | VDDD  | Supply                | Analog Supply Voltage                                   |

| C1    | TA    | Analog Input (VDDA)   | Ambient Temperature Sense Input, tie to VSS if not used |

| C2    | VSS   | Ground                | Supply Ground                                           |

| C3    | VSS   | Ground                | Supply Ground                                           |

| C4    | VSS   | Ground                | Supply Ground                                           |

| C5    | VSS   | Ground                | Supply Ground                                           |

| D1    | VSS   | Ground                | Supply Ground                                           |

| D2    | VSS   | Ground                | Supply Ground                                           |

| D3    | VSS   | Ground                | Supply Ground                                           |

| D4    | VDDA  | Supply                | Analog & Core Supply Voltage                            |

| D5    | VDDD  | Supply                | Analog Supply Voltage                                   |

| E1    | VDDA  | Supply                | Analog & Core Supply Voltage                            |

| E2    | VDDA  | Supply                | Analog & Core Supply Voltage                            |

| E3    | VSS   | Ground                | Supply Ground                                           |

| E4    | VDDA  | Supply                | Analog & Core Supply Voltage                            |

| E5    | VREF  | Analog I/O (VDDA)     | Internal DAC & ADC Voltage Reference Decoupling I/O     |

| F1    | GPIO2 | Digital I/O (VDDB)    | General Purpose IO2/Address Selection 2                 |

| F2    | VDDA  | Supply                | Analog & Core Supply Voltage                            |

| F3    | VSS   | Ground                | Supply Ground                                           |

| F4    | VDDA  | Supply                | Analog & Core Supply Voltage                            |

| F5    | VDDA  | Supply                | Analog & Core Supply Voltage                            |

| G1    | SDA   | Digital I/O (VDDB)    | Serial Data for I2C                                     |

| G2    | VDDA  | Supply                | Analog & Core Supply Voltage                            |

| G3    | VSS   | Ground                | Supply Ground                                           |

| Pin# | Name   | Type, (Supply Domain) | Description                               |

|------|--------|-----------------------|-------------------------------------------|

| G4   | VDDA   | Supply                | Analog & Core Supply Voltage              |

| G5   | VDDA   | Supply                | Analog & Core Supply Voltage              |

| H1   | SCL    | Digital Input (VDDB)  | Serial Data Clock for I2C                 |

| H2   | VDDA   | Supply                | Analog & Core Supply Voltage              |

| H3   | VSS    | Ground                | Supply Ground                             |

| H4   | VDDA   | Supply                | Analog & Core Supply Voltage              |

| H5   | GPIO1  | Digital I/O (VDDB)    | General Purpose IO1/Address Selection 1   |

| l1   | BCLK   | Digital I/O (VDDB)    | Serial Audio Data Bit Clock I2S/PCM Input |

| 12   | VDDA   | Supply                | Analog & Core Supply Voltage              |

| 13   | VSS    | Ground                | Supply Ground                             |

| 14   | VDDA   | Supply                | Analog & Core Supply Voltage              |

| 15   | IRQ    | Digital Output (VDDB) | Programmable Interrupt Output             |

| J1   | MCLK   | Digital Input (VDDB)  | Master Clock                              |

| J2   | VDDB   | Supply                | Digital IO Supply                         |

| J3   | FS     | Digital I/O (VDDB)    | Frame Sync I2S/PCM Input                  |

| J4   | ADCOUT | Digital Output (VDDB) | Serial Audio I2S/PCM Data Output          |

| J5   | DACIN  | Digital Input (VDDB)  | Serial Audio Data I2S/PCM Input           |

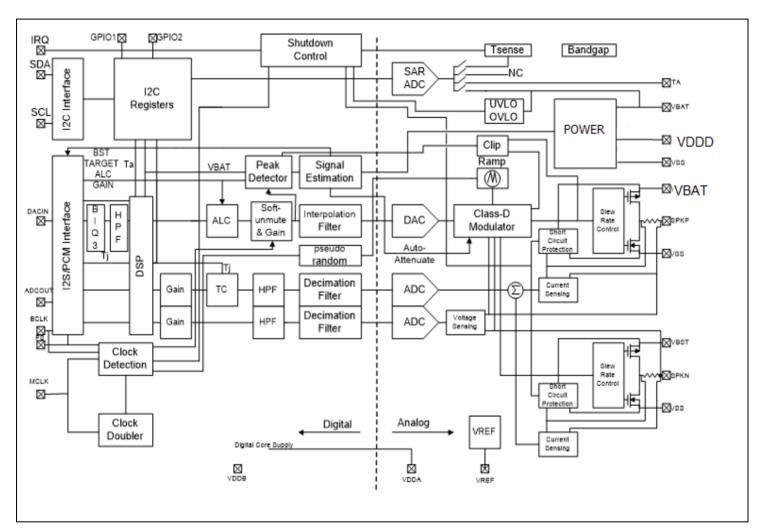

## **3 BLOCK DIAGRAM**

A Block Diagram for the NAU83G20 is provided in Figure 2.

Figure 2 NAU83G20 Block Diagram

## 4 ELECTRICAL CHARACTERISTICS

The tables in this chapter provide the various electrical parameters for the NAU83G20 and their values.

# 4.1 Absolute Maximum Ratings

Table 2 Absolute Maximum Ratings

| Parameter                            | Min       | Max        | Units |

|--------------------------------------|-----------|------------|-------|

| VDDB Digital I/O Supply Range        | -0.3      | 4.0        | V     |

| VDDD Analog Supply Range             | -0.3      | 6.0        | V     |

| VBAT Supply Range                    | -0.3      | 16.5       | V     |

| VDDA Analog Supply Range             | -0.3      | 2.2        | V     |

| Voltage Input Analog Range           | VSS - 0.3 | VDDA + 0.3 | V     |

| Voltage Input I/O Range              | VSS - 0.3 | VDDB + 0.3 | V     |

| Junction Temperature, T <sub>J</sub> | -40       | +150       | °C    |

| Storage Temperature                  | -65       | +150       | °C    |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely influence product reliability and result in failures not covered by the warranty.

## 4.2 Operating Conditions

Table 3 Recommended Operating Conditions for the NAU83G20

| Condition                        | Symbol | Min  | Typical | Max  | Units |

|----------------------------------|--------|------|---------|------|-------|

| Analog Supply Range              | VDDD   | 2.90 | 4.2     | 5.50 | V     |

| Analog Supply Range              | VDDA   | 1.62 | 1.8     | 1.98 | V     |

| Digital I/O Supply Range         | VDDB   | 1.62 | 3.0     | 3.6  | V     |

| VBAT Analog Supply               | VBAT   | VDDD | 12.6    | 14   | V     |

| Ground                           | VSS    |      | 0       |      | V     |

| Industrial Operating Temperature |        | -40  |         | +85  | °C    |

CAUTION: The following conditions needed to be followed for regular operation: VDDD >  $V_{DD}A$  -1.2V; VDDB > VDDA - 0.6V.

#### 4.3 Thermal Information

Table 4 Thermal Information for the NAU83G20

| Deskara             | Power | Та   | Theta JA (°C/W) |       |       | Theta  |

|---------------------|-------|------|-----------------|-------|-------|--------|

| Package             | (W)   | (°C) | 0 m/s           | 1 m/s | 2 m/s | (°C/W) |

| WLCSP50 2.57x5.28mm | 1     | 85   | 34.21           | 31.47 | 30.42 | 3.46   |

## 4.4 Electrical Parameters

#### **Table 5** Electrical Characteristics

Conditions:  $V_{DD}A = V_{DD}B = 1.8V$ ; VDDD = 4.2V. VBAT = 12.6V  $R_L = 8$   $\Omega + 33$   $\mu H$ , f = 1kHz, 48kHz sample rate,

MCLK=12.288MHz, Limits apply for  $T_A = 25$ °C

| Symbol | Parameter                                        |                   | Conditions                                                                 | Typical | Limit | Units |  |

|--------|--------------------------------------------------|-------------------|----------------------------------------------------------------------------|---------|-------|-------|--|

|        |                                                  | V <sub>DD</sub> A | all clocks off                                                             | 15.0    |       |       |  |

| ISD    | Shutdown Mode* Supply                            | V <sub>DD</sub> B | all clocks off                                                             | 0.3     | 2     | μΑ    |  |

| 130    | Current                                          | VDDD              | all clocks off                                                             | 0.4     | 4     |       |  |

|        |                                                  | VBAT              | All clocks off                                                             | 0.1     | TBD   |       |  |

|        |                                                  | V <sub>DD</sub> A | clocks off, clock gating on                                                | 15.0    |       |       |  |

| ISB    | Standby Mode** Supply                            | V <sub>DD</sub> B | clocks off, clock gating on                                                | 0.3     |       | μA    |  |

| IOD    | Current                                          | VDDD              | clocks off, clock gating on                                                | 0.4     |       | - μΛ  |  |

|        |                                                  | VBAT              | clocks off, clock gating on                                                | 0.3     | TBD   |       |  |

|        |                                                  | V <sub>DD</sub> A | idle Channel , DSP off                                                     | 8       |       |       |  |

| IDD    | Idle Channel Operating<br>Mode*** Supply Current | V <sub>DD</sub> B | idle Channel, DSP off                                                      | 0.2     |       | mA    |  |

| 100    |                                                  | VDDD              | idle Channel, DSP off                                                      | 3       |       | ША    |  |

|        |                                                  | VBAT              | idle Channel, DSP off                                                      | 4       |       |       |  |

|        |                                                  |                   | Class-D Channel                                                            |         |       |       |  |

|        |                                                  |                   | RL = 8 Ohm + 33 µH and Total<br>Harmonic Distortion+Noise (THD+N)<br>= 1%  | 9.4     |       | W     |  |

| Po     | Output Power                                     |                   | RL = 8 Ohm + 33 μH and Total<br>Harmonic Distortion+Noise (THD+N)<br>= 10% | 10.8    |       | W     |  |

|        |                                                  |                   | RL = 4 Ohm + 33 µH and Total<br>Harmonic Distortion+Noise (THD+N)<br>= 1%  | 17      |       | W     |  |

|        |                                                  |                   | RL = 4 Ohm + 33 µH and Total<br>Harmonic Distortion+Noise (THD+N)<br>= 10% | 20      |       | W     |  |

| THD+N  | Total Harmonic Distortion                        | + Noise           | $R_L = 8 \Omega + 33 \mu H$ , f=1kHz, $P_O = 1 W$                          | 0.021   |       | %     |  |

| Symbol            | Parameter                             | Conditions                                                                              | Typical | Limit | Units           |

|-------------------|---------------------------------------|-----------------------------------------------------------------------------------------|---------|-------|-----------------|

| eos               | Output Noise                          | A-Weighted, 20Hz-20kHz, no DAC input signal, gain = 19.1dB                              | 65      |       | μVrms           |

| PSRR              |                                       | DC, VDDD = 2.9V – 5.5V, GAIN = 19.1dB                                                   | 88      |       | dB              |

|                   |                                       | $f_{RIPPLE}$ = 217Hz, $V_{RIPPLE}$ = 200m $V_{P\_P}$ GAIN = 19.1dB                      | 92      |       | dB              |

|                   | Power Supply Rejection Ratio          | $f_{RIPPLE}$ = 1020Hz, $V_{RIPPLE}$ = 200m $V_{P\_P}$ GAIN = 19.1dB                     | 86      |       | dB              |

|                   |                                       | f <sub>RIPPLE</sub> = 4kHz, V <sub>RIPPLE</sub> = 200mV <sub>P_P</sub><br>GAIN = 19.1dB | 84      |       | dB              |

| Fres              | Frequency Response                    |                                                                                         | +-0.8   |       | dB              |

| Vos               | Output Offset Voltage                 | Idle Channel, Gain= 0dB                                                                 | ±0.7    | ±5    | mV              |

| Крор              | Pop and Click Noise                   | A-weighted, Idle DAC input, Clock<br>Gating, toggling clocks on/off                     | 0.03    |       | mVrms           |

|                   |                                       | A-weighted, Idle DAC input, toggling between -120dBFs DAC In & 2048 zero samples        | 0.03    |       | mVrms           |

| Rdson-P           | Driver P MOS-FET ON-resistance        | VDDD= 5.0V. $R_L$ = 8 $\Omega$ + 33 $\mu$ H, DC Output Clipping                         | 0.127   |       | Ohm             |

| Rdson-N           | Driver N MOS-FET ON-<br>resistance    | VDDD= 5.0V. $R_L$ = 8 $\Omega$ + 33 $\mu$ H, DC Output Clipping                         | 0.129   |       | Ohm             |

| Fsw               | Switching Frequency                   | Average                                                                                 | 300     |       | kHz             |

|                   | l                                     | Voltage Sense ADC                                                                       |         |       | <u> </u>        |

| THD+N             | ADC Total Harmonic Distortion + Noise | VDDD = 5.5V, +10dBVrms, Class-D off                                                     | 0.004   |       | %               |

| SNR               | Signal to Noise Ratio                 | Flat, 20Hz – 20kHz                                                                      | 101     |       | dB              |

| FS <sub>ADC</sub> | ADC Full Scale Input Level            |                                                                                         | 15.4    |       | V <sub>PK</sub> |

|                   |                                       | Current Sense ADC                                                                       |         |       |                 |

| THD+N             | ADC Total Harmonic Distortion + Noise |                                                                                         | 0.37    |       | %               |

| SNR               | Signal to Noise Ratio                 | Flat, 20Hz – 20kHz                                                                      | 82      |       | dB              |

| FS <sub>ADC</sub> | ADC Full Scale Input Level            |                                                                                         | 4.04    |       | Арк             |

|                   |                                       | Battery Sense ADC                                                                       | •       |       |                 |

| INL               | Integrated Non-Linearity              | VDDD= 2.9V-5.5V (gain & offset compensated)                                             | +/-1    |       | LSB             |

| DNL               | Differential Non-Linearity            | VDDD= 2.9V-5.5V                                                                         | +/-1    |       | LSB             |

| Symbol | Parameter        | Conditions                        | Typical | Limit | Units |  |  |

|--------|------------------|-----------------------------------|---------|-------|-------|--|--|

|        | Class-D          |                                   |         |       |       |  |  |

| Neff   | Power Efficiency | Output Power = 3 W, VDDD= 12 V    | 77      |       | %     |  |  |

|        |                  | Output Power = 6.0 W, VDDD = 12 V | 85      |       | %     |  |  |

|        |                  | Output Power = 9.5 W, VDDD = 12 V | 93      |       | %     |  |  |

Note: \*Shutdown mode: device has supplies without register loaded

<sup>\*\*</sup> Standby Mode: device register settings loaded without I2S clocks appear

<sup>\*\*\*</sup>Idle Channel operating mode: device register loaded and I2S clocks appear without DACIN

# 4.5 Digital I/O Parameters

Table 6 Digital I/O Characteristics

| Parameter            | Symbol            | Comments                           | Comments/Conditions                |                        | Max                    | Units                   |  |

|----------------------|-------------------|------------------------------------|------------------------------------|------------------------|------------------------|-------------------------|--|

| Input LOW level      | VIL               | $V_{DD}B = 1.8V$                   |                                    |                        | 0.3*V <sub>DD</sub> B  | V                       |  |

| Imput LOW level      | VIL               | V <sub>DD</sub> B :                | = 3.3V                             |                        | 0.34*V <sub>DD</sub> B | ]                       |  |

| Input HIGH level     | ViH               | V <sub>DD</sub> B :                | = 1.8V                             | 0.7*V <sub>DD</sub> B  |                        | V                       |  |

| Input i iiGi i ievei | VIH               | V <sub>DD</sub> B :                | = 3.3V                             | 0.66*V <sub>DD</sub> B |                        | - V                     |  |

| Output HIGH level    | V <sub>OH</sub>   | l – 1mΛ                            | V <sub>DD</sub> B=1.8V             | 0.9*V <sub>DD</sub> B  |                        | V                       |  |

| Output Filor Fiever  | VOH               | I <sub>Load</sub> = 1mA            | $V_{DD}B = 3.3V$                   | 0.95*V <sub>DD</sub> B |                        | ]                       |  |

| Output LOW level     | VoL               | I <sub>Load</sub> = 1mA            | $V_{DD}B = 1.8V$                   |                        | 0.1*V <sub>DD</sub> B  | V                       |  |

| Output LOVV level    |                   |                                    | V <sub>DD</sub> B=3.3V             |                        | 0.05*V <sub>DD</sub> B | - V                     |  |

|                      | _                 | Clock Multiplier Enabled N1=1      |                                    | 48                     | 52                     |                         |  |

| MCLK Dutycycle       | D <sub>MCLK</sub> | Clock Multiplier Enabled<br>N1=1/3 |                                    | 44                     | 56                     | %                       |  |

|                      |                   | Clock Multiplier Enabled<br>N1=1   |                                    | -                      | 0.1                    | nsec                    |  |

| MCLK Jitter          | itter jmclk       |                                    | Clock Multiplier Enabled<br>N1=1/3 |                        | 0.3                    | (Standard<br>Deviation) |  |

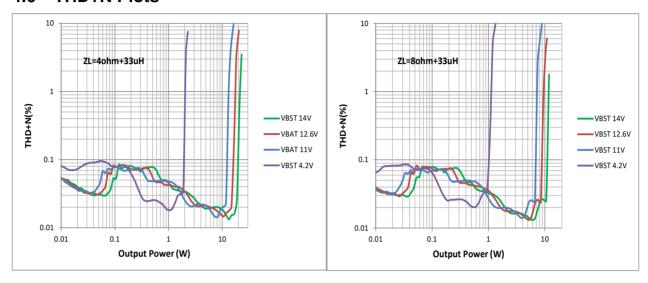

## 4.6 THD+N Plots

Figure 3 THD vs Po

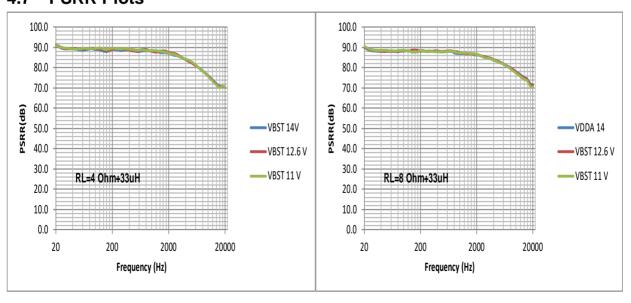

# 4.7 PSRR Plots

Figure 4 VBAT PSRR

Norminized Gain (dB)

2

-2

-10

20

2000

Frequency (Hz)

20000

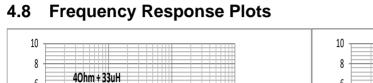

Figure 5 **Frequency Response**

-VBST 14

-VBST 11

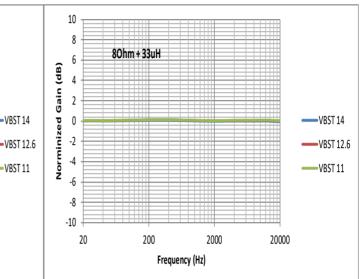

#### **Power Plots** 4.9

200

Figure 6 Efficiency vs Po

#### 5 FUNCTIONAL DESCRIPTION

This chapter provides detailed descriptions of the major functions of the NAU83G20 Monophonic Amplifier.

## 5.1 Inputs

The NAU83G20 provides digital inputs to acquire and process audio signals with high fidelity and flexibility. There is an input path from an I2S/PCM Interface. Additionally, the NAU83G20 has logic control inputs and a temperature monitoring input.

## 5.2 Outputs

The NAU83G20 Amplifier has a Class-D PWM driver that can drive an 8 Ohm speaker up a peak voltage of 14 V. The Class-D output voltage and current sensing data are provided at the I2S/PCM Interface output. Additionally, the NAU83G20 has an output for the interrupt.

## 5.3 ADC, DAC and Digital Signal Processing

The NAU83G20 has two independent, high-quality Analog-to-Digital Converters (ADCs) and one Digital-to-Analog Converter (DAC). These are high-performance, 24-bit sigma-delta converters, which are suitable for a very wide range of applications.

The ADC and DAC blocks also support advanced Digital Signal Processing (DSP) subsystems that enable a very wide range of programmable signal conditioning and signal optimizing functions. All digital processing is done with 24-bit precision to minimize processing artifacts and to maximize the audio dynamic range supported by the NAU83G20.

The ADC and DAC digital signal process can support four-point Dynamic Range Compressors (DRCs), high-pass filters, Automatic Level Control (ALC), soft mute, soft unmute and gain compensation. Two-point DRCs can be programmed to limit the maximum output level and/or amplify a low output level.

# 5.4 Digital Interfaces

Command and control of the device are accomplished by using a Serial Control Interface. The simple, but highly flexible, 2-wire Serial Control Interface is compatible with most commonly used command and control serial data protocols and host drivers, and industry standard I2S and PCM devices.

The digital audio I/O data streams can be transferred separately from command and control using either I2S or PCM audio data protocols.

# 5.5 Power Supply

This NAU83G20 has been designed to operate reliably under a wide range of power supply conditions and Power-On/Power-Off sequences. However, the Electro Static Detection (ESD) protection diodes between the supplies impact the application of the supplies. Because of these diodes, the following conditions need to be met:

VDDD > VDDA - 1.2 V and VDDB > VDDA - 0.6 V

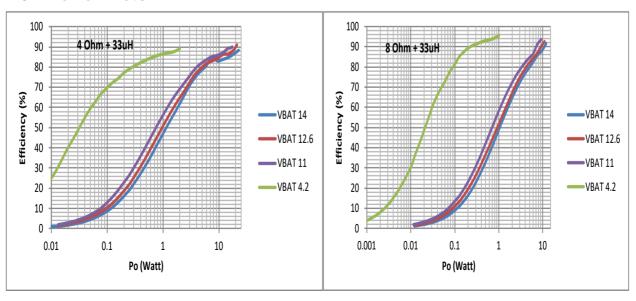

#### 5.6 Power-On-and-Off Reset

The NAU83G20 includes a Power-On-and-Off Reset circuit on-chip. The circuit resets the internal logic control at VDDD and VDDA supply power-up and this reset function is automatically generated internally when power supplies are too low for reliable operation. Reset thresholds are 1.4 V for VDDA during a power-

on ramp and 1.2 V for VDDA during a power-down ramp. Reset thresholds are 1.6 V for VDDD during a power-on ramp, and 1.2 V for VDDD during a power-down ramp. It should be noted that these values are much lower than the required voltage for normal operation of the chip.

The reset is held ON while the power levels for VDDD and VDDA are below their respective thresholds. Once the power levels rise above their thresholds, the reset is released. Once the reset is released, the registers are ready to be written to.

NOTE: It is also important that all the registers should be kept in their reset state for at least 6 µsec.

An additional internal RC filter-based circuit is added which helps the circuit to respond for fast ramp rates (~3 µsec) and to generate the desired reset period width (~3 µsec at typical corner). This filter is also used to eliminate supply glitches which can generate a false reset condition, typically 50 nsec.

For reliable operation, it is recommended to write to register **REG0X00** upon power-up. This will reset all registers to the known default state.

NOTE: When VDDA is below the power-on reset threshold, the digital IO pins will go to a tri-state condition.

Power-on-and-off Reset

# 5.7 Voltage Reference (VREF)

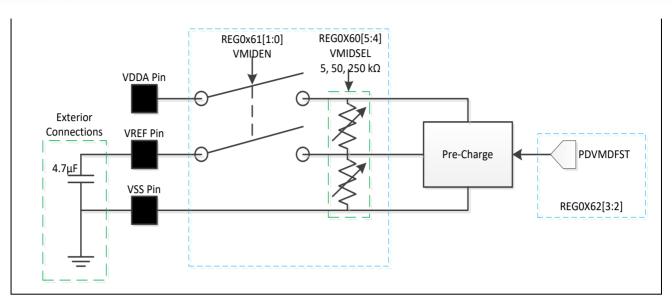

The NAU83G20 includes a mid-supply, reference circuit that produces voltage close to VDDA/2 that is decoupled to VSS through the VREF pin by means of an external bypass capacitor. Because VREF is used as a reference voltage for the majority of the NAU83G20, a large capacitance is required to achieve good power supply rejection at low frequency, typically 4.7  $\mu$ F is used. The Reference Voltage circuitry is shown in **Figure 7**.

Figure 7 VREF Circuitry

The output impedance can be set using VMID\_SEL REG0X60[5:4]. Refer to Table 7.

| VMID_SEL REG0X60[5:4] | VREF Resistor Selection    | VREF Impedance               |

|-----------------------|----------------------------|------------------------------|

| 00                    | Open, no resistor selected | Open, no impedance installed |

| 01                    | 50 kOhm                    | 2 5 kOhm                     |

| 10                    | 250 kOhm                   | 125 kOhm                     |

| 11                    | 5 kOhm                     | 2.5 kOhm                     |

Table 7 VREF Output Impedance Selection

#### **APPLICATION NOTES:**

- Larger capacitances can be used but increase the rise time of VREF and delay the line output signal.

- Due to the high impedance of the VREF pin, it is important to use a low-leakage capacitor.

- A pre-charge circuit has been implemented to reduce the VREF rise time. Once charged, this can be disabled using **PVDMFST REG0X62[3:2]** to save power or to prevent rapid changes in level due to fluctuations in VDDA.

#### 5.8 DAC Soft Mute

The Soft Mute function ramps down the DAC digital volume to zero when it is enabled by **SMUTE\_EN REG0X13[15]**. When disabled, the volume increases to the register-specified volume level for each channel. This function is beneficial for using the DAC without introducing pop-and-click sounds. When **DACEN\_SM REG0X13[13]** is set to '0', the volume will ramp up to the register-specified volume level if the DAC path has been enabled by setting **DACEN REG0X4[3]**. The volume will ramp down to zero if the DAC path is disabled.

#### 5.9 Hardware and Software Reset

The NAU83G20 and all of its control registers can be reset to initial default power-up conditions by writing any value to **REG0X00** *once* using any of the control interface modes. Writing to any other valid register address terminates the reset condition, but all registers will be set to their power-on default values. This is typically done during hardware reset.

The NAU83G20 can be reset to initialized power-up conditions by writing any value to **REG0X01** *twice* using any of the control interface modes. Writing to **REG0X01** will reset the NAU83G20, but all registers values will be unaffected. This is typically done during operation to quickly force NAU83G20 in the known initialized startup state.

#### **5.10 SAR ADC**

The SAR ADC is an 8-bit Analog-to-Digital Converter (ADC) used to detect the voltage level on the VDDD supply voltage, the junction temperature sensor, and the ambient temperature sensor.

#### 5.10.1 SAR ADC Functions

The SAR ADC is enabled by <u>SAR\_ENA\_REGOX07[0]</u>. Setting this bit to 1 enables the SAR ADC; setting the bit to 0 disables the function. After the SAR ADC has been enabled using **SAR\_ENA**, the SAR ADC enters a sampling phase. During this phase, the voltage level on the input is sampled at a speed determined by <u>SAMPLE\_SPEED\_REGOX07[3:2]</u>. This time can be adjusted from 2 µsec to 16 µsec, doubling each step, as shown in Table 8 Voltage Sampling Phase Time. During the sampling phase, the sample signal will be high together with the Most Significant Bit (MSB) and low with the Least Significant Bit (LSB).

| SAMPLE_SPEED_REG0X07[3:2] | Voltage Sampling Time |

|---------------------------|-----------------------|

| 00                        | 2 µsec                |

| 01                        | 4 µsec                |

| 10                        | 8 µsec                |

| 11                        | 16 µsec               |

Table 8 Voltage Sampling Phase Time

The maximum input current of the ADC can be reduced by selecting a bigger input resistor in series with the sampling capacitor. The value of the input resistor can track the sampling time. The SAR series resistor default setting = 001. Additional input limit resister values and settings are shown in Table 9 SAR ADC Current Limit Resistor Selection.

Table 9 SAR ADC Current Limit Resistor Selection

| REL SEL REG0X07[9:7] | Input Resistor Value |

|----------------------|----------------------|

| 000                  | 35 kOhm              |

| 001                  | 70 kOhm              |

| 010                  | 170 kOhm             |

| 011 | 360 kOhm |

|-----|----------|

| 1xx | Short    |

After the sampling phase, the ADC enters a conversion phase that consists of eight compare cycles. Each of these compare cycles can last from 500 nsec to 4 µsec, doubling each step. See Table 10 Compare Cycle Time Settings. Use <a href="COMP SPEED REG0X07[6:5]">COMP SPEED REG0X07[6:5]</a> to adjust the compare time. The total conversion has 8 compare cycles.

| COMP_SPEED REG0X07[6:5] | Time Settings |

|-------------------------|---------------|

| 00                      | 500 nsec      |

| 01                      | 1 µsec        |

| 10                      | 2 µsec        |

| 11                      | 4 µsec        |

Table 10 Compare Cycle Time Settings

#### **APPLICATION NOTE:**

SAMPLE\_SPEED REG0x07[3:2] is used for the SAR ADC sampling rate. Before changing the sampling rate, SAR\_ENA\_REG0X07[0] needs to be set to 0. After the sample speed is set, SAR\_ENA sets to 1.

#### 5.10.2 SAR ADC Control

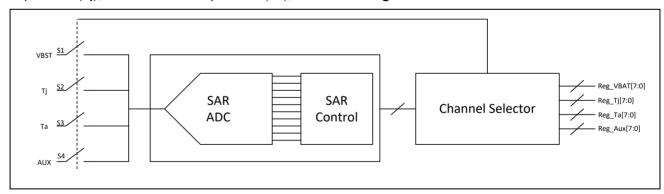

The NAU83G20 needs to process and monitor three inputs: Battery Supply Voltage (VBAT), Junction Temperature (Tj), and Ambient Temperature (Ta), as shown in **Figure 8**.

Figure 8 SAR ADC Control

Notes: The gain for all SAR ADC Channels is fixed to 1.0 \* VDDA; the raw data can be read from <a href="SAR\_ADC\_OUT\_01\_REG0x020">SAR\_ADC\_OUT\_01\_REG0x020</a> and <a href="SAR\_ADC\_OUT\_23\_REG0x021">SAR\_ADC\_OUT\_23\_REG0x021</a>. To convert from raw SAR ADC from <a href="SAR\_ADCOUT\_01">SAR\_ADC\_OUT\_23</a> please refer to the equation below:

$$Ti = [(raw\ Ti) - 89] * 1.6077$$

The SAR ADC reads a full scale of 16.5V on VBAT. Below is a table of the VBAT voltage and the SAR reading

VBAT = ((SAR ADC 0x20 [7:0]) \* 0.0622) + 0.5869

| VBAT (V) | SAR ADC (DEC) |

|----------|---------------|

| 4        | 55            |

| 5        | 71            |

| 6        | 87            |

| 7        | 103           |

| 8        | 119           |

| 9        | 135           |

| 10       | 151           |

| 11       | 168           |

| 12       | 184           |

| 13       | 200           |

| 14       | 216           |

| 15       | 232           |

| 16       | 248           |

| 16.5     | 255           |

Ta requires additional configuration through the output pin to activate its output.

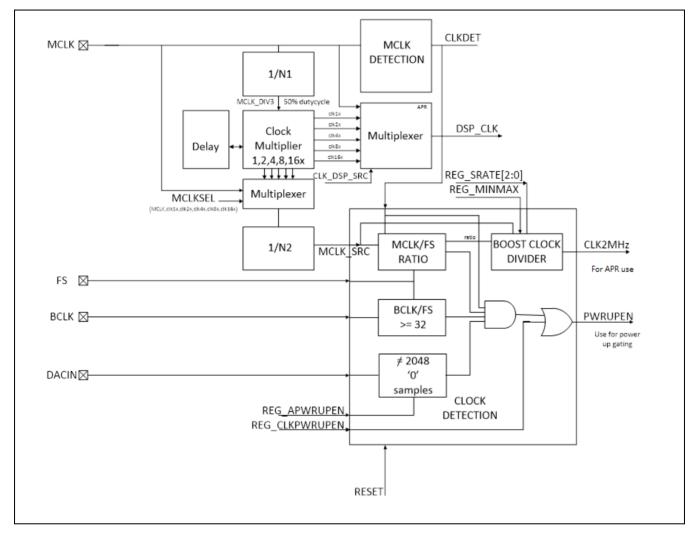

#### 5.11 Clock Detection

The NAU83G20 includes a Clock Detection circuit that can be used to enable and disable the audio paths, based on an initialized audio path setting. Enable the audio path through the I2C Interface; but, the actual power up/down can be gated by the clock detection circuit. Clock detection works with BCLK in 32bits or more than 32bits Fs format. The block diagram of the clock detection circuit is shown in **Figure 9**. Control register is located at **CLK\_DET\_** CTRL\_REG0x40. Divider N1 is selectable as 1, 2 or 3 and divider N2 is selectable as 1, 2, 4, 8.

Figure 9 NAU83G20 Clock Detection Circuit

## 5.11.1 Enabling Clock Detection

Clock detection in the NAU83G20 is enabled by setting **REG\_CLKPWRUPEN** = 0 (default) and meeting three or four conditions, depending on the configuration. If all conditions are met, the **PWRUPEN** signal will be asserted to 1. If any of the conditions are not met, the **PWRUPEN** signal is set to 0.

Conditions for enabling clock detection:

- 1) The NAU83G20 has custom logic clock detection circuits that detect if MCLK is present. Upon MCLK detection, the detector output MCLKDET goes to 1. When the MCLK disappears, MCLKDET goes back to 0. Up to 1 µsec is required to detect MCLK and the MCLK release time is about 50 µsec.

- 2) Clock detection logic uses the CLKDET and MCLK\_SRC to initiate detection of MCLK/FS ratio. MCLK\_SRC is derived from MCLK after programmable multiplication and/or division. The target ratios for MCLK/FS after programmable multiplication and/or division are 256, 400 & 500. When the clock detection logic detects a ratio of between 254 and 258 or between 398 and 402 or between 498 and 502 for one frame sync it will assert a valid MCLK/FS ratio. When the detection logic detects a ratio outside these valid ranges for two consecutive frame syncs it will assert an invalid MCLK/FS ratio. Even though it is required for the ratios to be exact 256, 400 or 500, having two extra cycles tolerance allows for occasional clock jitter, without disabling the audio path.

- 3) Clock detection logic also needs to detect the BCLK to make sure data can be recorded and played back. There needs to be at least 32 BCLK cycles per Frame Sync. MCLK can be used to count the number of BCLK with each Frame Sync.

- 4) If **REG\_APWRUPEN** is set to 1, clock detection will require non-zero samples to enable output of a power-up signal. Any non-zero sample will be sufficient. After power-up, if 2048 zero samples are detected, the **PWRUPEN** signal is asserted to 0. If **REG\_APWRUPEN** is set to 0, this function does not control the **PWRUPEN** signal.

## 5.11.2 Disabling Clock Detection

Clock detection in the NAU83G20 is disabled by setting **REG\_CLKPWRUPEN** to 1. In this state, **PWRUPEN** is no longer controlled by the enabling conditions listed above, but is set to 1. However, the MCLKDET and clock dividers are still active.

The range of the input clocks is shown in **Table 11**.

Table 11 Range of Input Clocks

| Signal                  | Min   | Max    |

|-------------------------|-------|--------|

| Frame Synch (FS) (kHz)  | 8     | 96     |

| Master Clock MCLK (MHz) | 2.048 | 24.576 |

## 5.11.3 Sampling and Over Sampling Rates

Possible Sampling Rate and MCLK SRC selections are shown in Table 12 and

Table 13. Note that **REG SRATE REG 0X40** must be programmed to identify the target sample rate.

Table 12 Sampling and Over Sampling Rates (Ranges 1-3)

| REG_SRATE               |      |       |       |              |      |                            |       |                 |     |           |       |        |

|-------------------------|------|-------|-------|--------------|------|----------------------------|-------|-----------------|-----|-----------|-------|--------|

| Range 1 000 Range 2 001 |      |       |       |              |      |                            |       |                 | Rar | nge 3 01  | 0     |        |

| MCLK_SRC/FS<br>Ratio    | FS ( | (kHz) |       | (_SRC<br>Hz) | FS ( | MCLK_SRC<br>FS (kHz) (MHz) |       | FS (kHz) MCLK_S |     | SRC (MHz) |       |        |

|                         | Min  | Max   | Min   | Max          | Min  | Max                        | Min   | Max             | Min | Max       | Min   | Max    |

| 256                     | 8    | 12    | 2.048 | 3.072        | 16   | 24                         | 4.096 | 6.144           | 32  | 48        | 8.192 | 12.288 |

| 400                     | 8    | 12    | 3.2   | 4.8          | 16   | 24                         | 6.4   | 9.6             | 32  | 48        | 12.8  | 19.2   |

| 500                     | 8    | 12    | 4     | 6            | 16   | 24                         | 8     | 12              | 32  | 48        | 16    | 24     |

Table 13 Sampling and Over Sampling Rates (Ranges 4-5)

| REG_SRATE            |      |             |                   |        |  |  |  |  |

|----------------------|------|-------------|-------------------|--------|--|--|--|--|

|                      |      | Range 4 011 |                   |        |  |  |  |  |

| MCLK_SRC/FS<br>Ratio | FS ( | (kHz)       | MCLK_SRC<br>(MHz) |        |  |  |  |  |

|                      | Min  | Max         | Min               | Max    |  |  |  |  |

| 256                  | 64   | 96          | 16.384            | 24.576 |  |  |  |  |

| 400                  | 64   | 96          | 25.6              | 38.4   |  |  |  |  |

| 500                  | 64   | 96          | 32                | 48     |  |  |  |  |

The only internal MCLK\_SRC/FS ratios allowed are: 256, 400 & 500. The clock divider or multiplier in register 0x03 needs to be setup to achieve one these three possible ratios.

Effective MCLK/FS ratios can be achieved with the clock multiplier under MCLK > 2Mhz condition, as shown in **Table 14**.

Table 14 Effective MCLK/FS Ratios (MCLK > 2Mhz)

| MCLK_SRC/FS ratio | Clock<br>Multiplier<br>(Reg0x03) | Effective ratio MCLK/FS |

|-------------------|----------------------------------|-------------------------|

| 256               | 8                                | 32                      |

| 400               | 8                                | 50                      |

| 500               | 8                                | 62.5                    |

| 256               | 4                                | 64                      |

| 400               | 4                                | 100                     |

| 500               | 4                                | 125                     |

| 256               | 2                                | 128                     |

| 400               | 2                                | 200                     |

| 500               | 2                                | 250                     |

| 256               | 1                                | 256                     |

| 400               | 1                                | 400                     |

| 500               | 1                                | 500                     |

For MCLK\_SRC/FS ratios of 256 the Over Sampling Ratio (OSR) can be set in register 0x28 & 0x29 to: 32, 64, 128 & 256. Note that the ADC & DAC clocks need to be set to their matching values in register 0x03.

■ For MCLK\_SRC/FS ratios of 400 & 500 the Over Sampling Ratio (OSR) is fixed to 100. For MCLK\_SRC/FS ratios of 400 the ADC & DAC clock dividers need to be set to ¼ in register 0x03. For MCLK\_SRC/FS ratios of 500 the ADC & DAC clock dividers are automatically set to 1/5.

## 5.12 High Pass Filters

There is a High-Pass Filter for each ADC Channel and each DAC Channel. The High-Pass Filters may be enabled by setting HPF\_EN REG0X12[15], [13], and [5]. The High-Pass Filter has two operation modes that apply to both channels simultaneously. In the Audio Mode, the filter is a simple first-order DC blocking filter, with a cut-off frequency of 3.7 Hz. In the Application-Specific Mode, the filter is a second-order audio frequency filter, with a programmable cut-off frequency. The programmable filter mode may be enabled by setting HPF\_APP REG0X12[14], [9], and [4].

**Table 15** identifies the cut-off frequencies with different sample rates.

Table 15 High-Pass Filter Cut-Off Frequencies

| HPFCUT | Sample Rate in KHz (FS) |     |                         |     |                      |     |                      |     |  |

|--------|-------------------------|-----|-------------------------|-----|----------------------|-----|----------------------|-----|--|

|        | REG_SRATE=<br>3'b000    |     | E= REG_SRATE=<br>3'b001 |     | REG_SRATE=<br>3'b010 |     | REG_SRATE=<br>3'b011 |     |  |

|        | 8                       | 12  | 16                      | 24  | 32                   | 48  | 64                   | 96  |  |

| 000    | 87                      | 130 | 87                      | 130 | 87                   | 130 | 87                   | 130 |  |

| 001    | 103                     | 155 | 103                     | 155 | 103                  | 155 | 103                  | 155 |  |

| 010    | 132                     | 198 | 132                     | 198 | 132                  | 198 | 132                  | 198 |  |

| 011    | 165                     | 248 | 165                     | 248 | 165                  | 248 | 165                  | 248 |  |

| 100    | 207                     | 311 | 207                     | 311 | 207                  | 311 | 207                  | 311 |  |

| 101    | 265                     | 398 | 265                     | 398 | 265                  | 398 | 265                  | 398 |  |

| 110    | 335                     | 503 | 335                     | 503 | 335                  | 503 | 335                  | 503 |  |

| 111    | 409                     | 614 | 409                     | 614 | 409                  | 614 | 409                  | 614 |  |

#### 5.13 Automatic Level Control

VBAT and VDDD Limit Threshold

The NAU83G20 employs several limit thresholds on the battery voltage VBAT. This limit threshold can be used to program gain changes in order to protect the system from shutting down or to prevent excessive current draw. On VBAT an ALC threshold between 7.75V and 16.25V can be programmed in order to adjust the digital gain when the battery voltage drops due to discharge. The ALC can reduce the output level in order to reduce the power consumed from the battery supply. See the NAU83G20 ALC section below for more details. When the battery voltage drops further down an Under Voltage Lockout Prevention (UVLOP) threshold can be set between 10.0V and 4.5V in order to limit the input current. This will prevent large currents from being drawn at low battery voltages as the device tries to supply the load and allow for the battery voltage to recover such that it does not approach the Under Voltage Lockout Threshold (UVLO). In addition, a second gain limiter can be activated to reduce the gain even further at a faster attack rate. The operation of this limiter will be described in this specification.

When the battery drops even further down despite the gain and current limiters, the class-D driver will shut down at the Under Voltage Lockout Threshold (UVLO) threshold of about 4.0V. If the VBAT drops even further below 1.6V then the device control and registers will reset.

On the VBAT output, the NAU83G20 employs only two limits. The NAU83G20 VBAT has an Over Voltage LockOut (OVLO) voltage of about 16.5V. If VBAT reaches above this voltage, the class-D driver will shut down and the outputs will remain at ground until the VBAT reaches below the OVLO threshold.

This section describes the various level control options based on the thresholds outlined above.

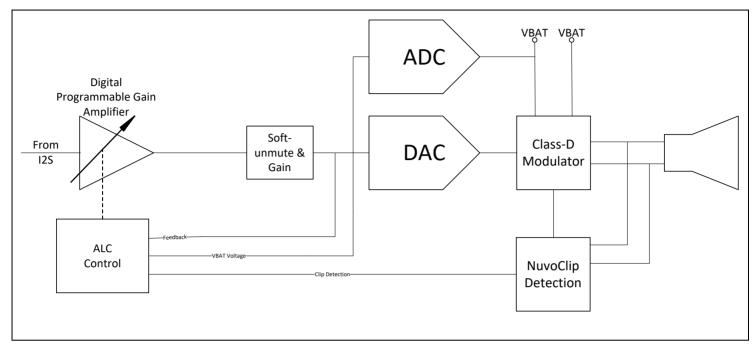

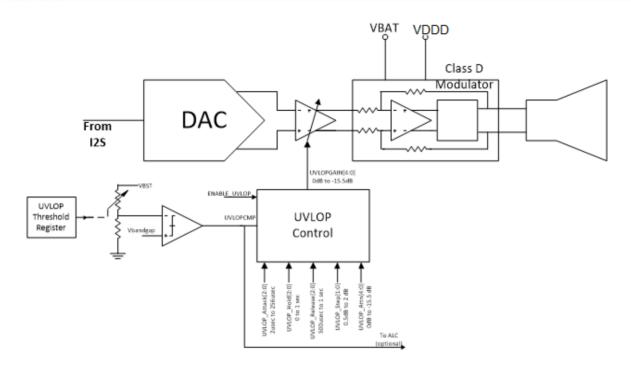

The digital Automatic Level Control (ALC) supports the input digital audio path of the NAU83G20 by providing an optimized signal level at the output of the Class-D Amplifier. This is achieved by automatically decreasing the amplitude of the input signal according to the user's set amplitude, clipping, or low battery voltage, and restoring amplitude when conditions are lifted. **Figure 10** illustrates the basic relationship of the ALC to other major functions of the NAU83G20.

Figure 10 Automatic Level Control

## 5.13.1 ALC Operation

The ALC is enabled by <u>ALC CTRL3.ALC EN REG0x2E[15]</u> and operates according to the Limiter Mode register <u>ALC\_CTRL3.LIM\_MDE\_REG0x2E[14:12]</u>. It uses feedback to detect the signal output level from either the output of the digital Programmable Gain Amplifier (dPGA) or output of the soft mute gain compensation through a Peak Detector, set by <u>ALC\_CTRL4.PEAK\_SEL\_REG0x2F[13]</u>. Using the output of the dPGA provides a direct feedback for control while using the output of the soft mute gain compensation allows for the ALC to adjust based on the activation of the soft mute, deactivating when the soft-mute function drops the signal below the user's set amplitude or reactivating when disabling the soft mute when signal rises above the set amplitude and/or clipping. More information can be read about the soft mute in Section <u>5.8</u>.

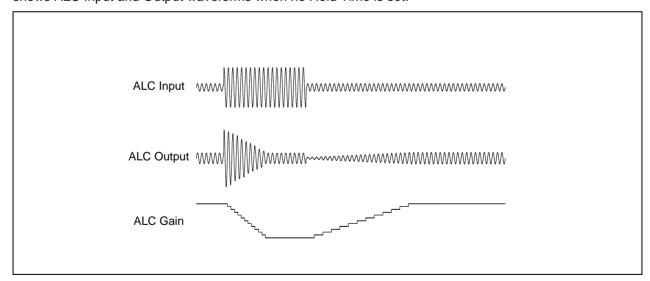

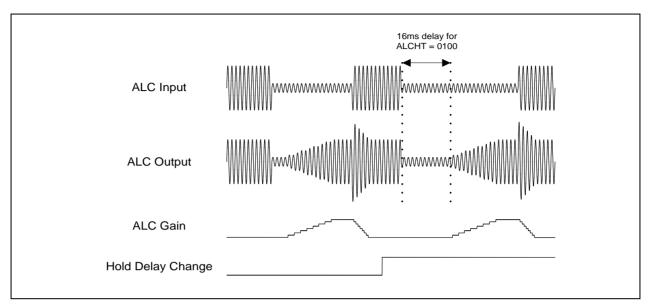

The Peak Detector can be configured by either using a full-wave rectification peak, ensuring equal ALC operation on both positive and negative signals, or absolute value calculated peak, which updates at every peak and degrades until a new peak is detected. This is set in ALC\_CTRL1.ALCPKSEL\_REG0x2C[11]. Additionally, the ALC can update either from the zero crossing point of the signal or immediately upon triggering. This is determined by the register ALC\_CTRL1.ALC\_ZC\_REG0x2C[14] and when enabled also overrides the register ALC\_CTRL4.LPGAZC\_REG0x2F[14] to ensure zero crossing point reference consistency. ALC updating on the zero crossing point ensures that if the ALC responds faster than the signal degrades, the ALC will wait until the signal reaches close to zero before changing the gain on the dPGA, or input signal gain. This may be helpful depending on the application and can reduce popping on speakers. If immediate action is needed for input signal attenuation then ALC ZC can be disabled. The ALC has three operational states: ALC Attack, ALC Release, and ALC Hold. In the ALC Attack state, the ALC decreases the dPGA gain at a single dB decrement at a time, gradually based on the ALCATK register; in the ALC Release state, the ALC increases the dPGA gain at a single dB increment at a time gradually based on the ALCDCY register; in the ALC Hold state, the ALC holds constant the dPGA gain for a specified time determined by the ALCHLD register. While the attack state is immediate upon meeting conditions, the ALC will enter the hold state before releasing the signal. This is to account for any noise or fluctuations that may occur on the input signal.

The registers below are used in every ALC operational mode that are defined in ALC CTRL3.LIM MDE REG0x2E[14:12].

- ALC\_CTRL3.ALC\_EN\_REG0x2E[15] ALC Enable Register, enables the ALC for operation.

- ALC\_CTRL1.ALCPKSEL\_REG0x2C[11] Selects between full-wave rectification peak (0) or absolute value calculated peak (1).

- <u>ALC\_CTRL1.ALC\_ZC\_REG0x2C[14]</u> Selects whether the ALC should update immediately at peak detection or at the zero crossing point of the signal. This is recommended as it prevents sudden changes that may occur.

- ALC\_CTRL1.ALCMAXGAIN\_REG0x2C[7:5] The maximum gain level allowed to be set by the ALC on the dPGA when enabled. This is applied automatically when ALC is enabled and acts as the upper limit the input signal is allowed until ALC is disabled.

- ALC\_CTRL1.ALCMINGAIN\_REG0x2C[3:1] The minimum gain level allowed to be set by the ALC on the dPGA when enabled. This acts as the lowest limit the input signal is allowed until the ALC is disabled.

- ALC CTRL2.ALCDCY REG0x2D[15:12] The rate at which the ALC will *release*, or increase the gain of, the signal determined by step time doubling its increment from 2µs to 4196µs at 0.1875dB per step. Typically, the decay time is much slower than the attack time. When the DAC output level is below the ALC Target value by at least 1.5 dB, the gain increases at a rate determined by this parameter. In Limiter Mode, the time constants are faster than in ALC mode.

- ALC\_CTRL2.ALCATK\_REG0x2D[11:8] The rate at which the ALC will attack, or attenuate, the signal determined by step time doubling its increment from 2μs to 4196μs at 0.1875dB per step. Typically, the attack time is much faster than the decay time. In the NAU83G20, when the absolute value of the DAC output exceeds the ALC Target Value ALCLVL, the gain will be reduced at a step-size and rate determined by this parameter. When the peak DAC output is at least 1.5 dB lower than the ALCLVL, the stepped gain reduction will halt.

- ALC CTRL2.ALCHLD REG0x2D[7:4] The length of time at which the ALC will hold the signal for, ranging from 0ms to 512ms. Hold time refers to the duration of time when no action is taken. This is typically used to avoid undesirable sounds that can happen when an ALC responds too quickly to a changing input signal. In the NAU83G20, the hold time value is the duration of time that the ADC output peak value must be less than the target value, ALCLVL, before there is an actual gain increase.

- ALC\_CTRL2.ALCLVL\_REG0x2D[3:0] A requirement for the input signal level to hold at after clearing the conditions specified in each of the ALC operational mode for the amount of time set in the ALCHLD register before entering the ALC Release state, or increase the gain of the dPGA at the rate specified by the ALCDCY register. This value is expressed as a fraction of Full Scale (FS) output from the DAC. Depending on the logic conditions, the output value used in the comparison may be either the instantaneous value of the DAC or a time weighted average of the DAC peak output level.

NOTE: See Chapter 6 Registers 0x2C to 0x2F for more information regarding settings for ALC functions.

The following are different operational modes allowed by the **LIM MDE** control register:

- Clip Limiting Mode

- Low-Battery Clip Limiting Mode

- Normal Limiting Mode

- Low-Battery Limiting Mode

- Low-Battery Limiting Mode with Preprogrammed VBAT Ratio

**NOTE:** The gain range for the **dPGA** is restricted between **ALCMAXGAIN** and **ALCMINGAIN**. Upon enabling of the ALC, the **dPGA** is automatically set to the **ALCMAXGAIN** and when an ALC event triggers, the gain is adjusted according to the conditions as long as the target attenuation level is below the **ALCMAXGAIN** and above the **ALCMINGAIN** restrictions.

#### 5.13.1.1 Clip Limiting Mode

#### Registers used in Clip Limiting Mode:

- ALC\_CTRL3.LIM\_MDE\_REG0X2E[14:12] = 000 ALC limiter mode set to 000 for operation based on clipping

- ALC\_CTRL4.ALCCLIPSTEP Reg0x2F[12:10] Maximum attenuation adjustment level as a comparison from the level clipping is detected. This value can range between the ranges of 0 to -1.75dB and will act as a soft wall, limiting the max gain change in each Attack State session or clipping event. This adjustment is limited by the ALCMINGAIN register, restricted to -32dB in this mode, where the maximum attenuation change cannot surpass this value.

- <u>CLIP\_CTRL\_Reg0x69[4]</u> Activation register for clip detection circuit is set to enable for detecting clipping. This is required to detect clipping in this mode.

#### Description:

In Clip Limiting Mode, ALC\_CTRL3.LIM\_MDE\_REG0X2E[14:12]=000, the DAC output is programmed to limit clipping by lowering the dPGA gain when clipping is detected. Immediately upon enable, the ALC will set the dPGA gain according to the ALCMAXGAIN value without delay or decay. A clip detection signal is provided by the NuvoClip detection circuit so long as the CLIP\_CTRL register is enabled. As soon as a clipping event is detected, the ALC goes into the Attack State, lowering the dPGA gain at the preprogrammed rate in the ALCATK register. This continues until the clipping detection no longer detects a clipping signal or if the maximum attenuation (CLIP\_GAINADJUST) per clipping event has been reached. If another consecutive clipping event occurs the ALC gain continues ramping down until another maximum attenuation (CLIP\_GAINADJUST) per clipping event has been reached or until the ALCMINGAIN has been reached. The gain setting applied by this method will remain constant until the output signal no longer clips AND the input signal level becomes 1.5dBFS below the ALC Target Level specified in the ALCLVL register for the entirety of the ALC Hold state specified in the ALC Hold Register ALCHLD, before the ALC enters the Release State to increase the gain at the rate specified in the ALCDCY register until the signal is at full scale or it clips again. If clipping again, the ALC will repeat this process to ensure no clipping.

<u>Example Problem Set</u>: Ensure that no clipping occurs. Limit the attenuation and release rate by a manageable amount to prevent any audible change.

### Register Settings for problem set:

- ALC CTRL1.REG0x2C = 0x20E2

- [14] ALC\_ZC set to update the ALC instantaneously prevent clipping as soon as possible

- o [11] ALCPK\_SEL set to update Peak Detection on rectified value.

- [7:5] <u>ALCMAXGAIN</u> set to 0dB. The absolute maximum gain that the dPGA is allowed. Upon enable, the ALC will immediately set the dPGA to this level and will restrict the *Release* state from going beyond this level.

- o [3:1] <u>ALCMINGAIN</u> set to -6dB. The absolute minimum gain that the **dPGA** is allowed. Upon enable, the ALC will restrict the *Attack* state from going beyond this level.

- The rest is left at default.

####

- [15:12] <u>ALCDCY</u> set to 16ms/step at 0.1875dB *increase* per step. Main occurrence in the ALC *Release* state. After each step the signal peak level is compared to the <u>ALCLVL</u> register. If the signal peak is *lower*, then the ALC takes another step. If the signal peak is *higher*, then the ALC enters the ALC *Attack* state. This setting is the recommended rate but can be adjusted to be faster or slower depending on user design.

- [11:8] <u>ALCATK</u> set to 16us/step at 0.1875dB *decrease* per step. Main occurrence in the ALC *Attack* state. After each step the signal peak level is compared to the <u>ALCLVL</u> register. If the signal peak is higher, then the ALC takes another step. If the signal peak is lower, then the ALC enters the ALC *Hold* state. This setting is the recommended rate but can be adjusted to be faster or slower depending on user design.

- [7:4] <u>ALCHLD</u> set to 32ms pause that occurs after the ALC *Attack* state where the ALC attenuates the signal based on the rate set in the <u>ALCATK</u> register. After occurring, the ALC will enter the ALC *Release* state. This setting is the recommended delay but can be adjusted to be faster or slower depending on user design.

- [3:1] <u>ALCLVL</u> set to -3dBFS. This is the comparison level which triggers the state of the ALC to go into Release or Hold and can affect stability of the signal.

- The rest is left at default.

- ALC\_CTRL3.REG0x2E = 0x8010

- [15] <u>ALC EN</u> is set to 1. This is the ALC Enable bit and should be the last register to write to ensure proper setup.

- o [14:12] **LIM\_MDE** is set to 000. This is set to Clip Limiting mode and follows the operation explained in the description portion of this section.

- o The rest is left at default.

- ALC\_CTRL4.REG0x2F = 0x0C20

- o [12:10] ALCCLIPSTEP set to -0.75dB as a soft-wall to change at a single clipping event.

- CLIP\_CTRL\_REG0x69 = 0x0010

- o [4] Enable the Nuvo Clip Detection Circuit.

The register settings above should be implemented as either part of or after the desired ON-sequence. To ensure proper sequence control, use I<sup>2</sup>C to write to each of the addresses in the following sequence from first to last: *0x2C*, *0x2D*, *0x2E*. The register *0x2E* is written to last as it holds the enable bit and will ensure proper activation of the ALC.

## 5.13.1.2 Low VBAT Clip Limiting Mode

Registers used in Low Battery Clip Limiting Mode:

- ALC\_CTRL3.LIM\_MDE\_REG0x2E[14:12] = 001 ALC limiter mode set to 001 for operation based on low battery and clipping mode

- ALC CTRL3.VBAT THRESHOLD REG0x2E[9:5] VBAT threshold value as an additional condition for ALC activation. This can be paired with other conditions or can require additional settings depending on the ALC operational mode.

- ALC\_CTRL4.ALCCLIPSTEP\_Reg0x2F[12:10] Maximum attenuation adjustment level as a comparison from the level clipping is detected. This value can range between the ranges of 0 to -1.75dB and will act as a soft wall, limiting the max gain change in each Attack State session or clipping event. This adjustment is limited by the ALCMINGAIN register, restricted to -32dB in this mode, where the maximum attenuation change cannot surpass this value.

- <u>CLIP CTRL Reg0x69[4]</u> Activation register for clip detection circuit is set to enable for detecting clipping. This is required to detect clipping in this mode.

#### **Description:**

In Low VBAT Clip Limiting Mode, ALC\_CTRL3.LIM\_MDE\_REG0x2E[14:12]=001, the DAC output is programmed to limit clipping by lowering the dPGA gain when clipping is detected with the condition of activating during low battery voltage operation. Immediately upon enable, the ALC will set the dPGA gain according to the ALCMAXGAIN value without delay or decay. A clip detection signal is provided by the NuvoClip detection circuit so long as the CLIP\_CTRL register is enabled. Immediately when a clipping event is detected AND the VBAT voltage is below the voltage specified in the VBAT\_THRESHOLD register, ALC will go into ALC Attack state, lowering the dPGA gain at the pre-programmed rate specified in the ALCATK register until the clipping detection no longer detects a clipping signal or if the maximum attenuation (CLIP\_GAINADJUST) per clipping event has been reached. If another consecutive clipping event occurs the ALC gain continues ramping down until another maximum attenuation (CLIP GAINADJUST) per clipping event has been reached or until the ALCMINGAIN has been reached. If either of the conditions are lifted, i.e. battery voltage is above **VBAT THRESHOLD** or the clipping is no longer detected, then the ALC will wait until the input signal level becomes 1.5dBFS below the ALC Target Level, set in the ALCLVL register, for the period of the ALC Hold state, based on time specified in the ALCHLD register. The ALC will then enter the Release state, increasing the gain at the rate specified in the ALCDCY register until reaching the maximum gain allowed, ALCMAXGAIN, or another clipping event is detected.

<u>Example Problem Set</u>: Ensure that no clipping occurs when VBAT lowers below 3.83V, this is most likely to happen when using a battery. Limit the attenuation and release rate by a manageable amount to prevent any audible change.

#### Register Settings for problem set:

### $ALC_CTRL1.Reg0x2C = 0x20E2$

- o [14] ALC\_ZC set to update the ALC instantaneously prevent clipping as soon as possible

- o [11] **ALCPK SEL** set to update Peak Detection on rectified value.

- o [7:5] ALCMAXGAIN set to 0dB. The absolute maximum gain that the dPGA is allowed. Upon enable, the ALC will immediately set the dPGA to this level and will restrict the *Release* state from going beyond this level.

- o [3:1] **ALCMINGAIN** set to -6dB. The absolute minimum gain that the **dPGA** is allowed. Upon enable, the ALC will restrict the *Attack* state from going beyond this level.

- The rest is left at default.

## ■ ALC\_CTRL2.REG0x2D = 0x5353

- [15:12] <u>ALCDCY</u> set to 16ms/step at 0.1875dB *increase* per step. Main occurrence in the ALC *Release* state. After each step the signal peak level is compared to the <u>ALCLVL</u> register. If the signal peak is *lower*, then the ALC takes another step. If the signal peak is *higher*, then the ALC enters the ALC *Attack* state. This setting is the recommended rate but can be adjusted to be faster or slower depending on user design.

- [11:8] <u>ALCATK</u> set to 16us/step at 0.1875dB *decrease* per step. Main occurrence in the ALC *Attack* state. After each step the signal peak level is compared to the <u>ALCLVL</u> register. If the signal peak is higher, then the ALC takes another step. If the signal peak is lower, then the ALC enters the ALC *Hold* state. This setting is the recommended rate but can be adjusted to be faster or slower depending on user design.

- [7:4] <u>ALCHLD</u> set to 32ms pause that occurs after the ALC *Attack* state where the ALC attenuates the signal based on the rate set in the <u>ALCATK</u> register. After occurring, the ALC will enter the ALC *Release* state. This setting is the recommended delay but can be adjusted to be faster or slower depending on user design.

- [3:1] <u>ALCLVL</u> set to -3dBFS. This is the comparison level which triggers the state of the ALC to go into Release or Hold and can affect stability of the signal.

- The rest is left at default.

### ALC CTRL3.REG0x2E = 0x9310

- [15] <u>ALC\_EN</u> is set to 1. This is the ALC Enable bit and should be the last register to write to ensure proper setup.

- [14:12] <u>LIM\_MDE</u> is set to 001. This is set to Low VBAT Clip Limiting mode and follows the operation explained in the description portion of this section.

- o [9:5] **VBAT\_THRESHOLD** is set to 9.75V to ensure ALC activation at this voltage.

- The rest is left at default.

- ALC CTRL4.Reg0x2F = 0x0C20

- o [12:10] ALCCLIPSTEP set to -.75dB as a soft-wall to change at a single clipping event.

- <u>CLIP CTRL REG0</u>x69 = 0x0010

- o [4] Enable the Nuvo Clip Detection Circuit.

The register settings above should be implemented as either part of or after the desired ON-sequence. To ensure proper sequence control, use I<sup>2</sup>C to write to each of the addresses in the following sequence from first to last: *0x2C*, *0x2D*, *0x2E*. The register *0x2E* is written to last as it holds the enable bit and will ensure proper activation of the ALC.

# 5.13.1.3 Normal Limiting Mode

Registers used in Normal Limiting Mode:

ALC\_CTRL3.LIM\_MDE\_REG0x2E[14:12]=010 - ALC limiter mode set to 010 for operation based on user's set amplitude.

### Description:

In **Normal Limiting Mode**, <u>ALC\_CTRL3.LIM\_MDE REG0x2E[14:12] =010</u>, a maximum DAC output level is programmed to limit the full scale output level. Immediately upon enable, the ALC will set the **dPGA** gain according to the <u>ALCMAXGAIN</u> value without delay or decay. The signal peak is read continuously until the level reaches above the user's set amplitude in the <u>ALCLVL</u> register. Upon overstepping the set amplitude, the ALC will enter the *Attack* state, lowering the **dPGA** gain at the pre-programmed rate specified in the

<u>ALCATK</u> register until the peak detector returns a lower level than the <u>ALCLVL</u> register. When the input signal level becomes 1.5dBFS below the ALC target level (<u>ALCLVL</u> register), then the ALC enters *Hold* state, holding the **dPGA** gain for a specified time determined by the <u>ALCHLD</u> register. The ALC then goes into the *Release* state, increasing the **dPGA** gain at the pre-programmed rate specified in the <u>ALCDCY</u> register until the **dPGA** gain is at maximum or until the peak returns a level above the <u>ALCLVL</u> register, in which the ALC will be triggered and enter the *Attack* state again.

<u>Example Problem Set</u>: Limit maximum output to not exceed -3dBFS limit and update on the zero crossing point to prevent any spontaneous change in the signal. Limit the attenuation and release rate by a manageable amount to prevent any audible change.

### Register Settings for problem set:

### ■ ALC CTRL1.REG0x2C = 0x68E2

- o [14] <u>ALC\_ZC</u> set to update the ALC on the zero crossing point of the signal, so there is no instantaneous changes on the signal when ALC adjusts.

- o [11] ALCPK SEL set to update Peak Detection on a calculated absolute value.

- [7:5] <u>ALCMAXGAIN</u> set to 0dB. The absolute maximum gain that the dPGA is allowed. Upon enable, the ALC will immediately set the dPGA to this level and will restrict the *Release* state from going beyond this level.

- [3:1] <u>ALCMINGAIN</u> set to -6dB. The absolute minimum gain that the dPGA is allowed. Upon enable, the ALC will restrict the *Attack* state from going beyond this level.

- The rest is left at default.

### ■ ALC CTRL2.REG0x2D = 0x5353

- [15:12] <u>ALCDCY</u> set to 16ms/step at 0.1875dB *increase* per step. Main occurrence in the ALC *Release* state. After each step the signal peak level is compared to the <u>ALCLVL</u> register. If the signal peak is *lower*, then the ALC takes another step. If the signal peak is *higher*, then the ALC enters the ALC *Attack* state. This setting is the recommended rate but can be adjusted to be faster or slower depending on user design.

- [11:8] <u>ALCATK</u> set to 16us/step at 0.1875dB *decrease* per step. Main occurrence in the ALC *Attack* state. After each step the signal peak level is compared to the <u>ALCLVL</u> register. If the signal peak is higher, then the ALC takes another step. If the signal peak is lower, then the ALC enters the ALC *Hold* state. This setting is the recommended rate but can be adjusted to be faster or slower depending on user design.

- o [7:4] <u>ALCHLD</u> set to 32ms pause that occurs after the ALC *Attack* state where the ALC attenuates the signal based on the rate set in the <u>ALCATK</u> register. After occurring, the ALC will enter the ALC *Release* state. This setting is the recommended delay but can be adjusted to be faster or slower depending on user design.

- [3:1] <u>ALCLVL</u> set to -3dBFS. The main component for ALC Normal Limiting Mode. This is the comparison level which triggers the state of the ALC to go into Attack, Release, or Hold as mentioned above.

- The rest is left at default.

###

- [15] <u>ALC\_EN</u> is set to 1. This is the ALC Enable bit and should be the last register to write to ensure proper setup.

- [14:12] <u>LIM MDE</u> is set to 010. This is set to Normal Limiting mode and follows the operation explained in the description portion of this section.

- o The rest is left at default.

##

Left at default settings

The register settings above should be implemented as either part of or after the desired ON-sequence. To ensure proper sequence control, use I<sup>2</sup>C to write to each of the addresses in the following sequence from first to last: *0x2C*, *0x2D*, *0x2E*. The register *0x2E* is written to last as it holds the enable bit and will ensure proper activation of the ALC.

# 5.13.1.4 Low Battery Limiting Mode

Registers used in Low Battery Limiting Mode:

- ALC\_CTRL3.LIM\_MDE\_REG0x2E[14:12]=011 ALC limiter mode set to 011 for operation based on low battery mode.

- ALC\_CTRL3.VBAT\_THRESHOLD\_REG0x2E[9:5] VBAT threshold value as the condition for ALC activation within <u>LIM\_MDE</u> = 011 and 100. The available values range from 7.75V (11111) to 16.25V (00000) at ~0.25V steps. For exact values, please refer to the Section <u>5.23</u>, the Control Register List.

### Description:

In **Low-Battery Limiting Mode**, <u>ALC\_CTRL3.LIM\_MDE\_REG0x2E[14:12]=011</u>, a maximum DAC output level is programmed to limit the full scale output level with the additional constraint of low-battery activation. Immediately upon enable, the ALC will set the **dPGA** gain according to the <u>ALCMAXGAIN</u> value without delay or decay.

The ALC activates when the VBAT voltage declines below the set value in the <u>VBAT\_THRESHOLD</u> register. The signal peak is read continuously until the level reaches above the user's set amplitude in the <u>ALCLVL</u> register. Upon overstepping the set amplitude, the ALC will enter the *Attack* state, lowering the <u>dPGA</u> gain at the pre-programmed rate specified in the <u>ALCATK</u> register until the peak detector returns a lower level than the <u>ALCLVL</u> register.