### General Description

The MX7837/MX7847 are dual, 12-bit, multiplying, voltage-output digital-to-analog converters (DACs). Each DAC has an output amplifier and a feedback resistor. The output amplifier is capable of developing ±10V across a  $2k\Omega$  load. The amplifier feedback resistor is internally connected to V<sub>OUT</sub> on the MX7847. No external trims are required to achieve full 12-bit performance over the entire operating temperature range.

The MX7847 has a 12-bit parallel data input, whereas the MX7837 operates with a double-buffered 8-bit-bus interface that loads data in two write operations. All logic signals are level triggered and are TTL and CMOS compatible. Fast timing specifications make these DACs compatible with most microprocessors.

## Applications

Small Component-Count Analog Systems

Digital Offset/Gain Adjustments

**Industrial Process Control**

**Function Generators**

**Automatic Test Equipment**

**Automatic Calibration**

Machine and Motion Control Systems

Waveform Reconstruction

Synchro Applications

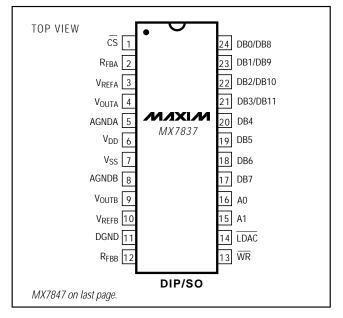

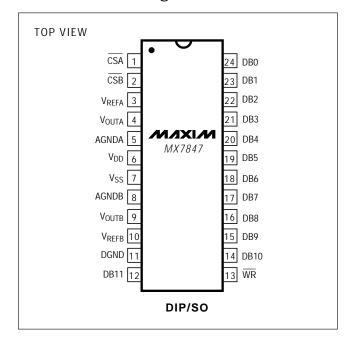

## Pin Configurations

#### **Features**

- **♦ Two 12-Bit Multiplying DACs with Buffered Voltage Output**

- Specified with ±12V or ±15V Supplies

- ♦ No External Adjustments Required

- ♦ Fast Timing Specifications

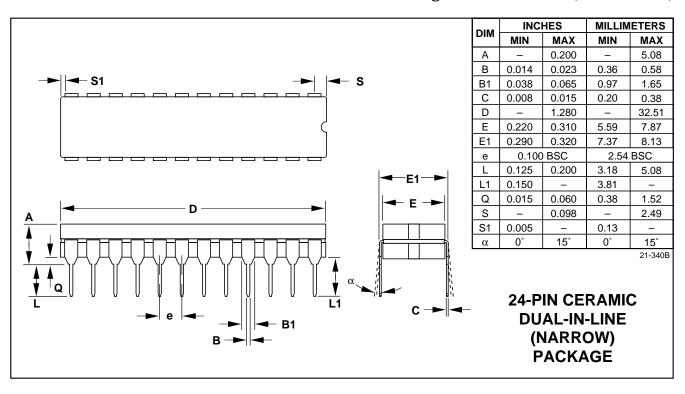

- 24-Pin DIP and SO Packages

- ♦ 12-Bit Parallel Interface (MX7847) 8-Bit + 4-Bit Interface (MX7837)

### Ordering Information

| PART             | TEMP. RANGE  | PIN-PACKAGE           | ERROR<br>(LSB) |

|------------------|--------------|-----------------------|----------------|

| <b>MX7837</b> JN | 0°C to +70°C | 24 Narrow Plastic DIP | ±1             |

| MX7837KN         | 0°C to +70°C | 24 Narrow Plastic DIP | ±1/2           |

| MX7837JR         | 0°C to +70°C | 24 Wide SO            | ±1             |

| MX7837KR         | 0°C to +70°C | 24 Wide SO            | ±1/2           |

| MX7837C/D        | 0°C to +70°C | Dice*                 | ±1             |

#### Ordering Information continued on last page.

Contact factory for availability and processing to MIL-STD-883.

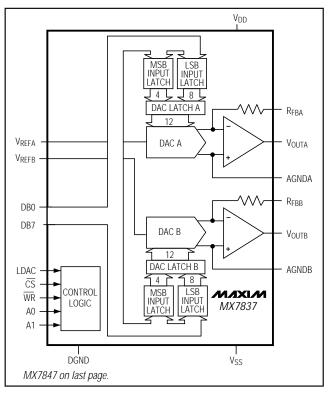

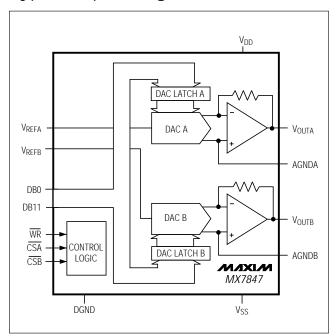

## Typical Operating Circuits

/U/IXI/U

#### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>DD</sub> to DGND, AGNDA, AGNDB                                    | 0.3V to +17V                    |

|--------------------------------------------------------------------------|---------------------------------|

| V <sub>SS</sub> to DGND, AGNDA, AGNDB (Note 1).                          | +0.3V to -17V                   |

| V <sub>REFA</sub> , V <sub>REFB</sub> to AGNDA, AGNDB (V <sub>SS</sub> - |                                 |

| AGNDA, AGNDB to DGND                                                     | $0.3V$ to $(V_{DD} + 0.3V)$     |

| V <sub>OUTA</sub> , V <sub>OUTB</sub> to AGNDA, AGNDB(V <sub>SS</sub>    | $- 0.3V$ ) to $(V_{DD} + 0.3V)$ |

| R <sub>FBA</sub> , R <sub>FBB</sub> to AGNDA, AGNDB(V <sub>SS</sub> -    | 0.3V) to $(V_{DD} + 0.3V)$      |

| Digital Inputs to DGND                                                   | $0.3V$ to $(V_{DD} + 0.3V)$     |

| Continuous Power Dissipation ( $T_A = +70^{\circ}$                       | C)                              |

| Narrow Plastic DIP (derate 13.33mW/°C ab                                 | ove +70°C)1067mW                |

| SO (derate 11.76mW/°C above +70°C)                                       | 941mW                           |

| Narrow CERDIP (derate 12.50mW/°C about                                   | ove +70°C)1000mW                |

|                                                                          |                                 |

| Operating Temperature Ranges:       |                |

|-------------------------------------|----------------|

| MX78_7J_/K                          | 0°C to +70°C   |

| MX78_7A_/B                          | 40°C to +85°C  |

| MX78_7SQ/TQ                         | 55°C to +125°C |

| Storage Temperature Range           | 65°C to +150°C |

| Lead Temperature (soldering, 10sec) | +300°C         |

|                                     |                |

**Note 1:** If V<sub>SS</sub> is open-circuited with V<sub>DD</sub> and either AGND applied, the V<sub>SS</sub> pin will float positive exceeding the *Absolute Maximum Ratings*. If this possibility exists, a Schottky diode connected between V<sub>SS</sub> and GND ensures the maximum ratings will be observed.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{DD}=11.4V~to~16.5V,~V_{SS}=-11.4V~to~-16.5V,~AGNDA=AGNDB=DGND=0V,~V_{REFA}=V_{REFB}=+10V,~R_L=2k\Omega,~C_L=100pF,~V_{OUT}~connected~to~R_{FB}~(MX7837),~T_A=T_{MIN}~to~T_{MAX},~unless~otherwise~noted.)~(Note~2)$

| PARAMETER                                                    | SYMBOL           |                                                        | CONDITIONS                   |             | MIN | TYP  | MAX  | UNITS |

|--------------------------------------------------------------|------------------|--------------------------------------------------------|------------------------------|-------------|-----|------|------|-------|

| STATIC PERFORMANCE (                                         | Note 3)          |                                                        |                              |             |     |      |      |       |

| Resolution                                                   | N                |                                                        |                              |             | 12  |      |      | Bits  |

| Dolativo Acquirocy                                           | INL              | MX78_7J/A/S                                            |                              |             |     |      | ±1   | LSB   |

| Relative Accuracy                                            | IINL             | MX78_7K/B/T                                            |                              |             |     |      | ±1/2 | LSD   |

| Differential Nonlinearity                                    | DNL              | Guaranteed mond                                        | otonic                       |             |     |      | ±1   | LSB   |

|                                                              |                  |                                                        | T <sub>A</sub> = +25°C       |             |     |      | ±2   |       |

| Zero-Code Offset Error                                       |                  | Loaded with all 0s,<br>tempco =                        |                              | MX78_7J/A   |     |      | ±4   | mV    |

| Zero-Code Offset Lifor                                       |                  | ±5µV/°C typ                                            | $T_A = T_{MIN}$ to $T_{MAX}$ | MX78_7K/B   |     |      | ±3   | mv    |

|                                                              |                  | , , ,                                                  |                              | MX78_7S/T   |     |      | ±5   | ]     |

|                                                              |                  | Loaded with all 1s,<br>tempco = ±2ppm<br>of FSR/°C typ | T <sub>A</sub> = +25°C       | MX78_7J/A/S |     |      | ±5   |       |

| Gain Error                                                   |                  |                                                        | l ''                         | MX78_7K/B/T |     | ±2   | LSB  |       |

|                                                              |                  |                                                        | TA - THAIRL TO THANK MIX     | MX78_7J/A/S |     |      | ±7   |       |

|                                                              |                  |                                                        |                              | MX78_7K/B/T |     |      | ±4   |       |

| REFERENCE INPUTS                                             |                  |                                                        |                              |             |     |      |      |       |

| V <sub>REF</sub> Input Resistance                            |                  |                                                        |                              |             | 8   | 10   | 13   | kΩ    |

| V <sub>REFA</sub> , V <sub>REFB</sub> Resistance<br>Matching |                  |                                                        |                              |             |     | ±0.5 | ±3   | %     |

| DIGITAL INPUTS                                               | •                |                                                        |                              |             |     |      |      |       |

| Input High Voltage                                           | V <sub>INH</sub> |                                                        |                              |             | 2.4 |      |      | V     |

| Input Low Voltage                                            | V <sub>INL</sub> |                                                        |                              |             |     |      | 0.8  | \ \ \ |

| Input Current                                                |                  | Digital inputs at 0'                                   | V and V <sub>DD</sub>        |             |     |      | ±1   | μΑ    |

| Input Capacitance (Note 4)                                   |                  |                                                        |                              |             |     |      | 8    | pF    |

| ANALOG OUTPUTS                                               |                  | -                                                      |                              |             |     |      |      |       |

| DC Output Impedance                                          |                  |                                                        |                              |             |     | 0.2  |      | Ω     |

| Short-Circuit Current                                        |                  | Vour connected t                                       | o AGND                       |             |     | 15   |      | mA    |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = 11.4V \ to \ 16.5V, \ V_{SS} = -11.4V \ to \ -16.5V, \ AGNDA = AGNDB = DGND = 0V, \ V_{REFA} = V_{REFB} = +10V, \ R_L = 2k\Omega, \ C_L = 100pF, \ V_{OUT} \ connected \ to \ R_{FB} \ (MX7837), \ T_A = T_{MIN} \ to \ T_{MAX}, \ unless \ otherwise \ noted.) \ (Note 1)$

| PARAMETER                                                           | SYMBOL                 | CONDITIONS                                                                                                    | MIN   | TYP | MAX   | UNITS             |  |  |

|---------------------------------------------------------------------|------------------------|---------------------------------------------------------------------------------------------------------------|-------|-----|-------|-------------------|--|--|

| POWER REQUIREMENTS                                                  |                        |                                                                                                               |       |     |       |                   |  |  |

| V <sub>DD</sub> Range                                               | $V_{DD}$               |                                                                                                               | 11.4  |     | 16.5  | V                 |  |  |

| V <sub>SS</sub> Range                                               | V <sub>SS</sub>        |                                                                                                               | -11.4 |     | -16.5 | V                 |  |  |

| Positive Supply Current                                             | I <sub>DD</sub>        | Output unloaded                                                                                               |       | 5   | 10    | mA                |  |  |

| Negative Supply Current                                             | I <sub>SS</sub>        | Output unloaded                                                                                               |       | 4   | 6     | mA                |  |  |

|                                                                     | ΔGain/ΔV <sub>DD</sub> | $V_{DD} = 15V \pm 5\%, V_{REF} = -10V$                                                                        |       |     | ±0.01 |                   |  |  |

| Power-Supply Rejection                                              | ΔGain/ΔV <sub>SS</sub> | V <sub>SS</sub> = -15V ±5%, V <sub>REF</sub> = 10V                                                            |       |     | ±0.01 | % per %           |  |  |

| Power-Supply Rejection                                              | ΔGain/ΔV <sub>DD</sub> | V <sub>DD</sub> = 12V ±5%, V <sub>REF</sub> = -8.9V                                                           |       |     | ±0.01 | % per %           |  |  |

|                                                                     | ΔGain/ΔV <sub>SS</sub> | V <sub>SS</sub> = -12V ±5%, V <sub>REF</sub> = 8.9V                                                           |       |     | ±0.01 | ]                 |  |  |

| AC CHARACTERISTICS                                                  |                        |                                                                                                               |       |     |       |                   |  |  |

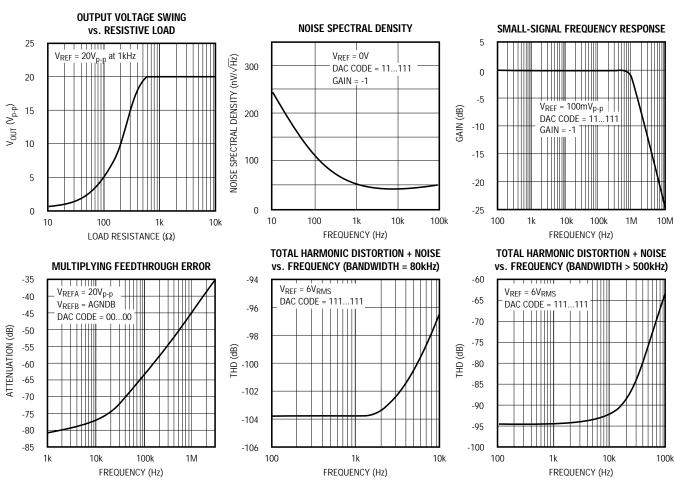

| Voltage-Output Settling<br>Time                                     | t <sub>S</sub>         | Settling time to within $\pm 1/2$ LSB of final DAC value; DAC latch alternately loaded will all 0s and all 1s |       | 4   |       | μs                |  |  |

| Slew Rate                                                           |                        |                                                                                                               |       | 7   |       | V/µs              |  |  |

| Digital-to Analog Glitch<br>Impulse                                 | Q                      | DAC latch alternately loaded with 0111 and 1000                                                               |       | 60  |       | nV-s              |  |  |

| Channel-to-Channel Isolation<br>(VREFA to VOUTB,<br>VREFB to VOUTA) |                        | V <sub>REF</sub> = 20p-p, 10kHz sine wave, Alternate DAC<br>Latch Loaded with all 0s                          |       | -95 |       | dB                |  |  |

| Multiplying Feedthrough<br>Error                                    |                        | V <sub>REF</sub> _ = 20V <sub>p-p</sub> , 10kHz sine wave, latches loaded with all 0s                         |       | -90 |       | dB                |  |  |

| Unity-Gain Small-Signal<br>Bandwidth                                |                        | V <sub>REF</sub> = 100mV <sub>p-p</sub> sine wave, DAC latch loaded with all 1s                               |       | 1   |       | MHz               |  |  |

| Full-Power Bandwidth                                                |                        | $V_{REF} = 20V_{p-p}$ sine wave, DAC latch loaded with all 1s                                                 |       | 125 |       | kHz               |  |  |

| Total Harmonic Distortion                                           | THD                    | V <sub>REF</sub> = 6V <sub>RMS</sub> , 1kHz, DAC latch loaded with all 1s                                     |       | -88 |       | dB                |  |  |

| Digital Crosstalk                                                   |                        | Code transition from all 0s to all 1s; see <i>Typical Operating Characteristics</i> graphs                    |       | 10  |       | nV-s              |  |  |

| Output Noise Voltage at +25°C (0.1Hz to 10Hz)                       |                        | Amplifier noise and Johnson noise of R <sub>FB</sub>                                                          |       | 2   |       | μV <sub>RMS</sub> |  |  |

Note 2: The analog outputs can swing to within 2.5V of the supply rails. Hence, for good linearity towards full-scale,  $|V_{REFA}|$  and  $|V_{REFB}|$  must be at least 2.5V lower than  $V_{DD}$  and  $|V_{SS}|$ . Tests done with supply voltages below  $\pm 12.5$ V are done with  $V_{REFA} = V_{REFB} = \pm 8.9$ V.

Note 3: Static performance tested at V<sub>DD</sub> = +15V, V<sub>SS</sub> = -15V. Performance over supplies guaranteed by PSRR test.

Note 4: Guaranteed by design.

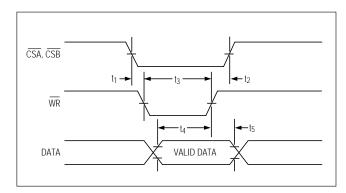

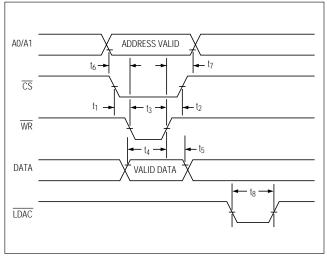

#### **TIMING CHARACTERISTICS**

$(V_{DD} = 11.4V \text{ to } 16.5V, V_{SS} = -11.4V \text{ to } -16.5V, \text{ AGNDA} = \text{AGNDB} = \text{DGND} = 0V, T_{A} = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted.})$  (Note 5)

| PARAMETER               | SYMBOL         | CONDITIONS  | MX78_7J/K/A/B<br>MIN MAX | MX78_7S/T<br>MIN MAX | UNITS |

|-------------------------|----------------|-------------|--------------------------|----------------------|-------|

| CS to WR Setup Time     | t <sub>1</sub> |             | 0                        | 0                    | ns    |

| CS to WR Hold Time      | t <sub>2</sub> |             | 0                        | 0                    | ns    |

| WR Pulse Width          | t <sub>3</sub> |             | 80                       | 80                   | ns    |

| Data to WR Setup Time   | t <sub>4</sub> |             | 80                       | 80                   | ns    |

| Data to WR Hold Time    | t <sub>5</sub> |             | 10                       | 10                   | ns    |

| Address to WR SetupTime | t <sub>6</sub> | MX7837 only | 15                       | 15                   | ns    |

| Address to WR Hold Time | t <sub>7</sub> | MX7837 only | 15                       | 15                   | ns    |

| LDAC Pulse Width        | t <sub>8</sub> | MX7837 only | 80                       | 80                   | ns    |

**Note 5:** All input signals are specified with  $t_R = t_F \le 5$ ns. Logic swing is 0V to 5V.

## Typical Operating Characteristics

(TA = +25°C,  $V_{DD}$  = 15V,  $V_{SS}$  = -15V,  $R_L$  = 2k $\Omega$ ,  $C_L$  = 100pF, unless otherwise noted)

Typical Operating Characteristics (continued)

$(T_A = +25$ °C,  $V_{DD} = 15$ V,  $V_{SS} = -15$ V,  $R_L = 2$ k $\Omega$ ,  $C_L = 100$ pF, unless otherwise noted.)

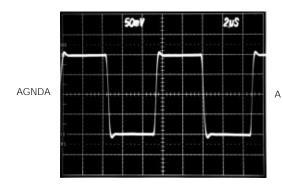

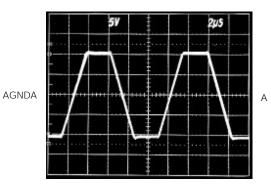

#### **SMALL-SIGNAL PULSE RESPONSE**

$A = V_{OUTA}, 50mV/div \\ TIMEBASE = 2\mu s/div \\ V_{REFA} = \pm 100mV \ SQUARE \ WAVE \\$

#### LARGE-SIGNAL PULSE RESPONSE

$A = V_{OUTA}, \, 5V/div$   $TIMEBASE = 2\mu s/div$   $V_{REFA} = \pm 10V \, SQUARE \, WAVE$

Pin Description

| PIN    |        | NAME                 | FUNCTION                                                                                                    |

|--------|--------|----------------------|-------------------------------------------------------------------------------------------------------------|

| MX7837 | MX7847 | NAIVIE               | FUNCTION                                                                                                    |

| 1      | -      | CS                   | Chip Select – active-low logic input                                                                        |

| -      | 1      | CSA                  | Chip-Select Input for DAC A – active-low logic input                                                        |

| 2      | -      | R <sub>FBA</sub>     | Amplifier Feedback Resistor for DAC A                                                                       |

| -      | 2      | CSB                  | Chip-Select Input for DAC B – active-low logic input                                                        |

| 3      | 3      | V <sub>REFA</sub>    | Reference Input Voltage for DAC A                                                                           |

| 4      | 4      | Vouta                | Analog Output Voltage from DAC A                                                                            |

| 5      | 5      | AGNDA                | Analog Ground for DAC A                                                                                     |

| 6      | 6      | $V_{\mathrm{DD}}$    | Positive Power Supply                                                                                       |

| 7      | 7      | V <sub>SS</sub>      | Negative Power Supply                                                                                       |

| 8      | 8      | AGNDB                | Analog Ground for DAC B                                                                                     |

| 9      | 9      | Voutb                | Analog Output Voltage from DAC B                                                                            |

| 10     | 10     | V <sub>REFB</sub>    | Reference Input Voltage for DAC B                                                                           |

| 11     | 11     | DGND                 | Digital Ground                                                                                              |

| 12     | -      | R <sub>FBB</sub>     | Amplifier Feedback Resistor for DAC B                                                                       |

| -      | 12     | DB11                 | Data Bit 11 (MSB)                                                                                           |

| 13     | 13     | WR                   | Write Input – active-low logic input (MX7837); positive-edge-triggered input used with CSA and CSB (MX7847) |

| 14     | -      | LDAC                 | Asynchronous Load – DAC input, active-low                                                                   |

| -      | 14-24  | DB10-DB0             | Data Bit 10 to Data Bit 0 (LSB)                                                                             |

| 15     | -      | A1                   | Address Input – most significant address input for input latches                                            |

| 16     | -      | A0                   | Address Input – least significant address input for input latches                                           |

| 17-20  | -      | DB7-DB4              | Data Bit 7 to Data Bit 4                                                                                    |

| 21-24  | -      | DB3/DB11-<br>DB0/DB8 | Data Bit 3 to Data Bit 0 (LSB), or Data Bit 11 (MSB) to Data Bit 8                                          |

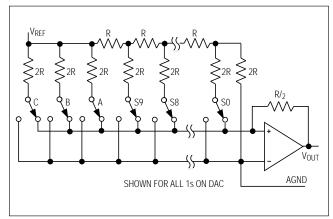

Figure 1. D/A Simplified Circuit Diagram

### \_Detailed Description

#### D/A Section

Figure 1 shows a simplified circuit diagram for one of the DACs and the output amplifier. Using a segmented scheme, the two MSBs of the 12-bit data word are decoded to drive the three switches (A to C). The remaining 10 bits drive the switches (S0 to S9) in a standard R-2R ladder.

Each switch (A to C) directs 1/4 of the total reference current, and the remaining current passes through the R-2R section.

The output amplifier and feedback resistor convert current to voltage as follows:  $V_{OUT\_} = (-D)(V_{REF\_})$ , where D is the fractional representation of the digital word. (D can be set from 0 to 4095/4096.)

The output amplifier is capable of developing  $\pm 10 V$  across a  $2 k \Omega$  load. It is internally compensated and settles to 0.01% FSR (1/2LSB) in less than 4µs.  $V_{OUT}$  on the MX7837 is not internally connected to  $R_{FB}$ .

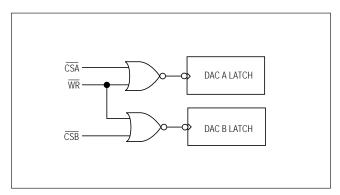

Figure 2. MX7847 Input Control Logic

# Interface Logic Information (MX7847)

Figure 2 shows the MX7847 input control logic. The device contains two independent DACs, each with its own  $\overline{\text{CS}}$  input and a common  $\overline{\text{WR}}$  input.  $\overline{\text{CSA}}$  and  $\overline{\text{WR}}$  control data loading to the DAC A latch, and  $\overline{\text{CSB}}$  and  $\overline{\text{WR}}$  control data loading to the DAC B latch. The latches are edge triggered so that input data is latched to the respective latch on  $\overline{\text{WR}}$ 's rising edge. The same data will be latched to both DACs if  $\overline{\text{CSA}}$  and  $\overline{\text{CSB}}$  are low and  $\overline{\text{WR}}$  is taken high. Table 1 shows the device control-logic truth table, and Figure 3 shows the write-cycle timing diagram.

Table 1. MX7847 Truth Table

| CSA      | CSB      | WR       | Function                  |

|----------|----------|----------|---------------------------|

| Х        | Х        | 1        | No Data Transfer          |

| 1        | 1        | Х        | No Data Transfer          |

| 0        | 1        | <u>.</u> | Data Latched to DAC A     |

| 1        | 0        | <u>.</u> | Data Latched to DAC B     |

| 0        | 0        | Ī        | Data Latched to Both DACs |

| <u>.</u> | 1        | 0        | Data Latched to DAC A     |

| 1        |          | 0        | Data Latched to DAC B     |

| <u>.</u> | <u>.</u> | 0        | Data Latched to Both DACs |

X = Don't Care I = Rising Edge Triggered

# Interface Logic Information (MX7837)

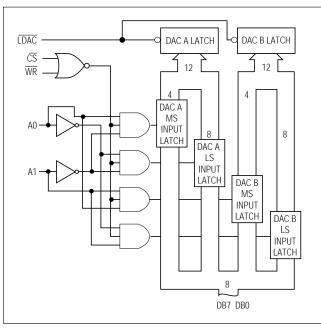

The MX7837 input loading structure is configured for interfacing with 8-bit-wide data-bus microprocessors. Each DAC has two 12-bit latches: an input latch, and a DAC latch. Each input latch is subdivided into a least-significant 8-bit latch and a most-significant 4-bit latch. The data held in the DAC latches determines the outputs. Figure 4 shows the MX7837 input control logic, and Figure 5 shows the write-cycle timing diagram.

Figure 3. MX7847 Write-Cycle Timing Diagram

Figure 4. MX7837 Input Control Logic

$\overline{\text{CS}}$ ,  $\overline{\text{WR}}$ , A0, and A1 control data loading to the input latches. The eight data inputs accept right-justified data, which can be loaded to the input latches in any sequence. If  $\overline{\text{LDAC}}$  is held high, loading data to the input latches will not change the analog output. A0 and A1 determine which input latch will receive the data when  $\overline{\text{CS}}$  and  $\overline{\text{WR}}$  are low. Table 2 shows the control logic truth table.

Table 2. MX7837 Truth Table

| CS | WR | <b>A</b> 1 | A0 | LDAC | Function                                                 |

|----|----|------------|----|------|----------------------------------------------------------|

| 1  | Х  | Χ          | Х  | 1    | No Data Transfer                                         |

| Х  | 1  | Χ          | Х  | 1    | No Data Transfer                                         |

| 0  | 0  | 0          | 0  | 1    | DAC A LS Input Latch Transparent                         |

| 0  | 0  | 0          | 1  | 1    | DAC A MS Input Latch Transparent                         |

| 0  | 0  | 1          | 0  | 1    | DAC B LS Input Latch Transparent                         |

| 0  | 0  | 1          | 1  | 1    | DAC B MS Input Latch Transparent                         |

| 1  | 1  | Х          | Х  | 0    | Updated Simultaneously from the Respective Input Latches |

X = Don't Care

The  $\overline{\text{LDAC}}$  input controls 12-bit data transfer from the input latches to the DAC latches. When  $\overline{\text{LDAC}}$  is taken low, both DAC latches (thus, both analog outputs) are updated simultaneously. When  $\overline{\text{LDAC}}$  is low, the DAC latches are transparent; DAC data is latched on the rising edge of  $\overline{\text{LDAC}}$ . The  $\overline{\text{LDAC}}$  input is asynchronous

Figure 5. MX7837 Write-Cycle Timing Diagram

and independent of  $\overline{\textbf{WR}}$ . This is useful in many applications, especially in updating multiple MX7837s simultaneously. However, be careful when exercising  $\overline{\textbf{LDAC}}$  during a write cycle; if an  $\overline{\textbf{LDAC}}$  operation overlaps a  $\overline{\textbf{CS}}$  and  $\overline{\textbf{WR}}$  operation, invalid data may be latched to the output. To avoid this,  $\overline{\textbf{LDAC}}$  must remain low after  $\overline{\textbf{CS}}$  or  $\overline{\textbf{WR}}$  have returned high for a period equal to or greater than  $t_8$ , the minimum  $\overline{\textbf{LDAC}}$  pulse width.

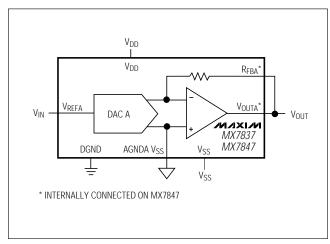

Unipolar Binary Operation

Figure 6 shows DAC A (MX7837/MX7847) connected for unipolar binary operation. Similar connections apply for DAC B. When  $V_{\text{IN}}$  is an AC signal, the circuit performs 2-quadrant multiplication. Table 3 shows the code table for this circuit. On the MX7847, the  $R_{\text{FB}}$  feedback resistor is internally connected to  $V_{\text{OUT}}$ .

**Table 3. Unipolar Code Table**

| DAC Latch Contents<br>MSB LSB | Analog Output, V <sub>OUT</sub>                                      |

|-------------------------------|----------------------------------------------------------------------|

| 1111 1111 1111                | $-V_{\text{IN}} \times \left(\frac{4095}{4096}\right)$               |

| 1000 0000 0000                | $-V_{IN} \times \left(\frac{2048}{4096}\right) = -\frac{1}{2}V_{IN}$ |

| 0000 0000 0001                | $-V_{IN} \times \left(\frac{1}{4096}\right)$                         |

| 0000 0000 0000                | OV                                                                   |

Note: 1LSB =

$$\left(\frac{V_{IN}}{4096}\right)$$

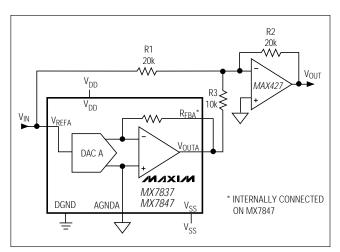

# Bipolar Operation (4-Quadrant Multiplication)

Figure 7 shows the MX7837/MX7847 connected for binary operation. The offset-binary coding is shown in Table 4. When  $V_{\rm IN}$  is an AC signal, the circuit performs 4-quadrant multiplication. R1, R2, and R3 resistors should be 0.01% ratio matched to maintain gain-error specifications. On the MX7847, the R<sub>FB</sub> feedback resistor is internally connected to  $V_{\rm OUT}$ .

Table 4. Bipolar Code Table

| DAC Latch Contents<br>MSB LSB | Analog Output, Vout                                       |

|-------------------------------|-----------------------------------------------------------|

| 1111 1111 1111                | $+V_{IN} \times \left(\frac{2047}{2048}\right)$           |

| 1000 0000 0001                | $+V_{IN} \times \left(\frac{1}{2048}\right)$              |

| 1000 0000 0000                | OV                                                        |

| 0111 1111 1111                | $-V_{IN} \times \left(\frac{1}{2048}\right)$              |

| 0000 0000 0000                | $-V_{IN} \times \left(\frac{2048}{2048}\right) = -V_{IN}$ |

Note: 1LSB =  $\left(\frac{V_{IN}}{2048}\right)$

## Applications Information

#### Ground Management

The use of an uninterrupted ground plane is strongly recommended. AC or transient voltages between analog and digital grounds (between AGNDA/AGNDB and DGND) can inject noise into the analog circuitry. Connect the MX7837/MX7847 AGNDs and DGND directly to the ground plane or to a star ground to ensure that they are at the same potential. In complex systems with separate analog and digital ground planes, connect two diodes (1N914 or equivalent) in inverse parallel between the AGND and DGND pins.

#### Power-Supply Decoupling

To minimize noise, decouple the  $V_{DD}$  and  $V_{SS}$  lines to DGND using a 10 $\mu$ F capacitor in parallel with a 0.1 $\mu$ F ceramic capacitor. Minimize capacitor lead lengths for best noise rejection.

## Operation with Reduced

#### Power-Supply Voltages

The MX7837/MX7847 are specified for operation with  $V_{DD}/V_{SS} = \pm 11.4 \text{V}$  to  $\pm 16.5 \text{V}$ . However, the output amplifier requires 2.5V of headroom, so the reference input should not come within 2.5V of  $V_{DD}/V_{SS}$  in order to maintain accuracy at full scale.

Figure 6. Unipolar Binary Operation

Figure 7. Bipolar Offset Binary Operation

## Pin Configurations (continued)

## Typical Operating Circuits (continued)

## \_Ordering Information (continued)

| PART             | TEMP. RANGE     | PIN-PACKAGE           | ERROR<br>(LSB) |

|------------------|-----------------|-----------------------|----------------|

| MX7837AN         | -40°C to +85°C  | 24 Narrow Plastic DIP | ±1             |

| MX7837BN         | -40°C to +85°C  | 24 Narrow Plastic DIP | ±1/2           |

| MX7837AR         | -40°C to +85°C  | 24 Wide SO            | ±1             |

| MX7837BR         | -40°C to +85°C  | 24 Wide SO            | ±1/2           |

| MX7837AQ         | -40°C to +85°C  | 24 Narrow CERDIP      | ±1             |

| MX7837BQ         | -40°C to +85°C  | 24 Narrow CERDIP      | ±1/2           |

| MX7837SQ         | -55°C to +125°C | 24 Narrow CERDIP      | ±1             |

| MX7837TQ         | -55°C to +125°C | 24 Narrow CERDIP      | ±1/2           |

| <b>MX7847</b> JN | 0°C to +70°C    | 24 Narrow Plastic DIP | ±1             |

| MX7847KN         | 0°C to +70°C    | 24 Narrow Plastic DIP | ±1/2           |

| MX7847JR         | 0°C to +70°C    | 24 Wide SO            | ±1             |

| MX7847KR         | 0°C to +70°C    | 24 Wide SO            | ±1/2           |

| MX7847C/D        | 0°C to +70°C    | Dice*                 | ±1             |

| MX7847AN         | -40°C to +85°C  | 24 Narrow Plastic DIP | ±1             |

| MX7847BN         | -40°C to +85°C  | 24 Narrow Plastic DIP | ±1/2           |

| MX7847AR         | -40°C to +85°C  | 24 Wide SO            | ±1             |

| MX7847BR         | -40°C to +85°C  | 24 Wide SO            | ±1/2           |

| MX7847AQ         | -40°C to +85°C  | 24 Narrow CERDIP      | ±1             |

| MX7847BQ         | -40°C to +85°C  | 24 Narrow CERDIP      | ±1/2           |

| MX7847SQ         | -55°C to +125°C | 24 Narrow CERDIP      | ±1             |

| MX7847TQ         | -55°C to +125°C | 24 Narrow CERDIP      | ±1/2           |

|                  |                 |                       |                |

Chip Topographies MX7837 MX7847 CS DB0/DB8 DB1/DB9 DB2/DB10 V<sub>REFA</sub> R<sub>FBA</sub>  $V_{REFA}$ CSB CSA DB0 DB1 DB2 DB3/ DB3  $V_{\text{OUTA}}$ Vouta DB11 DB4 DB4 AGNDA DB5 DB5 AGNDA · 0.250" 0.250" (6.35mm) (6.35mm)  $V_{DD}$  $V_{DD}$ Vss-Vss. DB6 DB6 AGNDB AGNDB -DB7 DB7  $V_{OUTB}$  $\nu_{\text{OUTB}}$ Α0 DB8 A1 DB9 LDAC V<sub>REFB</sub> DGND R<sub>FBB</sub>  $\overline{\mathsf{WR}}$ V<sub>REFB</sub> DGND DB11 WR DB10 0.140" 0.140" (3.56mm)(3.56mm)

TRANSISTOR COUNT: 1240; SUBSTRATE CONNECTED TO V<sub>DD</sub>.

TRANSISTOR COUNT: 1240; SUBSTRATE CONNECTED TO V<sub>DD</sub>.

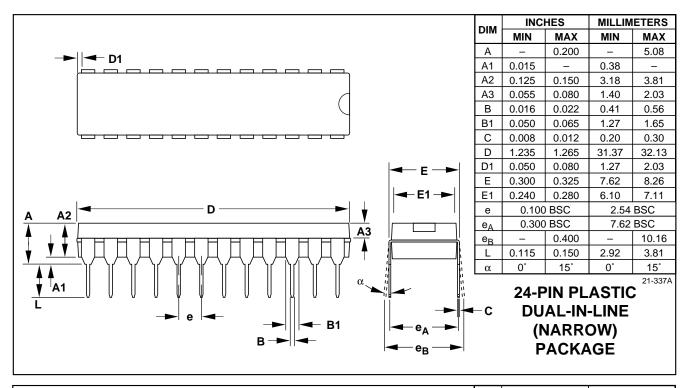

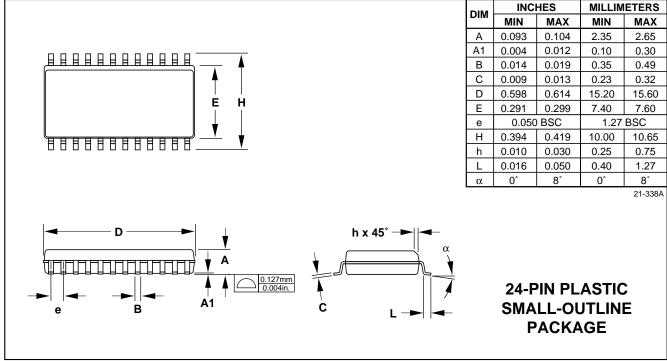

Package Information

Package Information (continued)

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.