# **MX619**

# Delta Modulation Codec meets EUROCOM D1-IA8

**Features**

DATA BULLETIN

- Meets EUROCOM D1-IA8

- Single Chip Full Duplex CVSD CODEC

- On-chip Input and Output Filters

- Programmable Sampling Clocks

- 3- or 4-bit Companding Algorithm

- Powersave Capabilities

- Low Power, 5.0V Operation

# **Applications**

- Military Communications

- Multiplexers, Switches, & Phones

The MX619 is a Continuously Variable Slope Delta Modulation (CVSD) Codec designed for use in military communications systems. This device is suitable for applications in military delta multiplexers, switches, and phones. The MX619 is designed to meet EUROCOM D1-IA8 specifications.

Encoder input and decoder output filters are incorporated on-chip. Sampling clock rates can be programmed to 16, 32, or 64kbps from an internal clock generator or externally injected in the 8 to 64kbps range. The sampling clock frequency is output for the synchronization of external circuits.

The encoder has an enable function for use in multiplexer applications. Encoder and Decoder forced idle capabilities are provided forcing 10101010...pattern in encode and a  $V_{DD}/2$  bias in decode. The companding circuit may be operated with an externally selectable 3- or 4-bit algorithm. The device may be placed in standby mode by selecting Powersave. A reference 1.024MHz oscillator uses an external clock or crystal.

The MX619 operates with a supply voltage of 5.0V and is available in the following packages: 24-pin PLCC (MX619LH), 22-pin CERDIP (MX619J), and 22-pin PDIP (MX619P).

# **CONTENTS**

| <b>3</b> 6 | Ctioi | 1       |                          | Page |

|------------|-------|---------|--------------------------|------|

|            |       |         |                          |      |

| 1          | Blo   | ck Dia  | ngram                    | 3    |

| 2          | Sigi  | nal Lis | st                       | 4    |

| 3          | Exte  | ernal ( | Components               | 6    |

| 4          | Ger   | neral E | Description              | 6    |

| 5          |       |         | on                       |      |

|            | 5.1   | CODI    | EC Integration           | 7    |

|            | 5.2   | Digita  | al to Analog Performance | 7    |

| 6          | Per   | forma   | nce Specification        | 11   |

|            | 6.1   | Electi  | rical Performance        | 11   |

|            |       | 6.1.1   | Absolute Maximum Ratings | 11   |

|            |       | 6.1.2   | Operating Limits         | 11   |

|            |       | 6.1.3   | 1 5                      |      |

|            |       | 6.1.4   | TIMING                   | 13   |

|            | 6.2   | Packa   | aging                    | 14   |

MX-COM, Inc. reserves the right to change specifications at any time and without notice.

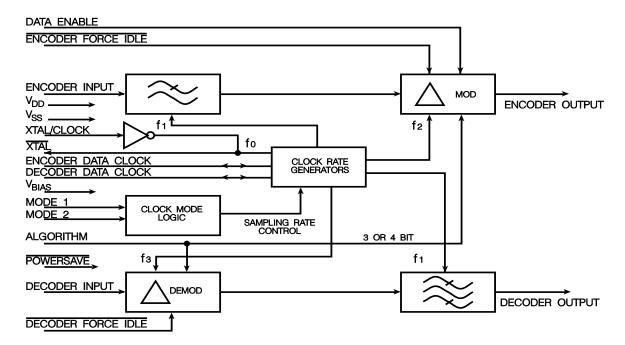

# 1 Block Diagram

Figure 1: Block Diagram

# **Signal List**

| J/P | LH | Name                  | Signal           | Description                                                                                                                                                                                                                                                       |

|-----|----|-----------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | 1  | Xtal/Clock            | input            | Input to the clock oscillator inverter. A 1.024MHz Xtal input or externally derived clock is injected here. See Clock Mode pins and Figure 2.                                                                                                                     |

|     | 2  | N/C                   |                  | No Connection                                                                                                                                                                                                                                                     |

| 2   | 3  | Xtal                  | output           | The 1.024 MHz output of the clock oscillator inverter.                                                                                                                                                                                                            |

| 3   | 4  | N/C                   |                  | No Connection                                                                                                                                                                                                                                                     |

| 4   | 5  | Encoder Data<br>Clock | input/<br>output | A logic I/O port. External encode clock input or internal data clock output. Clock frequency is dependent upon Clock Mode 1, 2 inputs and Xtal frequency (see Clock Mode pins).                                                                                   |

| 5   | 6  | Encoder Output        | output           | The encoder digital output. This is a three-state output whose condition is set by the Data Enable and Powersave inputs. See Table 2.                                                                                                                             |

| 6   | 7  | Encoder Force Idle    |                  | When this pin is at a logical "0" the encoder is forced to an idle state and the encoder digital output is 0101, a perfect idle pattern. When this pin is a logical "1" the encoder encodes as normal. Internal $1M\Omega$ pullup.                                |

| 7   | 8  | Data Enable           | input            | Data is made available at the encoder output pin by control of this input. See Encoder Output pin. Internal 1 M $\Omega$ pullup.                                                                                                                                  |

| 8   | 9  | N/C                   |                  | No Connection                                                                                                                                                                                                                                                     |

| 9   | 10 | V <sub>BIAS</sub>     |                  | Normally at $V_{DD}/2$ bias, this pin should be externally decoupled by capacitor C4. Internally pulled to $V_{SS}$ when "Powersave" is a logical "0".                                                                                                            |

| 10  | 11 | Encoder Input         | input            | The analog signal input. Internally biased at $V_{DD}/2$ , this input requires an external coupling capacitor. The source impedance should be less than $100\Omega$ . Output channel noise levels will improve with an even lower source impedance. See Figure 2. |

| 11  | 12 | V <sub>SS</sub>       | power            | Negative Supply                                                                                                                                                                                                                                                   |

| 12  | 13 | N/C                   |                  | No Connection                                                                                                                                                                                                                                                     |

| 13  | 14 | Decoder Output        | output           | The recovered analog signal is output at this pin. It is the buffered output of a lowpass filter and requires external components. During "Powersave" this output is open circuit.                                                                                |

| 14  | 15 | N/C                   |                  | No Connection                                                                                                                                                                                                                                                     |

| 15  | 16 | Powersave             |                  | A logic "0" at this pin puts most parts of the codec into a quiescent non-operational state. When at a logical "1", the codec operates normally. Internal 1 $M\Omega$ pullup.                                                                                     |

|     | 17 | N/C                   |                  | No Connection                                                                                                                                                                                                                                                     |

| 16  | 18 | Decoder Force Idle    |                  | A logic "0" at this pin gates a 0101 pattern internally to the decoder so that the Decoder Output goes to $V_{DD}/2$ . When this pin is a logical "1" the decoder operates as normal. Internal $1M\Omega$ pullup.                                                 |

| 17  | 19 | Decoder Input         |                  | The received digital signal input. Internal 1 $M\Omega$ pullup.                                                                                                                                                                                                   |

| 18  | 20 | Decoder Data<br>Clock | input/<br>output | A logic I/O port. External decode clock input or internal data clock output, dependent upon clock mode 1,2 inputs. See Clock Mode pins.                                                                                                                           |

| 19  | 21 | Algorithm             |                  | A logic "1" at this pin sets this device for a 3-bit companding algorithm. A logical "0" sets a 4-bit companding algorithm. Internal 1 $M\Omega$ pullup.                                                                                                          |

| J/P | LH | Name            | Signal | Description                                                                                                                                                                             |

|-----|----|-----------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 20  | 22 | Clock Mode 2    |        | Clock rates refer to f = 1024MHz Xtal/Clock input. During internal operation the data clock frequencies are available at the ports for external circuit synchronization. Independent or |

| 21  | 23 | Clock Mode 1    |        | common data rate inputs to Encode and Decode data clock ports may be employed in the External Clocks mode. Internal $1M\Omega$ pullups. See Table 3.                                    |

| 22  | 24 | V <sub>DD</sub> | power  | Positive Supply. A single 5.0V supply is required.                                                                                                                                      |

Table 1: Signal List

| Data Enable | Powersave | Encoder Output        |

|-------------|-----------|-----------------------|

| 1           | 1         | Enable                |

| 0           | 1         | High Z (open circuit) |

| 1           | 0         | $V_{SS}$              |

**Table 2: Encoder Output**

| Clock Mode 1 | Clock Mode 2 | Facility                |

|--------------|--------------|-------------------------|

| 0            | 0            | External Clocks         |

| 0            | 1            | Internal, 64kbps = f/16 |

| 1            | 0            | Internal, 32kbps = f/32 |

| 1            | 1            | Internal, 16kbps = f/64 |

Table 3: Clock Mode

#### 3 **External Components**

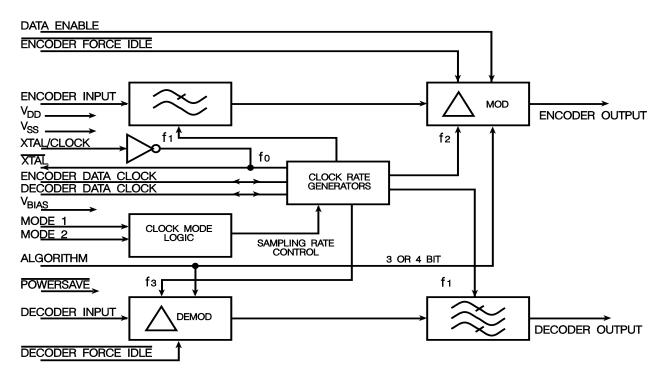

Figure 2: Recommended External Components for Typical Application

| R1 | Note 1 | 1M $\Omega$ | ±10% |

|----|--------|-------------|------|

| R2 | Note 2 | Selectable  |      |

| C1 | Note 3 | 33pF        | ±20% |

| C2 | Note 3 | 68pF        | ±20% |

| C3 | Note 4    | 1.0μF    | ±20% |

|----|-----------|----------|------|

| C4 | Note 5    | 1.0μF    | ±20% |

| C5 | Note 6    | 1.0μF    | ±20% |

| X1 | Note 7, 8 | 1.024MHz |      |

Table 4: Recommended External Components for Typical Application

#### Notes:

- 1. Oscillator inverter bias resister.

- Xtal Drive limiting resistor.

- Xtal circuit load capacitor.

- Encoder input coupling capacitor. The drive source impedance to this input should be less than  $100\Omega$ . Output idle channel noise levels will improve with even lower source impedance.

- Bias decoupling capacitor

- 6. V<sub>DD</sub> decoupling capacitor

- 7. A 1.024MHz Xtal/Clock input will yield exactly 16/32/64kbps data clock rates. Xtal circuitry shown is in accordance with MX-COM's Xtal Oscillator Application Note.

- 8. For best results, a crystal oscillator design should drive the clock inverter input with signal levels of at least 40% of V<sub>DD</sub>, peak to peak. Tuning fork crystals generally cannot meet this requirement. To obtain crystal oscillator design assistance, please consult you crystal manufacturer.

# **General Description**

The MX619 is a Continuously Variable Slope Delta Modulation (CVSD) Codec designed for use in military communications systems. This device is suitable for applications in military delta multiplexers, switches and phones. The MX619 is designed to meet EUROCOM D1-IA8 specifications.

Encoder input and decoder output filters are incorporated on-chip. Sampling clock rates can be programmed to 16, 32, or 64kbps from an internal clock generator or externally injected in the 8 to 64kbps range. The sampling clock frequency is output for the synchronization of external circuits.

The encoder has an enable function for use in multiplexer applications. Encoder and Decoder forced idle capabilities are provided forcing 10101010...pattern in encode and a V<sub>DD</sub>/2 bias in decode. The companding circuit may be operated with an externally selectable 3- or 4-bit algorithm. The device may be placed in standby mode by selecting Powersave. A reference 1.024MHz oscillator uses an external clock or crystal.

©2000 MX-COM. Inc. www.mxcom.com Tel: 800 638 5577 336 744 5050 Fax: 336 744 5054 Doc. # 20480189.002 4800 Bethania Station Road, Winston-Salem, NC 27105-1201 USA All Trademarks and service marks are held by their respective companies.

# 5 Application

Due to the very low levels of a signal idle channel noise specified for military applications, a noisy or badly regulated power supply could cause instability, putting the overall system performance out of specification. Adherence to the points listed below will assist in minimizing this problem.

- 1. Care should be taken in the design and layout of the printed circuit board.

- 2. All external components (as recommended in Figure 2) should be kept close to the package.

- 3. Tracks should be kept short, particularly the Encoder Input capacitor and the V<sub>BIAS</sub> capacitor.

- 4. Xtal/Clock tracks should be kept well away from analog inputs and outputs.

- 5. Inputs and outputs should be screened whenever possible.

- 6. A 'ground plane' connected to V<sub>SS</sub> will assist in eliminating external pick-up on the input and output pins.

- 7. It is recommended that the power supply rails have less that 1mV<sub>RMS</sub> of noise allowed.

- 8. The source impedance to the Encoder Input pin must be less that 100W; output idle channel, noise levels will improve with even power source impedances.

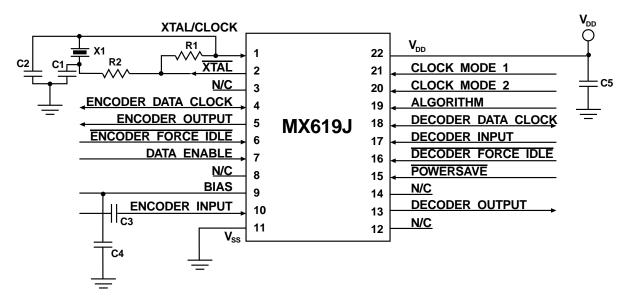

# 5.1 CODEC Integration

Figure 3: System Configuration using the MX619

## 5.2 Digital to Analog Performance

| Test | Sample<br>Rate | Bit Sequence at Decoder Input | MLA<br>Duty Cycle | Typical<br>Output<br>Level |

|------|----------------|-------------------------------|-------------------|----------------------------|

| а    | 16kbps         | 10110100100100101101          | 0                 | -41.5dBmO                  |

|      | 32kbps         | 1011011010101001001           | 0                 | -42.5dBmO                  |

| b    | 16kbps         | 11011001001001001101          | 0.05              | -25.0dBmO                  |

|      | 32kbps         | 1011011010101001001           | 0.05              | -25.0dBmO                  |

| С    | 16kbps         | 10110101000100101011          | 0.1               | -19.0dBmO                  |

|      | 32kbps         | 11011011010100100010001001    | 0.1               | -18.5dBmO                  |

| d    | 16kbps         | 11011001000010011011          | 0.2               | -11.0dBmO                  |

|      | 32kbps         | 11011101100101000100010001001 | 0.2               | -11.5dBmO                  |

| е    | 16kbps         | 11011010000010010111          | 0.3               | -6.5dBmO                   |

|      | 32kbps         | 111011101100100010            | 0.3               | -6.5dBmO                   |

| f    | 16kbps         | 11011010000001001111          | 0.4               | -3.0dBmO                   |

|      | 32kbps         | 111101110101000100            | 0.4               | -3.0dBmO                   |

| g    | 16kbps         | 111010100000001011            | 0.5               | 0dBmO                      |

|      | 32kbps         | 111110111010001000000         | 0.5               | 0dBmO                      |

Table 5: Bit Sequence Test

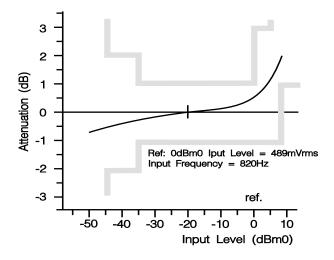

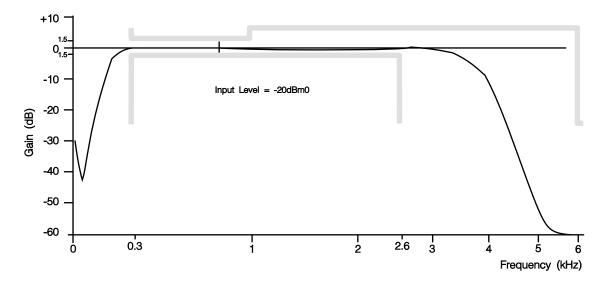

Figure 4: Gain vs. Input Level (16kbps)

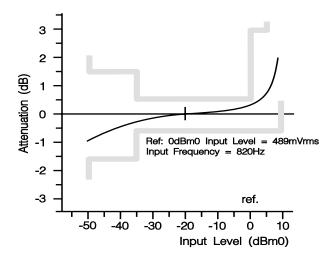

Figure 5: Gain vs. Input Level (32kbps)

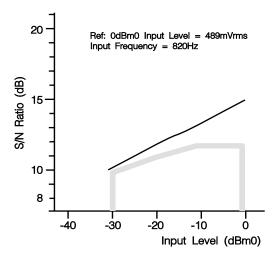

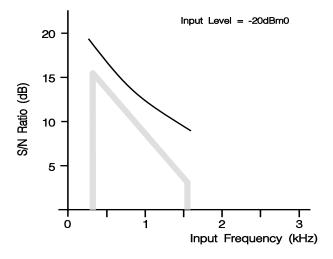

Figure 6: S/N vs. Input Level (16kbps)

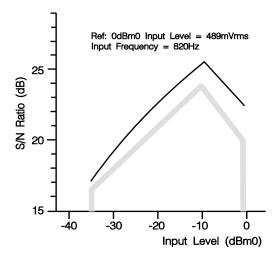

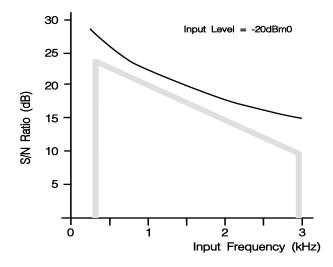

Figure 7: S/N vs. Input Level (32kbps)

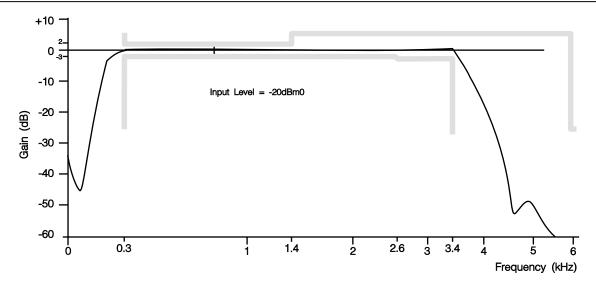

Figure 8: Attenuation distrotion vs. Frequency (16kbps)

Figure 9: S/N vs. Input Frequency (16kbps)

Figure 10: S/N vs. Input Frequency (32kbps)

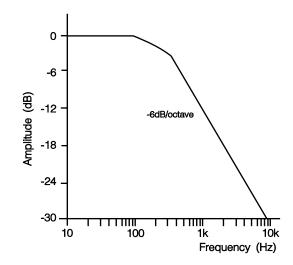

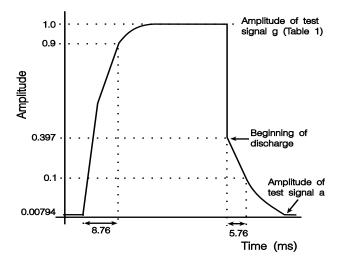

Figure 11: Principal Integrator Response

Figure 12: Compand Envelope

Figure 13: Attenuation Distortion vs. Frequency (32kbps)

# 6 Performance Specification

### 6.1 Electrical Performance

### 6.1.1 Absolute Maximum Ratings

Exceeding these maximum ratings can result in damage to the device.

|                                                              | Min. | Max.           | Units            |

|--------------------------------------------------------------|------|----------------|------------------|

| Supply (V <sub>DD</sub> - V <sub>SS</sub> )                  | -0.3 | 7.0            | V                |

| Voltage on any pin to V <sub>SS</sub>                        | -0.3 | $V_{DD} + 0.3$ | V                |

| Current                                                      |      |                |                  |

| $V_{DD}$                                                     | -30  | 30             | mA               |

| V <sub>SS</sub>                                              | -30  | 30             | mA               |

| any other pin                                                | -20  | 20             | mA               |

| J / P / LH Packages                                          |      |                |                  |

| Total Allowable Power Dissipation at T <sub>AMB</sub> = 25°C | -    | 800            | mW               |

| Derating above 25°C                                          | -    | 10             | mW/°C above 25°C |

| Storage Temperature                                          | -55  | 125            | °C               |

| Operating Temperature                                        | -40  | 85             | °C               |

### 6.1.2 Operating Limits

Correct operation of the device outside these limits is not implied.

|                                             | Min | Тур.  | Max. | Units |

|---------------------------------------------|-----|-------|------|-------|

| Supply (V <sub>DD</sub> - V <sub>SS</sub> ) | 4.5 | 5.0   | 5.5  | V     |

| Operating Temperature                       | -40 |       | 85   | °C    |

| Xtal Frequency                              | 500 | 1.024 | 1500 | MHz   |

### 6.1.3 Operating Characteristics

For the following conditions unless otherwise specified:  $V_{DD} = 5.0 \text{V}$  at  $T_{AMB} = 25 ^{\circ}\text{C}$ , Audio Test Frequency = 820Hz Xtal/Clock  $f_0 = 1.024 \text{MHz}$  3-bit Compand Algorithm, Sample Clock Rate = 32kbps, Audio level 0dB ref (0 dBm0) = 489mV<sub>RMS</sub>.

|                                              | Notes | Min. | Тур. | Max. | Units |

|----------------------------------------------|-------|------|------|------|-------|

| Static Values                                |       |      |      |      |       |

| Supply Voltage                               | 1     | 4.5  | 5.0  | 5.5  | V     |

| Supply Current (Enabled)                     |       |      | 5.5  |      | mA    |

| Supply Current (Powersave)                   |       |      | 400  |      | μΑ    |

| Input logic '1'                              | 8     | 3.5  |      |      | V     |

| Input Logic '0'                              | 8     |      |      | 1.5  | V     |

| Output Logic '1'                             |       | 4.0  |      |      | V     |

| Output Logic '0'                             |       |      |      | 1.0  | V     |

| Digital Input Impedance                      |       |      |      |      |       |

| Logic I/O pins                               |       | 1.0  | 10   |      | MΩ    |

| Logic Input pins, Pullup Resistor            | 2     | 300  |      |      | kΩ    |

| Digital output impedance                     |       |      | 4    |      | kΩ    |

| Analog Input Impedance                       | 4     |      | 1    |      | kΩ    |

| Analog Output Impedance                      | 7     |      |      | 800  | Ω     |

| Three State Output Leakage                   |       | -4   |      | 4    | μΑ    |

| Insertion Loss                               | 3     | -2   |      | 2    | dB    |

| Dynamic Values                               | 1,9   |      |      |      |       |

| Encoder                                      |       |      |      |      |       |

| Analog signal Input levels                   | 5, 9  | -35  |      | 6    | dBmO  |

| Principal Integrator Frequency               |       |      | 275  |      | Hz    |

| Encoder Passband                             |       |      | 3400 |      | Hz    |

| Compand Time Constant                        |       |      | 4.0  |      | ms    |

| Decoder                                      |       |      |      |      |       |

| Analog Signal Output Levels                  | 5, 9  | -35  | -10  | 6    | dBmO  |

| Decoder Passband                             |       | 300  |      | 3400 | Hz    |

| Encoder Decoder (Full Codec)                 |       |      |      |      |       |

| Compression Ration<br>(Cd = 0.5 to Cd = 0.0) |       | 50   |      |      |       |

| Passband                                     |       | 300  |      | 3400 | Hz    |

| Stopband                                     |       | 6    |      | 10   | KHz   |

| Stopband Attenuation                         |       |      | 60   |      | dB    |

| Passband Gain                                |       |      | 0    |      | dB    |

| Passband Ripple                              |       | -3   |      | 3    | dB    |

| 300Hz – 1400Hz                               |       | -1   |      | 1    | dB    |

| 1400Hz – 2600Hz                              |       | -1   |      | 1    | dB    |

| 2600Hz -3400Hz                               |       | -2   |      | 3    | dB    |

| Output Noise (Input Short Circuit)           | 9     |      |      | -60  | dBmOp |

| Perfect Idle Channel Noise                   |       |      |      |      |       |

| (Encode Forced)                              | 9     |      | -63  |      | dBmOp |

|                        | Notes | Min. | Тур. | Max. | Units |

|------------------------|-------|------|------|------|-------|

| Group Delay Distortion | 4     |      |      |      |       |

| (1000Hz-2600Hz)        | 6     |      |      | 450  | μs    |

| (600Hz-2800Hz)         | 6     |      |      | 750  | μs    |

| (500Hz-3000Hz)         | 6     |      |      | 1.5  | ms    |

| Xtal/clock Frequency   |       |      | 1024 |      | kHz   |

#### Notes:

- 1. Dynamic characteristics are specified at 5.0V unless otherwise specified.

- 2. All logic inputs except Encoder and Decoder Data clocks

- 3. For and encoder/Decoder combination, Insertion loss contributed by a single component is half this figure.

- 4. Driven with a source impedance of  $<100\Omega$ .

- 5. Recommended values See Figures 4, 5, 6, and 7.

- 6. Group Delay Distortion for the full codec is relative to the delay with and 820Hz, -20dB signal at the encoder input

- 7. An Emitter Follower output stage.

- 8.  $4V = 80\%V_{DD}$ ,  $3.5V = 70\%V_{DD}$ ,  $1.5V = 30\%V_{DD}$ ,  $1V = 20\%V_{DD}$

- 9. Analog Voltage Levels used:  $0dBmO = 489mV_{RMS} = -4dBm = 0dB$ .  $-15dBmO = 87mV_{RMS}$ .  $-20dBmO = 49mV_{RMS} = -24dBm$ .

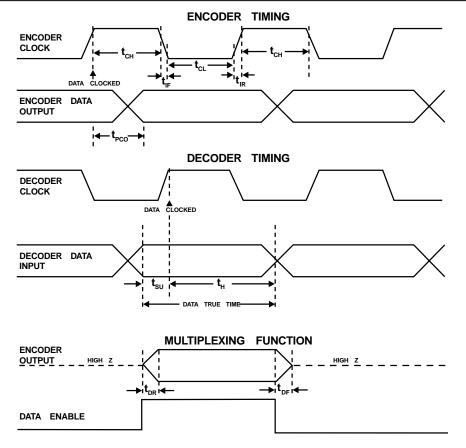

#### **6.1.4 TIMING**

| Serial Bus Timings (See Figure 14) |                            | Min. | Тур. | Max. | Units |

|------------------------------------|----------------------------|------|------|------|-------|

| t <sub>CH</sub>                    | Clock 1 pulse width        | 1.0  |      |      | μs    |

| t <sub>CL</sub>                    | Clock 0 pulse width        | 1.0  |      |      | μs    |

| t <sub>IR</sub>                    | Clock rise time            | 0    | 100  |      | ns    |

| t <sub>IF</sub>                    | Clock fall time            |      | 100  |      | ns    |

| t <sub>SU</sub>                    | Data set-up time           |      |      | 450  | ns    |

| t <sub>H</sub>                     | Data hold time             | 600  |      |      | ns    |

| t <sub>SU</sub> +t <sub>H</sub>    | Data true time             |      | 1.5  |      | μs    |

| t <sub>PCO</sub>                   | Clock to output delay time |      | 750  |      | ns    |

| t <sub>DR</sub>                    | Data rise time             |      | 100  |      | ns    |

| t <sub>DF</sub>                    | Data fall time             |      | 100  |      | ns    |

| Xtal input frequency = 1.024MHz    |                            |      |      |      |       |

Figure 14: CODEC Timing

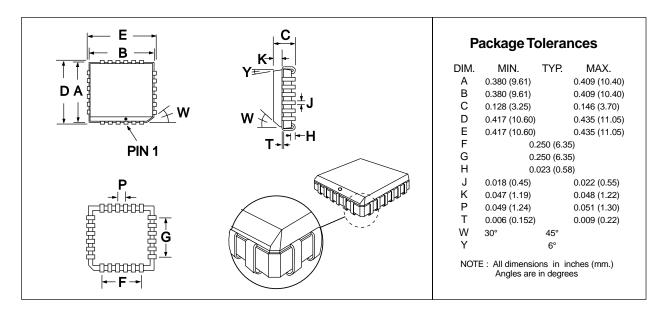

## 6.2 Packaging

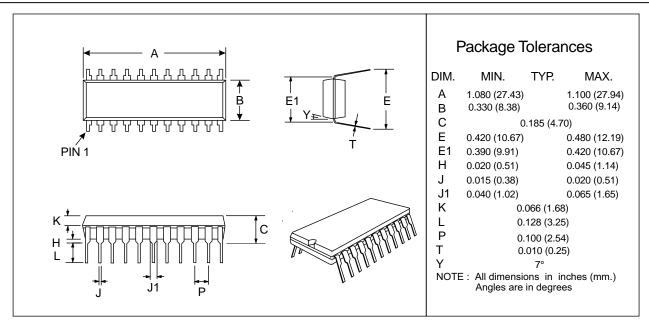

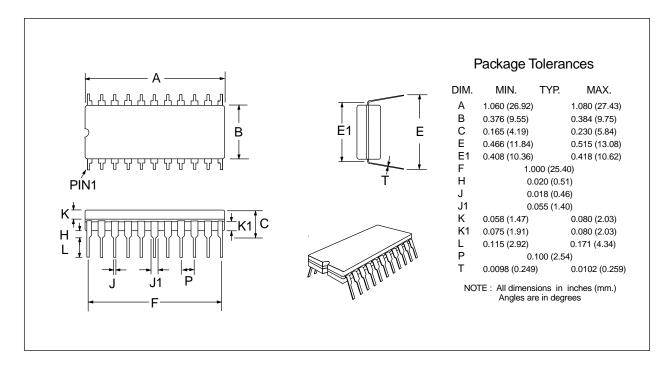

Figure 15: 24-pin PLCC (LH) Mechanical Outline: Order as part no. MX619LH

Figure 16: 22-pin PDIP (P) Mechanical Outline: Order as part no. MX619P

Figure 17: 22-pin CERDIP (J) Mechanical Outline: Order as part no. MX619J

#### **CML Product Data**

In the process of creating a more global image, the three standard product semiconductor companies of CML Microsystems Plc (Consumer Microcircuits Limited (UK), MX-COM, Inc (USA) and CML Microcircuits (Singapore) Pte Ltd) have undergone name changes and, whilst maintaining their separate new names (CML Microcircuits (UK) Ltd, CML Microcircuits (USA) Inc and CML Microcircuits (Singapore) Pte Ltd), now operate under the single title CML Microcircuits.

These companies are all 100% owned operating companies of the CML Microsystems Plc Group and these changes are purely changes of name and do not change any underlying legal entities and hence will have no effect on any agreements or contacts currently in force.

### **CML Microcircuits Product Prefix Codes**

Until the latter part of 1996, the differentiator between products manufactured and sold from MXCOM, Inc. and Consumer Microcircuits Limited were denoted by the prefixes MX and FX respectively. These products use the same silicon etc. and today still carry the same prefixes. In the latter part of 1996, both companies adopted the common prefix: CMX.

This notification is relevant product information to which it is attached.

## CML Microcircuits (USA) [formerly MX-COM, Inc.] Product Textual Marking

On CML Microcircuits (USA) products, the 'MX-COM' textual logo is being replaced by a 'CML' textual logo.

Company contact information is as below:

COMMUNICATION SEMICONDUCTORS

Oval Park, Langford, Maldon, Essex, CM9 6WG, England Tel: +44 (0)1621 875500 Fax: +44 (0)1621 875600 uk.sales@cmlmicro.com www.cmlmicro.com

COMMUNICATION SEMICONDUCTORS

4800 Bethania Station Road, Winston-Salem, NC 27105, USA Tel: +1 336 744 5050,

0800 638 5577

Fax: +1 336 744 5054

us.sales@cmlmicro.com

www.cmlmicro.com

No 2 Kallang Pudding Road, 09-05/ 06 Mactech Industrial Building, Singapore 349307

Tel: +65 7450426 Fax: +65 7452917 sg.sales@cmlmicro.com www.cmlmicro.com