# MV4325

## PROGRAMMABLE KEYPAD PULSE DIALLER

The MV4325 Keypad Pulse Dialler contains all the logic necessary to interface a 2 of 7 keypad and convert this key information to control and mute pulses simulating a telephone rotary dial. The MV4325 has programmable access pause capability to provide automatic interruption of dialing needed when accessing the toll network, WATS line or public network. The device is fabricated using Plessey Semiconductors' ISO-CMOS technology which enables the device to function down to 2.0V making it ideal for long loop operation.

The MV4325 will accept up to 20 digits and access pauses and will redial stored information at a later time by activation of # key. Device current in standby is less than 1 $\mu$ A at 1.0V.

The MV4325 is available in Ceramic DIL (DG, -40°C to  $+85^{\circ}\text{C}).$

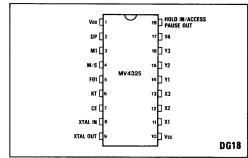

Fig.1 Pin connections (top view)

#### FEATURES

Last Number Redial

Multiple Access Pause Programming

Any Valid Keypad Input or HOLD IN Causes Exit from Access Pause

Oscillator Start Up Controlled from Keypad Input

Oscillator Power Down whilst not Dialling

300 Hz Key Tone indicates Valid Key

2.0V to 7.0V Supply Voltage Operating Range

Stores up to 20 Digits and Access Pauses

- Digit Memory Retained down to 1.0V at 1  $\mu$ A

- Selectable Mark/Space Ratio 663 : 333 or 60 : 40

- 10Hz Dialling Speed (932Hz Fast Test):)

#### APPLICATIONS

Pushbutton Telephones with Last Number Redial

Repertory Dialers

Tone to Pulse Converters

#### MV4325

#### **ABSOLUTE MAXIMUM RATINGS**

The absolute maximum ratings are limiting values above which operating life may be shortened or specified parameters may be degraded.

|                                  | MIN                   | MAX                    |                   | MIN | MAX    |

|----------------------------------|-----------------------|------------------------|-------------------|-----|--------|

| V <sub>DD</sub> -V <sub>SS</sub> | -0.3V                 | 10V                    |                   |     |        |

| Voltage on any pin               | V <sub>SS</sub> -0.3V | V <sub>DD</sub> + 0.3V |                   |     |        |

| Current at any pin               |                       | 10mA                   |                   |     |        |

| Operating Temperature            | -40 °C                | +85°C                  | Power Dissipation |     | 1000mW |

| Storage Temperature              | -65 °C                | + 150 °C               |                   |     |        |

#### **DC ELECTRICAL CHARACTERISTICS**

Test conditions (unless otherwise stated):  $T_{amb}$  = +25°C, f<sub>CLK</sub> = 3.579545 MHz; V<sub>DD</sub> = +3.0 V All voltages wrt V<sub>SS</sub>

|                 | CHARACTERISTIC |                          |                                                                                   | SYMBOL                 | MIN            | TYP*         | MAX  | UNITS    | TEST CONDITIONS                                    |                                                                |  |  |  |

|-----------------|----------------|--------------------------|-----------------------------------------------------------------------------------|------------------------|----------------|--------------|------|----------|----------------------------------------------------|----------------------------------------------------------------|--|--|--|

| 1               | S<br>U         | Supply Volta             | ge Operating Range                                                                | V <sub>DD</sub>        | 2.0            |              | 7.0  | v        |                                                    |                                                                |  |  |  |

| 2               | P              | Standby Sup              | ply Current                                                                       | IDDS                   |                |              | 1.0  | μA       | $CE = M/S = F01 = HOLD IN = V_{SS}, V_{DD} = 1$    |                                                                |  |  |  |

| 3               | ¥              | Operating Su             | upply Current                                                                     | IDD                    |                | 100          | 150  | μA       | 3.579545 MHz Crystal, CXTALOUT = 12pF              |                                                                |  |  |  |

| 4               |                | Pull-Up Tran             | sistor Source Current                                                             | ΙL                     | - 0.5          | - 3.0        | -12  | μA       | V <sub>IN</sub> = V <sub>SS</sub>                  | x <sub>1</sub> ,x <sub>2</sub> ,x <sub>3</sub>                 |  |  |  |

| 5               | ł              | Input Leakag             | nput Leakage Current<br>nput Leakage Current<br>Pull-Down Transistor Sink Current |                        |                | 0.1          |      | nA       | $v_{IN} = v_{DD}$                                  | Y <sub>1</sub> ,Y <sub>2</sub> ,Y <sub>3</sub> ,Y <sub>4</sub> |  |  |  |

| 6               | N<br>P         | Input Leakage Current    |                                                                                   | ΙIL                    |                | - 0.1        |      | nA       | V <sub>IN</sub> = V <sub>SS</sub>                  | M/S, F01                                                       |  |  |  |

| 7               | U              | Pull-Down Ti             | ransistor Sink Current                                                            | Чн                     | 0.5            | 3.0          | 8.0  | μA       | $V_{IN} = V_{DD}$                                  |                                                                |  |  |  |

| 8               |                | Input Low Level Voltage  |                                                                                   | VIL                    |                |              | 0.9  | v        | All inputs                                         |                                                                |  |  |  |

| 9               |                | Input High Level Voltage |                                                                                   | V <sub>IH</sub>        | 2.1            |              |      | V        |                                                    |                                                                |  |  |  |

| 10              |                | Voltage                  | Low-Level                                                                         | VOL                    |                | 0            | 0.01 | V        | No Load                                            |                                                                |  |  |  |

| 11              | 0              | Levels                   | High-level                                                                        | v <sub>он</sub>        | 2.99           | 3            |      | v        |                                                    |                                                                |  |  |  |

| <u>12</u><br>13 | T<br>P<br>U    | Drive<br>Current         | N-Channel                                                                         | 10L<br>10L             | 0.8<br>0.2     | 2.0<br>0.5   |      | mA<br>mA | V <sub>OUT</sub> = 2.3V<br>V <sub>OUT</sub> = 0.5V | DP, M <sub>1</sub> , M <sub>2</sub> , KT                       |  |  |  |

| 14<br>15        | т              | Current                  | P-Channel Source                                                                  | <sup>I</sup> ОН<br>IОН | - 0.8<br>- 0.2 | - 2.0<br>0.5 |      | mA<br>mA | V <sub>OUT</sub> = 0.7V<br>V <sub>OUT</sub> = 2.5V |                                                                |  |  |  |

| 16              | -              | Input Low Le             | evel Voltage                                                                      | VIL                    |                |              | 0.9  | v        |                                                    |                                                                |  |  |  |

| 17              | N<br>/         | Input High Level Voltage |                                                                                   | V <sub>IH</sub>        | 2.1            |              |      | V        |                                                    |                                                                |  |  |  |

| 18              | 0              | Output Low Level Current |                                                                                   | ΙΟL                    |                | 15           |      | ۸نر      | V <sub>OUT</sub> = 0.5V                            | CE,                                                            |  |  |  |

| 19              | T              | Output High              | Level Current                                                                     | юн                     |                | - 12         |      | μA       | V <sub>OUT</sub> = 2.5V                            | HOLD IN/ACCESS                                                 |  |  |  |

| 20              | U              | Input Force              | High Current (from V <sub>OL</sub> )                                              | IFH                    |                | 55           |      | Αυ       | $V_{IN} = 2.5V$                                    | PAUSE OUT                                                      |  |  |  |

| 21              | <u>'</u>       | Input Force              | Low Current (from VOH)                                                            | ۱ <sub>FL</sub>        |                | - 70         |      | Αų       | V <sub>IN</sub> = 0.5V                             |                                                                |  |  |  |

\* Typical parametric values are for Design Aid Only, not guaranteed and not subject to production testing. Timing waveforms are subject to production functional test.

#### AC ELECTRICAL CHARACTERISTICS

Test conditions (unless otherwise stated):  $T_{amb}$  = +25°C; f<sub>CLK</sub> = 3.579545 MHz; V<sub>DD</sub> = +3.0 V

|    |        | CHARACTERISTIC                    | SYMBOL          | MIN  | түр• | мах | UNITS | TEST CONDITIONS       |

|----|--------|-----------------------------------|-----------------|------|------|-----|-------|-----------------------|

| 1  |        | Output Rise Time                  | t <sub>R</sub>  |      | 1.0  |     | μs    | DP, M <sub>1</sub>    |

| 2  |        | Output Fall Time                  | tF              |      | 1.0  |     | μs    | C <sub>L</sub> = 50pF |

| 3  | D      | Maximum Clock Frequency           | fclk            | 3.58 |      |     | MHz   | 3.579545 MHz Crystal  |

| 4  | Y      | Mark to Crosse Patia              | M/S             |      | 2:1  |     |       | $M/S = O/C (V_{SS})$  |

| 5  | N<br>A | Mark to Space Ratio               | 11/5            |      | 3:2  |     |       | $M/S = V_{DD}$        |

| 6  | M      | System Clock Frequency (Internal) |                 |      | 300  |     | Hz    | F01 = V <sub>SS</sub> |

| 7  | С      | Impulsing Rate = I/T              |                 |      | 10   |     | Hz    | $F01 = V_{SS}$        |

| 8  |        | Fast Test Impulsing Rate          |                 |      | 14.9 |     | Hz    | $F01 = V_{DD}$        |

| 9  |        | Clock Start Up Time               | ton             |      | 1.5  | 4   | ms    | Timed from CE 1'1'    |

| 10 |        | Input Capacitance                 | C <sub>in</sub> |      | 5.0  |     | pF    | Any Input             |

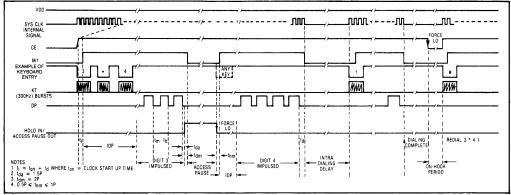

Fig.4 MV4325 timing diagram, CE Internal control

### MV4325

#### **PIN FUNCTIONS**

| V <sub>DD</sub>                                                | Positive voltag                                                                                 | e sup           | ply                |                                              |                               |                     |                           |                        |  |  |  |

|----------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-----------------|--------------------|----------------------------------------------|-------------------------------|---------------------|---------------------------|------------------------|--|--|--|

| DP                                                             | Dial Pulsing O                                                                                  | utput           | Buffer             |                                              |                               |                     |                           |                        |  |  |  |

| M1                                                             | Mute Output E                                                                                   | Suffer          |                    |                                              |                               |                     |                           |                        |  |  |  |

| M/S                                                            | Mark/Space (Break/Make) Ratio select. On-chip pull-down transistor to V <sub>SS</sub> . O/C 2:1 |                 |                    |                                              |                               |                     |                           |                        |  |  |  |

|                                                                | Note: O/C = Open Circuit V <sub>DD</sub> 3:2                                                    |                 |                    |                                              |                               |                     |                           |                        |  |  |  |

| F01                                                            | Impulsing Rate Selection.<br>On-chip pull-down transistor to V <sub>SS</sub> .                  |                 | F01                |                                              |                               | ctual*<br>sing Rate | System<br>Clock frequency |                        |  |  |  |

|                                                                |                                                                                                 |                 |                    | 0/C                                          | 10Hz                          | 10                  | ).13Hz                    | 303.9Hz                |  |  |  |

|                                                                | * Assumes f <sub>CLK</sub> = 3.579545MHz.                                                       |                 |                    | v <sub>DD</sub>                              | 932Hz                         | 932.17Hz            |                           | 27,965.1Hz             |  |  |  |

| CE                                                             | Chip Enable. A                                                                                  | n acti          | ve input. Control  | is internal via stat                         | ic keyboard decode            | e, or by            | external fo               | orcing.                |  |  |  |

| XTAL IN                                                        | Crystal Input.                                                                                  | Active          | , clamped low if C | CE = '0', high impe                          | dance if CE = '1'.            |                     |                           |                        |  |  |  |

| XTAL OUT                                                       | Crystal Output. Buffer to drive crystal. Capacitive load on-chip.                               |                 |                    |                                              |                               |                     |                           |                        |  |  |  |

| v <sub>ss</sub>                                                | System ground                                                                                   | ł               |                    |                                              |                               |                     |                           |                        |  |  |  |

| x <sub>1</sub> ,x <sub>2</sub> ,x <sub>3</sub>                 | Column keybo                                                                                    | ard In          | puts. On-chip pull | -up transistors to                           | V <sub>DD</sub> . Active LOW. |                     |                           |                        |  |  |  |

| Y <sub>1</sub> ,Y <sub>2</sub> ,Y <sub>3</sub> ,Y <sub>4</sub> | Row keyboard                                                                                    | Inpute          | s. On-chip pull-up | transistors to V <sub>DI</sub>               | D. Active LOW.                |                     |                           |                        |  |  |  |

| HOLD IN/                                                       | INPUT/OUTPUT                                                                                    | 0/C             | Normal Operation   | n                                            |                               |                     |                           |                        |  |  |  |

| ACCESS                                                         | INPUT                                                                                           | V <sub>DD</sub> | No impulsing. If   | activated during in                          | mpulsing, hold occu           | irs whe             | n the curre               | ent digit is complete. |  |  |  |

| PAUSE OUT                                                      | OUTPUT                                                                                          | V <sub>DD</sub> | Logic "1" level c  | vel output indicates access pause condition. |                               |                     |                           |                        |  |  |  |

| кт                                                             | 300Hz                                                                                           | Squ             | are wave bursts i  | ndicate valid keyp                           | ad input.                     |                     |                           |                        |  |  |  |

|                      | ]     | KEYPAD INPUT CODE |    |                |    |    |                |    |  |  |

|----------------------|-------|-------------------|----|----------------|----|----|----------------|----|--|--|

| No. of O/P<br>Pulses | Digit | Υ,                | Y₂ | Y <sub>3</sub> | Y₄ | Χ, | X <sub>2</sub> | X3 |  |  |

| 1                    | 1     | 0                 | 1  | 1              | 1  | 0  | 1              | 1  |  |  |

| 2                    | 2     | 0                 | 1  | 1              | 1  | 1  | 0              | 1  |  |  |

| 3                    | 3     | 0                 | 1  | 1              | 1  | 1  | 1              | 0  |  |  |

| 4                    | 4     | 1                 | 0  | 1              | 1  | 0  | 1              | 1  |  |  |

| 5                    | 5     | 1                 | 0  | 1              | 1  | 1  | 0              | 1  |  |  |

| 6                    | 6     | 1                 | 0  | 1              | 1  | 1  | 1              | 0  |  |  |

| 7                    | 7     | 1                 | 1  | 0              | 1  | 0  | 1              | 1  |  |  |

| 8                    | 8     | 1                 | 1  | 0              | 1  | 1  | 0              | 1  |  |  |

| 9                    | 9     | 1                 | 1  | 0              | 1  | 1  | 1              | 0  |  |  |

| 10                   | 0     | 1                 | 1  | 1              | 0  | 1  | 0              | 1  |  |  |

| RE-DIAL              |       | 1                 | 1  | 1              | 0  | 1  | 1              | 0  |  |  |

| ACCESS PAUSE         |       | 1                 | 1  | 1              | 0  | 0  | 1              | 1  |  |  |

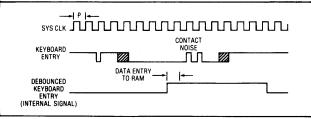

Fig.5 Keypad input debounce timing diagram

#### **OPERATING NOTES**

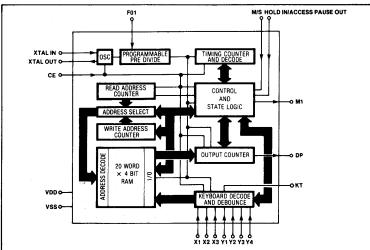

The MV4325 programmable keypad pulse dialer is optimized for use in key operated pulse dialling telephone sets and contains features which make it particularly suitable for applications where redial of last number dialled and repertory dial facilities are required.

Keypad information is accepted directly from a dual contact keypad having two single pole switches per key: one switch common to the column and one switch common to the row. The common row contacts are connected Y1 to Y4 and the common column contacts connected X1 to X3. The other side of each switch is connected to a common VSS line. The keypad code is shown in Table 1.

The MV4325 will accept up to 20 digits and access pauses, e.g. 18 digits plus 2 access pauses or alternately 19 digits plus 1 access pause. Prior to a keypad input being accepted contact bounce is eliminated by a circuit which ensures that any input which is valid for less than 10ms is rejected and any input valid for greater than 17ms is accepted as a valid key input. This circuit operates similarly on the trailing edge of a valid key input preventing multiple digit recognition in the presence of noise. Debounce operation is shown in Fig.5.

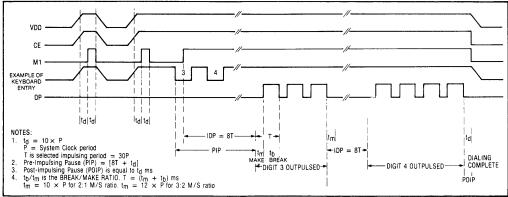

The first key entered in any dialling sequence initiates the oscillator on the MV4325 by internally taking CE high. Digits may be entered asynchronously from the keypad. Dialling and mute functions are output as shown in Fig.3 and Fig.4. Fig.3 shows use of the MV4325 with external control of CE. This mode is useful if a bistable latching relay is used to mute and switch the complete pulse dialer circuit. In this mode the pulse occurring on M1 when CE is taken high with no keypad input can be used to initiate the bistable latching relay.

Fig.4 shows the timing diagram of the MV4325 including access pause and redial mode. Initially CE is low and goes high on recognition of the first valid key input. Keypad data is entered asynchronously and dialling commences after recognition of the leading edge of the first valid key input. When an access pause is reached M1 goes low and Hold In/Access Pause Out goes high indicating the device is in an access pause. This output signal can be used to enable an external dial tone recognition circuit. Exit from the access pause is achieved by one of two methods. One method is by the next valid key operation. If a valid digit is entered, the digit will be entered in the next consecutive storage location in the digit memory. If the key # is activated, redialling of the number in memory will occur only if the device is in the redial mode. The alternative method to exit from an access pause is to pulse Hold In/Access Pause Out low, resetting the output latch associated with this input/output pin.

Fig.4 shows a pause in dialling between the completion of dialling digit 4 and keying digit 1. In this condition, the oscillator powers down to minimize power consumption and interfering signals, whilst CE remains high. On recognition of the next digit, the digit is entered in the next consecutive memory location and dialling resumes.

The end of a key entry sequence is indicated to the MV4325 by externally pulsing or clamping CE low. This causes the on-chip latch holding CE high to reset.

If the first key entered after a CE low period is #, redial of the last number dialled will occur. Access pause operation is as previously described. In the standby condition the MV4325 dissipates less than 1.0µW.

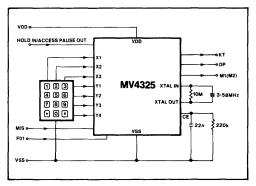

Fig.6 Application diagram