22 Din TOOD

## **SRAM**

## 1 MEG x 4 SRAM

WITH OUTPUT ENABLE

22 Din CO I

#### **FEATURES**

- High speed: 12, 15, 20, 25 and 35ns

- High-performance, low-power, CMOS double-metal process

- Multiple center power and ground pins for improved noise immunity

- Single +5V ±10% power supply

- Easy memory expansion with  $\overline{CE}$  and  $\overline{OE}$  options

- All inputs and outputs are TTL-compatible

- Fast OE access time: 6, 8, 10, 12 and 15ns

#### OPTIONS MARKING Timing 12ns access -12 15ns access -15 -20 20ns access 25ns access -25 -35 35ns access Packages Plastic SOJ (400 mil) DJ Plastic TSOP (400 mil) TG 2V data retention · Low power P Temperature Commercial (0°C to +70°C) None (-40°C to +85°C) Industrial IT Automotive (-40°C to +125°C) AT Extended $(-55^{\circ}\text{C to } + 125^{\circ}\text{C})$ Part Number Example: MT5C1M4B2DJ-35 L

NOTE: Not all combinations of operating temperature, speed, data retention

and low power are necessarily available. Please contact the factory for availabil-

#### **GENERAL DESCRIPTION**

ity of specific part number combinations.

The MT5C1M4B2 is organized as a 1,048,576 x 4 SRAM using a four-transistor memory cell with a high-speed, low-power CMOS process. Micron 4 Meg SRAMs are fabricated using double-layer metal, triple-layer polysilicon technology.

This device offers multiple center power and ground pins for improved performance. For flexibility in high-speed memory applications, Micron offers chip enable  $(\overline{CE})$  and output enable  $(\overline{OE})$  with this configuration. These enhancements can place the outputs in High-Z for additional flexibility in system design.

## PIN ASSIGNMENT (Top View)

| 32 | 2 <b>-Pin SO</b><br>(SD-5)                                                                                                                                                                                              | j   |                                                                                                                                            | n ISOP<br>SE-1) |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| A0 | 31<br>30<br>29<br>28<br>27<br>26<br>25<br>24<br>0<br>23<br>1<br>22<br>2<br>2<br>2<br>3<br>4<br>19<br>4<br>19<br>19<br>20<br>4<br>19<br>20<br>21<br>21<br>21<br>21<br>21<br>21<br>21<br>21<br>21<br>21<br>21<br>21<br>21 | A19 | A0 II 1 A1 II 2 A2 II 3 A3 II 4 A4 II 5 CE II 6 DO1 II 7 Vcc II 8 Vss II 9 DO2 II 10 WE II 11 A5 II 12 A6 II 13 A7 II 14 A8 II 15 A9 II 16 | 32              |

|    |                                                                                                                                                                                                                         |     |                                                                                                                                            |                 |

Writing to this device is accomplished when write enable  $(\overline{WE})$  and  $\overline{CE}$  inputs are both LOW. Reading is accomplished when  $\overline{WE}$  remains HIGH while output enable  $(\overline{OE})$  and  $\overline{CE}$  go LOW. The device offers a reduced power standby mode when disabled. This allows system designers to meet low standby power requirements.

The "P" version provides a 90 percent reduction in TTL standby current (ISB1) through the use of gated inputs on the  $\overline{\text{WE}}$ ,  $\overline{\text{OE}}$  and address lines, which also facilitates the design of battery backed systems. That is, the gated inputs simplify the design effort and circuitry required to protect against inadvertent battery current drain during power-down, when inputs may be at undefined levels.

All devices operate from a single +5V power supply and all inputs and outputs are fully TTL-compatible.

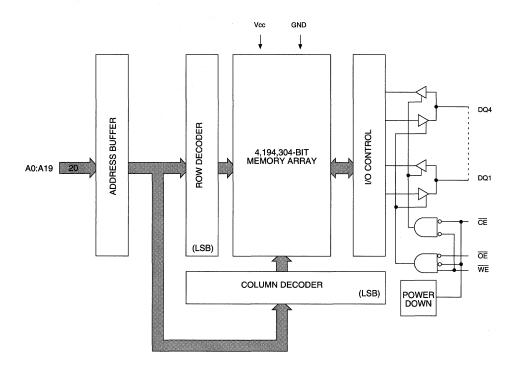

#### **FUNCTIONAL BLOCK DIAGRAM**

#### **TRUTH TABLE**

| MODE         | 0E | CE | WE | DQ     | POWER   |

|--------------|----|----|----|--------|---------|

| STANDBY      | Χ  | Н  | Х  | HIGH-Z | STANDBY |

| READ         | L  | L  | Н  | Q      | ACTIVE  |

| NOT SELECTED | Н  | L  | Н  | HIGH-Z | ACTIVE  |

| WRITE        | Х  | L  | L  | D      | ACTIVE  |

## THERMAL IMPEDENCE (EST)16

| PACKAGE | NUMBER<br>OF PINS | θ <sub>JC</sub> *<br>(°C/W) | θ <sub>JA</sub> *<br>(°C/W) |

|---------|-------------------|-----------------------------|-----------------------------|

| SOJ     | 32                | 15                          | 60                          |

| TSOP    | 32                | 5                           | 70                          |

<sup>\*</sup>The thermal impedence numbers assume the device is socketted on a PC board and air flow is zero.

#### **ABSOLUTE MAXIMUM RATINGS\***

Voltage on Vcc Supply Relative to Vss ......-1V to +7V Storage Temperature (plastic) .....-55°C to +150°C Short Circuit Output Current ......50mA Voltage on any pin relative to Vss .....-1V to Vcc+1 Junction Temperature\*\* .....+150°C

\*Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device.

This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

\*\*Maximum junction temperature depends upon package type, cycle time, loading, ambient temperature and airflow. See the Application Information section at the end of this data sheet for more information.

## ELECTRICAL CHARACTERISTICS AND RECOMMENDED DC OPERATING CONDITIONS

$(0^{\circ}C \le T_{\Delta} \le 70^{\circ}C; Vcc = 5V \pm 10\%)$

| DESCRIPTION                                               | CONDITIONS         | SYMBOL | MIN  | MAX   | UNITS | NOTES |  |

|-----------------------------------------------------------|--------------------|--------|------|-------|-------|-------|--|

| Input High (Logic 1) Voltage                              |                    | ViH    | 2.2  | Vcc+1 | V     | 1     |  |

| Input Low (Logic 0) Voltage                               |                    | VIL    | -0.5 | 0.8   | V     | 1, 2  |  |

| Input Leakage Current                                     | t 0V ≤ VIN ≤ VCC   |        | -2   | 2     | μΑ    |       |  |

| Output Leakage Current Output(s) disabled 0V ≤ Vouт ≤ Vcc |                    | ILo    | -2   | 2     | μА    |       |  |

| Output High Voltage                                       | Iон = -4.0mA       | Vон    | 2.4  |       | ٧     | 1     |  |

| Output Low Voltage                                        | oltage IoL = 8.0mA |        |      | 0.4   | ν     | 1     |  |

| Supply Voltage                                            | /oltage            |        | 4.5  | 5.5   | V     | 1     |  |

|                                    |                                                                                     |        |     |     |     |     |     | _     |       |

|------------------------------------|-------------------------------------------------------------------------------------|--------|-----|-----|-----|-----|-----|-------|-------|

|                                    |                                                                                     |        |     |     | MAX |     |     |       |       |

| DESCRIPTION                        | CONDITIONS                                                                          | SYMBOL | -12 | -15 | -20 | -25 | -35 | UNITS | NOTES |

| Power Supply<br>Current: Operating | TE ≤ VIL; Vcc = MAX f = MAX = 1/ tRC outputs open                                   | lcc    | 200 | 180 | 175 | 170 | 160 | mA    | 3     |

| Power Supply<br>Current: Standby   | CE ≥ ViH; Vcc = MAX<br>f = MAX = 1/ tRC<br>outputs open                             | ISB1   | 35  | 30  | 25  | 25  | 20  | mA    |       |

|                                    | P version only                                                                      | ISB1   | 2   | 2   | 2   | 2   | 2   | mA    |       |

|                                    | CE ≥ Vcc -0.2V; Vcc = MAX         VIN ≤ Vss +0.2V or         VIN ≥ Vcc -0.2V; f = 0 | ISB2   | 2   | 2   | 2   | 2   | 2   | mA    |       |

|                                    | P version only                                                                      | IsB2   | 2   | 2   | 2   | 2   | 2   | mA    |       |

#### **CAPACITANCE**

| DESCRIPTION        | CONDITIONS                       | SYMBOL | MAX | UNITS | NOTES |

|--------------------|----------------------------------|--------|-----|-------|-------|

| Input Capacitance  | T <sub>A</sub> = 25°C; f = 1 MHz | Cı     | 5   | pF    | 4     |

| Output Capacitance | Vcc = 5V                         | Co     | 7   | pF    | 4     |

MT5C1M4B2 1 MEG x 4 SRAM

#### **ELECTRICAL CHARACTERISTICS AND RECOMMENDED AC OPERATING CONDITIONS**

(Notes 5, 13) (0°C  $\leq T_A \leq 70$ °C; Vcc = 5V  $\pm 10$ %)

| DESCRIPTION                        |                   | -1  | -12 |     | -15 |     | -20 |     | -25                                     |     | -35 |       |       |

|------------------------------------|-------------------|-----|-----|-----|-----|-----|-----|-----|-----------------------------------------|-----|-----|-------|-------|

| DESCRIPTION                        | SYM               | MIN | MAX | MIN | MAX | MIN | MAX | MIN | MAX                                     | MIN | MAX | UNITS | NOTES |

| READ Cycle                         |                   |     |     |     |     |     |     |     |                                         |     |     |       |       |

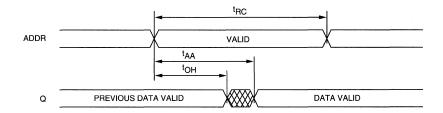

| READ cycle time                    | tRC               | 12  |     | 15  |     | 20  |     | 25  |                                         | 35  |     | ns    |       |

| Address access time                | <sup>t</sup> AA   |     | 12  |     | 15  |     | 20  |     | 25                                      |     | 35  | ns    |       |

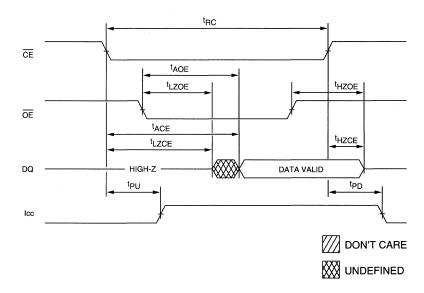

| Chip Enable access time            | tACE              |     | 12  |     | 15  |     | 20  |     | 25                                      |     | 35  | ns    |       |

| Output hold from address change    | tOH               | 3   |     | 3   |     | 3   |     | 3   |                                         | 3   |     | ns    |       |

| Chip Enable to output in Low-Z     | <sup>t</sup> LZCE | 3   |     | 3   |     | 5   |     | 5   |                                         | 5   |     | ns    | 7     |

| Chip disable to output in High-Z   | tHZCE             |     | 6   |     | 7   |     | 8   |     | 10                                      |     | 15  | ns    | 6, 7  |

| Chip Enable to power-up time       | <sup>t</sup> PU   | 0   |     | 0   |     | 0   |     | 0   |                                         | 0   |     | ns    |       |

| Chip disable to power-down time    | <sup>t</sup> PD   |     | 12  |     | 15  |     | 20  |     | 25                                      |     | 35  | ns    |       |

| Output Enable access time          | tAOE              |     | 6   |     | 8   |     | 10  |     | 12                                      |     | 15  | ns    |       |

| Output Enable to output in Low-Z   | tLZ0E             | 0   |     | 0   |     | 0   |     | 0   |                                         | 0   |     | ns    |       |

| Output disable to output in High-Z | tHZOE             |     | 5   |     | 6   |     | 7   |     | 10                                      |     | 12  | ns    | 6     |

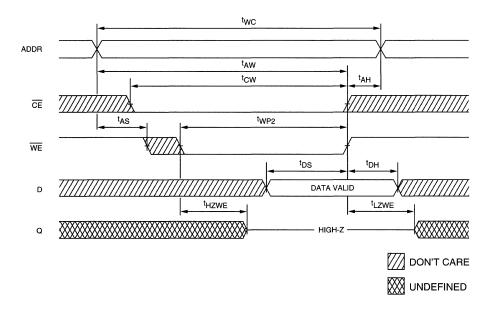

| WRITE Cycle                        |                   |     |     |     |     |     |     |     | *************************************** |     |     |       |       |

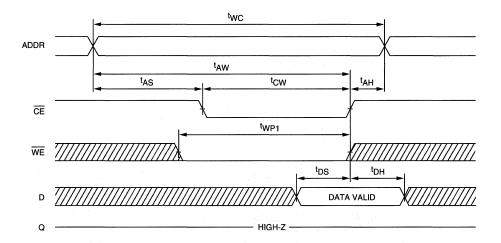

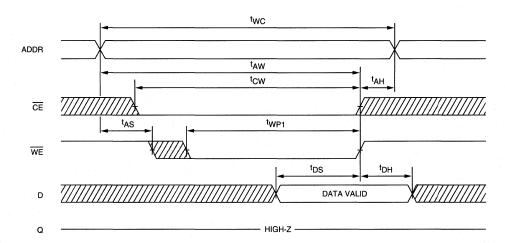

| WRITE cycle time                   | tWC               | 12  |     | 15  |     | 20  |     | 25  |                                         | 35  |     | ns    | -     |

| Chip Enable to end of write        | tCW               | 8   |     | 10  |     | 12  |     | 15  |                                         | 20  |     | ns    | -     |

| Address valid to end of write      | tAW               | 8   |     | 10  |     | 12  |     | 15  |                                         | 20  |     | ns    |       |

| Address setup time                 | t <sub>AS</sub>   | 0   |     | 0   |     | 0   |     | 0   |                                         | 0   |     | ns    |       |

| Address hold from end of write     | t <sub>AH</sub>   | 0   |     | 0   |     | 0   |     | 0   |                                         | 0   |     | ns    |       |

| WRITE pulse width                  | tWP1              | 8   |     | 9   |     | 10  |     | 15  |                                         | 20  |     | ns    |       |

| WRITE pulse width                  | tWP2              | 9   |     | 11  |     | 12  |     | 17  |                                         | 22  |     | ns    |       |

| Data setup time                    | tDS               | 6   |     | 7   |     | 8   |     | 10  |                                         | 15  |     | ns    |       |

| Data hold time                     | <sup>t</sup> DH   | 0   |     | 0   |     | 0   |     | 0   |                                         | 0   |     | ns    |       |

| Write disable to output in Low-Z   | tLZWE             | 3   |     | 3   |     | 4   |     | 5   |                                         | 5   |     | ns    | 7     |

| Write Enable to output in High-Z   | tHZWE             |     | 5   |     | 6   |     | 8   |     | 10                                      |     | 15  | ns    | 6, 7  |

#### **AC TEST CONDITIONS**

| Input pulse levels            | Vss to 3.0V    |

|-------------------------------|----------------|

| Input rise and fall times     | 3ns            |

| Input timing reference levels | 1.5V           |

| Output reference levels       | 1.5V           |

| Output loadSee F              | igures 1 and 2 |

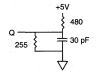

Fig. 1 OUTPUT LOAD EQUIVALENT

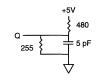

Fig. 2 OUTPUT LOAD EQUIVALENT

#### **NOTES**

- 1. All voltages referenced to Vss (GND).

- 2. -3V for pulse width < tRC/2.

- 3. Icc is dependent on output loading and cycle rates.

- 4. This parameter is sampled.

- 5. Test conditions as specified with the output loading as shown in Fig. 1 unless otherwise noted.

- tHZCE, tHZOE and tHZWE are specified with CL = 5pF as in Fig. 2. Transition is measured ±500mV from steady state voltage.

- At any given temperature and voltage condition, <sup>t</sup>HZCE is less than <sup>t</sup>LZCE, and <sup>t</sup>HZWE is less than <sup>t</sup>LZWE.

- 8.  $\overline{\text{WE}}$  is HIGH for READ cycle.

- 9. Device is continuously selected. Chip enable and output enables are held in their active state.

- 10. Address valid prior to, or coincident with, latest occurring chip enable.

- 11. tRC = Read Cycle Time.

- 12. Chip enable and write enable can initiate and terminate a WRITE cycle.

- 13. Contact Micron for IT/AT/XT timing and current specifications; they may differ from the commercial temperature range specifications shown in this data sheet.

- 14. Output enable  $(\overline{OE})$  is inactive (HIGH).

- 15. Output enable  $(\overline{OE})$  is active (LOW).

- 16. Micron does not warrant functionality nor reliability of any product in which the junction temperature exceeds 150°C. Care should be taken to limit power to acceptable levels.

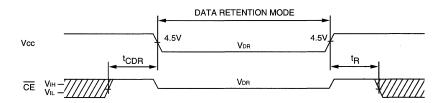

## DATA RETENTION ELECTRICAL CHARACTERISTICS (L and LP versions only)

| DESCRIPTION                             | CONDITIONS                                   |          | SYMBOL           | MIN             | MAX | UNITS | NOTES |

|-----------------------------------------|----------------------------------------------|----------|------------------|-----------------|-----|-------|-------|

| Vcc for Retention Data                  |                                              |          | VDR              | 2               |     | V     |       |

| Data Retention Current<br>L version     | <u>CE</u> ≥ (Vcc -0.2V)<br>Vin ≥ (Vcc -0.2V) | Vcc = 2V | ICCDR            |                 | 1   | mA    |       |

| L VOIGION                               | or ≤ 0.2V                                    | Vcc = 3V | ICCDR            |                 | 1.5 | mA    |       |

| Data Retention Current                  | <u>CE</u> ≥ (Vcc -0.2V)                      | Vcc = 2V | ICCDR            | . :             | 1   | mA    |       |

| LP version                              |                                              | Vcc = 3V | ICCDR            | -               | 1.5 | mA    |       |

| Chip Deselect to Data<br>Retention Time |                                              |          | <sup>t</sup> CDR | 0               |     | ns    | 4     |

| Operation Recovery Time                 |                                              |          | <sup>t</sup> R   | <sup>t</sup> RC |     | ns    | 4, 11 |

### **LOW Vcc DATA RETENTION WAVEFORM**

#### READ CYCLE NO. 18,9

#### READ CYCLE NO. 27,8,10

# **VOLT SRAN**

# WRITE CYCLE NO. 1 12 (Chip Enable Controlled)

# WRITE CYCLE NO. 2 12, 14 (Write Enable Controlled)

DON'T CARE

UNDEFINED

# WRITE CYCLE NO. 3<sup>7, 12, 15</sup> (Write Enable Controlled)

# **VOLT SRAM**

## APPLICATION INFORMATION THERMAL CONSIDERATIONS

This section describes how to determine the junction temperature during operating conditions. It is essential that the maximum junction temperature of the 4 Meg SRAM is not exceeded. If this temperature is exceeded it is necessary to add external cooling such as forced airflow or change the operating conditions. The maximum junction temperature for Micron SRAMs is 150°C. The limiting temperature factor is not the SRAM but the mold compound which prevents reliable operating temperatures significantly about 150°C. However, it is advisable to run the part as cool as possible since reliability (FIT rates) are exponentially dependent upon junction temperature.

The calculation of the actual junction temperature begins with the power calculation and then the junction temperation calculation. Equations 1 and 2 below show how  $T_j$  is determined using the ambient temperature, thermal resistance and operating power. If an airflow is introduced into a system then Equation 2 should be used with an airflow thermal multiplier. Specific thermal resistances are given in Micron technical note "SRAM Thermal Design Considerations" and in individual data sheets.

$$T_{j} = T_{A} + P * \theta_{JA}$$

(1)

$$T_i = T_A + P * \theta_{IA} * \theta_{M}$$

(2)

T<sub>j</sub> = Junction temperature of the active portion of the silicon die (°C)

T<sub>A</sub> = Ambient air temperature (°C) at which the device is operated

P = Average power dissipation of the device (W)

$\theta_{JA}$  = Junction to ambient thermal resistance (°C/W)  $\theta_{M}$  = Airflow multiplier. This value changes for different values of airflow over the part (fpm).

To solve the above equations the average operating power must be calculated. Total power has three separate components  $(P_1,\,P_2$  and  $P_3),\,P_1$  is the operating power dissipated by the chip,  $P_2$  is the AC output power due to the capacitive load and  $P_3$  is the DC output power due to TTL DC load current  $(P_3$  is usually negligible). For this example we have chosen  $P_2$  such that outputs are switching from a logic LOW

state to a logic HIGH state which gives the worst case output AC current. A complete description of these equations and their derivation is given in Micron technical note "Design Tips: 32K x 36 SRAM."

$$P_1 = Vcc Icc$$

$$P_2 = \frac{C_L}{T} (Vcc [V_{OH} - V_{OL}] - 0.5 [V_{OH}^2 - V_{OL}^2]) N_S$$

$$P_3 = (V_{CC} - V_{OH}) I_O N_H + V_{OL} I_I N_L$$

Vcc = Supply voltage Icc = Supply current

C<sub>1</sub> = Capacitive output loading

T = Clock period

V<sub>OH</sub> = Output high voltage

V<sub>OL</sub> = Output low voltage

$I_{O}$  = Output current on DQ lines which are high  $I_{I}$  = Input current on DQ lines which are low

$N_H$  = Number of DQ lines which are high  $N_I$  = Number of DQ lines which are low.

# Table 1 EFFECTS OF AIRFLOW ON 4 MEG SRAM SOJ PACKAGES

| Package | Air Flow | θ <sub>M</sub> Multiplier |

|---------|----------|---------------------------|

| PSOJ    | 200 fpm  | 0.7 - 0.75                |

| PSOJ    | 500 fpm  | 0.55 - 0.65               |

#### ADDITIONAL INFORMATION

For more information on thermal considerations see Micron's technical notes, "SRAM Thermal Design Considerations" and "Design Tips: 32K x 36 SRAM." These notes explain how to calculate thermal resistance and how to improve thermal performance in much greater detail. Also available is Micron's *Quality and Reliability Handbook*, which gives an explanation of how thermal impedances are calculated.