# 5 VOLT SYNCHRONOUS SRAW

# SYNCHRONOUS SRAM

## 128K x 9 SRAM

FULLY REGISTERED INPUTS AND OUTPUTS

### **FEATURES**

OPETONIC

- Timing specific to SPARC® microprocessor

- Fast cycle times: 12, 16.6 and 20ns

- Fast clock to data valid: 6, 8 and 10ns

- Single +5V ±10% power supply

- READ data and WRITE data registers

- · Common, TTL-compatible data inputs and outputs

- · All inputs and outputs registered with clock

- · Fully synchronous, pipelined architecture

| OPTIONS                 | MAKKING |

|-------------------------|---------|

| Timing                  |         |

| 6ns access/12ns cycle   | -12*    |

| 8ns access/16.6ns cycle | -16     |

| 10ns access/20ns cycle  | -20     |

|                         |         |

| Packages                |         |

| 32-pin SOI (400mil)     | DI      |

Part Number Example: MT58C1289DJ-16

NOTE: Not all combinations of operating temperature, speed, data retention and low power are necessarily available. Please contact the factory for availability of specific part number combinations.

### **PIN ASSIGNMENT (Top View)**

## **32-Pin SOJ** (SD-5)

| CLK  | þ | 1  | 32 | þ | Vcc  |

|------|---|----|----|---|------|

| SA15 | þ | 2  | 31 | þ | SA14 |

| SA8  | þ | 3  | 30 | þ | SA16 |

| SA7  | þ | 4  | 29 | þ | SWE  |

| SA6  | þ | 5  | 28 | þ | SA13 |

| SA5  | þ | 6  | 27 | þ | SA9  |

| SA4  | þ | 7  | 26 | þ | SA10 |

| SA3  | þ | 8  | 25 | þ | SA11 |

| SA2  | þ | 9  | 24 | þ | SOE  |

| SA1  | þ | 10 | 23 | þ | SA12 |

| SA0  | þ | 11 | 22 | þ | SCE  |

| SDQ1 | þ | 12 | 21 | þ | SDQ9 |

| SDQ2 | þ | 13 | 20 | þ | SDQ8 |

| SDQ3 | þ | 14 | 19 | þ | SDQ7 |

| SDQ4 | þ | 15 | 18 | þ | SDQ6 |

| Vss  | þ | 16 | 17 | þ | SDQ5 |

|      |   |    |    |   |      |

### **GENERAL DESCRIPTION**

The Micron SRAM family employs high-speed, low-power CMOS designs using a four-transistor memory cell. Micron SRAMs are fabricated using double-layer metal, double-layer polysilicon technology.

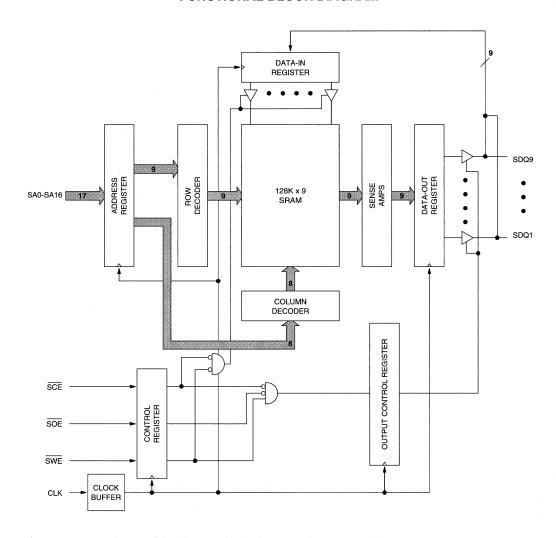

The MT58C1289 is a fully "pipelined" SRAM that integrates registers for address, data-in, data-out and synchronous chip enable (SCE), output enable (SOE) and write enable (SWE). All registers are triggered with the positive edge of the clock signal (CLK).

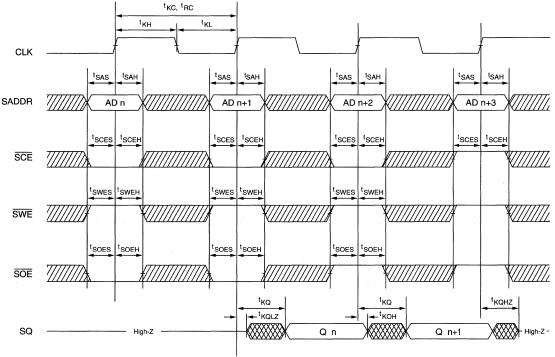

READ cycles are performed when SWE is HIGH and SOE and SCE are LOW at the positive edge of CLK. Read data is then presented at the next positive edge of CLK.

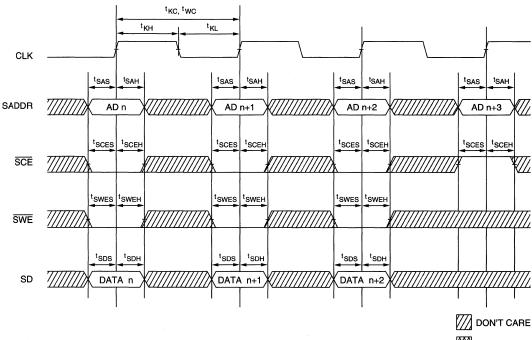

WRITE cycles occur when  $\overline{SWE}$  and  $\overline{SCE}$  are LOW at the rising edge CLK. Data present at the data input registers is written to the SRAM address present at the address input registers on that same rising edge of CLK. The WRITE cycle is internally self-timed, eliminating the need for complex write pulse generation external to the SRAM. The WRITE cycle requires three preceding deselect cycles when a WRITE cycle follows a READ cycle. This allows the D/Q lines to be in the High-Z state when write data is applied. The SRAM is deselected if  $\overline{SCE}$  is HIGH when a positive edge of CLK occurs.

The MT58C1289 operates from a +5V power supply.

<sup>\*</sup>Preliminary

### **FUNCTIONAL BLOCK DIAGRAM**

### **PIN DESCRIPTIONS**

| PLCC AND PQFP<br>PIN NUMBERS                               | SYMBOL    | TYPE             | DESCRIPTION                                                                                                                                                                                                                                                                                                        |

|------------------------------------------------------------|-----------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11, 10, 9, 8, 7, 6, 5, 4, 3, 27, 26, 25, 23, 28, 31, 2, 30 | SA0-SA16  | Input            | Address Inputs: These inputs are synchronous and must meet the setup and hold times around the positive edge of CLK. The address inputs are clocked into the address register on each positive edge of CLK.                                                                                                        |

| 29                                                         | SWE       | Input            | Synchronous Write Enable: This input determines if the cycle is a READ or WRITE cycle. SWE is LOW for a WRITE cycle and HIGH for a READ cycle. SWE is registered on every positive edge of CLK and must meet the setup and hold times referenced to that edge. WRITE cycles are self-timed internally by the SRAM. |

| 1                                                          | CLK       | Input            | Clock: All timing is controlled by the positive edge of CLK. All synchronous input and output signals are registered on the positive edge of CLK and must meet the setup and hold times referenced to that edge.                                                                                                   |

| 22                                                         | SCE       | Input            | Synchronous Chip Enable: This signal is used to enable the device. This is a synchronous input and must meet the setup and hold times around CLK. When SCE is HIGH, the SRAM automatically goes into the standby power mode.                                                                                       |

| 24                                                         | SOE       | Input            | Synchronous Output Enable: This active LOW input enables the output drivers. This is a synchronous input and must meet the setup and hold times around CLK.                                                                                                                                                        |

| 12, 13, 14, 15, 17,<br>18, 19, 20, 21                      | SDQ1-SDQ9 | Input/<br>Output | SRAM Data I/O: For a READ, control signals and address are presented at the rising edge of CLK and data is valid <sup>t</sup> KQ after the next rising edge of CLK. Data presented for a WRITE cycle must meet the setup and hold times around CLK.                                                                |

| 32                                                         | Vcc       | Supply           | Power Supply: +5V ±10%                                                                                                                                                                                                                                                                                             |

| 16                                                         | Vss       | Supply           | Ground: GND                                                                                                                                                                                                                                                                                                        |

### **TRUTH TABLE**

| OPERATION  | SCE | SWE | CLK   | SOE | D     | Q NEXT CLOCK | POWER   |

|------------|-----|-----|-------|-----|-------|--------------|---------|

| Deselected | Н   | Х   | 1     | Х   | Х     | High-Z       | Standby |

| READ       | L   | Н   | 1 1 1 | Н   | Х     | High-Z       | Active  |

| READ       | L   | Н   | 1 1   | L   | Х     | Q1-Q9        | Active  |

| WRITE      | L   | L   | 1     | Х   | D1-D9 | High-Z       | Active  |

### **ABSOLUTE MAXIMUM RATINGS\***

| Voltage on Vcc Supply Relative to Vss | 1V to +7V    |

|---------------------------------------|--------------|

| Voltage on any pin relative to Vss    | 1V to Vcc+1V |

| Storage Temperature (plastic)         |              |

| Power Dissipation                     | 1W           |

| Short Circuit Output Current          |              |

\*Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

### **ELECTRICAL CHARACTERISTICS AND RECOMMENDED DC OPERATING CONDITIONS**

$(0^{\circ}C \le T_A \le 70^{\circ}C; Vcc = 5V \pm 10\%)$

| DESCRIPTION                  | CONDITIONS                            | SYMBOL | MIN  | MAX   | UNITS | NOTES |

|------------------------------|---------------------------------------|--------|------|-------|-------|-------|

| Input High (Logic 1) Voltage |                                       | ViH    | 2.2  | Vcc+1 | V     | 1     |

| Input Low (Logic 0) Voltage  |                                       | VIL    | -0.5 | 0.8   | V     | 1, 2  |

| Input Leakage Current        | 0V ≤ VIN ≤ Vcc                        | ILı    | -1   | 1     | μА    |       |

| Output Leakage Current       | Output(s) disabled<br>0V ≤ Vouт ≤ Vcc | ILo    | -1   | 1     | μА    |       |

| Output High Voltage          | loн = -1.0mA                          | Vон    | 2.4  |       | V     | 1     |

| Output Low Voltage           | IoL = 4.0mA                           | Vol    |      | 0.4   | ٧     | 1     |

| Supply Voltage               |                                       | Vcc    | 4.5  | 5.5   | ٧     | 1     |

|                                    |                                                                                              |        |     | MAX |     |       |       |

|------------------------------------|----------------------------------------------------------------------------------------------|--------|-----|-----|-----|-------|-------|

| DESCRIPTION                        | CONDITIONS                                                                                   | SYMBOL | -12 | -16 | -20 | UNITS | NOTES |

| Power Supply<br>Current: Operating | CE ≤ V <sub>IL</sub> ; Vcc = MAX<br>outputs open<br>f = MAX = 1/ <sup>t</sup> RC             | Icc    | 200 | 160 | 150 | mA    | 3     |

|                                    | CE ≥ V <sub>IH</sub> ; V <sub>CC</sub> = MAX<br>outputs open<br>f = MAX = 1/ <sup>t</sup> RC | ISB1   | 90  | 70  | 60  | mA    |       |

| Power Supply<br>Current: Standby   | VCE ≥ VCC - 0.2V;   VCC = MAX; VIL ≤ VSS +0.2V   VIH ≥ VCC -0.2V; f = 0                      | IsB2   | 5   | 5   | 5   | mA    |       |

### **CAPACITANCE**

| DESCRIPTION                    | CONDITIONS                       | SYMBOL | МАХ | UNITS | NOTES |

|--------------------------------|----------------------------------|--------|-----|-------|-------|

| Input Capacitance              | T <sub>A</sub> = 25°C; f = 1 MHz | Cı     | 5   | pF    | 4     |

| Input/Output Capacitance (D/Q) | Vcc = 5V                         | Cı/o   | 7   | pF    | 4     |

# 5 VOLT SYNCHRONOUS SRAM

### **ELECTRICAL CHARACTERISTICS AND RECOMMENDED AC OPERATING CONDITIONS**

(Note 5)  $(0^{\circ}C \le T_A \le 70^{\circ}C; Vcc = 5V \pm 10\%)$

|                             |                   | -1  | 2*  | -1   | 6           | -            | 20   | 100         |         |

|-----------------------------|-------------------|-----|-----|------|-------------|--------------|------|-------------|---------|

| DESCRIPTION                 | SYM               | MIN | MAX | MIN  | MAX         | MIN          | MAX  | UNITS       | NOTES   |

| Clock                       |                   |     |     |      |             | <del>'</del> |      | <del></del> |         |

| Clock cycle time            | tKC               | 12  |     | 16.6 |             | 20           | 1944 | ns          | 1000    |

| Clock HIGH time             | tKH               | 4   |     | 5    |             | 5            |      | ns          |         |

| Clock LOW time              | t <sub>KL</sub>   | 4   |     | 5    |             | 5            |      | ns          |         |

| READ Cycle                  |                   |     |     |      | 7           |              |      |             |         |

| READ cycle time             | tRC               | 12  |     | 16.6 |             | 20           |      | ns          | 9       |

| Address setup time          | tSAS              | 3   |     | 3    |             | 3            |      | ns          | 9       |

| Address hold time           | <sup>t</sup> SAH  | 0.5 |     | 0.5  |             | 1            |      | ns          | 9       |

| Chip Enable setup time      | tSCES             | 3   |     | 3    |             | 3            |      | ns          | 9       |

| Chip Enable hold time       | <sup>t</sup> SCEH | 0.5 |     | 0.5  |             | 1            |      | ns          | 9       |

| Output Enable setup time    | tSOES             | 3   |     | 3    |             | 3            |      | ns          | 9       |

| Output Enable hold time     | <sup>t</sup> SOEH | 0.5 |     | 0.5  | 8 1 2 1 1 1 | 1            |      | ns          | 9       |

| Write Enable setup time     | tSWES             | 3   |     | 3    |             | 3            |      | ns          | 9       |

| Write Enable hold time      | tSWEH             | 0.5 |     | 0.5  |             | 1            |      | ns          | 9       |

| Output hold time from clock | tKOH              | 1   |     | 2    |             | 3            |      | ns          |         |

| Clock to data valid         | †KQ               |     | 6   |      | 8           | 1,11,11      | 10   | ns          | 1.00    |

| Clock to output High-Z      | <sup>t</sup> KQHZ |     | 6   |      | 8           | 1.64         | 10   | ns          | 4, 6, 7 |

| Clock to output Low-Z       | tKQLZ             | 0   |     | 0    |             | 0            |      | ns          | 4, 6, 7 |

| WRITE Cycle                 |                   |     |     |      |             | 1            |      |             |         |

| WRITE cycle time            | tWC               | 12  |     | 16.6 |             | 20           | T    | ns          | l a tar |

| Address setup time          | tSAS              | 3   |     | 3    |             | 3            |      | ns          | 9       |

| Address hold time           | <sup>t</sup> SAH  | 0.5 |     | 0.5  |             | 1            |      | ns          | 9       |

| Chip Enable setup time      | tSCES             | 3   |     | 3    |             | 3            |      | ns          | 9       |

| Chip Enable hold time       | <sup>t</sup> SCEH | 0.5 |     | 0.5  |             | 1            |      | ns          | 9       |

| Write Enable setup time     | tSWES             | 3   |     | 3    |             | 3            |      | ns          | 9       |

| Write Enable hold time      | tSWEH             | 0.5 |     | 0.5  |             | 1            |      | ns          | 9       |

| Data setup time             | tSDS              | 3   |     | 3    |             | 3            |      | ns          |         |

| Data hold time              | tSDH              | 0.5 |     | 0.5  |             | 1            |      | ns          |         |

<sup>\*</sup>Preliminary. Consult factory for availability.

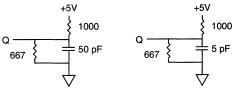

### **AC TEST CONDITIONS**

| Input pulse levels            | Vss to 3.0V          |

|-------------------------------|----------------------|

| Input rise and fall times     | 3ns                  |

| Input timing reference levels | 1.5V                 |

| Output reference levels       | 1.5V                 |

| Output load                   | .See Figures 1 and 2 |

Fig. 1 OUTPUT LOAD EQUIVALENT

Fig. 2 OUTPUT LOAD EQUIVALENT

### **NOTES**

- 1. All voltages referenced to Vss (GND).

- 2. -3V for pulse width  $< {}^{t}RC/2$ .

- 3. Icc is dependent on output loading and cycle rates.

- 4. This parameter is sampled.

- Test conditions as specified with the output loading as shown in Fig. 1 unless otherwise noted.

- Output loading is specified with CL = 5pF as in Fig. 2. Transition is measured ±500mV from steady state voltage.

- At any given temperature and voltage condition, <sup>t</sup>KQHZ is less than <sup>t</sup>KQLZ.

- 8. WE is HIGH for READ cycle.

- This is a synchronous device. All synchronous inputs must meet the setup and hold times with stable logic levels for all rising edges of CLK.

### **READ TIMING** 7, 8, 9

DON'T CARE

₩ UNDEFINED

### WRITE TIMING 7,9

UNDEFINED

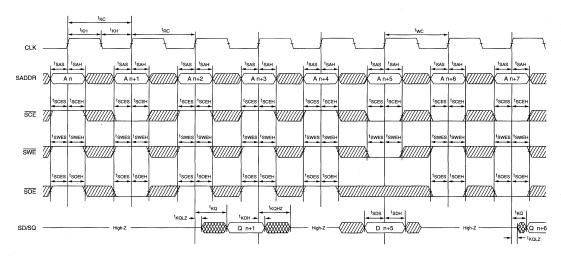

### **READ/WRITE TIMING 7, 8, 9**

DON'T CARE

₩ UNDEFINED