# **OKI** Semiconductor

This version Nov. 1997 Previous version: Mar. 1996

## MSC5301B-01

#### LCD COMMON/SEGMENT DRIVER WITH RAM

#### **GENERAL DESCRIPTION**

The MSC5301B-01 is an LCD driver LSI with built-in RAM. The device's bit mapping method offers greater flexibility because each bit of the RAM for display controls each section on the LCD panel. It can form a graphic display system of  $64 \times 16$  dots in one chip. In addition, the display can be expanded by using additional LSIs.

#### **FEATURES**

LCD driving voltage range

Operating power supply voltage range

5V ±10%

Display duty

Common output

Segment output

1/16 (1/5 bias)

16 outputs

64 outputs

RAM capacity

Serial transfer clock frequency (f<sub>SCK</sub>)

16 x 64 = 1024 bits

500 kHz Max.

• Multichip configuration available

Blanking available

• Built-in RC oscillation circuit

• Package:

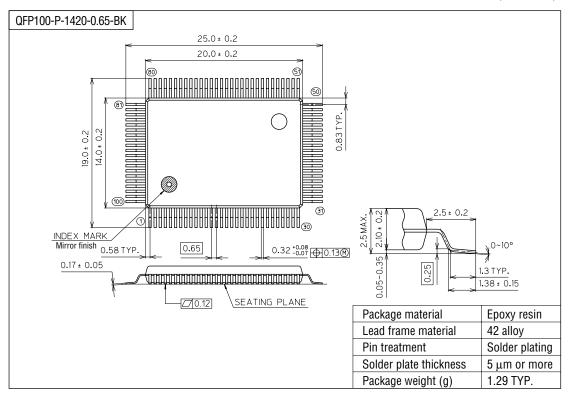

100-pin plastic QFP (QFP100-P-1420-0.65-BK) (Product name: MSC5301B-01GS-BK)

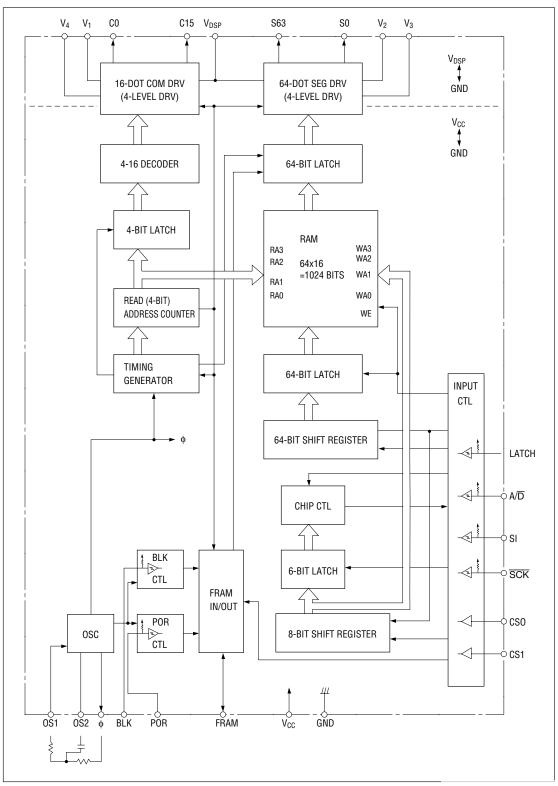

## **BLOCK DIAGRAM**

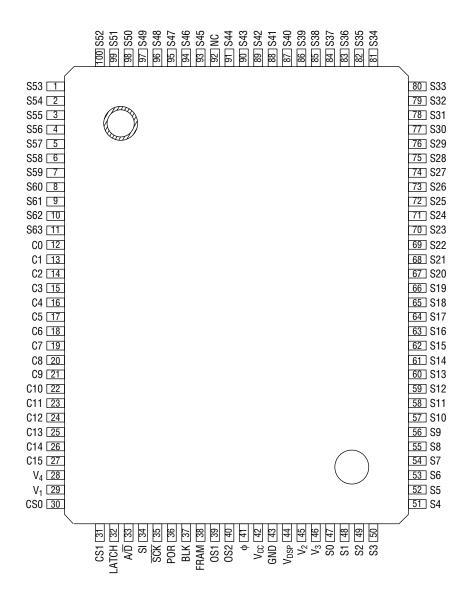

## **PIN CONFIGURATION (TOP VIEW)**

NC: No connection

100-Pin Plastic QFP

## **ABSOLUTE MAXIMUM RATINGS**

| Parameter            | Symbol            | Condition | Rating                                        | Unit |

|----------------------|-------------------|-----------|-----------------------------------------------|------|

| Power Supply Voltage | V <sub>CC</sub>   | Ta = 25°C | -0.3 to +6.5                                  | V    |

| Power Supply Voltage | V <sub>DSP</sub>  | Ta = 25°C | -0.3 to +18.0 *1                              | V    |

| Input Voltage        | V <sub>IN</sub>   | Ta = 25°C | -0.3V≤V <sub>IN</sub> ≤V <sub>CC</sub> +0.3   | V    |

| Input Voltage        | V <sub>INDP</sub> | Ta = 25°C | -0.3≤V <sub>INDP</sub> ≤V <sub>DSP</sub> +0.3 | V    |

| Power Dissipation    | P <sub>D</sub>    | Ta = 85°C | 275                                           | mW   |

| Storage Temperature  | T <sub>STG</sub>  | _         | -55 to +125                                   | °C   |

<sup>\*1</sup>  $V_{DSP} > V_1 > V_2 > V_3 > V_4 > GND$

## **RECOMMENDED OPERATING CONDITIONS**

| Parameter             | Symbol           | Condition | Range          | Unit |

|-----------------------|------------------|-----------|----------------|------|

| Power Supply Voltage  | V <sub>CC</sub>  | GND = 0V  | 4.5 to 5.5     | V    |

| Power Supply Voltage  | V <sub>DSP</sub> | GND = 0V  | 6.0 to 16.0 *1 | V    |

| Operating Temperature | T <sub>op</sub>  | _         | -40 to +85     | °C   |

| Shift Frequency       | f <sub>SCK</sub> | _         | 25 to 500      | kHz  |

| Oscillation Frequency | fφ               | _         | 3.84 to 16.0   | kHz  |

| Frame Frequency       | f <sub>FR</sub>  | _         | 60 to 250      | Hz   |

<sup>\*1</sup>  $V_{DSP}>V_1>V_2>V_3>V_4>GND$

## **ELECTRICAL CHARACTERISTICS**

#### **DC Characteristics**

$(V_{CC} = 5V, Ta = -40 \text{ to } +85^{\circ}C)$

| Parameter            | Symbol           | Cond                    | lition                    | Min.                | Тур. | Max.                | Unit |

|----------------------|------------------|-------------------------|---------------------------|---------------------|------|---------------------|------|

| "H" Input Voltage    | V <sub>IH</sub>  | — *1                    |                           | 3.5                 | _    | V <sub>CC</sub>     | V    |

| "L" Input Voltage    | V <sub>IL</sub>  | _                       | - *1                      | 0                   | _    | 1.5                 | V    |

| Hysteresis Voltage 1 | V <sub>HS1</sub> | _                       | - *2                      | 0.3                 | 0.8  | 1.4                 | V    |

| Hysteresis Voltage 2 | V <sub>HS2</sub> | _                       | - *9                      | 0.2                 | 0.4  | 0.8                 | V    |

| Pull-up Resistance   | R <sub>PU</sub>  | V <sub>I</sub> = 0V     | *2                        | 10                  | 35   | 60                  | kΩ   |

| Pull-up Voltage      | $V_{PH}$         | $ I_I  < 1\mu A$        | *2                        | 4.9                 | _    | _                   | V    |

| "H" Input Current    | l <sub>IH</sub>  | $V_{CC} = 5.5V, V_{IH}$ | t = 5.5V *3               | _                   | _    | ±10                 | μΑ   |

| "L" Input Current    | I <sub>IL</sub>  | $V_{CC} = 5.5V, V_{IL}$ | = 0V *3                   | _                   | _    | ±10                 | μΑ   |

| "H" Output Voltage   | V <sub>OH</sub>  | $I_0 = -0.4 \text{mA}$  | *4                        | 4.6                 | _    | _                   | V    |

| "L" Output Voltage   | V <sub>OL</sub>  | I <sub>0</sub> = 1.6mA  | I <sub>0</sub> = 1.6mA *4 |                     | _    | 0.4                 | V    |

| Common Driver        | $V_{DP}$         | $V_{DSP} = 10V$         | $I = -10\mu A$            | $V_{DSP}$ -0.4      | _    | _                   | V    |

| Output Voltage       | V <sub>1</sub>   | *5                      | $I = \pm 10\mu A$         | V <sub>1</sub> -0.4 | _    | V <sub>1</sub> +0.4 | V    |

|                      | V <sub>4</sub>   |                         | $I = \pm 10 \mu A$        | V <sub>4</sub> -0.4 | _    | V <sub>4</sub> +0.4 | V    |

|                      | V <sub>SS</sub>  |                         | I = +10μA                 | _                   | _    | 0.4                 | V    |

| Segment Driver       | $V_{DP}$         | $V_{DSP} = 10V$         | $I = -10\mu A$            | $V_{DSP}$ -0.4      | _    | _                   | V    |

| Output Voltage       | V <sub>2</sub>   | *6                      | $I = \pm 10 \mu A$        | V <sub>2</sub> -0.4 | _    | V <sub>2</sub> +0.4 | V    |

|                      | V <sub>3</sub>   |                         | $I = \pm 10 \mu A$        | V <sub>3</sub> -0.4 | _    | V <sub>3</sub> +0.4 | V    |

|                      | V <sub>SS</sub>  |                         | I = +10μA                 | _                   | _    | 0.4                 | V    |

| Supply Current 1     | I <sub>CC</sub>  | V <sub>CC</sub> = 5.0V  | *7                        | _                   | _    | 6.0                 | mA   |

| Supply Current 2     | I <sub>DSP</sub> | V <sub>CC</sub> = 5.0V  | *8                        | _                   |      | 0.5                 | mA   |

<sup>\*1</sup> Applicable to all input pins

<sup>\*2</sup> Applicable to LATCH,  $A/\overline{D}$ , SI,  $\overline{SCK}$ , BLK and POR pins

<sup>\*3</sup> Applicable to CS0, CS1, OS1 and FRAM pins

<sup>\*4</sup> Applicable to FRAM and \$\phi\$ pins

<sup>\*5</sup> Applicable to C0 - C15 pins

<sup>\*6</sup> Applicable to S0 - S63 pins

<sup>\*7</sup> f $\phi$  = 6.4 kHz, f<sub>SCK</sub> = 200 kHz, no load, display pattern = checkers V<sub>DSP</sub> = 16V, Current flows into V<sub>CC</sub> pin

<sup>\*8</sup>  $f\phi = 6.4 \text{ kHz}$ ,  $f_{SCK} = 200 \text{ kHz}$ , no load, display pattern = checkers  $V_{DSP} = 16V$ , Current flows into  $V_{DSP}$  pin

<sup>\*9</sup> Applicable to OS1 pin

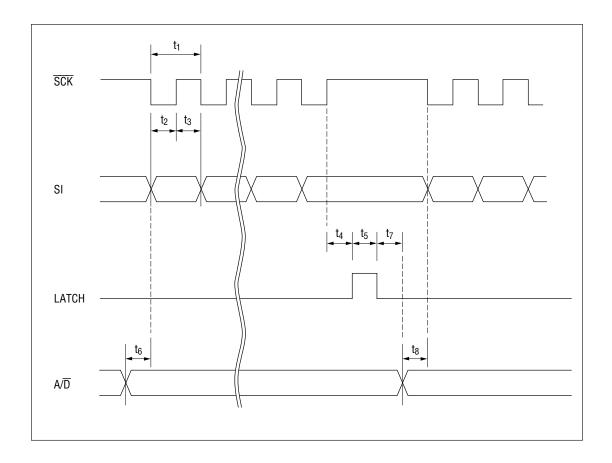

## **AC Characteristics**

| $(V_{CC} =$  | 5V. | Ta = | -40 to | +85° | C)               |

|--------------|-----|------|--------|------|------------------|

| ( v i .i . — | υν, | ıu – | 70 10  | 100  | $\mathbf{v}_{i}$ |

| Parameter          | Symbol          | Condition     | Min. | Тур. | Max. | Unit |

|--------------------|-----------------|---------------|------|------|------|------|

| SCK Clock Period   | t <sub>1</sub>  | _             | 2    | _    | _    | μs   |

| SI Data Setup Time | t <sub>2</sub>  | _             | 1    | _    | _    | μs   |

| SI Data Hold Time  | t <sub>3</sub>  | _             | 1    | _    | _    | μs   |

| SCK-LATCH Time     | t <sub>4</sub>  | _             | 1    | _    | _    | μs   |

| LATCH Pulse Width  | t <sub>5</sub>  | _             | 15   | _    | _    | μs   |

| A/D Setup Time     | t <sub>6</sub>  | _             | 1    | _    | _    | μs   |

| A/D Hold Time      | t <sub>7</sub>  | _             | 1    | _    | _    | μs   |

| A/D-SCK Time       | t <sub>8</sub>  | _             | 1    | _    | _    | μs   |

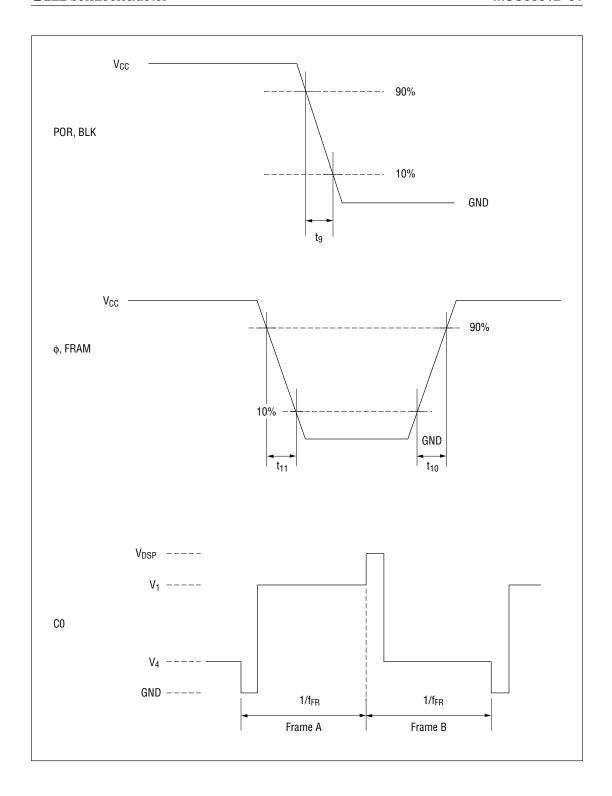

| POR, BLK Fall Time | t <sub>9</sub>  | _             | _    | _    | 20   | μs   |

| φ, FRAM Rise Time  | t <sub>10</sub> | $C_L = 50 pF$ | _    | _    | 0.3  | μS   |

| φ, FRAM Fall Time  | t <sub>11</sub> | $C_L = 50 pF$ | _    | _    | 0.3  | μs   |

| Frame Frequency    | f <sub>FR</sub> | *1            | 85   | 100  | 115  | Hz   |

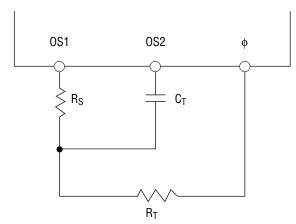

The dispersion of external resistors and capacitors is not included.  $R_S=1k\Omega,\,R_T=16k\Omega,\,C_T=4700pF,\,V_{CC}=4.5V\text{ to }5.5V$ \*1

$$R_S = 1k\Omega$$

,  $R_T = 16k\Omega$ ,  $C_T = 4700pF$ ,  $V_{CC} = 4.5V$  to 5.5V

#### **FUNCTIONAL DESCRIPTION**

#### **Pin Functional Description**

## • OS1 (Pin 39), OS2 (Pin 40), ♦ (Pin 41)

These are pins for the RC oscillation circuit. Connect external resistors and a capacitor as shown below. When inputting the external clock pulse, input it to OS1 pin. OS2 and  $\phi$  pins should be left open.

The relationship between the frame frequency  $f_{FR}$  and internal clock frequency  $f_{\phi}$  is expressed by the following equation:

(RC oscillation frequency = internal clock frequency)

$$f\phi = 4 \times 16 \times f_{FR}$$

In addition, the relationship between the frame frequence  $f_{FR}$  and frame synchronizing signal frequency  $f_{FRAM}$  is expressed by the following equation.

$$f_{FRAM} = f_{FR}/2$$

#### CS0 (Pin 30), CS1 (Pin 31)

Chip select input pins. Master or slave mode is selected by CS0 and CS1 as shown in the table below. A maximum of 4 chips can be connected in this manner. Use the master mode when using a single device.

| CS0 | CS1 | Operation mode |                          |

|-----|-----|----------------|--------------------------|

| L   | L   | Master mode    | H: V <sub>CC</sub> level |

| Н   | L   | Slave mode     | L: GND level             |

| L   | Н   | Slave mode     |                          |

| Н   | Н   | Slave mode     |                          |

## • FRAM (Pin 38)

This is an input and output pin for the frame synchronizing signal to be used for master/slave configuration. This is used as an output pin in master mode and as an input pin in slave mode.

#### SI (Pin 34)

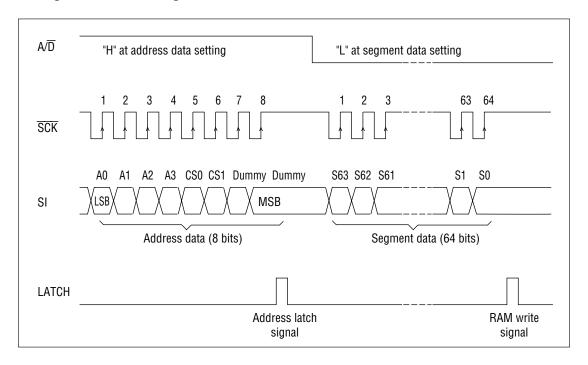

This is a serial data input of address data (8 bits) and segment data (64 bits). A pull-up resistor (10 k $\Omega$  - 60 k $\Omega$ ) and a Schmitt circuit are contained.

## • SCK (Pin 35)

This is a shift clock input of address data (8 bits) and segment data (64 bits). The serial data is shifted at the rising edge of  $\overline{SCK}$  pulse. A pull-up resistor (10 k $\Omega$  - 60 k $\Omega$ ) and a Schmitt circuit are contained.

## • LATCH (Pin 32)

This is a latch pulse input of address data (8 bits) and segment data (64 bits). The latch data comes through at "H" level of LATCH and the data just before "H" level is latched at "L" level. A pull-up resistor (10 k $\Omega$  - 60 k $\Omega$ ) and a Schmitt circuit are contained.

## A/D (Pin 33)

This is a data select signal input of address data (8 bits) and segment data (64 bits). "H" level is set in the case of address 8-bit input and "L" level is set in the case of segment data 64-bit input. A pull-up resistor ( $10 \text{ k}\Omega$  -  $60 \text{ k}\Omega$ ) and a Schmitt circuit are contained.

• V<sub>DSP</sub> (Pin 44), V<sub>1</sub> (Pin 29), V<sub>2</sub> (Pin 45), V<sub>3</sub> (Pin 46), V<sub>4</sub> (Pin 28), V<sub>CC</sub> (Pin 42), GND (Pin 43) These are power supply pins for this LSI and bias power supply pins for LCD driving. V<sub>CC</sub>, which is a power supply pin, is from 4.5V to 5.5V and GND, which is a ground pin, is 0V. V<sub>DSP</sub>, which is an LCD driving power supply pin, is usually used in the range between 6V and 16V. V<sub>1</sub>, V<sub>2</sub>, V<sub>3</sub> and V<sub>4</sub> are bias power supply pins for LCD driving and are usually used with the bias voltage supplied from an external source.

#### • BLK (Pin 37)

This is an input pin to control the LCD panel display.

When a "H" level is input (or when this pin is open), the segment output pins S0 - S63 come to the levels  $V_2$  -  $V_3$  and the LCD panel is turned off. In addition, during this period, reading of data from display RAM stops but writing into the display RAM of address and segment data input from the SI pin is enabled.

When this pin is changed from "H" to "L" level, the frame synchronizing signal FRAM is output within 2 cycles of an internal clock f $\phi$ , and multiple chips are synchronized. Then, the display RAM address is set to "0000". After 1/16 frame cycle from FRAM signal generation, the output is applied from the "0001" data of the display RAM address to the segment driver. When the power supply is turned on, keep this pin to "H" level (or leave open) until writing data to the RAM is completed, because the display RAM contents are undefined at power-on. A pull-up resistor (10 k $\Omega$  - 60 k $\Omega$ ) and a Schmitt circuit are contained.

#### POR (Pin 36)

This is a power-on-reset input pin. When a "H" level is input (or when this pin is open), the common and segment outputs come to the static display-off state regardless of the BLK pin and the segment output pins S0-S63 become  $V_3$  level and the common output pins C0-C15 become  $V_4$  level.

When this pin changes from "H" to "L" level, the frame synchronizing signal FRAM is output within 2 cycles of an internal clock  $f\phi$ , synchronized at multichip, and is moreover dynamic-operated from the frame B. The display RAM address is set to "0000."

After 1/16 frame cycle from FRAM signal generation, the data at display RAM address "0001" is output to the segment driver. However, because the BLK pin is usually at "H" level when the power-on-reset is released, reading data from the display RAM stops and display-off segment data is forcibly transferred to the segment output.

A pull-up resistor (10 k $\Omega$  - 60 k $\Omega$ ) and a Schmitt are contained.

#### • C0 (Pin 12) - C15 (Pin 27)

These are 16-output pins of common driver which are used for LCD panel driving. The outputs have 4 levels.  $V_{DSP}$  and GND levels are select levels. The V1 and V4 levels are non-select levels.

#### • S0 (Pin 47) - S63 (Pin 11)

These are 64-output pins of segment driver which are used for LCD panel driving. The outputs have 4 levels.  $V_{DSP}$  and GND levels are used as display-on ones, which correspond to "1" of the display RAM data.  $V_2$  and  $V_3$  levels are used as display-off ones, which correspond to "0" of the display RAM data.

## **NOTES ON USE**

Note the following when turning power on and off:

The LCD drivers of this IC require a high voltage. For this reason, if a high voltage is applied to the LCD drivers with the logic power supply floating, excess current flows. This may damage the IC. Be sure to carry out the following power-on and power-off sequences:

When turning power on:

First turn  $V_{CC}$  ON, next  $V_{DSP}$ ,  $V_4$ ,  $V_3$ ,  $V_2$ ,  $V_1$  ON. Or both ON at the same time.

When turning power off:

First turn V<sub>DSP</sub>, V<sub>4</sub>, V<sub>3</sub>, V<sub>2</sub>, V<sub>1</sub> OFF, next V<sub>CC</sub> OFF. Or both OFF at the same time.

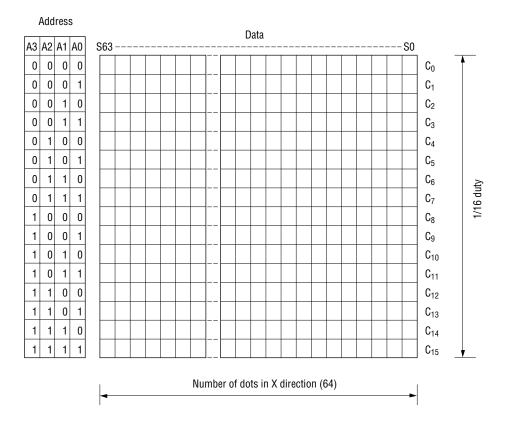

## Relationship Between LCD Screen Size and Display RAM

This LCD driver has built-in RAM for the display of  $16 \times 64 = 1024$  bits and each address corresponds to each 1/16 duty of the LCD.

The data corresponds to the number of dots in the X direction. The relation between the LCD screen size and the display RAM is shown below.

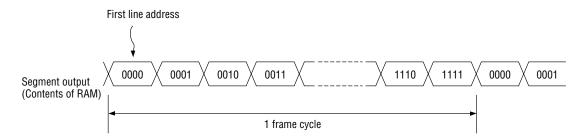

#### Relationship Between Frame Cycle and Display RAM Data

The output of the display RAM data corresponds to the segment output. The relationship between the frame cycle and the display RAM data is as follows:

OKI Semiconductor www.MSC5301B-01

## **Multiple Configuration**

This LCD driver can form multiple configuration.

It is possible to form a maximum of 4 devices (a panel of up to  $256 \times 16$  dots in size can be formed) by using chip select signals CS0 and CS1. The devices in multiple configuration must be synchronized with one another. In this configuration, one device in the master mode and the other devices in the slave mode are used in combination. In the master mode, the original oscillation signal  $\phi$  and the synchronous signal FRAM are output; in the slave mode, the original oscillation signal  $\phi$  and the synchronous signal FRAM are input.

Refer to items CS0 and CS1 of pin description on the mode setting method.

The original oscillation signal output pin  $\phi$  of the master mode device is connected to the OS1 pin of the slave mode device and the synchronizing signal pin FRAM is also connected to the FRAM pin of the slave mode device.

Connect SI,  $\overline{SCK}$ , LATCH,  $A/\overline{D}$ , POR and BLK of the master mode device to SI,  $\overline{SCK}$ , LATCH,  $A/\overline{D}$ , POR and BLK of each of the slave mode devices and connect them to CPU for control. In addition, connect the devices so that  $V_{DSP}$ ,  $V_1$ ,  $V_2$ ,  $V_3$ ,  $V_4$  and GND are shared between the devices, and connect them to each voltage level divided by external resistors.

## **Address Data Configuration**

| (MSB) |               |     |         |    |       |         | (LSB) |

|-------|---------------|-----|---------|----|-------|---------|-------|

| 7     | 6             | 5   | 4       | 3  | 2     | 1       | 0     |

| Dumm  | Dummy data    |     | address |    | Lower | address |       |

| DM    | DM            | CS1 | CS0     | A3 | A2    | A1      | A0    |

|       |               |     |         |    |       |         |       |

|       |               |     |         |    |       |         |       |

| 2     | 2 bits 2 bits |     |         | 4  | bits  |         |       |

The lower address, which is the display RAM address, corresponds to the common sides C0 - C15 of the LCD panel.

The upper address corresponds to the logical state of chip select pins CS0 and CS1 and the lower address is set to the device.

For the device to output the common signal ( $\phi$ , FRAM), set both of the upper address 2 bits to "L". The 2 bits of dummy data can be set to either "L" or "H".

OKI Semiconductor wwMSc5301B-01

## Serial Signal to be Input From CPU

The following signals are input from an external CPU to this LCD driver.

- Serial transfer clock  $\rightarrow \overline{SCK}$

- Serial transfer data  $\rightarrow$  SI

- Serial transfer latch  $\rightarrow$  LATCH

- Serial data select  $\rightarrow A/\overline{D}$

The operations are shown in the following table.

| Mode                    | A/D | SCK                       | LATCH                                                       | SI                                                                                                         |

|-------------------------|-----|---------------------------|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| Address data input mode | Н   | Shifts at the rising edge | 8-bit address latch at falling edge (level sensitive)       | 8-bit address data<br>Serial input from LSB side                                                           |

| Segment data input mode | L   | Shifts at the rising edge | 64-bit segment data latch at falling edge (level sensitive) | 64-bit segment data Serial input from S63 corresponding data "1" : Display-on data, "0" : Display-off data |

#### **Timing Chart of Serial Signal Transferred From CPU**

#### Notes:

- 1. Make sure to set the address before writing the segment data to RAM. Then, write the segment data to RAM.

- 2. While the POR pin is "H" (upon power-on reset), neither the address data nor the segment data can be entered.

Operation upon Power ON (When Single Device Used)

## $V_{CC}$ P0R BLK (External R and C) FRAM Common signal output Frame A Frame B Frame B Frame A Frame B Frame B Frame A Frame A Segment signal\_output www.DataSheet4U.com Dynamic light-out state Dynamic operation (normal operation) RAM address 0 - F 0 - F 0-0 0-F 0 - F 0 - F 0 - F

OKI Semiconductor www.MSC5301B-01

## **PACKAGE DIMENSIONS**

(Unit: mm)

Notes for Mounting the Surface Mount Type Package

The SOP, QFP, TSOP, SOJ, QFJ (PLCC), SHP and BGA are surface mount type packages, which are very susceptible to heat in reflow mounting and humidity absorbed in storage.

Therefore, before you perform reflow mounting, contact Oki's responsible sales person for the product name, package name, pin number, package code and desired mounting conditions (reflow method, temperature and times).