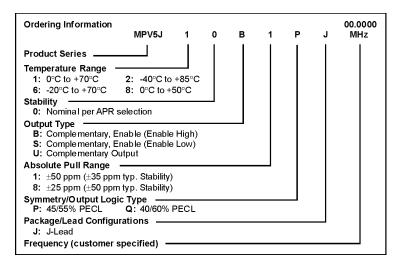

## MPV5J Series 9x14 mm, 5.0 Volt, PECL/LVDS VCXO

- Integrated phase jitter of less than 1 ps from 12 kHz to 20 MHz

- Ideal for low noise PLL applications

0.300

(7.62)

TYP

|                           | PARAMETER                     | Symbol                                      | Min.                                                                                                 | Тур.       | Max.      | Units  | Condition                  |  |

|---------------------------|-------------------------------|---------------------------------------------|------------------------------------------------------------------------------------------------------|------------|-----------|--------|----------------------------|--|

|                           | Frequency Range               | F                                           | 30 800 MHz<br>(Consult factory for exact frequency availability)                                     |            |           |        |                            |  |

|                           | Frequency Stability           | ∆F/F                                        | (See Ordering Information)                                                                           |            |           | 1      | See Note 1                 |  |

|                           | Operating Temperature         | TA                                          | (See Ordering Information)                                                                           |            |           |        |                            |  |

|                           | Storage Temperature           | Ts                                          | -55                                                                                                  |            | +125      | °C     |                            |  |

|                           | Input Voltage                 | Vcc                                         | 4.75                                                                                                 | 5.0        | 5.25      | V      |                            |  |

|                           | Input Current                 | ldd                                         |                                                                                                      | 60         | 70        | mA     |                            |  |

|                           | Symmetry (Duty Cycle)         |                                             | (See Ordering Information)                                                                           |            |           |        |                            |  |

|                           | Load                          |                                             |                                                                                                      |            |           |        | See Note 2                 |  |

|                           | Rise/Fall Time                | Tr/Tf                                       |                                                                                                      | .35        | .55       | ns     | @ 20/80% LVPECL            |  |

| tions                     |                               |                                             |                                                                                                      | .50        | 1.0       | ns     | @ 20/80% LVDS              |  |

|                           | Logic "1" Level               | Voh                                         | Vcc -1.02                                                                                            |            |           | V      |                            |  |

|                           | Logic "0" Level               | Vol                                         |                                                                                                      |            | Vcc -1.63 | V      |                            |  |

|                           | Phase Jitter                  | φJ                                          |                                                                                                      |            |           |        |                            |  |

|                           | @ 77.76 MHz                   |                                             |                                                                                                      | 0.6        | 0.9       | ps RMS | Integrated 12 kHz - 20 MHz |  |

| fica                      | @ 155.52 MHz                  |                                             |                                                                                                      | 0.3        | 0.55      | ps RMS | Integrated 12 kHz - 20 MHz |  |

| eci                       | @ 622.08 MHz                  |                                             |                                                                                                      | 0.25       | 0.5       | ps RMS | Integrated 12 kHz - 20 MHz |  |

| Electrical Specifications | Phase Noise (Typical)         | 100 Hz                                      | 1 kHz                                                                                                | 10 kHz     | 100 kHz   | 1 MHz  | Offset from carrier        |  |

|                           | @ 77.76 MHz                   | -80                                         | -110                                                                                                 | -133       | -144      | -147   | dBc/Hz                     |  |

|                           | @ 155.52 MHz                  | -80                                         | -110                                                                                                 | -133       | -144      | -147   | dBc/Hz                     |  |

|                           | @ 622.08 MHz                  | -70                                         | -100                                                                                                 | -125       | -135      | -137   | dBc/Hz                     |  |

|                           | Modulation Bandwidth          | fm                                          | 10                                                                                                   |            |           | Khz    | -3 dB bandwidth            |  |

|                           | Input Impedance               | Zin                                         | 50                                                                                                   |            |           | KΩ     |                            |  |

|                           | Control Voltage               | Vcc                                         | 0                                                                                                    |            | 5.0       | V      | Pin 1 voltage              |  |

|                           | Center Frequency              | Vc0                                         | <u> </u>                                                                                             | 2.5        | 0.0       | v      |                            |  |

|                           | Linearity                     | 1000                                        |                                                                                                      | 5          | 10        | %      |                            |  |

|                           | Pullability                   | APR                                         | (See Ordering Information)                                                                           |            |           |        | See Note 3                 |  |

|                           | Enable/Disable Logic          |                                             | CMOS high, Vcc or N/C - enables output                                                               |            |           |        | Output Option B            |  |

|                           |                               |                                             | CMOS low or GND - disables output                                                                    |            |           |        |                            |  |

|                           |                               |                                             | PECL low, GND, or N/C - enables output                                                               |            |           |        | Output Option S            |  |

|                           |                               |                                             |                                                                                                      |            |           |        | Output Option S            |  |

| Environmental             | Machanical Shash              | PECL high - disables output                 |                                                                                                      |            |           |        |                            |  |

|                           | Mechanical Shock<br>Vibration | Per MIL-STD-202, Method 213, Condition C    |                                                                                                      |            |           |        |                            |  |

|                           |                               | Per MIL-STD-202, Method 201 & 204           |                                                                                                      |            |           |        |                            |  |

| ror                       | Reflow Solder Conditions      | 240°C for 10 s max., or 230°C for 90 s max. |                                                                                                      |            |           |        |                            |  |

| ivi                       | Hermeticity                   |                                             | Per MIL-STD-202, Method 112 (1 x 10 <sup>®</sup> atm.cc/s of helium)<br>Per MIL-STD-883, Method 2003 |            |           |        |                            |  |

| ш                         | Solderability                 | Let MIL-8                                   | 5 I D-883, Me                                                                                        | ethod 2003 | 5         |        |                            |  |

1. Stability given for deviation over temperature.

2. PECL load - see load circuit diagram #5.

3. APR specification inclusive of initial tolerance, deviation over temperature, shock, vibration, supply voltage, and aging.

MtronPTI reserves the right to make changes to the product(s) and service(s) described herein without notice. No liability is assumed as a result of their use or application.

Please see www.mtronpti.com for our complete offering and detailed datasheets. Contact us for your application specific requirements: MtronPTI 1-800-762-8800.

0.565 (14.22) MAX 6 5 4 0.385 (9.78) MAX 1 2 3

in inches (mm).

C DENOTES PIN 1.

SUGGESTED SOLDER PAD LAYOUT

## **Pin Connections**

| PIN | FUNCTION             |  |  |

|-----|----------------------|--|--|

| 1   | Control Voltage      |  |  |

| 2   | Output Enable or N/C |  |  |

| 3   | Ground/Case          |  |  |

| 4   | Output Q             |  |  |

| 5   | Output Q or N/C      |  |  |

| 6   | +Vcc                 |  |  |