## **MPV3J Series** 9x14 mm, 3.3 Volt, PECL/LVDS, VCXO

Ultra low jitter VCXO approaching SAW jitter performance but with the temperature stability advantage of a crystal based resonator

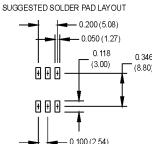

| <br>⊕ ⊕ ⊕ —    | 0.118 (3.00) | 0.346 (8.80) |

|----------------|--------------|--------------|

| <b>₱ ₱ ₱ =</b> | 100 (2.54)   | <u> </u>     |

## **Pin Connections**

| PIN | FUNCTION             |

|-----|----------------------|

| 1   | Control Voltage      |

| 2   | Output Enable or N/C |

| 3   | Ground/Case          |

| 4   | Output Q             |

| 5   | Output Q or N/C      |

| 6   | +Vcc                 |

|                | PARAMETER             | Symbol | Min.                       | Тур.        | Max.            | Units      | Condition/Notes            |

|----------------|-----------------------|--------|----------------------------|-------------|-----------------|------------|----------------------------|

|                | Frequency Range       | F      | 30                         |             | 800             | MHz        | See Note 1                 |

|                | Operating Temperature | TA     | (See Ordering              | g Informati |                 |            |                            |

|                | Storage Temperature   | Ts     | -55                        |             | +125            | °C         |                            |

|                | Frequency Stability   | ΔF/F   | (See Ordering              | g Informati |                 | See Note 2 |                            |

|                | Aging                 |        |                            |             |                 |            |                            |

|                | 1st Year              |        | -3/-5                      |             | +3/+5           | ppm        | < 52 MHz / ≥ 52 MHz        |

|                | Thereafter (per year) |        | -1/-2                      |             | +1/+2           | ppm        | < 52 MHz / ≥ 52 MHz        |

|                | Pullability/APR       |        | (See Ordering Information) |             |                 |            | See Note 3                 |

|                | Control Voltage       | Vc     | Ò                          | 1.65        | 3.3             | V          | Pin 1 Voltage              |

|                | Linearity             |        |                            | 5           | 10              | %          | Positive Monotonic Slope   |

|                | Modulation Bandwidth  | fm     | 10                         |             |                 | kHz        | -3 dB bandwidth            |

| <u>س</u> ا     | Input Impedance       | Zin    | 50k                        |             |                 | Ohms       |                            |

| ΙË             | Input Voltage         | Vcc    | 3.135                      | 3.3         | 3.465           | V          |                            |

| ä              | Input Current         | Icc    |                            | 60          | 70              | MA         |                            |

| Specifications | Output Type           |        |                            |             |                 |            | PECL/LVDS                  |

|                | Load                  |        |                            |             |                 |            | See Note 4                 |

|                | Symmetry (Duty Cycle) |        |                            |             |                 |            | Vcc – 1.3 VDC              |

| ca             | Output Skew           |        |                            |             | 200             | ps         |                            |

| ᄩ              | Differential Voltage  | Vo     | 250                        | 350         | 450             | mV         | LVDS                       |

| Electrical     | Logic "1" Level       | Voh    | Vcc – 1.02                 |             |                 | V          | PECL                       |

| ۱۳             | Logic "0" Level       | Vol    |                            |             | Vcc - 1.63      | V          | PECL                       |

|                | Rise/Fall Time        | Tr/Tf  |                            | 0.35        | 0.55            | ns         | @ 20/80% LVPECL            |

|                |                       |        |                            | 0.50        | 1.0             | Ns         | @ 20/80% LVDS              |

|                | Enable/Disable Logic  |        | 80% Vcc min                | or N/C: ou  | Output Option B |            |                            |

|                |                       |        | 20 % Vcc ma                |             |                 |            |                            |

|                |                       |        | PECL low, G                |             | Output Option S |            |                            |

|                |                       |        | PECL high –                |             |                 |            |                            |

|                | Start up Time         |        |                            | 5           |                 | ms         |                            |

| 1              | Phase Jitter          | ΦЈ     |                            |             |                 |            |                            |

|                | @ 155.52 MHz          |        |                            | 0.3         | 0.55            | ps RMS     | Integrated 12 kHz – 20 MHz |

|                | @ 622.08 MHz          |        |                            | 0.25        | 0.5             | ps RMS     | Integrated 12 kHz – 20 MHz |

|                | Phase Noise (Typical) | 10 Hz  | 100 Hz                     | 1 kHz       | 10 kHz          | 100 kHz    | Offset from carrier        |

| Ш              | @ 155.52 MHz          | -50    | -80                        | -115        | -135            | -140       | dBc/Hz                     |

- Note 1: Consult factory for exact frequency availability

- Note 2: Stability given for deviation over temperature

- Note 3: APR specification inclusive of initial tolerance, deviation over temperature, shock, vibration, supply voltage, and aging

- Note 4: PECL load see load circuit diagram #5. LVDS load see load circuit diagram #9.

MtronPTI reserves the right to make changes to the product(s) and service(s) described herein without notice. No liability is assumed as a result of their use or application.