# **6525 TRI-PORT INTERFACE**

## CONCEPT ...

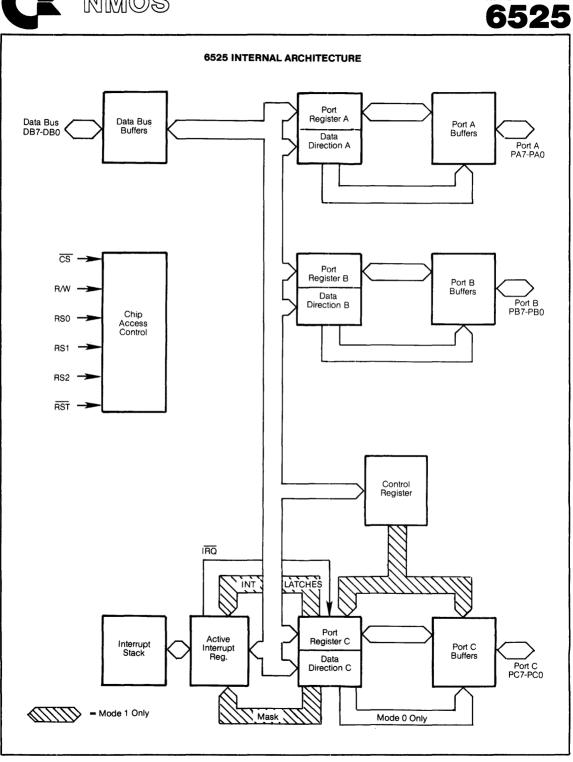

The 6525 TRI-PORT Interface (TPI) is designed to simplify the implementation of complex I/O operations in microcomputer systems. It combines two dedicated 8-bit I/O ports with a third 8-bit port programmable for either normal I/O operation or priority interrupt/handshaking control. Depending on the mode selected, the 6525 can provide 24 individually programmable I/O lines or 16 I/O lines, 2 handshake lines and 5 priority interrupt inputs.

# FEATURES:

- 24 individually programmable I/O lines or 16 I/O lines, 2 handshake lines and 5 interrupt inputs.

- Priority or non-priority interrupts

- · Automatic handshaking

- Completely static operation

- Two TTL Drive Capability

- 8 directly addressable registers

- 1 MHz, 2MHz and 3MHz operation

| 6525 | REGISTERS   |

|------|-------------|

| 0020 | neolo i eno |

| *000 | R0                                | PRA-Port Register A              |  |  |  |  |  |  |  |

|------|-----------------------------------|----------------------------------|--|--|--|--|--|--|--|

| 001  | R1                                | PRB-Port Register B              |  |  |  |  |  |  |  |

| 010  | R2                                | PRC – Port Register C            |  |  |  |  |  |  |  |

| 011  | R3                                | DDRA – Data Direction Register A |  |  |  |  |  |  |  |

| 100  | R4                                | DDRB-Data Direction Register B   |  |  |  |  |  |  |  |

| 101  | R5                                | DDRC – Data Direction Register C |  |  |  |  |  |  |  |

| 110  | R6                                | CR – Control Register            |  |  |  |  |  |  |  |

| 111  | R7                                | AIR – Active Interrupt Register  |  |  |  |  |  |  |  |

| *NC  | *NOTE: RS2, RS1, RS0 respectively |                                  |  |  |  |  |  |  |  |

|     | <u> </u> |    | 1   |

|-----|----------|----|-----|

| VSS | 1        | 40 | DB7 |

| PA0 | 2        | 39 | DB6 |

| PA1 | 3        | 38 | DB5 |

| PA2 | 4        | 37 | DB4 |

| PA3 | 5        | 36 | DB3 |

| PA4 | 6        | 35 | DB2 |

| PA5 | 7        | 34 | DB1 |

| PA6 | 8        | 33 | DB0 |

| PA7 | 9        | 32 | PC7 |

| PB0 | 10       | 31 | PC6 |

| PB1 | 11       | 30 | PC5 |

| PB2 | 12       | 29 | PC4 |

| PB3 | 13       | 28 | PC3 |

| PB4 | 14       | 27 | PC2 |

| PB5 | 15       | 26 | PC1 |

| PB6 | 16       | 25 | PC0 |

| PB7 | 17       | 24 | RSO |

| ĊŚ  | 18       | 23 | RS1 |

| R/W | 19       | 22 | RS2 |

| VDD | 20       | 21 | RES |

# NMOS

MPS

# MAXIMUM RATINGS

Supply Voltage, V<sub>CC</sub> Input/Output Voltage, V<sub>IN</sub> Operating Temperature, T<sub>OP</sub> Storage Temperature, T<sub>STG</sub> -0.3V to +7.0V -0.3V to +7.0V 0°C to 70°C -55°C to 150°C

All inputs contain protection circuitry to prevent damage due to high static discharges. Care should be exercised to prevent unnecessary application of voltages in excess of the allowable limits.

#### COMMENT

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only. Functional operation of this device at these or any other conditions above those indicated in the operational sections of this specification is not implied and exposure to absolute maximum rating conditions for extended periods may affect device reliability.

| CHARACTERISTIC                                                                                                                     | SYMBOL          | MIN   | ТҮР   | MAX   | UNIT |

|------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------|-------|-------|------|

| Input High Voltage (Normal Operating Levels)                                                                                       | ⊻ін             | + 2.0 | 1.5   | Vcc   | v    |

| Input Low Voltage (Normal Operating Levels)                                                                                        | VIL             | -0.3  | 1.2   | +0.8  | v    |

| Input Leakage Current<br>Vin <u>= 0 to 5.0 V</u><br>WRITE, RES, CS, RS2-RS0                                                        | JIN             | 0     | ± 1.0 | ± 2.5 | μA   |

| Three-State (Off State) Input Current<br>(V <sub>in</sub> = 0.4 to 2.4 V V <sub>CC</sub> = max)<br>D0-D7, PA0-P7, PB0-PB7, PC0-PC7 | ITSI            | 0     | ± 2.0 | ± 10  | Αų   |

| Output High Voltage<br>(V <sub>CC</sub> = min, Load = 200 µA)                                                                      | ∨он             | 2.4   | 3.5   | VCC   | v    |

| Output Low Voltage<br>(V <sub>CC</sub> = min, Load = 3.2 mA)                                                                       | VOL             | VSS   | 0.2   | 0.4   | V    |

| Output High Current (Sourcing)<br>(VOH = 2.4 V)                                                                                    | юн              | -200  | -1000 | -     | Aц   |

| Output Low Current (Sinking)<br>(V <sub>OL</sub> = 0.4 V)                                                                          | IOL             | 3.2   | _     | _     | mA   |

| Supply Current                                                                                                                     | lcc             | _     | 50    | 100   | mA   |

| Input Capacitance<br>(Vin 0V, TA = 25°C, f = 1.0 MHz)<br><u>D0-D7, PA0-</u> PA7, PB0-PB7, PC0-PC7<br>WRITE, RES, RS2-RS0, CS       | C <sub>in</sub> | _     | 7     | 10    | ρF   |

| Output Capacitance<br>( $V_{in} = 0V, T_A = 25^{\circ}C, f = 1.0 \text{ MHz}$ )                                                    | Cout            | _     | 7     | 10    | pF   |

# CHARACTERISTICS (V<sub>CC</sub> = 5.0 V $\pm$ 5%, V<sub>SS</sub> = 0V, T<sub>A</sub> = 0° to 70°C)

Note: Negative sign indicates outward current flow, positive indicates inward flow.

<u>ต</u>ยุ ส. 21, ย**ณ** 1.5

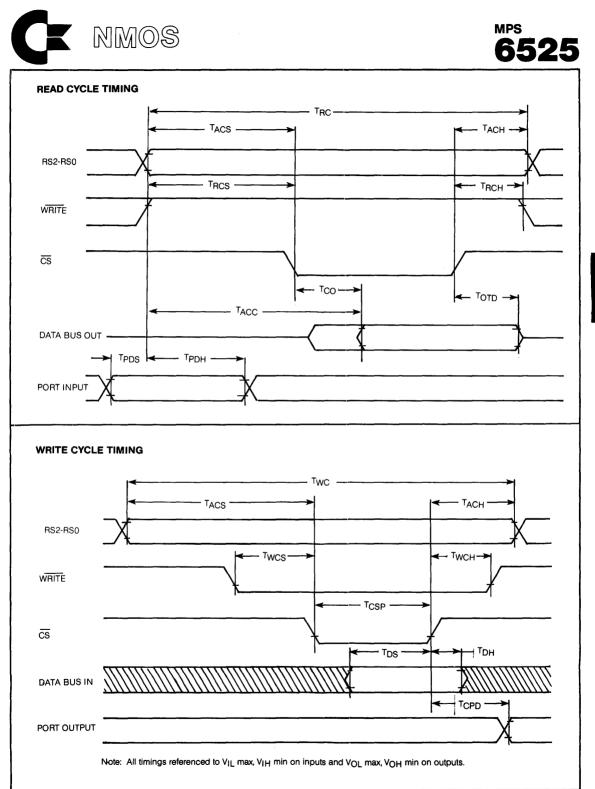

# READ CYCLE TIMING

|        |                                  |     | 25  | 65  | 25A | 652 | 25B |       |

|--------|----------------------------------|-----|-----|-----|-----|-----|-----|-------|

| Symbol | Characteristic                   | MIN | MAX | MIN | MAX | MIN | MAX | UNITS |

| TRC    | Read Cycle                       | 450 |     | 225 | -   | 165 | _   | ns    |

| TACC   | Access Time <sup>1</sup>         | -   | 450 | —   | 225 | _   | 155 | ns    |

| тсо    | CS to Output Valid               | —   | 270 |     | 120 | -   | 70  | ns    |

| TACS   | ACS RS to CS Set Up              |     | -   | 0   | —   | o   | -   | ns    |

| ТАСН   | RS to CS Hold                    | 0   | _   | 0   |     | 0   | -   | ns    |

| TRCS   | R/W high to CS Set Up            | 0   | —   | о   | -   | 0   | -   | ns    |

| TRCH   | R/W high to $\overline{CS}$ Hold | 0   | —   | 0   | —   | 0   | —   | ns    |

| TOTD   | OTD CS to Output off Delay       |     | 120 | 20  | 120 | 20  | 100 | ns    |

| TPDS   | DS Port Input Set Up             |     | -   | 60  | —   | 40  | _   | ns    |

| TPDH   | Port Input Hold                  | 150 | -   | 150 | —   | 150 | _   | ns    |

NOTE 1 - Access time measured from later of R/W high or RS stable.

## WRITE CYCLE TIMING

|        |                       | 65  | 25   | 652 | 25A | 652 |     |       |

|--------|-----------------------|-----|------|-----|-----|-----|-----|-------|

| Symbol | Characteristic        | MIN | MAX  | MIN | MAX | MIN | MAX | UNITS |

| TWC    | Write Cycle           | 450 | -    | 225 |     | 165 | _   | ns    |

| TACS   | RS to CS Set Up       | 0   |      | 0   | —   | 0   | -   | ns    |

| ТАСН   | RS to CS Hold         | 0   | -    | 0   | -   | 0   | —   | ns    |

| TWCS   | R/W low to CS Set Up  | 0   | —    | 0   | —   | 0   | -   | ns    |

| тусн   | R/W low to CS Hold    | О   | —    | 0   | —   | О   | —   | ns    |

| TDS    | Data Bus to CS Set Up | 150 |      | 100 | —   | 50  | —   | ns    |

| TDH    | Data Bus to CS Hold   | 0   | —    | 0   | —   | 0   | —   | ns    |

| TCPD   | CS to Port Out Delay  | —   | 1000 | —   | 500 |     | 330 | ns    |

| TCSP   | CS Pulse Width        | 420 | _    | 200 | -   | 150 | _   | ns    |

#### 6525 INTERNAL REGISTERS

|     | ADDR | ESS |    |                 |                 | RE              | GISTE           | R BITS          |                 |                 |                 | REGISTER NAME                       | COMMENT                                  |  |  |  |

|-----|------|-----|----|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-------------------------------------|------------------------------------------|--|--|--|

| RS2 | RS1  | RSO | мс | D7              | D6              | D5              | D4              | D3              | D2              | D1              | DO              |                                     |                                          |  |  |  |

| 0   | 0    | 0   | х  | PA <sub>7</sub> | PA <sub>6</sub> | PA <sub>5</sub> | PA4             | PA <sub>3</sub> | PA <sub>2</sub> | PA <sub>1</sub> | PA <sub>0</sub> | Port Register A (PRA)               |                                          |  |  |  |

| 0   | 0    | 1   | х  | PB7             | PB <sub>6</sub> | PB5             | PB <sub>4</sub> | PB <sub>3</sub> | PB <sub>2</sub> | PB <sub>1</sub> | PB <sub>0</sub> | Port Register B (PRB)               |                                          |  |  |  |

| 0   | 1    | 0   | 0  | PC7             | PC <sub>6</sub> | PC5             | PC4             | PC <sub>3</sub> | PC <sub>2</sub> | PC <sub>1</sub> | PC <sub>0</sub> | Port Register C (PRC)               |                                          |  |  |  |

| 0   | 1    | 0   | 1  | CB              | CA              | IRQ             | IL4             | IL3             | IL2             | IL <sub>1</sub> | IL0             | Port Register C (PRC)               | Handshake and Interrupt Latches (MODE 1) |  |  |  |

| 0   | 1    | 1   | x  | DA7             | DA <sub>6</sub> | DA5             | DA4             | DA3             | DA <sub>2</sub> | DA <sub>1</sub> | DA <sub>0</sub> | Data Direction<br>Register A (DDRA) | 0=Input; 1=Output                        |  |  |  |

| 1   | 0    | 0   | x  | DB7             | DB6             | DB5             | DB4             | DB3             | DB2             | DB1             | DB0             | Data Direction<br>Register B (DDRB) | 0=Input; 1=Output                        |  |  |  |

| 1   | 0    | 1   | 0  | DC7             | DC <sub>6</sub> | DC5             | DC4             | DC3             | DC2             | DC1             | DC <sub>0</sub> | Data Direction<br>Register C (DDRC) | 0=Input: 1=Output (MODE 0)               |  |  |  |

| 1   | 0    | 1   | 1  | -               | _               |                 | Μ4              | M <sub>3</sub>  | $M_2$           | M <sub>1</sub>  | MO              | Interrupt Mask Register             | 0=Mask: 1=Enable (MODE 1)                |  |  |  |

| 1   | 1    | 0   | Х  | CB1             | CB0             | CA <sub>1</sub> | CAO             | IE4             | IE3             | IP              | мč              | Control Register (CR)               | Mode Selected by MC                      |  |  |  |

| 1   | 1    | 1   | 1  | —               |                 | _               | AI4             | Al3             | AI <sub>2</sub> | AI <sub>1</sub> | AI0             | Active Interrupt Register (AIR)     |                                          |  |  |  |

#### 6525 FUNCTIONAL DESCRIPTION

#### Control Register (CR)

The bits of the control register select the various operating modes of the 6525. Although the exact function of each bit is explained throughout the functional description, the functions are summarized here for convenience.

| CONTROL REGISTER BIT   | 7                    | 6   | 5   | 4   | 3   | 2   | 1  | 0  |  |  |

|------------------------|----------------------|-----|-----|-----|-----|-----|----|----|--|--|

| FUNCTIONAL DESIGNATION | СВ1                  | СВО | CA1 | CA0 | IE4 | IE3 | IP | МС |  |  |

| CB Line Control        | L                    |     | L   |     |     |     |    |    |  |  |

| CA Line Control        |                      |     |     | J · |     |     |    |    |  |  |

| 14 Active Edge Select  |                      |     |     |     |     |     |    |    |  |  |

| 13 Active Edge Select  | 3 Active Edge Select |     |     |     |     |     |    |    |  |  |

| Interrupt Priority     |                      |     |     |     |     |     |    |    |  |  |

| Mode Control           |                      |     |     |     |     |     |    |    |  |  |

#### MODE 0 - (MC=0)

In Mode 0, three 8 bit bi-directional ports (A, B, C) are available on the 6525. Each port has two associated read/ write registers:

#### Data Direction Registers (DDRA, DDRB, DDRC)

Each bit of the data direction registers controls the corresponding pin of the associated port as follows:

| DDR bit | Direction of port pin                                            |

|---------|------------------------------------------------------------------|

| 0<br>1  | Input (Output driver disabled)<br>Output (Output driver enabled) |

#### Port Registers (PRA, PRB, PRC)

Reading the Port Register returns the logic states of the associated port pins. The pin voltage levels must meet the V<sub>I</sub>H and V<sub>I</sub>L specification limits to ensure valid data. (Excessive loading of the output driver may cause the data read to differ from the expected output.) If the port pin is programmed as an output by the DDR, the output driver is set to the last data written to the corresponding PR bit.

#### MODE 1 - (MC=1)

In Mode 1, the 6525 provides 2 8-bit bi-directional ports (A and B) as in Mode 0. By writing MC=1, Port C is automatically converted to a 5 level priority interrupt controller with interrupt output (IRO) and a handshake control line for each port (CA and CB).

| MOD | E 0 PIN NAMES | PC7 | PC6 | PC5 | PC4 | PC3 | PC2 | PC1 | PC0 |

|-----|---------------|-----|-----|-----|-----|-----|-----|-----|-----|

| MOD | E 1 PIN NAMES | СВ  | CA  | ĪRQ | 14  | 13  | 12  | 11  | 10  |

#### Port Register C - PRC (Mode 1)

All bits of the PRC can be read as in Mode 0 but the state of the interrupt latches, rather than the interrupt pins, is returned in the five low order bits of PRC. Writing "0" to a PRC bit clears the corresponding interrupt latch but has no effect on the CA, CB, or IRQ outputs. Writing "1" to a PRC bit has no effect on Mode 1.

| ĺ | MODE 0 BIT NAMES | PC7 | PC6 | PC5 | PC4 | PC3 | PC <sub>2</sub> | PC1 | PC <sub>0</sub> |

|---|------------------|-----|-----|-----|-----|-----|-----------------|-----|-----------------|

|   | MODE 1 BIT NAMES | CB  | CA  | TRQ | IL4 | IL3 | IL <sub>2</sub> | IL1 | IL <sub>0</sub> |

#### CA and CB Outputs --- (PC6 and PC7)

CA and CB may be used as general purpose outputs or as data transfer signals for ports A and B. The operation of CA and CB is selected as follows:

| CA1 | CA0 |                                                                     | СВ1 | сво | CB OUTPUT MODE                                                       |

|-----|-----|---------------------------------------------------------------------|-----|-----|----------------------------------------------------------------------|

| 0   | 0   | Set high by active<br>transition of I3. Reset low<br>by reading PRA |     |     | Set low by writing PRB.<br>Reset high by active<br>transition of I4. |

| 0   | 1   | Pulses low for at least 500<br>ns after reading PRA.                | 0   | 1   | Pulses low for at least 500<br>ns after writing PRB.                 |

|     | 0   | CA low<br>CA high                                                   | 1   | 0   | CB low<br>CB high                                                    |

#### IRQ Output - (PC5)

The Interrupt Request is set low when an unmasked interrupt (see below) is activated. IRQ is reset high by reading the Active Interrupt Register (AIR). The IRQ output has an open drain to allow wire AND tying of multiple outputs.

#### 14, 13, 12, 11, 10 Inputs - (PC4-PC0)

The five low order pins of Port C are interrupt inputs in Mode 1. A negative (high to low) transition on 12, 11 or 10 sets the corresponding latch in PRC to indicate an interrupt, while either transition of I3 or I4 can be selected to set its latch as follows:

| IE3 | 13 EDGE SELECTION                                                                                                                      | IE4 | 14 EDGE SELECTION                                                                      |

|-----|----------------------------------------------------------------------------------------------------------------------------------------|-----|----------------------------------------------------------------------------------------|

| 1   | I3 sets IL <sub>3</sub> latch on negative<br>(hi-low) transition.<br>I3 sets IL <sub>3</sub> latch as positive<br>(low-hi) transition. | 1   | I4 sets IL4 latch on negative transition.<br>I4 sets IL4 latch on positive transition. |

#### Interrupt Mask Register (DDRC in Mode 1)

In Mode 1, the five low order bits of the DDRC are utilized as interrupt mask bits of the five corresponding interrupt latches. Writing a "1" to the mask register enables the corresponding interrupt latch to initiate an interrupt while a "0" masks the interrupt latch output. Masking does not prevent the interrupt latch from being set by an active input transition. The interrupt mask register can be read and written.

#### **Active Interrupt Register (AIR)**

The five low order bits of the AIR contain the present interrupt status of the 6525. A "1" in a bit of the AIR indicates that the corresponding interrupt is active. Reading the AIR clears all AIR bits and resets any interrupt latch which had set a bit in the AIR. READING AND WRITING OF THE AIR AFFECTS THE INTERRUPT PRIORITY STACK. Therefore, the AIR should be accessed only in strict accordance to the following rules:

- 1. READ THE AIR ONLY TO INDICATE BEGINNING OF INTERRUPT SERVICE.

- 2. WRITE THE AIR ONLY TO INDICATE CONCLUSION OF INTERRUPT SERVICE.

#### DESCRIPTION OF PRIORITY INTERRUPT OPERATION

#### No Priority Operation Selected - (IP=0)

When an active transition occurs on an interrupt input (see I4-I0), the corresponding interrupt latch is set. If this latch is not masked, the corresponding bit of the AIR is set, IRQ (PC5) is activated low, and other interrupt latches are prevented from setting new bits in the AIR. After reading the AIR, is cleared to await new input and IRQ is reset high. Any interrupt latches remaining set will now restart this interrupt sequence. If multiple interrupts have been received in the interim, multiple bits will be set in the AIR and all corresponding interrupt latches will be cleared when the AIR is read. Therefore, software must recognize the occurrence of multiple interrupts when no priority operation is selected.

#### Priority Operation Selected - (IP=1)

The five interrupt inputs have a fixed priority: I4 > I3 > I2 > I1 > I0. When priority operation is selected, only the highest priority interrupt is placed in the AIR, ensuring only one bit set in the AIR at any time. When an interrupt occurs, the corresponding interrupt latch is set as before but is then compared with the present active interrupt, the new bit in the AIR is set and IRQ is activated low. When AIR is read, the contents of the AIR are pushed onto a 5 level stack for comparison with subsequent interrupts and AIR is cleared.

After servicing the new interrupt, the processor must write to the AIR (clearing the AIR) to instruct the 6525 that this interrupt service is complete. The previous interrupt status is then recalled (popped) to the top of the stack to be used for evaluating new interrupt inputs. Interrupts of lesser priority than the active interrupt are masked until all higher level interrupts are acknowledged and completed by the processor (as indicated by AIR reads and writes). When all higher priority interrupts have been serviced, the 6525 will allow a lower priority interrupt to indicate a new interrupt sequence.

The following examples illustrate the priority interrupt operation:

- A. Single Interrupt

- 1. Interrupt received by negative transition on I1.

- 2. Interrupt latch 1 (IL1) is set.

- 3. Bit A1 set in AIR.

- 4. IRO activated low.

- 5. Processor responds by reading AIR to determine which interrupt occurred.

- 6. AIR is pushed onto interrupt stack and latch 1 is cleared.

- 7. AIR is cleared and IRQ reset high.

- 8. Upon completion of service, processor writes to AIR.

- Interrupt stack is popped, restoring previous interrupt status.

- B. Lower priority interrupt received during active interrupt

1. I1 received and latched.

- 2. A<sub>1</sub> is set and IRQ activated low.

- 3. Processor reads AIR to determine 11 is active.

- 4. AIR pushed onto stack and IL1 cleared.

- 5. AIR cleared and IRQ reset high.

- 6. Processor is servicing I1 while I0 occurs and sets IL0.

- 7. Interrupt stack prevents lower priority IL<sub>0</sub> from initiating a new interrupt.

- 8. Upon completion of 11 service, processor writes to AIR, popping 11 interrupt out of stack.

- 9. ILO is now permitted to initiate a new interrupt service.

- C. Higher priority interrupt received during active interrupt

- 1. Interrupt I1 received and latched.

- 2. A1 is set and IRQ activated low.

- 3. Processor reads AIR to determine I1 is active.

- 4. AIR is pushed onto stack and IL1 cleared.

- 5. AIR cleared and IRQ reset high.

- 6. Processor is servicing I1 when I2 occurs and sets IL2.

- 7. A2 is set and IRQ activated low because IL2 has higher priority than 11 in stack.

- 8. Processor recognizes interrupt request and calls interrupt service routine.

- 9. Processor reads AIR to determine I2 is active.

- 10. New AIR is pushed onto interrupt stack and IL<sub>2</sub> cleared.

- 11. AIR cleared and IRQ reset high.

- 12. Processor services I2.

- Upon completion of I2 service, processor writes to AIR popping I2 interrupt from stack, restoring I1 status to top of stack (still preventing an I0 interrupt).

- 14. Processor return from interrupt resumes services of suspended 11 routine.

- Upon completion of I1, processor writes to AIR, popping I1 interrupt from stack, leaving no active interrupts.

#### 6525 INTERFACE AND CONTROL

#### Initialization

A low on the RES pin clears all 6525 internal registers. This puts the 6525 in Mode 0 with all three ports selected as inputs (floating), preventing any conflicts on the bi-directional port lines. For port pins to be used as outputs, the desired output data may be written to the port register before enabling the output driver. This sequence can eliminate undesired output conditions when the outputs are enabled via the DDR.

When selecting Mode 1, all interrupt inputs and IE3, IE4 must be stable before writing MC bit to "1." If this can not be ensured, the interrupt latches (PRC4-PRC0) should be cleared by writing 0 to PRC after MC=1 and before unmasking the interrupt latches. Similarly, if CA and CB are to be used as data transfer handshake lines, no PRA reads or PRB writes should occur after RES or before actual data transfers are to begin.

#### **Processor Interface**

The 6525 is a fully static device with interface characteristics similar to a static RAM. To read, the RS and R/W lines are stabilized and then  $\overline{CS}$  is switched low, gating the desired register onto the system data bus. (In 650X systems,  $\overline{CS}$  may be gated with d2). The system timing must accommodate both the TACC (address) and T<sub>CO</sub> (chip select) delays before requiring valid data. To write to the 6525, similar timing is required, with the processor providing valid write data at least DS before  $\overline{CS}$  switches high. To guarantee proper operation of the 6525, THE R/W LINE MUST BE STABLE ANY TIME  $\overline{CS}$  IS LOW.

COMMODORE SEMICONDUCTOR GROUP reserves the right to make changes to any products herein to improve reliability, function or design. COMMODORE SEMICONDUCTOR GROUP does not assume any liability arising ot of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others.