# 6523 TRI-PORT INTERFACE

# CONCEPT ...

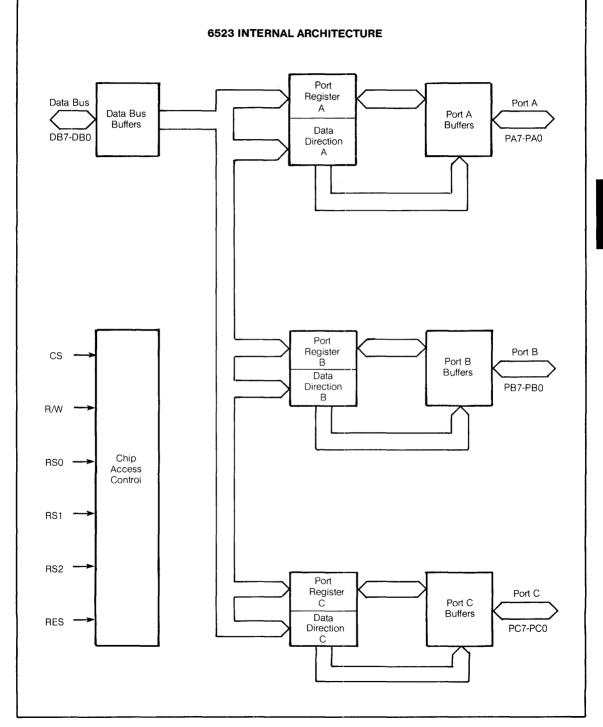

The 6523 TRI-PORT Interface (TPI) is designed to simplify the implementation of complex I/O operations in microcomputer systems. It has three dedicated 8-bit I/O ports which provide 24 individually programmable I/O lines.

# FEATURES:

- 24 individually programmable I/O lines

- Completely static operation

- Two TTL Drive Capability

- 6 directly addressable registers

- 1 MHz, 2MHz and 3MHz operation

| 0523 REGISTERS                    |   |         |                                  |  |  |  |

|-----------------------------------|---|---------|----------------------------------|--|--|--|

| *000                              |   | R0      | PRA — Port Register A            |  |  |  |

| 001                               |   | R1      | PRB — Port Register B            |  |  |  |

| 010                               |   | R2      | PRC — Port Register C            |  |  |  |

| 011                               |   | R3      | DDRA - Data Direction Register A |  |  |  |

| 100                               |   | R4      | DDRB — Data Direction Register B |  |  |  |

| 101                               |   | R5      | DDRC — Data Direction Register   |  |  |  |

| 110                               | ł | Illegal | States                           |  |  |  |

| 111                               | Ş | Illegal | States                           |  |  |  |

| *NOTE: RS2, RS1, RS0 respectively |   |         |                                  |  |  |  |

READ DECIOTEDO

# **6523 PIN CONFIGURATION**

| VSS | 1  | 40 | DB7 |

|-----|----|----|-----|

| PAO | 2  | 39 | DB6 |

| PA1 | 3  | 38 | DB5 |

| PA2 | 4  | 37 | D84 |

| PA3 | 5  | 36 | DB3 |

| PA4 | 6  | 35 | DB2 |

| PA5 | 7  | 34 | DB1 |

| PA6 | 8  | 33 | DB0 |

| PA7 | 9  | 32 | PC7 |

| PB0 | 10 | 31 | PC6 |

| P81 | 11 | 30 | PC5 |

| PB2 | 12 | 29 | PC4 |

| PB3 | 13 | 28 | PC3 |

| PB4 | 14 | 27 | PC2 |

| PB5 | 15 | 26 | PC1 |

| PB6 | 16 | 25 | PC0 |

| PB7 | 17 | 24 | RS0 |

| ĊS  | 18 | 23 | RS1 |

| R/W | 19 | 22 | RS2 |

| VDD | 20 | 21 | RES |

|     |    |    | 1   |

# MAXIMUM RATINGS

Supply Voltage, V<sub>CC</sub> Input/Output Voltage, V<sub>IN</sub> Operating Temperature, T<sub>OP</sub> Storage Temperature, T<sub>STG</sub> -0.3V to +7.0V -0.3V to +7.0V 0°C to 70°C -55°C to 150°C

All inputs contain protection circuitry to prevent damage due to high static discharges. Care should be exercised to prevent unnecessary application of voltages in excess of the allowable limits.

## COMMENT

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only. Functional operation of this device at these or any other conditions above those indicated in the operational sections of this specification is not implied and exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# CHARACTERISTICS (V<sub>CC</sub> = 5.0 V $\pm$ 5%, V<sub>SS</sub> = 0V, T<sub>A</sub> = 0° to 70°C)

| CHARACTERISTIC                                                                                                               | SYMBOL           | MIN   | ТҮР   | МАХ   | UNIT |

|------------------------------------------------------------------------------------------------------------------------------|------------------|-------|-------|-------|------|

| Input High Voltage (Normal Operating Levels)                                                                                 | ViH              | + 2.0 |       | Vcc   | V    |

| Input Low Voltage (Normal Operating Levels)                                                                                  | VIL              | -0.3  |       | +0.8  | v    |

| Input Leakage Current<br>Vin = 0 to <u>5.0 V</u><br>WRITE, RES, CS, RS2-RS0                                                  | ΊΝ               | 0     | ± 1.0 | ± 2.5 | μA   |

| Three-State (Off State) Input Current<br>(Vin = 0.4 to 2.4 V V <sub>CC</sub> = max)<br>D0-D7, PA0-P7, PB0-PB7, PC0-PC7       | ITSI /           | 0     | ± 2.0 | ± 10  | Aц   |

| Output High Voltage<br>(V <sub>CC</sub> = min, Load = 200 µA)                                                                | ∨он              | 2.4   | 3.5   | Vcc   | v    |

| Output Low Voltage<br>(V <sub>CC</sub> = min, Load = 3.2 mA)                                                                 | VOL              | VSS   | 0.2   | 0.4   | V    |

| Output High Current (Sourcing)<br>(V <sub>OH</sub> = 2.4 V)                                                                  | <sup>і</sup> он  | -200  | -1000 | _     | Aц   |

| Output Low Current (Sinking)<br>(V <sub>OL</sub> = 0.4 V)                                                                    | IOL              | 3.2   | -     | -     | mA   |

| Supply Current                                                                                                               | lcc              | _     | 50    | 100   | mA   |

| Input Capacitance<br>(Vin 0V, TA = 25°C, f = 1.0 MHz)<br><u>D0-D7, PA0-</u> PA7, PB0-PB7, PC0-PC7<br>WRITE, RES, RS2-RS0, CS | C <sub>in</sub>  | _     | 7     | 10    | pF   |

| Output Capacitance $(V_{in} = 0V, T_A = 25^{\circ}C, f = 1.0 \text{ MHz})$                                                   | C <sub>out</sub> | _     | 7     | 10    | pF   |

Note: Negative sign indicates outward current flow, positive indicates inward flow.

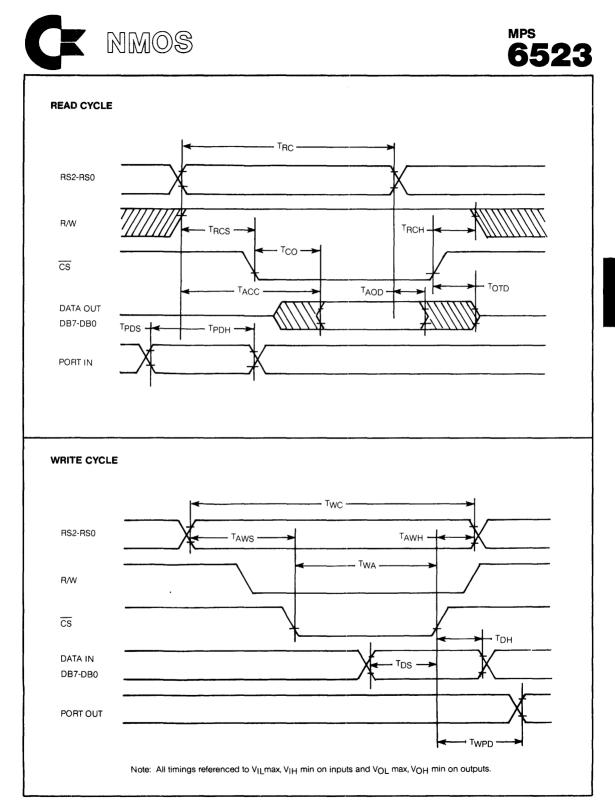

# READ CYCLE TIMING

|                 |                                  | 6523 |     | 6523A |     | 6523B |     |       |

|-----------------|----------------------------------|------|-----|-------|-----|-------|-----|-------|

| SYMBOL          | SYMBOL CHARACTERISTIC            |      | MAX | MIN   | MAX | MIN   | MAX | UNITS |

| T <sub>RC</sub> | Read Cycle                       | 450  |     | 225   | _   | 165   | —   | ns    |

| TACC            | Access Time <sup>1</sup>         | _    | 450 | -     | 225 | —     | 165 | ns    |

| TCO             | CS to Output Valid               |      | 270 |       | 120 | _     | 70  | ns    |

| TRCS            | TRCS R/W high to CS Setup        |      | _   | 0     | —   | 0     | _   | ns    |

| TRCH            | R/W high to $\overline{CS}$ Hold | 0    |     | 0     | _   | 0     | _   | ns    |

| тотр            | CS to Output Off Delay           | 20   | 120 | 20    | 120 | 20    | 120 | ns    |

| TAOD            | Address to Output Delay          | 50   | _   | 50    |     | 50    | -   | ns    |

| TPDS            | Port Input Setup                 | 120  |     | 60    | _   | 40    |     | ns    |

| TPDH            | Port Input Hold                  | 150  | _   | 150   | —   | 150   | _   | ns    |

Note 1: Access Time measured from later of WRITE high or RS stable.

# WRITE CYCLE TIMING

|                               |                                    | 6523 |      | 6523A |     | 6523B |     |       |

|-------------------------------|------------------------------------|------|------|-------|-----|-------|-----|-------|

| SYMBOL                        | CHARACTERISTIC                     | MIN  | MAX  | MIN   | MAX | MIN   | MAX | UNITS |

| TWC                           | Write Cycle                        | 450  |      | 225   |     | 165   |     | ns    |

| TWA                           | TWA Write Active Time <sup>2</sup> |      | _    | 200   | _   | 150   | _   | ns    |

| TAWS Address to R/W low Setup |                                    | 0    | -    | 0     | -   | 0     | _   | ns    |

| TAWH                          | TAWH Address to R/W low Hold       |      | -    | 0     | —   | 0     |     | ns    |

| TDS                           | Data bus in Setup                  | 150  |      | 100   | -   | 50    |     | ns    |

| тон                           | Data bus in Hold                   | 0    | _    | 0     | _   | 0     | _   | ns    |

| TWPD                          | Write active to Port out Delay     | —    | 1000 | _     | 500 | _     | 330 | ns    |

Note 2:  $T_{WA}$  is the time while both  $\overline{CS}$  and R/W are low.

## 6523 FUNCTIONAL DESCRIPTION

Three 8 bit bi-directional ports (A, B, C) are available on the 6523. Each port has two associated read/write registers:

### Data Direction Registers (DDRA, DDRB, DDRC)

Each bit of the data direction registers controls the corresponding pin of the associated port as follows:

| DDR bit | Direction of port pin          |  |  |  |  |

|---------|--------------------------------|--|--|--|--|

| 0       | Input (Output driver disabled) |  |  |  |  |

| 1       | Output (Output driver enabled) |  |  |  |  |

#### Port Registers (PRA, PRB, PRC)

Reading the Port Register returns the logic states of the associated port pins. The pin voltage levels must meet the  $V_{IH}$  and  $V_{IL}$  specification limits to ensure valid data. (Excessive loading of the output driver may cause the data read to differ from the expected output.) If the port pin is programmed as an output by the DDR, the output driver is set to the last data written to the corresponding PR bit.

## 6523 INTERFACE SIGNALS

## CS - Chip Select Input

The  $\overrightarrow{CS}$  input controls the activity of the 6523. A low level on  $\overrightarrow{CS}$  causes the device to respond to signals on the R/W and address (RS) lines. A high on  $\overrightarrow{CS}$  prevents these lines from controlling the 6523. The  $\overrightarrow{CS}$  line is normally activated (low) by the appropriate address combination from the processor.

#### R/W - Read/Write Input

The R/W signal is normally supplied by the microprocessor and controls the direction of data transfers of the 6523. A high on R/W indicates a read (data transfer out of the 6523), while a low indicates a write (data transfer into the 6523).

#### RS2-RS0 - Address Inputs

The address inputs select the internal registers (in conjunction with  $\overline{CS}$  and R/W) as indicated by the register table.

#### DB7-DB0 - Data Bus Inputs/Outputs

The eight data bus pins transfer information between the 6523 and the system data bus. These pins are high impedance inputs unless CS is low and R/W is high, to read the device. During this read, the data bus output buffers are enabled, driving the data from the selected register onto the system data bus.

### RES - Reset Input

A low on the RES pin clears internal registers. This sets all three ports as inputs (floating), preventing any conflicts on the bidirectional port lines. For port pins to be used as outputs, the desired output data may be written to the port register before enabling the output driver. This sequence can eliminate undesired output conditions when the outputs are enabled via the DDR.

COMMODORE SEMICONDUCTOR GROUP reserves the right to make changes to any products herein to improve reliability, function or design. COMMODORE SEMICONDUCTOR GROUP does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others.