# mps<sub>.</sub>

## MPSafe<sup>™</sup> QM, 5.5V, PMIC with 6 Buck Converters, AEC-Q100 Qualified

## DESCRIPTION

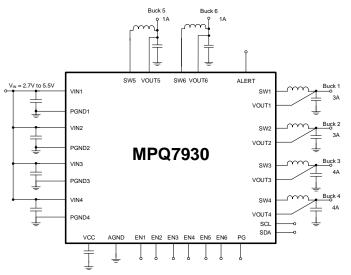

The MPQ7930 device is a power management IC (PMIC) designed meet the power management requirements of processors used in various safety-relevant automotive systems.

Six integrated synchronous buck converters can be configured as 3 dual-phase or 6 singlephase converters. With dynamic voltage scaling, the output voltage of each converter can be changed during normal operation. The PMBus interface provides packet error checking (PEC) and integrated multi-page one-time programmable (MOTP) memory for a high degree of configurability.

Six enable pins allow each regulator to be sequenced independently for flexible timing control. This allows the device to meet a wide variety of sequencing requirements.

To prevent overshoot during start-up, soft-start functionality is featured on each converter, and the slew rate can be configured via the MOTP.

2MHz, fixed-frequency pulse-width modulation (PWM) control regulates the output voltage ( $V_{OUT}$ ), offers fast transient performance, and allows for a large reduction in external inductor and capacitor values. In addition, frequency spread spectrum (FSS) reduces EMI noise.

Full protection features include under-voltage lockout (UVLO), over-current protection (OCP), under-voltage protection (UVP), over-voltage protection (OVP), and thermal shutdown.

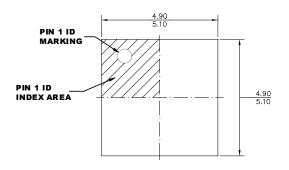

The MPQ7930 is available in a TQFN-32 (5mmx5mm) package, and is AEC-Q100 qualified.

## FEATURES

- Designed for Automotive Applications:

- $\circ$  ~ 2.7V to 5.5V Input Voltage (V\_{IN}) Range

- -40°C to +150°C Junction Temperature Rating

- Reduced Board Size and BOM:

- Six Synchronous Buck Converters (Independent or Multi-Phase Operation): Two 4A, Two 3A, and Two 1A

- Integrated and Adjustable Compensation Network for each Buck Converter

- o Dynamic Voltage Scaling

- PMBus Interface with Packet Error Checking (PEC)

- Optimized for EMC/EMI:

- 180° Phase Shift between Bucks 1, 3, and 6, then Bucks 2, 4, and 5

- 2MHz Switching Frequency (f<sub>SW</sub>)

- Frequency Spread Spectrum (FSS)

- Additional Features:

- Multi-Page One-Time Programmable (MOTP) Memory

- Configurable Sequencing

- Power Good Output

- ALERT Indicator

- Over-Current Protection (OCP), Over-Voltage Protection (OVP), and Under-Voltage Protection (UVP) with Hiccup

- Available in a TQFN-32 (5mmx5mm)

Package with Wettable Flank

- Available in AEC-Q100 Grade 1

## APPLICATIONS

- Advanced Driver Assistance Systems (ADAS)

- Surround View System Electronic Control Units (ECUs)

- ADAS Domain Controllers

- Drive Assist ECUs

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance. "MPS", the MPS logo, and "Simple, Easy Solutions" are trademarks of Monolithic Power Systems, Inc. or its subsidiaries.

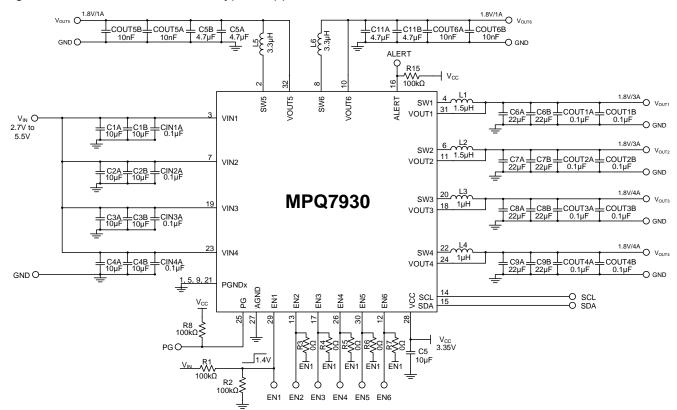

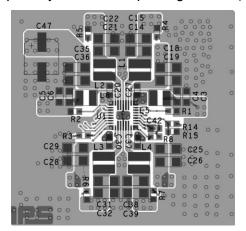

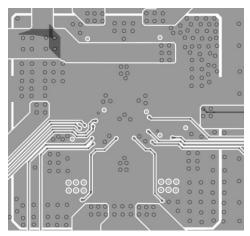

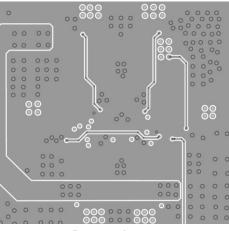

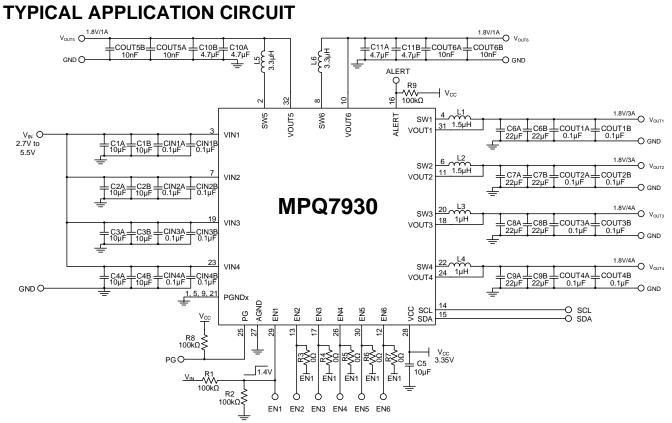

## TYPICAL APPLICATION

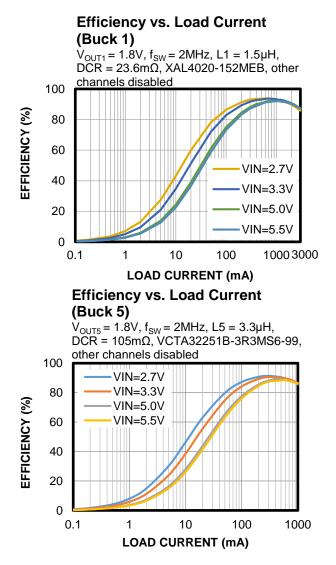

## Efficiency vs. Load Current (Buck 3)

### **ORDERING INFORMATION**

| Part Number*            | Package           | Top Marking | MSL Rating*** |

|-------------------------|-------------------|-------------|---------------|

| MPQ7930GUTE-xxxx-AEC1** | TQFN-32 (5mmx5mm) | See Below   | 1             |

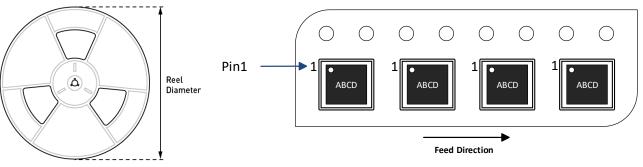

\* For Tape & Reel, add suffix -Z (e.g. MPQ7930GUTE-xxxx-AEC1-Z).

\*\* "xxxx" is the configuration code identifier for the register settings stored in the OTP register. The first value must be a numerical value (0–9), while the last three values can be a hexadecimal value between 0 and F. The default code is "0000". Contact an MPS FAE to create this unique number.

\*\*\* Moisture Sensitivity Level Rating

| TOP MARKING |

|-------------|

| MPSYYWW     |

| MP7930      |

| LLLLLL      |

| E           |

MPS: MPS prefix YY: Year code WW: Week code MP7930: Part number LLLLLLL: Lot number E: Wettable flank

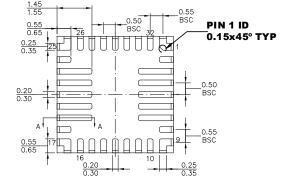

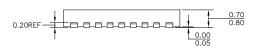

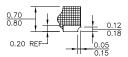

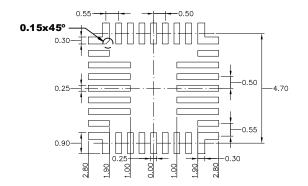

### **PACKAGE REFERENCE**

|       |   |         |       | то  | P VIE | EW  |           |       |    |       |

|-------|---|---------|-------|-----|-------|-----|-----------|-------|----|-------|

|       |   | VOUT5 \ | VOUT1 | EN5 | EN1   | VCC | AGND      | EN4   |    |       |

| PGND1 | 1 | 32      | 31    | 30  | 29    | 28  | 27        | 26    | 25 | PG    |

| SW5   | 2 |         |       |     |       |     |           |       | 24 | VOUT4 |

| VIN1  | 3 |         | )     |     |       |     | (         |       | 23 | VIN4  |

| SW1   | 4 |         | )     |     |       |     | (         |       | 22 | SW4   |

| PGND2 | 5 |         | )     |     |       |     | $\square$ |       | 21 | PGND4 |

| SW2   | 6 |         |       |     |       |     | (         |       | 20 | SW3   |

| VIN2  | 7 |         |       |     |       |     | (         |       | 19 | VIN3  |

| SW6   | 8 |         |       |     |       |     |           |       | 18 | VOUT3 |

| PGND3 | 9 | 10      | 11    | 12  | 13    | 14  | 15        | 16    | 17 | EN3   |

|       |   | VOUT6   | VOUT2 | EN6 | EN2   | SCL | SDA       | ALERT |    |       |

|       |   | Т       | QFN   | -32 | (5m   | mx5 | mm)       | )     |    |       |

## **PIN FUNCTIONS**

| Pin #           | Name  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 5, 9,<br>21  | PGNDx | Power ground. The PGND pins are internally connected.                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2               | SW5   | <b>Switch node 5.</b> The SW5 pin is the switching node of the internal power switches for buck converter 5. Float this pin or connect a $100k\Omega$ resistor between this pin and GND if it is not used.                                                                                                                                                                                                                                                          |

| 3, 7,<br>19, 23 | VINx  | <b>Input supply voltage.</b> VIN supplies power to all the internal control circuitries and the power switches. The decoupling capacitor connected from VIN to ground must be placed close to VIN to minimize switching spikes. The VIN pins are not internally connected. It is not allowed to separate different VIN pins; connect the VIN pins using copper pours and vias.                                                                                      |

| 4               | SW1   | <b>Switch node 1.</b> The SW1 pin is the switching node of the internal power switches for buck converter 1. Float this pin or connect a $100k\Omega$ resistor between this pin and GND if it is not used.                                                                                                                                                                                                                                                          |

| 6               | SW2   | <b>Switch node 2.</b> The SW2 pin is the switching node of the internal power switches for buck converter 2. Float this pin or connect a $100k\Omega$ resistor between this pin and GND if it is not used.                                                                                                                                                                                                                                                          |

| 8               | SW6   | <b>Switch node 6.</b> The SW6 pin is the switching node of the internal power switches for buck converter 6. Float this pin or connect a $100k\Omega$ resistor between this pin and GND if it is not used.                                                                                                                                                                                                                                                          |

| 10              | VOUT6 | <b>Feedback input pin 6.</b> The VOUT6 pin is the feedback voltage input for buck converter 6. Float this pin or connect a $100k\Omega$ resistor between this pin and GND if it is not used.                                                                                                                                                                                                                                                                        |

| 11              | VOUT2 | <b>Feedback input pin 2.</b> The VOUT2 pin is the feedback voltage input for buck converter 2. Float this pin or connect a $100k\Omega$ resistor between this pin and GND if it is not used.                                                                                                                                                                                                                                                                        |

| 12              | EN6   | <b>Buck 6 enable.</b> Pull the EN6 pin below the specified threshold (1.3V) to shut down buck 6. Pull this pin up above the specified threshold (1.4V) to enable buck 6. There is an internal pull-down resistor that depends on the pin's voltage. After V <sub>CC</sub> is on, the pull-down resistor is 1.95MΩ when the pin voltage exceeds 1.4V, or it is $1.05M\Omega$ when the pin voltage is below 1.4V. Connect this pin to GND if it is not used.          |

| 13              | EN2   | <b>Buck 2 enable.</b> Pull the EN2 pin below the specified threshold (1.3V) to shut down buck 2. Pull this pin up above the specified threshold (1.4V) to enable buck 2. There is an internal pull-down resistor that depends on the pin's voltage. After $V_{CC}$ is on, the pull-down resistor is 1.95M $\Omega$ when the pin voltage exceeds 1.4V, or it is 1.05M $\Omega$ when the pin voltage is below 1.4V. Connect this pin to GND if it is not used.        |

| 14              | SCL   | <b>PMBus serial clock.</b> The SCL pin is an open-drain port, and it cannot be floated. Use an external pull-up resistor to connect this pin to the PMBus supply rail. Connect this pin to GND if it is not used.                                                                                                                                                                                                                                                   |

| 15              | SDA   | <b>PMBus serial data.</b> This pin is an open-drain port, and it cannot be floated. Use an external pull-up resistor to connect this pin to the PMBus supply rail. Connect this pin to GND if it is not used.                                                                                                                                                                                                                                                       |

| 16              | ALERT | <b>Open-drain fault output.</b> The ALERT pin asserts active low if a failure occurs. Use a resistor to pull ALERT up to a power source. Float this pin or connect this pin to GND if not used.                                                                                                                                                                                                                                                                     |

| 17              | EN3   | <b>Buck 3 enable.</b> Pull the EN3 pin below the specified threshold (1.3V) to shut down buck 3. Pull this pin up above the specified threshold (1.4V) to enable buck 3. There is an internal pull-down resistor that depends on the pin's voltage. After V <sub>cc</sub> is on, the pull-down resistor is 1.95M $\Omega$ when the pin voltage exceeds 1.4V, or it is 1.05M $\Omega$ when the pin voltage is below 1.4V. Connect this pin to GND if it is not used. |

| 18              | VOUT3 | <b>Feedback input pin 3.</b> The VOUT3 pin is the feedback voltage input for buck converter 3. Float this pin or connect a $100k\Omega$ resistor between this pin and GND if it is not used.                                                                                                                                                                                                                                                                        |

## PIN FUNCTIONS (continued)

| Pin # | Name  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 20    | SW3   | Switch node 3. The SW3 pin is the switching node of the internal power switches for buck converter 3. Float this pin or connect a $100k\Omega$ resistor between this pin and GND if it is not used.                                                                                                                                                                                                                                                              |

| 22    | SW4   | <b>Switch node 4.</b> The SW4 pin is the switching node of the internal power switches for buck converter 4. Float this pin or connect a $100k\Omega$ resistor between this pin and GND if it is not used.                                                                                                                                                                                                                                                       |

| 24    | VOUT4 | <b>Feedback input pin 4.</b> The VOUT4 pin is the feedback voltage input for buck converter 4. Float this pin or connect a $100k\Omega$ resistor between this pin and GND if it is not used.                                                                                                                                                                                                                                                                     |

| 25    | PG    | <b>Power good indicator.</b> The output of PG is an open drain of an N-channel MOSFET. PG goes high if all the output voltages are within +4.5%/-3.5% or +6.5%/-5.5% of their nominal voltages. Use a resistor to pull PG up to a power source. Float this pin or connect this pin to GND if not used.                                                                                                                                                           |

| 26    | EN4   | <b>Buck 4 enable.</b> Pull the EN4 pin below the specified threshold (1.3V) to shut down buck 4. Pull this pin up above the specified threshold (1.4V) to enable the buck 4. There is an internal pull-down resistor that depends on the pin's voltage. After $V_{CC}$ is on, the pull-down resistor is 1.95M $\Omega$ when the pin voltage exceeds 1.4V, or it is 1.05M $\Omega$ when the pin voltage is below 1.4V. Connect this pin to GND if it is not used. |

| 27    | AGND  | <b>Analog ground.</b> The AGND pin is the reference GND for the internal logic and signal circuit. AGND is not internally connected to the power ground. Ensure that AGND is connected to power ground in the PCB.                                                                                                                                                                                                                                               |

| 28    | VCC   | <b>Internal bias supply.</b> The internal, 3.35V low-dropout (LDO) regulator supplies power to the control circuit and gate drivers. Connect a $10\mu$ F capacitor from VCC to AGND with a trace that is as short as possible.                                                                                                                                                                                                                                   |

| 29    | EN1   | <b>Buck 1 enable.</b> Pull the EN1 pin below the specified threshold (1.3V) to shut down buck 1. Pull this pin up above the specified threshold (1.4V) to enable the buck 1. There is an internal pull-down resistor that depends on the pin's voltage. After $V_{CC}$ is on, the pull-down resistor is 1.95M $\Omega$ when the pin voltage exceeds 1.4V, or it is 1.05M $\Omega$ when the pin voltage is below 1.4V. Connect this pin to GND if it is not used. |

| 30    | EN5   | <b>Buck 5 enable.</b> Pull the EN5 pin below the specified threshold (1.3V) to shut down buck 5. Pull this pin up above the specified threshold (1.4V) to enable the buck 5. There is an internal pull-down resistor that depends on the pin's voltage. After $V_{CC}$ is on, the pull-down resistor is 1.95M $\Omega$ when the pin voltage exceeds 1.4V, or it is 1.05M $\Omega$ when the pin voltage is below 1.4V. Connect this pin to GND if it is not used. |

| 31    | VOUT1 | <b>Feedback input pin 1.</b> The VOUT1 pin is the feedback voltage input for buck converter 1. Float this pin or connect a $100k\Omega$ resistor between this pin and GND if it is not used.                                                                                                                                                                                                                                                                     |

| 32    | VOUT5 | <b>Feedback input pin 5.</b> The VOUT5 pin is the feedback voltage input for buck converter 5. Float this pin or connect a $100k\Omega$ resistor between this pin and GND if it is not used.                                                                                                                                                                                                                                                                     |

### ABSOLUTE MAXIMUM RATINGS (1)

| VINx, SWx                       | 0.3V to +6.5V                            |

|---------------------------------|------------------------------------------|

| EN <sub>X</sub>                 | 0.3V to +5V                              |

| All other pins                  | 0.3V to +4V                              |

| Continuous power dissipation (7 | Γ <sub>A</sub> = 25°C) <sup>(2)(6)</sup> |

| QFN-32 (5mmx5mm)                | 6.16W                                    |

| Operating junction temperature  | 150°C                                    |

| Lead temperature                | 260°C                                    |

| Storage temperature             | -65°C to +150°C                          |

### ESD Ratings

Human body model (HBM) .....Class 2 <sup>(3)</sup> Charged-device model (CDM)...... Class C2b

#### **Recommended Operating Conditions**

#### **Thermal Resistance** $\theta_{JA}$ $\theta_{JC}$

TQFN-32 (5mmx5mm)

| JESD51-7       | 31.7 | .2.6 | °C/W <sup>(5)</sup>  |

|----------------|------|------|----------------------|

| EVQ7930-UT-00A | 20.3 | .0.7 | .°C/W <sup>(6)</sup> |

#### Notes:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature, T<sub>J</sub> (MAX), the junction-toambient thermal resistance,  $\theta_{JA}$ , and the ambient temperature, T<sub>A</sub>. The maximum allowable continuous power dissipation at any ambient temperature is calculated by P<sub>D</sub> (MAX) = (T<sub>J</sub> (MAX) - T<sub>A</sub>) /  $\theta_{JA}$ . Exceeding the maximum allowable power dissipation can cause excessive die temperature, and the regulator may go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- Per AEC-Q100-002.

- 4) Per AEC-Q100-011.

- 5) Measured on a JESD51-7, 4-layer PCB. The values given in this table are only valid for comparison with other packages and cannot be used for design purposes. These values were calculated in accordance with JESD51-7, and simulated on a specified JEDEC board. They do not represent the performance obtained in an actual application. The value of  $\theta_{JC}$  shows the thermal resistance from junction-to-case bottom.

- 6) Measured on an MPS standard EVB: EVQ7930-UT-00A, a 9cmx9cm, 2oz. copper, 4-layer PCB. The value of  $\theta_{JC}$  shows the thermal resistance from junction-to-case top.

## **ELECTRICAL CHARACTERISTICS**

#### $V_{IN} = 5V$ , $V_{EN} = 2V$ , $T_J = -40^{\circ}$ C to +150°C, typical values are at $T_J = 25^{\circ}$ C, unless otherwise noted.

| Parameter                                                  | Symbol          | Condition                                                | Min     | Тур  | Max  | Units |

|------------------------------------------------------------|-----------------|----------------------------------------------------------|---------|------|------|-------|

| Input Supply Voltage                                       | -               | •                                                        |         |      |      |       |

| V <sub>IN</sub> under-voltage lockout                      | Vin_uvlo        |                                                          | 2.4     |      | 2.8  | V     |

| (UVLO) rising threshold                                    |                 |                                                          | 2.4     |      | 2.0  | v     |

| V <sub>IN</sub> UVLO hysteresis                            | VIN_UVLO_HYS    |                                                          |         | 180  |      | mV    |

| V <sub>IN</sub> quiescent current                          | IQ_ON           | All bucks on, no switching                               |         |      | 20   | mA    |

| V <sub>IN</sub> shutdown current                           | $I_{Q_OFF}$     | All bucks off, all enables low                           |         |      | 150  | μA    |

| VCC Regulator                                              |                 |                                                          |         |      |      |       |

| VCC regulation voltage                                     | Vvcc            | C = 2.2µF, I <sub>OUT</sub> = 10mA                       | 3.1     | 3.35 | 3.6  | V     |

| Vcc UVLO rising threshold                                  | Vvcc_uvlo       |                                                          |         | 2.48 |      | V     |

| Oscillator                                                 |                 |                                                          |         |      |      |       |

| Switching frequency range (7)                              | fsw             |                                                          |         | 2    |      | MHz   |

| Switching frequency accuracy                               | fsw_acc         |                                                          | -10     |      | +10  | %     |

| Minimum on time (7)                                        | ton_min         |                                                          |         | 60   |      | ns    |

| Minimum off time (7)                                       | toff_min        |                                                          |         | 60   |      | ns    |

| Spread spectrum modulation frequency spread <sup>(7)</sup> | fss_spread      |                                                          |         | 15   |      | %     |

| Spread spectrum modulation frequency rate <sup>(7)</sup>   | fss_rate        |                                                          |         | 9    |      | kHz   |

| Dynamic Output Voltage                                     |                 | ·                                                        | •       |      |      | •     |

| VOUT output range (7)                                      | Vout            | VOUT_SL = 1                                              | 0.20625 |      | 1.8  | V     |

| voor output range                                          | VOUT            | VOUT_SL = 2                                              | 0.4125  |      | 3.6  | V     |

| VOUT accuracy                                              | Maura and       | $VOUT_SL = 1,$<br>$V_{OUT} = 600mV,$<br>$V_{CC} = 3.35V$ | -1.5    |      | +1.5 | %     |

| VOUT accuracy                                              | Vout_acc        | $VOUT\_SL = 1,$<br>$V_{OUT} = 600mV,$<br>$V_{CC} = 2.5V$ | -1.5    |      | +1.5 | %     |

| VOUT start-up slew rate range                              |                 | VOUT_SL = 1                                              | 1.25    |      | 10   | mV/µs |

| (7)                                                        | VOUTSLEW_ST     | VOUT_SL = 2                                              | 2.5     |      | 20   | mV/µs |

| VOUT start-up slew rate<br>accuracy                        | Voutslew_st_acc |                                                          | -15     |      | +15  | %     |

| VOUT shutdown slew rate                                    |                 | VOUT SL = 1                                              | 1.25    |      | 10   | mV/µs |

| range <sup>(7)</sup>                                       | Voutslew_sp     | VOUT_SL = 2                                              | 2.5     |      | 20   | mV/µs |

| VOUT shutdown slew rate accuracy                           | VOUTSLEW_SP_ACC |                                                          | -15     |      | +15  | %     |

| VOUT dynamic slew rate                                     |                 | VOUT_SL = 1                                              | 2.5     |      | 20   | mV/µs |

| range <sup>(7)</sup>                                       | VOUTSLEW        | VOUT_SL = 2                                              | 5       |      | 40   | mV/µs |

| VOUT dynamic slew rate<br>accuracy                         | Voutslew_acc    |                                                          | -15     |      | +15  | %     |

**ELECTRICAL CHARACTERISTICS** *(continued)*  $V_{IN} = 5V$ ,  $V_{EN} = 2V$ ,  $T_J = -40^{\circ}C$  to +150°C, typical values are at  $T_J = 25^{\circ}C$ , unless otherwise noted.

| Parameter                                | Symbol        | Condition     | Min | Тур | Max  | Units |

|------------------------------------------|---------------|---------------|-----|-----|------|-------|

| Start-up delay time range (7)            | ton_delay     |               | 0   |     | 7750 | μs    |

| Shutdown delay time range (7)            | toff_delay    |               | 0   |     | 7750 | μs    |

| Buck Converter 1 (Buck 1)                |               |               |     |     |      |       |

| Buck 1 high-side switch on resistance    | RDS_HS_BUCK1  |               |     | 40  | 90   | mΩ    |

| Buck 1 low-side switch on resistance     | RDS_LS_BUCK1  |               |     | 20  | 45   | mΩ    |

| SW1 switch leakage current               | IILEAK_BUCK1  |               |     |     | 50   | μA    |

| SW1 peak current limit <sup>(7)</sup>    | ILIM_HS_BUCK1 | 0xCE = 'b00   | 4   | 6   | 7.8  | Α     |

| SW1 valley current limit (7)             | LIM_LS_BUCK1  | 0xCE = 'b00   | 3   | 4   | 5.1  | Α     |

| SW1 ZCD current <sup>(7)</sup>           | IZCD_BUCK1    |               |     |     | 300  | mA    |

| SW1 reverse current limit (7)            | REV_BUCK1     | 0xCE = 'b00   | 2   | 3   | 4    | Α     |

| VOUT1 foodbook lookogo                   | RFB1_BUCK1    | VOUT_SL = 1   | 12  |     |      | kΩ    |

| VOUT1 feedback leakage                   | RFB2_BUCK1    | $VOUT_SL = 2$ | 12  |     |      | kΩ    |

| VOUT1 output discharge                   | RDIS_BUCK1    |               |     | 100 |      | Ω     |

| Buck Converter 2 (Buck 2)                |               |               |     |     |      |       |

| Buck 2 high-side switch on resistance    | RDS_HS_BUCK2  |               |     | 40  | 90   | mΩ    |

| Buck 2 low-side switch on resistance     | RDS_LS_BUCK2  |               |     | 20  | 45   | mΩ    |

| SW2 switch leakage current               | IILEAK_BUCK2  |               |     |     | 50   | μA    |

| SW2 peak current limit (7)               | ILIM_HS_BUCK2 | 0xCE = 'b00   | 4   | 6   | 7.8  | A     |

| SW2 valley current limit (7)             | LIM_LS_BUCK2  | 0xCE = 'b00   | 3   | 4   | 5.1  | Α     |

| SW2 ZCD current <sup>(7)</sup>           | IZCD_BUCK2    |               |     |     | 300  | mA    |

| SW2 reverse current limit (7)            | REV_BUCK2     | 0xCE='b00     | 2   | 3   | 4    | Α     |

|                                          | RFB1_BUCK2    | VOUT_SL = 1   | 12  |     |      | kΩ    |

| VOUT2 feedback leakage                   | RFB2_BUCK2    | VOUT_SL = 2   | 12  |     |      | kΩ    |

| VOUT2 output discharge                   | RDIS_BUCK2    |               |     | 100 |      | Ω     |

| Buck Converter 3 (Buck 3)                |               |               | •   | •   |      | •     |

| Buck 3 high-side switch on resistance    | Rds_Hs_BUCK3  |               |     | 30  | 55   | mΩ    |

| Buck 3 low-side switch on resistance     | Rds_ls_buck3  |               |     | 16  | 32   | mΩ    |

| SW3 switch leakage current               | IILEAK_BUCK3  |               |     |     | 60   | μA    |

| SW3 peak current limit (7)               | ILIM_HS_BUCK3 | 0xCE = 'b00   | 5.5 | 8   | 11   | A     |

| SW3 valley current limit (7)             | LIM_LS_BUCK3  | 0xCE = 'b00   | 4   | 4.8 | 5.8  | Α     |

| SW3 ZCD current <sup>(7)</sup>           | IZCD_BUCK3    |               |     |     | 400  | mA    |

| SW3 reverse current limit (7)            | REV_BUCK3     | 0xCE = 'b00   | 3.5 | 4.5 | 5.5  | Α     |

|                                          | RFB1_BUCK3    | VOUT_SL = 1   | 12  |     |      | kΩ    |

| VOUT3 feedback leakage                   | RFB2_BUCK3    | VOUT_SL = 2   | 12  |     |      | kΩ    |

| VOUT3 output discharge                   | RDIS_BUCK3    | _             |     | 100 |      | Ω     |

| Buck Converter 4 (Buck 4)                | _             |               |     |     |      |       |

| Buck 4 high-side switch on resistance    | RDS_HS_BUCK4  |               |     | 30  | 55   | mΩ    |

| Buck 4 low-side switch on resistance     | RDS_LS_BUCK4  |               |     | 16  | 32   | mΩ    |

| SW4 switch leakage current               | IILEAK_BUCK4  |               |     |     | 60   | μA    |

| SW4 peak current limit <sup>(7)</sup>    | ILIM_HS_BUCK4 | 0xCE = 'b00   | 5.5 | 8   | 11   | A     |

| SW4 valley current limit <sup>(7)</sup>  | ILIM_LS_BUCK4 | 0xCE = 'b00   | 4   | 4.8 | 5.8  | A     |

| SW4 ZCD current <sup>(7)</sup>           | Izcd_buck4    |               |     | -   | 400  | mA    |

| SW4 reverse current limit <sup>(7)</sup> | IREV_BUCK4    | 0xCE = 'b00   | 3.5 | 4.5 | 5.5  | A     |

|                                          | RFB1_BUCK4    | VOUT_SL = 1   | 12  |     |      | kΩ    |

| VOUT4 feedback leakage                   | RFB2_BUCK4    | VOUT SL = 2   | 12  |     |      | kΩ    |

| VOUT4 output discharge                   | RDIS_BUCK4    |               |     | 100 |      | Ω     |

## ELECTRICAL CHARACTERISTICS (continued)

$V_{IN} = 5V$ ,  $V_{EN} = 2V$ ,  $T_J = -40^{\circ}$ C to +150°C, typical values are at  $T_J = 25^{\circ}$ C, unless otherwise noted.

| Parameter                                | Symbol                   | Condition               | Min   | Тур  | Max   | Units |

|------------------------------------------|--------------------------|-------------------------|-------|------|-------|-------|

| Buck Converter 5 (Buck 5)                |                          |                         |       |      |       |       |

| Buck 5 high-side switch on               | Dee us susur             |                         |       | 130  | 250   | mΩ    |

| resistance                               | Rds_hs_buck5             |                         |       | 130  | 250   | 11122 |

| Buck 5 low-side switch on                | RDS_LS_BUCK5             |                         |       | 75   | 140   | mΩ    |

| resistance                               | INDS_LS_BUCK5            |                         |       | 75   | 140   | 11152 |

| SW5 switch leakage current               | IILEAK_BUCK5             |                         |       |      | 20    | μA    |

| SW5 peak current limit (7)               | ILIM_HS_BUCK5            | 0xCE = 'b00             | 1.2   | 1.8  | 2.7   | A     |

| SW5 valley current limit (7)             | ILIM_LS_BUCK5            | 0xCE = 'b00             | 0.9   | 1.5  | 2     | A     |

| SW5 ZCD current <sup>(7)</sup>           | IZCD_BUCK5               |                         |       |      | 175   | mA    |

| SW5 reverse current limit (7)            | IREV_BUCK5               | 0xCE = 'b00             | 0.7   | 1.1  | 1.4   | A     |

| VOUT5 feedback leakage                   | RFB1_BUCK5               | VOUT_SL = 1             | 12    |      |       | kΩ    |

|                                          | RFB2_BUCK5               | VOUT_SL = 2             | 12    |      |       | kΩ    |

| VOUT5 output discharge                   | RDIS_BUCK5               |                         |       | 100  |       | Ω     |

| Buck Converter 6 (Buck 6)                | •                        |                         |       |      |       |       |

| Buck 6 high-side switch on               | RDS_HS_BUCK6             |                         |       | 130  | 250   | mΩ    |

| resistance                               | TOS_HS_BUCK6             |                         |       | 150  | 230   | 11152 |

| Buck 6 low-side switch on                | RDS_LS_BUCK6             |                         |       | 75   | 140   | mΩ    |

| resistance                               | INDS_LS_BUCK6            |                         |       | 75   | 140   | 11152 |

| SW6 switch leakage current               | IILEAK_BUCK6             |                         |       |      | 20    | μA    |

| SW6 peak current limit (7)               | ILIM_HS_BUCK6            |                         | 1.2   | 1.8  | 2.7   | Α     |

| SW6 valley current limit (7)             | ILIM_LS_BUCK6            |                         | 0.9   | 1.5  | 2     | Α     |

| SW6 ZCD current <sup>(7)</sup>           | IZCD_BUCK6               |                         |       |      | 175   | mA    |

| SW6 reverse current limit <sup>(7)</sup> | IREV_BUCK6               |                         | 0.7   | 1.1  | 1.4   | Α     |

|                                          | R <sub>FB1_BUCK6</sub>   | VOUT_SL = 1             | 12    |      |       | kΩ    |

| VOUT6 feedback leakage                   | RFB2_BUCK6               | VOUT_SL = 2             | 12    |      |       | kΩ    |

| VOUT6 output discharge                   | RDIS_BUCK6               |                         |       | 100  |       | Ω     |

| Thermal Protection                       |                          |                         |       |      |       |       |

| Thermal warning (7)                      | T <sub>TW</sub>          |                         | 125   | 140  | 155   | °C    |

| Thermal warning hysteresis (7)           | T <sub>TW_HYS</sub>      |                         |       | 20   |       | °C    |

| Thermal shutdown (7)                     | T <sub>TSD</sub>         |                         | 155   | 170  | 185   | °C    |

| Thermal shutdown hysteresis (7)          | T <sub>TSD_HYS</sub>     |                         |       | 20   |       | °C    |

| Output Voltage Protection                |                          | ·                       |       |      |       |       |

| VOUT over-voltage (OV)                   |                          | V/ 1 0V/                | 112.5 | 115  | 117.5 | 0/    |

| threshold                                | Vout_ov                  | Vout = 1.8V             | 112.5 | 115  | C.111 | %     |

| VOUT OV hysteresis                       | Vout_ov_hys              | Vout = 1.8V             |       | 5.5  |       | %     |

| VOUT under-voltage (UV)                  | Max                      | V <sub>OUT</sub> = 1.8V | 72.5  | 75   | 77.5  | %     |

| threshold                                | V <sub>OUT_UV</sub>      | $v_{OUT} = 1.0 v$       | 72.0  | 75   | 11.5  | 70    |

| VOUT UV hysteresis                       | Vout_uv_hys              | Vout = 1.8V             |       | 5    |       | %     |

| Hiccup time range (7)                    | thic                     |                         | 2     |      | 8     | ms    |

| Enable                                   |                          |                         |       |      |       |       |

| ENx logic on threshold                   | V <sub>ENx_LOG</sub>     |                         | 0.25  | 0.65 | 1     | V     |

| ENx rising threshold                     | V <sub>ENx_</sub> RISING |                         | 1.25  | 1.4  | 1.55  | V     |

| ENx falling threshold                    | VENx_FALLING             |                         | 1.15  | 1.3  | 1.45  | V     |

| ENx voltage hysteresis                   | VENx_HYS                 |                         |       | 100  |       | mV    |

| ENx leakage                              | IENx                     | $V_{ENx} = 3.3V$        |       |      | 12    | μA    |

**ELECTRICAL CHARACTERISTICS** *(continued)*  $V_{IN} = 5V$ ,  $V_{EN} = 2V$ ,  $T_J = -40^{\circ}C$  to +150°C, typical values are at  $T_J = 25^{\circ}C$ , unless otherwise noted.

| Parameter                                          | Symbol               | Condition                                                               | Min   | Тур   | Max   | Units |

|----------------------------------------------------|----------------------|-------------------------------------------------------------------------|-------|-------|-------|-------|

| Power Good                                         |                      |                                                                         |       | -     |       |       |

| PG OV rising threshold <sup>(8)</sup>              | PGov                 | $V_{OUT} = 1.8V$ , percentage of actual $V_{REF}$ , PG_THRESHOLD[0] = 1 | 102.5 | 104.5 | 106.5 | %     |

|                                                    | . 000                | $V_{OUT}$ = 1.8V, percentage of actual $V_{REF}$ , PG_THRESHOLD[0] = 0  | 104.5 | 106.5 | 108.5 | %     |

| PG OV threshold hysteresis <sup>(8)</sup>          | PGov_Hys             | Vout = 1.8V                                                             |       | 0.5   |       | %     |

| PG UV falling threshold <sup>(8)</sup>             | PGuv                 | $V_{OUT} = 1.8V$ , percentage of actual $V_{REF}$ , PG_THRESHOLD[0] = 1 | 94.5  | 96.5  | 98.5  | %     |

| ,                                                  |                      | $V_{OUT} = 1.8V$ , percentage of actual $V_{REF}$ , PG_THRESHOLD[0] = 0 | 92.5  | 94.5  | 96.5  | %     |

| PG UV threshold hysteresis <sup>(8)</sup>          | PG <sub>UV_HYS</sub> | $V_{OUT} = 1.8V$                                                        |       | 0.5   |       | %     |

| PG sink capability                                 | IPG                  | I <sub>PG</sub> = 4mA                                                   |       |       | 300   | mV    |

| PG delay range (7)                                 | tpg_delay            |                                                                         | 0     |       | 10    | ms    |

| ALERT                                              |                      |                                                                         |       |       |       |       |

| ALERT sink capability                              | I <sub>RST</sub>     | I <sub>RESET</sub> = 4mA                                                |       |       | 300   | mV    |

| System Clock                                       |                      |                                                                         |       |       |       |       |

| System clock                                       | f <sub>CLK</sub>     |                                                                         |       | 2     |       | MHz   |

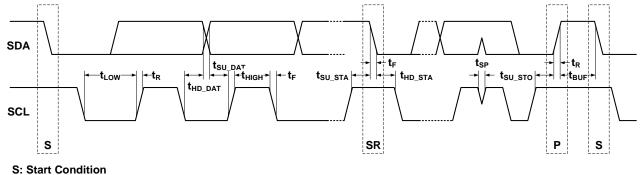

| PMBus Logic Interface <sup>(7)</sup>               |                      |                                                                         |       |       |       |       |

| SCL/SDA input logic low                            | VIL                  |                                                                         |       |       | 0.4   | V     |

| SCL/SDA input logic high                           | VIH                  |                                                                         | 1.2   |       |       | V     |

| SDA output logic low                               | V <sub>OL</sub>      | $I_{LOAD} = 3mA$                                                        |       |       | 0.4   | V     |

| SCL clock frequency                                | f <sub>SCL</sub>     |                                                                         |       |       | 1000  | kHz   |

| SCL high time                                      | t <sub>HIGH</sub>    |                                                                         | 0.6   |       |       | μs    |

| SCL low time                                       | t <sub>LOW</sub>     |                                                                         | 1.3   |       |       | μs    |

| Data set-up time                                   | t <sub>SU_DAT</sub>  |                                                                         | 100   |       |       | ns    |

| Data hold time                                     | t <sub>HD_DAT</sub>  |                                                                         | 0     |       | 0.9   | μs    |

| Set-up time for repeated start                     | t <sub>su_sta</sub>  |                                                                         | 0.6   |       |       | μs    |

| Hold time for start                                | t <sub>HD_STA</sub>  |                                                                         | 0.6   |       |       | μs    |

| Bus free time between a start and a stop condition | tBUF                 |                                                                         | 1.3   |       |       | μs    |

| Set-up time for stop condition                     | tsu_s⊤o              |                                                                         | 0.6   |       |       | μs    |

| Rising time of SCL/SDA                             | t <sub>R</sub>       |                                                                         |       |       | 300   | ns    |

| Falling time of SCL/SDA                            | tF                   |                                                                         |       |       | 300   | ns    |

| Pulse width of suppressed spike                    | t <sub>SP</sub>      |                                                                         | 0     |       | 50    | ns    |

| Capacitance bus for each bus line                  | Св                   |                                                                         |       |       | 400   | pF    |

Notes:

Derived from bench characterization. Not tested in production. 7)

Power good threshold is based on the nominal output voltage of each output. 8)

### PMBUS-COMPATIBLE INTERFACE TIMING DIAGRAM

SR: Repeated Start Condition

P: Stop Condition

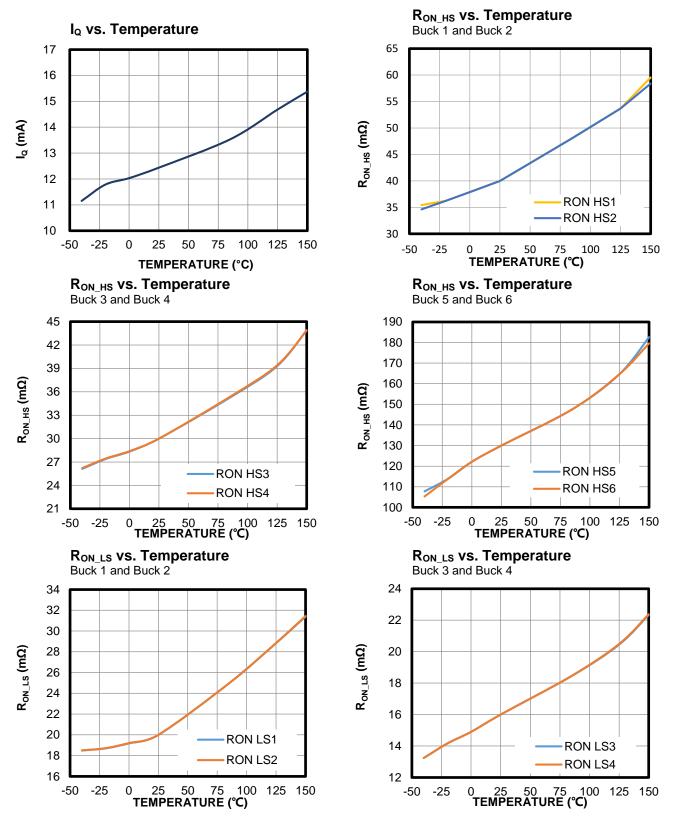

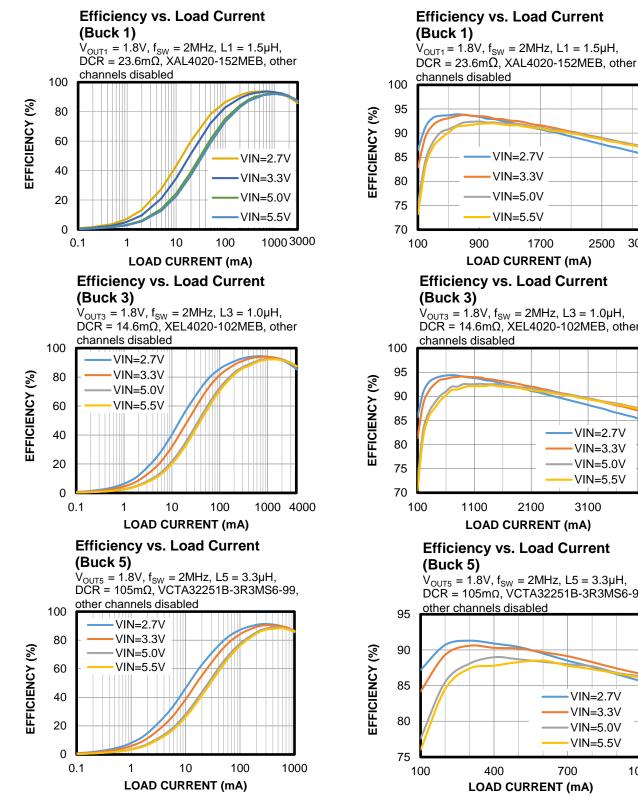

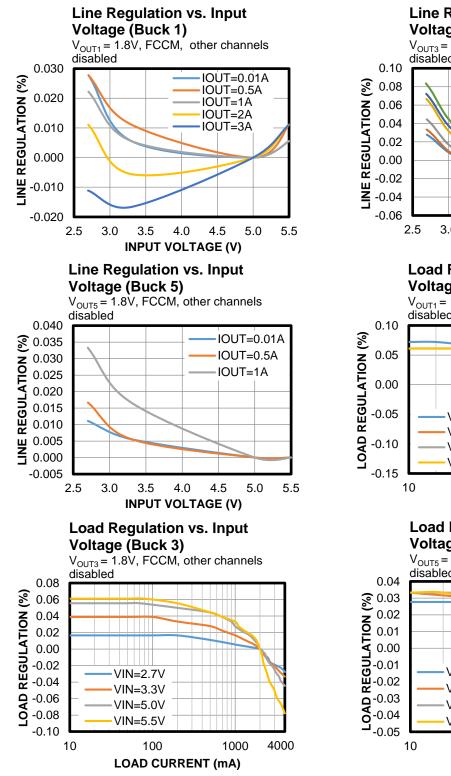

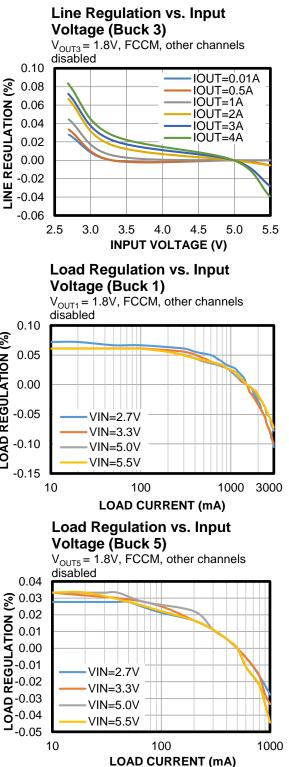

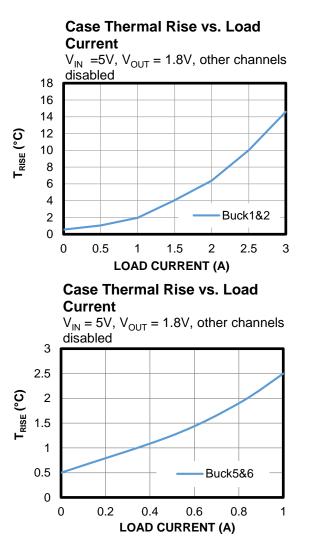

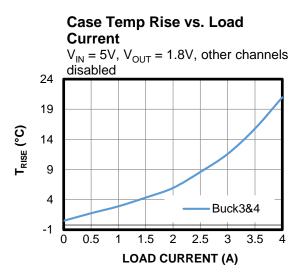

## **TYPICAL CHARACTERISTICS**

$V_{IN} = 5V$ ,  $T_J = -40^{\circ}C$  to  $+150^{\circ}C$ , unless otherwise noted.

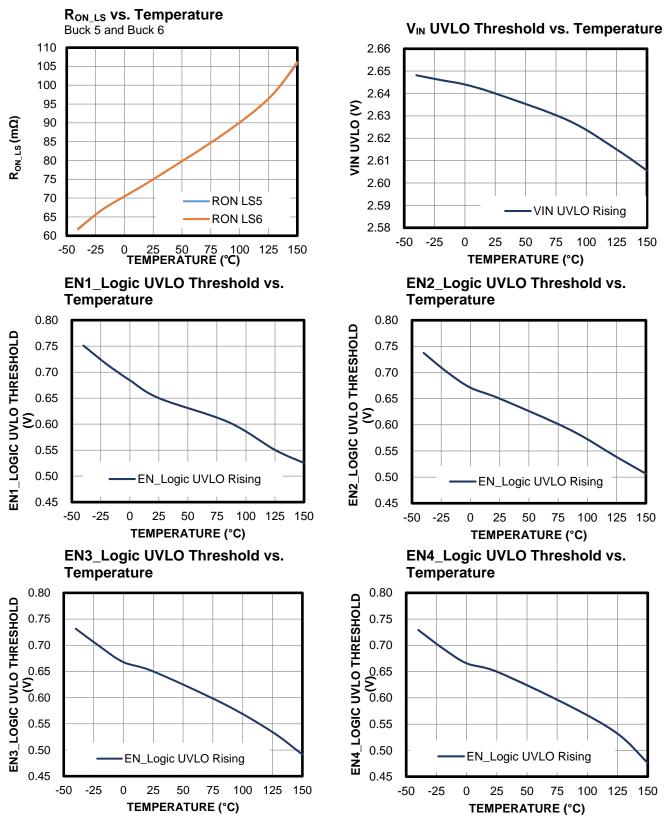

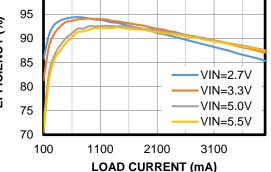

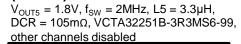

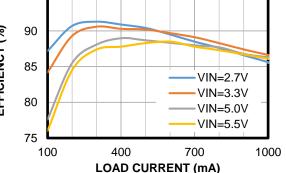

## TYPICAL CHARACTERISTICS (continued)

$V_{IN} = 5V$ ,  $T_J = -40^{\circ}C$  to +150°C, unless otherwise noted.

MPQ7930 Rev. 1.0 2/14/2023 MF

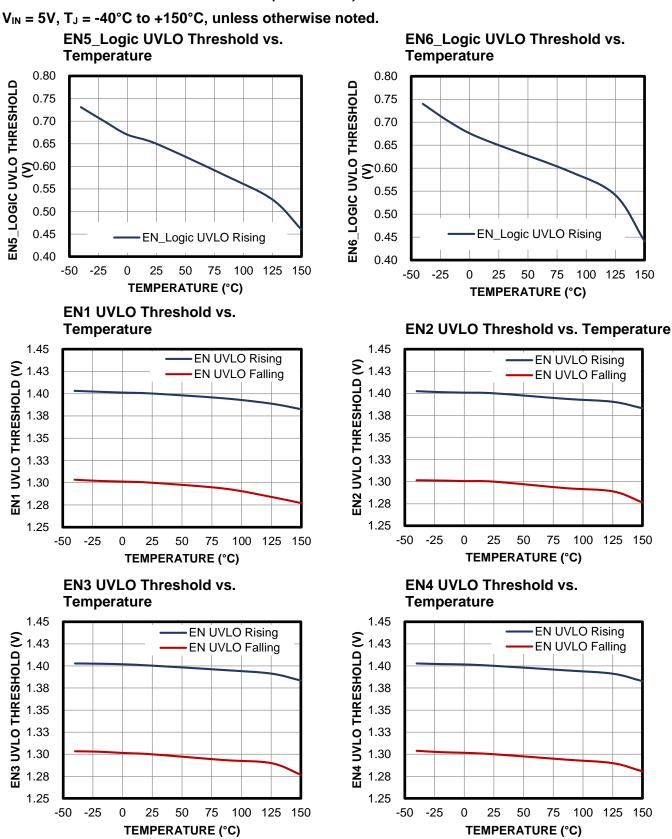

## TYPICAL CHARACTERISTICS (continued)

.0 MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2023 MPS. All Rights Reserved.

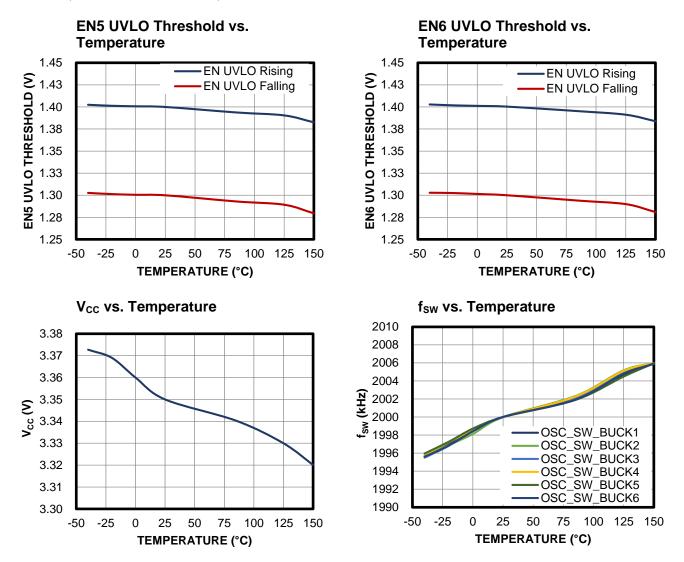

## TYPICAL CHARACTERISTICS (continued)

$V_{IN} = 5V$ ,  $T_J = -40^{\circ}C$  to +150°C, unless otherwise noted.

## TYPICAL PERFORMANCE CHARACTERISTICS

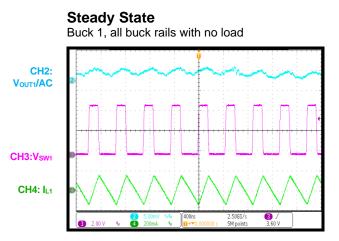

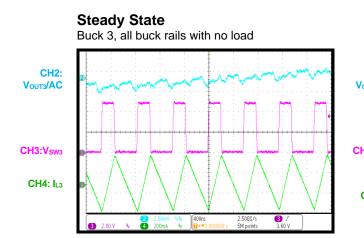

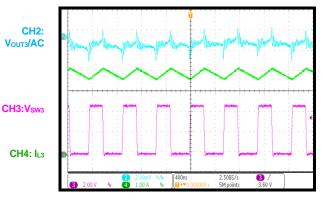

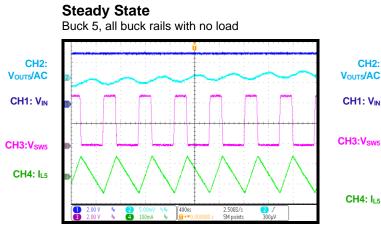

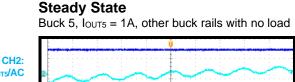

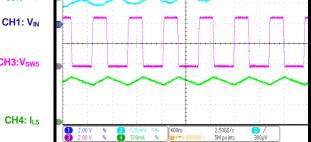

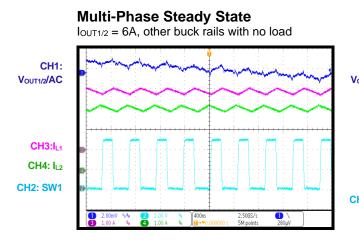

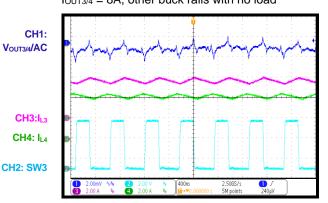

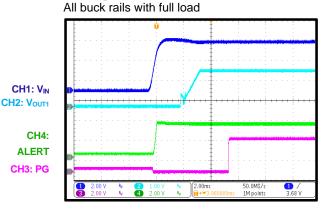

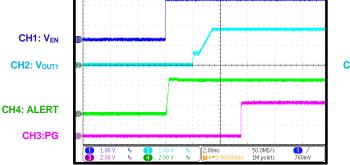

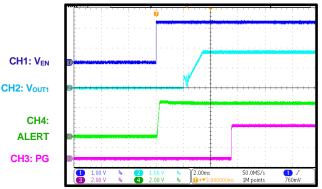

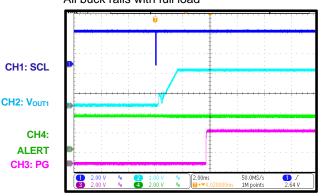

$V_{IN} = 5V$ ,  $V_{OUT1} = V_{OUT2} = V_{OUT3} = V_{OUT4} = V_{OUT5} = V_{OUT6} = 1.8V$ ,  $L1 = L2 = 1.5\mu$ H,  $L3 = L4 = 1\mu$ H, L5 = L6 =  $3.3\mu$ H, C<sub>OUT1</sub> = C<sub>OUT2</sub> = 2 x 22 $\mu$ F, C<sub>OUT3</sub> = C<sub>OUT4</sub> = 2 x 22 $\mu$ F, C<sub>OUT5</sub> = C<sub>OUT6</sub> = 2 x 4.7 $\mu$ F,  $f_{SW} = 2MHz$ ,  $T_A = 25^{\circ}C$ , unless otherwise noted.

### VIN=2.7V VIN=3.3V VIN=5.0V VIN=5.5V 1700 2500 3000

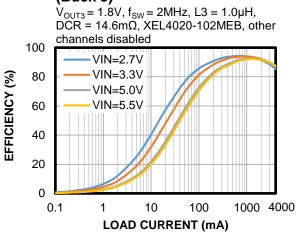

## Efficiency vs. Load Current

$V_{OUT3} = 1.8V, f_{SW} = 2MHz, L3 = 1.0\mu H,$ DCR = 14.6mΩ, XEL4020-102MEB, other channels disabled

## Efficiency vs. Load Current

MPQ7930 Rev. 1.0 2/14/2023

MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2023 MPS. All Rights Reserved.

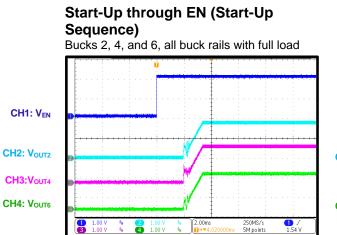

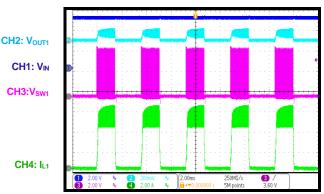

$V_{IN} = 5V$ ,  $V_{OUT1} = V_{OUT2} = V_{OUT3} = V_{OUT4} = V_{OUT5} = V_{OUT6} = 1.8V$ ,  $L1 = L2 = 1.5\mu$ H,  $L3 = L4 = 1\mu$ H,  $L5 = L6 = 3.3\mu$ H,  $C_{OUT1} = C_{OUT2} = 2 \times 22\mu$ F,  $C_{OUT3} = C_{OUT4} = 2 \times 22\mu$ F,  $C_{OUT5} = C_{OUT6} = 2 \times 4.7\mu$ F,  $f_{SW} = 2$ MHz,  $T_A = 25^{\circ}$ C, unless otherwise noted.

$V_{IN} = 5V$ ,  $V_{OUT1} = V_{OUT2} = V_{OUT3} = V_{OUT4} = V_{OUT5} = V_{OUT6} = 1.8V$ ,  $L1 = L2 = 1.5\mu$ H,  $L3 = L4 = 1\mu$ H,  $L5 = L6 = 3.3\mu$ H,  $C_{OUT1} = C_{OUT2} = 2 \times 22\mu$ F,  $C_{OUT3} = C_{OUT4} = 2 \times 22\mu$ F,  $C_{OUT5} = C_{OUT6} = 2 \times 4.7\mu$ F,  $f_{SW} = 2$ MHz,  $T_A = 25^{\circ}$ C, unless otherwise noted.

$V_{IN} = 5V$ ,  $V_{OUT1} = V_{OUT2} = V_{OUT3} = V_{OUT4} = V_{OUT5} = V_{OUT6} = 1.8V$ ,  $L1 = L2 = 1.5\mu$ H,  $L3 = L4 = 1\mu$ H,  $L5 = L6 = 3.3\mu$ H,  $C_{OUT1} = C_{OUT2} = 2 \times 22\mu$ F,  $C_{OUT3} = C_{OUT4} = 2 \times 22\mu$ F,  $C_{OUT5} = C_{OUT6} = 2 \times 4.7\mu$ F,  $f_{SW} = 2$ MHz,  $T_A = +25^{\circ}$ C, unless otherwise noted.

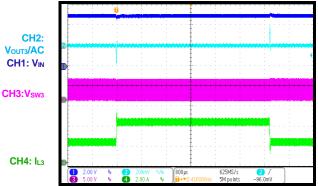

CH2: Vouri/AC CH2: Vouri/AC CH4: IL1

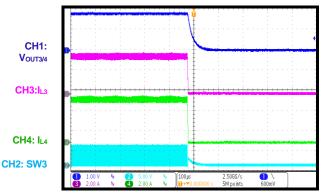

Steady State

Buck 3,  $I_{OUT3} = 4A$ , other buck rails with no load

$V_{IN} = 5V$ ,  $V_{OUT1} = V_{OUT2} = V_{OUT3} = V_{OUT4} = V_{OUT5} = V_{OUT6} = 1.8V$ ,  $L1 = L2 = 1.5\mu$ H,  $L3 = L4 = 1\mu$ H,  $L5 = L6 = 3.3\mu$ H,  $C_{OUT1} = C_{OUT2} = 2 \times 22\mu$ F,  $C_{OUT3} = C_{OUT4} = 2 \times 22\mu$ F,  $C_{OUT5} = C_{OUT6} = 2 \times 4.7\mu$ F,  $f_{SW} = 2$ MHz,  $T_A = 25^{\circ}$ C, unless otherwise noted.

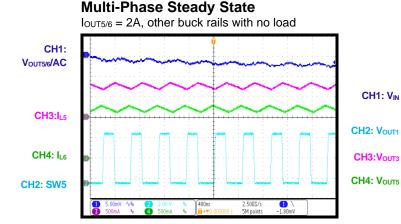

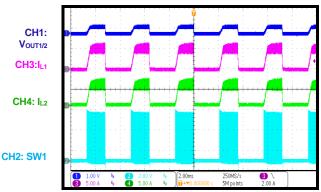

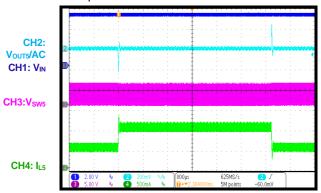

Multi-Phase Steady State

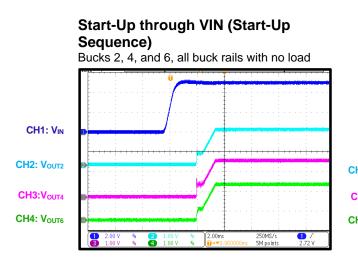

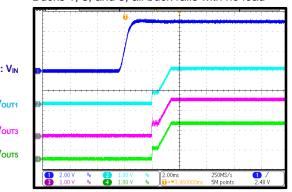

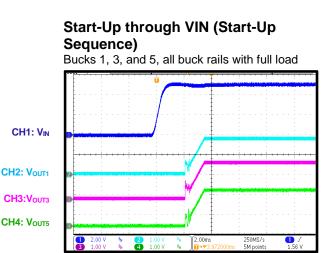

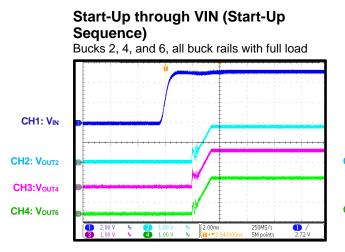

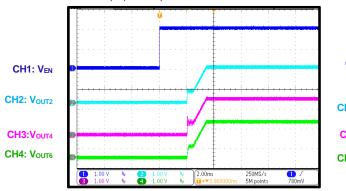

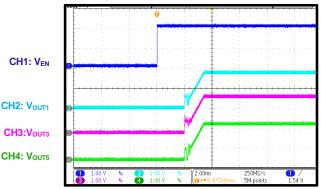

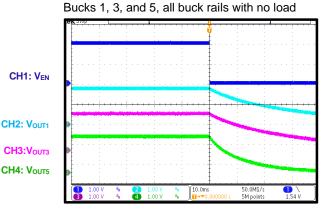

Start-Up through VIN (Start-Up Sequence)

**Sequence)** Bucks 1, 3, and 5, all buck rails with no load

MPQ7930 Rev. 1.0 2/14/2023 MI

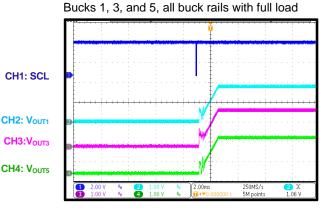

$V_{IN} = 5V$ ,  $V_{OUT1} = V_{OUT2} = V_{OUT3} = V_{OUT4} = V_{OUT5} = V_{OUT6} = 1.8V$ ,  $L1 = L2 = 1.5\mu$ H,  $L3 = L4 = 1\mu$ H, L5 = L6 =  $3.3\mu$ H, C<sub>OUT1</sub> = C<sub>OUT2</sub> = 2 x 22 $\mu$ F, C<sub>OUT3</sub> = C<sub>OUT4</sub> = 2 x 22 $\mu$ F, C<sub>OUT5</sub> = C<sub>OUT6</sub> = 2 x 4.7 $\mu$ F,  $f_{SW} = 2MHz$ ,  $T_A = 25^{\circ}C$ , unless otherwise noted.

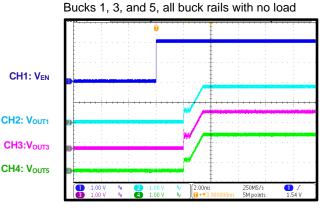

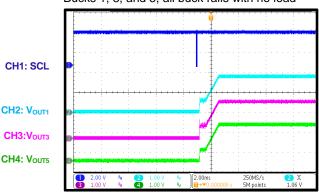

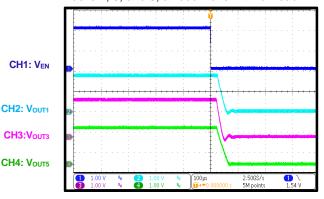

### Start-Up through EN (Start-Up Sequence)

Bucks 2, 4, and 6, all buck rails with no load

MPQ7930 Rev. 1.0

2/14/2023

Start-Up through EN (Start-Up Sequence)

#### Start-Up through EN (Start-Up Sequence)

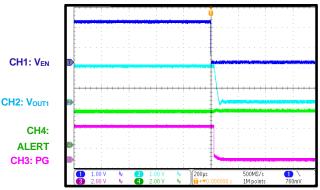

Bucks 1, 3, and 5, all buck rails with full load

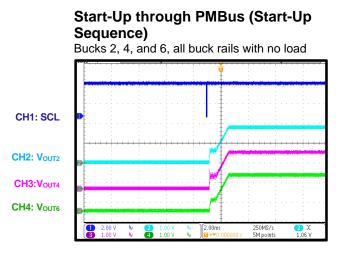

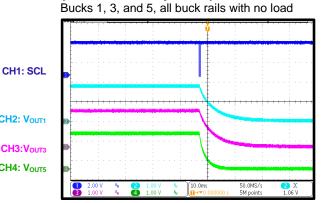

#### Start-Up through PMBus (Start-Up Sequence) Bucks 1, 3, and 5, all buck rails with no load

CH2: VOUT1

MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2023 MPS. All Rights Reserved.

$V_{IN} = 5V$ ,  $V_{OUT1} = V_{OUT2} = V_{OUT3} = V_{OUT4} = V_{OUT5} = V_{OUT6} = 1.8V$ ,  $L1 = L2 = 1.5\mu$ H,  $L3 = L4 = 1\mu$ H,  $L5 = L6 = 3.3\mu$ H,  $C_{OUT1} = C_{OUT2} = 2 \times 22\mu$ F,  $C_{OUT3} = C_{OUT4} = 2 \times 22\mu$ F,  $C_{OUT5} = C_{OUT6} = 2 \times 4.7\mu$ F,  $f_{SW} = 2M$ Hz,  $T_A = 25^{\circ}$ C, unless otherwise noted.

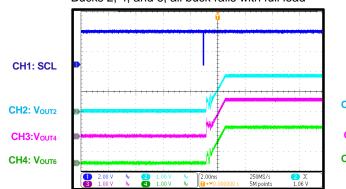

## Start-Up through PMBus (Start-Up Sequence)

Bucks 2, 4, and 6, all buck rails with full load

## Start-Up through PMBus (Start-Up Sequence)

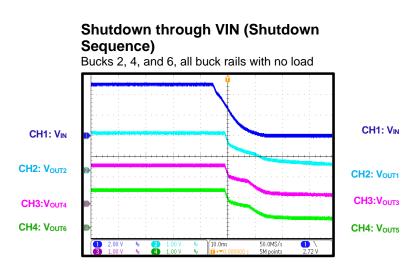

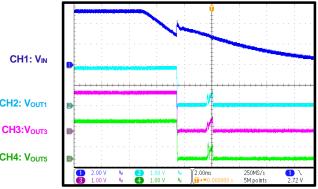

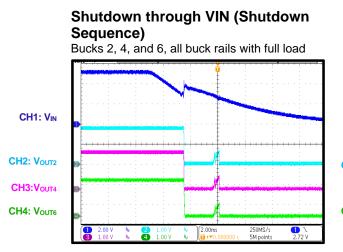

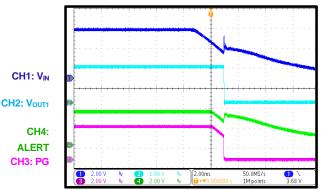

## Shutdown through VIN (Shutdown Sequence)

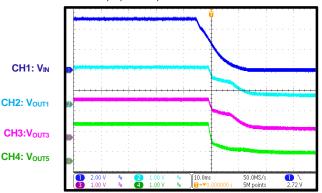

Bucks 1, 3, and 5, all buck rails with no load

## Shutdown through VIN (Shutdown Sequence)

MPQ7930 Rev. 1.0 2/14/2023

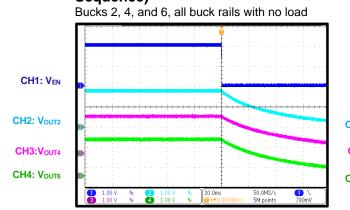

$V_{IN} = 5V$ ,  $V_{OUT1} = V_{OUT2} = V_{OUT3} = V_{OUT4} = V_{OUT5} = V_{OUT6} = 1.8V$ ,  $L1 = L2 = 1.5\mu$ H,  $L3 = L4 = 1\mu$ H,  $L5 = L6 = 3.3\mu$ H,  $C_{OUT1} = C_{OUT2} = 2 \times 22\mu$ F,  $C_{OUT3} = C_{OUT4} = 2 \times 22\mu$ F,  $C_{OUT5} = C_{OUT6} = 2 \times 4.7\mu$ F,  $f_{SW} = 2M$ Hz,  $T_A = 25^{\circ}$ C, unless otherwise noted.

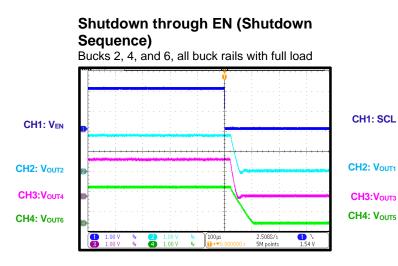

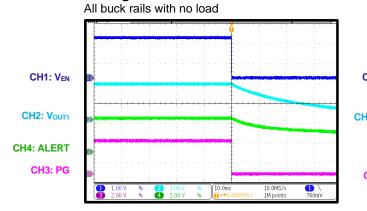

## Shutdown through EN (Shutdown Sequence)

## Shutdown through EN (Shutdown Sequence)

## Shutdown through EN (Shutdown Sequence)

Bucks 1, 3, and 5, all buck rails with full load

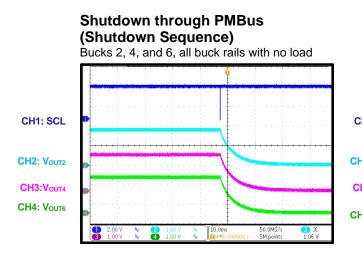

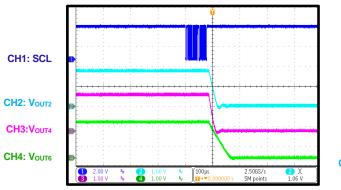

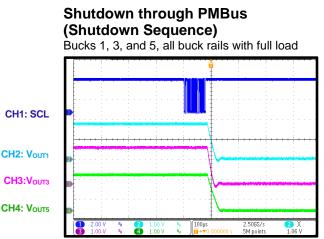

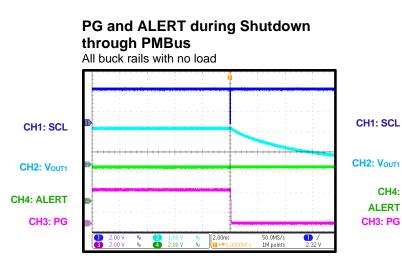

### Shutdown through PMBus (Shutdown Sequence)

MPQ7930 Rev. 1.0 2/14/2023 M

$V_{IN} = 5V$ ,  $V_{OUT1} = V_{OUT2} = V_{OUT3} = V_{OUT4} = V_{OUT5} = V_{OUT6} = 1.8V$ ,  $L1 = L2 = 1.5\mu$ H,  $L3 = L4 = 1\mu$ H,  $L5 = L6 = 3.3\mu$ H,  $C_{OUT1} = C_{OUT2} = 2 \times 22\mu$ F,  $C_{OUT3} = C_{OUT4} = 2 \times 22\mu$ F,  $C_{OUT5} = C_{OUT6} = 2 \times 4.7\mu$ F,  $f_{SW} = 2$ MHz,  $T_A = 25^{\circ}$ C, unless otherwise noted.

## Shutdown through PMBus (Shutdown Sequence)

Bucks 2, 4, and 6, all buck rails with full load

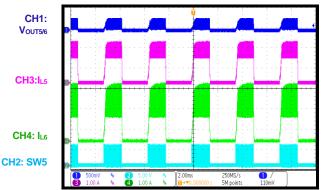

Multi-Phase Shutdown Iout5/6 = 2A, other buck rails with no load CH1: Vout5/6 CH3:IL5 CH4: IL6

CH2: SW5

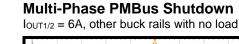

#### Multi-Phase PMBus Shutdown

IOUT3/4 = 8A, other buck rails with no load

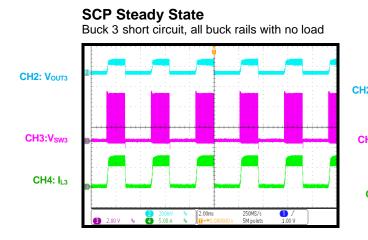

### **SCP Steady State**

Buck 1 short circuit, all buck rails with no load

$V_{IN} = 5V$ ,  $V_{OUT1} = V_{OUT2} = V_{OUT3} = V_{OUT4} = V_{OUT5} = V_{OUT6} = 1.8V$ ,  $L1 = L2 = 1.5\mu$ H,  $L3 = L4 = 1\mu$ H,  $L5 = L6 = 3.3\mu$ H,  $C_{OUT1} = C_{OUT2} = 2 \times 22\mu$ F,  $C_{OUT3} = C_{OUT4} = 2 \times 22\mu$ F,  $C_{OUT5} = C_{OUT6} = 2 \times 4.7\mu$ F,  $f_{SW} = 2MHz$ ,  $T_A = 25^{\circ}C$ , unless otherwise noted.

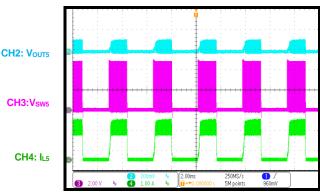

**SCP Steady State** Buck 5 short circuit, all buck rails with no load

load

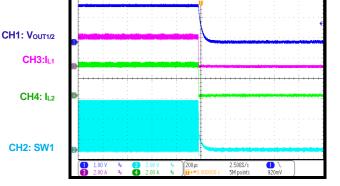

### Multi-Phase SCP Steady State

Buck 5/6 short circuit, other buck rails with no load

2.00m

2

250MS/: 5M point

CH3:IL3 CH4: IL4 **CH2: SW3** 0

MPQ7930 Rev. 1.0 2/14/2023

$V_{IN} = 5V$ ,  $V_{OUT1} = V_{OUT2} = V_{OUT3} = V_{OUT4} = V_{OUT5} = V_{OUT6} = 1.8V$ ,  $L1 = L2 = 1.5\mu$ H,  $L3 = L4 = 1\mu$ H,  $L5 = L6 = 3.3\mu$ H,  $C_{OUT1} = C_{OUT2} = 2 \times 22\mu$ F,  $C_{OUT3} = C_{OUT4} = 2 \times 22\mu$ F,  $C_{OUT5} = C_{OUT6} = 2 \times 4.7\mu$ F,  $f_{SW} = 2M$ Hz,  $T_A = 25^{\circ}$ C, unless otherwise noted.

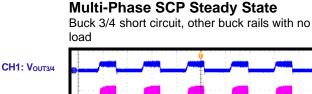

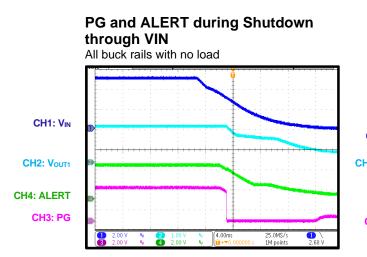

## PG and ALERT during Start-Up through VIN

## PG and ALERT during Start-Up through EN All buck rails with no load

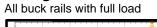

## CH1: SCL CH2: Vourn CH4: ALERT CH3: PG

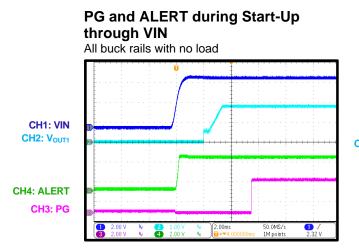

## PG and ALERT during Start-Up through EN

All buck rails with full load

#### PG and ALERT during Start-Up through PMBus All buck rails with full load

MPQ7930 Rev. 1.0 2/14/2023

$V_{IN} = 5V$ ,  $V_{OUT1} = V_{OUT2} = V_{OUT3} = V_{OUT4} = V_{OUT5} = V_{OUT6} = 1.8V$ ,  $L1 = L2 = 1.5\mu$ H,  $L3 = L4 = 1\mu$ H,  $L5 = L6 = 3.3\mu$ H,  $C_{OUT1} = C_{OUT2} = 2 \times 22\mu$ F,  $C_{OUT3} = C_{OUT4} = 2 \times 22\mu$ F,  $C_{OUT5} = C_{OUT6} = 2 \times 4.7\mu$ F,  $f_{SW} = 2$ MHz,  $T_A = 25^{\circ}$ C, unless otherwise noted.

## PG and ALERT during Shutdown through EN

#### PG and ALERT during Shutdown through VIN All buck rails with full load

## PG and ALERT during Shutdown through EN

All buck rails with full load

## PG and ALERT during Shutdown through PMBus

$V_{IN} = 5V$ ,  $V_{OUT1} = V_{OUT2} = V_{OUT3} = V_{OUT4} = V_{OUT5} = V_{OUT6} = 1.8V$ ,  $L1 = L2 = 1.5\mu$ H,  $L3 = L4 = 1\mu$ H,  $L5 = L6 = 3.3\mu$ H,  $C_{OUT1} = C_{OUT2} = 2 \times 22\mu$ F,  $C_{OUT3} = C_{OUT4} = 2 \times 22\mu$ F,  $C_{OUT5} = C_{OUT6} = 2 \times 4.7\mu$ F,  $f_{SW} = 2$ MHz,  $T_A = 25^{\circ}$ C, unless otherwise noted.

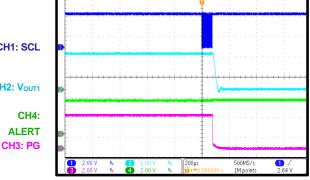

Load Transient Response

IOUT3 transient from 2A to 4A, slew rate is 2A/µs

#### Load Transient Response

$I_{\text{OUT5}}$  transient from 0.5A to 1.0A, slew rate is 2.0A/µs

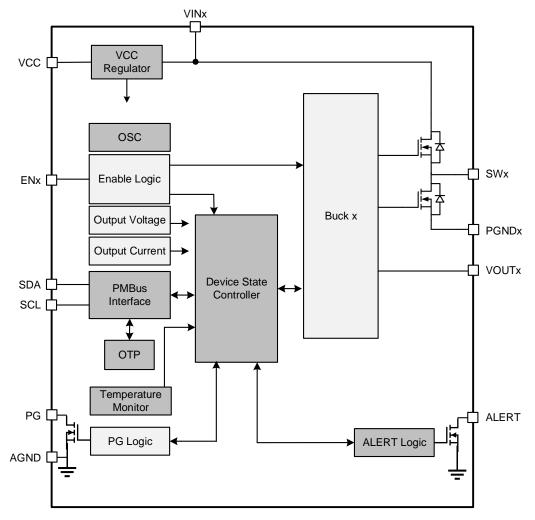

## FUNCTIONAL BLOCK DIAGRAM

Figure 2: Functional Block Diagram

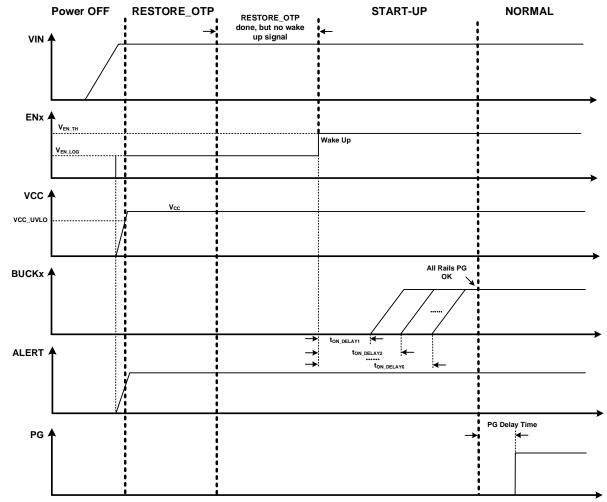

### **START-UP BEHAVIOR**

Figure 3: Start-Up Behavior

### **OPERATION**

The MPQ7930 is a highly flexible power solution for advanced driver assistance systems (ADAS) and system-on-chip (SoCs). lt integrates six high-frequency, synchronous, rectified step-down converters. The PMBus and multi-page one-time programmable (OTP) memory allow for significant configurations to meet the requirements of the target SoC.

#### **High-Efficiency Buck Regulators**

Bucks 1–6 are synchronous, step-down DC/DC converters with built-in under-voltage lockout (UVLO), soft start, compensation, and hiccup current limit protection. Fixed-frequency peak current control provides fast transient response and a stable frequency. The switching clock phase shifts from buck 1-6 during continuous conduction mode (CCM).

#### **Multi-Phase Operation**

Multi-phase operation is available and can be configured via the OTP. Any changes that are made are updated after the device restarts. The multi-phase pairs are buck 1 and buck 2, buck 3 and buck 4, then buck 5 and buck 6. If two bucks operate in parallel, the configuration page for the lower-numbered buck is used.

#### **Light-Load Operation**

The MPQ7930 can support forced continuous conduction mode (FCCM).

FCCM allows the inductor current to reach negative values up to the negative current limit. FCCM provides the best transient response and frequency performance. The advantages of FCCM are its controllable frequency, lower output ripple, and smaller peak inductor current under light loads.

#### **Dynamic Voltage Scaling**

The output voltage (VOUT) can be changed via the PMBus during normal operation. When the voltage changes, the slope is determined by the VOUT\_SLEW register.

If users regulate VOUT\_CMD to exceed VOUT MAX VOUT MIN or via the VOUT COMMAND register, V<sub>OUT</sub> is limited to its maximum (V<sub>OUT MAX</sub>) or minimum (V<sub>OUT MIN</sub>). This protection mechanism can prevent abnormal system operation due to writing an incorrect value for VOUT\_COMMAND. The

values for VOUT MAX and VOUT MIN are determined by the VOUT MAX and VOUT MIN commands. If V<sub>OUT</sub> changes due to external reasons, VOUT\_MAX and VOUT\_MIN do not protect from these changes.

#### V<sub>IN</sub> and V<sub>CC</sub> Under-Voltage Lockout (UVLO)

Input under-voltage lockout (UVLO) is derived from VIN (pin 23). If VIN falls below VIN UVLO and  $V_{CC}$  exceeds  $V_{CC}$  UVLO, the MPQ7930 enters the restore OTP state with no output. During this time, PMBus communication operates normally. If V<sub>CC</sub> falls below V<sub>CC UVLO</sub>, the MPQ7930 enters the power off state, and PMBus communication is unavailable.

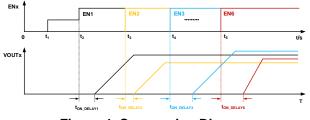

#### **Power Sequencing**

The MPQ7930 provides six enable pins (ENx), and each output is controlled by a separate pin. Typically, power sequencing is controlled externally, but each output can be further delayed. For each buck, the delay time can be independent and freely configured via the TON DELAY register. TON DELAY sets the time from when the EN level exceeds EN RISING THRESHOLD and when VOUT starts to rise after the completion of RESORE OTP.

Figure 4 shows the sequencing diagram. EN1 can be replaced by any ENx pin.

Figure 4: Sequencing Diagram

#### Internal Soft Start

The soft-start function is implemented to prevent the PMIC's V<sub>OUT</sub> from overshooting during start-up. When the MPQ7930 starts up, the internal circuitry of each power rail generates a soft-start voltage that ramps up from 0V. During soft start, an initial step can be observed on the output voltage.

The soft-start period lasts until the voltage on the soft-start capacitor exceeds the reference voltage ( $V_{REF}$ ). At this point,  $V_{REF}$  takes over. The soft start slew rate of each output can be configured via the OTP.

During soft start, an initial step can be observed on the output voltage.

#### **Output Discharge**

The MPQ7930 provide a  $100\Omega$  discharge resistor for each output. The discharge resistor is between the VOUTx pin and AGND. The resistor is connected to a discharge circuit only when the shutdown signal is enabled. The energy on the output capacitor is discharged through the  $100\Omega$  resistor. During normal operation, the discharge resistor is disconnected.

#### Power Good (PG) and ALERT Indicators

PG and ALERT are open-drain outputs. PG asserts if the voltage is not within the PG range. The PG range of each buck can be configured via the PG\_CONFIG register.

The ALERT pin asserts to indicate issues with the device's status (see Table 1). By default, over-voltage protection (OVP), under-voltage protection (UVP), thermal warning, thermal shutdown, packet error checking (PEC) errors, and communications errors can assert the ALERT flag. The ALERT flag remains asserted until the relevant fault and status register are cleared. Some of faults can also be masked. CLEAR\_FAULTS clears any fault bit in all status registers.

When PG and ALERT de-assert, the MPQ7930 provides a variety of delay time options (0ms, 2ms, 5ms, and 10ms) via the PG\_ALERT\_DELAY register.

| Fault Types                          |               |                  |  |  |  |  |  |

|--------------------------------------|---------------|------------------|--|--|--|--|--|

| Fault Type                           | PG<br>Assert? | ALERT<br>Assert? |  |  |  |  |  |

| Thermal shutdown                     | Yes           | Yes              |  |  |  |  |  |

| Thermal warning                      | Yes           | Yes              |  |  |  |  |  |

| PMBus CRC error                      | Yes           | Yes              |  |  |  |  |  |

| PMBus<br>communication error         | Yes           | Yes              |  |  |  |  |  |

| Busy                                 | Yes           | Yes              |  |  |  |  |  |

| Force PG assertion<br>by register    | Yes           | No               |  |  |  |  |  |

| Force ALERT<br>assertion by register | No            | Yes              |  |  |  |  |  |

| VOUT_MAX/MIN<br>register warning     | Yes           | Yes              |  |  |  |  |  |

| OVP                                  | Yes           | Yes              |  |  |  |  |  |

| UVP                                  | Yes           | Yes              |  |  |  |  |  |

| PG threshold (OV)                    | Yes           | No               |  |  |  |  |  |

| PG threshold (UV)                    | Yes           | No               |  |  |  |  |  |

#### Table 1: PG and ALERT Response for Different Fault Types

#### **Output Over-Voltage Protection (OVP)**

If an output exceeds the OVP threshold, that output shuts off for the hiccup time, then the normal start-up sequence starts again. If enabled, the output discharge function works throughout the hiccup time.

#### Output Under-Voltage Protection (UVP)

If an output falls below the UVP threshold, that output shuts off for a hiccup time, then the normal start-up sequence starts again. If enabled, the output discharge function works throughout the hiccup time.

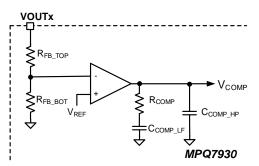

#### Compensation

The MPQ7930 integrates internal compensation for each buck output. The compensation can be adjusted via the OTP. If changes are made to the OTP values, these changes are made after the output is disabled then enabled again.

Figure 5 on page 33 shows a typical Type II compensation network that is fully integrated in the chip. The components' values can be configured via the PMBus.

Figure 5: Compensation Network

### **Frequency Spread Spectrum (FSS)**

Frequency spread spectrum (FSS) modulates the clock frequency with a triangle wave. The modulation range is typically 15%, and the frequency is 9kHz. This can be enabled or disabled via the PMBus. When FSS is enabled, the operating frequency drops from 2MHz to its minimum value, and then the operating frequency slowly increases. After reaching the maximum value, it slowly decreases again. When FSS is disabled, the operating frequency changes from its current value to 2MHz.

If the output voltage of any channel is below 0.8V, it is recommended to disable FSS. This reduces the output voltage ripple impact on PG, as caused by FSS.

### Thermal Warning and Shutdown

Thermal warning is indicated by asserting a bit in the thermal warning register and asserting the PG and ALERT pins. All rails can operate normally when the device triggers thermal warning, but not thermal shutdown.

Thermal shutdown disables the device until the temperature drops below the hysteresis point. PG and ALERT also assert in thermal shutdown.

### **PMBUS INTERFACE**

### **PMBus Serial Interface Description**

The power management bus (PMBus) is an open standard, power management protocol that defines a means of communication with power conversion and other devices. The PMBus is a two-wire, bidirectional serial interface, consisting of a serial data line (SDA) and a serial clock line (SCL). The lines are externally pulled to a bus voltage when they are idle. Connecting to the line, a master device generates the SCL signal and device address, then arranges the communication sequence. The MPQ7930 works as a slave-only device that supports both the standard mode (100kb/s) and fast mode (400kb/s) bidirectional data transfer, adding flexibility to the power supply solution. The output voltage, transition slew rate, and other converter parameters can be instantaneously controlled by the PMBus interface.

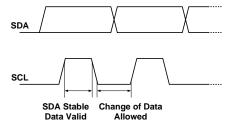

### **Data Validity**

One clock pulse is generated for each data bit transferred. The data on the SDA line must be stable during the high period of the clock. The high or low state of the SDA line can only change when the clock signal on the SCL line is low (see Figure 6).

Figure 6: Bit Transfer on the PMBus

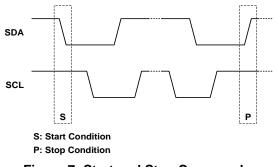

### Start and Stop Commands

The start and stop commands are signaled by the master device, which signifies the beginning and the end of the PMBus transfer. The start command (S) is defined as the SDA signal transitioning from high to low while the SCL line is high. The stop command (P) is defined as the SDA signal transitioning from low to high while the SCL is high (see Figure 7).

Figure 7: Start and Stop Commands

Start and stop commands are always generated by the master. The bus is considered busy after the start condition. The bus is considered free again after a certain time after the stop

condition. The bus stays busy if a repeated start (Sr) is generated instead of a stop command. The start and repeated start commands are functionally identical.

#### **Transfer Data**

Every byte put on the SDA line must be 8 bits long. Each byte must be followed by an acknowledge (ACK) bit. The acknowledgerelated clock pulse is generated by the master. The transmitter releases the SDA line (high) during the acknowledge clock pulse. The receiver must pull down the SDA line during the acknowledge clock pulse, so that it remains stable low during the high period of the clock pulse.

Figure 8 on page 34 shows the data transfer format. After the start command, a slave address is sent. This address is 7 bits long, followed by an eighth data direction bit (R/W). A 0 indicates a transmission (write), while a 1 indicates a request for data (read). A data transfer is always terminated by a stop command, which is generated by the master. However, if the master wants to continue to communicate on the bus, it can generate a repeated start command and address another slave without first generating a stop command.

Figure 8: A Complete Data Transfer

#### Packet Error Checking (PEC)

The packet error checking (PEC) mechanism is employed to improve communication reliability and robustness. Whenever applicable, PEC is implemented by appending a packet error code after the data of each message transfer.

The PEC is a CRC-8 error-checking byte, calculated on all the message bytes (including

addresses and read/write bits). The PEC is appended to the message by the device that supplied the last data byte.

If an incorrect PEC is received, a communications fault is triggered, and the PG flag and ALERT flag assert. The PG flag deasserts after the PG\_DELAY time. The ALERT de-asserts when the relevant fault register is cleared.

#### **PMBus Communication Failure**

A data transmission fault occurs when the data is not properly transferred between the devices. There are several data transmission faults, listed below:

- Sending too little data

- Reading too little data

- The host sends too many bytes

- The host reads too many bytes

- Improperly set read bit in the address byte

- Unsupported command code

The communication failure is recorded in the register STATUS\_CML.

#### Write/Read Sequence

All PMBus commands are supported by the MPQ7930, following the write/read sequence (see Figure 9 on page 35 and Figure 10 on page 35). Five commands can be implemented with or without PEC:

- 1. Send command only

- 2. Write byte

- 3. Write word

- 4. Read byte

- 5. Read word

If the master writes a command to a read-only register, the MPQ7930 performs the same action as if the host has sent too many bytes. If the master reads a command from a write-only register, the MPQ7930 performs the same action as the host would if it read too many bytes.

|                                                       |                                                  |                  |        | _   |                 |     | _                          | ,              |       |       |                                         |     |                |    |   |

|-------------------------------------------------------|--------------------------------------------------|------------------|--------|-----|-----------------|-----|----------------------------|----------------|-------|-------|-----------------------------------------|-----|----------------|----|---|

| 1)                                                    | S                                                | Slave Address    | Wr     | Α   | Command Code    | Α   | Ρ                          |                |       |       |                                         |     |                |    |   |

| 2)                                                    | S                                                | Slave Address    | Wr     | Α   | Command Code    | А   |                            | Data Byte A    | P     |       |                                         |     |                |    |   |

| <i>_</i> )                                            | 0                                                | Olave / Iddi 000 |        | ~   | Command Code    | ~   |                            | Bata Byte 7    |       |       |                                         |     |                |    |   |

| 3)                                                    | S                                                | Slave Address    | Wr     | А   | Command Code    | А   | Da                         | ata Byte Low   | Dat   | ta By | te High A P                             |     |                |    |   |

|                                                       |                                                  |                  |        |     |                 |     |                            |                |       | _     |                                         |     | <b>T</b>       |    |   |

| 4)                                                    | S                                                | Slave Address    | Wr     | A   | Command Code    | A   | S                          | Slave Address  | Rd    | Α     | Data Byte                               | NA  | Ρ              |    |   |

| 5)                                                    | S                                                | Slave Address    | Wr     | Α   | Command Code    | А   | s                          | Slave Address  | Rd    | Α     | Data Byte Low                           | A   | Data Byte High | NA | Р |

| ,                                                     | _                                                |                  |        |     |                 |     | _                          |                |       |       | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |     |                |    |   |

|                                                       | S = Start                                        |                  |        |     |                 |     |                            | Master to Slav | е     |       |                                         |     |                |    |   |

|                                                       |                                                  | P = Stop         |        |     |                 |     |                            | Slave to Maste | r     |       |                                         |     |                |    |   |

|                                                       | A = Acknowledge (ACK) Wr = Write (Bit Value = 0) |                  |        |     |                 |     |                            |                |       |       |                                         |     |                |    |   |

| NA = Not Acknowledge (NACK) Rd = Read (Bit Value = 1) |                                                  |                  |        |     |                 |     |                            |                |       |       |                                         |     |                |    |   |

| Figure 9: PMBus Write/Read Sequence without PEC       |                                                  |                  |        |     |                 |     |                            |                |       |       |                                         |     |                |    |   |

| 1)                                                    | S                                                | Slave Address    | wr     | A   | Command code    | A   |                            | PEC Byte A     | Р     |       |                                         |     |                |    |   |

| 1)                                                    | 3                                                | Slave Address    | VVI    | ~   | Command Code    |     |                            | FLC Byte       |       |       |                                         |     |                |    |   |

| 2)                                                    | S                                                | Slave Address    | Wr     | А   | Command Code    | А   |                            | Data Byte A    |       | PEC   | Byte A P                                |     |                |    |   |

|                                                       |                                                  |                  |        |     |                 |     |                            |                | _     |       |                                         |     |                |    |   |

| 3)                                                    | S                                                | Slave Address    | Wr     | A   | Command Code    | A   | Da                         | ata Byte Low   | Dat   | a By  | te High A F                             | PEC | Byte A P       |    |   |

| 4)                                                    | S                                                | Slave Address    | Wr     | А   | Command Code    | Α   | S                          | Slave Address  | Rd    | A     | Data Byte                               | А   | PEC Byte       | NA | Ρ |

|                                                       |                                                  |                  |        |     |                 |     |                            |                |       |       | -                                       |     |                |    |   |

| 5)                                                    | S                                                | Slave Address    | Wr     | А   | Command Code    | А   | S                          | Slave Address  | Rd    | А     | Data Byte Low                           | А   | Data Byte High | А  |   |

|                                                       |                                                  |                  |        |     |                 |     |                            |                |       |       |                                         | [   | PEC Byte       | NA | Ρ |

|                                                       |                                                  | S                | i = St | art |                 |     |                            | Master to      | Slave |       |                                         |     |                |    |   |

|                                                       |                                                  |                  | e St   | •   |                 |     | Slave to Master            |                |       |       |                                         |     |                |    |   |

|                                                       |                                                  |                  |        |     | owledge (ACK)   |     | Wr = Write (Bit Value = 0) |                |       |       |                                         |     |                |    |   |

|                                                       |                                                  | N                | IA = 1 | NOT | Acknowledge (NA | CK) |                            | Rd = Read (Bit | value | e = 1 | )                                       |     |                |    |   |

Figure 10: PMBus Write/Read Sequence with PEC

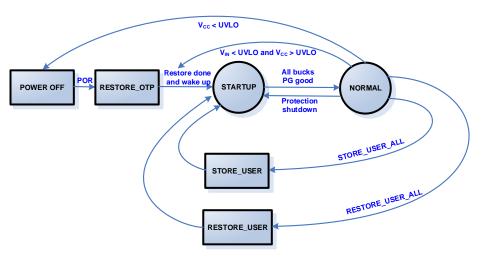

### STATE MACHINE DESCRIPTION

The state machine describes the different states of operation. The device has 6 states: power off (POWER OFF), restore OTP (RESTORE\_OTP), start-up (STARTUP), normal (NORMAL), store user (STORE\_USER), and restore user (RESTORE\_USER).

Figure 11 shows the state diagram. Each state is described in greater detail below.

Figure 11: System State Machine

#### Power Off State (POWER OFF)

The MPQ7930 is in the power off state if  $V_{CC}$  is below its UVLO threshold. All functions are disabled in this state.

#### **Restore OTP State (RESTORE\_OTP)**

When  $V_{CC}$  exceeds its rising UVLO threshold, the MPQ7930 enters the restore OTP state and begins to restore registers from the embedded OTP content data.

### Start-Up State (STARTUP)

After OTP is complete, and the wake-up signal is enabled, the device enters the start-up state. If the wake-up signal is enabled during RESTORE\_OTP, the MPQ7930 automatically enters the start-up state once the OTP is done being restored. In the start-up state, the other supplies are enabled and start to ramp up.

#### Normal State (NORMAL)

The MPQ7930 enters the normal state as soon as every output regulator voltage is detected to have a power good status. The normal state is the standard operating state for the MPQ7930, during which all relevant output regulators are up and running.

#### Store User State (STORE\_USER)