CMOS

**XPEXAR**

Very Low Power, 1 MSPS, 10-Bit Analog-to-Digital Converter with 8-Channel Mux

### FEATURES

- 10-Bit Resolution

- 8-Channel Mux

- Sampling Rates from <1 kHz to 1 MHz</li>

- Very Low Power CMOS 30 mW (typ)

- Power Down; Lower Consumption 3 mW (typ)

- Input Range between GND and V<sub>DD</sub>

- No S/H Required for Analog Signals less than 100 kHz

- No S/H Required for CCD Signals less than 1 MHz

- Single Power Supply (4 to 6 Volts)

- Latch-Up Free

- High ESD Protection: 4000 Volts Minimum

- 3 V Version: MP87L99

# BENEFITS

- Reduced Board Space (Small Package)

- Reduced External Parts, No Sample/Hold Needed

- Suitable for Battery & Power Critical Applications

- Designer can Adapt Input Range & Scaling

## APPLICATIONS

- µP/DSP Interface and Control Applications

- High Resolution Imaging Scanners & Copiers

- Wireless Digital Communications

- Multiplexed Data Acquisition

## **GENERAL DESCRIPTION**

The MP8799 is a flexible, easy to use, precision 10-bit Analog-to-Digital Converter with 8-channel mux that operates over a wide range of input and sampling conditions. The MP8799 can operate with pulsed "on demand" conversion operation or continuous "pipeline" operation for sampling rates up to 1 MHz. The elimination of the S/H requirements, very low power, and small package size offer the designer a low cost solution. No sample and hold is required for charge couple device applications up to 1 MHz, or multiplexed input applications when the signal source bandwidth is limited to 100 kHz. The input architecture of the MP8799 allows direct interface to any analog input range between AGND and AV<sub>DD</sub> (0 to 2 V, 1 to 4 V, 0 to 5 V, etc.). The user simply sets V<sub>REF(+)</sub> and V<sub>REF(-)</sub> to encompass the desired input range.

Scaled reference resistor tap @ 1/4 R, 1/2 R and 3/4 R allows for customizing the transfer curve as well as providing a 1/2 span reference voltage. Digital outputs are CMOS and TTL compatible.

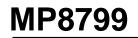

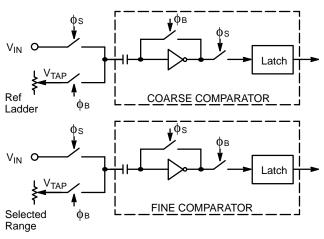

The MP8799 uses a two-step flash technique. The first segment converts the 4 MSBs and consists of 15 autobalanced comparators, latches, an encoder, and buffer storage registers. The second segment converts the remaining 6 LSBs.

When the power down input is "high", the data outputs DB9 to DB0 hold the current values and  $V_{REF(-)}$  is disconnected from  $V_{REF1(-)}$ . The power consumption during the power down mode is approximately 3mW.

## **ORDERING INFORMATION**

| Package | Temperature  | Part No. | DNL   | INL   |

|---------|--------------|----------|-------|-------|

| Type    | Range        |          | (LSB) | (LSB) |

| PQFP    | –40 to +85°C | MP8799AE | ±1    | 2     |

SIMPLIFIED BLOCK AND TIMING DIAGRAM

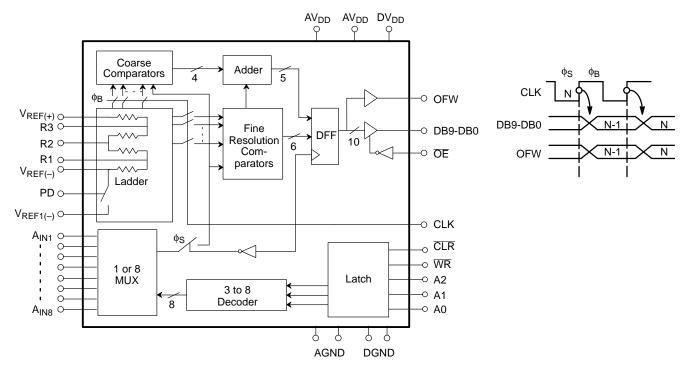

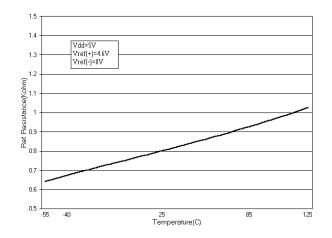

# **PIN CONFIGURATIONS**

See Packaging Section for Package Dimensions

44-Pin PQFP (10mm x 10mm) QN44

# **PIN OUT DEFINITIONS**

| PIN NO. | NAME                 | DESCRIPTION                | ] | PIN NO. | NAME             | DESCRIPTION             |

|---------|----------------------|----------------------------|---|---------|------------------|-------------------------|

| 1       | DB6                  | Data Output Bit 6          | 1 | 23      | R3               | Reference Ladder Tap    |

| 2       | DB7                  | Data Output Bit 7          |   | 24      | N/C              | No Connect              |

| 3       | DGND                 | Digital Ground             |   | 25      | A <sub>IN1</sub> | Analog Signal Input 1   |

| 4       | DGND                 | Digital Ground             |   | 26      | A <sub>IN2</sub> | Analog Signal Input 2   |

| 5       | DV <sub>DD</sub>     | Digital V <sub>DD</sub>    |   | 27      | A <sub>IN3</sub> | Analog Signal Input 3   |

| 6       | CLR                  | Clear (Active Low)         |   | 28      | A <sub>IN4</sub> | Analog Signal Input 4   |

| 7       | WR                   | Write (Active Low)         |   | 29      | A <sub>IN5</sub> | Analog Signal Input 5   |

| 8       | A2                   | Address 2                  |   | 30      | AGND             | Analog Ground           |

| 9       | A1                   | Address 1                  |   | 31      | $AV_{DD}$        | Analog V <sub>DD</sub>  |

| 10      | A0                   | Address 0                  |   | 32      | $AV_{DD}$        | Analog V <sub>DD</sub>  |

| 11      | CLK                  | Clock Input                |   | 33      | A <sub>IN6</sub> | Analog Signal Input 6   |

| 12      | ŌĒ                   | Output Enable (Active Low) |   | 34      | AGND             | Analog Ground           |

| 13      | N/C                  | No Connect                 |   | 35      | PD               | Power Down              |

| 14      | DB8                  | Data Output Bit 8          |   | 36      | A <sub>IN7</sub> | Analog Signal Input 7   |

| 15      | DB9                  | Data Output Bit 9 (MSB)    |   | 37      | DB0              | Data Output Bit 0 (LSB) |

| 16      | OFW                  | Overflow Output            |   | 38      | DB1              | Data Output Bit 1       |

| 17      | V <sub>REF(+)</sub>  | Upper Reference Voltage    |   | 39      | DB2              | Data Output Bit 2       |

| 18      | V <sub>REF(-)</sub>  | Lower Reference Voltage    |   | 40      | DB3              | Data Output Bit 3       |

| 19      | V <sub>REF1(-)</sub> | Lower Reference Voltage    |   | 41      | DB4              | Data Output Bit 4       |

| 20      | R1                   | Reference Ladder Tap       |   | 42      | DB5              | Data Output Bit 5       |

| 21      | R2                   | Reference Ladder Tap       |   | 43      | N/C              | No Connect              |

| 22      | A <sub>IN8</sub>     | Analog Signal Input 8      |   | 44      | N/C              | No Connect              |

# TRUTH TABLE FOR INPUT CHANNEL SELECTION

| CLR | WR | A2 | A1 | A0 | Selected<br>Analog Input |

|-----|----|----|----|----|--------------------------|

| L   | Х  | Х  | Х  | Х  | A <sub>IN1</sub>         |

| н   | L  | L  | L  | L  | A <sub>IN1</sub>         |

| н   | L  | L  | L  | Н  | A <sub>IN2</sub>         |

| н   | L  | L  | н  | L  | A <sub>IN3</sub>         |

| н   | L  | L  | н  | Н  | A <sub>IN4</sub>         |

| н   | L  | Н  | L  | L  | A <sub>IN5</sub>         |

| н   | L  | Н  | L  | Н  | A <sub>IN6</sub>         |

| н   | L  | Н  | н  | L  | A <sub>IN7</sub>         |

| н   | L  | н  | н  | н  | A <sub>IN8</sub>         |

| Н   | Н  | х  | х  | х  | Previous<br>Selection    |

Note:  $\overline{CLR}$ ,  $\overline{WR}$ , A2, A1, A0 are internally connected to ground through 500k $\Omega$  resistance.

# ELECTRICAL CHARACTERISTICS TABLE

Unless Otherwise Specified:  $AV_{DD} = DV_{DD} = 5 V$ ,  $F_S = 1 MHz$  (50% Duty Cycle),

$V_{REF(+)} = 4.6, V_{REF(-)} = AGND, T_A = 25^{\circ}C$

|                                           |                                 |                     | 25°C  |                     |        |                                             |

|-------------------------------------------|---------------------------------|---------------------|-------|---------------------|--------|---------------------------------------------|

| Parameter                                 | Symbol                          | Min                 | Тур   | Max                 | Units  | Test Conditions/Comments                    |

| KEY FEATURES                              |                                 |                     |       |                     |        |                                             |

| Resolution                                |                                 | 10                  |       |                     | Bits   |                                             |

| Sampling Rate                             | F <sub>S</sub>                  | .001                |       | 1                   | MHz    | For Rated Performance                       |

| ACCURACY (A Grade) <sup>2</sup>           |                                 |                     |       |                     |        |                                             |

| Differential Non-Linearity                | DNL                             |                     |       | <u>+</u> 1          | LSB    | LSB                                         |

| Integral Non-Linearity                    | INL                             |                     |       | 2                   | LSB    | Best Fit Line<br>(Max INL – Min INL)/2      |

| Zero Scale Error                          | EZS                             |                     | +0.50 |                     | LSB    | Reference from $V_{REF(+)}$ to $V_{REF(-)}$ |

| Full Scale Error                          | EFS                             |                     | -2.5  |                     | LSB    |                                             |

| REFERENCE VOLTAGES                        |                                 |                     |       |                     |        |                                             |

| Positive Ref. Voltage                     | V <sub>REF(+)</sub>             |                     |       | AV <sub>DD</sub>    | V      |                                             |

| Negative Ref. Voltage                     | V <sub>REF(-)</sub>             | AGND                |       |                     | V      |                                             |

| Differential Ref. Voltage <sup>5</sup>    | V <sub>REF</sub>                | 0.5                 |       | AV <sub>DD</sub>    | V      |                                             |

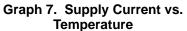

| Ladder Resistance                         | RL                              | 525                 | 675   | 900                 | Ω      |                                             |

| Ladder Temp. Coefficient <sup>1</sup>     | R <sub>TCO</sub>                |                     | 2000  |                     | ppm/°C |                                             |

| Ladder Switch Resistance <sup>1</sup>     |                                 |                     | 12    |                     | Ω      |                                             |

| Ladder Switch Off Leakage <sup>1</sup>    | I <sub>ILKG-SW</sub>            |                     | 50    |                     | nA     |                                             |

| ANALOG INPUT <sup>1</sup>                 |                                 |                     |       |                     |        |                                             |

| Input Bandwidth                           |                                 |                     | 100   |                     | kHz    |                                             |

| Input Voltage Range <sup>7</sup>          | V <sub>IN</sub>                 | V <sub>REF(-)</sub> |       | V <sub>REF(+)</sub> | V      |                                             |

| Input Capacitance <sup>3</sup>            | C <sub>IN</sub>                 | ( )                 | 60    | ( )                 | pF     |                                             |

| Aperture Delay                            | t <sub>AP</sub>                 |                     | 35    | 45                  | ns     |                                             |

| DIGITAL INPUTS                            |                                 |                     |       |                     |        |                                             |

| Logical "1" Voltage                       | VIH                             | 2.0                 |       |                     | V      |                                             |

| Logical "0" Voltage                       | VIL                             |                     |       | 0.8                 | V      |                                             |

| Leakage Currents                          | I <sub>IN</sub>                 |                     |       |                     |        | V <sub>IN</sub> =DGND to DV <sub>DD</sub>   |

| CLK                                       |                                 |                     |       | <u>+</u> 100        | μA     |                                             |

| PD, OE (Internal Res to DGND)             |                                 | -5                  |       | 30                  | μΑ     |                                             |

| Input Capacitance                         |                                 |                     | 5     |                     | pF     |                                             |

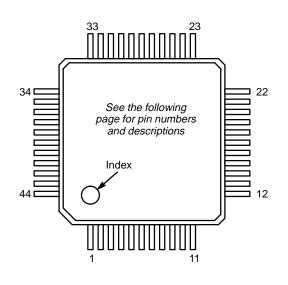

| Clock Timing (See Figure 1.) <sup>1</sup> |                                 |                     |       |                     |        |                                             |

| Clock Period                              | Τ <sub>S</sub>                  | 1000                |       |                     | ns     |                                             |

| Rise & Fall Time <sup>4</sup>             | t <sub>R</sub> , t <sub>F</sub> |                     |       | 10                  | ns     |                                             |

| "High" Time <sup>6</sup>                  | t <sub>B</sub>                  | 250                 |       | 500,000             | ns     |                                             |

| "Low" Time <sup>6</sup>                   | ts                              | 150                 |       | 500,000             | ns     |                                             |

|                                           |                                 |                     |       |                     |        |                                             |

# ELECTRICAL CHARACTERISTICS TABLE (CONT'D)

|                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                |                                             | 25°C          |                                           |                                                              |                                                                                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|---------------------------------------------|---------------|-------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| Parameter                                                                                                                                                                                                                                                                                                                                                                                                  | Symbol                                                                         | Min                                         | Тур           | Max                                       | Units                                                        | Test Conditions/Comments                                                                         |

| DIGITAL OUTPUTS                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                |                                             |               |                                           |                                                              | C <sub>OUT</sub> =15 pF                                                                          |

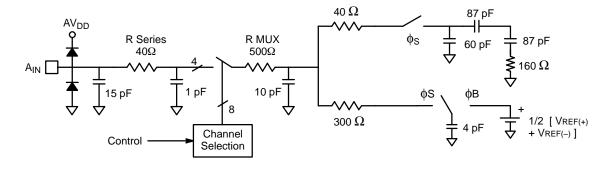

| Logical "1" Voltage<br>Logical "0" Voltage<br>Tristate Leakage<br>Data Hold Time ( <i>See</i> Figure 1.) <sup>1</sup><br>Data Valid Delay <sup>1</sup><br>Write Pulse Width <sup>1</sup><br>Multiplexer Address Setup Time <sup>1</sup><br>Multiplexer Address Hold Time <sup>1</sup><br>Delay from WR to Multiplexer <sup>1</sup><br>Enable<br>Power Down Time <sup>1</sup><br>Power Up Time <sup>1</sup> | Voh<br>Vol<br>loz<br>thld<br>tdl<br>twr<br>tas<br>tah<br>tmuxen1<br>tpd<br>tpu | DV <sub>DD</sub> -0.5<br>0<br>40<br>80<br>0 | 30<br>35      | 0.4<br>±5<br>35<br>45<br>80<br>300<br>200 | V<br>V<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns | I <sub>LOAD</sub> = 2 mA<br>I <sub>LOAD</sub> = 4 mA<br>V <sub>OUT</sub> = 0 to DV <sub>DD</sub> |

| POWER SUPPLIES <sup>8</sup>                                                                                                                                                                                                                                                                                                                                                                                |                                                                                |                                             |               |                                           |                                                              |                                                                                                  |

| Power Down (I <sub>DD</sub> )<br>Operating Voltage (AV <sub>DD</sub> , DV <sub>DD</sub> )<br>Current (AV <sub>DD</sub> + DV <sub>DD</sub> )                                                                                                                                                                                                                                                                | I <sub>PD-DD</sub><br>V <sub>DD</sub><br>I <sub>DD</sub>                       | 4                                           | 0.6<br>5<br>6 | 1.2<br>6.5<br>10                          | mA<br>V<br>mA                                                | V <sub>IN</sub> = 2 V                                                                            |

NOTES:

Guaranteed. Not tested.

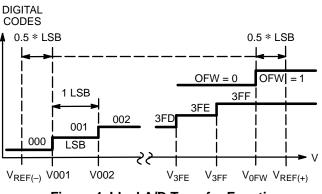

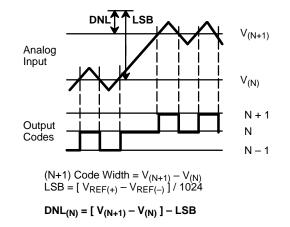

2 Tester measures code transition voltages by dithering the voltage of the analog input (V<sub>IN</sub>). The difference between the measured code width and the ideal value (V<sub>REF</sub>/1024) is the DNL error (see Figure 4.). The INL error is the maximum distance (in LSBs) from the best fit line to any transition voltage (See Figure 7.).

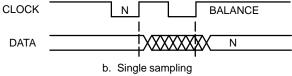

3 See V<sub>IN</sub> input equivalent circuit (see Figure 9.).

Clock specification to meet aperture specification (t<sub>AP</sub>). Actual rise/fall time can be less stringent with no loss of accuracy. Specified values guarantee functional device. Refer to other parameters for accuracy. 4

5

6 System can clock MP8799 with any duty cycle as long as all timing conditions are met.

7 Input range where input is converted correctly into binary code. Input voltage outside specified range converts to zero or full scale output.

8 DV<sub>DD</sub> and AV<sub>DD</sub> are connected through the silicon substrate. Connect together at the package.

Specifications are subject to change without notice

## ABSOLUTE MAXIMUM RATINGS (TA = +25°C unless otherwise noted)<sup>1, 2, 3</sup>

| V <sub>DD</sub> (to GND)                                           | +7 V                               |

|--------------------------------------------------------------------|------------------------------------|

| V <sub>REF(+)</sub> , V <sub>REF(-)</sub> , V <sub>REF1(-)</sub> , | GND –0.5 to V_DD +0.5 V            |

| All A <sub>INs</sub>                                               | GND –0.5 to V_DD +0.5 V            |

| All Inputs                                                         | GND –0.5 to V_DD +0.5 V            |

| All Outputs                                                        | GND –0.5 to V <sub>DD</sub> +0.5 V |

| Storage Temperature                            |

|------------------------------------------------|

| Lead Temperature (Soldering 10 seconds) +300°C |

| Package Power Dissipation Rating to 75°C       |

| PQFP 450mW                                     |

| Derates above 75°C 14mW/°C                     |

#### NOTES:

- Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation at or above this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

- 2 Any input pin which can see a value outside the absolute maximum ratings should be protected by Schottky diode clamps (HP5082-2835) from input pin to the supplies. All inputs have protection diodes which will protect the device from short transients outside the supplies of less than 100mA for less than 100 $\mu$ s. V<sub>DD</sub> refers to AV<sub>DD</sub> and DV<sub>DD</sub>. GND refers to AGND and DGND. 3

Figure 1. MP8799 Timing Diagram

## THEORY OF OPERATION

#### **Analog-to-Digital Conversion**

The MP8799 converts analog voltages into 1024 digital codes by encoding the outputs of 15 coarse and 67 fine comparators. Digital logic is used to generate the overflow bit. The conversion is synchronous with the clock and it is accomplished in 2 clock periods.

The reference resistance ladder is a series of 1025 resistors. The first and the last resistor of the ladder are half the value of the others so that the following relations apply:

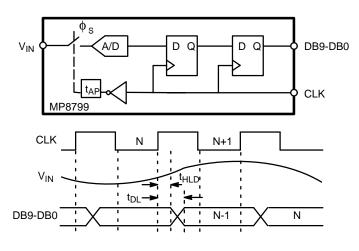

$\begin{array}{ll} R_{REF} = 1024 * R & V_{REF} = V_{REF(+)} - V_{REF(-)} = 1024 * LSB \\ \mbox{The clock signal generates the two internal phases, } \varphi_B (CLK \\ \mbox{high}) \mbox{ and } \varphi_S (CLK \mbox{ low} = sample) (See Figure 2.). The rising \\ \mbox{edge of the CLK input marks the end of the sampling phase } (\varphi_S). \\ \mbox{Internal delay of the clock circuitry will delay the actual instant} \end{array}$

when  $\varphi_S$  disconnects the latches from the comparators. This delay is called aperture delay (t\_{AP}).

The coarse comparators make the first pass conversion and selects a ladder range for the fine comparators. The fine comparators are connected to the selected range during the next  $\varphi_B$  phase.

Figure 2. MP8799 Comparators

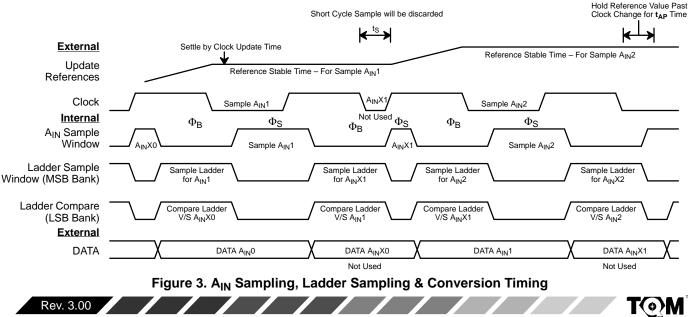

#### AIN Sampling, Ladder Sampling, and Conversion Timing

Figure 3. shows this relationship as a timing chart. A<sub>IN</sub> sampling, ladder sampling and output data relationships are shown for the general case where the levels which drive the ladder need to change for each sampled A<sub>IN</sub> time point. The ladder is referenced for both last A<sub>IN</sub> sample and next A<sub>IN</sub> sample at the same time. If the ladder's levels change by more than 1 LSB, one of the samples must be discarded. Also note that the clock low period for the discarded A<sub>IN</sub> can be reduced to the minimum t<sub>S</sub> time of 150 ns.

6

#### Accuracy of Conversion: DNL and INL

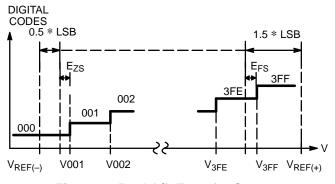

The transfer function for an ideal A/D converter is shown in *Figure 4.*

The overflow transition (V<sub>OFW</sub>) takes place at:

$V_{IN} = V_{OFW} = V_{REF(+)} - 0.5 * LSB$

The first and the last transitions for the data bits take place at:

$V_{IN} = V001 = V_{REF(-)} + 0.5 * LSB$

$V_{IN} = V_{3FF} = V_{REF(-)} - 1.5 * LSB$

LSB = V<sub>REF</sub> / 1024 = (V<sub>3FF</sub> - V001) / 1022

Note that the overflow transition is a flag and has no impact on the data bits.

In a "real" converter the code-to-code transitions don't fall exactly every  $V_{REF}/1024$  volts.

A positive DNL (Differential Non-Linearity) error means that the real width of a particular code is larger than 1 LSB. This error is measured in fractions of LSBs.

A Max DNL specification guarantees that ALL code widths (DNL errors) are within the stated value. A specification of Max DNL =  $\pm$  0.5 LSB means that all code widths are within 0.5 and 1.5 LSB. If V<sub>REF</sub> = 4.608 V then 1 LSB = 4.5 mV and every code width is within 2.25 and 6.75 mV.

### Figure 5. DNL Measurement On Production Tester

The formulas for Differential Non-linearity (DNL), Integral Non-Linearity (INL) and zero and full scale errors ( $E_{ZS}$ ,  $E_{FS}$ ) are:

DNL (001) = V002 - V001 - LSB

:::

$\mathsf{DNL}(\mathsf{3FE}) = \mathsf{V}_{\mathsf{3FF}} - \mathsf{V}_{\mathsf{3FE}} - \mathsf{LSB}$

$E_{FS}$  (full scale error) =  $V_{3FF} - [V_{REF(+)} - 1.5 * LSB]$

$E_{ZS}$  (zero scale error) =  $V_{001} - [V_{REF(-)} + 0.5 * LSB]$

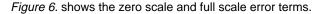

*Figure 7.* gives a visual definition of the INL error. The chart shows a 3-bit converter transfer curve with greatly exaggerated DNL errors to show the deviation of the real transfer curve from the ideal one.

After a tester has measured all the transition voltages, the computer draws a line parallel to the ideal transfer line. By definition the best fit line makes equal the positive and the negative INL errors. For example, an INL error of -1 to +2 LSB's relative to the Ideal Line would be  $\pm 1.5$  LSB's relative to the best fit line.

Figure 7. INL Error Calculation

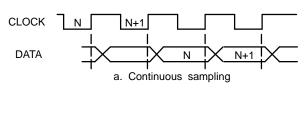

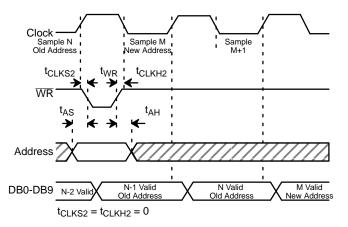

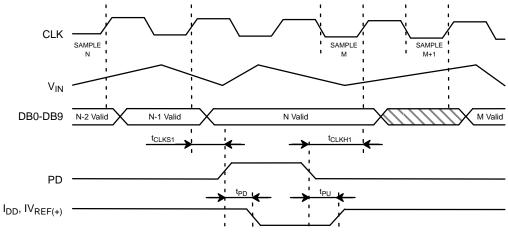

## **Clock and Conversion Timing**

A system will clock the MP8799 continuously or it will give clock pulses intermittently when a conversion is desired. The timing of *Figure 8a* shows normal operation, while the timing of *Figure 8b* keeps the MP8799 in balance and ready to sample the analog input.

Figure 8. Relationship of Data to Clock

#### **Analog Input**

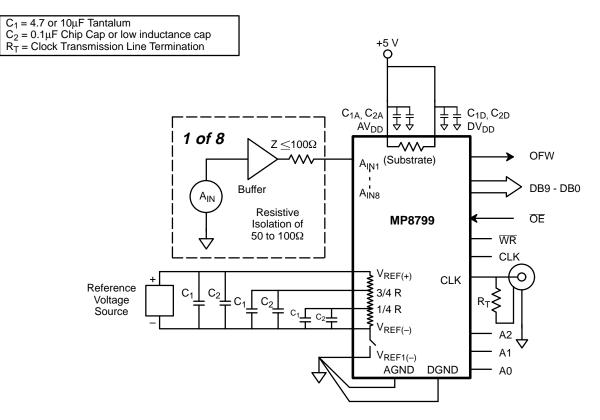

The MP8799 has very flexible input range characteristics. The user may set  $V_{REF(+)}$  and  $V_{REF(-)}$  to two fixed voltages and then vary the input DC and AC levels to match the  $V_{REF}$  range. Another method is to first design the analog input circuitry and then adjust the reference voltages for the analog input range. One advantage is that this approach may eliminate the need for external gain and offset adjust circuitry which may be required by fixed input range A/Ds.

The MP8799's performance is optimized by using analog input circuitry that is capable of driving the  $A_{IN}$  input. *Figure 9.* shows the equivalent circuit for  $A_{IN}$ .

Figure 9. Analog Input Equivalent Circuit

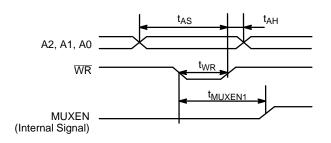

## Analog Input Multiplexer

The MP8799 includes a 8-Channel analog input multiplexer. The relationship between the clock, the multiplexer address, the  $\overline{\text{WR}}$  and the output data is shown in *Figure 10.*

Figure 10. MUX Address Timing

Figure 11. Analog MUX Timing

### **Reference Voltages**

The input/output relationship is a function of V<sub>REF</sub>:

$$\begin{aligned} A_{IN} &= V_{IN} - V_{REF(-)} \\ V_{REF} &= V_{REF(+)} - V_{REF(-)} \\ DATA &= 1023 * (A_{IN}/V_{REF}) \end{aligned}$$

A system can increase total gain by reducing V<sub>REF</sub>.

## **Digital Interfaces**

The logic encodes the outputs of the comparators into a binary code and latches the data in a D-type flip-flop for output.

The functional equivalent of the MP8799 (*Figure 12.*) is composed of:

- 1) Delay stage  $(t_{AP})$  from the clock to the sampling phase  $(\phi_S)$ .

- 2) An ideal analog switch which samples  $V_{IN}$ .

- An ideal A/D which tracks and converts V<sub>IN</sub> with no delay.

- A series of two DFF's with specified hold (t<sub>HLD</sub>) and delay (t<sub>DL</sub>) times.

$t_{AP}, t_{HLD} \, and \, t_{DL}$  are specified in the Electrical Characteristics table.

Figure 12. MP8799 Functional Equivalent Circuit and Interface Timing

#### **Power Down**

Figure 13. shows the relationship between the clock, sampled  $A_{\rm IN}$  to output data relationship and the effect of power down.

Figure 13. Power Down Timing Diagram

APPLICATION NOTES

Figure 14. Typical Circuit Connections

The following information will be useful in maximizing the performance of the MP8799.

- All signals should not exceed AV<sub>DD</sub> +0.5 V or AGND -0.5 V or DV<sub>DD</sub> +0.5 V or DGND -0.5 V.

- 2. Any input pin which can see a value outside the absolute maximum ratings (AV<sub>DD</sub> or DV<sub>DD</sub>+0.5 V or AGND -0.5 V) should be protected by diode clamps (HP5082-2835) from input pin to the supplies. All MP8799 inputs have input protection diodes which will protect the device from short transients outside the supply ranges.

- The design of a PC board will affect the accuracy of MP8799. 3. Use of wire wrap is not recommended.

- 4. The analog input signal (VIN) is quite sensitive and should be properly routed and terminated. It should be shielded from the clock and digital outputs so as to minimize cross coupling and noise pickup.

- 5. The analog input should be driven by a low impedance (less than 50 $\Omega$ ).

- 6. Analog and digital ground planes should be substantial and common at one point only. The ground plane should act as a Rev. 3.00

shield for parasitics and not a return path for signals. To reduce noise levels, use separate low impedance ground paths. DGND should not be shared with other digital circuitry. If separate low impedance paths cannot be provided, DGND should be connected to AGND next to the MP8799.

- 7. DV<sub>DD</sub> should not be shared with other digital circuitry to avoid conversion errors caused by digital supply transients. DV<sub>DD</sub> for the MP8799 should be connected to AV<sub>DD</sub> next to the MP8799.

- 8. DV<sub>DD</sub> and AV<sub>DD</sub> are connected inside the MP8799 through the N - doped silicon substrate. Any DC voltage difference between DV<sub>DD</sub> and AV<sub>DD</sub> will cause undesirable internal currents.

- 9. Each power supply and reference voltage pin should be decoupled with a ceramic  $(0.1\mu F)$  and a tantalum  $(10\mu F)$  capacitor as close to the device as possible.

- 10. The digital output should not drive long wires. The capacitive coupling and reflection will contribute noise to the conversion. When driving distant loads, buffers should be used.  $100\Omega$  resistors in series with the digital outputs in some applications reduces the digital output disruption of AIN.

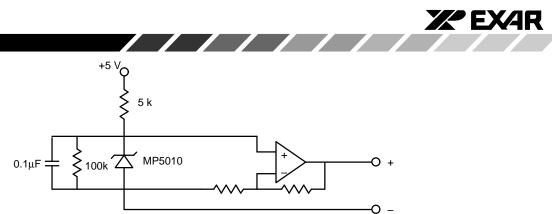

Figure 15. Example of a Reference Voltage Source

For R = 5k use Beckman Instruments #694-3-R10k resistor array or equivalent.

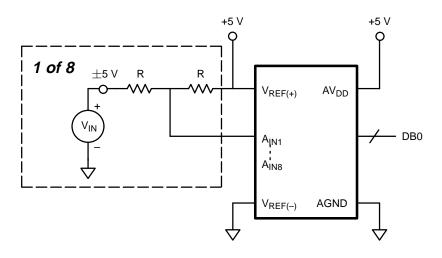

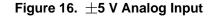

NOTE: High R values affect the input BW of ADC due to the ( $R * C_{IN}$  of ADC) time constant. Therefore, for different applications the R value needs to be selected as a tradeoff between  $A_{IN}$  settling time and power dissipation.

For R = 5k use Beckman Instruments #694-3-R10k resistor array or equivalent. NOTE: High R values affect the input BW of ADC due to the (R \* C<sub>IN</sub> of ADC) time constant. Therefore, for different applications the R value needs to be selected as a tradeoff between A<sub>IN</sub> settling time and power dissipation.

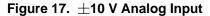

@ Power Down write values to DAC 3, 2, 1 = DAC 4 to minimize power consumption.  $Only A_{IN}$  and Ladder detail shown.

Figure 18. A/D Ladder and  $A_{IN}$  with Programmed Control (of  $V_{REF(+),}$   $V_{REF(-),}$  1/4 and 3/4 TAP.)

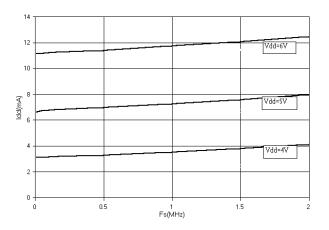

Vdd=6V

Vdd=5V

Vdd=4V

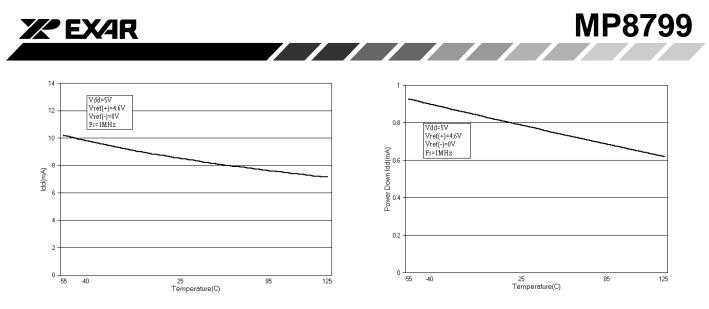

# PERFORMANCE CHARACTERISTICS

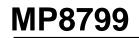

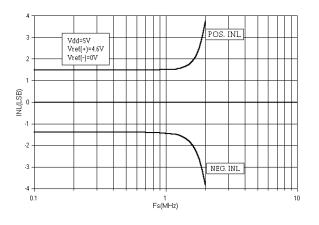

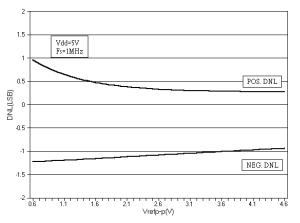

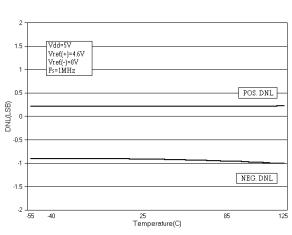

Graph 1. DNL vs. Sampling Frequency

Graph 2. INL vs. Sampling Frequency

Graph 4. Power Down Current vs.

**Sampling Frequency**

0.8

Power Down Idd(mA) 9.0

0.2

0.

0

www.DataSheet.in

Graph 8. Power Down Current vs. Temperature

Graph 9. Reference Resistance vs. Temperature

# 44 LEAD PLASTIC QUAD FLAT PACK (10mm X 10mm PQFP, METRIC) QN44

|                          | MILLI | METERS | INC   | CHES   |  |  |

|--------------------------|-------|--------|-------|--------|--|--|

| SYMBOL                   | MIN   | MAX    | MIN   | MAX    |  |  |

| А                        |       | 2.45   |       | 0.096  |  |  |

| A <sub>1</sub>           | 0.25  | _      | 0.01  | _      |  |  |

| A <sub>2</sub>           | 1.9   | 2.1    | 0.100 | 0.108  |  |  |

| В                        | 0.3   | 0.4    | 0.012 | 0.018  |  |  |

| С                        | 0.13  | 0.23   | 0.005 | 0.009  |  |  |

| D                        | 12.95 | 13.45  | 0.510 | 0.530  |  |  |

| D <sub>1</sub>           | 9.9   | 10.1   | 0.392 | 0.396  |  |  |

| е                        | 0.8   | BSC    | 0.03  | 15 BSC |  |  |

| L                        | 0.65  | 1.03   | 0.026 | 0.037  |  |  |

| α                        | 0°    | 7°     | 0°    | 7°     |  |  |

| Coplanarity = 4 mil max. |       |        |       |        |  |  |

www.DataSheet.ir

Notes

Notes

Notes

## NOTICE

EXAR Corporation reserves the right to make changes to the products contained in this publication in order to improve design, performance or reliability. EXAR Corporation assumes no responsibility for the use of any circuits described herein, conveys no license under any patent or other right, and makes no representation that the circuits are free of patent infringement. Charts and schedules contains here in are only for illustration purposes and may vary depending upon a user's specific application. While the information in this publication has been carefully checked; no responsibility, however, is assumed for inaccuracies.

EXAR Corporation does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless EXAR Corporation receives, in writing, assurances to its satisfaction that: (a) the risk of injury or damage has been minimized; (b) the user assumes all such risks; (c) potential liability of EXAR Corporation is adequately protected under the circumstances.

Copyright 1993 EXAR Corporation Datasheet April 1995 Reproduction, in part or whole, without the prior written consent of EXAR Corporation is prohibited.