# **MP7626**

Microprocessor Compatible Buffered Multiplying 16-Bit Digital-to-Analog Converter

# FEATURES C

• Four Quadrant Multiplication

X EXA

- 16-Bit Monotonicity

- Low Power Consumption

- TTL/5 V CMOS Compatible

- Single-Buffered or Transparent Data inputs

- Decoded DAC Approach

- Latch-Up Free

- 8-Bit Bus Version: MP7636A

# APPLICATIONS

- Digitally Programmable References

- Programmable Audio Attenuator

- High Accuracy Process Control Systems

- Automatic Test Equipment

- Easy Interface to 8 and 16-Bit Microprocessor Buses

# **GENERAL DESCRIPTION**

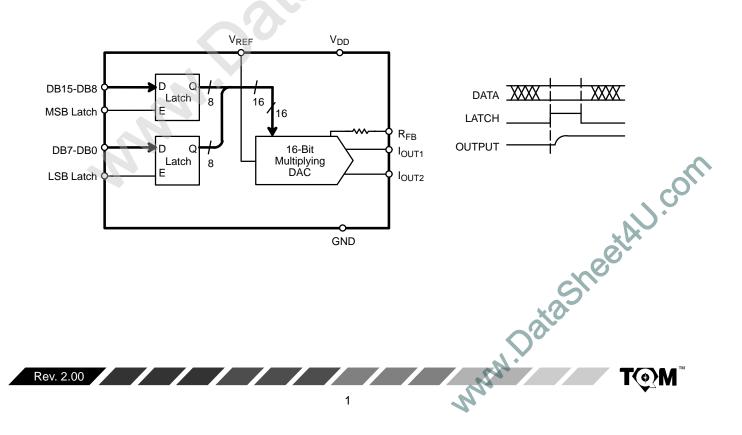

The MP7626 is a CMOS 16-bit Digital-to-Analog Converter (DAC) that is manufactured using advanced thin film resistors on a double metal CMOS process. It incorporates a unique bit decoding technique yielding lower glitch, higher speed and

excellent accuracy over temperature and time. 16 bit differential non-linearity is achieved with minimal trimming.

Two 8-bit latches (MSB latch and LSB latch) hold the 16-bit data which are converted by the DAC. A 16-bit bus can load both latches in one cycle. An 8-bit bus loads one latch at a time. By making the latches transparent (MSB latch = LSB latch = High) the DAC will continuously convert the BIT1 - BIT16 inputs.

## SIMPLIFIED BLOCK AND TIMING DIAGRAM

# **ORDERING INFORMATION**

| Package<br>Type | Temperature<br>Range | Part No.  | INL<br>(LSB) | DNL<br>(LSB) | Gain Error<br>(% FSR) |

|-----------------|----------------------|-----------|--------------|--------------|-----------------------|

| Plastic Dip     | –40 to +85°C         | MP7626JN  | <u>+</u> 4   | <u>+</u> 4   | <u>+</u> 0.1          |

| Plastic Dip     | –40 to +85°C         | MP7626KN  | <u>+</u> 2   | <u>+</u> 2   | <u>+</u> 0.1          |

| PLCC            | –40 to +85°C         | MP7626JP  | <u>+</u> 4   | <u>+</u> 4   | <u>+</u> 0.1          |

| PLCC            | –40 to +85°C         | MP7626KP  | <u>+</u> 2   | <u>+</u> 2   | <u>+</u> 0.1          |

| Ceramic Dip     | –40 to +85°C         | MP7626JD* | <u>+</u> 4   | <u>+</u> 4   | <u>+</u> 0.1          |

| Ceramic Dip     | –40 to +85°C         | MP7626KD* | <u>+</u> 2   | <u>+</u> 2   | <u>+</u> 0.1          |

\*Recommend using MP7626KN or JN

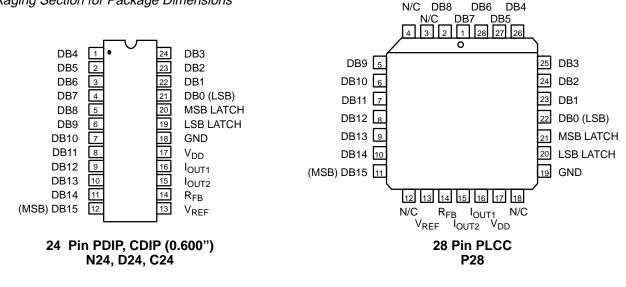

## **PIN CONFIGURATION**

See Packaging Section for Package Dimensions

#### **PIN OUT DEFINITIONS**

| DIP | PLCC | NAME | DESCRIPTION             | DIP | PLCC | NAME              | DESCRIPTION                    |

|-----|------|------|-------------------------|-----|------|-------------------|--------------------------------|

| 1   | 26   | DB4  | Data Input Bit 4        | 13  | 13   | V <sub>REF</sub>  | Reference Input Voltage        |

| 2   | 27   | DB5  | Data Input Bit 5        | 14  | 14   | R <sub>FB</sub>   | Internal Feedback Resistor Pin |

| 3   | 28   | DB6  | Data Input Bit 6        | 15  | 15   | I <sub>OUT2</sub> | Current Output 2               |

| 4   | 1    | DB7  | Data Input Bit 7        | 16  | 16   | I <sub>OUT1</sub> | Current Output 1               |

| 5   | 2    | DB8  | Data Input Bit 8        | 17  | 17   | V <sub>DD</sub>   | Power Supply                   |

| 6   | 5    | DB9  | Data Input Bit 9        | 18  | 19   | GND               | Ground                         |

| 7   | 6    | DB10 | Data Input Bit 10       | 19  | 20   | LSB               | LSB Latch Enable               |

| 8   | 7    | DB11 | Data Input Bit 11       | 20  | 21   | MSB               | MSB Latch Enable               |

| 9   | 8    | DB12 | Data Input Bit 12       | 21  | 22   | DB0               | Data Input Bit 0 (LSB)         |

| 10  | 9    | DB13 | Data Input Bit 13       | 22  | 23   | DB1               | Data Input Bit 1               |

| 11  | 10   | DB14 | Data Input Bit 14       | 23  | 24   | DB2               | Data Input Bit 2               |

| 12  | 11   | DB15 | Data Input Bit 15 (MSB) | 24  | 25   | DB3               | Data Input Bit 3               |

# **ELECTRICAL CHARACTERISTICS**

(VDD = + 15 V, VREF = +10 V unless otherwise noted)

| Parameter                                                                                                                | Symbol                                                                    | Min | 25 <sup>°</sup> С<br>Тур | Max                      | Tmin to<br>Min | Tmax<br>Max              | Units                    | Test Conditions/Comments                                                             |

|--------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|-----|--------------------------|--------------------------|----------------|--------------------------|--------------------------|--------------------------------------------------------------------------------------|

| STATIC PERFORMANCE <sup>1</sup>                                                                                          |                                                                           |     |                          |                          |                |                          |                          | FSR = Full Scale Range                                                               |

| Resolution (All Grades)                                                                                                  | N                                                                         | 16  |                          |                          | 16             |                          | Bits                     |                                                                                      |

| Relative Accuracy<br>J<br>K                                                                                              | INL                                                                       |     |                          | <u>+</u> 4<br><u>+</u> 2 |                | <u>+</u> 4<br><u>+</u> 2 | LSB                      | Best Fit Straight Line Spec.<br>(Max INL – Min INL) / 2                              |

| Differential Non-Linearity<br>J<br>K                                                                                     | DNL                                                                       |     |                          | <u>+</u> 4<br><u>+</u> 2 |                | <u>+</u> 4<br><u>+</u> 2 | LSB                      |                                                                                      |

| Gain Error                                                                                                               | GE                                                                        |     |                          | <u>+</u> 0.1             |                | <u>+</u> 0.1             | % FSR                    | Using Internal R <sub>FB</sub>                                                       |

| Gain Temperature Coefficient <sup>2</sup>                                                                                | TC <sub>GE</sub>                                                          |     |                          |                          |                | <u>+</u> 2               | ppm/°C                   | ∆Gain/∆Temperature                                                                   |

| Power Supply Rejection Ratio                                                                                             | PSRR                                                                      |     |                          | <u>+</u> 50              |                | <u>+</u> 50              | ppm/%                    | $ \Delta Gain/\Delta V_{DD}  \Delta V_{DD} = \pm 5\%$                                |

| Output Leakage Current                                                                                                   | Ι <sub>ΟυΤ</sub>                                                          |     |                          | <u>+</u> 10              |                | <u>+</u> 200             | nA                       | I <sub>OUT1</sub>                                                                    |

| DYNAMIC PERFORMANCE <sup>2</sup>                                                                                         |                                                                           |     |                          |                          |                |                          |                          | R <sub>L</sub> =100Ω, C <sub>L</sub> =13pF                                           |

| Current Settling Time<br>AC Feedthrough at I <sub>OUT1</sub>                                                             | ts<br>F <sub>T</sub>                                                      |     | 2<br>2                   |                          |                |                          | μs<br>mV p-p             | Full Scale Change to 0.1%<br>V <sub>REF</sub> = 10kHz, 20 Vp-p, sinewave             |

| REFERENCE INPUT                                                                                                          |                                                                           |     |                          |                          |                |                          |                          |                                                                                      |

| Input Resistance                                                                                                         | R <sub>IN</sub>                                                           | 2.5 |                          | 7.5                      | 2.5            | 7.5                      | kΩ                       |                                                                                      |

| DIGITAL INPUTS <sup>3</sup>                                                                                              |                                                                           |     |                          |                          |                |                          |                          |                                                                                      |

| Logical "1" Voltage<br>Logical "0" Voltage<br>Input Leakage Current<br>Input Capacitance <sup>2</sup><br>Data<br>Control | V <sub>IH</sub><br>V <sub>IL</sub><br>I <sub>LKG</sub><br>C <sub>IN</sub> | 3.0 | 2.4<br>5<br>5            | 0.8<br><u>+</u> 1        | 3.0            | 0.8<br><u>+</u> 1        | V<br>V<br>μA<br>pF<br>pF |                                                                                      |

| ANALOG OUTPUTS <sup>2</sup>                                                                                              |                                                                           |     |                          |                          |                |                          |                          |                                                                                      |

| Output Capacitance                                                                                                       | Cout1<br>Cout1<br>Cout2<br>Cout2                                          |     |                          | 280<br>120<br>100<br>240 |                |                          | pF<br>pF<br>pF<br>pF     | DAC Inputs all 1's<br>DAC Inputs all 0's<br>DAC Inputs all 1's<br>DAC Inputs all 0's |

| POWER SUPPLY                                                                                                             |                                                                           |     |                          |                          |                |                          |                          |                                                                                      |

| Functional Voltage Range <sup>5</sup><br>Supply Current                                                                  | V <sub>DD</sub><br>I <sub>DD</sub>                                        | 4.5 |                          | 16.5<br>1                | 5.0            | 16.5<br>1                | V<br>mA                  | All digital inputs = 0 V or all = 5 V                                                |

# **ELECTRICAL CHARACTERISTICS (CON'T)**

| Parameter                                             | Symbol                             | Min        | 25°C<br>Typ | Max | Tmin to<br>Min | o Tmax<br>Max | Units    | Test Conditions/Comments |

|-------------------------------------------------------|------------------------------------|------------|-------------|-----|----------------|---------------|----------|--------------------------|

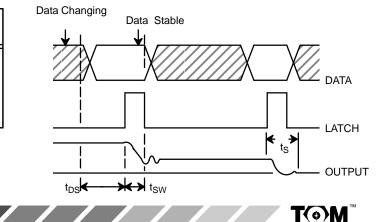

| SWITCHING<br>CHARACTERISTICS <sup>2, 4</sup>          |                                    |            |             |     |                |               |          |                          |

| Data Valid to Write Set-Up Time<br>Write Strobe Width | t <sub>DS</sub><br>t <sub>SW</sub> | 250<br>125 |             |     |                |               | ns<br>ns |                          |

#### NOTES:

- <sup>1</sup> Full Scale Range (FSR) is 10V for unipolar mode.

- <sup>2</sup> Guaranteed but not production tested.

- <sup>3</sup> Digital input levels should not go below ground or exceed the positive supply voltage, otherwise damage may occur.

- <sup>4</sup> See timing diagram.

- <sup>5</sup> Specified values guarantee functionality. Refer to other parameters for accuracy.

#### Specifications are subject to change without notice

## ABSOLUTE MAXIMUM RATINGS (TA = +25°C unless otherwise noted)<sup>1, 2</sup>

| Supply Voltage                                       | +17 V <sub>DC</sub>  |

|------------------------------------------------------|----------------------|

| Voltage at Any Digital Input GND -0.5 to VI          | <sub>DD</sub> +0.5 V |

| DC Voltage Applied to IOUT1 or IOUT2 GND -0.5        | to +17 V             |

| Voltage at V <sub>REF</sub> , R <sub>FB</sub> Inputs | <u>+</u> 25 V        |

| Storage Temperature Range –65°C to 150°C |  |

|------------------------------------------|--|

| Package Power Dissipation Rating to 75°C |  |

| CDIP, PDIP, PLCC 1050mW                  |  |

| Derates above 75°C 14mW/°C               |  |

#### NOTES:

- Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation at or above this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

- Any input pin which can see a value outside the absolute maximum ratings should be protected by Schottky diode clamps (HP5082-2835) from input pin to the supplies. *All inputs have protection diodes* which will protect the device from short transients outside the supplies of less than 100mA for less than 100µs.

#### APPLICATION NOTES Refer to Applications Section for Additional Information

## LATCH CONTROL

Rev. 2.00

| MSB<br>LATCH | LSB<br>LATCH | FUNCTION                   |

|--------------|--------------|----------------------------|

| 0            | 0            | Data Latched (Held)        |

| 1            | 0            | Transfer (DB15-DB8) to DAC |

| 0            | 1            | Transfer (DB7-DB0) to DAC  |

| 1            | 1            | Transparent Mode           |

## **TIMING DIAGRAM**

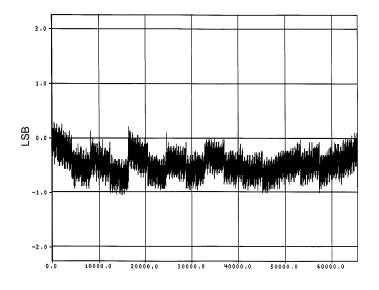

**PERFORMANCE CHARACTERISTICS**

Graph 1. Relative Accuracy vs. Digital Code

**APPLICATION NOTES** Refer to Section 8 for Applications Information

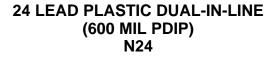

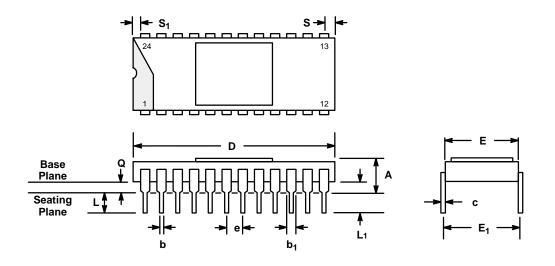

|                    | INC   | HES    | MILLIN | IETERS |

|--------------------|-------|--------|--------|--------|

| SYMBOL             | MIN   | MAX    | MIN    | MAX    |

| А                  |       | 0.225  |        | 5.72   |

| A <sub>1</sub>     | 0.015 | _      | 0.38   |        |

| В                  | 0.014 | 0.023  | 0.356  | 0.584  |

| B <sub>1</sub> (1) | 0.038 | 0.065  | 0.965  | 1.65   |

| С                  | 0.008 | 0.015  | 0.203  | 0.381  |

| D                  | 1.160 | 1.290  | 29.46  | 32.77  |

| E                  | 0.585 | 0.625  | 14.86  | 15.88  |

| E <sub>1</sub>     | 0.500 | 0.610  | 12.70  | 15.49  |

| е                  | 0.1   | 00 BSC | 2.5    | 4 BSC  |

| L                  | 0.115 | 0.150  | 2.92   | 3.81   |

| α                  | 0°    | 15°    | 0°     | 15°    |

| Q <sub>1</sub>     | 0.055 | 0.070  | 1.40   | 1.78   |

| S                  | 0.040 | 0.098  | 1.02   | 2.49   |

Note: (1) The minimum limit for dimensions B1 may be 0.023" (0.58 mm) for all four corner leads only.

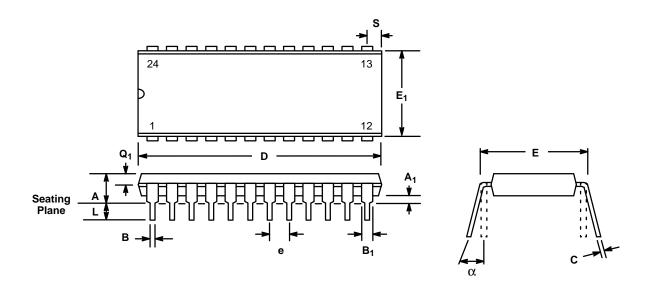

#### 24 LEAD CERAMIC DUAL-IN-LINE (600 MIL CDIP) D24

|                | INCHES |        | MILLIN | <b>IETERS</b> |       |

|----------------|--------|--------|--------|---------------|-------|

| SYMBOL         | MIN    | MAX    | MIN    | MAX           | NOTES |

| А              |        | 0.225  |        | 5.72          |       |

| b              | 0.014  | 0.023  | 0.356  | 0.584         | _     |

| b <sub>1</sub> | 0.038  | 0.065  | 0.965  | 1.65          | 2     |

| С              | 0.008  | 0.015  | 0.203  | 0.381         | _     |

| D              |        | 1.290  |        | 32.77         | 4     |

| E              | 0.500  | 0.610  | 12.70  | 15.49         | 4     |

| E <sub>1</sub> | 0.590  | 0.620  | 14.99  | 15.75         | 7     |

| е              | 0.10   | DO BSC | 2.5    | 4 BSC         | 5     |

| L              | 0.120  | 0.200  | 3.05   | 5.08          | _     |

| L <sub>1</sub> | 0.150  |        | 3.81   |               | —     |

| Q              | 0.015  | 0.075  | 0.381  | 1.91          | 3     |

| S              |        | 0.098  |        | 2.49          | 6     |

| S <sub>1</sub> | 0.005  |        | 0.13   |               | 6     |

| α              | 0°     | 15°    | 0°     | 15°           | _     |

#### NOTES

- 1. Index area; a notch or a lead one identification mark is located adjacent to lead one and is within the shaded area shown.

- 2. The minimum limit for dimension  $b_1$  may be 0.023 (0.58 mm) for all four corner leads only.

- 3. Dimension Q shall be measured from the seating plane to the base plane.

- 4. This dimension allows for off-center lid, meniscus and glass overrun.

- 5. The basic lead spacing is 0.100 inch (2.54 mm) between centerlines.

- 6. Applies to all four corners.

- 7. This is measured to outside of lead, not center.

#### 24 LEAD CERAMIC SIDE-BRAZED DUAL-IN-LINE (600 MIL S/B DIP) C24

|                | INCHES |        | MILLIN | <b>IETERS</b> |       |

|----------------|--------|--------|--------|---------------|-------|

| SYMBOL         | MIN    | MAX    | MIN    | MAX           | NOTES |

| А              | _      | 0.225  |        | 5.72          |       |

| b              | 0.014  | 0.023  | 0.356  | 0.584         | —     |

| b <sub>1</sub> | 0.038  | 0.065  | 0.965  | 1.65          | 2     |

| с              | 0.008  | 0.015  | 0.203  | 0.381         |       |

| D              | _      | 1.290  |        | 32.77         | 4     |

| E              | 0.500  | 0.610  | 12.70  | 15.49         | 4     |

| E <sub>1</sub> | 0.590  | 0.620  | 14.99  | 15.75         | 7     |

| е              | 0.10   | DO BSC | 2.5    | 4 BSC         | 5     |

| L              | 0.120  | 0.200  | 3.05   | 5.08          | _     |

| L <sub>1</sub> | 0.150  | _      | 3.81   |               | _     |

| Q              | 0.015  | 0.075  | 0.381  | 1.91          | 3     |

| S              | —      | 0.098  |        | 2.49          | 6     |

| S <sub>1</sub> | 0.005  |        | 0.13   |               | 6     |

#### NOTES

- 1. Index area; a notch or a lead one identification mark is located adjacent to lead one and is within the shaded area shown.

- 2. The minimum limit for dimension  $b_1$  may be 0.023 (0.58 mm) for all four corner leads only.

- 3. Dimension Q shall be measured from the seating plane to the base plane.

- 4. This dimension allows for off-center lid, meniscus and glass overrun.

- 5. The basic lead spacing is 0.100 inch (2.54 mm) between centerlines.

- 6. Applies to all four corners.

- 7.  $E_1$  shall be measured at the centerline of the leads.

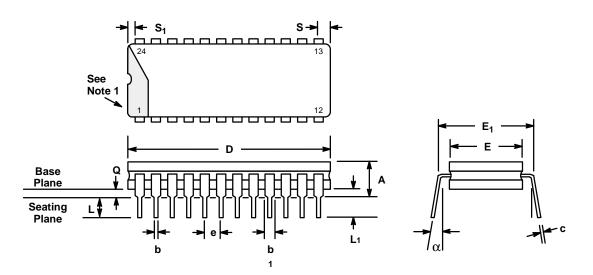

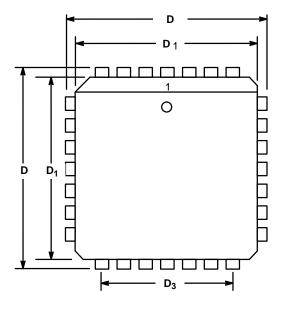

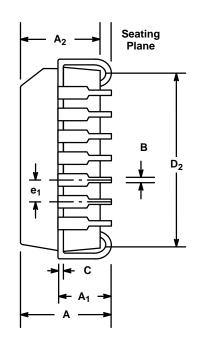

## 28 LEAD PLASTIC LEADED CHIP CARRIER (PLCC) P28

|                    | INC   | CHES   | MILLI | METERS |

|--------------------|-------|--------|-------|--------|

| SYMBOL             | MIN   | MAX    | MIN   | MAX    |

| А                  | 0.165 | 0.180  | 4.19  | 4.57   |

| A <sub>1</sub>     | 0.100 | 0.110  | 2.54  | 2.79   |

| A <sub>2</sub>     | 0.148 | 0.156  | 3.76  | 3.96   |

| В                  | 0.013 | 0.021  | 0.330 | 0.533  |

| С                  | 0.008 | 0.012  | 0.203 | 0.305  |

| D                  | 0.485 | 0.495  | 12.32 | 12.57  |

| D <sub>1</sub> (1) | 0.450 | 0.454  | 11.43 | 11.53  |

| D <sub>2</sub>     | 0.390 | 0.430  | 9.91  | 10.92  |

| D <sub>3</sub>     | 0.3   | 00 Ref | 7.6   | 2 Ref. |

| e <sub>1</sub>     | 0.0   | 50 BSC | 1.2   | 7 BSC  |

Note: (1) Dimension  $D_1$  does not include mold protrusion. Allowed mold protrusion is 0.254 mm/0.010 in.

**Notes**

**Notes**

#### NOTICE

EXAR Corporation reserves the right to make changes to the products contained in this publication in order to improve design, performance or reliability. EXAR Corporation assumes no responsibility for the use of any circuits described herein, conveys no license under any patent or other right, and makes no representation that the circuits are free of patent infringement. Charts and schedules contains here in are only for illustration purposes and may vary depending upon a user's specific application. While the information in this publication has been carefully checked; no responsibility, however, is assumed for inaccuracies.

EXAR Corporation does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless EXAR Corporation receives, in writing, assurances to its satisfaction that: (a) the risk of injury or damage has been minimized; (b) the user assumes all such risks; (c) potential liability of EXAR Corporation is adequately protected under the circumstances.

Copyright EXAR Corporation Datasheet April 1995 Reproduction, in part or whole, without the prior written consent of EXAR Corporation is prohibited.