# **MP7612**

Octal 12-Bit DAC Array<sup>TM</sup> D/A Converter with Output Amplifier and Serial Data/Address μP Control Logic

## **FEATURES**

Eight Independent 12-Bit DACs with Output Amplifiers

**XEXAR** ... the analog plus company<sup>TM</sup>

- Low Power 320 mW (typ.)

- Serial Digital Data and Address Port (3-Wire Standard)

- 12-Bit Resolution, 11 Bit Accuracy

- **Extremely Well Matched DACs**

- Extremely Low Analog Ground Current (<60µA/Channel)

- +10 V Output Swing with +11.4 V Supplies

- Zero Volt Output Preset (Data = 10 .. 00)

- **Rugged Construction Latch-Up Free**

- Parallel Version: MP7613

## **APPLICATIONS**

April 1996-4

- **Data Acquisition Systems**

- ATE

- **Process Control**

- Self-Diagnostic Systems

- Logic Analyzers

- **Digital Storage Scopes**

- PC Based Controller/DAS

## **GENERAL DESCRIPTION**

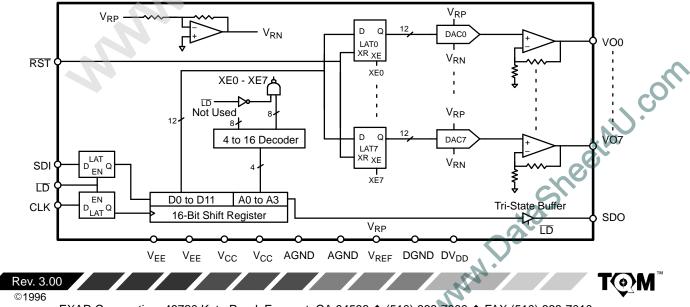

The MP7612 provides eight independent 12-bit resolution Digital-to-Analog Converters with voltage output amplifiers and a 3-wire standard serial digital address and data port.

Typical DAC matching for B grade versions is 0.7 LSB across all codes. Accuracy of ±0.75 LSB for DNL and ±1 LSB for INL is also achieved for B grades. The output amplifier is capable of sinking and sourcing 5mA, and the output voltage settles to 12-bits in less than 30µs (typ.).

The MP7612 is equipped with a serial data (3-wire standard) µ-processor logic interface to reduce pin count, package size, and board space.

Built using an advanced linear BiCMOS, these devices offer rugged solutions that are latch-up free, and take advantage of EXAR's patented thin-film resistor process which exhibits excellent long term stability and reliability.

EXAR Corporation, 48720 Kato Road, Fremont, CA 94538 (510) 668-7000 FAX (510) 668-7010

#### SIMPLIFIED BLOCK DIAGRAM

## **ORDERING INFORMATION**

| Package<br>Type | Temperature<br>Range | Part No. | Res.<br>(Bits) | INL<br>(LSB) | DNL<br>(LSB) | FSE<br>(LSB) |

|-----------------|----------------------|----------|----------------|--------------|--------------|--------------|

| PLCC            | –40 to +85°C         | MP7612BP | 12             | ±1           | ±0.75        | ±6           |

| PLCC            | –40 to +85°C         | MP7612AP | 12             | ±2           | ±1           | ±8           |

| SOIC            | –40 to +85°C         | MP7612BS | 12             | ±1           | ±0.75        | ±6           |

| SOIC            | –40 to +85°C         | MP7612AS | 12             | ±2           | ±1           | ±8           |

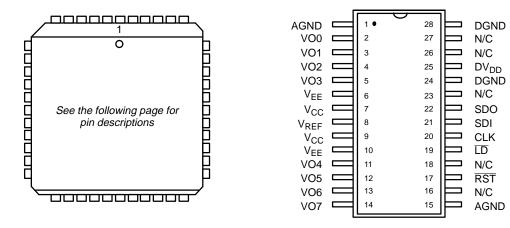

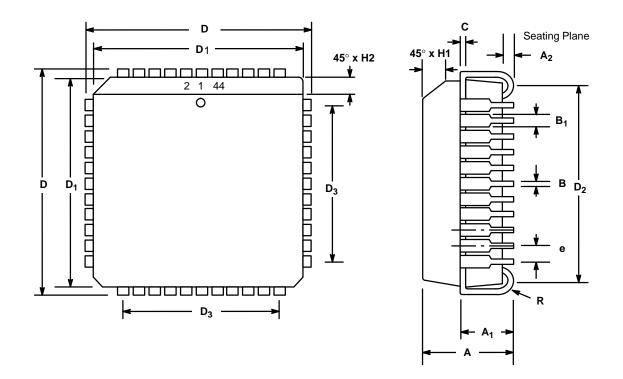

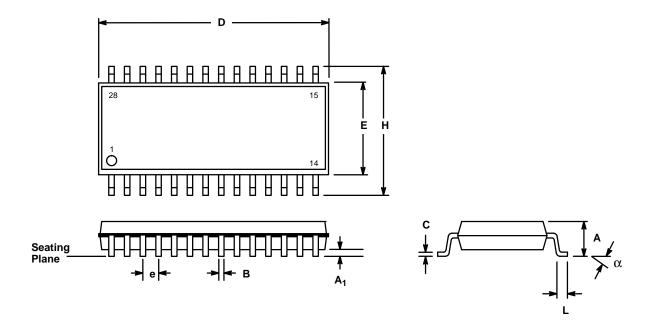

## **PIN CONFIGURATIONS**

44 Pin PLCC

28 Pin SOIC (Jedec, 0.346")

## **PIN DESCRIPTION**

| SOIC<br>Pin # | PLCC<br>Pin #                                                                                | Symbol           | Description                            |

|---------------|----------------------------------------------------------------------------------------------|------------------|----------------------------------------|

| 1             | 2                                                                                            | AGND             | Analog Ground                          |

| 2             | 3                                                                                            | VO0              | DAC 0 Output                           |

| 3             | 4                                                                                            | VO1              | DAC 1 Output                           |

| 4             | 5                                                                                            | VO2              | DAC 2 Output                           |

| 5             | 6                                                                                            | VO3              | DAC 3 Output                           |

| 6             | 7                                                                                            | V <sub>EE</sub>  | Analog Negative Power Supply (-12 V)   |

| 7             | 9                                                                                            | V <sub>CC</sub>  | Analog Positive Power Supply (+12 V)   |

| 8             | 12                                                                                           | V <sub>REF</sub> | Voltage Reference Input (+5 V)         |

| 9             | 13                                                                                           | V <sub>CC</sub>  | Analog Positive Power Supply (+12 V)   |

| 10            | 15                                                                                           | V <sub>EE</sub>  | Analog Negative Power Supply (-12 V)   |

| 11            | 18                                                                                           | VO4              | DAC 4 Output                           |

| 12            | 19                                                                                           | VO5              | DAC 5 Output                           |

| 13            | 20                                                                                           | VO6              | DAC 6 Output                           |

| 14            | 21                                                                                           | VO7              | DAC 7 Output                           |

| 15            | 24                                                                                           | AGND             | Analog Ground                          |

| 16            |                                                                                              | N/C              | No Connection                          |

| 17            | 26                                                                                           | RST              | Reset all DACs to 0 V Output           |

| 18            |                                                                                              | N/C              | No Connection                          |

| 19            | 29                                                                                           | LD               | Load Signal; Load Data to Selected DAC |

| 20            | 31                                                                                           | CLK              | Serial Data Clock                      |

| 21            | 32                                                                                           | SDI              | Serial Data Input                      |

| 22            | 34                                                                                           | SDO              | Shift Register Serial Output           |

| 23            |                                                                                              | N/C              | No Connection                          |

| 24            | 37                                                                                           | DGND             | Digital Ground                         |

| 25            | 40                                                                                           | DV <sub>DD</sub> | Digital Positive Power Supply (+5 V)   |

| 26            |                                                                                              | N/C              | No Connection                          |

| 27            | 1, 8, 10, 11, 14,<br>16, 17, 22, 23,<br>25, 27, 28, 30,<br>33, 35, 36, 38,<br>39, 41, 42, 43 | N/C              | No Connection                          |

| 28            | 44                                                                                           | DGND             | Digital Ground                         |

## ELECTRICAL CHARACTERISTICS

$V_{CC}$  = +12 V,  $V_{EE}$  = -12 V,  $V_{REF}$  = 5 V,  $DV_{DD}$  = 5.0 V, T = 25°C, Output Load = 5k $\Omega$  (unless otherwise noted)

| Parameter                                                                                                                                                                   | Symbol                             | Min        | 25 <sup>°</sup> С<br>Тур | Max                | Tmin to<br>Min | Tmax<br>Max        | Units                      | Test Conditions/Comments                                                                                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|------------|--------------------------|--------------------|----------------|--------------------|----------------------------|---------------------------------------------------------------------------------------------------------------------------|

| STATIC PERFORMANCE                                                                                                                                                          |                                    |            |                          |                    |                |                    |                            |                                                                                                                           |

| Resolution (All Grades)                                                                                                                                                     | N                                  | 12         |                          |                    |                |                    | Bits                       |                                                                                                                           |

| Integral Non-Linearity<br>(Relative Accuracy)<br>A<br>B                                                                                                                     | INL                                |            |                          | 土2<br>土1           |                | 土2<br>土1           | LSB                        | End Point Linearity Spec                                                                                                  |

| Differential Non-Linearity<br>A<br>B                                                                                                                                        | DNL                                |            |                          | 土1<br>土0.75        |                | 土1<br>土0.75        | LSB                        |                                                                                                                           |

| Positive Full Scale Error<br>A<br>B                                                                                                                                         | +FSE                               |            | 6<br>4                   | 土8<br>土6           |                | 土8<br>土6           | LSB                        |                                                                                                                           |

| Negative Full Scale Error<br>A<br>B                                                                                                                                         | -FSE                               |            | 6<br>4                   | 土8<br>土6           |                | 土8<br>土6           | LSB                        |                                                                                                                           |

| Bipolar Zero Offset<br>A<br>B                                                                                                                                               | ZOFS                               |            |                          | $^{\pm4}_{\pm3}$   |                | 土4<br>土3           | LSB                        |                                                                                                                           |

| INL Matching<br>A<br>B                                                                                                                                                      | ΔINL                               |            |                          | 土2<br>土1.5         |                | 土2<br>土1.5         | LSB                        |                                                                                                                           |

| All Channels Maximum Error<br>with DAC 0 adjusted to<br>minimum error<br>A<br>B                                                                                             | ME                                 |            |                          | ±4<br>±2           |                | ±4<br>±2           | LSB                        |                                                                                                                           |

| Bipolar Zero Matching<br>A<br>B                                                                                                                                             | ∆ZOFS                              |            |                          | $\pm 4$<br>$\pm 3$ |                | $\pm 4$<br>$\pm 3$ | LSB                        |                                                                                                                           |

| Full Scale Error Matching<br>A<br>B                                                                                                                                         | FSE                                |            |                          | $^{\pm4}_{\pm3}$   |                | 土4<br>土3           | LSB                        |                                                                                                                           |

| DYNAMIC PERFORMANCE                                                                                                                                                         |                                    |            |                          |                    |                |                    |                            |                                                                                                                           |

| Voltage Settling from LD<br>to VDAC Out <sup>1</sup><br>Channel-to-Channel Crosstalk <sup>1, 6</sup><br>Digital Feedthrough <sup>1, 6</sup><br>Power Supply Rejection Ratio | t <sub>sd</sub><br>CT<br>Q<br>PSRR |            | 30<br>0.04<br>–70        | 50<br>5            |                | 50                 | μsec<br>LSB<br>dB<br>ppm/% | ZS to FS (20 V Step)<br>DC<br>CLK and Data to V <sub>OUTi</sub><br>$\Delta V_{EE} \& \Delta V_{CC} = \pm 5\%$ , ppm of FS |

| REFERENCE INPUTS                                                                                                                                                            |                                    |            |                          |                    |                |                    |                            |                                                                                                                           |

| Impedance of V <sub>REF</sub><br>V <sub>REF</sub> Voltage1, <sup>2</sup>                                                                                                    | REF<br>V <sub>REF</sub>            | 350<br>3.5 | 700                      | 1.05k<br>6         | 350            | 1.05k              | Ω<br>V                     | See Application Hints for driving the reference input                                                                     |

## **ELECTRICAL CHARACTERISTICS (CONT'D)**

| Parameter                                                                                                                                                                                                                                                                                                                                                                                              | Symbol                                                                                                                                                                                                               | Min                                                            | 25 <sup>°</sup> С<br>Тур                     | Max                                        | Tmin to<br>Min                         | Tmax<br>Max                                | Units                                              | Test Conditions/Comments                                                                                                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|----------------------------------------------|--------------------------------------------|----------------------------------------|--------------------------------------------|----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| DIGITAL INPUTS <sup>3</sup>                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                      |                                                                | .76                                          | max                                        |                                        |                                            |                                                    |                                                                                                                                                    |

| Logic High<br>Logic Low<br>Input Current<br>Input Capacitance <sup>1</sup>                                                                                                                                                                                                                                                                                                                             | V <sub>IH</sub><br>V <sub>IL</sub><br>IL<br>CL                                                                                                                                                                       | 2.4                                                            |                                              | 0.8<br><u>+</u> 10<br>8                    |                                        |                                            | V<br>V<br>μA<br>pF                                 |                                                                                                                                                    |

| ANALOG OUTPUTS                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                      |                                                                |                                              |                                            |                                        |                                            |                                                    |                                                                                                                                                    |

| Output Swing<br>Output Drive Current<br>Output Impedance<br>Output Short Circuit Current                                                                                                                                                                                                                                                                                                               | R <sub>O</sub><br>Isc                                                                                                                                                                                                | -V <sub>EE</sub> +1.4<br>-5                                    | V <sub>CC</sub><br>1<br>25<br>30<br>40<br>55 | -1.4<br>5                                  |                                        |                                            | V<br>mA<br>mA<br>mA<br>mA<br>mA                    | +FS to AGND<br>+FS to V <sub>EE</sub><br>–FS to AGND<br>–FS to V <sub>CC</sub>                                                                     |

| DIGITAL OUTPUTS                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                      |                                                                |                                              |                                            |                                        |                                            |                                                    |                                                                                                                                                    |

| Output High Voltage<br>Output Low Voltage                                                                                                                                                                                                                                                                                                                                                              | V <sub>OH</sub><br>V <sub>OL</sub>                                                                                                                                                                                   |                                                                | 4.5<br>0.5                                   |                                            |                                        |                                            | V<br>V                                             |                                                                                                                                                    |

| POWER SUPPLIES                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                      |                                                                |                                              |                                            |                                        |                                            |                                                    |                                                                                                                                                    |

| V <sub>CC</sub> Voltage <sup>5</sup><br>V <sub>EE</sub> Voltage <sup>5</sup><br>DV <sub>DD</sub> Voltage<br>Positive Supply Current<br>Negative Supply Current<br>Digital Supply Current<br>Power Dissipation                                                                                                                                                                                          | V <sub>CC</sub><br>V <sub>EE</sub><br>DV <sub>DD</sub><br>I <sub>CC</sub><br>I <sub>DD</sub><br>PD <sub>ISS</sub>                                                                                                    | V <sub>REF</sub> +1.5<br>–12.75<br>4.5                         | 12<br>-12<br>5<br>8<br>15<br>320             | 12.75<br>-5<br>5.5<br>10<br>20<br>2<br>420 | V <sub>REF</sub> +1.5<br>-12.75<br>4.5 | 12.75<br>-5<br>5.5<br>10<br>20<br>2<br>450 | V<br>V<br>mA<br>mA<br>mW                           | Bipolar zero<br>Bipolar zero<br>Bipolar zero<br>Bipolar zero                                                                                       |

| ANALOG GROUND CURRENT                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                      |                                                                |                                              |                                            |                                        |                                            |                                                    |                                                                                                                                                    |

| Per Channel <sup>1</sup>                                                                                                                                                                                                                                                                                                                                                                               | I <sub>AGND</sub>                                                                                                                                                                                                    |                                                                | ±60                                          |                                            |                                        |                                            | μΑ                                                 | See Application Notes                                                                                                                              |

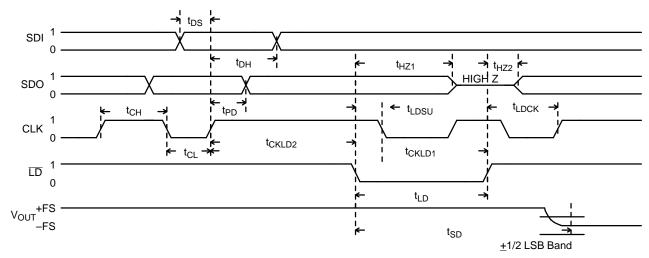

| DIGITAL TIMING<br>SPECIFICATIONS <sup>1,4</sup><br>Input Clock Pulse Width<br>Data Setup Time<br>Data Hold Time<br>CLK to SDO Propagation Delay<br>DAC Register Load Pulse Width<br>Preset Pulse Width<br>Clock Edge to Load Time<br>ID Falling Edge to SDO<br>Tri-state Enable<br>ID Rising Edge to SDO<br>Tri-state Disable<br>ID Rising Edge to CLK Enable<br>ID Set-up Time with Respect<br>to CLK | t <sub>CH</sub> , t <sub>CL</sub><br>t <sub>DS</sub><br>t <sub>DH</sub><br>t <sub>PD</sub><br>t <sub>LD</sub><br>t <sub>PR</sub><br>t <sub>CKLD1</sub><br>t <sub>CKLD2</sub><br>t <sub>HZ1</sub><br>t <sub>HZ2</sub> | 35<br>15<br>15<br>35<br>50<br>140<br>0<br>50<br>50<br>50<br>30 |                                              | 40                                         |                                        |                                            | ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns | $V_{IL} = 0$ , $V_{IH} = 5.0$ , $C_L = 20 \text{ pF}$<br>Note: $t_{LD}$ and $t_{CKLD2}$ cannot both be min. since $t_{CKLD1} = t_{CKLD2} + t_{LD}$ |

## **ELECTRICAL CHARACTERISTICS (CONT'D)**

#### NOTES:

- <sup>1</sup> Guaranteed; not tested.

- <sup>2</sup> Specified values guarantee functionality.

- <sup>3</sup> Digital inputs should not go below digital GND or exceed DV<sub>DD</sub> supply voltage.

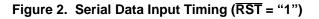

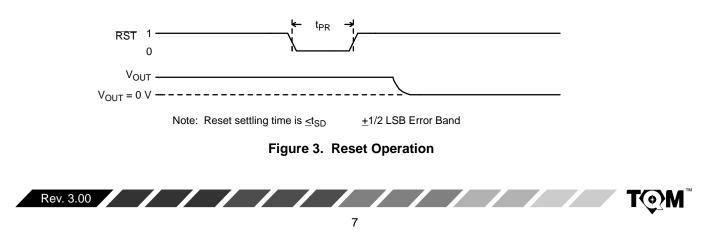

- <sup>4</sup> See Figures 2 and 3. All digital input signals are specified with  $t_R = t_F = 10$  ns 10% to 90% and timed from a 50% voltage level.

- <sup>5</sup> For power supply values <  $\pm 2 * V_{REF}$ , the output swing is limited as specified in Analog Outputs.

- <sup>6</sup> Digital feedthrough and channel-to-channel crosstalk are heavily dependent on the board layout and environment.

#### Specifications are subject to change without notice

/ / / / / /

#### ABSOLUTE MAXIMUM RATINGS (TA = +25°C unless otherwise noted)<sup>1, 2</sup>

| V <sub>CC</sub> to AGND                                                                   | Analog Inputs & Outputs Indefinite Shorts to V <sub>CC</sub> , V <sub>EE</sub> , DV <sub>DD</sub> , AGND, DGND (provided that power dissipation of the package spec is not exceeded) |

|-------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DV <sub>DD</sub> to DGND                                                                  | Operating Temperature Range<br>Extended Industrial                                                                                                                                   |

| V <sub>REF</sub> to DGND +7.0 V                                                           | Maximum Junction Temperature –65°C to 150°C                                                                                                                                          |

| VREF 10 DGND +7.0 V                                                                       | Storage Temperature150°C                                                                                                                                                             |

| AGND to DGND $\pm 1 \text{ V}$<br>(Functionality guaranteed for $\pm 0.5 \text{ V}$ only) | Lead Temperature (Soldering, 10 sec) +300°C                                                                                                                                          |

| Digital Input & Output Voltage to DGND -0.5 to DV <sub>DD</sub><br>+0.5V                  | Package Power Dissipation Rating @ 75°C<br>SOIC, PLCC 1150mW<br>Derates above 75°C 15mW/°C                                                                                           |

#### NOTES:

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation at or above this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

Any input pin which can see a value outside the absolute maximum ratings should be protected by Schottky diode clamps (HP5082-2835) from input pin to the supplies. *All inputs have protection diodes* which will protect the device from short transients outside the supplies of less than 100mA for less than 100µs.

### APPLICATION NOTES Refer to Section 8 in the 1995 Data Acquisition products Databook for Applications Information

NOTE: When using these DACs to drive remote devices, the accuracy of the output can be improved by utilizing a remote analog ground connection. The difference between the DGND and AGND should be limited to  $\pm$ 300 mV to assure normal operation. If there is any chance that the AGND to DGND can be greater than  $\pm$ 1 V, we recommend two back-to-back diodes be used between DGND and AGND to clamp the voltage and prevent damage to the DAC. Using a buffer between the remote ground location and AGND may help reduce noise induced from long lead or trace lengths.

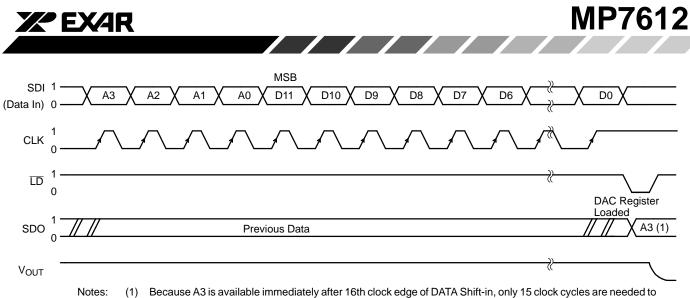

(1) Because A3 is available immediately after 16th clock edge of DATA Shift-in, only 15 clock cycles are needed to complete the readback.

Figure 1. Serial Data Timing and Loading

**MP7612**

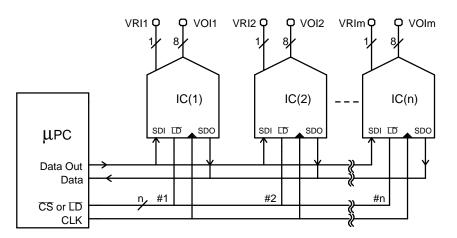

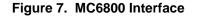

The MP7612 is equipped with a serial data (3-wire standard)  $\mu$ -processor logic interface to reduce pin count, package size, and board wire (space). If the  $\overline{\text{LD}}$  signal is high, the CLK signal loads the digital input bits (SDI) into the shift register (4 bits address A3 to A0 plus 12 bits data DB11 to DB0 for the MP7612). The  $\overline{\text{LD}}$  signal going low loads the data into the selected DAC.

The  $\overline{\text{LD}}$  signal going low also disables the serial data (SDI), output (SDO 3-stated) and the CLK input. This design tremendously reduces digital noise and glitch transients into the DACs due to free running CLK and SDI. Note also that the preset signal ( $\overline{\text{RST}}$ ) resets all analog outputs to 0 volt regardless of digital inputs.

| Function                                                                          | A3                                        | A2                                  | A1                                            | A0                           | LD                                                                                                                                                                              | CLK           | RST               | SDI                 | SDO                                                          |

|-----------------------------------------------------------------------------------|-------------------------------------------|-------------------------------------|-----------------------------------------------|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------------------|---------------------|--------------------------------------------------------------|

| Shift Data In and Out                                                             | Х                                         | Х                                   | Х                                             | Х                            | 1                                                                                                                                                                               | 0→1<br>Repeat | 1                 | Data Input<br>Valid | Data Output<br>Valid                                         |

| Stop Shifting<br>Data In and<br>Out                                               | Х                                         | Х                                   | Х                                             | Х                            | 0                                                                                                                                                                               | Х             | 1                 | Х                   | Hi-Z                                                         |

| Load DACs<br>DAC 0<br>DAC 1<br>DAC 2<br>DAC 3<br>DAC 4<br>DAC 5<br>DAC 6<br>DAC 7 | 0<br>0<br>0<br>0<br>0<br>0<br>0<br>1<br>1 | 0<br>0<br>0<br>1<br>1<br>1<br>0<br> | 0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br> | 0<br>10101010<br>10101010101 | No Operation<br>$1 \rightarrow 0$<br>$1 \rightarrow 0$<br>$1 \rightarrow 0$<br>$1 \rightarrow 0$<br>$1 \rightarrow 0$<br>$1 \rightarrow 0$<br>$1 \rightarrow 0$<br>No Operation | ****          | 1 1 1 1 1 1 1 1 1 | ××××××× ××          | Hi-Z<br>Hi-Z<br>Hi-Z<br>Hi-Z<br>Hi-Z<br>Hi-Z<br>Hi-Z<br>Hi-Z |

| Reset all DACs<br>to 0 V                                                          | X                                         | X                                   | X                                             | X                            | No Operation<br>X                                                                                                                                                               | x             | 0                 | X                   | X                                                            |

## Table 1. Digital Function Truth TableSerial In/Serial Out

Note: For timing information see Electrical Characteristics

| Hex Code | Binary Code  | Output Voltage = 2 • Vr (-1 + <u>2•D</u> )<br>(Vr = +5 V) 4096 |

|----------|--------------|----------------------------------------------------------------|

| 000      | 000000000000 | 10 • (-1 + 0) = -10                                            |

|          |              |                                                                |

| 7 F F    | 01111111111  | $10 \bullet (-1 + \frac{4094}{4096}) = -4.88 \text{ mV}$       |

| 800      | 100000000000 | $10 \bullet (-1 + \frac{4096}{4096}) = 0$                      |

| 801      | 10000000001  | $10 \bullet (-1 + \frac{4098}{4096}) = 4.88 \text{ mV}$        |

| FFF      | 11111111111  | $10 \bullet (-1 + \frac{8190}{4096}) = 9.99512$                |

**MP7612**

Table 2.MP7612Ideal DAC Output vs. Input Code

Note: See Electrical Characteristics for real system accuracy

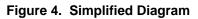

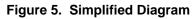

Figure 6. Simplified Diagram

## MP7612

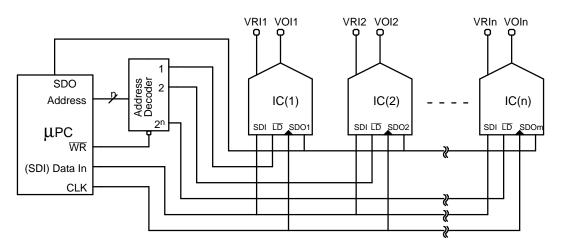

#### NOTES

- 1. Execute consecutive memory write instructions while manipulating the data between WRITEs so that each WRITE presents the next bit.

- 2. The serial data loading is triggered by the CLK pulse which is asserted by a decoded memory WRITE to memory location 2000, R/W, and 02. A WRITE to address 4000 transfers data from input shift register to DAC register.

#### NOTES:

- 1. Clock generated by WR and decoding address 8000.

- 2. Data is clocked in the DAC shift register by executing memory write instructions. The clock input is generated by decoding address 8000 and WR. Data is then loaded into the DAC register with a memory write instruction to address 4000.

- 3. Serial data must be present in the right justified format in registers H & L of the microprocessor.

Figure 8. 8085 Interface

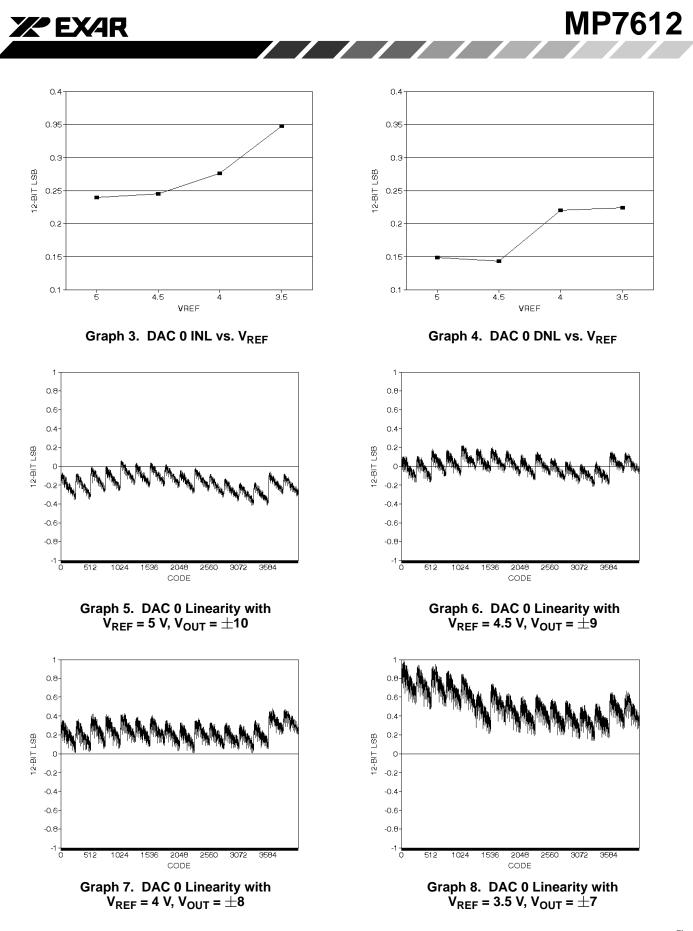

PERFORMANCE CHARACTERISTICS

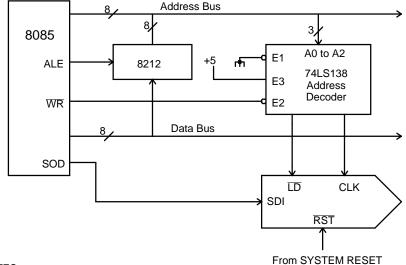

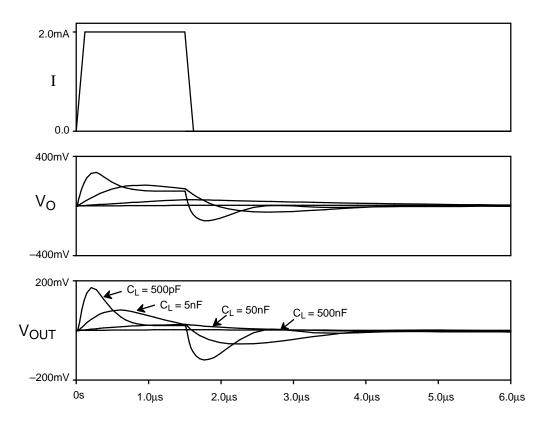

Graph 1 shows the typical output settling characteristic of the MP7610 Family for a RESET -> ZS -> FS -> ZS series of code transitions. The top graph shows the output voltage transients, while the bottom graph shows the difference between the output and the ideal output.

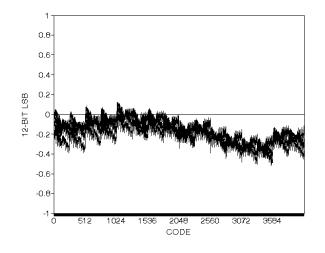

Graph 2. Linearity with  $V_{REF} = 5$  V, All DACs, All Codes

Rev. 3.00

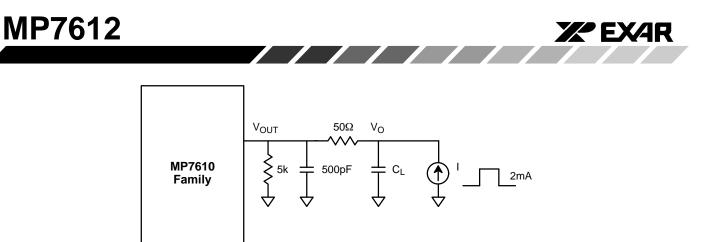

CL = 500pF, 5nF, 50nF, 500nF

Graph 9. Typical Response of the MP7610 Family Analog Output to a Current Pulse with CL=500pF, 5nF, 50nF, 500nF (See Figure 9. above)

44 LEAD PLASTIC LEADED CHIP CARRIER (PLCC)

|                | INC   | CHES    | MILLI | METERS  |

|----------------|-------|---------|-------|---------|

| SYMBOL         | MIN   | MAX     | MIN   | MAX     |

| А              | 0.165 | 0.180   | 4.19  | 4.57    |

| A <sub>1</sub> | 0.090 | 0.120   | 2.29  | 3.05    |

| A <sub>2</sub> | 0.020 |         | 0.51  |         |

| В              | 0.013 | 0.021   | 0.33  | 0.53    |

| B <sub>1</sub> | 0.026 | 0.032   | 0.66  | 0.81    |

| С              | 0.008 | 0.013   | 0.19  | 0.32    |

| D              | 0.685 | 0.695   | 17.40 | 17.65   |

| D <sub>1</sub> | 0.650 | 0.656   | 16.51 | 16.66   |

| D <sub>2</sub> | 0.590 | 0.630   | 14.99 | 16.00   |

| D <sub>3</sub> | 0.5   | 00 typ. | 12.7  | 70 typ. |

| е              | 0.0   | 50 BSC  | 1.2   | 7 BSC   |

| H1             | 0.042 | 0.056   | 1.07  | 1.42    |

| H2             | 0.042 | 0.048   | 1.07  | 1.22    |

| R              | 0.025 | 0.045   | 0.64  | 1.14    |

Note: The control dimension is the inch column

|                | INC   | HES    | MILLIN | METERS |

|----------------|-------|--------|--------|--------|

| SYMBOL         | MIN   | MAX    | MIN    | МАХ    |

| А              | 0.093 | 0.104  | 2.35   | 2.65   |

| A <sub>1</sub> | 0.004 | 0.012  | 0.10   | 0.30   |

| В              | 0.013 | 0.020  | 0.33   | 0.51   |

| С              | 0.009 | 0.013  | 0.23   | 0.32   |

| D              | 0.706 | 0.718  | 17.93  | 18.24  |

| E              | 0.340 | 0.350  | 8.64   | 8.89   |

| е              | 0.0   | 50 BSC | 1.2    | 7 BSC  |

| Н              | 0.460 | 0.485  | 11.68  | 12.32  |

| L              | 0.016 | 0.050  | 0.40   | 1.27   |

| α              | 0°    | 8°     | 0°     | 8°     |

Note: The control dimension is the millimeter column

Notes

Notes

Notes

## NOTICE

EXAR Corporation reserves the right to make changes to the products contained in this publication in order to improve design, performance or reliability. EXAR Corporation assumes no responsibility for the use of any circuits described herein, conveys no license under any patent or other right, and makes no representation that the circuits are free of patent infringement. Charts and schedules contained here in are only for illustration purposes and may vary depending upon a user's specific application. While the information in this publication has been carefully checked; no responsibility, however, is assumed for inaccuracies.

EXAR Corporation does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless EXAR Corporation receives, in writing, assurances to its satisfaction that: (a) the risk of injury or damage has been minimized; (b) the user assumes all such risks; (c) potential liability of EXAR Corporation is adequately protected under the circumstances.

Copyright 1993 EXAR Corporation Datasheet April 1996 Reproduction, in part or whole, without the prior written consent of EXAR Corporation is prohibited.