Configurable 2.7V-6V Mini PMIC with Dual 2.5A/3.5A Buck, One Load Switch, and Input Power Supervisory

The Future of Analog IC Technology

NOT RECOMMENDED FOR NEW DESIGNS, REFER TO MP5479 OR MP5417

#### DESCRIPTION

MP5403 The monolithic а power management unit containing two highefficiency, step-down, switching converters and a load switch. The two regulators supply current up to 3.5A and 2.5A separately, and the load switch supplies up to 3A of load current with an extremely low R<sub>DS(ON)</sub>. With an input range of up to 6V, the MP5403 is ideal for powering ASIC and SOC for solid-state drives and other compact power systems.

The peak-current-mode control scheme with pulse-skip-mode operation provides the two switchers with fast transient response, high light-load efficiency, and minimum capacitance by using an interleaving PWM clock between the two switchers. The 3A load switch with a low  $20m\Omega$  on resistance provides flexible system configuration.

A full set of enable control pins and power good open-drain indicators allow for easy implementation of the start-up and shutdown sequences.

Full protection features include over-current protection (OCP) and thermal shutdown.

The MP5403 requires a minimal number of readily available, standard, external components and is available in a small UTQFN-20 (2.5mmx3mm) package.

## **FEATURES**

- Low I<sub>Q</sub>: 85µA for Two Switchers Total

- Two Buck Converters

- $\circ$  3.5A with 55m $\Omega$ /20m $\Omega$  R<sub>DS(ON)</sub>

- $\circ$  2.5A with  $60m\Omega/22m\Omega$  R<sub>DS(ON)</sub>

- 1.5MHz Switching Frequency

- 180° Interleaving Operation

- o 100% Duty Cycle

- Load Switch Mode by Pulling FB Low

- Latch-Off Short-Circuit Protection (SCP)

- Parallel Capability by Connecting SW Nodes Together

- Internal Soft Start and Output Discharge

- Optimized Light-Load Efficiency

- Available Fixed Output Options via Package Trim:

Ch1: 0.9V, 1.1V, 2.5V, 2.85V Ch2: 0.9V, 1.2V, 1.8V, 2.5V

- One Load Switch

- $\circ$  3A with 20m $\Omega$  R<sub>DS(ON)</sub>

- Soft Start and Output Discharge

- Over-Current Protection (OCP)

- EN and Power Good for Power Sequencing

- Input Power Failure Indicator (PFL) with Adjustable Threshold and Delay

- Thermal Shutdown

- Available in Ultra-Thin UTQFN-20 (2.5mmx3mm) Package

#### **APPLICATIONS**

- Solid-State Drives

- Hybrid Drives

- Low Voltage System Power

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance. "MPS" and "The Future of Analog IC Technology" are registered trademarks of Monolithic Power Systems, Inc.

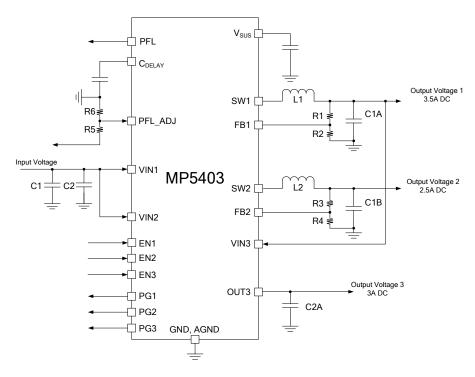

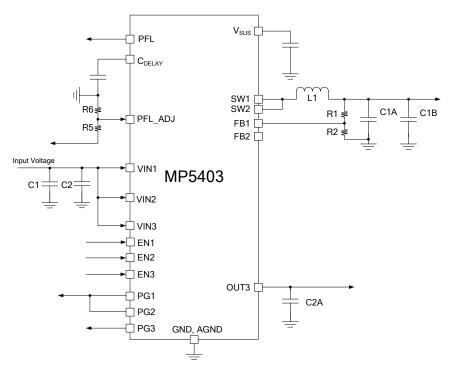

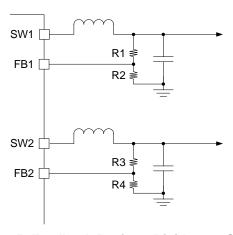

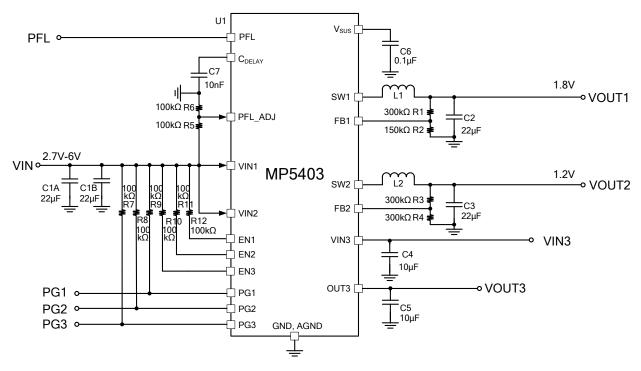

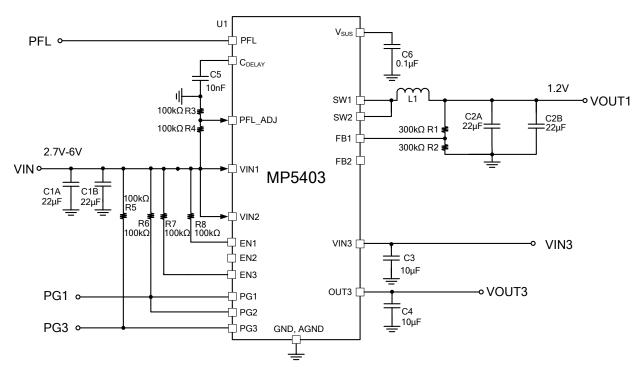

## **TYPICAL APPLICATION**

#### Two Bucks and One Load Switch

One Parallel Buck and One Load Switch

## **ORDERING INFORMATION**

| Part Number* | Package              | Top Marking |

|--------------|----------------------|-------------|

| MP5403GQBU   | UTQFN-20 (2.5mmx3mm) | See Below   |

<sup>\*</sup> For Tape & Reel, add suffix -Z (e.g. MP5403GQBU-Z)

## **TOP MARKING**

APZ

YWW

LLL

APZ: Product code of MP5403GQBU

Y: Year code WW: Week code LLL: Lot number

## **PACKAGE REFERENCE**

| ADOOLUTE MANUALIMA DATINGO (1                       | ١,      |

|-----------------------------------------------------|---------|

| ABSOLUTE MAXIMUM RATINGS (1                         |         |

| Supply voltage (VIN1/2/3)6.5                        | V       |

| V <sub>SW1/2</sub> 0.3V (-5V for <10ns              | s)      |

|                                                     |         |

| to 6.5V (10V for <10ns All other pins0.3V to 6.5    | 3/      |

| Continuous power dissipation (T 125°C)              | V       |

| Continuous power dissipation $(T_A = +25^{\circ}C)$ | ٥١      |

| 2.08W <sup>(2</sup>                                 | ۷)      |

| Junction temperature 150°                           | С       |

| Lead temperature260°                                |         |

| Storage temperature65°C to +150°                    | Ċ.      |

|                                                     | •       |

| Recommended Operating Conditions (3)                |         |

| Supply voltage (VIN1)2.7V to 6                      | V       |

| If VIN1 > UVLO, supply voltage (VIN2)               |         |

|                                                     |         |

|                                                     |         |

| If VIN1 > UVLO, supply voltage (VIN3)               |         |

|                                                     |         |

| If VIN1 < UVLO, supply voltage (VIN3)               |         |

|                                                     |         |

| 2.7V to 6                                           | V       |

| 2.7V to 6                                           | V       |

|                                                     | V<br>/2 |

| Thermal Resistance (4) | $oldsymbol{	heta}_{JA}$ | $\boldsymbol{\theta}_{JC}$ |       |

|------------------------|-------------------------|----------------------------|-------|

| UTQFN-20 (2.5mmx3mm)   | 60                      | 13                         | .°C/W |

#### NOTES:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature  $T_J$  (MAX), the junction-to-ambient thermal resistance  $\theta_{JA}$ , and the ambient temperature  $T_A$ . The maximum allowable continuous power dissipation at any ambient temperature is calculated by  $P_D$  (MAX) =  $(T_J$  (MAX)- $T_A$ )/ $\theta_{JA}$ . Exceeding the maximum allowable power dissipation produces an excessive die temperature, causing the regulator to go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- The device is not guaranteed to function outside of its operating conditions.

- 4) Measured on JESD51-7, 4-layer PCB.

## **ELECTRICAL CHARACTERISTICS**

VIN1/2 = 3.6V, VIN3 = 3.6V,  $T_J$  = -40°C to 125°C <sup>(7)</sup>, typical value is tested at  $T_J$  = 25°C unless otherwise noted.

| Parameters                                       | Symbol                 | Condition                                                                                         | Min | Тур  | Max  | Units  |

|--------------------------------------------------|------------------------|---------------------------------------------------------------------------------------------------|-----|------|------|--------|

| Buck Regulators (5)                              |                        |                                                                                                   |     |      | ·    |        |

| Input voltage range                              | V <sub>IN1</sub>       | For VIN1                                                                                          | 2.7 |      | 6    | V      |

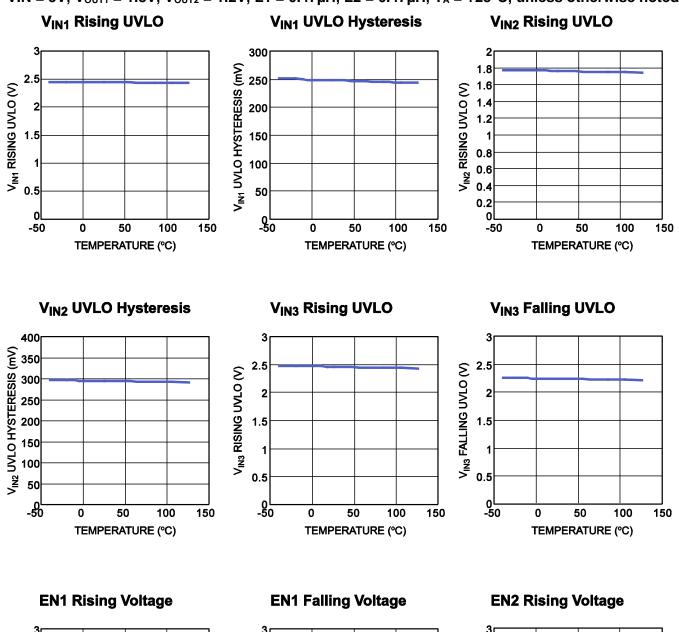

| Under-voltage lockout threshold rising           | V <sub>IN1_R</sub>     | For VIN1                                                                                          | 2.3 | 2.5  | 2.65 | V      |

| Under-voltage lockout threshold hysteresis       | V <sub>IN1_HYS</sub>   | For VIN1                                                                                          |     | 250  |      | mV     |

| Input voltage range for Rail2                    | $V_{\text{IN2}}$       | $VIN1 > V_{IN1\_R}$                                                                               | 2   |      | 6    | V      |

| VIN2 under-voltage lockout threshold rising      | $V_{IN2\_R}$           | For VIN2                                                                                          |     | 1.8  | 1.85 | V      |

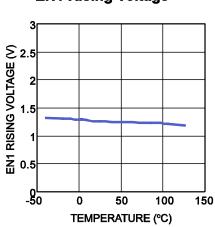

| VIN2 under-voltage lockout threshold hysteresis  | V <sub>IN2</sub> _HYS  | For VIN2                                                                                          |     | 300  |      | mV     |

| Supply current (shutdown)                        | I <sub>SD</sub>        | $V_{EN1/2/3} = 0V, T_J = 25^{\circ}C$                                                             |     |      | 1    | μΑ     |

| Supply current (quiescent)                       | I <sub>Q1+Q2</sub>     | $V_{EN1/2} = 2V$ , $V_{EN3} = 0V$ , $V_{FB1/2} = 1V$                                              |     | 85   | 110  | μΑ     |

| High-side switch on resistance for 3.5A switcher | R <sub>DS(ON)1_H</sub> |                                                                                                   |     | 55   |      | mΩ     |

| Low-side switch on resistance for 3.5A switcher  | R <sub>DS(ON)1_L</sub> |                                                                                                   |     | 20   |      | mΩ     |

| High-side switch on resistance for 2.5A switcher | R <sub>DS(ON)2_H</sub> |                                                                                                   |     | 65   |      | mΩ     |

| Low-side switch on resistance for 2.5A switcher  | R <sub>DS(ON)2_L</sub> |                                                                                                   |     | 22   |      | mΩ     |

| Switch leakage current                           | I <sub>LK_SW1/2</sub>  | V <sub>EN1/2</sub> = 0V, VIN1/2 = 6V,<br>V <sub>SW1/2</sub> = 0V and 6V,<br>T <sub>J</sub> = 25°C |     | 0    | 1    | μA     |

| High-side current limit for 3.5A switcher        | Ішм1_н                 | Duty = 33%                                                                                        | 4.5 | 5.6  |      | А      |

| High-side current limit for 2.5A switcher        | I <sub>LIM2_H</sub>    | Duty = 33%                                                                                        | 3.5 | 4.7  |      | Α      |

| Low-side zero crossing current                   | I <sub>ZCD1/2</sub>    | For both channels                                                                                 |     | 0.1  |      | Α      |

| Oscillator frequency                             | F <sub>SW1/2</sub>     | CCM                                                                                               | 1.2 | 1.5  | 1.8  | MHz    |

| Phase shift                                      | PhS                    | CCM                                                                                               |     | 180  |      | degree |

| Minimum on time (6)                              | T <sub>MIN</sub> ON    |                                                                                                   |     | 70   |      | ns     |

| Minimum off time (6)                             | T <sub>MIN_OFF</sub>   |                                                                                                   |     | 100  |      | ns     |

| Maximum duty cycle (6)                           | $D_{MAX}$              |                                                                                                   |     | 100  |      | %      |

|                                                  | V <sub>FB1/2</sub>     | T <sub>J</sub> = 25°C                                                                             | 594 | 600  | 606  | mV     |

| Feedback voltage                                 |                        | $T_J = -40^{\circ}\text{C to } 125^{\circ}\text{C}^{(7)}$                                         | 591 | 600  | 609  | mV     |

| Feedback currents                                | <b>I</b> FB1/2         | FB1/2 = 0.65V                                                                                     |     | 10   | 50   | nA     |

| Internal soft-start time                         | T <sub>SS1/2</sub>     | From 10% Vout to 90% Vout                                                                         |     | 0.35 |      | ms     |

| Output discharge resistor                        | R <sub>DIS1/2</sub>    |                                                                                                   |     | 13   |      | Ω      |

# **ELECTRICAL CHARACTERISTICS** (continued)

VIN1/2 = 3.6V, VIN3 = 3.6V,  $T_J$  = -40°C to 125°C <sup>(7)</sup>, typical value is tested at  $T_J$  = 25°C unless otherwise noted.

| Parameters                                 | Symbol                                                       | Condition                                          | Min  | Тур | Max  | Units |

|--------------------------------------------|--------------------------------------------------------------|----------------------------------------------------|------|-----|------|-------|

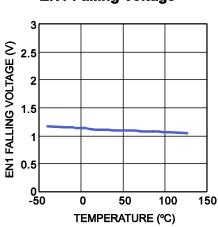

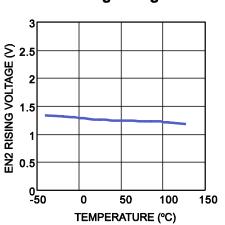

| EN high logic                              | EN <sub>1/2_H</sub>                                          |                                                    | 1.05 | 1.3 | 1.5  | V     |

| EN hysteresis                              | EN <sub>1/2_HYS</sub>                                        |                                                    |      | 150 |      | mV    |

| ENIA/O input accordant                     |                                                              | V <sub>EN</sub> = 2V                               |      | 1   |      |       |

| EN1/2 input current                        | I <sub>EN1/2</sub>                                           | V <sub>EN</sub> = 0V                               |      | 0   |      | μA    |

| EN1 turn-on delay                          | EN <sub>TD_1</sub>                                           | For channel 1                                      |      | 100 |      | μs    |

| EN2 turn-on delay                          | EN <sub>TD_2</sub>                                           | For channel 2,<br>VIN1 > V <sub>IN1_R</sub>        |      | 100 |      | μs    |

| Power good upper trip threshold            | PG <sub>1/2_H</sub>                                          | FB with respect to the regulation                  |      | +30 |      | %     |

| Power good lower trip threshold            | PG <sub>1/2_L</sub>                                          | FB with respect to the regulation                  |      | -10 |      | %     |

| Power good hysteresis                      | PG <sub>HY</sub>                                             |                                                    |      | 5   |      | %     |

| Power good delay for rising                | PD <sub>TD_1/2</sub> H                                       |                                                    |      | 20  |      | μs    |

| Power good delay for falling               | PD <sub>TD_1/2</sub> L                                       |                                                    |      | 60  |      | μs    |

| Power good sink current capability         | V <sub>PG_LO_1/2</sub>                                       | Sink 1mA                                           |      |     | 0.4  | V     |

| Power good leakage current                 | PG <sub>LK_1/2</sub>                                         | V <sub>PG</sub> = 1.8V                             |      | 1   |      | μA    |

| Load Switch                                |                                                              |                                                    |      |     |      |       |

| Input voltage range                        | $V_{IN3} \qquad \frac{VIN1 > V_{IN1\_R}}{VIN1 < V_{IN1\_R}}$ | $VIN1 > V_{IN1\_R}$                                | 0.6  |     | 6    | V     |

| Input voltage range                        |                                                              | 2.7                                                |      | 6   | V    |       |

| Under-voltage lockout threshold rising     | V <sub>IN3_R</sub>                                           | For VIN3                                           | 2.3  | 2.5 | 2.65 | V     |

| Under-voltage lockout threshold hysteresis | VIN3_HYS                                                     | For VIN3                                           |      | 200 |      | mV    |

| Supply current (quiescent)                 | I <sub>Q3</sub>                                              | From VIN3, $V_{EN1/2} = 0V$ , $V_{EN3} = 3.6V$     |      | 160 | 250  | μA    |

| On resistor                                | R <sub>DSON</sub>                                            |                                                    |      | 20  |      | mΩ    |

| EN3 high logic threshold                   | EN <sub>3_H</sub>                                            |                                                    | 1.05 | 1.3 | 1.5  | V     |

| EN3 hysteresis                             | EN <sub>3_HYS</sub>                                          |                                                    |      | 150 |      | mV    |

| EN3 turn-on delay                          | EN <sub>TD_3</sub>                                           | VIN1 > V <sub>IN1_R</sub>                          |      | 70  |      | μs    |

| LN3 turn-on delay                          | LINID_3                                                      | VIN1 < V <sub>IN1_R</sub>                          |      | 70  |      |       |

| EN3 input current                          |                                                              | V <sub>EN3</sub> = 2V                              |      | 1   |      |       |

| ENS Input current                          | I <sub>EN3</sub>                                             | $V_{EN3} = 0V$                                     |      | 0   |      | μA    |

| PG3 high logic threshold                   | PG <sub>3_H</sub>                                            | VIN3 - V <sub>оитз</sub> is smaller than the range | 150  | 200 |      | mV    |

| PG3 low logic threshold                    | PG <sub>3_L</sub>                                            | VIN3 - V <sub>OUT3</sub> is larger than the range  |      | 250 |      | mV    |

| Power good delay for rising                | PD <sub>TD_3</sub>                                           |                                                    |      | 40  |      | μs    |

| Power good sink current capability         | V <sub>PG_LO_3</sub>                                         | Sink 1mA                                           |      |     | 0.4  | V     |

| Power good leakage current                 | PG <sub>LK_3</sub>                                           | V <sub>PG</sub> = 1.8V                             |      | 1   |      | μΑ    |

| Current limit                              | I <sub>LIM3</sub>                                            |                                                    |      | 5.6 |      | Α     |

# **ELECTRICAL CHARACTERISTICS** (continued)

VIN1/2 = 3.6V, VIN3 = 3.6V,  $T_J$  = -40°C to 125°C <sup>(7)</sup>, typical value is tested at  $T_J$  = 25°C unless otherwise noted.

| Parameters                                 | Symbol              | Condition                                                             | Min | Тур  | Max | Units |

|--------------------------------------------|---------------------|-----------------------------------------------------------------------|-----|------|-----|-------|

| Internal soft-start time                   | T <sub>ss3</sub>    | From 10% V <sub>OUT</sub> to 90% V <sub>OUT</sub>                     |     | 0.35 |     | ms    |

| Output resistor                            | R <sub>DIS</sub>    |                                                                       |     | 13   |     | Ω     |

| Power Failure Circuitry                    |                     |                                                                       |     |      |     |       |

| V <sub>SUS</sub> voltage                   | V <sub>SUS</sub>    |                                                                       |     | 3.6  |     | V     |

| V <sub>SUS</sub> leakage current           | I <sub>SUS_LK</sub> | V <sub>SUS</sub> = 3.6V, VIN1 = VIN3<br>= 3.6V, T <sub>J</sub> = 25°C |     | 0    | 1   | μA    |

| DEL AD L'reference                         | PFL_ADJ             | T <sub>A</sub> = 25°C                                                 | 594 | 600  | 606 | mV    |

| PFL_ADJ reference                          |                     | $T_A = -40^{\circ}\text{C to } 125^{\circ}\text{C}^{(7)}$             | 591 | 600  | 609 |       |

| PFL hysteresis                             | PFL_HYS             |                                                                       |     | 3    |     | %     |

| PFL high-to-low delay                      | T <sub>PFL_HL</sub> |                                                                       |     | 1    |     | μs    |

| C <sub>DELAY</sub> internal current source | I <sub>DELAY</sub>  |                                                                       |     | 3.1  |     | μA    |

| Power good sink current capability         | $V_{PFL\_LO}$       | Sink 1mA                                                              |     |      | 0.4 | V     |

| Power good leakage current                 | PFLLK               | V <sub>PFL</sub> = 1.8V                                               |     | 1    |     | μΑ    |

| Thermal shutdown (6)                       | T <sub>SD</sub>     |                                                                       |     | 160  |     | °C    |

| Thermal hysteresis (6)                     | T <sub>HYS</sub>    |                                                                       |     | 30   |     | °C    |

#### NOTES:

- 5) VIN1 provides control voltage if VIN3 is lower than 2.7V.

- 6) Guaranteed by design.

- 7) Guaranteed by characterization test, not production tested.

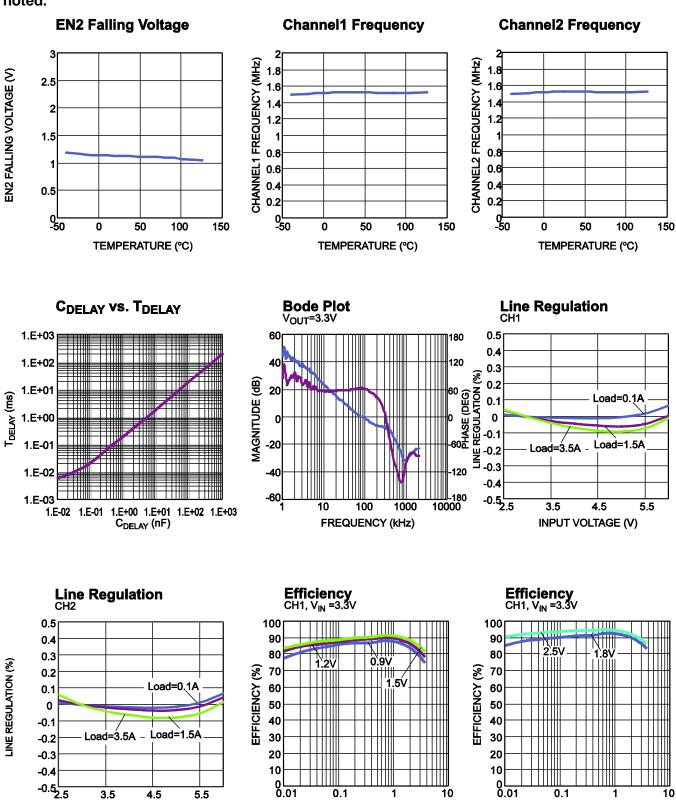

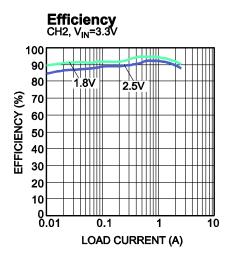

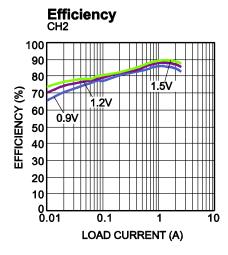

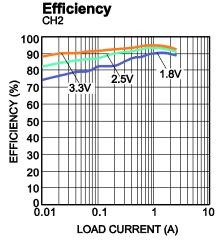

## TYPICAL PERFORMANCE CHARACTERISTICS

VIN = 5V,  $V_{OUT1}$  = 1.8V,  $V_{OUT2}$  = 1.2V, L1 = 0.47 $\mu$ H, L2 = 0.47 $\mu$ H,  $T_A$  = +25°C, unless otherwise noted.

## TYPICAL PERFORMANCE CHARACTERISTICS (continued)

VIN = 5V,  $V_{OUT1}$  = 1.8V,  $V_{OUT2}$  = 1.2V, L1 = 0.47 $\mu$ H, L2 = 0.47 $\mu$ H,  $T_A$  = +25°C, unless otherwise noted.

INPUT VOLTAGE (V)

LOAD CURRENT (A)

LOAD CURRENT (A)

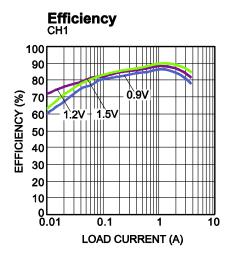

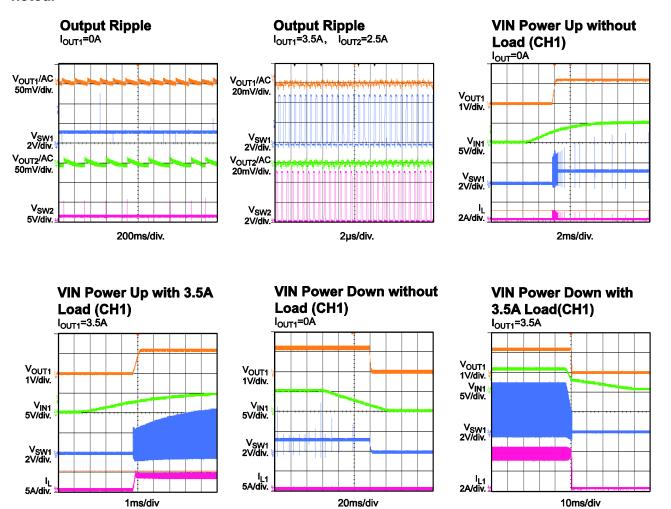

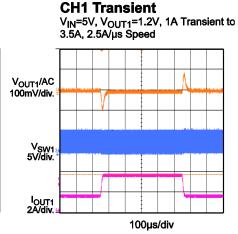

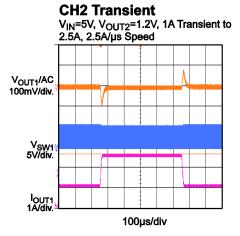

## TYPICAL PERFORMANCE CHARACTERISTICS (continued)

VIN = 5V,  $V_{OUT1}$  = 1.8V,  $V_{OUT2}$  = 1.2V, L1 = 0.47 $\mu$ H, L2 = 0.47 $\mu$ H,  $T_A$  = +25°C, unless otherwise noted.

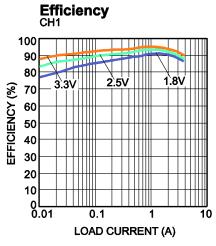

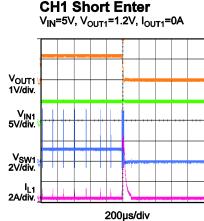

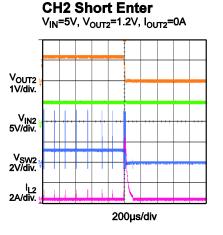

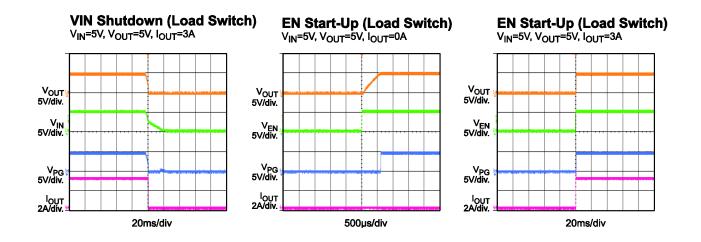

## TYPICAL PERFORMANCE CHARACTERISTICS (continued)

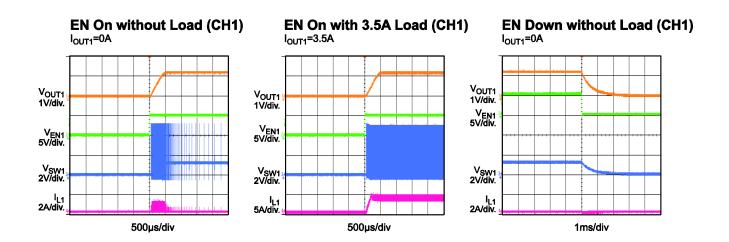

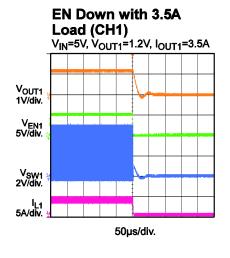

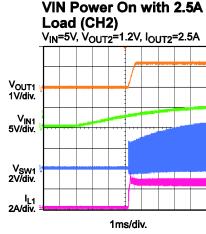

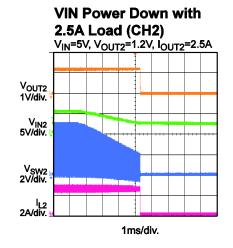

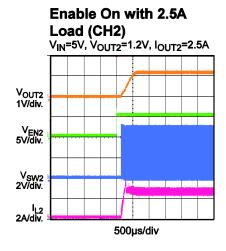

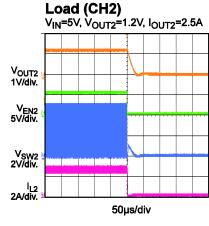

VIN = 5V,  $V_{OUT1}$  = 1.2V,  $V_{OUT2}$  = 1.2V, L1 = 0.47 $\mu$ H, L2 = 0.47 $\mu$ H,  $T_A$  = +25°C, unless otherwise noted.

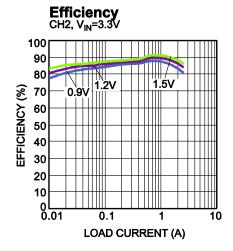

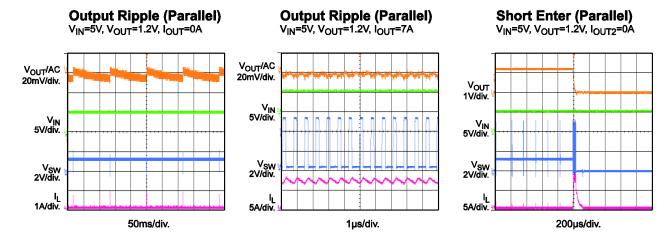

## TYPICAL PERFORMANCE CHARACTERISTICS (continued)

VIN = 5V,  $V_{OUT1}$  = 1.2V,  $V_{OUT2}$  = 1.2V, L1 = 0.47 $\mu$ H, L2 = 0.47 $\mu$ H,  $T_A$  = +25°C, unless otherwise noted.

**Enable Down with 2.5A**

## TYPICAL PERFORMANCE CHARACTERISTICS (continued)

VIN = 5V,  $V_{OUT1}$  = 1.2V,  $V_{OUT2}$  = 1.2V, L1 = 0.47 $\mu$ H, L2 = 0.47 $\mu$ H,  $T_A$  = +25°C, unless otherwise noted.

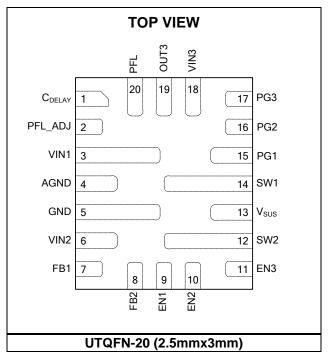

## **PIN FUNCTIONS**

| Pin# | Name               | Description                                                                                                                                                                                                                                                   |

|------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | C <sub>DELAY</sub> | <b>Programmable PFL low-to-high delay time.</b> When C <sub>DELAY</sub> is floated, the delay time is minimized.                                                                                                                                              |

| 2    | PFL_ADJ            | <b>Power failure threshold adjust.</b> A resistor divider connected to the voltage rails is used to program the power failure threshold. The resistor divider needs to be monitored.                                                                          |

| 3    | VIN1               | Input supply voltage to the 3.5A switching regulators and internal logic module. Place a small decoupling capacitor as close to VIN1 and GND as possible.                                                                                                     |

| 4    | AGND               | Analog ground.                                                                                                                                                                                                                                                |

| 5    | GND                | Ground.                                                                                                                                                                                                                                                       |

| 6    | VIN2               | <b>Input supply voltage to the 2.5A switching regulators.</b> Place a small decoupling capacitor as close to VIN2 and GND as possible.                                                                                                                        |

| 7    | FB1                | <b>Feedback voltage sensing for the 3.5A regulator.</b> Connect the output voltage of the 3.5A regulator through a resistor divider to FB1 to achieve output voltage regulation. Pull FB1 to ground to operate the 3.5A regulator in 100% duty cycle on mode. |

| 8    | FB2                | Feedback voltage sensing for the 2.5A regulator. Connect the output voltage of the 2.5A regulator through a resistor divider to FB2 to achieve output voltage regulation. Pull FB2 to ground to operate the 2.5A regulator in 100% duty cycle on mode.        |

| 9    | EN1                | <b>Enable on/off control for the 3.5A regulator.</b> There is a $2M\Omega$ resistor from EN1 to GND internally. Float or ground EN1 to turn off the 3.5A regulator.                                                                                           |

| 10   | EN2                | <b>Enable on/off control for the 2.5A regulator.</b> There is a $2M\Omega$ resistor from EN2 to GND internally. Float or ground EN2 to turn off the 2.5A regulator.                                                                                           |

| 11   | EN3                | Enable on/off control for the load switch. There is a $2M\Omega$ resistor from EN3 to GND internally. Float or ground EN3 to turn off the load switch.                                                                                                        |

| 12   | SW2                | <b>Switch output for the 2.5A regulator.</b> A thick and wide power routing trace is recommended for SW2 to conduct current.                                                                                                                                  |

| 13   | Vsus               | Sustain voltage. Place a small decoupling capacitor as close to $V_{\text{SUS}}$ and GND as possible.                                                                                                                                                         |

| 14   | SW1                | <b>Switch output for the 3.5A regulator.</b> A thick and wide power routing trace is recommended for SW1 to conduct current.                                                                                                                                  |

| 15   | PG1                | <b>Power good for the 3.5A regulator.</b> PG1 is an open-drain output. When the output voltage is between -10% to +30% of the regulation, PG1 is pulled high externally. When there is no supply, PG1 is pulled low internally.                               |

| 16   | PG2                | <b>Power good for the 2.5A regulator.</b> PG2 is an open-drain output. When the output voltage is between -10% to +30% of the regulation, PG2 is pulled high externally. When there is no supply, PG2 is pulled low internally.                               |

| 17   | PG3                | <b>Power good for the load switch.</b> PG3 is an open-drain output. When the output voltage is below 200mV compared with the input voltage, PG3 is pulled high externally.                                                                                    |

| 18   | VIN3               | Input supply voltage for the load switch.                                                                                                                                                                                                                     |

| 19   | OUT3               | Output voltage for the load switch.                                                                                                                                                                                                                           |

| 20   | PFL                | <b>Power failure indicator.</b> PFL is an open-drain output. When the PFL_ADJ voltage is less than 0.6V, PFL is pulled low immediately.                                                                                                                       |

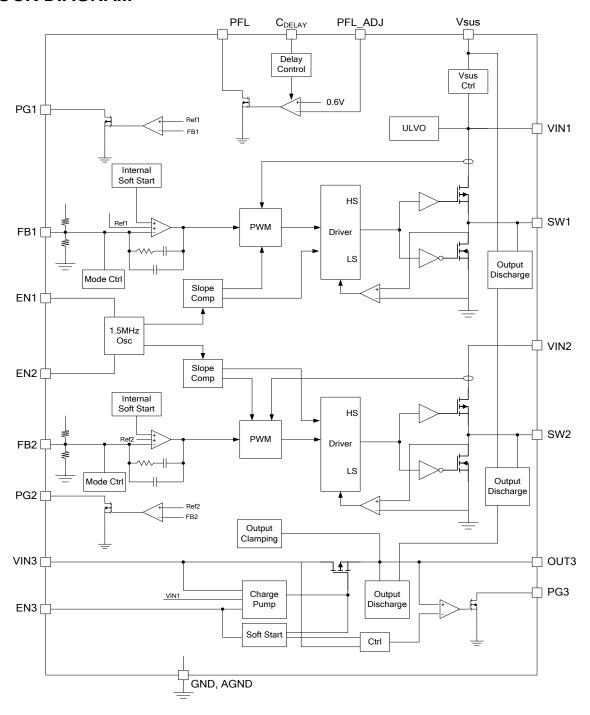

## **BLOCK DIAGRAM**

**Figure 1: Functional Block Diagram**

## **OPERATION**

The MP5403 has two step-down regulators and one load switch integrated into an ultra-small UTQFN-20 package. The two buck regulators are able to run up to 3.5A and 2.5A of load current, respectively. With a peak current mode control scheme and an interleaving PWM clock, the MP5403 minimizes the input voltage ripple and achieves a fast dynamic load response. The load switch has 3A and only  $20m\Omega$  of  $R_{DS(ON)}$ , achieves extremely small conduction loss, and provides tight regulation with a high load current. The load switch can also clamp  $V_{OUT}$  to 5.5V. The MP5403 can be used in compact solid-state drives (SSD), portable instruments, and battery-powered devices.

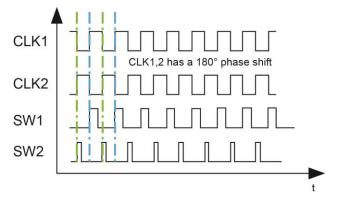

#### **Peak-Current Mode Control**

The two buck regulators of the MP5403 operate at an 180° phase shift to reduce the input current ripple and the required input capacitor. In continuous conduction mode (CCM), two internal clocks control the switching behavior. The high-side MOSFET (HS-FET) turns on at the corresponding clock's rising edge. The two clocks are at an 180° phase shift. When the high-side switch current increases and reaches the internal compensation voltage, the high-side switch is turned off, and the low-side switch is turned on to conduct current.

Figure 2: Phase Shift

The switching frequency is 1.5MHz, typically, running in CCM. With a lower input voltage, the switching frequency falls and works with a large duty cycle and a fixed off-time mode.

#### **Light-Load Operation**

In light load mode, the MP5403 uses a proprietary control scheme to save power and improve efficiency. The MP5403 turns off the low-side switch when the inductor current begins reversing. The MP5403 then works in discontinuous conduction mode (DCM) operation. With light-load mode control, the switching loss can be greatly reduced due to the lower switching frequency.

A zero-current cross detection (ZCD) circuit is used to detect if the inductor current begins reversing. Considering the internal circuit propagation time, the typical delay is 50ns. This means that the inductor current continues falling after ZCD is triggered in this delay. If the inductor current falling slew rate is fast (Vout is high or close to VIN), the low-side MOSFET (LS-FET) is turned off, and the inductor current may be negative. This prevents the MP5403 from entering DCM operation. If DCM operation is required, the off time of the LS-FET in CCM should be longer than 100ns. For example, if VIN is 3.6V and V<sub>OUT</sub> is 3.4V, then the off time in CCM is 37ns. It is difficult to enter DCM at light load. Using a smaller inductor can improve this and make it easier to enter DCM.

#### Enable (EN)

When VIN1 is greater than the under-voltage lockout (UVLO) threshold (typically 2.5V), the regulators or the load switch can be enabled by pulling its EN pins above the EN UVLO threshold. Leave the EN pins floating or pull the EN pins down to ground to disable the corresponding channel. There is an internal  $2M\Omega$  resistor from the EN pins to ground. There is a delay of about 100µs for the VIN1 and VIN2 enable start-up. The VIN3 enable start-up delay is shorter (around 70µs).

#### Soft Start (SS) and Output Discharge

The MP5403 has a built-in soft start (SS) that ramps up the output voltage at a controlled slew rate to prevent overshooting at start-up for both step-down regulators and the load switch. For the step-down regulator, the soft-start time is about 500µs, typically. For the load switch, the soft-start time is set to around 350µs. When the regulators are disabled, the internal discharge

resistor discharges  $V_{\text{OUT}}$ . The discharge resistor is biased by  $V_{\text{SUS}}$  (see Table 1).

**Table 1: Output Discharge Conditions**

| Output Discharge | VIN                                | EN   |

|------------------|------------------------------------|------|

| No               | >UVLO                              | High |

| Yes              | >UVLO                              | Low  |

| Yes              | <uvlo< td=""><td>High</td></uvlo<> | High |

| Yes              | <uvlo< td=""><td>Low</td></uvlo<>  | Low  |

## **Power Good (PG) Indicators**

The MP5403 has three separate power good (PG), open-drain, output indicators for the regulators and load switch. For the two stepdown regulators, when FB is in the regulation window (between 90% to 130% of the reference voltage, 0.6V), PG1 and PG2 are pulled up to the external bus voltage through external resistors. The pull-up resistors are recommend not to be too low to ensure that the leakage current is small when the PG pins are low and not too high if the PG pins are used to drive the downstream signals. Normally, pull-up resistors between  $10k\Omega$  to  $400k\Omega$  are sufficient. The PG rising delay is around 20µs. If the FB voltage drops below 90% or above 130% of the reference voltage, the PG pins are pulled down to ground by an internal MOSFET. The MOSFET has a maximum R<sub>DS(ON)</sub> of less than  $400\Omega$ . There is also a  $60\mu s$  delay for the PG falling threshold trigger.

The power good pin for the load switch (PG3) is pulled high when the input voltage of the load switch (VIN3) is higher than its UVLO threshold, the output voltage (VOUT3) is less than 200mV compared with the input voltage of the load switch, and there is around 40µs of rising delay for the PG3 indicator. If any of these three conditions are not met, PG3 is pulled low.

The PG indicators are pulled low when VIN1 is below UVLO. In this condition, the PG pins are self-driven low (around 0.6V).

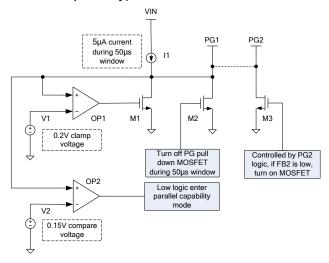

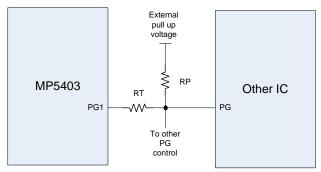

There is another important feature on PG to detect the parallel capability usage (see Figure 3). After VIN rises above ULVO and either EN1 or EN2 is high, the MP5403 uses an internal 50µs detection time window to determine if the buck regulator is entering parallel mode. The

schematic in Figure 3 is only active in the 50µs detection window.

During this 50 $\mu$ s time window, the PG1 (M2) switch is turned off, and an internal 5 $\mu$ A pulled high current is applied on PG1. The PG2 (M3) switch (<400 $\Omega$ ) is turned on. If the PG1 voltage is <150mV, the MP5403 enters parallel mode (EN1 controls the parallel mode on/off). If the PG1 voltage is >150mV, the MP5403 enters independent working mode (EN1 and EN2 control separately).

Figure 3: PG Functional Schematic

If PG1 is connected to PG2 externally, the PG1 voltage is pulled below 150mV to make the MP5403 enter parallel mode.

The PG1 connection requires special consideration (see Figure 4). If PG1 is connected to another IC's PG to control the other device together, a resistor (RT) is required to prevent the MP5403 from entering parallel mode. RT is suggested to be  $50k\Omega$ .

Figure 4: PG Connection Example

## **Power Failure Indicator (PFL)**

The power failure indicator (PFL) senses the external voltage rails. When the input voltage is below the programmed threshold, the PFL open-drain output is pulled low immediately to indicate the monitored power failure. This function is enabled by pulling any of the EN pins (EN1, EN2, or EN3) high and disabled by pulling all of the EN pins low. For example, if all EN pins are low, PFL is zero, even if VIN is above the UVLO threshold and PFL\_ADJ is higher than 0.6V. Ensure that there is at least one EN pin that is high before using it to control the other pins.

PFL\_ADJ is used to adjust the power failure threshold voltage. A resistor divider is used to monitor the voltage rail. When the PFL\_ADJ voltage is lower than 0.6V, PFL is pulled down to indicate the sense power failure. When the PFL\_ADJ voltage is higher than the 0.6V reference voltage, PFL is pulled high with the delay, which is set by CDELAY.

Choose C<sub>DELAY</sub> using Equation (1):

$$T_{DELAY}(\mu s) = \frac{C_{DELAY}(pF) \times 0.62}{I_{DELAY}(\mu A)} + 3.5 \mu s$$

(1)

Where  $T_{DELAY}$  is the PFL delay time, and  $I_{DELAY}$  is the  $C_{DELAY}$  internal current source (typically 3.1µA).

#### **Current Limit**

The MP5403 has a high-side 5.6A current limit for the first regulator and a 4.7A current limit for the second regulator. When the high-side switch reaches the current limit threshold, the regulators shut down the high-side switch and force the low-side switch on until the low-side current drops to the low-side valley current threshold (5A and 4A for the two regulators). After the low-side current reaches the valley current threshold, the high-side switch is allowed to turn on again. If the high load current persists, the high side turns on again, and the current limit mechanism repeats until the output voltage drops to the short-circuit threshold. If the high-load current does not persist, then the regulator runs back to normal condition.

For the load switch, the current limit begins working when the load switch current reaches the current limit threshold. The gate is pulled low to regulate the load switch current to the current limit. The output voltage drops until thermal shutdown occurs.

### **Short Circuit and Recovery**

When CH1 or CH2 is in buck mode, the MP5403 enters short-circuit protection (SCP) mode when the inductor current reaches the current limit for 300µs continuously or the output voltage drops below 50% of the regulation voltage. In SCP mode, the MP5403 disables the output power stage, discharges the soft-start capacitor, and enters latch-off protection mode. The MP5403 restarts by recycling the power.

## **Parallel Capability**

By connecting SW1 and SW2 together and connecting PG1 and PG2 together, the two step-down regulators can run in parallel mode to increase the output power capability. In this mode, only FB1 is used to program the output voltage. Keep FB2 floating.

#### Load-Switch Mode of Buck1/2

By pulling FB1 or FB2 to ground, the step-down regulator 1 or 2 can enter load-switch mode without having to install an inductor. The MP5403 pulses a smaller current to the FB pins before the system starts up. If a low impedance is connected to the FB pins, the MP5403 enters load-switch mode, where the high-side switch is turned on gradually to achieve a soft start, and short-circuit protection is equipped.

# APPLICATION INFORMATION Output Voltage Setting

The output voltage of the two switchers can be adjusted with external resistor dividers (see Figure 5). The typical reference voltage of both FB1 and FB2 is 600mV. The maximum allowed voltage for the outputs is close to the input voltage minus the voltage drop when the high-side switch is 100% turned on.

Figure 5: Feedback Resistor Dividers to Set the Output Voltages

The divider current is recommended to be higher than 500nA to avoid influence from the feedback node leakage current (which is in the 10nA level). Additionally, considering control loop optimization, the pull-up resistor is recommended to be between  $100k\Omega$  to  $500k\Omega$ . Then, the pull-down resistor can be calculated with Equation (2):

R2(orR4) =

$$\frac{\text{R1(orR3)}}{\frac{\text{V}_{\text{OUT}}}{\text{0.6V}} - 1}$$

(2)

Table 2 shows some typical output voltages and their corresponding recommended resistor divider values.

Table 2: Output Voltage vs. Resistor Values

| V <sub>out</sub> | R1    | R2     |

|------------------|-------|--------|

| 1.2V             | 300kΩ | 300kΩ  |

| 1.5V             | 300kΩ | 200kΩ  |

| 1.8V             | 300kΩ | 150kΩ  |

| 2.5V             | 300kΩ | 95.3kΩ |

| 3.3V             | 300kΩ | 66.5kΩ |

NOTE: C<sub>OUT</sub> is 22µF for each channel.

## **Inductor Selection**

The inductor has a great impact on several key performances for the step-down switcher, such as inductor current ripple, output voltage ripple, efficiency, and load transient response.

Calculate the inductor current ripple with Equation (3):

$$\Delta I_{L} = \frac{V_{OUT} (V_{IN} - V_{OUT})}{V_{IN} \cdot L \cdot f_{SW}}$$

(3)

Calculate the inductor peak current with Equation (4):

$$I_{Lpk} = I_{Load} + \frac{\Delta I_L}{2}$$

(4)

Choosing the inductance is a trade-off between the output ripple, efficiency, and transient response. The larger the inductance is, the smaller the output ripple, but the slower the response. Choose an inductance to make the ripple current 30% to 40% of the max load current.

The inductor saturation current must be higher than the inductor peak current.

The inductor also impacts the solution efficiency in terms of conduction loss and coil-related loss. Generally, the DC resistance provides DC conduction loss information. For AC conduction loss and coil-related loss, please refer to the vendor datasheet for more detailed information.

#### **Input Capacitor Selection**

The input capacitor reduces the surge current drawn from the input and the switching noise from the device. Select an input capacitor with a switching frequency impedance less than the input source impedance to prevent high-frequency switching current from passing to the input source. Use low ESR ceramic capacitors with X5R or X7R dielectrics and small temperature coefficients. For most applications, a 22µF capacitor is sufficient.

## **Output Capacitor Selection**

The output capacitor limits the output voltage ripple and ensures a stable regulation loop. Select an output capacitor with low impedance at the switching frequency. Use ceramic capacitors with X5R or X7R dielectrics. Using an electrolytic capacitor may result in additional output voltage ripple, thermal issues, and require additional care in selecting the feedback resistor (R1) due to the large ESR. For most applications, a 22µF capacitor is sufficient.

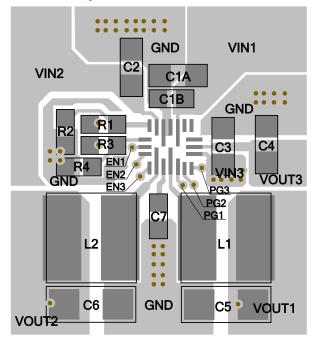

## **PCB Layout Guidelines**

Efficient PCB layout of the switching power supplies is critical for stable operation. If the layout is not done carefully, regarding the high switching frequency converter especially, the regulator could show poor line or load regulation and stability issues. For best results, refer to Figure 6 and follow the guideline below.

Place the input capacitor as close to the IC pins as possible for the high-speed stepdown regulator to provide clean control voltage.

**Top Layer**

Bottom Layer

Figure 6: Recommended PCB Layout

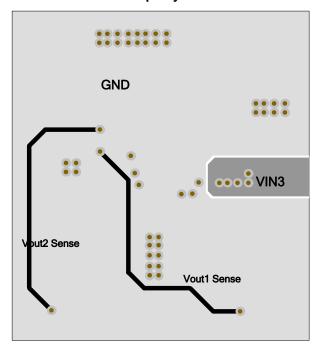

# **TYPICAL APPLICATION CIRCUITS**

Figure 7: Typical System Architecture Using 2 Units

Figure 8: Typical System Architecture Using Parallel

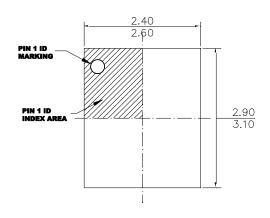

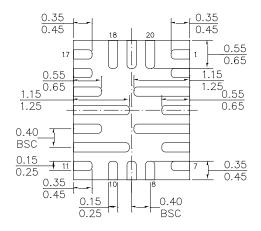

## **PACKAGE INFORMATION**

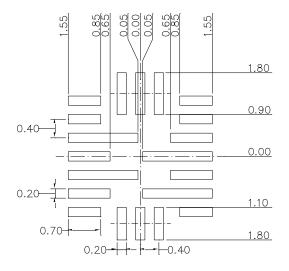

## **UTQFN-20 (2.5mmx3mm)**

**TOP VIEW**

**BOTTOM VIEW**

#### **SIDE VIEW**

## **NOTE:**

- 1) LAND PATTERN OF PIN3,5,12 AND 14 HAVE THE SAME LENGTH AND WIDTH.

- 2) LAND PATTERN OF PIN4,6,13 AND 15 HAVE THE SAME LENGTH AND WIDTH.

- 3)ALL DIMENSIONS ARE IN MILLIMETERS.

- 4) EXPOSED PADDLE SIZE DOES NOT INCLUDE MOLD FLASH.

- 5) LEAD COPLANARITY SHALL BE 0.10 MILLIMETERS MAX.

- 6) DRAWING CONFIRMS TO JEDEC MO-220.

- 7) DRAWING IS NOT TO SCALE.

## **RECOMMENDED LAND PATTERN**

**NOTICE:** The information in this document is subject to change without notice. Please contact MPS for current specifications. Users should warrant and guarantee that third party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.