# MP5029-C

USB Charging Port Controller with Current-Limit Switch, Supporting CDP, DCP, and QC3.0 Modes

## DESCRIPTION

The MP5029-C is a fully integrated, USB Type-C port controller, which is also compatible with a legacy Type-A port. It integrates a low-R<sub>DS(ON)</sub> USB current-limit switch and charging port identification circuit. The MP5029-C supports 3A of continuous output current.

The MP5029-C supports charging downstream port (CDP) mode, dedicated charging port (DCP) schemes for battery charging specification (BC1.2), divider mode, 1.2V/1.2V mode, and quick-charge specification (QC3.0) without the need for external user interaction. The MP5029-C can also support Type-C 5V @ 3A DFP mode.

Full protection features include hiccup current limiting, input over-voltage protection (OVP), thermal shutdown (TSD), and short-to-battery protection.

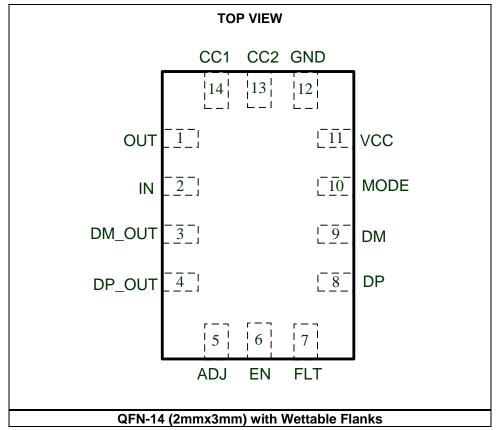

The MP5029-C requires a minimal number of readily available, standard external components to complete the USB switch and charging mode auto-detection solution. The MP5029-C is available in a QFN-14 (2mmx3mm) package.

## FEATURES

- Up to 22V Voltage Rating for Input and Output

- Supports BC1.2 CDP Mode

- Supports 5V DCP schemes for BC1.2, Divider Mode, 1.2V/1.2V Mode

- Supports QC3.0 (3.6V to 12V Output) Mode

- Supports Type-C 5V @ 3A DFP Mode

- I/O Pins (DP, DM, CC1, and CC2) Support Short-to-Battery Protection

- OUT Short-to-Battery Protection when V<sub>BUS</sub> Is Enabled

- Line Drop Compensation for 5V Output

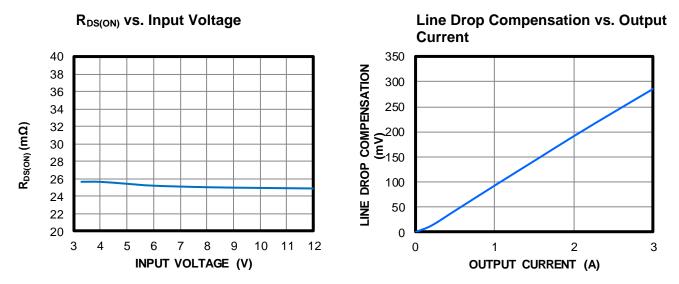

- 25mΩ Low R<sub>DS(ON)</sub> Power MOSFET

- MODE Pin to Program Charging Mode

- Intelligent Load Shedding vs. Temperature Function

- Fault Indication for Over-Current, Input OVP, Thermal Shutdown, and Short-to-Battery Fault

- OCP, OVP, and OTP Protections

- Input Over-Voltage Discharge

- ±8kV HBM ESD Rating CC1, CC2, and OUT to GND

- ±2kV HBM ESD Rating DM, DP to GND

- 1W VCONN Power Supply

- Available in a QFN-14 (2mmx3mm) Package with Wettable Flanks

## APPLICATIONS

- USB Charging Downstream Ports (CDP)

- USB Type-C Port

- Dedicate Charging Port (DCP)

- USB Hub

All MPS parts are lead-free, halogen free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance. "MPS", the MPS logo, and "Simple, Easy Solutions" are registered trademarks of Monolithic Power Systems, Inc. or its subsidiaries.

# **TYPICAL APPLICATION**

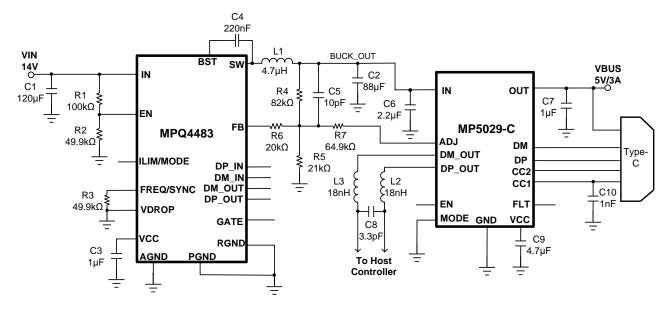

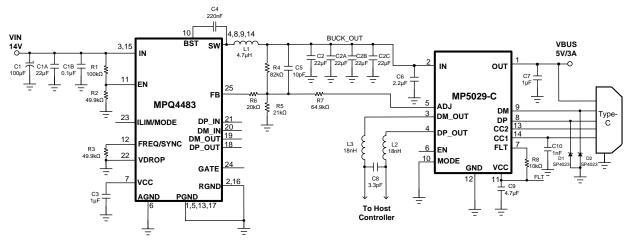

Type-C Port with USB2.0 CDP Mode Application

## **ORDERING INFORMATION**

| Part Number* | Package          | Top Marking |

|--------------|------------------|-------------|

| MP5029GD-C   | QFN-14 (2mmx3mm) | See Below   |

\* For Tape & Reel, add suffix -Z (e.g. MP5029GD-C-Z).

**TOP MARKING**

BMQ YWW

BMQ: Product code Y: Year code WW: Week code LLLL: Lot number

# **PIN FUNCTIONS**

| Pin # | Name   | Description                                                                                                                                                                                                                                            |  |

|-------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1     | OUT    | Output of USB current-limit switch.                                                                                                                                                                                                                    |  |

| 2     | IN     | <b>Supply voltage.</b> The MP5029-C can operate with a 5V typical input voltage for Type-C and USB2.0 applications, or a 3.6V to 12V input voltage for QC3.0 applications.                                                                             |  |

| 3     | DM_OUT | D- data line to USB host controller.                                                                                                                                                                                                                   |  |

| 4     | DP_OUT | D+ data line to USB host controller.                                                                                                                                                                                                                   |  |

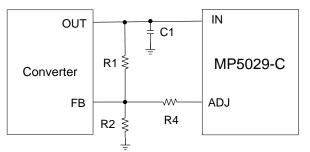

| 5     | ADJ    | <b>Output voltage adjustment pin.</b> ADJ sinks a current from the upstream DC/DC converter's FB pin to ground to regulate the DC/DC converter's output voltage. ADJ also provides line drop compensation.                                             |  |

| 6     | EN     | <b>Enable control pin.</b> Apply a logic high voltage to EN to enable the IC. Pull EN to logic low to disable the IC. EN has an internal $7\mu$ A auto pull-up current to the internal 3.5V power supply.                                              |  |

| 7     | FLT    | Fault indication. Open drain.                                                                                                                                                                                                                          |  |

| 8     | DP     | <b>D+ data line to USB connector.</b> DP is the input/output used for handshaking with portable devices.                                                                                                                                               |  |

| 9     | DM     | <b>D- data line to USB connector.</b> DM is the input/output used for handshaking with portable devices.                                                                                                                                               |  |

| 10    | MODE   | MP5029-C charging mode selection. Connect MODE to VCC, float MODE, or short MODE to ground to select three different modes.<br>VCC: DCP mode and enable QC3.0<br>Float: DCP mode and disable QC3.0<br>GND: CDP mode                                    |  |

| 11    | VCC    | Internal 3.5V LDO output. Bypass VCC with a 4.7µF ceramic capacitor.                                                                                                                                                                                   |  |

| 12    | GND    | Ground pin.                                                                                                                                                                                                                                            |  |

| 13    | CC2    | CC2 <b>Configuration channel.</b> CC2 is used to detect connections and configure<br>interface across the USB Type-C cables and connectors. Once a connective<br>established, CC1 or CC2 is reassigned to provide power over the VCONN pin of<br>plug. |  |

| 14    | CC1    | <b>Configuration channel.</b> CC1 is used to detect connections and configure the interface across the USB Type-C cables and connectors. Once a connection is established, CC1 or CC2 is reassigned to provide power over the VCONN pin of the plug.   |  |

## ABSOLUTE MAXIMUM RATINGS (1)

| Supply voltage (V <sub>IN</sub> )  | 0.3V to +24V                              |

|------------------------------------|-------------------------------------------|

| Output voltage (V <sub>OUT</sub> ) | 0.3V to +24V                              |

| CC1, CC2, DM, DP                   | 0.3V to +24V                              |

| DM_OUT, DP_OUT, VCC                | 0.3V to +4.5V                             |

| EN pin0.3V to +4V c                | or 250µA for >4V                          |

| All other pins                     | 0.3V to +4V                               |

| Continuous power dissipation (7    | Γ <sub>A</sub> = 25°C) <sup>(2) (5)</sup> |

| QFN-14 (2mmx3mm)                   | 3.29W                                     |

| Junction temperature               | 150°C                                     |

| Lead temperature                   | 260°C                                     |

| Storage temperature                |                                           |

#### **Recommended Operating Conditions** <sup>(3)</sup>

| Supply voltage (V <sub>IN</sub> )  | 5V or                             |

|------------------------------------|-----------------------------------|

|                                    | 3.6V - 12V (QC3.0) <sup>(4)</sup> |

| Output voltage (VOUT)              | follows with VIN                  |

| Output current (I <sub>OUT</sub> ) | up to 3A                          |

| Operating junction temp (T         |                                   |

#### Thermal Resistance $\theta_{JA} = \theta_{JC}$

QFN-14 (2mmx3mm)

| EV5029-C-GD-00A <sup>(5)</sup> | . 38 | .12 | °C/W |

|--------------------------------|------|-----|------|

| JESD51-7 <sup>(6)</sup>        | . 70 | 15  | °C/W |

#### Notes:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature  $T_J$  (MAX), the junction-toambient thermal resistance  $\theta_{JA}$ , and the ambient temperature  $T_A$ . The maximum allowable continuous power dissipation at any ambient temperature is calculated by  $P_D$  (MAX) = ( $T_J$  (MAX) -  $T_A$ ) /  $\theta_{JA}$ . Exceeding the maximum allowable power dissipation produces an excessive die temperature, causing the regulator to go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- 3) The device is not guaranteed to function outside of its operating conditions.

- 4) For lower  $V_{IN}$  applications, see the Operation section on page 17.

- 5) Measured on an EV5029-C-GD-00A, 4-layer PCB, 50mmx50mm.

- 6) Measured on a JESD51-7, 4-layer PCB. The value of  $\theta_{JA}$  given in this table is only valid for comparison with other packages, and cannot be used for design purposes. These values were calculated in accordance with JESD51-7 and simulated on a specified JEDEC board. They do not represent the performance obtained in an actual application.

# **ELECTRICAL CHARACTERISTICS**

## $V_{IN} = 5V$ , $T_J = -40^{\circ}C$ to $+125^{\circ}C$ <sup>(7)</sup>, typical value is tested at $T_J = 25^{\circ}C$ , unless otherwise noted.

| Parameter                                                     | Symbol                     | Condition                                                                              | Min  | Тур  | Max  | Units |

|---------------------------------------------------------------|----------------------------|----------------------------------------------------------------------------------------|------|------|------|-------|

| V <sub>IN</sub> under-voltage lockout rising threshold        | VIN_UVLO1                  | ADJ starts to work                                                                     | 2.7  | 3.0  | 3.3  | V     |

| UVLO hysteresis                                               | VUVLOHYS1                  |                                                                                        |      | 100  |      | mV    |

| Second V <sub>IN</sub> under-voltage lockout rising threshold | Vin_uvlo2                  | Power MOSFET turn-on                                                                   | 2.9  | 3.1  | 3.3  | V     |

| Second UVLO hysteresis                                        | VUVLOHYS2                  |                                                                                        |      | 200  |      | mV    |

| EN rising threshold                                           | $V_{EN\_R}$                |                                                                                        | 1.9  | 2.0  | 2.1  | V     |

| EN hysteresis                                                 | $V_{\text{EN}_{\text{F}}}$ |                                                                                        |      | 100  |      | mV    |

| EN auto pull-up current                                       | I <sub>EN_UP</sub>         |                                                                                        | 3.5  | 7.0  | 10.5 | μA    |

| VCC voltage                                                   | Vvcc                       | Ivcc = 0mA                                                                             | 3.3  | 3.5  | 3.7  | V     |

| Shutdown current                                              | I <sub>Q_STD</sub>         | EN = 0                                                                                 |      | 22   | 40   | μA    |

|                                                               |                            | V <sub>IN</sub> = 5V, Type-C detach mode                                               |      | 175  | 225  |       |

| Supply current                                                | lα                         | $V_{IN} = 5V$ , no load,<br>CC1 = 5.1k $\Omega$ , not including<br>CC1 pull-up current |      | 230  | 300  | μA    |

| MODE logic high voltage                                       | V <sub>Mode_H</sub>        |                                                                                        | 2    |      |      | V     |

| MODE float voltage                                            | V <sub>Mode_F</sub>        |                                                                                        | 1.15 |      | 1.95 | V     |

| MODE logic low voltage                                        | V <sub>Mode_L</sub>        |                                                                                        |      |      | 0.7  | V     |

| USB Power FET                                                 |                            |                                                                                        |      |      |      |       |

| On resistance                                                 | RDSON                      | V <sub>IN</sub> = 5V                                                                   |      | 25   | 45   | mΩ    |

| Input discharge resistance                                    | R <sub>DIS_IN</sub>        |                                                                                        | 150  | 200  | 250  | Ω     |

| Soft-start time                                               | tss                        | V <sub>IN</sub> = 5V, no load                                                          | 250  | 500  | 750  | μs    |

| Current Limit Set                                             | •                          |                                                                                        |      | •    | •    | •     |

| USB current limit                                             | ILIMIT1                    | Type-C mode,<br>room temperature                                                       | 3.10 | 3.65 | 4.20 | А     |

|                                                               | ILIMIT2                    | Type-A mode,<br>room temperature                                                       | 2.45 | 2.85 | 3.25 | А     |

| Output Voltage Control                                        |                            |                                                                                        |      |      |      |       |

| Default V <sub>IN</sub> voltage                               | V <sub>IN_Def</sub>        | $I_{OUT} = 0A$ , full temperature                                                      | -3%  | 5.1  | +3%  | V     |

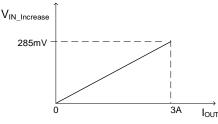

| Line drop compensation                                        | VIN_5_C                    | Iout = 3A                                                                              |      | 285  | 400  | mV    |

| Protection                                                    |                            |                                                                                        |      |      |      |       |

| V <sub>IN</sub> OVP threshold                                 | V <sub>OVP1</sub>          | Mode = float or GND, $V_{IN} = 5V$                                                     | 5.60 | 5.95 | 6.30 | V     |

| VIN OVP Infestiold                                            | V <sub>OVP2</sub>          | Mode = VCC, $V_{IN} = 5V$                                                              | 5.50 | 5.75 | 6.00 | V     |

| V <sub>IN</sub> OVP recovery threshold                        | V <sub>OV_Recovery</sub>   | Reset mode to 5V default                                                               | 5.20 | 5.45 | 5.70 | V     |

| DM, DP pins OVP rising                                        | $V_{OV\_DM\_DP}$           |                                                                                        | 3.7  | 4.0  | 4.3  | V     |

| DM, DP pins OVP<br>hysteresis                                 | Vov_dm_dp_<br>hys          |                                                                                        |      | 130  |      | mV    |

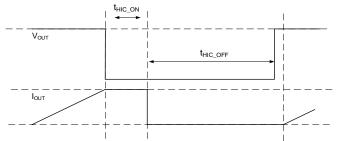

| OCP hiccup mode on-time                                       | thic_on                    |                                                                                        |      | 2    |      | ms    |

| OCP hiccup mode off-time                                      | thic_off                   |                                                                                        |      | 2    |      | s     |

| Shutdown temperature <sup>(8)</sup>                           | tsтр                       |                                                                                        |      | 150  |      | °C    |

| Hysteresis <sup>(8)</sup>                                     | t <sub>HYS</sub>           |                                                                                        |      | 25   |      | °C    |

MP5029-C Rev. 1.0 6/17/2019 MP www.MonolithicPower.com

MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2019 MPS. All Rights Reserved.

# ELECTRICAL CHARACTERISTICS (continued)

## $V_{IN} = 5V$ , $T_J = -40^{\circ}C$ to $+125^{\circ}C$ <sup>(7)</sup>, typical value is tested at $T_J = 25^{\circ}C$ , unless otherwise noted.

| Parameter                                                           | Symbol                        | Condition                                          | Min   | Тур   | Max   | Units |

|---------------------------------------------------------------------|-------------------------------|----------------------------------------------------|-------|-------|-------|-------|

| FLT output low voltage                                              | V <sub>FLT_Low</sub>          | Sink 1mA                                           |       |       | 150   | mV    |

| FLT leakage                                                         | IFLT_LKG                      | VFAULT = 4V                                        |       |       | 1     | μA    |

| BC1.2 DCP Short Mode                                                |                               |                                                    |       |       |       |       |

|                                                                     |                               | $V_{DP} = 0.8V, I_{DM} = 1mA$                      |       |       | 40    | Ω     |

| DP/DM short resistance                                              | $R_{DP/DM\_Short}$            | $V_{DP} = 0.8V, I_{DM} = 1mA,$<br>full temperature |       |       | 45    | Ω     |

| 1.2V/1.2V Mode                                                      |                               |                                                    |       |       |       |       |

| DP/DM output voltage                                                | Vdp/dm_1.2V                   |                                                    | 1.1   | 1.2   | 1.3   | V     |

| DP/DM output impedance                                              | RDP/DM_1.2V                   |                                                    | 200   | 300   | 400   | kΩ    |

| Divider Mode                                                        |                               |                                                    |       |       |       |       |

| DP/DM output voltage                                                | V <sub>DP/DM</sub>            | $V_{IN} = V_{OUT} = 5V$                            | 2.50  | 2.70  | 2.85  | V     |

| DP/DM output impedance                                              | Rdp/dm                        |                                                    | 20    | 26    | 32    | kΩ    |

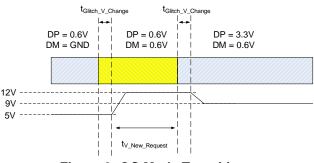

| Quick Charge 3.0 Mode                                               |                               |                                                    |       |       |       |       |

| Data detect voltage                                                 | VDAT_REF                      |                                                    | 0.25  | 0.30  | 0.40  | V     |

| Output voltage select reference                                     | $V_{\text{SEL}_{\text{REF}}}$ |                                                    | 1.8   | 2.0   | 2.2   | V     |

| DP output impedance                                                 | R <sub>DP_QC</sub>            |                                                    | 300   | 400   | 1500  | kΩ    |

| DM output impedance                                                 | R <sub>DM_QC</sub>            |                                                    | 13    | 20    | 27    | kΩ    |

| DM low glitch time (8)                                              | t <sub>Glitch_DM</sub>        |                                                    |       | 10    |       | ms    |

| DP high glitch time                                                 | <b>t</b> Glitch_DP            |                                                    | 800   | 1200  | 1600  | ms    |

| Output voltage change glitch time                                   | tGlitch_V_<br>Change          |                                                    | 20    | 40    | 60    | ms    |

| Bus voltage step                                                    | VBUS_CONT_<br>STEP            |                                                    | 150   | 200   | 250   | mV    |

| Time for $V_{BUS}$ to discharge to 5V when DP < 0.6V <sup>(8)</sup> | tv_unplug                     |                                                    |       |       | 500   | ms    |

| USB Type-C 5V/3A Mode -                                             | - Both CC1 a                  | and CC2 Pins                                       |       |       |       |       |

| CC resistor to disable<br>Type-C mode                               | RA                            | CC1 pin                                            | 90    |       | 100   | kΩ    |

| CC voltage to enable<br>V <sub>CONN</sub>                           | V <sub>Ra</sub>               |                                                    |       |       | 0.75  | V     |

| CC voltage to enable $V_{\text{BUS}}$                               | $V_{Rd}$                      | Use 0.8V and 2.6V as threshold                     | 0.85  |       | 2.45  | V     |

| CC detach threshold                                                 | V <sub>OPEN</sub>             | Use 2.6V as threshold                              | 2.75  |       |       | V     |

| CC voltage at $5.1k\Omega$ Rd                                       | Vcc_Rd                        | CC pin pull-down by $5.1k\Omega$                   | 1.310 | 1.683 | 2.040 | V     |

| CC voltage falling<br>debounce timer                                | tcc_debounce                  | VBUS enable deglitch                               | 100   | 130   | 200   | ms    |

| CC voltage rising debounce timer                                    | tPD_debounce                  | V <sub>BUS</sub> disable deglitch                  | 10    | 15    | 20    | ms    |

# ELECTRICAL CHARACTERISTICS (continued)

## $V_{IN} = 5V$ , $T_J = -40^{\circ}C$ to $+125^{\circ}C$ <sup>(7)</sup>, typical value is tested at $T_J = 25^{\circ}C$ , unless otherwise noted.

| Parameter                                                           | Symbol                | Condition                                                                     | Min   | Тур   | Max   | Units |

|---------------------------------------------------------------------|-----------------------|-------------------------------------------------------------------------------|-------|-------|-------|-------|

| V <sub>CONN</sub> output power                                      | Pvconn                | V <sub>CONN</sub> comes from MP5029-C<br>input with some series<br>resistance | 1     |       |       | W     |

| V <sub>BUS</sub> to ground impedance                                | RBUS                  | Type-C detach, after output<br>discharge turn-off                             | 72.4  |       |       | kΩ    |

| CDP MODE                                                            |                       |                                                                               |       |       |       |       |

| DM CDP output voltage                                               | Vdm_src               | $V_{DP} = 0.6V$                                                               | 0.50  | 0.64  | 0.70  | V     |

| Vau and impodence                                                   | Dura area             | I <sub>DM</sub> = 250μA                                                       |       | 0.3   | 0.5   | kΩ    |

| V <sub>DM_SRC</sub> impedance                                       | Rvdm_src              | DM connect to GND                                                             |       | 1     |       | kΩ    |

| DP rising lower window threshold for V <sub>DM_SRC</sub> activation | Vdat_ref              | 50mV hysteresis                                                               | 0.340 | 0.375 | 0.410 | V     |

| DP rising upper window threshold for $V_{DM\_SRC}$ deactivation     | V <sub>LGC_SRC</sub>  | 100mV hysteresis                                                              | 0.78  | 0.83  | 0.88  | V     |

| V <sub>DM_SRC</sub> on/off deglitch time                            | VDM_SRC_<br>Degh      |                                                                               |       | 5     |       | ms    |

| RDP_Down                                                            | $R_{\text{DP}}$       |                                                                               | 14.25 | 19.50 | 24.80 | kΩ    |

| DP/DM switch on<br>resistance                                       | R <sub>ON_DP/DM</sub> |                                                                               |       | 4     | 7     | Ω     |

| DP to DP_OUT SW on capacitor <sup>(8)</sup>                         | Cdp                   | Same for DM switch                                                            |       | 9     |       | pF    |

| 3dB bandwidth of analog data SW <sup>(8)</sup>                      | fвw                   |                                                                               | 500   |       |       | MHz   |

#### Notes:

7) All min/max parameters are tested at T<sub>J</sub> = 25°C. Limits over temperature are guaranteed by design, characterization, and correlation.

8) Guaranteed by engineering sample characterization.

# **TYPICAL CHARACTERISTICS**

$V_{IN}$  = 5V,  $V_{OUT}$  = 5V,  $T_A$  = 25°C, unless otherwise noted.

# **TYPICAL PERFORMANCE CHARACTERISTICS**

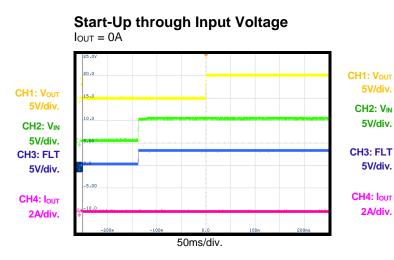

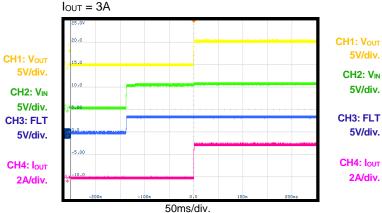

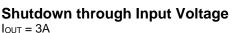

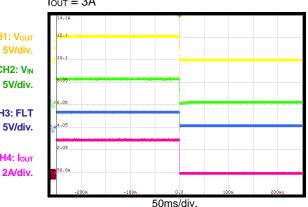

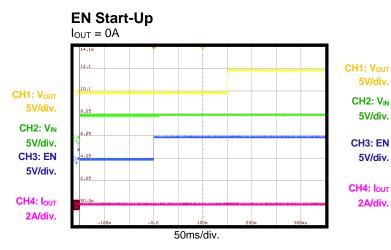

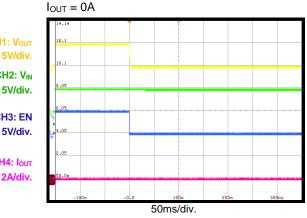

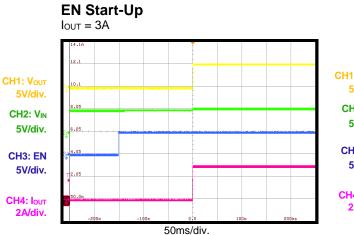

$V_{IN} = 5V$ ,  $V_{OUT} = 5V$ ,  $T_A = 25^{\circ}C$ , Type-C mode, CC1 pull-down by 5.1k $\Omega$  resistor, unless otherwise noted. Connect the MP5029-C input  $V_{IN}$  to the MPQ4483 output. System\_ $V_{IN} = 14V$  is the input of the MPQ4483.

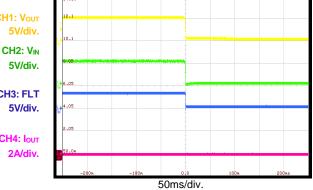

Shutdown through Input Voltage Iout = 0A

Start-Up through Input Voltage

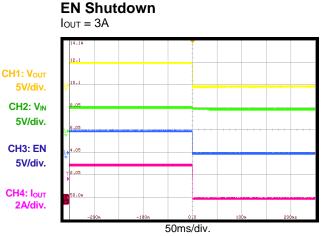

EN Shutdown

$V_{IN} = 5V$ ,  $V_{OUT} = 5V$ ,  $T_A = 25^{\circ}C$ , Type-C mode, CC1 pull-down by 5.1k $\Omega$  resistor, unless otherwise noted. Connect the MP5029-C input  $V_{IN}$  to the MPQ4483 output. System\_ $V_{IN} = 14V$  is the input of the MPQ4483.

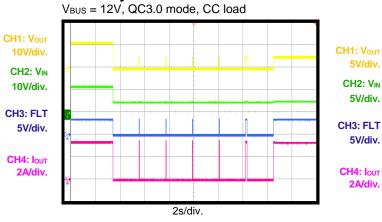

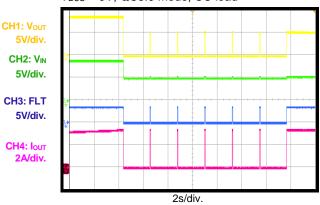

# Over-Current Protection Entry and Recovery

# Over-Current Protection Entry and Recovery

# Over-Current Protection Entry and Recovery

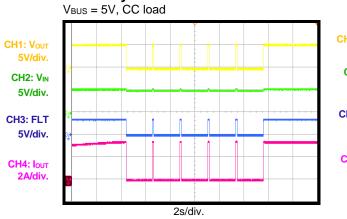

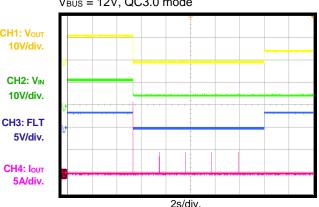

V<sub>BUS</sub> = 9V, QC3.0 mode, CC load

#### Short-Circuit Protection Entry and Recovery VBUS = 5V

$V_{IN} = 5V$ ,  $V_{OUT} = 5V$ ,  $T_A = 25^{\circ}C$ , Type-C mode, CC1 pull-down by 5.1k $\Omega$  resistor, unless otherwise noted. Connect the MP5029-C input  $V_{IN}$  to the MPQ4483 output. System\_ $V_{IN} = 14V$  is the input of the MPQ4483.

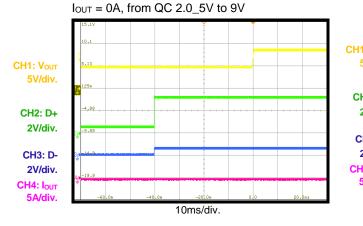

Mode Transition from 5V to 9V

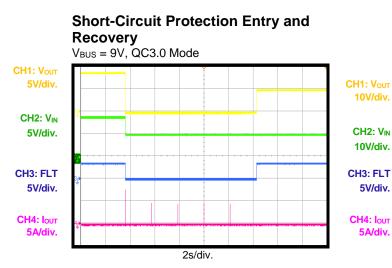

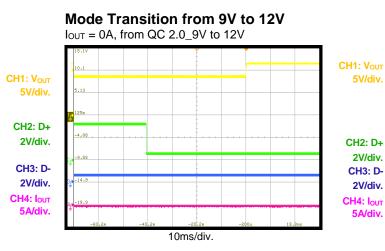

Short-Circuit Protection Entry and Recovery VBUS = 12V, QC3.0 mode

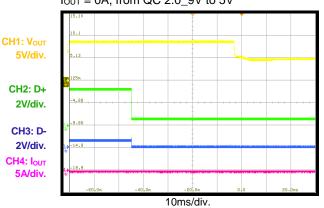

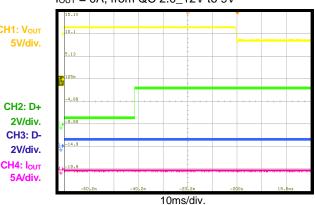

Mode Transition from 9V to 5V IOUT = 0A, from QC 2.0\_9V to 5V

Mode Transition from 12V to 9V IOUT = 0A, from QC 2.0\_12V to 9V

$V_{IN} = 5V$ ,  $V_{OUT} = 5V$ ,  $T_A = 25^{\circ}C$ , Type-C mode, CC1 pull-down by 5.1k $\Omega$  resistor, unless otherwise noted. Connect the MP5029-C input  $V_{IN}$  to the MPQ4483 output. System\_ $V_{IN} = 14V$  is the input of the MPQ4483.

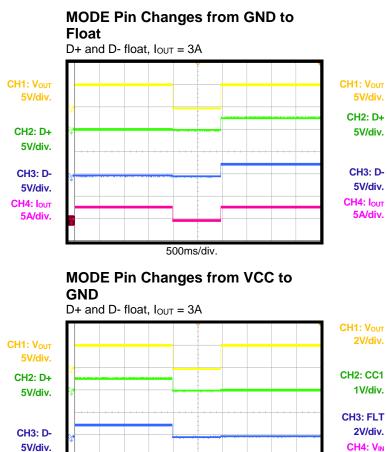

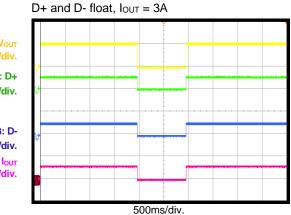

# MODE Pin Changes from Float to VCC

## Load Shedding Entry

Buck output set to 4.9V,  $V_{BUS} = 5V$ , CC1 = 5.1k $\Omega$ , CDP mode

## Load Shedding Entry

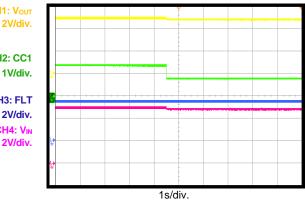

Buck output set to 3.6V,  $V_{BUS} = 5V$ , CC1 = 5.1k $\Omega$ , QC3.0 mode

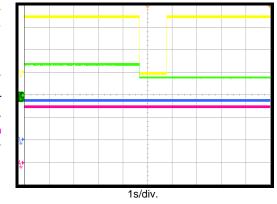

#### Load Shedding Entry Buck output set to 4.9V, $V_{BUS} = 5V$ , $CC1 = 5.1k\Omega$ , DCP mode CH1: VOUT CH1: VOUT 2V/div. 2V/div. CH2: CC1 CH2: CC1 1V/div. 1V/div. CH3: FLT CH3: FLT 2V/div. 2V/div. CH4: VIN CH4: VIN 2V/div. 2V/div. 1s/div.

500ms/div.

СH4: Іоит 5A/div.

#### MP5029-C Rev. 0.81 www.MonolithicPower.com 6/17/2019 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. Preliminary Specifications Subject to Change © 2019 MPS. All Rights Reserved.

$V_{IN} = 5V$ ,  $V_{OUT} = 5V$ ,  $T_A = 25^{\circ}C$ , Type-C mode, CC1 pull-down by  $5.1k\Omega$  resistor, unless otherwise noted. Connect the MP5029-C input  $V_{IN}$  to the MPQ4483 output. System\_ $V_{IN} = 14V$  is the input of the MPQ4483.

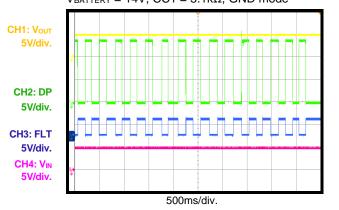

**DP Short to Battery** VBATTERY = 14V, CC1 =  $5.1k\Omega$ , GND mode

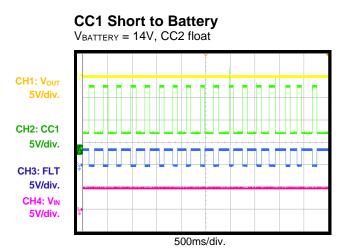

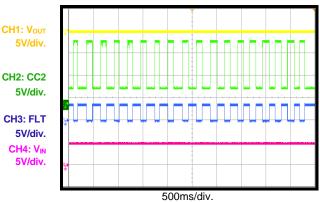

CC2 Short to Battery VBATTERY = 14V, CC1 float

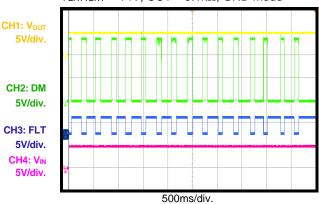

DM Short to Battery

VBATTERY = 14V, CC1 =  $5.1k\Omega$ , GND mode

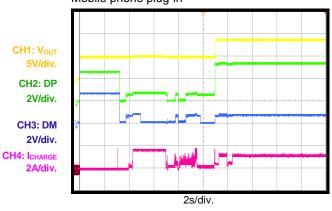

#### **QC 3.0 Device Charging Test** Mobile phone plug-in

$V_{IN} = 5V$ ,  $V_{OUT} = 5V$ ,  $T_A = 25^{\circ}C$ , Type-C mode, CC1 pull-down by  $5.1k\Omega$  resistor, unless otherwise noted. Connect the MP5029-C input  $V_{IN}$  to the MPQ4483 output. System\_ $V_{IN} = 14V$  is the input of the MPQ4483.

#### Eye Diagram

Measured by a 50cm cable, without MP5029-C connection (see Figure 14)

#### Eye Diagram

Measured on an EVB by a 50cm cable, with a MP5029-C data switch (see Figure 14)

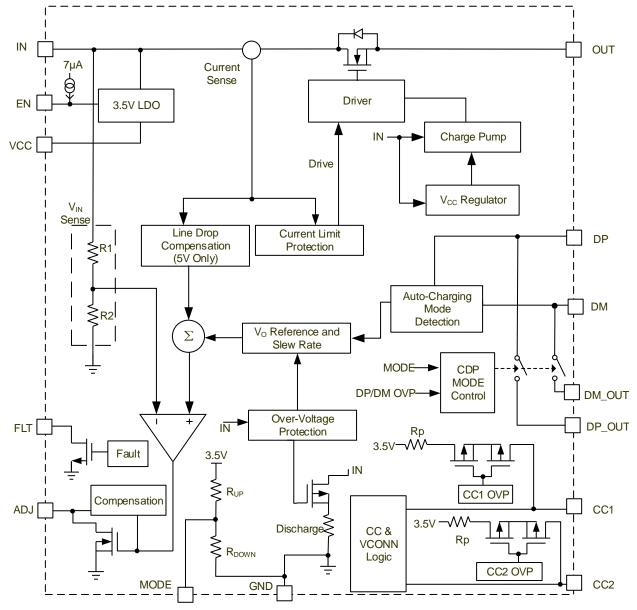

# FUNCTIONAL BLOCK DIAGRAM

Figure 1: Functional Block Diagram

# OPERATION

The MP5029-C integrates a USB current limit switch and charging port identification circuits. It achieves 3A of continuous output current over a wide input supply range.

The MP5029-C supports quick-charge specification (QC3.0), and is compatible with QC2.0. The MP5029-C also supports CDP and DCP schemes for battery-charging specification (BC1.2), divider mode, and 1.2V/1.2V mode without the need for external user interaction.

The MP5029-C also supports Type-C 5V @ 3A DFP mode.

The part provides line drop compensation for a 5V output. Full protection features include hiccup current limiting, input over-voltage protection (OVP), thermal shutdown, and short-to-battery protection.

### **Operation Supply Voltage**

The MP5029-C has a two-stage input voltage threshold. The first threshold is about 3V, and the second threshold is the under-voltage lockout (UVLO) of the power MOSFET. When  $V_{IN}$  exceeds the first threshold, the MP5029-C's ADJ block turns on, which sinks a current to adjust the upstream regulator's output to an accurate 5.1V (typical). After this process, the MP5029-C enables the power MOSFET and enters a fully working state.

### Under Voltage Lockout (UVLO)

Under-voltage lockout (UVLO) protects the chip from operating at an insufficient supply voltage. The MP5029-C's second UVLO comparator monitors the input voltage. If the input voltage exceeds the second UVLO threshold (about 3.1V), the power MOSFET turns on at a controlled slew rate after a fixed delay.

### Internal Soft Start (SS)

The internal soft start prevents inrush current and keeps the output voltage from overshooting during start-up.

## Enable Control (EN)

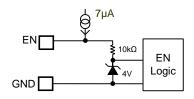

The MP5029-C has an enable control pin (EN). The MP5029-C has an internal  $7\mu$ A pull-up current that allows EN to be floated for auto start-up. Pull EN high or float EN to enable the IC. Pull EN low to disable the IC.

Apply a mid-level voltage (0.9V to 1.8V) to EN to force the chip to enter client mode. In client mode, the USB switch is off, but the DP/DM high speed data switch is on.

EN is clamped internally using a 4V Zener diode (see Figure 2). When connecting EN to >4V VIN through a pull-up resistor, limit the EN input current to less than 250µA. Connecting EN directly to a voltage source without a pull-up resistor requires limiting the voltage amplitude to less than 4V.

Figure 2: Zener Diode between EN and GND

## QC Mode Voltage Transition – Class A

If the downstream device of the MP5029-C supports QC specification, the device can support output voltages greater than 5V via DM and DP communication. If a higher USB output voltage is required, use the ADJ pin. Typically, ADJ is connected to the FB pin of the upstream voltage converter. After the handshake, the MP5029-C sinks a controlled ADJ current gradually to adjust V<sub>OUT</sub> to 9V, 12V, or any other voltage (e.g. 200mV). Because of the MP5029-C's smart controller mode, only one ADJ pin is needed to set different high-voltage values and meet the QC specification. The output voltage transition is smooth with no undershoot or overshoot (see Figure 3 and Table 1).

Figure 3: QC Mode Transition

| Portable Device |      | LICD Output Voltage                             |

|-----------------|------|-------------------------------------------------|

| DP              | DM   | USB Output Voltage                              |

| 0.6V            | 0.6V | 12V                                             |

| 3.3V            | 0.6V | 9V                                              |

| 0.6V            | 3.3V | 3.6V to 12V/200mV<br>step according to<br>QC3.0 |

| 3.3V            | 3.3V | No action                                       |

| 0.6V            | GND  | 5V                                              |

Table 1: QC Mode Definition

When the downstream device is removed,  $V_{OUT}$  returns to the default 5V automatically. The input-to-ground discharge resistor helps perform this procedure quickly.

#### Line Drop Compensation

The MP5029-C can compensate for an output voltage drop, such as high resistance caused by a long trace, to maintain a fairly constant 5V load-side voltage. The line drop compensation is only active at 5V  $V_{IN}$ , and increases the input voltage by 285mV at 3A output current (see Figure 4).

Figure 4: Line Drop Compensation

The line drop compensation is realized through ADJ. The ADJ voltage ( $V_{ADJ}$ ) sinks a controlled current slowly. The line drop compensation amplitude increases linearly as the load current increases.

In a no-load condition, if the input voltage is below the typical 5.1V, ADJ sinks a current to regulate the upstream regulator's output voltage to 5.1V. If the input voltage is above 5.1V, the MP5029-C no longer regulates the input voltage. For a quick load transient response, configure R1/R2 to allow the default output voltage to be less than 5.1V, maintaining that ADJ works continuously.

Figure 5 shows typical ADJ configuration. The ADJ sink current capability is 500µA. ADJ requires a feedback current of less than 500µA through R1. Calculate R1 with Equation (1):

$$R1(k\Omega) > \frac{\Delta V(V)}{0.5}$$

(1)

Where  $\Delta V$  is the maximum line drop compensation value, plus the difference in voltage between 5.1V and the buck voltage.

Figure 5: ADJ Configuration

There is another  $V_{ADJ}$  configuration to limit the maximum output voltage by inserting a resistor (R4) between FB and  $V_{ADJ}$ . With R4, the maximum output voltage can be limited with Equation (2):

$$V_{\text{OUT}_Max}(V) = \frac{R_1 + R_2 // R_4}{R_2 // R_4} \times V_{FB}(V)$$

(2)

After adding R4, the maximum ADJ sink current is limited with Equation (3):

$$I_{ADJ_Max}(\mu A) = \frac{V_{FB} - V_{OFFSET}(mV)}{R_4(k\Omega)}$$

(3)

Where V<sub>OFFSET</sub> is about 100mV.

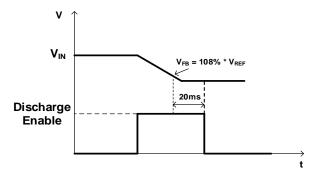

## Input Over-Voltage and Discharge

To protect the downstream device over-voltage, the MP5029-C provides an input OVP discharge function. Because the MP5029-C supports QC3.0 protocol, it has a dynamic overvoltage protection threshold.

An accurate and fast comparator monitors the over-voltage condition of the input. If the input voltage rises above the threshold, the power MOSFET remains on, while the input-to-ground discharge path is active. When the input voltage falls below the typical 5.45V, the MP5029-C exits OVP mode.

The input-to-ground discharge resistance is always active during high-to-low voltage change mode. This resistance is disabled when FB is less than 108% of  $V_{REF}$  with a 20ms delay and

OV is removed (see Figure 6).

#### Figure 6: Input Discharge During High Voltage to Low Voltage Transition

QC mode is reset during the OVP rising edge.

### **Over-Current Protection**

Once the device reaches its current limit threshold, the internal circuit regulates the gate voltage to hold the current in the power MOSFET constant (see Figure 7). If the overcurrent condition lasts longer than 2ms, the MP5029-C enters hiccup mode.

In hiccup mode, the MP5029-C turns off the power MOSFET. For QC mode, it resets to 5.1V, ADJ changes  $V_{IN}$  to 5.1V,  $V_{IN}$  OVP may occur, the QC logic resets, and the discharge resistor turns on. After the hiccup off timer (2s), the MP5029-C restarts to check if the OC is still present. The QC logic releases when the hiccup signal disappears.

Figure 7: Over-Current Protection

## **Short-Circuit Protection (SCP)**

If the load current increases rapidly due to a short circuit, the current may greatly exceed the current-limit threshold before the control loop can respond. If the current reaches an internal secondary current-limit level (about 9A), a fast turn-off circuit activates to turn off the power MOSFET. This limits the peak current through the switch to limit the input voltage drop. Afterward, the power MOSFET turns on again if the part is still in a short-circuit condition. The MP5029-C treats this as an over-current condition, and enters hiccup mode or thermal shutdown. After the short-circuit condition is removed, the MP5029-C recovers automatically.

If  $V_{IN} > 9V$  and the operation mode is CDP or DCP mode (non-QC3.0), the MP5029-C does not support output short-circuit protection (SCP). It does support output SCP when the operation mode is QC3.0 with  $V_{IN} > 9V$ . In this case,  $V_{IN}$  automatically changes to 5.1V (typical) once SCP is triggered.

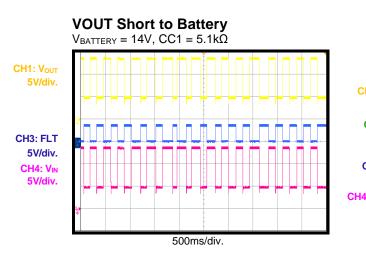

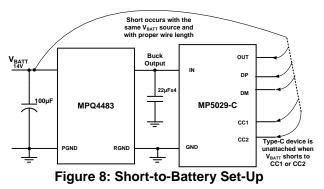

## Short-to-Battery Protection

The MP5029-C provides CC1, CC2, DP, DM, and OUT short-to-battery protections when the IC is enabled.

The MP5029-C has a high internal voltage rating. During a CC1/CC2 or DP/DM short-tobattery condition, the MP5029-C can withstand high voltage on the internal components. Additionally, the ESD breakdown voltage is much larger than the battery voltage.

During a 5V USB output short-to-battery condition, the USB input rises up to trigger OVP, and the USB input discharge path turns on.

When the MPQ4483 is used as a buck regulator, the buck output capacitor should be placed between the buck output and PGND, instead of RGND (see Figure 8).

## **Fault Indication**

FLT is the fault indication pin. FLT is in an open-drain state during shutdown, start-up, and normal operation. It asserts (logic low) during over-current, input over-voltage, DP/DM pin

over-voltage, CC1/CC2 pin over-voltage, or over-temperature conditions. FLT asserts low until the fault condition is removed, and the USB output voltage goes back to high. There is a 2ms deglitch timer during an over-current condition to prevent a false trigger on FLT. If the over-current condition lasts for 2ms, FLT goes low. The FLT signal is not deglitched during over-voltage and over-temperature conditions.

#### **Mode Selection**

The MP5029-C supports DCP and CDP mode through MODE pin control (see Table 2). The MODE pin logic level can be changed dynamically when the MP5029-C is working. There are three logic levels: pull to ground, float pin, and tie to VCC. If MODE is connected to GND, CDP mode is selected. In CDP mode, the USB output voltage is always about 5V with current limit and line drop compensation. If MODE is connected to VCC, DCP mode is selected, QC3.0 is enabled, and line drop compensation is active for 5V. If MODE is left floating, DCP mode is selected, QC3.0 is disabled, and line drop compensation is active for 5V.

In DCP mode, the MP5029-C provides power for USB devices with protocol auto-detection, and supports the following charging schemes:

- USB Battery Charging Specification BC1.2 / Chinese Telecommunications Industry Standard YD/T 1591-2009

- Divider mode

- 1.2V/1.2V mode

- Type-C 5V @ 3A DFP mode

In QC3.0 mode, the MP5029-C provides power for portable devices, and supports the following charging schemes:

- USB Battery Charging Specification BC1.2 / Chinese Telecommunications Industry Standard YD/T 1591-2009

- Divider mode

- 1.2V/1.2V mode

- Type-C 5V @ 3A DFP mode

- Quick charge 3.0/2.0

| Table 2: | MODE | Pin Selection |  |

|----------|------|---------------|--|

|----------|------|---------------|--|

| MODE Pin<br>Status | Supported Charge Mode                                                                                              |  |

|--------------------|--------------------------------------------------------------------------------------------------------------------|--|

| Logic high         | DCP mode with QC function,<br>divider mode, 1.2V/1.2V mode,<br>5V <sub>OUT</sub> with line drop<br>compensation    |  |

| Float              | DCP mode without QC function,<br>divider mode, 1.2V/1.2V mode,<br>5V <sub>OUT</sub> with line drop<br>compensation |  |

| GND                | CDP mode, 5Vout with line drop compensation                                                                        |  |

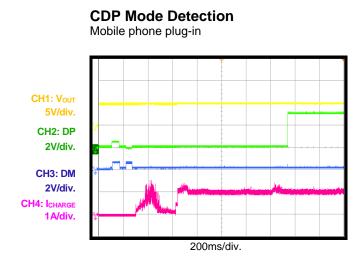

#### CDP Mode

The MP5029-C supports charging downstream port (CDP) mode in compliance with the USB2.0 definition of a host or a hub.

DM outputs a 0.64V voltage when DP is forced with 0.6V, and DP does not output any voltage when DM is forced with 0.6V.

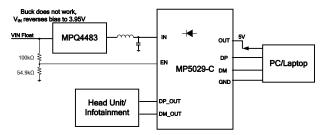

#### **Client Mode**

The MP5029-C supports client mode operation. This mode is useful when upgrading software through a USB port (see Figure 9).

Figure 9: Client Mode

In this case, OUT is powered by an external 5V USB bus voltage, but the system input has no supply (see Figure 9). The MP5029-C USB switch shuts down due to low EN voltage (set by the EN divider resistors), and the DP/DM data switches turn on when their EN is higher than the MOSFET  $V_{GS}$  threshold. An external host (e.g. laptop) can read and update head unit software. Under this condition,  $V_{IN}$  is biased to about 3.95V through the USB switch and buck high-side body diode. Ensure other units on the same  $V_{IN}$  line do not start up.

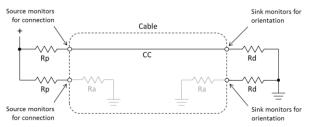

#### USB Type-C Mode and VCONN

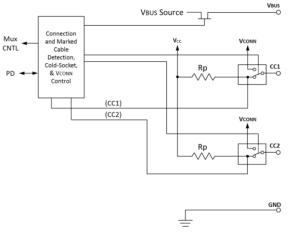

For USB Type-C solutions, two pins on the connector (CC1 and CC2) are used to establish and manage the source-to-sink connection. The

general concept for setting up a valid connection between a source and sink is based on being able to detect terminations residing in the product being attached. To aid in defining the functional behavior of CC, a pull-up (Rp) and pull-down (Rd =  $5.1k\Omega$ ) termination model is used, based on a pull-up resistor and pulldown resistor (see Figure 10).

Figure 10: Pull-Up/Pull-Down CC Model

Initially, a source exposes independent Rp terminations on its CC1 and CC2 pins, and a sink exposes independent Rd terminations on its CC1 and CC2 pins. The source-to-sink combination of this circuit configuration represents a valid connection. To detect this, the source monitors CC1 and CC2 for a voltage lower than its unterminated voltage. The choice of Rp is a function of the pull-up termination voltage and the source's detection circuit. This indicates that a sink, a powered cable, or a sink connected via a powered cable has been attached.

Two termination combinations on the CC pins are defined for directly attached accessory modes: Ra/Ra for audio adapter accessory mode, and Rd/Rd for debug accessory mode. In both cases, the MP5029-C's  $V_{OUT}$  is disabled (see Figure 11).

A port that behaves as a source has the following functional characteristics:

- 1. The source uses a MOSFET to enable or disable the power delivery across  $V_{\text{BUS}}$ . Initially, the source is disabled.

- 2. The source supplies pull-up resistors (Rp) on CC1 and CC2 and monitors both to detect a sink. The presence of an Rd pull-down resistor on either CC1 or CC2 indicates that a sink is being attached. The value of Rp indicates the initial USB Type-C current level supported by the host. The MP5029-C default Rp is  $4.7k\Omega$ , which represents a 3A current level.

- 3. The source uses the CC pin pull-down characteristic to detect and determine which CC pin is intended to supply VCONN (when Ra is discovered).

- 4. Once a sink is detected, the source enables  $V_{\text{BUS}}$  and VCONN.

- 5. The source can adjust the value of Rp dynamically to indicate a change in the available USB Type-C current to a sink. For example, at high temperatures, the MP5029-C changes Rp to  $12k\Omega$  to indicate a 1.5A current ability.

- The source monitors the continued presence of Rd to detect a sink detach. When a detach event is detected, the source is removed, and V<sub>BUS</sub> and VCONN return to step 2.

### Disable Type-C Mode (Type-A Mode)

During the MP5029-C's initial start-up, the IC sources  $10\mu$ A for  $20\mu$ s on CC1. If the CC1 voltage falls into the preset voltage range, USB latches in Type-A mode unless the MP5029-C is re-enabled. Type-C mode is disabled, which means the CC attach and detach logic is disabled, and V<sub>BUS</sub> is always enabled. The current limit changes to its Type-A specification.

To trigger this mode, the external pull-down resistor should be  $90k\Omega$  to  $100k\Omega$ . Do not add an extra capacitor on CC1. In normal Type-C mode applications, a 1nF capacitor should be added on CC1 to avoid falsely triggering Type-A mode.

# MP5029-C – USB CHARGING PORT CONTROLLER, SUPPORTS CDP, DCP & QC3.0

#### Load Shedding vs. Temperature

When the sensed temperature exceeds  $125^{\circ}$ C, the USB port's CC pin pull-up resistance (Rp) changes to  $12k\Omega$  to advertise its source capability change (to 1.5A). The internal Rd detection threshold also changes from 0.4V to 1.6V. The Ra detection threshold changes to <0.4V. The current limit remains unchanged.

For QC mode, once the part enters load shedding,  $V_{BUS}$  restarts, then keeps working at 5V. Meanwhile, QC3.0 mode is disabled via DP/DM. For DCP mode without QC or CDP mode, once the part enters load shedding,  $V_{BUS}$  does not restart, but line drop compensation and ADJ function stop.

If the sensed temperature is below  $85^{\circ}$ C and lasts for 16s, USB Type-C current capability changes back to 3A (Rp = 4.7k $\Omega$ ). V<sub>BUS</sub> restarts with QC mode again if QC mode is selected.

In the typical Type-A application schematic, when load shedding occurs, ADJ stops working and the USB output reduces to 4.9V (set by the R1/R2 divider). This helps the Type-A downstream device reduce charge current.

#### **Thermal Shutdown**

Thermal shutdown prevents the chip from operating at exceedingly high temperatures. When the silicon die temperature exceeds 150°C, the entire chip shuts down. When the temperature falls below its lower threshold (typically 125°C), the chip is enabled again.

## **APPLICATION INFORMATION**

### **COMPONENT SELECTION**

#### Selecting the Input Capacitor

low-ESR capacitors Use for the best performance. Ceramic capacitors with X5R or dielectrics are highly recommended X7R of their low ESR and small because temperature coefficients. 2.2µF to 22µF ceramic capacitors recommended are for most applications.

When selecting an input capacitor, be sure to consider the pre-stage converter stability. The input capacitor of the MP5029-C acts as the output capacitor of the converter. Ensure that the converter is stable with an additional output capacitor.

#### Selecting the Output Capacitor

capacitors Use low-ESR for the best performance. Ceramic capacitors with X5R or X7R dielectrics are highly recommended for their low ESR and small temperature coefficients. A 1µF ceramic capacitor is recommended for most applications.

#### **Other Considerations**

The upstream DC/DC converter should have a higher current limit threshold than the MP5029-C's current limit.

In normal Type-C mode application, a 1nF capacitor should be added on CC1 to avoid falsely triggering Type-A mode. For more details, see the Typical Application Circuit schematics on page 25.

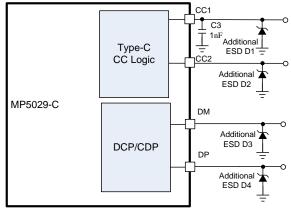

#### **ESD** Protection for I/O Pins

A higher ESD level should be considered for all USB I/O pins. In order to further extend the DP, DM, CC1, and CC2 pins' ESD level for covering complicated application environments, an additional ESD diode should be added on all pins (see Figure 12).

#### Figure 12: Recommended I/O pins ESD Enhancing

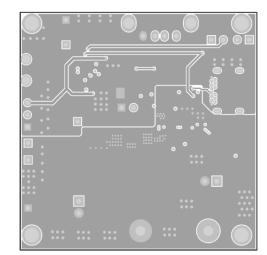

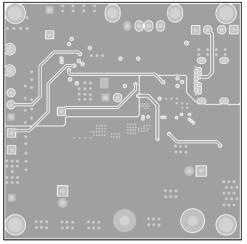

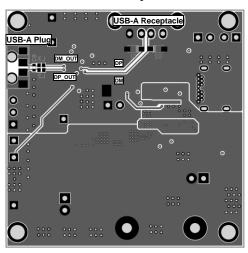

#### PCB Layout Guidelines (9)

Efficient PCB layout is critical for normal operation and thermal dissipation. For best results, refer to Figure 13 and follow the guidelines below:

- 1. Use short, direct, and wide traces to connect the IC's IN/OUT pins.

- 2. Make the trace length between VCC and the capacitor to GND as short as possible.

- 3. Keep the V<sub>ADJ</sub> trace to the upstream converter's FB pin as short as possible to prevent noise injection.

- 4. Route DP, DM, DP OUT, and DM OUT with differential pairs and continuous GND. Keep away from high-speed signals.

- 5. Keep the routing as short as possible for DP, DM, DP OUT, and DM OUT.

- 6. Avoid vias and corners. Use two 45° turns to make a single 90° turn.

#### Note:

The recommended layout is based on the Typical Application 9) Circuit on page 25.

00

USB-A Receptacle

MPQ4483

00

VIN

0

USB-A Plug

Ο

Ο

JP1

0

O

v022

O

v026

I

rest

I

rest

I

rest

000

MP5029-C

BUCK\_OUT

0

Top Layer

PGND

Middle Layer 2

Middle Layer 1

**Bottom Layer**

Figure 13: Recommended PCB Layout

# **TYPICAL APPLICATION CIRCUITS**

Figure 14: MPQ4483 + MP5029-C for Type-C Port with CDP Mode

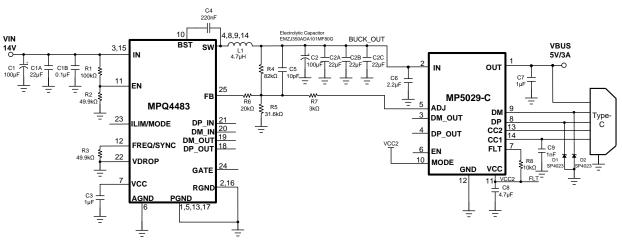

Figure 15: MPQ4483 + MP5029-C for Type-C Port with QC3.0

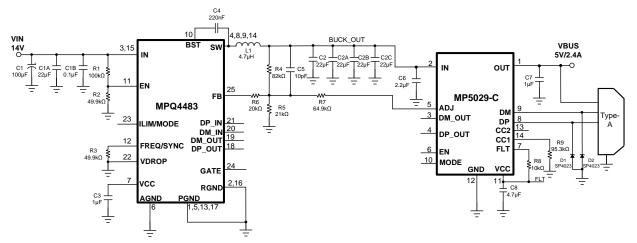

Figure 16: MPQ4483 + MP5029-C for Type-A Port with 5V DCP Mode

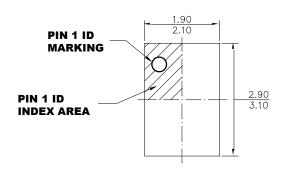

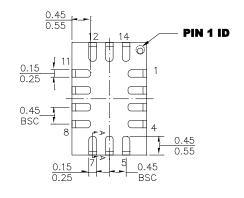

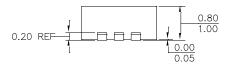

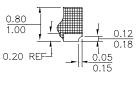

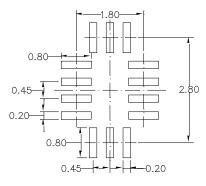

## **PACKAGE INFORMATION**

QFN-14 (2mmx3mm)

TOP VIEW

**BOTTOM VIEW**

SIDE VIEW

#### **RECOMMENDED LAND PATTERN**

#### NOTE:

THE LEAD SIDE IS WETTABLE.

ALL DIMENSIONS ARE IN MILLIMETERS.

LEAD COPLANARITY SHALL BE 0.08 MILLIMETERS MAX.

JEDEC REFERENCE IS MO-220.

DRAWING IS NOT TO SCALE.

**NOTICE:** The information in this document is subject to change without notice. Please contact MPS for current specifications. Users should warrant and guarantee that third-party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.