## MN5901

8-Bit, 100MHz FLASH A/D CONVERTER

## **FEATURES**

- 8-Bit Resolution

- 100MHz Min. Conversion Rate

- 80MHz Large Signal Bandwidth

- 5.0 Effective Bits, fain =35MHz (Guaranteed Over Temp Range)

- Balanced Input Range

- End Point Error 1LSB Max (Guaranteed Over Temp Range)

- .85LSB Max Linearity (Guaranteed Over Temp Range)

- 100K ECL Compatible Output Data

- Operating Temp Range

-55°C to +125°C case, (Optional)

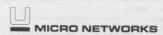

#### 24 PIN SIDE-BRAZED DIP

Dimensions In Inches (millimeters)

#### DESCRIPTION

The MN5901 is an ultra-high speed monolithic Analog to Digital converter which has 8-bit resolution and a guaranteed conversion speed (strobe frequency) of 100MHz. The MN5901 utilizes the ''flash'' or parallel principle, whereby a field of 255 comparators simultaneously determine the precise analog input. The comparators' outputs are converted to ECL compatible outputs through three encoding stages which are activated by two strobe signals. The MN5901's input is easily driven by a 50-ohm source without the burden of a pre-amplifier or level shifter. Reference sense pins +V<sub>REF,S</sub> and -V<sub>REF,S</sub> allow compensation for voltage drops at the top and bottom of the reference resistance string which contribute to the MN5901's precise end point accuracy (1LSB max over the full operating temperature range).

Packaged in a small 24-pin hermetically sealed ceramic DIP, the MN5901 offers outstanding differential linearity (.95LSB max over the specified temperature range) and a high signal-to-noise-ratio (SNR) of 38dB min at 35MHz as well as a precise endpoint accuracy of 1LSB max over the full temperature range. Micro Networks provides important dynamic testing of dynamic linearity (effective bits), signal-to-noise-ratio, and total harmonic distortion over the full operating temperature range at a conversion rate of 100MHz for 100% of all military temperature range devices. The MN5901 is specified for operation from -4.5V supplies for output compatibility with 100K ECL logic and is also compatible with 10K ECL logic when operated from -5.2V.

Devices are offered for operation over  $-25^{\circ}$ C to  $+85^{\circ}$ C (case), and  $-55^{\circ}$ C to  $+125^{\circ}$ C (case, H models). Contact factory for availability of fully compliant MIL-STD-883, Method 5008 devices.

## **APPLICATIONS**

Radar Systems

Digital Oscilloscopes

Automatic Test Equipment

ECM Equipment

Analytical Systems

SOLD & SUPPLIED BY

# Priority Electronics &

MELBOURNE: Suite 1, 23-25 Melrose St. Sandringham, Vic. 3191 Australia

Australia Phone: (03) 521 0266 Fax: (03) 521 0356 SYDNEY: Suite 2, 25 Chard Road Brookvale, N.S.W. 2100 Australia Phone: (02) 905 6024

Fax: (02) 939 6348

ber 1990 ht©1990 letworks reserved

## MN5901 8-Bit 100MHz A/D CONVERTER

#### **ABSOLUTE MAXIMUM RATINGS**

Operating Temperature Range (case)

Specified Temperature Range (case):

MN5901

MN5901H, MN5901H-883

Storage Temperature Range

Positive Supply Voltages (+Vcc. +Vcc. p)

Negative Supply Voltages (-VeE, VeE, D)

Reference Voltages (+VaEF, -VREF)

Analog Input Voltages

Ugital Input Voltages

Output Current (Ipo - Ipr)

-55°C to +125°C -25°C to +85°C -55°C to +125°C

-55°C to +125°C -65°C to +150°C -0.3 to +6.0 Volts +0.3 to -6.0 Volts -2.5 to +1.5 Volts -2.5 to +1.5 Volts -3.5 to +0.0 Volts

20mA

#### **ORDERING INFORMATION**

| PART NUMBER —                                                      | MN5901H-88 |

|--------------------------------------------------------------------|------------|

| Add suffix "H" for -55°C to +125°C operation.                      |            |

| Add "-883" suffix to "H" models for MIL-STD-883 compliant devices. | SCIDEA AND |

| Thermal Information                                                |            |

Thermal resistance:

Junction-to-case (bottom of package)

Junction-to-ambient, free air dissipation

44°C/W

#### SPECIFICATIONS (TA = +25°C: Voc Voc p = +5.0V: VEF VEF p = -4.5V: +VBFF = +1.00V: -VBFF = -1.00V unless otherwise noted)

| ANALOG INPUTS                                                                                                                                                                                                                 | MIN.                                 | TYP.          | MAX.                                                   | UNITS                             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|---------------|--------------------------------------------------------|-----------------------------------|

| Input Voltage Range Analog Input Current ( $V_{AIN} \ge +V_{REF}$ ) (Note 1) ( $V_{AIN} \le -V_{REF}$ ) Input Impedance Input Capacitance ( $V_{AIN} \ge +V_{REF}$ ) ( $V_{AIN} \le -V_{REF}$ ) Full Power Bandwidth (Note 2) | -2<br>150                            | ±1 6 50 60 80 | +1<br>700<br>10                                        | Volts  µA  µA  KOhms  pF  pF  MHz |

| REFERENCE INPUTS                                                                                                                                                                                                              | 2020 Of the mailton                  |               |                                                        |                                   |

| Reference Voltages (Note 3) (+V <sub>REF,</sub> -V <sub>REF</sub> ) Reference Ladder Resistance Ladder Temperature Coefficient                                                                                                | -2.0<br>105                          | 150<br>0.45   | +1.0<br>190                                            | Volts<br>Ohms<br>Ohms/°C          |

| DIGITAL INPUTS                                                                                                                                                                                                                |                                      |               |                                                        |                                   |

| Logic Levels: Over Temperature (Note 4)                                                                                                                                                                                       | -1.165<br>4<br>3                     | 5             | -1.475<br>30<br>40                                     | Volts Volts  A  nA  pF  ns  ns    |

| STR 2 DIGITAL OUTPUTS                                                                                                                                                                                                         | 3                                    |               |                                                        | 115                               |

| Logic Levels: Over Temperature (Notes 4 & 5) Logic "1" Logic "0" Output Rise Time (Note 6)                                                                                                                                    | -1.025<br>-1.810                     |               | 880<br>-1.620<br>3<br>3                                | Volts<br>Volts<br>ns<br>ns        |

| Output Fall Time (Note 6)  TRANSFER CHARACTERISTICS                                                                                                                                                                           |                                      |               | 3                                                      | 110                               |

| Integral Nonlinearity Error Over Temperature (Note 4) Differential Linearity Error Over Temperature (Note 4) No Missing Codes End Point Error (Note 7)                                                                        | - Prompty 3 NOS<br>mesoya le ligiona | Guaranteed C  | ±.5<br>±.85<br>±.6<br>±.95<br>Over Temperature<br>+.90 | LSB<br>LSB<br>LSB<br>LSB          |

| Over Temperature (Notes 4 & 7)                                                                                                                                                                                                |                                      |               | ±1.0                                                   | LSB                               |

| 学的 的复数 等级 医性性                                                                                                                                                                                                                                                                                                                             | MIN.                                | TYP.                                                     | MAX.               | UNITS                            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|----------------------------------------------------------|--------------------|----------------------------------|

| DYNAMIC PERFORMANCE                                                                                                                                                                                                                                                                                                                       |                                     |                                                          |                    |                                  |

| Conversion Rate Over Temperature<br>Aperture Delay<br>Aperture Jitter                                                                                                                                                                                                                                                                     | 100                                 | 125<br>1<br>25                                           |                    | MHz<br>ns<br>ps                  |

| Conversion Time (Notes 6 & 8) Output Propagation Delay (Notes 6 & 9) Output Hold Time (Notes 6 & 15) Transient Response (Note 10) Overvoltage Recovery Time (Note 11)                                                                                                                                                                     | 5                                   | 10                                                       | 20<br>15           | ns<br>ns<br>ns<br>ns             |

| AC LINEARITY (Note 12)                                                                                                                                                                                                                                                                                                                    |                                     |                                                          |                    |                                  |

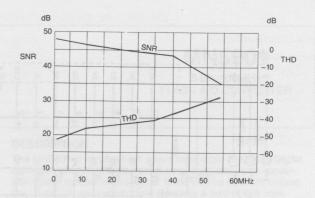

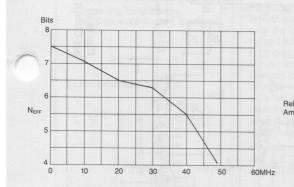

| Dynamic Linearity (Effective Bits) $f_{AN} = 1.0MHz$ $f_{AN} = 10MHz$ $f_{AN} = 35MHz Over Temperature (Note 4)$ Signal-lo Noise Ratio (SNR) $f_{AN} = 1.0MHz$ $f_{AN} = 10MHz$ $f_{AN} = 35MHz Over Temperature (Note 4)$ Total Harmonic Distortion (THD) $f_{AN} = 1.0MHz$ $f_{AN} = 1.0MHz$ $f_{AN} = 35MHz Over Temperature (Note 4)$ | 7.0<br>6.0<br>5.0<br>42<br>40<br>38 | 7.5<br>7.0<br>5.4<br>48<br>47<br>44<br>-52<br>-47<br>-35 | -42<br>-40<br>-33  | dB<br>dB<br>dB<br>dB<br>dB<br>dB |

| POWER SUPPLIES (Note 13)                                                                                                                                                                                                                                                                                                                  | See Marketon Co.                    |                                                          |                    |                                  |

| Positive Supply Current (I <sub>CC</sub> + I <sub>CC</sub> , <sub>D</sub> ) Over Temperature Negative Supply Current (I <sub>EE</sub> + I <sub>EE</sub> , <sub>D</sub> ) (Note 14) Over Temperature (Note 4)                                                                                                                              |                                     | 180<br>83                                                | 200<br>210<br>95   | mA<br>mA<br>mA                   |

| Power Consumption 25°C Over Temperature (Note 4) Power Supply Rejection                                                                                                                                                                                                                                                                   |                                     | 1.3                                                      | 100<br>1.43<br>1.5 | mA<br>Watts<br>Watts             |

| V <sub>CC</sub><br>V <sub>EE</sub>                                                                                                                                                                                                                                                                                                        | 200                                 | 35<br>35                                                 |                    | dB<br>dB                         |

#### SPECIFICATION NOTES

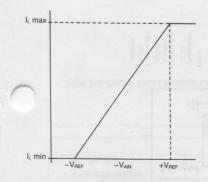

- 1. Analog input current varies linearly as a function of input voltage. See Figure

- 4. Analog Input Current versus Analog Input Voltage.

2. Full Power Bandwidth is the input frequency at which the output amplitude. drops 3dB with respect to the measured output amplitude when driven by a

- 50-ohm line terminated in 50 ohms.

- +V<sub>REF</sub> must always be more positive than -V<sub>REF</sub>.

This specification is guaranteed over the applicable temperature range.

- 5. Digital outputs are measured with an output load of 100 ohms connected to -2 Volts.

- 6. Measured on the MSB.

- 7. The positive end point error is measured with the analog input equal to +V<sub>REF</sub> less 1.5 LSB's. The negative endpoint error is measured with the analog input

- equal to  $-V_{\rm REF}$  plus 0.5 LSB's.

8. Includes one full clock conversion (10 ns) plus output propagation delay time.

- 9. Measured from falling edge of STR2 to data valid.

- 10. Full step to 8-bit accuracy.11. Time to recover to 8-bit accuracy after an overvoltage whose input is equal to 150% of the Full-Scale input voltage.

- 12. The AC linearity tests are performed at 100MHz sampling rate using the recommended strobe timing. The specified performance characteristics are derived from the FFT of the converter's response to a full scale (2 Vp-p) sinewave input. The analog input source impedance is 25 ohms (50 ohm line with a 50 ohm termination).

- For normal operation, the power supplies should remain stable within ±5% (V<sub>CC</sub>, V<sub>CC</sub>, D = +5.00V ±.25V and V<sub>EE</sub>, V<sub>EE</sub>, D = -4.5V ±.22V). The positive supplies, V<sub>CC</sub> and V<sub>CC</sub>, D, may be operated from separate power supplies with the restriction that voltage differential between the two supplies is no greater than 0.1 Volts. Similarly the negative supplies,  $V_{\text{EE}}$  and  $V_{\text{EE},\,\text{D}}$  may be operated from separate supplies with the restriction that the voltage differential between the two supplies be no greater than 0.1 Volts.

- 14. The MN5901's digital outputs are compatible with 10K ECL logic when operated from -5.2V rather than -4.5V. Operation from -5.2V will result in an increase in power consumption.

- 15. Measured from the falling edge of STR2 to previous data invalid.

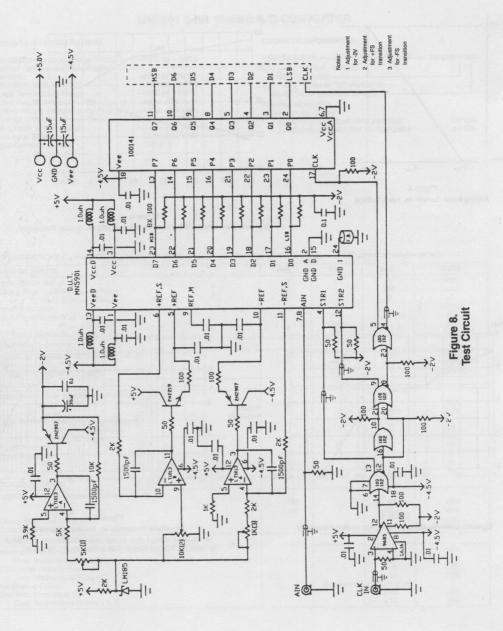

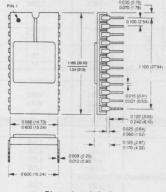

Figure 1. Block Diagram

#### APPLICATION INFORMATION

The MN5901 has an input voltage range which is symmetrical about ground and has a low input capacitance. It can be easily driven from either a monolithic amplifier or a 50-ohm system without the burden of pre-amplifiers or level shifters. Lower input impedances will, however, result in improved performance. When driving the input with an amplifier, care should be taken to select one that has a high bandwidth and low output impedance to fully utilize the MN5901's wide input bandwidth. Two analog input pins are provided in order to reduce the losses caused by lead inductance. The user should connect these two pins together close to the package.

Internal reference voltages for the MN5901's 255 comparators are derived from the  $V_{\rm REF}$  inputs by means of a reference ladder network. The MN5901 provides both reference input pins and reference sense pins. This allows the user to compensate for voltage errors caused by I-R drops from the reference inputs through the package to the reference ladder. Test circuit, Figure 8 includes circuitry that has been proven to be a simple and effective means of driving the reference inputs. The MN5901 does not include an overflow function. Consequently, the digital output will remain at 11111111 for inputs more positive than  $+V_{\rm REF}$  and will stay at 00000000 for inputs more negative than  $-V_{\rm REF}$ . The pin  $V_{\rm REF,M}$  requires no adjustments and is provided for RF decoupling only.

LAYOUT SUGGESTIONS — It is strongly recommended that a substantial ground plane be placed under and around the MN5901. This can serve as the common tie point for both analog and digital grounds. An alternative is to use separate analog and digital ground planes. In this case, the digital ground plane should surround the digital output and clock pins and the analog ground plane should

surround the analog input and reference pins. The analog and digital grounds should then be connected together with a 1 uh inductor. A third alternative is to use a single ground plane which is connected to digital ground. Both Analog GND and Digital GND pins on the MN5901 can be connected to this ground plane. The Analog and  $V_{\rm REF}$  inputs should be referenced to a separate analog ground which could be RF isolated from digital ground through a 1uh inductor. There is an additional pin, GND1, provided for the collectors of the output emitter followers. This pin may be connected directly at the MN5901 to Digital Gnd or it may be connected to a common system ground external to the MN5901. In the latter case, it is recommended that the connecting wire have a ferrite bead around it. The selection of which grounding scheme is the best one to use is dependent on system configuration and noise levels. Experimentation is recommended.

Interference from digital switching may be minimized by isolating the various supplies. This can be accomplished by connecting 1 uh inductors in series with each of the four power supply pins:  $V_{CC}$ ,  $V_{CC}$ , D,  $V_{EE}$  and  $V_{EE}$ , D.

It is recommended that .01uf ceramic decoupling capacitors be connected directly at the MN5901 to reduce the effects of system noise on converter accuracy. The  $+V_{\text{REF}}, +V_{\text{REF}}, -V_{\text{REF}}, -V_{\text{REF}}$  and  $V_{\text{REF},\text{M}}$  pins should be decoupled to analog ground. The  $V_{\text{CC}}$  p and  $V_{\text{EE}}$ , p pins should be decoupled to digital ground.  $V_{\text{CC}}$  and  $V_{\text{EE}}$ , p bins should be decoupled to whichever ground the Analog GND pin is connected. Low-inductance chip capacitors will provide the best results.

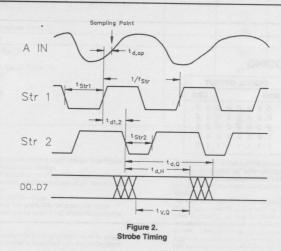

### STROBE TIMING

Each of the 255 comparators in the MN5901 consists of a differential amplifier followed by a master/slave register stage. The master and slave sections of the register are controlled independently using strobe signals, STR1 and STR2, respectively.

When STR1 is low, the master section samples the difference between the analog input and the corresponding tap on the reference ladder. The rising edge of STR1 stores the result of this comparison in the master latch.

When STR2 is low, the slave latch samples the output of the master. This value is held in the slave following the rising edge of STR2 and allowed to propagate through the encoding stages to the A/D output.

For sampling frequencies up to 75MHz, the two strobe inputs of the MN5901 can be driven by complementary logic signals having a 50% duty cycle. To optimize performance above this sampling rate,

however, requires slightly different timing. For operation at 100 MSPS, STR1 should still have a 50% duty cycle, being high for 5 nsec and low for 5 nsec. In order to provide the largest possible data valid window at the digital outputs (tyo in Figure 2), the low time of STR2 should be shortened to 3.5 nsec. Also, the sampling of the slave section of the register is optimized by delaying the falling edge of STR2 by 3 nsec after the rising edge of STR1. See Figure 2. Note that this results in the rising edge of STR2 occurring after the falling edge of STR1.

While this sounds complicated, implementation is easy and minor variations in this timing will not significantly affect performance. Using just three sections of a 100102 ECL gate, all required timing can be derived from a single-phase, 50% duty cycle clock. See Figure 3. All dynamic testing is done using this clock circuit.

## **PIN DESIGNATIONS**

| Pin | Symbol              | Function                                  | 13 | VEE, D             | Negative Supply Voltage                 |

|-----|---------------------|-------------------------------------------|----|--------------------|-----------------------------------------|

| 1   | VEE                 | Negative Supply Voltage<br>Analog Section | 14 | V <sub>CC, D</sub> | Digital Section Positive Supply Voltage |

| 2   | GND A               | Analog Ground                             |    |                    | Digital Section                         |

| 3   | Vcc                 | Positive Supply Voltage                   | 15 | GND                | Digital Ground                          |

|     | .00                 | Analog Section                            | 16 | D <sub>0</sub>     | Bit 0 (LSB)                             |

| 4   | STR1                | Strobe Signal 1                           | 17 | D <sub>1</sub>     | Bit 1                                   |

| 5   | +V <sub>REF</sub>   | Positive Reference Voltage                | 18 | D <sub>2</sub>     | Bit 2                                   |

| 6   | +VREF. S            | Positive Reference Voltage Sense          | 19 | D <sub>3</sub>     | Bit 3                                   |

| 7   | AIN                 | Analog Input                              | 20 | D <sub>4</sub>     | Bit 4                                   |

| 8   | AIN                 | Analog Input                              | 21 | D <sub>5</sub>     | Bit 5                                   |

| 9   | V <sub>REF. M</sub> | Center Tap of Reference Divider           | 22 | D <sub>6</sub>     | Bit 6                                   |

| 10  | -VREF               | Negative Reference Voltage                | 23 | D <sub>7</sub>     | Bit 7 (MSB)                             |

| 11  | -VREF, S            | Negative Reference Voltage Sense          | 24 | GND 1              | Ground Connection for                   |

| 10  | CTD 2               | Strobe Signal 2                           |    |                    | Output Emitter Follower                 |

## **DIGITAL OUTPUT CODING**

| ANALOG INPUT                           | DIGITAL OUTPUT |   |   |   |   |   |     |   |  |

|----------------------------------------|----------------|---|---|---|---|---|-----|---|--|

|                                        | MSB            |   |   |   |   | 7 | LSB |   |  |

| -V <sub>REF</sub>                      | 0              | 0 | 0 | 0 | 0 | 0 | 0   | 0 |  |

| -V <sub>REF</sub> +1/2LSB              | 0              | 0 | 0 | 0 | 0 | 0 | 0   | Ø |  |

| -1/2LSB                                | Ø              | Ø | Ø | Ø | Ø | Ø | Ø   | Ø |  |

| +½LSB                                  | 1              | 0 | 0 | 0 | 0 | 0 | 0   | Ø |  |

| +V <sub>REF</sub> -3/ <sub>2</sub> LSB | 1              | 1 | 1 | 1 | 1 | 1 | 1   | Ø |  |

The analog input voltages shown above are the theoretical voltages for the corresponding digital output. Example: With an analog input of  $-V_{\rm REF} + V_{\rm L} LSB$ , the output code will be at the transition of the codes 00000000 and 00000001.

Figure 4.

Analog Input Current vs. Input Voltage

Figure 6. Signal-to-Noise-Ratio (SNR) and Harmonic (THD) vs. Analog Frequency

Figure 5.

Dynamic Linearity (Effective Bits) vs. Analog Frequency

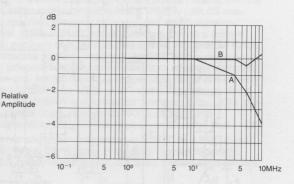

Figure 7.

Amplitude Response vs. Analog Frequency

A) Includes voltage drop across source impedance (25 ohms)

B) Does not include voltage drop across source (25 ohms)