MICROCOMPUTER MN103E

# MN103E010H/040H LSI User's Manual

Pub.No.23301-020E

**Panasonic**

PanaXSeries is a trademark of Matsushita Electric Industrial Co., Ltd.

The other corporation names, logotype and product names written in this book are trademarks or registered trademarks of their corresponding corporations.

#### Request for your special attention and precautions in using the technical information and semiconductors described in this book

- (1) An export permit needs to be obtained from the competent authorities of the Japanese Government if any of the products or technologies described in this book and controlled under the "Foreign Exchange and Foreign Trade Law" is to be exported or taken out of Japan.

- (2) The technical information described in this book is limited to showing representative characteristics and applied circuits examples of the products. It neither warrants non-infringement of intellectual property right or any other rights owned by our company or a third party, nor grants any license.

- (3) We are not liable for the infringement of rights owned by a third party arising out of the use of the product or technologies as described in this book.

- (4) The products described in this book are intended to be used for standard applications or general electronic equipment (such as office equipment, communications equipment, measuring instruments and household appliances).

Consult our sales staff in advance for information on the following applications:

- Special applications (such as for airplanes, aerospace, automobiles, traffic control equipment, combustion equipment, life support systems and safety devices) in which exceptional quality and reliability are required, or if the failure or malfunction of the products may directly jeopardize life or harm the human body.

- Any applications other than the standard applications intended.

- (5) The products and product specifications described in this book are subject to change without notice for modification and/or improvement. At the final stage of your design, purchasing, or use of the products, therefore, ask for the most up-to-date Product Standards in advance to make sure that the latest specifications satisfy your requirements.

- (6) When designing your equipment, comply with the guaranteed values, in particular those of maximum rating, the range of operating power supply voltage, and heat radiation characteristics. Otherwise, we will not be liable for any defect which may arise later in your equipment. Even when the products are used within the guaranteed values, take into the consideration of incidence of break down and failure mode, possible to occur to semiconductor products. Measures on the systems such as redundant design, arresting the spread of fire or preventing glitch are recommended in order to prevent physical injury, fire, social damages, for example, by using the products.

- (7) When using products for which damp-proof packing is required, observe the conditions (including shelf life and amount of time let standing of unsealed items) agreed upon when specification sheets are individually exchanged.

- (8) This book may be not reprinted or reproduced whether wholly or partially, without the prior written permission of Matsushita Electric Industrial Co., Ltd.

If you have any inquiries or questions about this book or our semiconductors, please contact one of our sales offices listed at the back of this book.

### Table of contents

| Chapter 1  | Overview                    |

|------------|-----------------------------|

| Chapter 2  | CPU                         |

| Chapter 3  | Operating Modes             |

| Chapter 4  | Clock generator (CKG)       |

| Chapter 5  | Bus controller (BCU)        |

| Chapter 6  | On-Chip RAM (OCR)           |

| Chapter 7  | System Bus Controller (SBC) |

| Chapter 8  | Memory Bus Controller (MBC) |

| Chapter 9  | DMA Controller (DMAC)       |

| Chapter 10 | 8-bit Timer Module (TM8)    |

| Chapter | 11 | 16-bit Timer Module (TM16)  |

|---------|----|-----------------------------|

| Chapter | 12 | Serial interface (SIF)      |

| Chapter | 13 | Interrupt controller (INTC) |

| Chapter | 14 | Watchdog timer (WDT)        |

| Chapter | 15 | AFE interface (AFE)         |

| Chapter | 16 | A/D Converter (ADC)         |

| Chapter | 17 | Real-time Clock (RTC)       |

| Chapter | 18 | IrDA Controller (IRC)       |

| Chapter | 19 | I2C Controller (I2C)        |

| Chapter | 20 | I/O Ports (PIO)             |

## Chapter 21 Electrical Specifications

Chapter 22 Appendix

**Revision Record**

21 22

Table of Contents

#### TABLE OF CONTENTS

| 1. |      | Ove   | erviev | ν                                           | 39   |

|----|------|-------|--------|---------------------------------------------|------|

|    | 1.1. | G     | eneral | L                                           | 40   |

|    | 1.2. | Fe    | eature |                                             | 40   |

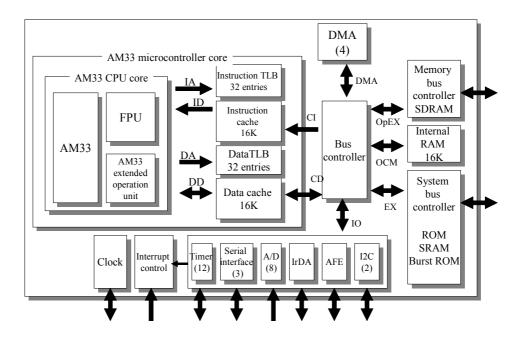

|    | 1.3. | B     | lock D | iagram                                      | 44   |

|    | 1.4. | Pi    | in Des | criptions Pin Assignments                   | 45   |

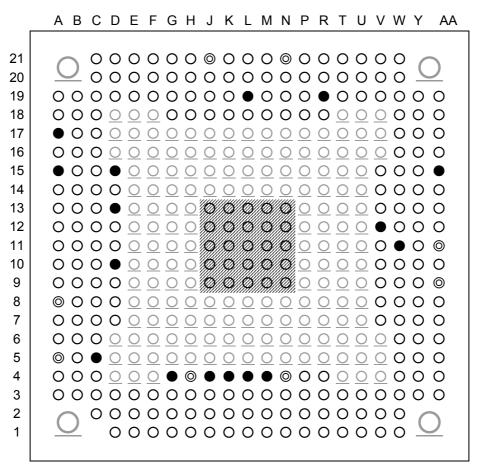

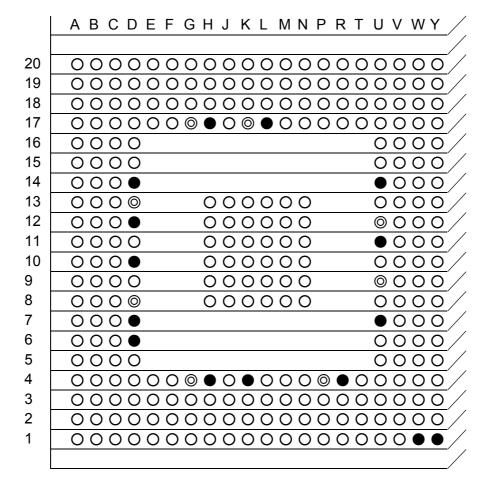

|    | 1.   | .4.1. | Pin    | e assingments                               | . 45 |

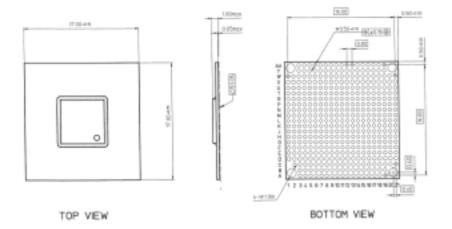

|    |      | 1.4.1 | 1.1.   | MN103E040HYB Pin assignments (Top view)     | .45  |

|    |      | 1.4.1 | 1.2.   | MN103E010HRA Pin assignments (Top view)     | .50  |

|    | 1.   | .4.2. | Pin    | Functions                                   | 53   |

|    | 1.5. | R     | egiste | r List                                      | 61   |

| 2. |      | CP    | U      |                                             | 73   |

|    | 2.1. | Ir    | ntrodu | ction                                       | . 74 |

|    | 2    | .1.1. | Ove    | erview                                      | . 74 |

|    | 2    | .1.2. | Fee    | ntures                                      | . 74 |

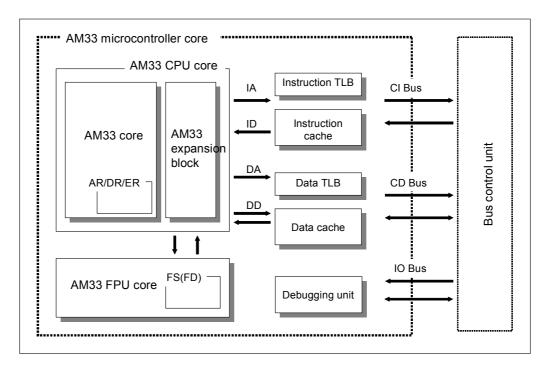

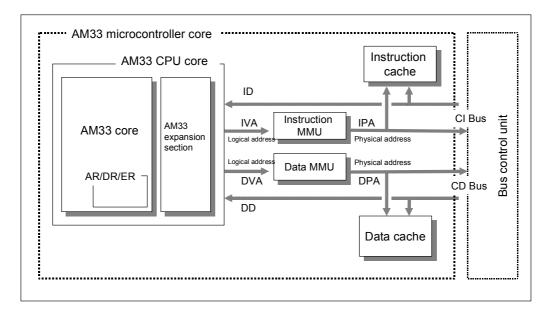

|    | 2.2. | G     | eneral | Block Diagram                               | 75   |

|    | 2.3. | P     | rogran | nming Model                                 | . 77 |

|    | 2    | .3.1. | Bas    | sic Register Set                            | . 77 |

|    |      | 2.3.1 | 1.1.   | Address Registers                           | .78  |

|    |      | 2.3.1 | 1.2.   | Data Registers                              | .79  |

|    |      | 2.3.1 | 1.3.   | Extended General-purpose Registers          | .80  |

|    |      | 2.3.1 | 1.4.   | Stack Pointers                              | .80  |

|    |      | 2.3.1 | 1.5.   | Program Counter                             | .80  |

|    |      | 2.3.1 | 1.6.   | EPSW/PSW: Processor Status Word             | .81  |

|    |      | 2.3.1 | 1.7.   | Loop Instruction Register                   | .84  |

|    |      | 2.3.1 | 1.8.   | Loop Address Register                       | .84  |

|    |      | 2.3.1 | 1.9.   | Multiply/divide Register                    | .84  |

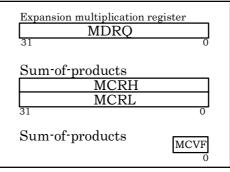

|    | 2    | .3.2. | Ext    | tended Operation Register Set               | . 85 |

|    |      | 2.3.2 | 2.1.   | Multiply/Divide Register                    | .85  |

|    |      | 2.3.2 | 2.2.   | Multiply-and-accumulate Operation Registers | .85  |

|    |      | 2.3.2 | 2.3.   | Multiply-and-accumulate Overflow Flag       | .85  |

|    | 2    | .3.3. | Flo    | ating-point Register Set                    | . 86 |

|    |      | 2.3.3 | 3.1.   | Floating-point Registers                    | .86  |

|    |      | 2.3.3 | 3.2.   | Floating-point Unit Control Register        | .86  |

|    | 2    | .3.4. | Sys    | stem Register Set                           | . 89 |

|    |      | 2.3.4 | 4.1.   | Register List                               | .91  |

| 2.3.4.2.     | CPU Mode Register                      |  |

|--------------|----------------------------------------|--|

| 2.3.4.3.     | CPU Pipeline Control Register          |  |

| 2.3.4.4.     | CPU Revision Register                  |  |

| 2.3.4.5.     | Interrupt Vector Registers             |  |

| 2.3.4.6.     | Supervisor Interrupt Status Register   |  |

| 2.3.4.7.     | NMI Control Register                   |  |

| 2.3.4.8.     | Data Access Exception Address Register |  |

| 2.3.4.9.     | Trap Base Register                     |  |

| 2.3.4.10.    | MMU Registers                          |  |

| 2.3.4.11.    | Process Identifier Register            |  |

| 2.3.4.12.    | Page Table Base Register               |  |

| 2.3.4.13.    | Page Table Entry Upper Register        |  |

| 2.3.4.14.    | Page Table Entry Lower Register        |  |

| 2.3.4.15.    | Page Table Entry Lower Register 2      |  |

| 2.3.4.16.    | MMU Exception Cause Register (MMUFCR)  |  |

| 2.3.4.17.    | Cache Control Register                 |  |

| 2.4. Data F  | 'ormats                                |  |

| 2.5. Instru  | ctions                                 |  |

| 2.5.1. In    | struction Formats                      |  |

| 2.5.2. Ad    | ldressing Modes                        |  |

| 2.5.3. In    | struction Set                          |  |

| 2.5.3.1.     | Transfer Instructions                  |  |

| 2.5.3.2.     | Arithmetic Operation Instructions      |  |

| 2.5.3.3.     | Compare Instruction                    |  |

| 2.5.3.4.     | Logic Operation Instructions           |  |

| 2.5.3.5.     | Bit Manipulation Instructions          |  |

| 2.5.3.6.     | Shift Instructions                     |  |

| 2.5.3.7.     | NOP Instruction                        |  |

| 2.5.3.8.     | Branch Instructions                    |  |

| 2.5.3.9.     | Extended Operation Instructions        |  |

| 2.5.3.10.    | LIW Extended Operation Instructions    |  |

| 2.5.3.11.    | Floating-point Operation Instructions  |  |

| 2.5.3.12.    | Debug Instruction                      |  |

| 2.6. Interru | ıpt System                             |  |

| 2.6.1. Or    | verview of Interrupts                  |  |

| 2.6.1.1.     | CPU Mode                               |  |

| 2.6.1.2 | E. Exception Opera      | ation Modes                                              | 127 |

|---------|-------------------------|----------------------------------------------------------|-----|

| 2.6.1.3 | 8. Privileged Level     |                                                          | 127 |

| 2.6.2.  | Interrupt Types (A      | M33/1,0 Mode)                                            | 128 |

| 2.6.2.1 | . Reset Interrupts      | 3                                                        | 128 |

| 2.6.    | 2.1.1. Reset Pin Inte   | rrupts                                                   | 128 |

| 2.6.2.2 | 2. Nonmaskable Ir       | iterrupts                                                | 128 |

| 2.6.    | 2.2.1. WDT Overflow     | v Interrupt                                              | 129 |

| 2.6.    | 2.2.2. NMI Pin Inter    | rupts                                                    | 129 |

| 2.6.2.3 | . Maskable Interr       | upts                                                     | 129 |

| 2.6.2.4 | . MMU Exception         | IS                                                       | 130 |

| 2.6.    | 2.4.1. Instruction TI   | B Miss Exception                                         | 131 |

| 2.6.    | 2.4.2. Data TLB Mis     | s Exception                                              | 131 |

| 2.6.    | 2.4.3. Instruction Ac   | cess Exception                                           | 131 |

| 2.6.    | 2.4.4. Data Access E    | xception                                                 | 131 |

| 2.6.2.5 | 5. System Exception     | ons                                                      | 132 |

| 2.6.    | 2.5.1. Privileged Ins   | truction Execution Exception                             | 132 |

| 2.6.    | 2.5.2. Unimplemente     | ed Instruction Exception                                 | 132 |

| 2.6.    | 2.5.3. Extended oper    | ration unit exception/unimplemented extended instruction |     |

| exce    | ption 132               |                                                          |     |

| 2.6.    | 2.5.4. Illegal Memor    | y Access Exceptions                                      | 132 |

| 2       | .6.2.5.4.1. Illegal Ins | truction Access Exceptions                               | 134 |

| 2       | .6.2.5.4.2. Illegal Da  | ta Access Exceptions                                     | 134 |

| 2       | .6.2.5.4.3. I/O Space   | Instruction Access Exceptions                            | 134 |

| 2       | .6.2.5.4.4. Privileged  | Space Instruction Access Exceptions                      | 134 |

| 2       | .6.2.5.4.5. Privileged  | Space Data Access Exceptions                             | 134 |

| 2       | .6.2.5.4.6. Data Spac   | e Instruction Access Exceptions                          | 134 |

| 2.6.    | 2.5.5. Misalignment     | Exception                                                | 135 |

| 2.6.    | 2.5.6. Double Fault.    |                                                          | 135 |

| 2.6.    | 2.5.7. Bus Errors       |                                                          | 135 |

| 2.6.2.6 | 5. System Call Ins      | truction Exceptions                                      | 136 |

| 2.6.2.7 | 7. FPU Exceptions       |                                                          | 136 |

| 2.6.2.8 | 8. "FPU Disabled"       | Exception                                                | 137 |

| 2.6.2.9 | . FPU Unimplem          | ented Instruction Exception                              | 137 |

| 2.6.2.1 | 0. FPU Operation        | Exception                                                | 137 |

| 2.6.3.  | List of Interrupt C     | odes and Interrupt Vectors (AM33/1.0 Mode)               | 137 |

| 2.6.4.  | Interrupt Types (A      | M33/2.0 Mode)                                            | 140 |

|     | 2.6.4.1.    | Reset Interrupts                                                     | 140 |

|-----|-------------|----------------------------------------------------------------------|-----|

|     | 2.6.4.1.1.  | Reset Pin Interrupts                                                 | 140 |

|     | 2.6.4.2.    | Nonmaskable Interrupts                                               | 140 |

|     | 2.6.4.2.1.  | WDT Overflow Interrupt                                               | 141 |

|     | 2.6.4.2.2.  | NMI Pin Interrupts                                                   | 141 |

|     | 2.6.4.3.    | Maskable Interrupts                                                  | 141 |

|     | 2.6.4.4.    | MMU Exceptions                                                       | 142 |

|     | 2.6.4.4.1.  | Instruction TLB Miss Exception                                       | 143 |

|     | 2.6.4.4.2.  | Data TLB Miss Exception                                              | 143 |

|     | 2.6.4.4.3.  | Instruction Access Exception                                         | 143 |

|     | 2.6.4.4.4.  | Data Access Exception                                                | 143 |

|     | 2.6.4.5.    | System Exceptions                                                    | 143 |

|     | 2.6.4.5.1.  | Privileged Instruction Execution Exception                           | 144 |

|     | 2.6.4.5.2.  | Unimplemented Instruction Exception                                  | 144 |

|     | 2.6.4.5.3.  | Extended operation unit exception/unimplemented extended instruction |     |

|     | exception   | 144                                                                  |     |

|     | 2.6.4.5.4.  | Illegal Memory Access Exceptions                                     | 144 |

|     | 2.6.4.5     | .4.1. Illegal Instruction Access Exceptions                          | 146 |

|     | 2.6.4.5     | .4.2. Illegal Data Access Exceptions                                 | 146 |

|     | 2.6.4.5     | .4.3. I/O Space Instruction Access Exceptions                        | 146 |

|     | 2.6.4.5     | .4.4. Privileged Space Instruction Access Exceptions                 | 146 |

|     | 2.6.4.5     | .4.5. Privileged Space Data Access Exceptions                        | 146 |

|     | 2.6.4.5     | .4.6. Data Space Instruction Access Exceptions                       | 146 |

|     | 2.6.4.5.5.  | Misalignment Exception                                               | 146 |

|     | 2.6.4.5.6.  | Double Fault                                                         | 146 |

|     | 2.6.4.5.7.  | Bus Errors                                                           | 147 |

|     | 2.6.4.6.    | System Call Instruction Exceptions                                   | 147 |

|     | 2.6.4.7.    | FPU Exceptions                                                       | 149 |

|     | 2.6.4.8.    | "FPU Disabled" Exception                                             | 149 |

|     | 2.6.4.9.    | FPU Unimplemented Instruction Exception                              | 149 |

|     | 2.6.4.10.   | FPU Operation Exception                                              | 149 |

| 2   | 2.6.5. List | of Interrupt Codes and Interrupt Vectors (AM33/2.0 Mode)             | 150 |

| 2   | 2.6.6. Ret  | urning from an Interrupt                                             | 152 |

| 2   | 2.6.7. Prie | prity Ranking                                                        | 153 |

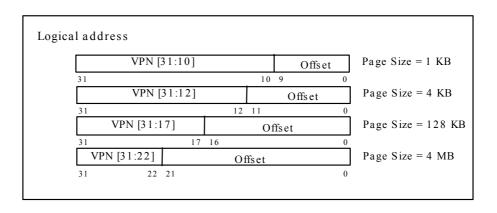

| 2.7 | . Memory    | Management                                                           | 154 |

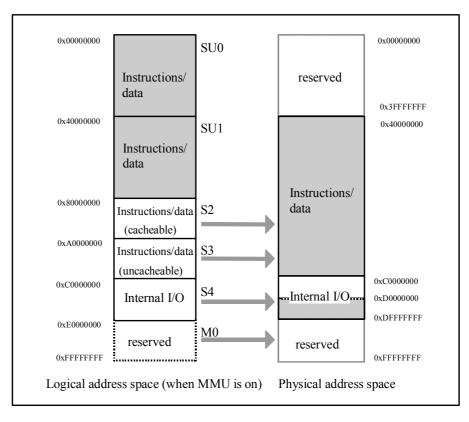

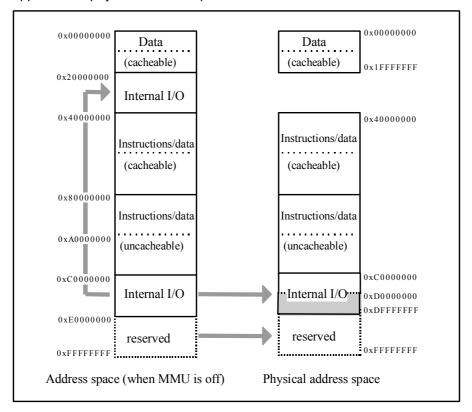

| 2   | 2.7.1. Add  | lress Space                                                          | 155 |

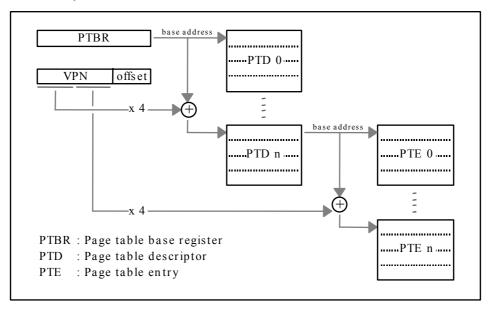

| 2.7.2. Ad    | ddress Translation and Process Identifiers        |  |

|--------------|---------------------------------------------------|--|

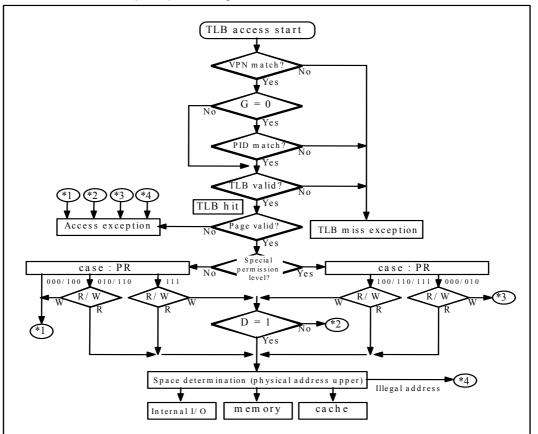

| 2.7.3. T     | LB (Translation Lookaside Buffer)                 |  |

| 2.7.3.1.     | TLB Configuration                                 |  |

| 2.7.3.2.     | TLB Address Comparison                            |  |

| 2.7.3.3.     | TLB Entry Lock                                    |  |

| 2.7.4. M     | MU Functions                                      |  |

| 2.7.4.1.     | MMU Hardware Management                           |  |

| 2.7.4.2.     | MMU Software Management                           |  |

| 2.7.4.2.     | 1. MMU Register Settings                          |  |

| 2.7.4.2.     | 2. TLB Entry Registration                         |  |

| 2.7.4.2.     | 3. TLB Entry Read                                 |  |

| 2.7.4.2.     | 4. TLB Entry Deletion                             |  |

| 2.7.4.3.     | Table Work                                        |  |

| 2.7.5. E     | xceptions                                         |  |

| 2.7.5.1.     | Instruction TLB Miss Exception                    |  |

| 2.7.5.2.     | Data TLB Miss Exception                           |  |

| 2.7.5.3.     | Instruction Access Exception                      |  |

| 2.7.5.4.     | Data Access Exception                             |  |

| 2.7.5.5.     | Exception Cause Codes                             |  |

| 2.7.5.6.     | Flow of Processing When an Exception Is Generated |  |

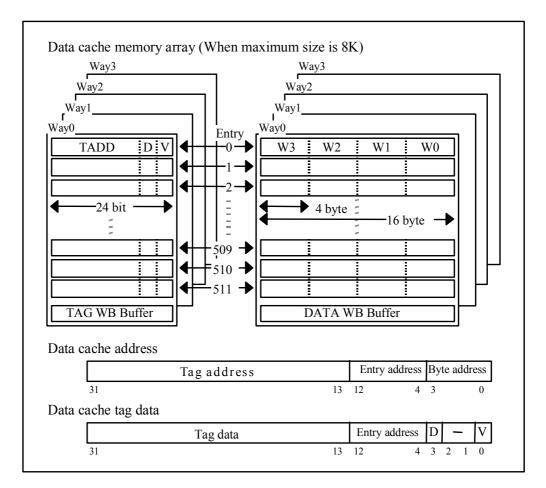

| 2.8. Cache   |                                                   |  |

| 2.8.1. In    | struction Cache                                   |  |

| 2.8.2. D.    | ata Cache                                         |  |

| 2.8.3. O     | peration                                          |  |

| 2.8.3.1.     | Instruction Cache                                 |  |

| 2.8.3.1.     | 1. Initialization                                 |  |

| 2.8.3.1.     | 2. Reading Operation                              |  |

| 2.8.3.2.     | Data Cache                                        |  |

| 2.8.3.2.     | 1. Initialization                                 |  |

| 2.8.3.2.     | 2. Reading Operation                              |  |

| 2.8.3.2.     | 3. Write Operation                                |  |

| 2.8.3.2.     | 4. Consistency between Caches and External Memory |  |

| 2.8.3.3.     | Way Operation Mode                                |  |

| 2.8.3.4.     | Cache Entry Address Allocation                    |  |

| 2.9. Floatin | ng-point Unit                                     |  |

| 2.9.1. O     | verview                                           |  |

| 2.9.2. Data Format                                |     |

|---------------------------------------------------|-----|

| 2.9.2.1. Floating-point Format                    |     |

| 2.9.2.1.1. Floating-point Numbers                 |     |

| 2.9.2.1.2. Floating-point Format                  |     |

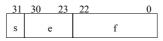

| 2.9.2.1.3. Single-precision Floating-point Format |     |

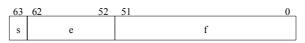

| 2.9.2.1.4. Double-precision Floating-point Format |     |

| 2.9.2.2. NaN (Not-a-Number)                       |     |

| 2.9.2.3. Denormalized Numbers                     |     |

| 2.9.3. Rounding                                   |     |

| 2.9.4. Exceptions                                 |     |

| 2.9.4.1. FPU Disable Exception                    |     |

| 2.9.4.2. FPU Unimplemented Instruction Exception  |     |

| 2.9.4.3. FPU Operation Exceptions                 |     |

| 2.9.4.3.1. Exception Causes                       |     |

| 2.9.4.3.2. FPU Exception Enable                   |     |

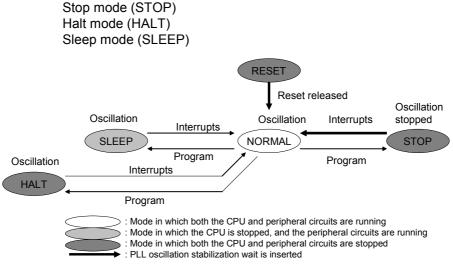

| 3. Operating Modes                                |     |

| 3.1. General                                      |     |

| 3.2. Low power consumption modes                  |     |

| 3.3. Oscillation Stabilization Wait Operation     |     |

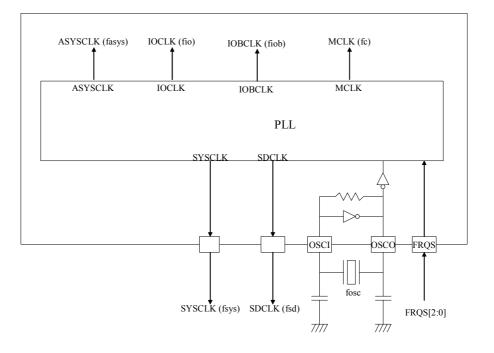

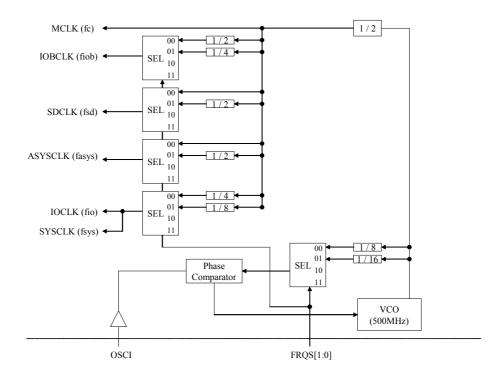

| 4. Clock generator (CKG)                          | 191 |

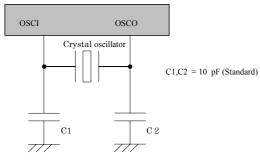

| 4.1. General                                      |     |

| 4.2. Features                                     |     |

| 4.3. Block Diagram                                |     |

| 4.4. Description of Operation                     |     |

| 4.4.1. Input Frequency                            |     |

| 4.4.2. Clock Supply                               |     |

| 4.4.3. Cautions                                   |     |

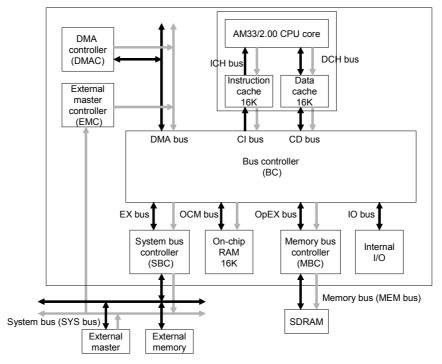

| 5. Bus controller (BCU)                           |     |

| 5.1. General                                      |     |

| 5.2. Features                                     |     |

| 5.3. Configuration                                |     |

| 5.4. Description of Registers                     |     |

| 5.4.1. Bus controller control register            |     |

| 5.4.2. Bus error source register                  |     |

| 5.4.3. Bus error address register                 |     |

| 5.5. De | escription of Operation                     |     |

|---------|---------------------------------------------|-----|

| 5.5.1.  | Bus Error Detection                         |     |

| 5.5.2.  | Burst Transfer                              |     |

| 5.5.3.  | Bus Lock                                    |     |

| 5.5.4.  | Write Buffer                                |     |

| 5.6. M  | emory Space                                 |     |

| 6. On-  | Chip RAM (OCR)                              | 205 |

| 6.1. Ge | eneral                                      |     |

| 6.2. Fe | eatures                                     |     |

| 7. Sys  | tem Bus Controller (SBC)                    |     |

| 7.1. Ge | eneral                                      |     |

| 7.2. Fe | eatures                                     |     |

| 7.3. De | escription of Registers                     |     |

| 7.3.1.  | Base Address Register                       |     |

| 7.3.2.  | Bank control register 0                     |     |

| 7.3.3.  | Bank control register 1                     |     |

| 7.3.4.  | Bank control register 2                     |     |

| 7.4. De | escription of Operation                     |     |

| 7.4.1.  | Access Data Alignment                       |     |

| 7.4.2.  | Transfer Size                               |     |

| 7.4.3.  | Chip select                                 |     |

| 7.4.4.  | SRAM Interface                              |     |

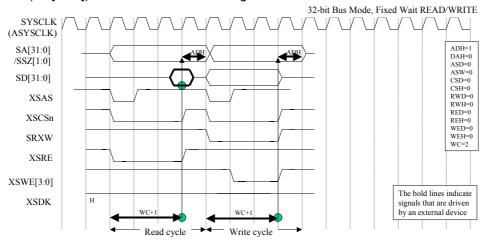

| 7.4.4   | 1.1. 32-bit Bus Fixed Wait Access           | 217 |

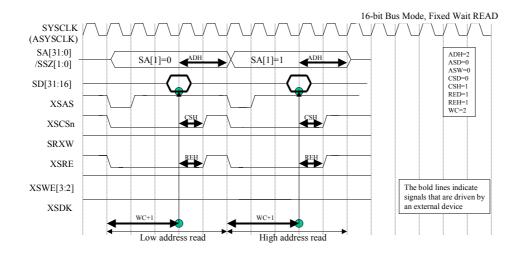

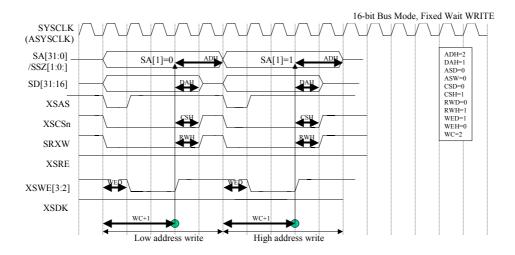

| 7.4.4   | 16-bit Bus Fixed Wait Access                | 218 |

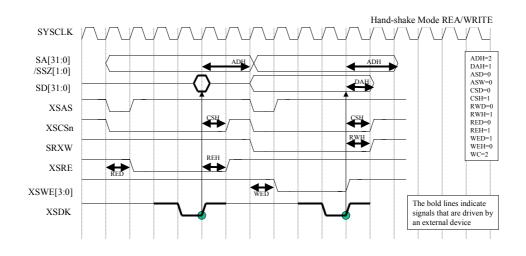

| 7.4.4   | .3. 32-bit Bus Handshake Access             | 219 |

| 7.4.4   | .4. 16-bit Bus Handshake Access             |     |

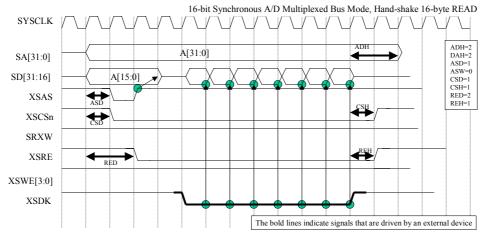

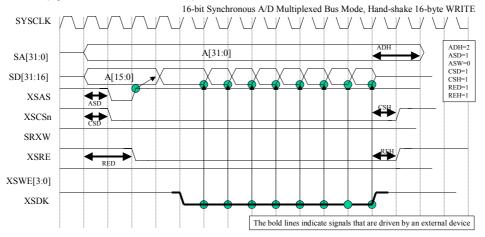

| 7.4.5.  | Address/Data Multiplexed Interface          |     |

| 7.4.5   | 5.1. 32-bit Bus Fixed Wait Access           |     |

| 7.4.5   | 5.2. 16-bit Bus Fixed Wait Access           |     |

| 7.4.5   | 5.3. 32-bit Bus Handshake Access            |     |

| 7.4.5   | 6.4. 16-bit Bus Handshake Access            |     |

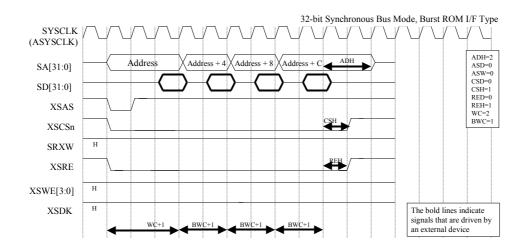

| 7.4.6.  | Burst ROM Interface                         |     |

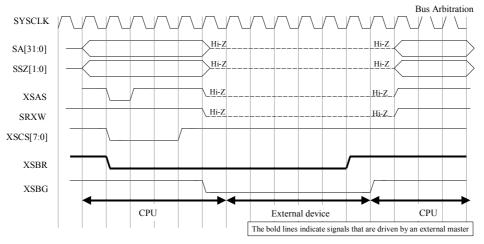

| 7.4.7.  | External Master Device Support              |     |

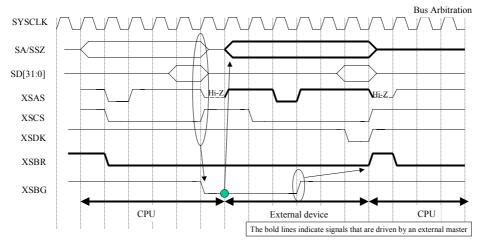

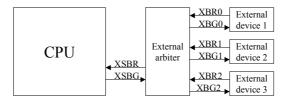

| 7.4.7   | 7.1. Bus Arbitration                        | 230 |

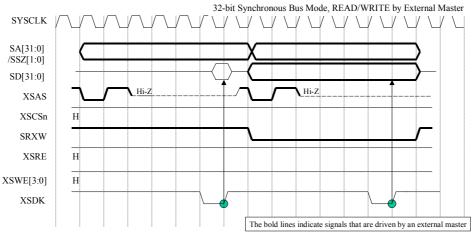

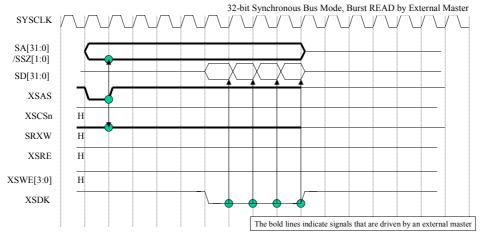

| 7.4.7   | 7.2. External Master Device Access          | 232 |

| 7.4     | 4.7.2.1. Internal Memory, Memory Bus Access | 232 |

|      | 7.4.7   | 7.2.2.  | System Bus Access                                         | 234 |

|------|---------|---------|-----------------------------------------------------------|-----|

| 7.5. | Cau     | itions  |                                                           |     |

| 7.   | 5.1.    | Limi    | tations concerning the bus timing setting                 |     |

| 8.   | Mem     | orv B   | us Controller (MBC)                                       |     |

| 8.1. |         |         |                                                           |     |

| 8.2. |         |         |                                                           |     |

| 8.3. | Des     | criptio | on of Registers                                           |     |

| 8.   | 3.1.    | Bus 1   | node control register                                     |     |

| 8.   | 3.2.    | Refre   | sh period register                                        |     |

| 8.   | 3.3.    | Base    | address register 0                                        |     |

| 8.   | 3.4.    | Base    | address register 1                                        | 243 |

| 8.   | 3.5.    | SD si   | hadow register                                            | 244 |

| 8.4. | Des     | criptio | on of Operation                                           |     |

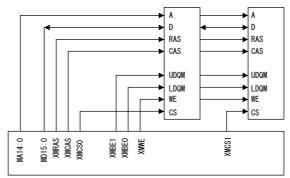

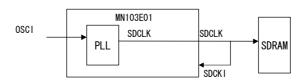

| 8.   | 4.1.    | Conn    | ection Example                                            |     |

| 8.   | 4.2.    | Clock   | Generation                                                | 246 |

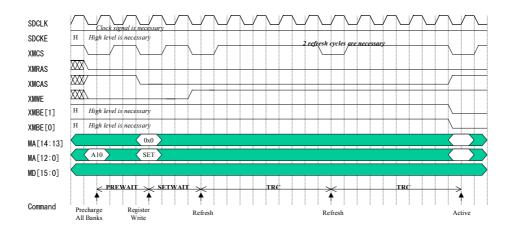

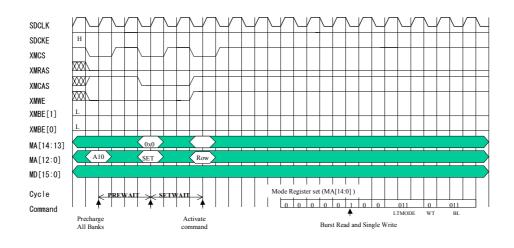

| 8.   | 4.3.    | SDR.    | AM Initialization                                         | 246 |

| 8.   | 4.4.    | Acces   | ss Mode                                                   |     |

| 8.   | 4.5.    | Acces   | ss Data Alignment                                         | 247 |

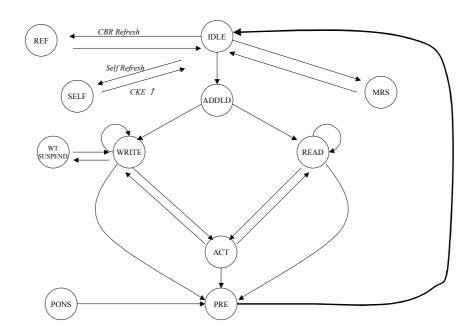

| 8.   | 4.6.    | SDR.    | AM Controller State Transitions                           |     |

| 8.   | 4.7.    | Addr    | essing                                                    |     |

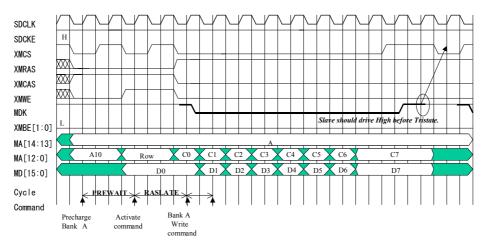

| 8.   | 4.8.    | Timi    | ng Diagram                                                |     |

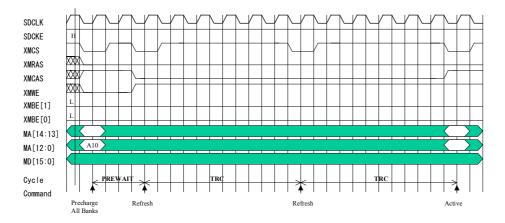

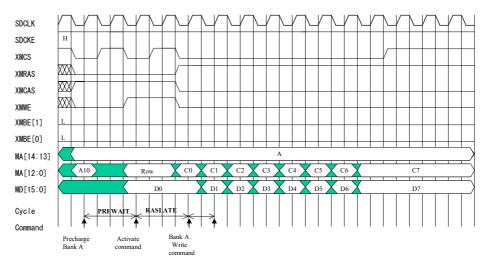

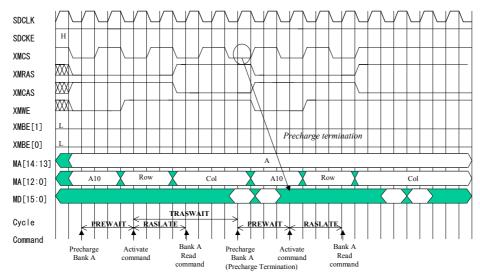

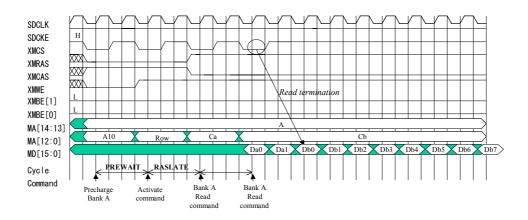

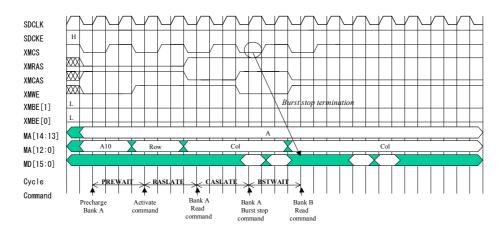

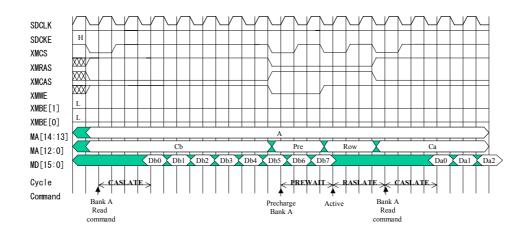

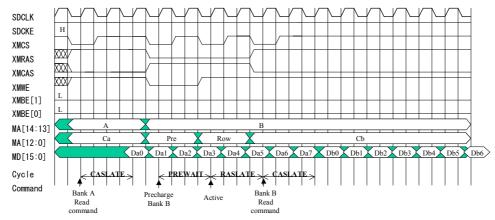

|      | 8.4.8.1 | . N     | Normal Operation Mode                                     | 249 |

|      | 8.4.8   | 8.1.1.  | Power up sequence setting                                 | 249 |

|      | 0.111   |         | Mode Register Settings                                    |     |

|      | 8.4.8   | 8.1.3.  | Auto-refresh (CBR refresh)                                | 250 |

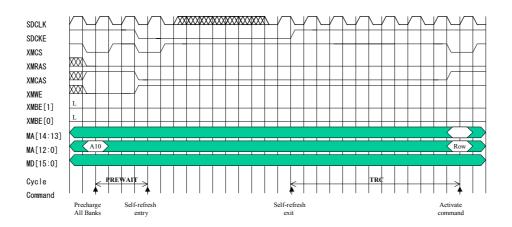

|      | 8.4.8   | 8.1.4.  | Self-refresh                                              |     |

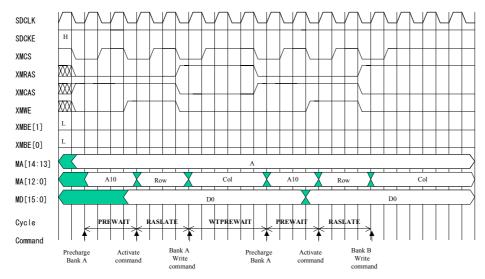

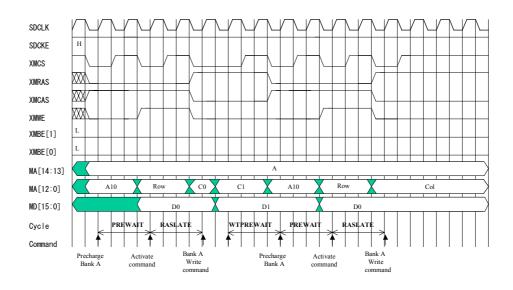

|      | 8.4.8   | 8.1.5.  | Single write access (Page miss)                           |     |

|      | 8.4.8   | 8.1.6.  | 2-word write access (Page miss)                           |     |

|      | 8.4.8   | 8.1.7.  | 8-word write access (Page miss)                           |     |

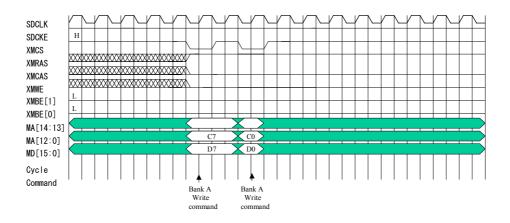

|      | 8.4.8   | 8.1.8.  | 1-word continuous write access (Page hit)                 |     |

|      |         | 8.1.9.  | 8-word continuous write access (Page hit)                 |     |

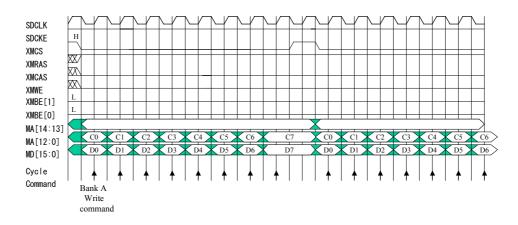

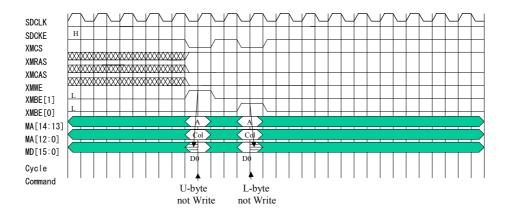

|      |         | 8.1.10. | Byte access                                               |     |

|      |         | 8.1.11. | 2-word burst read access (Precharge termination)          |     |

|      |         | 8.1.12. | 2-word burst read access (Read termination)               |     |

|      | 8.4.8   | 8.1.13. | 2-word burst read access (Burst stop command termination) |     |

|      | 8.4.8   | 8.1.14. | Continuous burst read access (Same bank & Page miss)      | 255 |

| 8.4.8.1         | .15. Continuous burst read access (Different Bank & Page miss)      | 256 |

|-----------------|---------------------------------------------------------------------|-----|

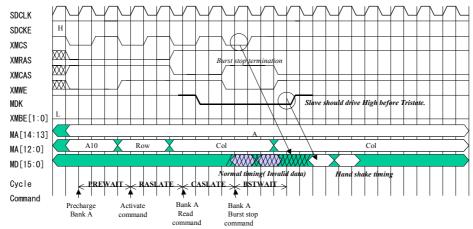

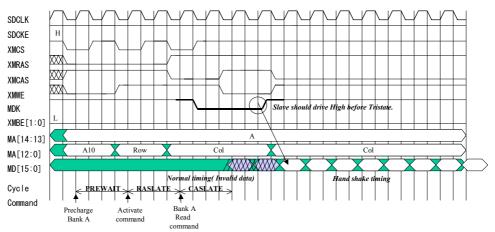

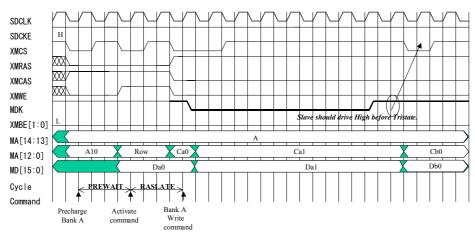

| 8.4.8.2.        | Handshake Mode                                                      | 256 |

| 8.4.8.2         | 2.1. Read access                                                    | 257 |

| 8.4.8.2         | 2.2. Burst Read Access                                              | 257 |

| 8.4.8.2         | 2.3. Write access                                                   | 258 |

| 8.4.8.2         | 2.4. Burst Write Access                                             | 258 |

| 8.5. Cauti      | ons                                                                 | 259 |

| 9. DMA C        | Controller (DMAC)                                                   | 261 |

| 9.1. Gener      | ral                                                                 |     |

| 9.2. Featu      | res                                                                 | 262 |

| 9.3. Descr      | iption of Registers                                                 | 263 |

| 9.3.1. I        | DMA Control Register                                                |     |

| 9.3.2. I        | OMA Source Address Register                                         |     |

| 9.3.3. I        | OMA Destination Address Register                                    |     |

| 9.3.4. I        | OMA Transfer Word Size Register                                     |     |

| 9.3.5. I        | DMA Intermittent Transfer Count Register                            |     |

| 9.4. Descr      | iption of Operation                                                 |     |

| 9.4.1. 7        | Types of Transfers                                                  |     |

| 9.4.2. 7        | Fransfer modes                                                      |     |

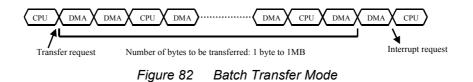

| 9.4.2.1.        | Batch Transfer Mode                                                 |     |

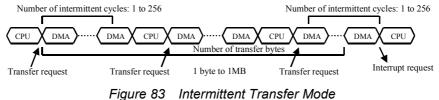

| 9.4.2.2.        | Intermittent Transfer Mode                                          |     |

| 9.4.3. H        | Priority ranking                                                    |     |

| 9.4.4. E        | Bus Lock                                                            |     |

| 9.4.5. T        | ransfer unit:                                                       | 269 |

| 9.4.6. N        | Number of intermittent transfers                                    |     |

| 9.4.7. 7        | Transfer Addresses                                                  |     |

| 9.4.7.1.        | Specification of Transfer Source and Transfer Destination Addresses |     |

| 9.4.7.2.        | Relationship between the Transfer Unit and Address Alignment        |     |

| 9.4.7.3.        | Address Alignment Requirements for 16-byte Transfers                |     |

| <i>9.4.8. 1</i> | Transfer Size                                                       |     |

| <i>9.4.9. 1</i> | Transfer Initiation                                                 | 270 |

| 9.4.9.1.        | Transfer Initiation by an External Request                          |     |

| 9.4.9.2.        | Transfer Initiation by an External Interrupt                        |     |

| 9.4.9.3.        | Transfer Initiation by an Internal Interrupt                        |     |

| 9.4.9.4.        | Transfer Initiation by Software                                     | 271 |

| 9.4.10.         | Transfer Start/Interruption/End/Forced Termination                  |     |

| 9.5. Ca  | utions                                                       |     |

|----------|--------------------------------------------------------------|-----|

| 9.5.1.   | Cautions about specifying transfer address                   |     |

| 9.5.2.   | Cautions about specifying the transfer size                  |     |

| 9.5.3.   | Cautions about DMA transfer bus error                        |     |

| 10. 8-bi | t Timer Module (TM8)                                         |     |

| 10.1.    | General                                                      |     |

| 10.2.    | Features                                                     |     |

| 10.3.    | Description of Registers                                     |     |

| 10.3.1.  | Timer Mode Register                                          |     |

| 10.3.2.  | Timer Base Register                                          | 276 |

| 10.3.3.  | Timer Binary Counter                                         |     |

| 10.3.4.  | Timer prescaler control register                             |     |

| 10.4.    | Description of Operation                                     |     |

| 10.4.1.  | Operation Start Procedure                                    |     |

| 10.4.2.  | Operation Stop Procedure                                     | 278 |

| 10.4.3.  | Clock Source Selection                                       |     |

| 10.4.4.  | Cascaded connection                                          | 278 |

| 10.4.5.  | Example of Using the Prescaler and Cascaded Connection       |     |

| 10.5.    | Cautions                                                     |     |

| 11. 16-k | bit Timer Module (TM16)                                      |     |

| 11.1.    | General                                                      |     |

| 11.2.    | Features                                                     |     |

| 11.3.    | List of Functions                                            |     |

| 11.4.    | Description of Registers                                     |     |

| 11.4.1.  | Timer mode register                                          |     |

| 11.4.2.  | Timer 6 mode register                                        |     |

| 11.4.3.  | Timer Base Register                                          |     |

| 11.4.4.  | Timer binary counter                                         |     |

| 11.4.5.  | Timer 6 Compare/Capture A Mode Register                      |     |

| 11.4.6.  | Timer 6 Compare/Capture B Mode Register                      |     |

| 11.4.7.  | Timer 6 Compare/Capture Register A                           |     |

| 11.4.8.  | Timer 6 Compare/Capture Register B                           |     |

| 11.4.9.  | Timer prescaler control register                             |     |

| 11.5.    | Description of Operations of timers 4, 5, 7, 8, 9, 10 and 11 | 296 |

| 11.5.1.  | Interval Timer and Timer Output                              |     |

| 11.5.    | 1.1. Operation Start Procedure                               |     |

| 11.5.1.2   | Operation Stop Procedure                         |     |

|------------|--------------------------------------------------|-----|

| 11.5.2.    | Event Count                                      |     |

| 11.5.2.1   | . Operation Start Procedure                      |     |

| 11.5.3.    | Cascaded connection                              |     |

| 11.6. De   | scription of Operations of Timer 6               | 300 |

| 11.6.1.    | Binary Counter Settings                          | 300 |

| 11.6.2.    | Compare/Capture Register Settings                | 300 |

| 11.6.3.    | High-Speed PWM Mode Settings                     | 301 |

| 11.7. Ca   | utions                                           |     |

| 12. Serial | interface (SIF)                                  | 303 |

| 12.1. Ge   | neral                                            |     |

| 12.2. Fe   | atures                                           |     |

| 12.2.1.    | Serial Interface 0 (Serial Interface 1)          | 304 |

| 12.2.2.    | Serial Interface 2                               | 305 |

| 12.3. Re   | gisters                                          | 306 |

| 12.3.1.    | Serial Control Register                          | 307 |

| 12.3.2.    | Serial Interrupt Mode Register                   | 309 |

| 12.3.3.    | Serial Transmit Buffer                           |     |

| 12.3.4.    | Serial Receive Buffer                            |     |

| 12.3.5.    | Serial Status Register                           |     |

| 12.3.6.    | Serial 2 Control Register                        |     |

| 12.3.7.    | Serial 2 Interrupt Mode Register                 |     |

| 12.3.8.    | Serial 2 Transmit Buffer                         |     |

| 12.3.9.    | Serial 2 Receive Buffer                          |     |

| 12.3.10.   | Serial 2 Status Register                         |     |

| 12.3.11.   | Serial 2 Timer Register                          |     |

| 12.4. De   | scription of Operation (Serial interface 0 or 1) |     |

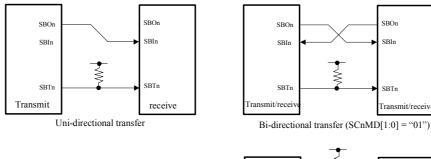

| 12.4.1.    | Connections                                      |     |

| 12.4.2.    | Baud Rate                                        |     |

| 12.4.3.    | Using Clock Synchronous Mode                     | 320 |

| 12.4.4.    | Using Start-Stop Synchronous Mode                | 321 |

| 12.4.5.    | Using I2C Mode                                   | 322 |

| 12.4.6.    | Receive Errors                                   |     |

| 12.5. De   | scription of Operation (Serial interface 2)      | 323 |

| 12.5.1.    | Connections                                      |     |

| 12.5.2.    | Baud Rate                                        | 324 |

| 12.6.        | Cautions                                            |                                 |

|--------------|-----------------------------------------------------|---------------------------------|

| 13. Ir       | nterrupt controller (INTC)                          |                                 |

| 13.1.        | General                                             |                                 |

| 13.2.        | Features                                            |                                 |

| 13.3.        | Interrupt Signal Assignments                        |                                 |

| 13.4.        | Description of Registers                            |                                 |

| <i>13.</i> 4 | 4.1. Relationship Between the Timer frequency d     | ivision ratio and the Baud Rate |

|              | 330                                                 |                                 |

| 13.4         | 4.2. Group n Interrupt Control Register             |                                 |

| 13.4         | 4.3. Interrupt Acceptance Group Register            |                                 |

| 13.4         | 4.4. External Pin Interrupt Condition Specification | on Register                     |

| 13.5.        | Description of Operation                            |                                 |

| 13.6.        | Cautions                                            |                                 |

| 14. V        | Vatchdog timer (WDT)                                |                                 |

| 14.1.        | General                                             |                                 |

| 14.2.        | Features                                            |                                 |

| 14.3.        | Description of Registers                            |                                 |

| 14.3         | 3.1. Watchdog Binary Counter                        |                                 |

| 14.3         | 3.2. Watchdog Timer Control Register                |                                 |

| 14.3         | 3.3. Reset Control Register                         |                                 |

| 14.4.        | Description of Operation                            |                                 |

| 14.4         | 4.1. Oscillation Stabilization Wait Operation       |                                 |

| 14.4         | 4.2. Watchdog Operation                             |                                 |

| 14.4         | 4.3. Self-Reset Operation                           |                                 |

| 14.5.        | Cautions                                            |                                 |

| 15. A        | Analog Front End interface (AFE)                    |                                 |

| 15.1.        | General                                             |                                 |

| 15.2.        | Features                                            |                                 |

| 15.3.        | Register                                            |                                 |

| 15.3         | 3.1. Analog Front End System Control Register       |                                 |

| 15.3         | 3.2. Analog Front End Interrupt Mask Register       |                                 |

| 15.3         | 3.3. Analog Front End Status Register               |                                 |

| 15.3         | 3.4. Analog Front End Control Register              |                                 |

| 15.3         | 3.5. Analog Front End Transmit Buffer Register      |                                 |

| 15.3         | 3.6. Analog Front End Receive Buffer Register       |                                 |

|                                                                                                                                     | Analog Front End FIFO Size Register                                                                                                                                                                                                                                                                 |     |

|-------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 15.3.8.                                                                                                                             | Analog Front End Eye Pattern Register                                                                                                                                                                                                                                                               |     |

| 15.3.9.                                                                                                                             | Analog Front End Second Source Register                                                                                                                                                                                                                                                             |     |

| 15.4. De                                                                                                                            | scription of Operation                                                                                                                                                                                                                                                                              |     |

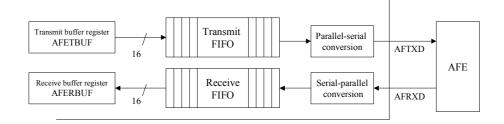

| 15.4.1.                                                                                                                             | Data Transmit and Receive                                                                                                                                                                                                                                                                           | 353 |

| 15.4.2.                                                                                                                             | Interrupts                                                                                                                                                                                                                                                                                          |     |

| 15.4.3.                                                                                                                             | NCU Control                                                                                                                                                                                                                                                                                         | 353 |

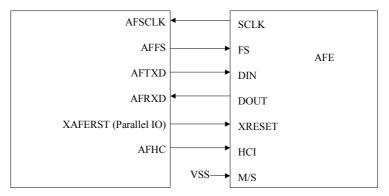

| 15.4.4.                                                                                                                             | Example Connections with Analog Front End Devices                                                                                                                                                                                                                                                   |     |

| 16. A/D C                                                                                                                           | onverter (ADC)                                                                                                                                                                                                                                                                                      |     |

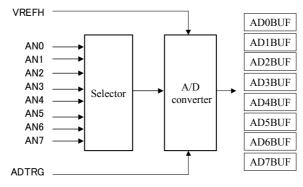

| 16.1. Ge                                                                                                                            | neral                                                                                                                                                                                                                                                                                               | 356 |

| 16.2. Fe                                                                                                                            | atures                                                                                                                                                                                                                                                                                              |     |

| 16.3. De                                                                                                                            | scription of Registers                                                                                                                                                                                                                                                                              |     |

| 16.3.1.                                                                                                                             | A/D Conversion Control Register                                                                                                                                                                                                                                                                     |     |

| <i>16.3.2.</i>                                                                                                                      | A/D Conversion Data Buffer                                                                                                                                                                                                                                                                          | 359 |

| 16.4. De                                                                                                                            | scription of Operation                                                                                                                                                                                                                                                                              |     |

| 16.4.1.                                                                                                                             | Selecting the Operational Mode                                                                                                                                                                                                                                                                      | 360 |

| 16.4.2.                                                                                                                             | Selecting the Conversion Reference Clock                                                                                                                                                                                                                                                            | 360 |

| 16.5. Ca                                                                                                                            | utions                                                                                                                                                                                                                                                                                              |     |

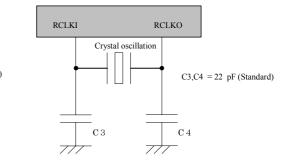

| 17. Real-t                                                                                                                          | ime Clock (RTC)                                                                                                                                                                                                                                                                                     |     |

|                                                                                                                                     | neral                                                                                                                                                                                                                                                                                               |     |

|                                                                                                                                     |                                                                                                                                                                                                                                                                                                     |     |

| 17.2. Fe                                                                                                                            | atures                                                                                                                                                                                                                                                                                              |     |

|                                                                                                                                     | atures<br>gisters                                                                                                                                                                                                                                                                                   |     |

|                                                                                                                                     |                                                                                                                                                                                                                                                                                                     |     |

| 17.3. Re                                                                                                                            | gisters                                                                                                                                                                                                                                                                                             |     |

| 17.3. Re<br><i>17.3.1.</i><br><i>17.3.2.</i>                                                                                        | gisters<br>Seconds Count Register                                                                                                                                                                                                                                                                   |     |

| 17.3. Re<br><i>17.3.1.</i><br><i>17.3.2.</i>                                                                                        | gisters<br>Seconds Count Register<br>Seconds Alarm Register                                                                                                                                                                                                                                         |     |

| 17.3. Re<br><i>17.3.1.</i><br><i>17.3.2.</i><br><i>17.3.3.</i>                                                                      | gisters<br>Seconds Count Register<br>Seconds Alarm Register<br>Minutes Count Register                                                                                                                                                                                                               |     |

| 17.3. Re<br><i>17.3.1.</i><br><i>17.3.2.</i><br><i>17.3.3.</i><br><i>17.3.4.</i>                                                    | gisters<br>Seconds Count Register<br>Seconds Alarm Register<br>Minutes Count Register<br>Minutes Alarm Register                                                                                                                                                                                     |     |

| 17.3. Re<br>17.3.1.<br>17.3.2.<br>17.3.3.<br>17.3.4.<br>17.3.5.                                                                     | gisters<br>Seconds Count Register<br>Seconds Alarm Register<br>Minutes Count Register<br>Minutes Alarm Register<br>Hours Count Register                                                                                                                                                             |     |

| 17.3. Re<br>17.3.1.<br>17.3.2.<br>17.3.3.<br>17.3.4.<br>17.3.5.<br>17.3.6.                                                          | gisters<br>Seconds Count Register<br>Seconds Alarm Register<br>Minutes Count Register<br>Minutes Alarm Register<br>Hours Count Register<br>Hours Alarm Register                                                                                                                                     |     |

| 17.3. Re<br>17.3.1.<br>17.3.2.<br>17.3.3.<br>17.3.4.<br>17.3.5.<br>17.3.6.<br>17.3.7.                                               | gisters<br>Seconds Count Register<br>Seconds Alarm Register<br>Minutes Count Register<br>Minutes Alarm Register<br>Hours Count Register<br>Hours Alarm Register<br>Day of the Week Count Register                                                                                                   |     |

| 17.3. Re<br>17.3.1.<br>17.3.2.<br>17.3.3.<br>17.3.4.<br>17.3.5.<br>17.3.6.<br>17.3.7.<br>17.3.8.                                    | gisters<br>Seconds Count Register<br>Seconds Alarm Register<br>Minutes Count Register<br>Minutes Alarm Register<br>Hours Count Register<br>Hours Alarm Register<br>Day of the Week Count Register<br>Days Count Register                                                                            |     |

| 17.3. Re<br>17.3.1.<br>17.3.2.<br>17.3.3.<br>17.3.4.<br>17.3.5.<br>17.3.6.<br>17.3.7.<br>17.3.8.<br>17.3.9.                         | gisters<br>Seconds Count Register<br>Seconds Alarm Register<br>Minutes Count Register<br>Minutes Alarm Register<br>Hours Count Register<br>Hours Alarm Register<br>Day of the Week Count Register<br>Days Count Register<br>Months Count Register                                                   |     |

| 17.3. Re<br>17.3.1.<br>17.3.2.<br>17.3.3.<br>17.3.4.<br>17.3.5.<br>17.3.6.<br>17.3.7.<br>17.3.8.<br>17.3.9.<br>17.3.10.             | gisters<br>Seconds Count Register<br>Seconds Alarm Register<br>Minutes Count Register<br>Minutes Alarm Register<br>Hours Count Register<br>Hours Alarm Register<br>Day of the Week Count Register<br>Days Count Register<br>Months Count Register<br>Years Count Register                           |     |

| 17.3. Re<br>17.3.1.<br>17.3.2.<br>17.3.3.<br>17.3.4.<br>17.3.5.<br>17.3.6.<br>17.3.7.<br>17.3.8.<br>17.3.9.<br>17.3.10.<br>17.3.11. | gisters<br>Seconds Count Register<br>Seconds Alarm Register<br>Minutes Count Register<br>Minutes Alarm Register<br>Hours Count Register<br>Hours Alarm Register<br>Day of the Week Count Register<br>Days Count Register<br>Months Count Register<br>Years Count Register<br>RTC Control Register A |     |

| 17.4.1.        | Initial Settings                                | 375 |

|----------------|-------------------------------------------------|-----|

| 17.4.2.        | Updating the Time                               | 375 |

| 17.4.3.        | Alarm Function                                  | 375 |

| 17.4.4.        | Re-setting the Clock                            | 375 |

| 17.4.5.        | Reading the Clock                               | 376 |

| 17.4.6.        | Interrupts                                      | 376 |

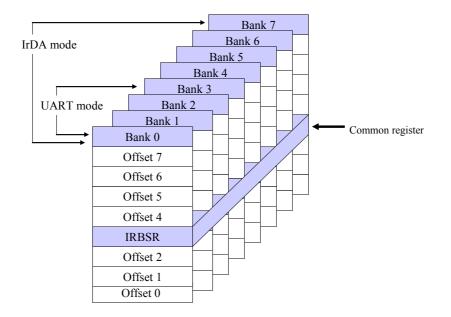

| 18. IrDA Co    | ntroller (IRC)                                  | 377 |

| 18.1. Gene     | ral                                             |     |

| 18.2. Featu    | ıres                                            |     |

| 18.3. Regis    | ster                                            | 379 |

| <i>18.3.1.</i> | Bank 0                                          | 383 |

| 18.3.1.1.      | IrDA transmitter data register                  |     |

| 18.3.1.2.      | IrDA receiver data register                     |     |

| 18.3.1.3.      | IrDA interrupt enable register                  |     |

| 18.3.1.4.      | IrDA extended interrupt enable register         |     |

| 18.3.1.5.      | IrDA interrupt identification register          |     |

| 18.3.1.6.      | IrDA extended interrupt identification register |     |

| 18.3.1.7.      | IrDA FIFO control register                      |     |

| 18.3.1.8.      | IrDA link control register                      |     |

| 18.3.1.9.      | IrDA bank control register                      |     |

| 18.3.1.10.     | IrDA modem control register                     |     |

| 18.3.1.11.     | IrDA mode control register                      |     |

| 18.3.1.12.     | IrDA link status register                       |     |

| 18.3.1.13.     | IrDA extended link status register              |     |

| 18.3.1.14.     | IrDA modem status register                      |     |

| 18.3.1.15.     | IrDA scratch register                           |     |

| 18.3.1.16.     | IrDA extended status/control register           |     |

| <i>18.3.2.</i> | Bank 1                                          | 398 |

| 18.3.2.1.      | Divisor latch register                          |     |

| 18.3.2.1       | 1. IrDA devisor latch lower register            |     |

| 18.3.2.1       | 2. IrDA divisor latch upper register            |     |

| <i>18.3.3.</i> | Bank 2                                          | 400 |

| 18.3.3.1.      | IrDA extended control register 1                |     |

| 18.3.3.2.      | IrDA extended control register 2                |     |

| 18.3.3.3.      | IrDA receive FIFO data level register           | 401 |

| 18.3.3.4.      | IrDA transmit FIFO data level register          | 401 |

| 18.3.4.  | Bank 3                                                         | 402 |

|----------|----------------------------------------------------------------|-----|

| 18.3.4.1 | 1. IrDA link control shadow register                           |     |

| 18.3.4.2 | 2. IrDA FIFO control shadow register                           |     |

| 18.3.5.  | Bank 4                                                         | 403 |

| 18.3.5.1 | 1. Timer initial value register                                |     |

| 18.3.    | 5.1.1. IrDA timer initial value lower register                 |     |

| 18.3.    | 5.1.2. IrDA timer initial value upper register                 |     |

| 18.3.5.2 | 2. IrDA infrared control register 1                            |     |

| 18.3.5.3 | 3. Transmit frame length counter                               |     |

| 18.3.    | 5.3.1. IrDA transmit frame length lower count register         | 405 |

| 18.3.    | 5.3.2. IrDA transmit frame length upper count register         | 405 |

| 18.3.5.4 | 4. Receiver frame maximum-length counter                       |     |

| 18.3.    | 5.4.1. IrDA receiver frame maximum-length lower count register |     |

| 18.3.    | 5.4.2. IrDA receiver frame maximum-length upper count register |     |

| 18.3.6.  | Bank 5                                                         | 407 |

| 18.3.6.1 | 1. IrDA pipeline mode register                                 |     |

| 18.3.6.2 | 2. IrDA infrared control register 2                            |     |

| 18.3.6.3 | 3. IrDA status-FIFO frame status register                      |     |

| 18.3.6.4 | 4. IrDA status FIFO frame-length count register                | 411 |

| 18.3.    | 6.4.1. IrDA status FIFO frame-length lower count register      | 411 |

| 18.3.    | 6.4.2. IrDA status FIFO frame length upper count register      | 412 |

| 18.3.7.  | Bank 6                                                         | 412 |

| 18.3.7.1 | 1. IrDA infrared control register 3                            |     |

| 18.3.7.2 | 2. IrDA MIR pulse setting register                             |     |

| 18.3.7.3 | 3. IrDA SIR pulse width register                               |     |

| 18.3.7.4 | 4. IrDA beginning/preamble length register                     |     |

| 18.3.7.8 | 5. IrDA FIR pulse width register                               |     |

| 18.3.8.  | Bank 7                                                         | 416 |

| 18.3.8.1 | 1. IrDA infrared interface control register 1                  |     |

| 18.3.8.2 | 2. IrDA infrared interface control register 2                  |     |

| 18.3.8.3 | 3. IrDA extended control register 4                            |     |

| 18.4. Oj | perational description                                         | 420 |

| 18.4.1.  | Transmit data FIFO                                             |     |

| 18.4.2.  | Receive data FIFO                                              | 420 |

| 18.4.3.  | Status FIFO                                                    | 421 |

| 18.4.4.  | IrDA Version 1.0 mode                                          | 422 |

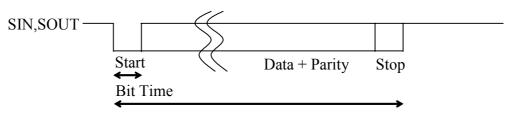

| 18.4.4.1.      | UART mode                                          |     |

|----------------|----------------------------------------------------|-----|

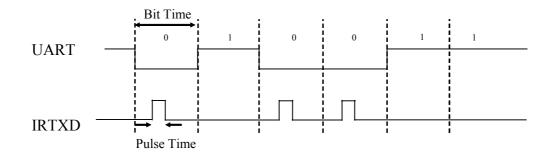

| 18.4.4.2.      | SIR mode                                           | 423 |

| 18.4.5.        | IrDA Version 1.1 mode                              | 424 |

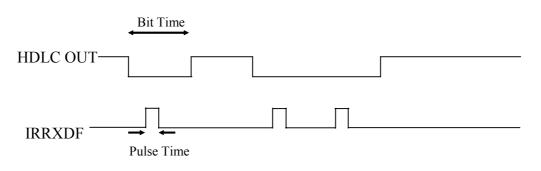

| 18.4.5.1.      | MIR mode                                           | 424 |

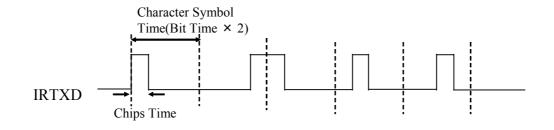

| 18.4.5.2.      | FIR mode                                           |     |

| 18.4.6.        | Interrupt                                          | 426 |

| 18.4.6.1.      | Interrupt priority                                 | 426 |

| 18.4.6         | 1.1. UART mode/SIR mode                            |     |

| 18.4.6         | 1.2. MIR/FIR mode                                  | 427 |

| 18.4.7.        | FIFO timeout                                       | 429 |

| 18.4.7.1.      | UART mode/SIR mode                                 |     |

| 18.4.7.2.      | MIR/FIR mode                                       | 430 |

| 18.4.8.        | FIFO underrun prevent function (Transmit deferral) | 430 |

| 18.4.9.        | Transmit stop function                             | 430 |

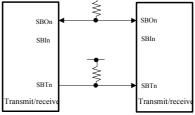

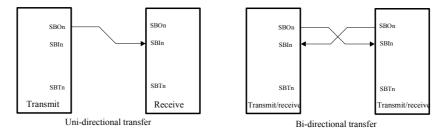

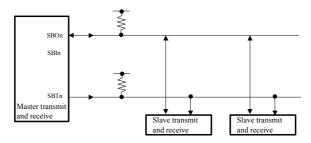

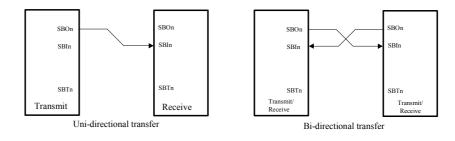

| 18.4.10.       | IR-UNIT interface                                  | 431 |

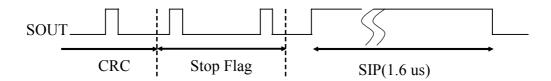

| 18.4.11.       | Interaction pulse (SIP) transmission               | 431 |

| 19. I2C Co     | ntroller (I2C)                                     | 433 |

| 19.1. Ger      | neral                                              | 434 |

| 19.2. Fea      | tures                                              | 434 |

| 19.3. Reg      | isters                                             | 435 |

| 19.3.1.        | I2C Transmit Data Register                         | 436 |

| <i>19.3.2.</i> | I2C Receive Data Register                          | 437 |

| 19.3.3.        | I2C Slave Address Register                         | 439 |

| 19.3.4.        | I2C Clock Register                                 | 440 |

| 19.3.5.        | I2C Bus Reset Register                             | 441 |

| 19.3.6.        | I2C Bus Status Register                            | 442 |

| 19.4. Des      | cription of Operation                              | 443 |

| 19.4.1.        | Master Transmit                                    | 443 |

| 19.4.2.        | Master Receive                                     | 443 |

| 19.4.3.        | Slave Transmit                                     | 444 |

| 19.4.4.        | Slave Receive                                      | 444 |

| 19.4.5.        | Interrupt Causes                                   | 444 |

| 20. I/O Poi    | ts (PIO)                                           | 447 |

|                | ieral                                              |     |

| 20.2. Pin      | Configuration                                      | 448 |

| 20.2.1.        | I/O Port 0                                         | 448 |

| 20.2.2.     | I/O Port 1                                     | 448 |

|-------------|------------------------------------------------|-----|

| 20.2.3.     | I/O Port 2                                     |     |

| 20.2.4.     | I/O Port 3                                     |     |

| 20.2.5.     | I/O Port 4                                     |     |

| 20.2.6.     | I/O Port 5                                     |     |

| 20.3. Reg   | gisters                                        |     |

| 20.3.1.     | Port 0 Mode Register                           |     |

| 20.3.2.     | Port 0 Pin Register                            |     |

| 20.3.3.     | Port 0 Output Register                         |     |

| 20.3.4.     | Port 0 Timer Pin Input/Output Control Register |     |

| 20.3.5.     | Port 1 Mode Register                           |     |

| 20.3.6.     | Port 1 Pin Register                            |     |

| 20.3.7.     | Port 1 Output Register                         |     |

| 20.3.8.     | Port 1 Timer Input/Output Control Register     |     |

| 20.3.9.     | Port 2 Mode Register                           |     |

| 20.3.10.    | Port 2 Pin Register                            |     |

| 20.3.11.    | Port 2 Output Register                         |     |

| 20.3.12.    | Port 3 Mode Register                           |     |

| 20.3.13.    | Port 3 Pin Register                            |     |

| 20.3.14.    | Port 3 Output Register                         |     |

| 20.3.15.    | Port 4 Mode Register                           |     |

| 20.3.16.    | Port 4 Pin Register                            |     |

| 20.3.17.    | Port 4 Output Register                         |     |

| 20.3.18.    | Port 5 Mode Register                           |     |

| 20.3.19.    | Port 5 Pin Register                            |     |

| 20.3.20.    | Port 5 Output Register                         |     |

| 21. Electri | cal Specifications                             |     |

|             | solute maximum ratings                         |     |

|             | erational requirements                         |     |

| -           | characteristics                                |     |

| 21.4. A/I   | O converter characteristics                    |     |

| 21.5. AC    | characteristics                                |     |

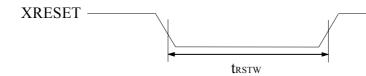

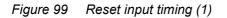

| 21.5.1.     | Reset signal timing                            |     |

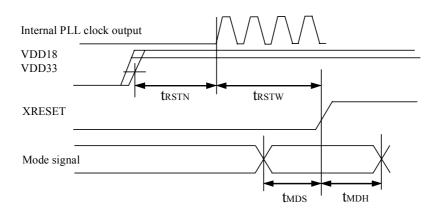

| 21.5.2.     | Clock timing                                   |     |

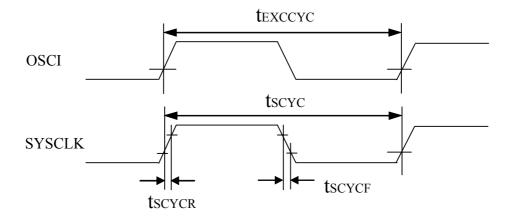

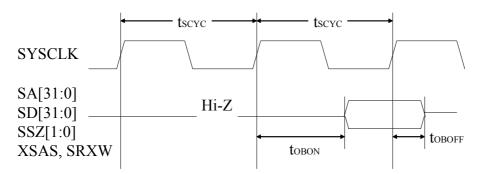

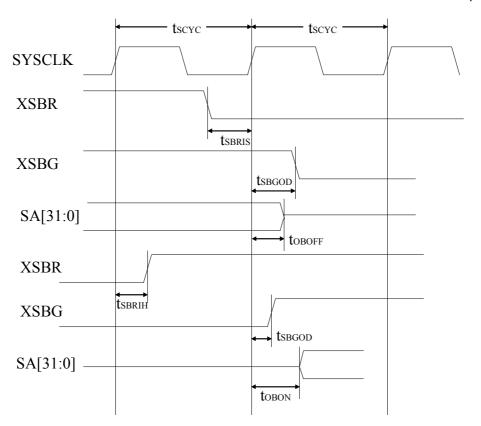

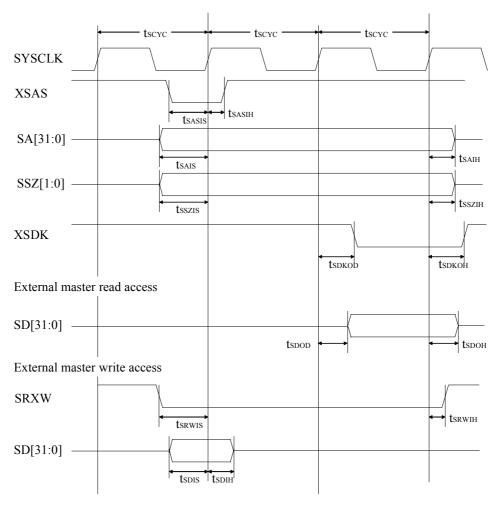

| 21.5.3.     | System bus signal timing                       |     |

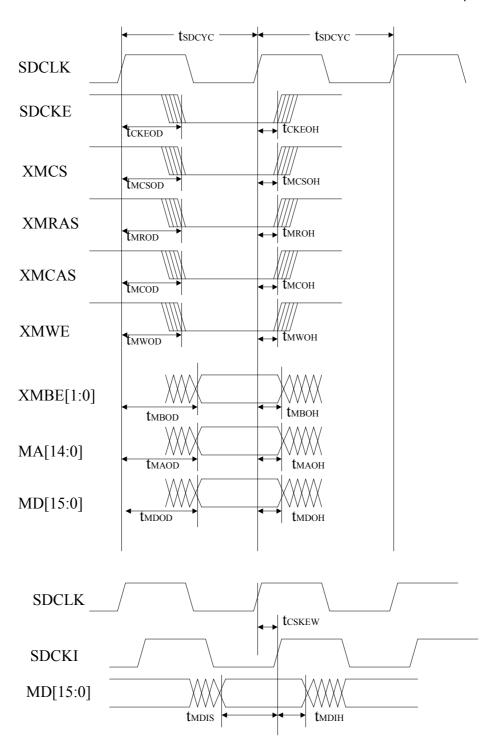

| 21.5.4.     | Memory bus signal timing                       |     |

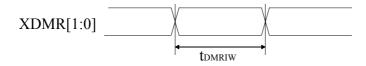

| 21.5.5.            | DMA signal timing                         | 496        |

|--------------------|-------------------------------------------|------------|

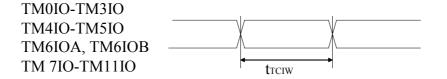

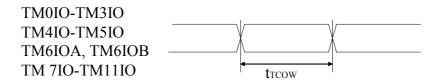

| 21.5.6.            | Timer counter signal timing               |            |

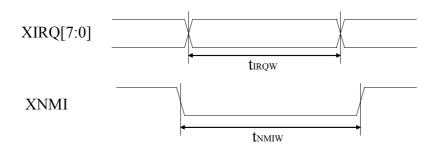

| 21.5.7.            | External interrupt signal timing          |            |

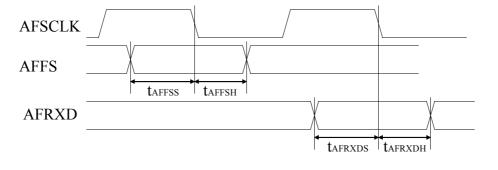

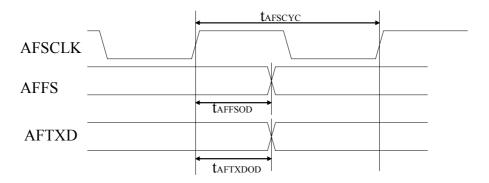

| 21.5.8.            | Analog Front End signal timing            |            |

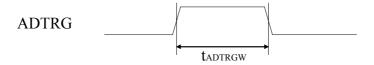

| 21.5.9.            | A/D conversion signal timing              | 500        |

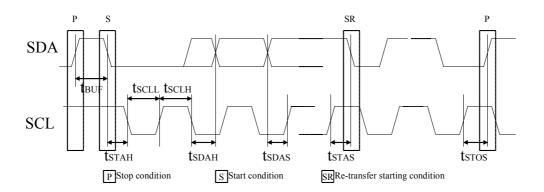

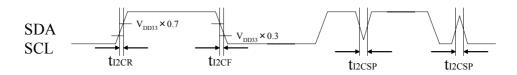

| 21.5.10            | 0. I2C Interface signal timing            | 501        |

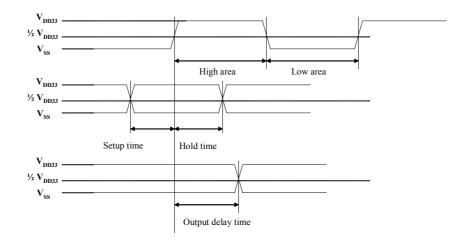

| 21.5.11            | . AC characteristics measuring conditions | 503        |

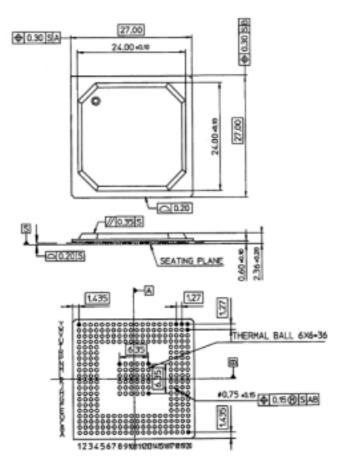

| 22. App            | endix                                     | 505        |

|                    |                                           |            |

| 22.1. l            | Pin list                                  |            |

|                    | Pin list<br>Address Map                   |            |

| 22.2. A            |                                           |            |

| 22.2. A<br>22.3. ] | Address Map                               | 510<br>513 |

### FIGURES

| Figure 1 Block Diagram                                                            | 44  |

|-----------------------------------------------------------------------------------|-----|

| Figure 2 MN103E040HYB pin assignments                                             | 45  |

| Figure 3 MN103E010HRA pin assignments                                             | 50  |

| Figure 4 Block diagram of AM33 microcontroller core                               | 75  |

| Figure 5 Basic register set list                                                  | 78  |

| Figure 6 Extended Operation Register Set                                          | 85  |

| Figure 7 System register set                                                      | 90  |

| Figure 8 Data formats                                                             | 115 |

| Figure 9 Instruction format                                                       | 117 |

| Figure 10 Block diagram                                                           | 154 |

| Figure 11 Address space when using an MMU                                         | 155 |

| Figure 12 Address space when not using MMU                                        | 156 |

| Figure 13 TLB configuration                                                       | 158 |

| Figure 14 TLB Refill referencing the page table                                   | 161 |

| Figure 15 MMU Exception process flow                                              | 164 |

| Figure 16 Instruction cache                                                       | 166 |

| Figure 17 Data cache                                                              | 167 |

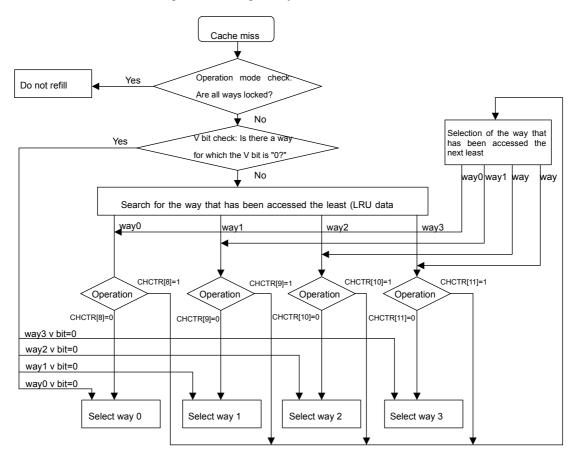

| Figure 18 Flowchart for selecting the refill target way for the instruction cache | 170 |

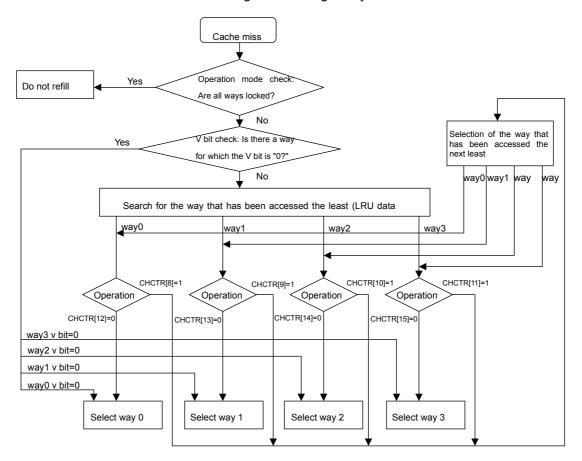

| Figure 19 Flowchart for selecting the refill target way for the data cache        | 172 |

| Figure 20 Floating-point format                                                   | 179 |

| Figure 21 State Transition Diagram                                                | 188 |

| Figure 22 Clock Generator Block Diagram                                           | 193 |

| Figure 23 PLL Block Diagram                                                       | 193 |

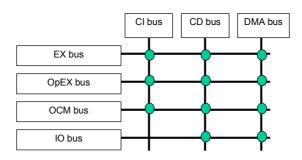

| Figure 24 Internal Bus Configuration                                              |     |

| Figure 25 Connection Relationships between the Master Bus and Slave Bus           | 197 |

| Figure 26 Access data alignment                                                   | 215 |

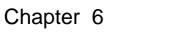

| Figure 27 Chip select                                                             | 217 |

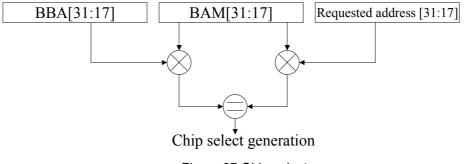

| Figure 28 Timing Chart for 32-bit Bus Fixed Wait Access                           | 218 |

| Figure 29 Timing Chart for 32-bit Bus Fixed Wait Access                           | 218 |

| Figure 30 Timing Chart for a 16-bit Bus Fixed Wait Read Access                    | 219 |

| Figure 31 Timing Chart for a 16-bit Bus Fixed Wait Access                         | 219 |

| Figure 32 Timing Chart for 32-bit Bus Handshake Access                            | 220 |

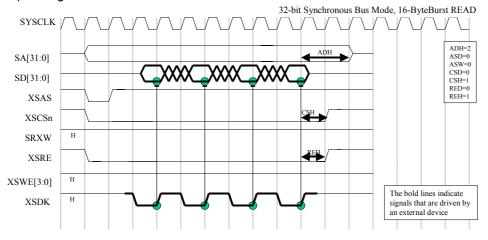

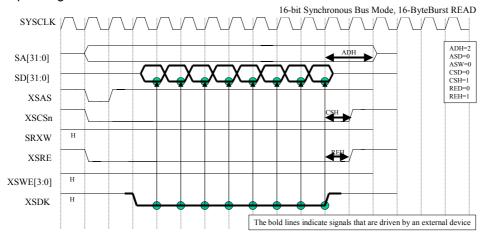

| Figure 33 Timing Chart for 16-byte Burst Read Access                              | 220 |

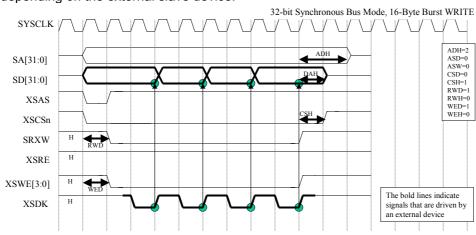

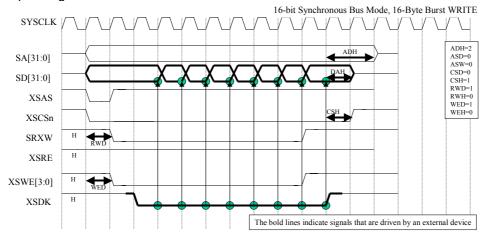

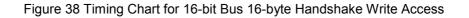

| Figure 34 Timing Chart for 16-byte Burst Write Access                             | 221 |

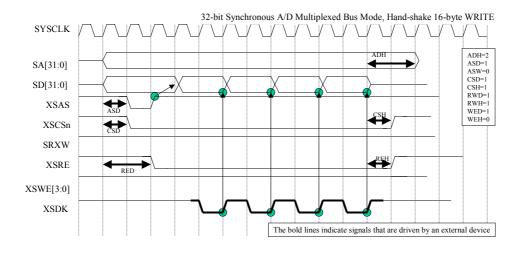

| Figure 35 Timing Chart for a 16-bit Bus Handshake Read Access                     | 221 |

| Figure 36 Timing Chart for a 16-bit Bus Handshake Write Access                               | 222   |

|----------------------------------------------------------------------------------------------|-------|

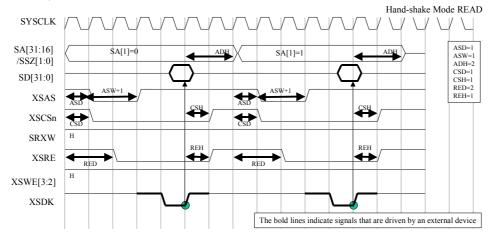

| Figure 37 Timing Chart for 16-bit Bus 16-byte Handshake Read Access                          | 222   |

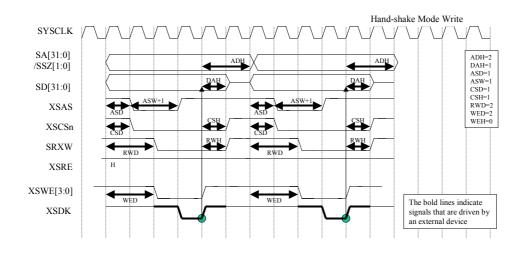

| Figure 38 Timing Chart for 16-bit Bus 16-byte Handshake Write Access                         | 223   |

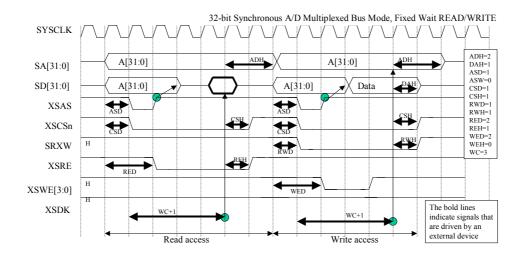

| Figure 39 Timing Chart for 32-bit Bus Address Data Multiplexed/Fixed Wait Access             | 224   |

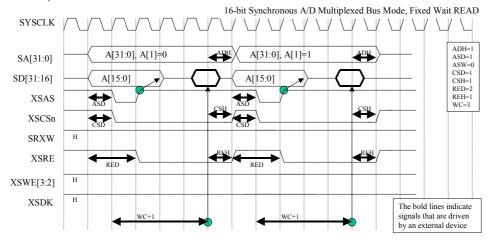

| Figure 40 Timing Chart for 16-bit Address Data Multiplxed/Fixed Wait Read Access             | 225   |

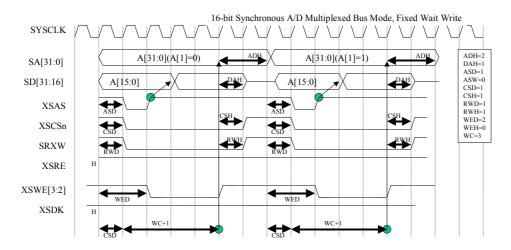

| Figure 41 Timing Chart for 16-bit Bus Address Data Multiplxed/Fixed Wait Write Access        | 225   |

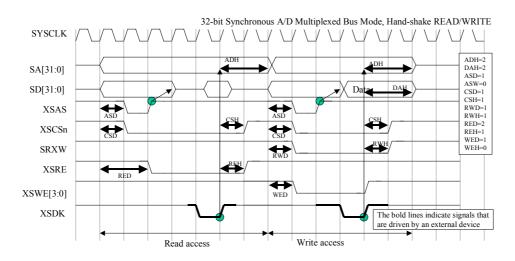

| Figure 42Timing Chart for 32-bit Bus Address Data Multiplexed/Handshake Access               | 226   |

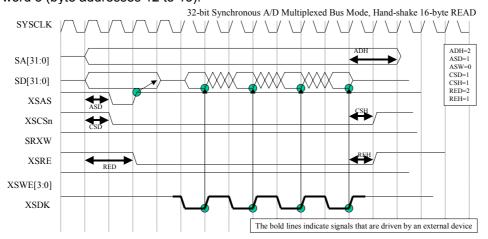

| Figure 43 Timing Chart for 16-byte Handshake Read Access                                     | 226   |

| Figure 44 Timing Chart for 16-byte Handshake Write Access                                    | 227   |

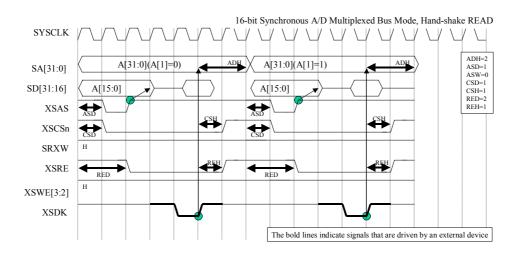

| Figure 45 Timing Chart for 16-bit Bus Handshake Read Access                                  | 228   |

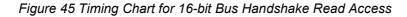

| Figure 46 Timing Chart for 16-bit Bus Handshake Write Access                                 | 228   |

| Figure 47 Timing Chart for 16-bit Bus 16-byte Handshake Read Access                          | 229   |

| Figure 48 Timing Chart for 16-bit Bus 16-byte Handshake Access                               | 229   |

| Figure 49 Timing Chart for Burst ROM 16-byte Read Access                                     |       |

| Figure 50 System bus arbitration                                                             | 230   |

| Figure 51 When a bus access with high priority is performed during using the bus of the exte | ernal |

| master device.                                                                               | 231   |

| Figure 52 Bus arbitration function                                                           | 231   |

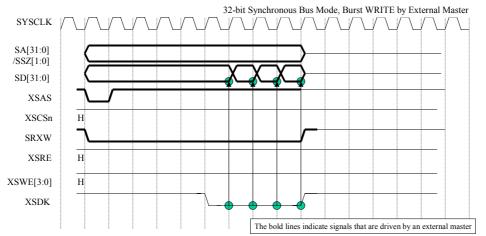

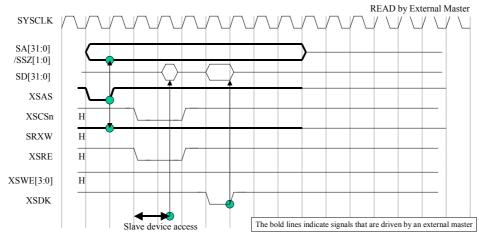

| Figure 53 Timing Chart for External Master Device Access (Read/Write Access)                 | 232   |

| Figure 54 Timing Chart for External Master Device Access (16-byte Burst Read Access)         | 233   |

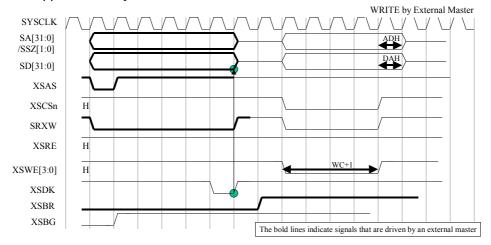

| Figure 55 Timing Chart for External Master Device Access (16-byte Burst Write Access)        | 233   |

| Figure 56 External Master Device Read (Read of a Slave Device on the System Bus)             | 234   |

| Figure 57 External Master Device Write (Write to a Slave Device on the System Bus)           | 234   |