# **ML924**

## T-77-11 .

## **REMOTE CONTROL RECEIVER**

The ML924 is an MOS/LSI integrated circuit for use as a receiver of remote control signals generated by the SL490B transmitter circuit, using PPM (Pulse Position Modulation) encoding technique. The receiver has 5 digital outputs whose response to PPM codes may be programmed by six control lines. It has a handshake interface which provides communication with microprocessors and computers.

### **FEATURES**

- 5 Open Drain Outputs with Enable

- Handshake or Interrupt Microprocessor and Computer Interface Signals

- On-Chip Oscillator

- 6 Control Lines to Programme Output Response

- 3 Selectable Output Modes

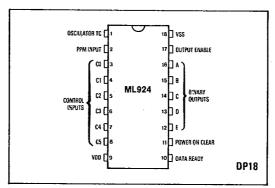

Fig.1 Pin connections (top view)

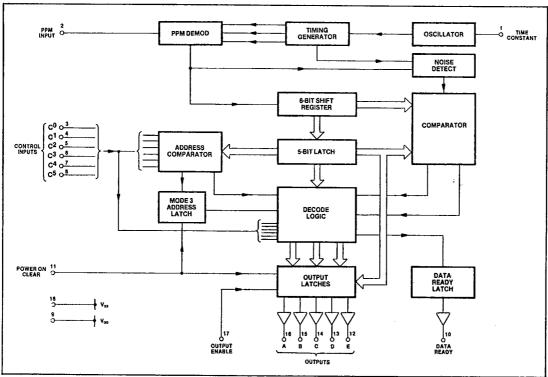

Fig.2 ML924 block diagram

#### **ELECTRICAL CHARACTERISTICS**

Test conditions (unless otherwise stated): VSS = 0V; VDD = -16V; Tamb = +25°C

T-77-11

0

| Characteristic                | Pin      |      | Value |           |       |                                           |

|-------------------------------|----------|------|-------|-----------|-------|-------------------------------------------|

| Characteristic                | PHI      | Min. | Тур.  | Max.      | Units | Conditions                                |

| Supply voltage                | 9        | 12   |       | 18        | ٧     |                                           |

| Supply current                | 9        |      | 6     |           | mA    |                                           |

| Input logic level high ('1')  | 3-8,17   | -1   |       | 0         | ν     |                                           |

| Input logic level low ('0')   |          | VDD  |       | Voo + 3.5 | v     |                                           |

| Output logic level high ('1') | 10,12-16 | -1   |       | ov        |       |                                           |

| Output logic level low ('0')  |          | VDD  |       | Voc + 0.5 | v     | 50k to VDD                                |

| Oscillator frequency          | 1        | 15   | 3k    | 150k      | Hz    | Typical TC: $C = 22nF$ , $R = 100k\Omega$ |

| PPM input level high          | 2        | -1   |       | ov        |       |                                           |

| PPM input level low           |          | Voo  |       | -6V       |       |                                           |

| PPM input pulse width         | 2        | 1    |       | 22Tosc    | μs    | $T = \frac{1}{f_{osc}}$                   |

| Power clear time constant     | 11       | 1    | 400   |           | ms    | 1000                                      |

NOTE

Rosc (Pin 1) is  $56\,\mathrm{k}\Omega$  to  $156\,\mathrm{k}\Omega$ , fosc  $\simeq \frac{1}{0.15\,\mathrm{CR}}$

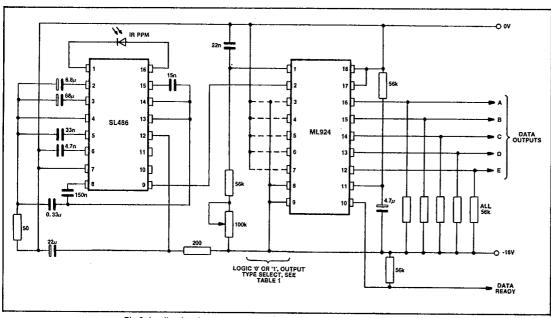

Fig.3 Application for receiving 32 codes, from SL490 transmitter, in mode 1

### **PIN FUNCTIONS**

Positive Logic '1' = Vss, 0V Logic '0' = VDD, -16V Oscillator TC An RC time constant at this pin defines the internal clock frequency. The clock frequency may be varied.

from 15Hz to 150kHz.

2. PPM Input The output of the Front End Amplifier is connected to this pin; the signal must consist of a normal low level with pulses to the high state.

3-8. Control Word Co to Cs Six control bits form the control word which programs the response of the five outputs (see Table 1).

9. Vop -12V to -18V power supply.

Data Ready Open drain output. An output of logic '1' indicates the reception of a valid PPM word. It will remain at logic '1' for the duration of transmission.

Power Clear A capacitor and resistor connected to this pin define the time delay for the Power Clear Circuit.

Outputs E-A Open drain outputs which respond to the PPM input as defined in Table 1.

Output Enable A logic '1' will enable outputs A to E A.

17. Output Enable A logic '1' will enable outputs A to E. A logic '0' will turn all outputs off.

18. Vss OV (Ground).

#### **APPLICATION NOTES**

T-77-11

15E

By setting combinations of logic states on the six control line inputs, Co to C5 (pins 3 to 8), the outputs E to A (pins 12 to 16) on the ML924, can respond to the PPM input word (as shown in Fig.4) in three modes, detailed below:

Each output E to A directly corresponds to bits e to a in the PPM word. The type of output available can be either latched (LA) or momentary (M) according to the combination of Co to Cs used, as given in Table 1. This mode allows direct control of all five bits on one receiver, by the 32 codes from an SL490B transmitter. Fig.3 shows the ML924 used in this mode in conunction with an SL486 infra-red pre-

#### Control Mode 2

Bits a and b, in the PPM input word, address one of up to four (binary 0 to 3) receivers that has been correspondingly designated that number (W1W0), by bits Co and C1 in the control word (Table 1). Bits c and d in the PPM input word, address one of four outputs D to A, on this addressed receiver (Table 1, note 2), via code V1Vo. Output E is not used.

Bits C2 to C5, in the control word, select combinations of output types; either set/reset (S/R) or momentary (M) as shown in Table 1. The addressed output (V1Vo) on the addressed receiver (W1W0) will either be reset by bit e of the PPM input word (logic '0'), or set (pulsed if momentary type output), if bit e is logic '1'.

This mode thus allows the state of up to 16 bits (4 each on 4 receivers), to be individually controlled by the PPM input word, with the 32 codes from an SL490B transmitter. Table 2(a) shows, in detail, the received code interpretation for mode 2.

#### Control Mode 3

The PPM input word can be interpreted as address or data, depending on the logic state of bit e. If bit e is logic '0', bits a to d address one of up to sixteen (binary 0 to 15) receivers that has been correspondingly designated that number (U3U2U1U0) by bits Co to C3 in the control word (Table 1). If bit e is logic '1', then bits a to d correspond to the outputs A to D on the currently addressed receiver.

The output types can either be all latched (LA) or all momentary (M), depending on the logic state of control bits C4 and C5 (Table 1).

Output E of the currently addressed receiver is used as an address acknowledge output (true high), and will go high upon reception of a valid address code. This output will remain high until reception of an invalid address code, or a power-on reset. Thus, only one of the sixteen possible bit E outputs will be high at any one time.

In this manner, up to sixty-four bits (four bits each on sixteen receivers) can be individually controlled by the PPM input word, with the 32 codes from an SL490B transmitter. Fig.5 outlines the application diagram for mode 3, using the maximum possible number of receivers (for one PPM rate). Details of the input PPM code interpretation for mode 3 are given in Table 2(b).

In all modes, taking the output enable input (pin 17) low swithces off all the outputs, except data ready, but the device retains the data internally.

The momentary (M) type of output means that data is available during reception of the PPM input word only, i.e. after a valid word has been detected by the ML924. A valid word is realised when two successive identical PPM input words are detected. The DATA READY output is at logic '1' during the reception of a valid PPM input word. All momentary outputs will be returned to zero when reception of the valid PPM input word ceases (i.e. a successive word is different or absent from the preceding word). DATA READY will also return to the zero state. If the latched (LA) type of output has been chosen, the received data will be latched and retained when reception ceases. Note also that in mode 3 a valid (matched) received address code is also latched. Similarly, for a set/reset (S/R) type of output, data is retained when reception ceases.

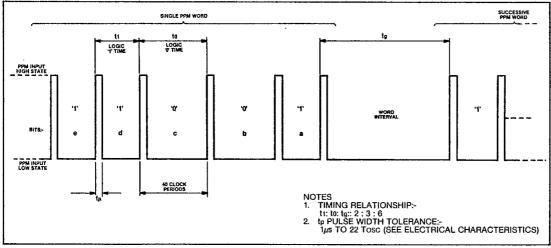

Fig.4 PPM input word format, showing 11001 example

Fig.5 Application for controlling up to 64 bits in mode 3

|               | Co                | ontro                                | l wo                            | rd                                                                               |                                         | Control                                        |                                         | Outp                      | ut resp                 | onse                 |                                         | Interpretation of PPM input words                                                                                                               |                                                                                        |  |  |  |  |

|---------------|-------------------|--------------------------------------|---------------------------------|----------------------------------------------------------------------------------|-----------------------------------------|------------------------------------------------|-----------------------------------------|---------------------------|-------------------------|----------------------|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--|--|--|--|

| C5            | C4                | C <sub>3</sub>                       | C2                              | C <sub>1</sub>                                                                   | Co                                      | mode                                           | E                                       | D                         | С                       | В                    | A                                       | e d c b a                                                                                                                                       | e d c b a                                                                              |  |  |  |  |

| 0 0 0 0 0 0 0 | 0 0 0 0 1 1 1 1 1 | 0<br>0<br>0<br>1<br>1<br>1<br>0<br>0 | 0<br>0<br>1<br>1<br>1<br>0<br>0 | 0<br>0<br>1<br>1<br>1<br>1<br>W <sub>1</sub><br>W <sub>1</sub><br>W <sub>1</sub> | 0<br>1<br>1<br>1<br>1<br>Wo<br>Wo<br>Wo | 1<br>1<br>1<br>1<br>1<br>1<br>2<br>2<br>2<br>2 | LA LA LA LA T T T T T T T T T T T T T T | LA LA M M S/R S/R S/R S/R | LA LA M M S/R S/R S/R M | LA M M M S/R S/R M M | LA<br>M<br>M<br>M<br>M<br>S/R<br>M<br>M | PPM decoded on all outputs directly  O V1 V0 W1 W0  Output Receiver address address Resets an S/R type output. No effect on a momentary output. | Output Receiver address address Sets an S/R type output, or pulses a momentary output. |  |  |  |  |

| 1 1           | 0 1               | U3<br>U3                             |                                 |                                                                                  | Uo<br>Uo                                | 3                                              | AA<br>AA                                | LA<br>M                   | LA<br>M                 | LA<br>M              | LA<br>M                                 | 0 U <sub>3</sub> U <sub>2</sub> U <sub>1</sub> U <sub>0</sub> Receiver address  Designates address mode                                         | PPM data Sent to outputs on addressed receiver Designates data mode                    |  |  |  |  |

Table 1 Interpretation of ML924 control word

- Control mode 1: Direct response to the PPM code.

Control mode 2: W₁W₀ is a 2 bit address for the receiver, designated W₁W₀ by the control word. V₁V₀ selects one of 4 outputs on the addressed receiver.

T-77-11

| V1 | ۷o | Addressed output |

|----|----|------------------|

| 0  | 0  | A (Pin 16)       |

| 0  | -1 | B (Pin 15)       |

| 1  | 0  | C (Pin 14)       |

| 1  | 0  | D (Pin 13)       |

- 3. Control mode 3: U3U2U1U0 is a 4 bit address that selects, by means of 16 PPM codes, the receiver designated U3U2U1U0 by the control word, when bit e of the PPM code is '0'. If bit e is '1', the 4 outputs A to D on the currently addressed receiver are directly controlled by bits a to d.

- Control mode 3: The E output of the receiver acts as an address acknowledge (AA) output. This goes high when a receiver

detects a valid address instruction, and indicates that it will receive subsequent data transmission.

#### **OPERATING NOTES**

#### Receiver Oscillator

The receiver operates on a time scale fixed by an internal oscillator and its external components. The oscillator may be adjusted to any value between 15Hz and 150kHz (allowing different receiver systems to respond to different transmission rates within the same area). If more than one ML924 is being used in a receiver system (control modes 2 or 3) the oscillators can be connected together, still allowing the receiver system timing to be set with one adjustment only. In other words, only one RC arrangement is needed, with pin 1 on all ML924's connected together for the devices constituting the single receiver system.

#### **Setting Up Procedure**

When designing a system using the SL490B/491 transmitters and the ML924 receiver, it is not necessary to adjust the PPM rate on both transmitter and receiver. The usual arrangement is to have a fixed resistor of 33k from pin 16 of the SL490B/491 and to choose the capacitor connected for pin 16 to pin 17 to give the required PPM rate. The value is calculated from the formula to = 1.4CR. Provided fairly close tolerance components are used for C1 and R1, then assembled transmitter units should be interchangeable without adjustment.

The timing components on the ML924 receiver can be selected using the formula

$$f_{IX} = \frac{1}{0.15CR}$$

where  $f_{IX} = \frac{40}{t_0}$

to being the PPM logic 0 time from the transmitter.

The value of R for the receiver should be between 47k and 200k, a typical arrangement being to use a 47k fixed resistor and a 100k pot as shown in Fig.6. The capacitor should be selected from the above formula to give the nominal frequency somewhere near the mid-range setting of the potentiometer.

Final adjustment is made by setting the period on the receiver oscillator time constant pin to 1/40th of the transmitter PPM logic '0' time, using the potentiometer. Connection to the receiver time constant pin should be made using a x10 oscilloscope probe to reduce circuit loading.

#### Maximum Bit Control

In all modes, the maximum possible number of bits that can be controlled by one 32 code transmitter, can be increased by using more than one PPM rate. For example, it is possible to control a maximum of 128 bits in mode 3, by using 16 receivers operating on one PPM rate, and 16 receivers operating on a second PPM rate separated from the first by a fator of at least 2. If using an SL490B transmitter, a transmission rate of n and (nx2) may be incorporated in one device application, thus allowing 128 bits to be controlled by one 32 code transmitter.

T-77-11

| PPM word bits                           | _a1     | b_1                       | а<br>0                          | b<br>1 | a<br>1         | <u>b</u> | _a<br>0 | b_0            | } w₀W₁                          | С   | d       | e |

|-----------------------------------------|---------|---------------------------|---------------------------------|--------|----------------|----------|---------|----------------|---------------------------------|-----|---------|---|

| Receiver address/<br>control word bits  | C₀<br>1 | C <sub>1</sub>            | C <sub>0</sub>                  | C1     | C <sub>0</sub> | C1<br>0  | ပိ ၀    | C <sub>1</sub> |                                 |     |         |   |

| 1                                       | 3       | 1                         | 3                               | 10     | 2              | 9        | 2       | 28             | V <sub>0</sub> V <sub>1</sub> { | _ 1 | 1<br>D  | 1 |

| Sets an S/R type                        | 2       | 7                         | 2                               | 26     | 2              | :5       | 2       | 24             | V <sub>0</sub> V <sub>1</sub> { | _0_ | 1<br>C  | 1 |

| output to 1; pulses on momentary output | 23      |                           | 22                              |        | 21             |          | 20      |                | V <sub>0</sub> V <sub>1</sub> { | _1  | 0<br>B  | 1 |

|                                         | 1       | 9                         | 1                               | 18     | 1              | 17       |         | 16             | V <sub>0</sub> V <sub>1</sub> { | _0  | 0<br>A, | 1 |

| 1                                       | 1       | 15                        |                                 | 14     | 1              | 13       |         | 12             | V <sub>0</sub> V <sub>1</sub> { | _1. | 1<br>D  | 0 |

| Resets an S/R type output to zero; no   |         | 11                        |                                 | 10     |                | 9        |         | 8              | VoV1 {                          | _0  | 1<br>C  | 0 |

| change momen-<br>tary output            |         | 7 6 5 4 V <sub>0</sub> V- | V <sub>0</sub> V <sub>1</sub> { | -1     | 0<br>B         | 0        |         |                |                                 |     |         |   |

| (                                       |         | 3                         |                                 | 2      |                | 1        |         | 0              | V <sub>0</sub> V <sub>1</sub> { | 0_  | O<br>Ā  | 0 |

Decimal equivalent codes (a) mode 2

ML924 output address

| PPM word bits                          | - a -          | b_         | a<br>0           | b<br>1         | a<br>1         | <u>b</u>       | a<br>0  | b              | С  | d  | е |

|----------------------------------------|----------------|------------|------------------|----------------|----------------|----------------|---------|----------------|----|----|---|

| Receiver address/<br>control word bits | C <sub>0</sub> | <u>C</u> 1 | <sub>ပိ</sub> ုဝ | C <sub>1</sub> | C <sub>0</sub> | C <sub>1</sub> | C₀<br>0 | C <sub>1</sub> | C2 | Сз |   |

| 1                                      | 3              | 11         | 30               |                | 29             |                | 28      |                | +  | 1  | 1 |

| Output                                 | 2              | 27         |                  | 26             |                | 25             |         | 24             |    | 1  | 1 |

| data                                   | 2              | 23         |                  | 22             |                | 21             |         | 20             |    | 0  | 1 |

| (                                      | 1              | 19         |                  | 18             |                | 17             |         | 16             |    | 0  | 1 |

| 1                                      | 1              | 15         | 14               |                | 1              | 3              | ۱       | 12             | 1  | 1  | 0 |

| Address                                | 1              | 11         |                  | 10             |                | 9              |         | 8              |    | 1  | 0 |

| data                                   |                | 7          |                  | 6              |                | 5              |         | 4              | 1  | 0  | 0 |

| (                                      |                | 3          | 2                |                | 1              |                | 0       |                | 0  | 0  | 0 |

Decimal equivalent codes (b) mode 3

Table 2 ML924 received PPM code interpretation, for modes 2 and 3

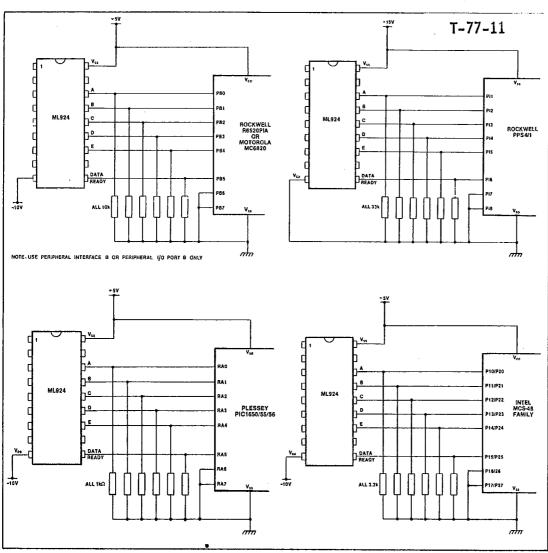

Fig.6 Interface to commonly used microprocessors