# **LAPIS** Semiconductor

#### FEDL9059E-01

# Issue Date: April. 13, 2007

# **ML9059E**

# 132-Channel LCD Driver with Built-in RAM for LCD Dot Matrix Displays

#### **GENERAL DESCRIPTION**

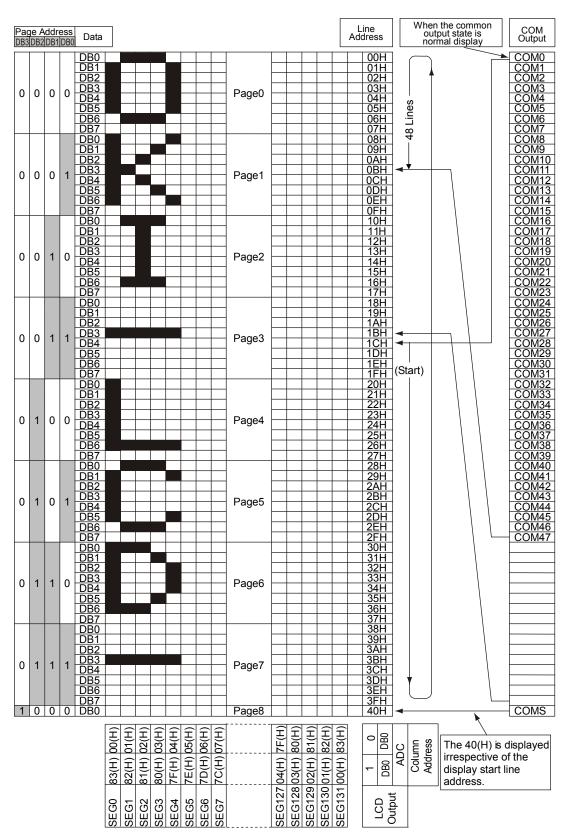

The ML9059E is an LSI for dot matrix graphic LCD devices carrying out bit map display. This LSI can drive a dot matrix graphic LCD display panel under the control of an 8- bit microcomputer (hereinafter described MPU). Since all the functions necessary for driving a bit map type LCD device are incorporated in a single chip, using the ML9059E makes it possible to realize a bit map type dot matrix graphic LCD display system with only a few chips. Since the bit map method in which one bit of display RAM data turns ON or OFF one dot in the display panel, it is possible to carry out displays with a high degree of freedom such as Chinese character displays, etc. With one chip, it is possible to construct a graphic display system with a maximum of  $49 \times 132$  dots. The display can be expanded further using two chips. However, the ML9059E is not used in a multiple chip configuration when a line reversal drive is set.

The ML9059E is made using a CMOS process. Because it has a built-in RAM, low power consumption is one of its features, and is therefore suitable for displays in battery-operated portable equipment.

The ML9059E has 49 common signal outputs and 132 segment signal outputs and one chip can drive a display of up to  $49 \times 132$  dots.

#### **FEATURES**

Direct display of the RAM data using the bit map method Display RAM data "1" ... Dot is displayed Display RAM data "0" ... Dot is not displayed (during forward display)

• Dis play RAM capacity

$65 \times 132 = 8580 \text{ bits}$

• LCD Drive circuits

49 common outputs, 132 segment outputs

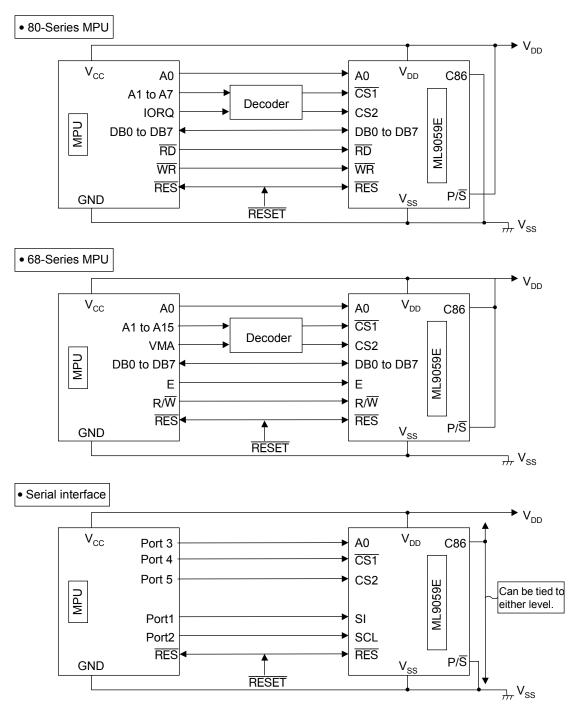

- MPU interface: Can select an 8-bit parallel or serial interface

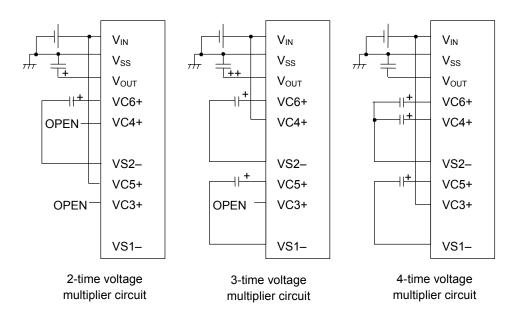

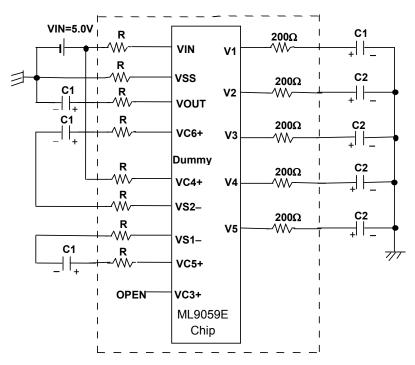

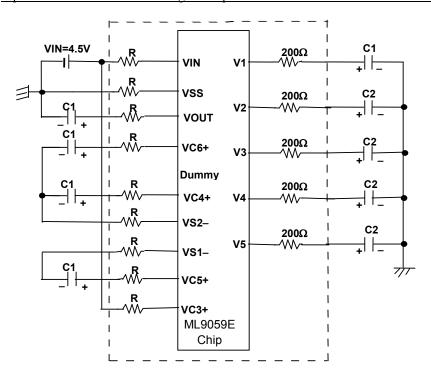

- Built-in voltage multiplier circuit for the LCD drive power supply

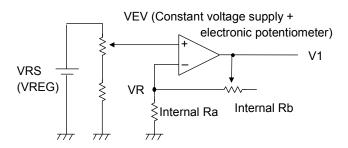

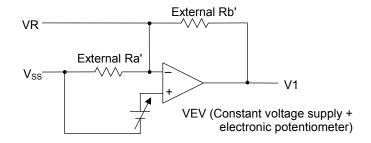

- Built-in LCD drive voltage adjustment circuit

- Built-in LCD drive bias generator circuit

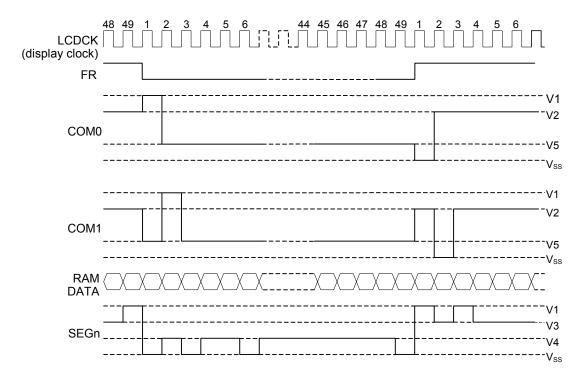

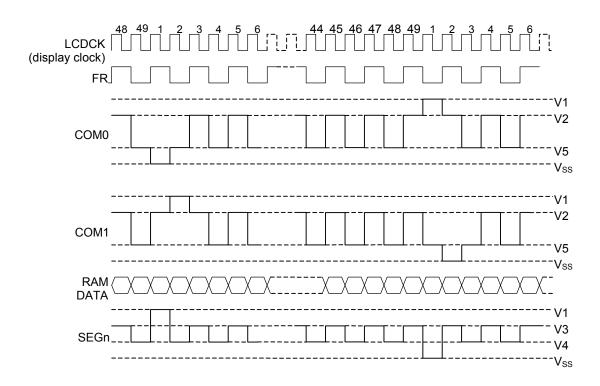

- Can select frame reversal drive or line reversal drive by command

- Built-in oscillator circuit (Internal RC oscillator/external clock input)

- A variety of commands

Read/write of display data, display O N/OFF, forward/reverse display, all dots O N/all dots OFF, set page address, set display start address, etc.

• P ower supply voltage

Logic power supply:  $V_{DD}$ - $V_{SS} = 3.7 \text{ V}$  to 5.5 V

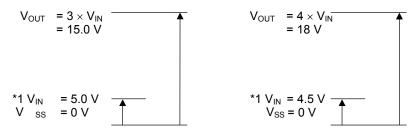

Voltage multiplier reference voltage:  $V_{IN}$ - $V_{SS}$  = 3.7 V to 5.5 V

(2- to 4-time multiplier available)

LCD Drive voltage:  $V_{BI}$ - $V_{SS}$  = 6.0 to 18 V

- Package: Gold bump chip (Bump hardness: Low, DV)

- : Gold bump chip (Bump hardness: High, CV)

- This device is not resistant to radiation and light.

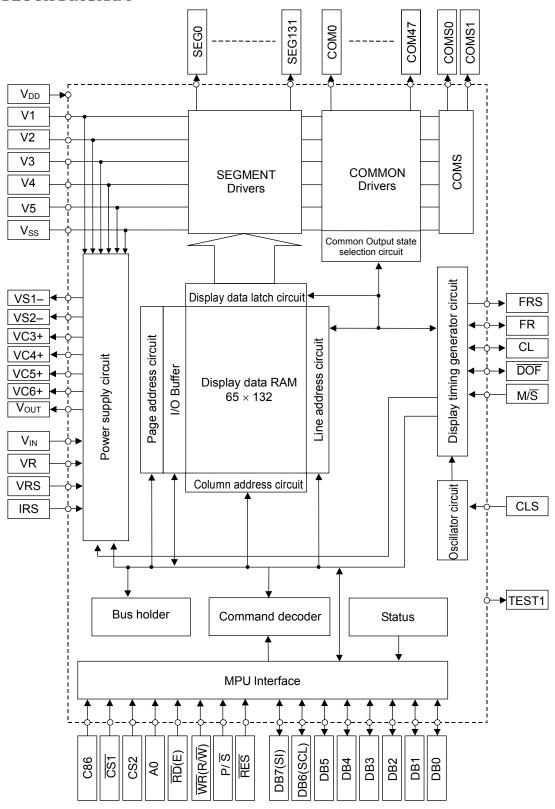

# **BLOCK DIAGRAM**

# **ABSOLUTE MAXIMUM RATINGS**

$V_{SS} = 0 V$

| Parameter                            | Symbol           | Condition             | Rated value                    | Unit | Applicable pins  |

|--------------------------------------|------------------|-----------------------|--------------------------------|------|------------------|

| Power supply voltage                 | $V_{DD}$         | Tj = 25°C             | -0.3 to +6.5                   | ٧    | $V_{DD}$         |

| Bias voltage                         | $V_{BI}$         | Tj = 25°C             | -0.3 to +20                    | ٧    | V1 to V5         |

| Voltage multiplier output voltage    | V <sub>OUT</sub> | Tj = 25°C             | -0.3 to +20                    | >    | V <sub>OUT</sub> |

| Voltage moultiplier reference        |                  | 2-time multiplication | -0.3 to +5.5                   |      |                  |

| Voltage multiplier reference voltage | $V_{IN}$         | 3-time multiplication | -0.3 to +5.5                   | VV   | IN               |

| voltage                              |                  | 4-time multiplication | -0.3 to +5.0                   |      |                  |

| Input voltage                        | Vı               | Tj = 25°C             | -0.3 to V <sub>DD</sub> +0.3 V |      | All inputs       |

| Storage temperature range            | T <sub>STG</sub> | Chip                  | -55 to +125                    | ů    | _                |

Tj:Chip surface temperature

# RECOMMENDED OPERATING CONDITIONS

$V_{SS} = 0 V$

| Parameter                      | Symbol            | Condition                | Rated value | Unit      | Applicable pins |

|--------------------------------|-------------------|--------------------------|-------------|-----------|-----------------|

| Power supply voltage           | V <sub>DD</sub> — |                          | 3.7 to 5.5  | V         | $V_{DD}$        |

| Bias voltage                   | $V_{BI}$          | <del>_</del>             | 6 to 18     | ٧         | V1 to V5        |

| Valta as moultiplier reference |                   | 2-time multiplication    | 3.7 to 5.5  |           |                 |

| Voltage multiplier reference   | V <sub>IN</sub>   | 3-time multiplication    | 3.7 to 5.5  | VV        | IN              |

| voltage                        |                   | 4-time multiplication    | 3.7 to 4.5  |           |                 |

| Voltage multiplier output      |                   | Estemal innet            | C 0 to 10   |           | \ /             |

| voltage                        | V <sub>OUT</sub>  | External input 6.0 to 18 | V           | $V_{OUT}$ |                 |

| Operating temperature range    | $T_{JOP}$         | _                        | -40 to +85  | °C        | _               |

Note 1: The electrical characteristics are influenced by COG trace resistance. This LSI always has to be evaluated before using.

- The voltages  $V_{DD}$ , V1 to V5, and  $V_{OUT}$  are values taking  $V_{SS}$  = 0 V as the reference. The highest bias potential is V1 and the lowest is  $V_{SS}$ . Note 2:

- Note 3:

- Note 4: Always maintain the relationship  $V1 \ge V2 \ge V3 \ge V4 \ge V5 \ge V_{SS}$  among these voltages.

Note 5: When using an external power supply, follow the procedure for power application.

When applying external power to the  $V_{OUT}$  pin only, apply  $V_{OUT}$  after  $V_{DD}$ . When applying external power to the V1 pin only, apply V1 after  $V_{DD}$ . When applying external power to the V1 pin to V5 pin, apply V1 to V5 after  $V_{DD}$ .

Note that the above (Note 4) must be satisfied including transient state at power application.

When using an external power supply, follow the procedure for power removal described Note 6: bel

When external power is in use for the  $V_{OUT}$  pin only, remove  $V_{OUT}$  after  $V_{DD}$ . When external power is in use for the V1 pin only, remove V1 after  $V_{DD}$ .

When external power is in use for the V1 pin to V5 pin, remove V1 to V5 after V<sub>DD</sub>.

Note that the above (Note 4) must be satisfied including transient state at power removal.

# **ELECTRICAL CHARACTERISTICS**

# **DC** Characteristics

$[V_{SS} = 0 \text{ V}, V_{DD} = 3.7 \text{ to } 5.5 \text{ V}, \text{ Tj} = -40 \text{ to } +85^{\circ}\text{C}]$

|                                        |                    |                  |                             | [V <sub>S</sub>            | $_{\rm SS} = 0 \ V$ | $V_{DD} = 3.7 \text{ to}$  | 5.5 V, I | $=-40 \text{ to } +85^{\circ}\text{C}$         |

|----------------------------------------|--------------------|------------------|-----------------------------|----------------------------|---------------------|----------------------------|----------|------------------------------------------------|

| Para                                   | meter              | Symbol           | Condition                   | Min                        | Тур М               | ax U                       | nit      | Applicable pins                                |

| "H" Input vo                           | oltage             | V <sub>IH</sub>  |                             | $0.8 \times V_{\text{DD}}$ |                     | $V_{DD}$                   | V        | *1                                             |

| "L" Input vo                           | ltage              | V <sub>IL</sub>  |                             | 0                          |                     | $0.2 \times V_{\text{DD}}$ | V        | '                                              |

| "H" Input vo                           | oltage             | V <sub>IH</sub>  |                             | $0.8 \times V_{\text{DD}}$ |                     | $V_{DD}$                   |          |                                                |

| "L" Input vo                           | ltage              | V <sub>IL</sub>  |                             | 0                          |                     | $0.2 \times V_{DD}$        | V        | *2                                             |

| Hysteresis                             | Hysteresis width Δ |                  | <sub>DD</sub> = 5.0 V       | 0.85                       | 1.0                 | 1.55                       |          |                                                |

| "H" output                             | voltage            | V <sub>OH</sub>  | $I_{OH} = -0.5 \text{ mA}$  | $0.8 \times V_{\text{DD}}$ |                     |                            | V        | *3                                             |

| "L" output v                           | oltage             | $V_{OL}$         | $I_{OL} = 0.5 \text{ mA}$   | _                          | _                   | $0.2 \times V_{\text{DD}}$ | V        | 3                                              |

| "H" Input cu                           | urrent             | I <sub>IH</sub>  | $V_I = V_{DD}$              | -1.0                       | _                   | +1.0                       | μA *4    | *5                                             |

| "L" Input cu                           | ırrent             | I <sub>IL</sub>  | V <sub>I</sub> = 0 V        | -3.0                       | _                   | +3.0                       | μΑ 4     | 5                                              |

| Input capad                            | citance            | Cı               | Tj=25°C<br>F=10kHz          | _                          | 8 12                |                            | pF *     | 1, *2                                          |

| V1 output voltage temperature gradient |                    | V1TC             | Tj = 25°C<br>V1 = 12 V      | -0.03 -0                   | .05                 | -0.08                      | %/°C     | V1                                             |

| Reference                              | voltage            | $V_{REG}$        | Tj = 25°C                   | 2.925                      | 3.00                | 3.075                      | V        | V <sub>RS</sub>                                |

| V1 output v                            | oltage             | V1               | *6                          | 10.58                      | 10.85               | 11.12                      | V        | V1                                             |

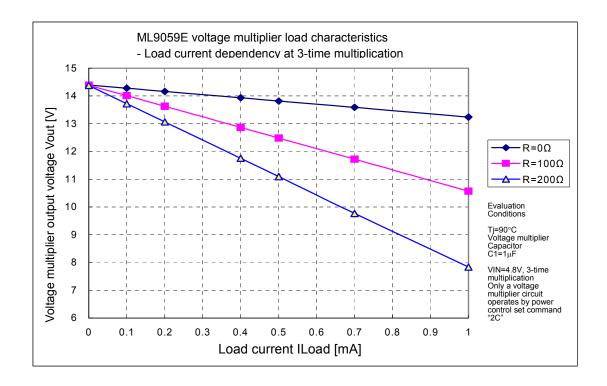

| Voltage mu                             | •                  | V <sub>OUT</sub> | 3-time<br>multiplication *7 | 13.0                       | _                   |                            | V        | V <sub>оит</sub>                               |

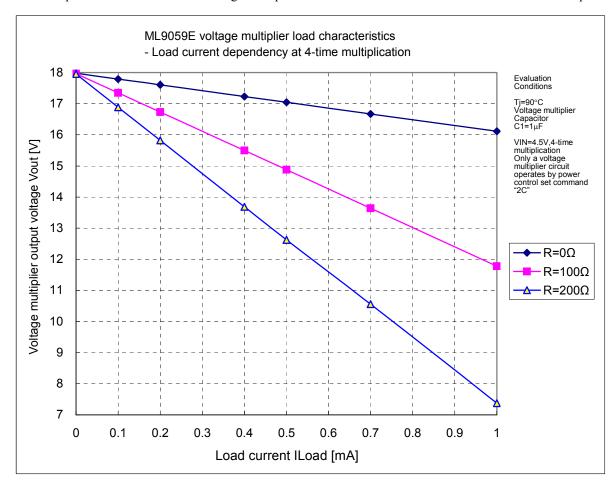

| output volta                           | age                | <b>V</b> 001     | 4-time<br>multiplication *8 | 15.9 —                     |                     | _                          | V        | V <sub>оит</sub>                               |

| V <sub>OUT</sub> - V1 v                | roltage            | Vot1             | *9                          | 0.6                        | _                   | _                          | V        | $V_{OUT}$ , $V1$                               |

| LCD driver ON resistance               |                    | R <sub>ON</sub>  | I <sub>O</sub> = ±50 μA     | ı                          | _                   | 10                         | kΩ       | SEG1 to 131,<br>COMS0,<br>COMS1,<br>COM0 to 47 |

|                                        | Internal           | f                | Ti = 25°C                   | 27                         | 33                  | 39                         | kHz      | *10                                            |

| Oscillator                             | oscillation        | f <sub>OSC</sub> | Tj = 25°C                   | 21 —                       |                     | 47                         | kHz      |                                                |

| frequency                              | External input     | f <sub>EXT</sub> |                             | 14                         | 17                  | 20                         | kHz      | CL*10                                          |

<sup>\*1:</sup> DB0 to DB5, DB7 (SI), FR, DOF Pins

<sup>\*2:</sup> A0,  $\overline{\text{CS1}}$ , CS2, CLS, M/S, C86, P/S, IRS,  $\overline{\text{RD}}$  (E),  $\overline{\text{WR}}$  (R/W),  $\overline{\text{RES}}$ , CL, DB6 (SCL) Pins

<sup>\*3:</sup> DB0 to DB7, FR, FRS, DOF, CL Pins

<sup>\*4:</sup> A0,  $\overline{RD}$  (E),  $\overline{WR}$  (R/ $\overline{W}$ ),  $\overline{CS1}$ , CS2, CLS, M/ $\overline{S}$ , C86, P/ $\overline{S}$ ,  $\overline{RES}$ , IRS Pins

<sup>\*5:</sup> Applicable to the pins DB0 to DB5, DB6 (SCL), DB7 (SI), CL, FR, DOF in the high impedance state.

<sup>\*6:</sup> Tj = 25°C,  $\alpha$  = 31, (1+Rb/Ra) = 4,  $V_{OUT}$  = 13.5 V (External input), LCD drive output = no-load

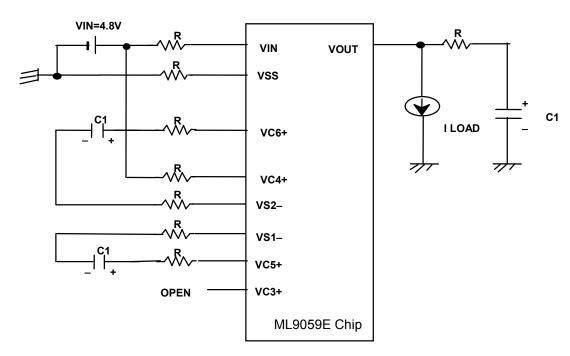

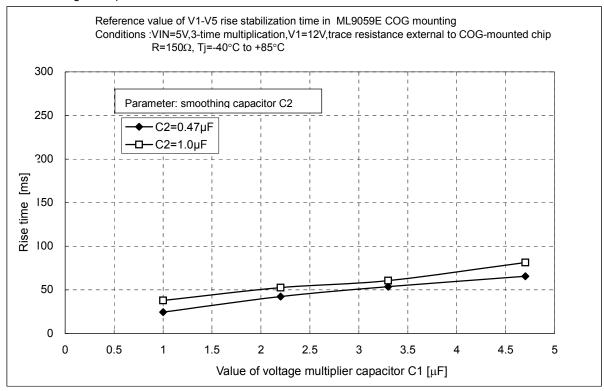

<sup>\*7:</sup> V  $_{IN}$  = 4.8 V, voltage multiplier capacitor C1 = 2.6 to 4.0  $\mu$ F, voltage multiplier output load current I = 500  $\mu$ A. Only a voltage multiplier circuit operates, not activating the voltage adjustment circuit and V/F circuit, by command "2C".

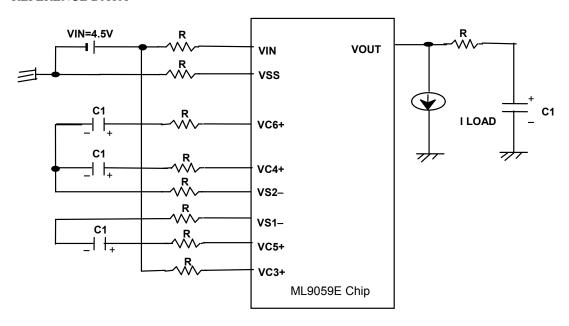

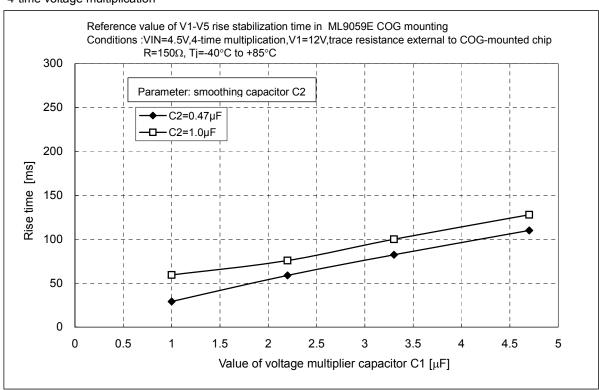

- \*8: V  $_{IN}$  = 4.5 V, voltage multiplier capacitor C1 = 2.6 to 4.0  $\mu$ F, voltage multiplier output load current I = 500  $\mu$ A. Only a voltage multiplier circuit operates, not activating the voltage adjustment circuit and V/F circuit, by command "2C".

- \*9: V1 load current I = 400  $\mu$ A. 8 V is externally input to V<sub>OUT</sub>. The voltage adjustment circuit and V/F circuit operate by command "2B". LCD output = no load

- \*10: See Table 1 for the relationship between the oscillator frequency and the frame frequency.

Table 1. Relationship among the oscillator frequency ( $f_{OSC}$ ), external input frequency ( $f_{EXT}$ ) display clock frequency ( $f_{LCDCK}$ ), and LCD frame frequency ( $f_{FR}$ )

| Parar    | n eter                                   | Display clock frequency (f <sub>LCDCK</sub> ) | LCD frame frequency (f <sub>FR</sub> ) |

|----------|------------------------------------------|-----------------------------------------------|----------------------------------------|

| ML9059E  | When the internal oscillator is used     | fosc/8                                        | $f_{\text{OSC}}/(8 \times 49)$         |

| MILSUSSE | When the internal oscillator is not used | f <sub>EXT</sub> /4 f                         | EXT/(4× 49)                            |

ullet Operating current consumption value (1) D uring display operation, internal power supply OFF (The current flowing through V  $_{DD}$  with V1 to V5 externally applied when an external power supply is used, not including the current for the LCD drive)

|                 | [V              |                                                                             |    |             |                                               | j = 25°C] |    |

|-----------------|-----------------|-----------------------------------------------------------------------------|----|-------------|-----------------------------------------------|-----------|----|

| Dianlay mada    | Symbol          | Symbol Condition -                                                          |    | Rated value |                                               | Unit      |    |

| Display mode    | Symbol          |                                                                             |    | Тур         | Max                                           | Offic     |    |

| All-white I     | DD              | V <sub>DD</sub> = 5 V, V1- V <sub>SS</sub> = 11 V, no load                  | _  | 16          | 45                                            | ^         |    |

|                 |                 | DD                                                                          | DD | DD          | $V_{DD}$ = 3.7 V, V1- $V_{SS}$ = 8 V, no load | 1         | 12 |

| Checker pattern |                 | $V_{DD} = 5 \text{ V}, \text{ V1- V}_{SS} = 11 \text{ V}, \text{ no load}$  | 1  | 16          | 45                                            |           |    |

|                 | I <sub>DD</sub> | $V_{DD} = 3.7 \text{ V}, \text{ V1- V}_{SS} = 8 \text{ V}, \text{ no load}$ | _  | 12          | 35                                            | μΑ        |    |

(2) During display operation, internal power supply ON (Total of currents flowing through  $V_{\text{DD}}$  and  $V_{\text{IN}}$ )

|                                   | 1 7 1             | [V                                                                                                                            |                                                                                                                                                                                                       |            | <sub>SS</sub> = 0 | V, Tj = | 25°C] |

|-----------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------------------|---------|-------|

| Display                           | Symbol (          | onditio                                                                                                                       | n .                                                                                                                                                                                                   | Rated valu |                   | lue     | Unit  |

| mode                              | Symbol            | Ondide                                                                                                                        | [V       SS = 0 V,       Pated value       Min     Typ     M       —     100     1       d     —     110     1       d     —     120     2       pad     —     120     2       ad     —     120     2 | Max        | Offic             |         |       |

| All-white I DD                    |                   | Frame reversal,<br>$V_{DD}$ , $V_{IN}$ = 5 V, 3-time<br>voltage multiplication<br>V1 - $V_{SS}$ = 11 V, no load               |                                                                                                                                                                                                       | _          | 100               | 170     |       |

|                                   | DDIN              | Frame reversal,  V <sub>DD</sub> , V <sub>IN</sub> = 3.7 V, 4-time voltage multiplication V1 - V <sub>SS</sub> = 8 V, no load |                                                                                                                                                                                                       | _          | 110               | 190     | μΑ    |

|                                   |                   | 16-line reversal,<br>$V_{DD,} V_{IN} = 5 \text{ V}$ , 3-time<br>voltage multiplication<br>V1 - $V_{SS}$ = 11 V, no load       | _                                                                                                                                                                                                     |            | 100               | 170     |       |

| Checker pattern I <sub>DDIN</sub> |                   | Frame reversal,<br>$V_{DD,} V_{IN} = 5 \text{ V}$ , 3-time<br>voltage multiplication<br>V1 - $V_{SS}$ = 11 V, no load         |                                                                                                                                                                                                       | _          | 120               | 205     |       |

|                                   | I <sub>DDIN</sub> | Frame reversal,<br>$V_{DD}$ , $V_{IN}$ = 3.7 V, 4-time<br>voltage multiplication<br>V1 - $V_{SS}$ = 8 V, no load              |                                                                                                                                                                                                       | _          | 130               | 220     | μА    |

|                                   | 1<br>V<br>V       | 16-line reversal,<br>$V_{DD,} V_{IN} = 5 \text{ V}$ , 3-time<br>voltage multiplication<br>V1 - $V_{SS}$ = 11 V, no load       | _                                                                                                                                                                                                     |            | 120               | 205     |       |

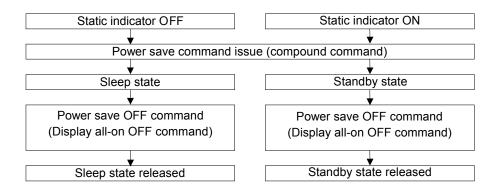

# • Power save mode current consumption

$[V_{SS} = 0 V, Tj = 25^{\circ}C]$

| Parameter Sy | mbal              | Condition                | R   | Rated value |       | Unit |

|--------------|-------------------|--------------------------|-----|-------------|-------|------|

|              | mbol Condition    | Min                      | Тур | Max         | Offic |      |

| Sleep mode   | I <sub>DDS1</sub> | $V_{DD} = 3.7 \text{ V}$ | _   | 0.3         | 5     | ^    |

| Standby mode | I <sub>DDS2</sub> | V <sub>DD</sub> = 3.7 V  | _   | 9           | 15    | μΑ   |

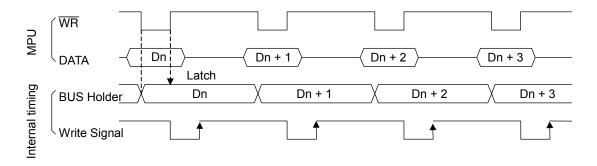

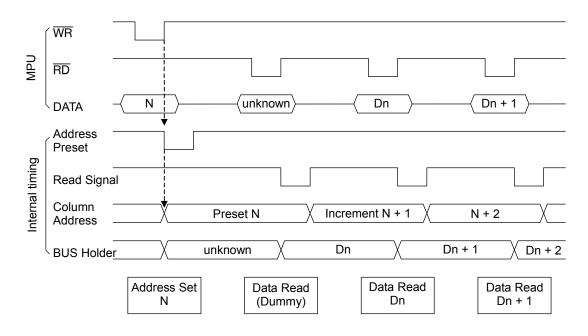

# **Parallel Interface Timing Characteristics**

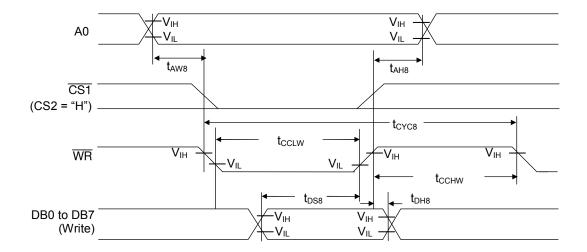

• System bus Write characteristics 1 (80-series MPU)

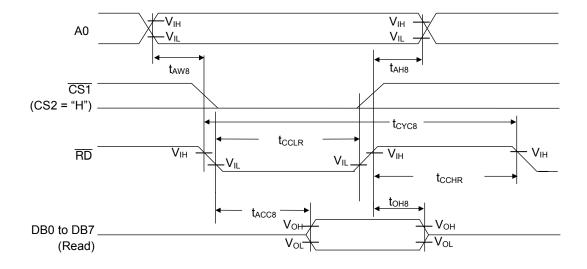

• System bus Read characteristics 1 (80-series MPU)

$[V_{DD} = 4.5 \text{ to } 5.5 \text{ V}, \text{ Tj} = -40 \text{ to } +85^{\circ}\text{C}]$

|                              |                     | 0 175       | Rated                                                                                                                                                                                                                         | Rated value |      |

|------------------------------|---------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------|

| Parameter Sy                 | mbol                | Condition   | Min         Max           5         —           5         —           166         —           30         —           55         —           55         —           30         —           10         —           70         — | Max         | Unit |

| Address hold time            | t <sub>AH8</sub>    |             | 5                                                                                                                                                                                                                             | _           |      |

| Address setup time           | t <sub>AW8</sub>    |             | 5                                                                                                                                                                                                                             | _           |      |

| System cycle time            | t <sub>CYC8</sub>   |             | 166                                                                                                                                                                                                                           | _           |      |

| Control L pulse width (WR) t | CCLW                |             | 30                                                                                                                                                                                                                            | _           |      |

| Control L pulse width (RD)   | t <sub>CCLR</sub>   |             | 70                                                                                                                                                                                                                            | _           |      |

| Control H pulse width (WR)   | t <sub>CCHW</sub>   |             | 55                                                                                                                                                                                                                            | _           | ns   |

| Control H pulse width (RD) t | CCHR                |             | 55                                                                                                                                                                                                                            | 1           |      |

| Data setup time              | t <sub>DS8</sub>    |             | 30                                                                                                                                                                                                                            | 1           |      |

| Data hold time               | t <sub>DH8</sub>    |             | 10                                                                                                                                                                                                                            | _           |      |

| RD Access time               | t <sub>ACC8</sub> — | CL = 100 pF |                                                                                                                                                                                                                               | 70          |      |

| Output disable time          | t <sub>OH8</sub>    | CL = 100 pF | 5 50                                                                                                                                                                                                                          |             |      |

$[V_{DD} = 3.7 \text{ to } 4.5 \text{ V}, \text{ Tj} = -40 \text{ to } +85^{\circ}\text{C}]$

|                              |                     | £           |                                  |     |       |

|------------------------------|---------------------|-------------|----------------------------------|-----|-------|

| Parameter Sy                 | mbol                | Condition   | Rated value                      |     | Unit  |

| Farameter Sy                 | IIIDOI              | Condition   | Min 5 5 5 300 60 120 60 60 40 15 | Max | Offic |

| Address hold time            | t <sub>AH8</sub>    |             | 5                                | _   |       |

| Address setup time           | t <sub>AW8</sub>    |             | 5                                | _   |       |

| System cycle time            | t <sub>CYC8</sub>   |             | 300                              | 1   |       |

| Control L pulse width (WR) t | CCLW                |             | 60                               | 1   |       |

| Control L pulse width (RD)   | t <sub>CCLR</sub>   |             | 120                              | 1   |       |

| Control H pulse width (WR)   | t <sub>CCHW</sub>   |             | 60                               | _   | ns    |

| Control H pulse width (RD) t | CCHR                |             | 60                               | _   |       |

| Data setup time              | t <sub>DS8</sub>    |             | 40                               | _   |       |

| Data hold time               | t <sub>DH8</sub>    |             | 15                               | _   |       |

| RD Access time               | t <sub>ACC8</sub> — | CL = 100 pF |                                  | 140 |       |

| Output disable time          | t <sub>OH8</sub>    | CL = 100 pF | 10 10                            | 0   |       |

- Note 1: The input signal rise and fall times are specified as 15ns or less. When using the system cycle time for fast speed, the specified values are  $(tr + tf) \le (t_{CYC8} - tf)$  $t_{\text{CCLW}} - t_{\text{CCHW}}$ ) or  $(\text{tr} + \text{tf}) \leq (t_{\text{CYC8}} - t_{\text{CCLR}} - t_{\text{CCHR}})$ . All timings are specified taking the levels of 20% and 80% of  $V_{\text{DD}}$  as the reference.

- The values of  $t_{CCLW}$  and  $t_{CCLR}$  are specified during the overlapping period of  $\overline{CS1}$  at "L" (CS2 = Note 3: "H") and the "L" levels of WR and RD, respectively.

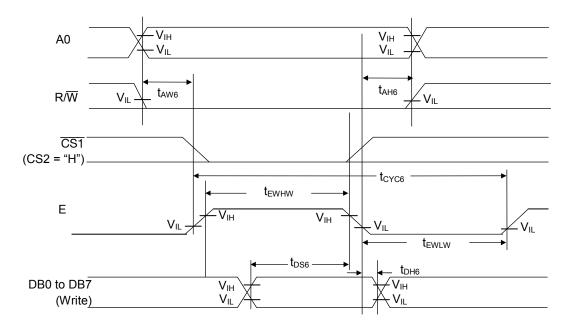

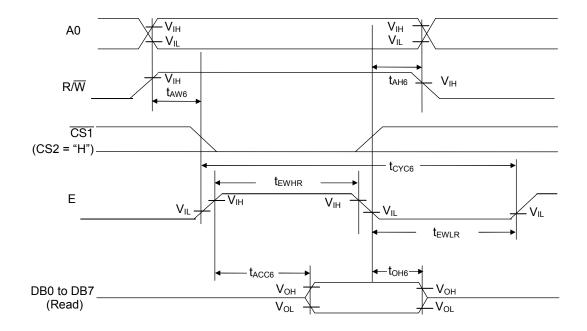

• System bus Write characteristics 2 (68-series MPU)

• System bus Read characteristics 2 (68-series MPU)

$[V_{DD} = 4.5 \text{ to } 5.5 \text{ V}, \text{ Tj} = -40 \text{ to } +85^{\circ}\text{C}]$

| Darameter Sv         |         | mbol              | Condition   | Rated | Rated value |      |

|----------------------|---------|-------------------|-------------|-------|-------------|------|

| Parameter Sy         |         | IIIDOI            | Condition   |       | Max         | Unit |

| Address hold time    |         | t <sub>AH6</sub>  |             | 5     | _           |      |

| Address setup time   |         | t <sub>AW6</sub>  |             | 5     | _           |      |

| System cycle time    |         | t <sub>CYC6</sub> |             | 166   | _           |      |

| Data setup time      |         | t <sub>DS6</sub>  |             | 30    | _           |      |

| Data hold time       |         | t <sub>DH6</sub>  |             | 10    | _           |      |

| Access time          |         | t <sub>ACC6</sub> | CL = 100 pF | _     | 70          | ns   |

| Output disable time  |         | t <sub>OH6</sub>  |             | 10    | 50          |      |

| Enable H pulse width | Read    | t <sub>EWHR</sub> |             | 70    | _           |      |

| Enable H pulse width | Write   | t <sub>EWHW</sub> |             | 30    | _           |      |

| Enable I mules width | Read    | t <sub>EWLR</sub> |             | 60    | _           |      |

| Enable L pulse width | Write t | EWLW              |             | 60    | _           |      |

$[V_{DD} = 3.7 \text{ to } 4.5 \text{ V}, \text{ Tj} = -40 \text{ to } +85^{\circ}\text{C}]$

| Davamatar Cu         |         | male al           | Condition   | Rated  | value | Unit |  |

|----------------------|---------|-------------------|-------------|--------|-------|------|--|

| Parameter Sy         |         | mbol              | Condition   | Min    | Max   | Unit |  |

| Address hold time    |         | t <sub>AH6</sub>  |             | 5      |       |      |  |

| Address setup time   |         | t <sub>AW6</sub>  |             | 5      | _     |      |  |

| System cycle time    |         | t <sub>CYC6</sub> | 300         |        | _     |      |  |

| Data setup time      |         | t <sub>DS6</sub>  | 40          |        | _     |      |  |

| Data hold time       |         | t <sub>DH6</sub>  |             | 15     | _     |      |  |

| Access time          |         | t <sub>ACC6</sub> | CL = 100 pF | _      | 140   | ns   |  |

| Output disable time  |         | t <sub>OH6</sub>  | OL = 100 pr | 10 100 |       |      |  |

| Enable Haulee width  | Read t  | EWHR              | 120         |        | _     |      |  |

| Enable H pulse width | Write t | EWHW              |             | 60     | _     |      |  |

| English mules width  | Read t  | EWLR              | 60          |        | _     |      |  |

| Enable L pulse width | Write t | EWLW              |             | 60     | _     |      |  |

Note 1: The input signal rise and fall times are specified as 15ns or less. When using the system cycle time for fast speed, the specified values are  $(tr + tf) \le (t_{CYC6} - t_{CYC6})$

$t_{\text{EWLW}} - t_{\text{EWHW}}) \text{ or } (\text{tr + tf}) \leq (t_{\text{CYC6}} - t_{\text{EWLR}} - t_{\text{EWHR}}).$  Note 2: All timings are specified taking the levels of 20% and 80% of  $V_{\text{DD}}$  as the reference.

The values of  $t_{EWLW}$  and  $t_{EWLR}$  are specified during the overlapping period of  $\overline{CS1}$  at "L" (CS2 = Note 3: "H") and the "H" level of E.

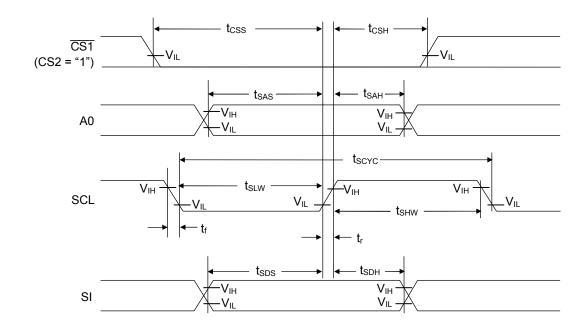

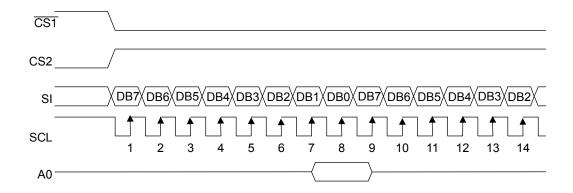

# **Serial Interface Timing Characteristics**

# • Serial interface

$[V_{DD} = 4.5 \text{ to } 5.5 \text{ V}, \text{ Tj} = -40 \text{ to } +85^{\circ}\text{C}]$

|                     |                  | . 55      | , , |             |      |

|---------------------|------------------|-----------|-----|-------------|------|

| Dorameter Sv        | mbol             | Condition |     | Rated value |      |

| Parameter Sy        | IIIDOI           | Condition | Min |             | Unit |

| Serial clock period | tscyc            |           | 200 | _           |      |

| SCL "H" Pulse width | t <sub>SHW</sub> |           | 75  | _           |      |

| SCL "L" Pulse width | t <sub>SLW</sub> |           | 75  | _           |      |

| Address setup time  | t <sub>sas</sub> |           | 50  | _           |      |

| Address hold time   | t <sub>SAH</sub> |           | 100 | _           | ns   |

| Data setup time     | t <sub>SDS</sub> |           | 50  | _           |      |

| Data hold time      | t <sub>sDH</sub> |           | 50  | _           |      |

| CS setup time       | t <sub>CSS</sub> |           | 100 | _           |      |

| CS hold time        | t <sub>csн</sub> |           | 100 | _           |      |

|                     |                  |           |     |             |      |

Note 1: The input signal rise and fall times are specified as 15ns or less. Note 2: All timings are specified taking the levels of 20% and 80% of  $V_{DD}$  as the reference.

$[V_{DD} = 3.7 \text{ to } 4.5 \text{ V}, \text{ Tj} = -40 \text{ to } +85^{\circ}\text{C}]$

| Doromotor Cv        | mala al          | Condition | Rated | value | Unit |  |

|---------------------|------------------|-----------|-------|-------|------|--|

| Parameter Sy        | mbol             | Condition | Min   | Max   | Oill |  |

| Serial clock period | tscyc            |           | 250   | _     |      |  |

| SCL "H" Pulse width | t <sub>SHW</sub> |           | 100   | _     |      |  |

| SCL "L" Pulse width | t <sub>SLW</sub> |           | 100   | _     |      |  |

| Address setup time  | t <sub>SAS</sub> |           | 150   | _     |      |  |

| Address hold time   | t <sub>SAH</sub> |           | 150   | _     | ns   |  |

| Data setup time     | t <sub>SDS</sub> |           | 100   | _     |      |  |

| Data hold time      | t <sub>SDH</sub> |           | 100   | _     |      |  |

| CS setup time       | t <sub>CSS</sub> |           | 150   | _     |      |  |

| CS hold time        | t <sub>сsн</sub> |           | 150   |       |      |  |

Note 1: The input signal rise and fall times are specified as 15ns or less.

Note 2: All timings are specified taking the levels of 20% and 80% of  $V_{DD}$  as the reference.

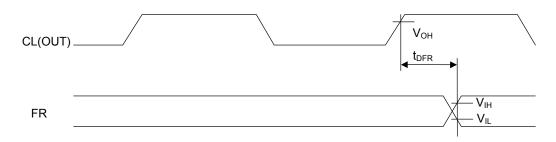

# • Display control output timing

$[V_{DD} = 4.5 \text{ to } 5.5 \text{ V}, \text{ Tj} = -40 \text{ to } +85^{\circ}\text{C}]$

|               |                  |            | [ · DD · · |      | , ., | ,     |

|---------------|------------------|------------|------------|------|------|-------|

| Parameter Sy  | mbol             | Condition  | F          | Unit |      |       |

|               | IIIDOI           | Condition  | Min        | Тур  | Max  | Offic |

| FR Delay time | t <sub>DFR</sub> | CL = 50 pF | _          | 10   | 40   | ns    |

$[V_{DD} = 3.7 \text{ to } 4.5 \text{ V}, \text{ Tj} = -40 \text{ to } +85^{\circ}\text{C}]$

| Parameter Sy  | mhal             | Condition  | F   | Linit |     |      |

|---------------|------------------|------------|-----|-------|-----|------|

|               | mbol             | Condition  | Min | Тур   | Max | Unit |

| FR Delay time | t <sub>DFR</sub> | CL = 50 pF | _   | 20    | 80  | ns   |

Note 1: All timings are specified taking the levels of 20% and 80% of  $V_{DD}$  as the reference.

Note 2: Valid only when the device operates in master mode.

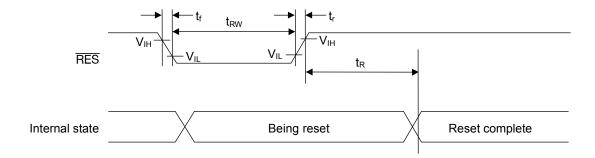

# • Reset input timing

$[V_{DD} = 4.5 \text{ to } 5.5 \text{ V}, \text{ Tj} = -40 \text{ to } +85^{\circ}\text{C}]$

| Parameter Sy          | mbol            | Condition | R     | Unit |     |       |

|-----------------------|-----------------|-----------|-------|------|-----|-------|

| Farameter Sy          | IIIDOI          | Condition | Min   | Тур  | Max | Offic |

| Reset time            | t <sub>R</sub>  |           | _     | _    | 0.5 | 110   |

| Reset "L" pulse width | t <sub>RW</sub> |           | 0.5 — |      | _   | μs    |

$[V_{DD} = 3.7 \text{ to } 4.5 \text{ V}, \text{ Tj} = -40 \text{ to } +85^{\circ}\text{C}]$

| Doromotor Sv          | mbol            | Condition | R   | Unit |     |       |  |

|-----------------------|-----------------|-----------|-----|------|-----|-------|--|

| Parameter Sy          | IIIDOI          | Condition | Min | Тур  | Max | UTIIL |  |

| Reset time            | t <sub>R</sub>  |           | _   | _    | 1   |       |  |

| Reset "L" pulse width | t <sub>RW</sub> |           | 1 — |      | _   | μs    |  |

Note 1: The input signal rise and fall times  $(t_r,\,t_f)$  are specified as 15 ns or less. Note 2: All timings are specified taking the levels of 20% and 80% of  $V_{DD}$  as the reference.

# PIN DESCRIPTION

| Function F       | Pin name      | Number of pins | I/O D | escr iption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|------------------|---------------|----------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                  | DB0 to<br>DB7 | 8 I/O          |       | These are 8-bit bi-directional data bus pins that can be connected to 8-bit standard MPU data bus pins. When a serial interface is selected $(P/\overline{S} = \text{`L''})$ :  DB7: Serial data input pin (SI)  DB6: Serial clock input pin (SCL)  In this case, DB0 to DB5 will be in the high impedance state. DB0 to DB7 will all be in the high impedance state when the chip select is in the inactive state.  Fix the DB0 to DB5 pins at "H" or "L" level.                                                               |  |  |  |  |

|                  | A0 1          |                | I     | Normally, the lowest bit of the MPU address bus is connected and used for distinguishing between data and commands.  A0 = "H": Indicates that DB0 to DB7 is display data.  A1 = "L": Indicates that DB0 to DB7 is control data.                                                                                                                                                                                                                                                                                                 |  |  |  |  |

|                  | RES           | 11             |       | Initial setting is made by making $\overline{RES}$ = "L". The reset operation is made during the active level of the $\overline{RES}$ signal.                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

|                  | CS1<br>CS2    | 21             |       | These are t he c hip select si gnals. T he C hip Select of the LSI becomes active when $\overline{\text{CS1}}$ is "L" and also CS2 is "H" and allows the input/output of data or commands.                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| MPU<br>Interface | RD<br>(E)     | 11             |       | The active level of this signal is "L" when connected to an 80-series MPU. This pin is connected to the $\overline{\text{RD}}$ signal of the 80-series MPU, and the data bus of the ML9059E goes into the output state when this signal is "L". The active level of this signal is "H" when connected to a 68-series MPU. This pin will be the Enable and clock input pin when connected to a 68-series MPU. When a serial interface is selected (P/ $\overline{\text{S}}$ = "L"), fix this pin at "H" or "L" level.            |  |  |  |  |

|                  | WR<br>(R/W)   | 11             |       | The active level of this signal is "L" when connected to an 80-series MPU. This pin is connected to the $\overline{WR}$ signal of the 80-series MPU. The data on the data bus is latched into the ML9059E at the rising edge of the $\overline{WR}$ signal. When connected to a 68-series MPU, this pin becomes the input pin for the Read/Write control signal. R/ $\overline{W}$ = "H": Read, R/ $\overline{W}$ = "L": Write When a serial interface is selected (P/ $\overline{S}$ = "L"), fix this pin at "H" or "L" level. |  |  |  |  |

|                  | C86 1         |                | I     | This is the pin for selecting the MPU interface type.  C86 = "H": 68-Series MPU interface.  C86 = "L": 80-Series MPU interface.                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| Function Pi                               | n name            | Number of pins | I/O D | Descr iption                                                                                                                                                                                                                                                                                                                                                        |                                                                                  |                                        |                           |        |        |                      |              |

|-------------------------------------------|-------------------|----------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|----------------------------------------|---------------------------|--------|--------|----------------------|--------------|

| MPU                                       |                   |                |       | P/S = 1                                                                                                                                                                                                                                                                                                                                                             | "H": P<br>"L": S<br>ns of                                                        | arallel da<br>erial data<br>the LSI ha | •                         |        |        |                      | ·            |

| Interface                                 | P/S 1             |                | I     | P/S                                                                                                                                                                                                                                                                                                                                                                 | Da                                                                               | ta/commar                              | id D                      | ata    | Read   | /Write               | Serial clock |

|                                           |                   |                |       | "H"                                                                                                                                                                                                                                                                                                                                                                 |                                                                                  | A0                                     | DB0                       | to DB7 | RD,    | WR                   | _            |

|                                           |                   |                |       | "L"                                                                                                                                                                                                                                                                                                                                                                 |                                                                                  | A0                                     | SI                        | (D7)   | _      | _                    | SCL(DB6)     |

|                                           |                   |                |       |                                                                                                                                                                                                                                                                                                                                                                     | During serial data input, it is not possible to read the display data in the RAM |                                        |                           |        |        |                      |              |

| Oscillator<br>circuit                     | CLS 1             |                | _     | This is the pin for selecting whether to enable or disable the internal oscillator circuit for the display clock.  CLS = "H": The internal oscillator circuit is enabled.  CLS = "L": The internal oscillator circuit is disabled (External input).  When CLS = "L", the display clock is input at the pin CL.                                                      |                                                                                  |                                        |                           |        |        |                      |              |

| Display<br>timing<br>generator<br>circuit | M/ <del>S</del> 1 |                | ı     | This is the pin for selecting whether master operation or so operation is made towards the ML9059E. During slave oper the synchronization with the LCD display system is a chieve inputting the timing signals necessary for LCD display.  M/S = "H": Master operation  M/S = "L": Slave operation  The functions of the different circuits and pins will be as for |                                                                                  |                                        |                           |        |        | peration,<br>eved by |              |

|                                           |                   |                |       |                                                                                                                                                                                                                                                                                                                                                                     | "H"                                                                              | circuit<br>Enabled                     | supply circuit<br>Enabled | Output | Output | Output               | Output       |

|                                           |                   |                |       | "H"                                                                                                                                                                                                                                                                                                                                                                 | "L"                                                                              | Disabled                               | Enabled                   | Input  | Output | Output               | Output       |

|                                           |                   |                |       | 44 T                                                                                                                                                                                                                                                                                                                                                                | "H"                                                                              | Disabled Di                            |                           | Input  | Input  | Output               | Input        |

|                                           |                   |                |       | "L" -                                                                                                                                                                                                                                                                                                                                                               | "L"                                                                              | Disabled                               | Disabled                  | Input  | Input  | Output               | Input        |

| Function F           | Pin name | Number of pins | I/O D | escr                                                                                                                             |                                                       |                | iption                                                                                              |  |  |

|----------------------|----------|----------------|-------|----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|----------------|-----------------------------------------------------------------------------------------------------|--|--|

|                      |          |                |       | This is the clock input/output pin.  The function of this pin will be as follows depending on the states of M/S and CLS signals. |                                                       |                |                                                                                                     |  |  |

|                      |          |                |       | M/S                                                                                                                              | CLS                                                   | CL             |                                                                                                     |  |  |

|                      | CL 1     |                | I/O   | " <b>—</b> "                                                                                                                     | "H"                                                   | Output         |                                                                                                     |  |  |

|                      | CL I     |                | 1/0   | П                                                                                                                                | "L"                                                   | Input          |                                                                                                     |  |  |

|                      |          |                |       | " "                                                                                                                              | "H"                                                   | Input          |                                                                                                     |  |  |

|                      |          |                |       | _                                                                                                                                | "L" Inp                                               | ut             |                                                                                                     |  |  |

| Display              |          |                |       | When th e correspond                                                                                                             |                                                       |                | in the ma ster/slave mode, the connected.                                                           |  |  |

| timing               |          |                |       | This is the                                                                                                                      | input/outpu                                           | ıt pin for LC  | CD display frame reversal signal.                                                                   |  |  |

| generator<br>circuit |          |                |       | M/S = "H": Output                                                                                                                |                                                       |                |                                                                                                     |  |  |

| 0.1.00.1.0           | FR 1     |                | I/O   | M/S = "L": Input                                                                                                                 |                                                       |                |                                                                                                     |  |  |

| _                    |          |                |       | When t he M L9059E is us ed in the master/slave mo de, the corresponding FR pin has to be connected.                             |                                                       |                |                                                                                                     |  |  |

|                      |          |                |       | This is the                                                                                                                      | This is the blanking control pin for the LCD display. |                |                                                                                                     |  |  |

|                      |          |                |       | M/S = "H": Output                                                                                                                |                                                       |                |                                                                                                     |  |  |

|                      | DOF 1    |                | I/O   | M/S = "L": Input                                                                                                                 |                                                       |                |                                                                                                     |  |  |

|                      |          |                |       | When t he M L9059E is us ed in the master/slave mo de, the corresponding $\overline{DOF}$ pin has to be connected.               |                                                       |                |                                                                                                     |  |  |

|                      | EDC 4    |                |       | This is the                                                                                                                      | output pin                                            | for static dr  | ive.                                                                                                |  |  |

|                      | FRS 1    |                | 0     | This pin is                                                                                                                      | used in cor                                           | mbination v    | vith the FR pin.                                                                                    |  |  |

|                      |          |                |       | This is the                                                                                                                      | pin for sele                                          | ecting the re  | esistor for adjusting the voltage V1.                                                               |  |  |

|                      |          |                |       | IRS = "H":                                                                                                                       | The interna                                           | al resistor is | s used.                                                                                             |  |  |

|                      | IRS 1    |                | ı     |                                                                                                                                  |                                                       |                | is not used. The voltage V1 is                                                                      |  |  |

| Power supply         |          |                |       | the pins VF                                                                                                                      | R. This pin                                           | is effective   | ntial divider resistors connected to only in the master operation. This rel during slave operation. |  |  |

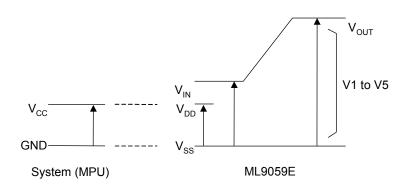

| circuit              | $V_{DD}$ | 12             | _     | These pins                                                                                                                       | are tied to                                           | the MPU p      | ower supply pin V <sub>CC</sub> .                                                                   |  |  |

|                      | $V_{SS}$ | 12             |       | These are                                                                                                                        | the 0 V pin                                           | s connecte     | d to the system ground (GND).                                                                       |  |  |

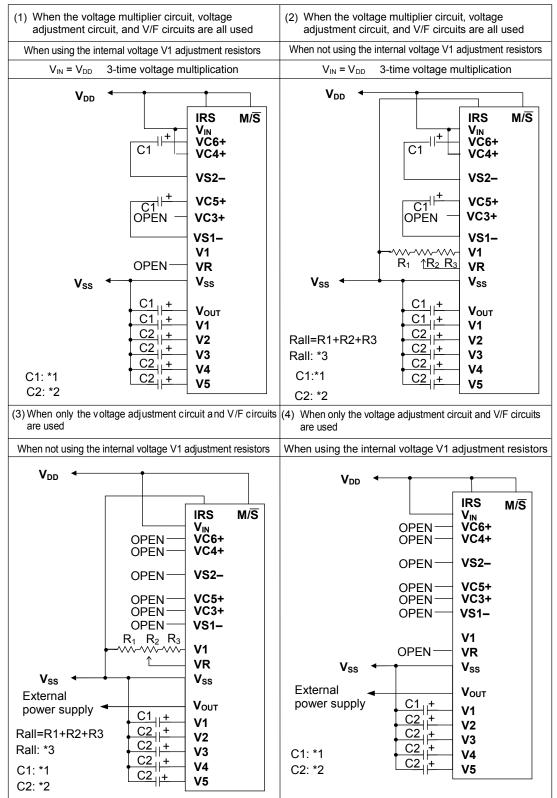

|                      | VIN      | 5              | _     | These are the reference power supply pins of the voltage multiple circuit for driving the LCD.                                   |                                                       |                |                                                                                                     |  |  |

| Function F                                                                                                                                                                  | Pin name         | Number of pins | I/O D                | escr iption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|                                                                                                                                                                             | $V_{RS}$         | 2              | _                    | These are the test pins for the LCD power supply voltage adjustment circuit. Leave these pins open.                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

|                                                                                                                                                                             | V <sub>OUT</sub> | 2              | I/O                  | These are the output pins during voltage multiplication. Connect a capacitor between these pins and V <sub>SS</sub> .                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

|                                                                                                                                                                             | V1<br>V2         |                |                      | These are the multiple level power supply pins for the LCD power supply. The voltages specified for the LCD cells are applied to these pins af ter res istor network v oltage division or aft er impedance transformation u sing operational a mplifiers. The v oltages are specified taking $V_{SS}$ as the reference, and the following relationship should be maintained among them. $V1 \geq V2 \geq V3 \geq V4 \geq V5 \geq V_{SS}$ Master operation: When the power supply is O N, the following |  |  |  |  |  |

|                                                                                                                                                                             | V3<br>V4<br>V5   | 10 I/O         |                      | voltages are applied to V2 to V5 from the built-in power supply circuit. The selection of voltages is determined by the LCD bias set command.                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

|                                                                                                                                                                             |                  |                |                      | ML9059E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

|                                                                                                                                                                             |                  |                |                      | V2 7/8 × V1 5/6 × V1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

|                                                                                                                                                                             |                  |                | V3 6/8 × V1 4/6 × V1 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

|                                                                                                                                                                             |                  |                |                      | V4 2/8 × V1 2/6 × V1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| Power supply                                                                                                                                                                |                  |                |                      | V5 1/8 × V1 1/6 × V1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

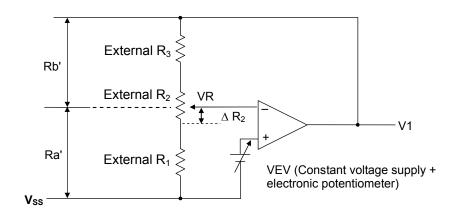

| circuit                                                                                                                                                                     | VR               | 2              | I                    | Voltage adjustment pins. Voltages between V1 and $V_{SS}$ are applied using a resistance voltage divider. These pins are effective only when the internal resistors for voltage V1 adjustment are not used (IRS = "L"). Do not use these pins when the internal resistors for voltage V1 adjustment are used (IRS = "H").                                                                                                                                                                              |  |  |  |  |  |

|                                                                                                                                                                             | VS1-3            |                | 0                    | These are the pins for connecting the negative side of the capacitors for voltage multiplication.                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

|                                                                                                                                                                             | VS2-3            |                | 0                    | Connect capacitors between these pins and VC3+, VC5+.  These are the pins for connecting the negative side of the capacitors for voltage multiplication.  Connect capacitors between these pins and VC4+, VC6+.                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| These are the input pins for voltage multiplication.  VC3+ 3  O Apply the voltage equal to V <sub>IN</sub> to the pins or leave depending on voltage multiplication values. |                  |                |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

|                                                                                                                                                                             | VC4+ 3           |                | 0                    | These are the pins for connecting the positive side of the capacitors for voltage multiplication.  Connect capacitors between VS2– and these pins.  For 3-time voltage multiplication, the pins are configured as inputs for voltage multiplication.                                                                                                                                                                                                                                                   |  |  |  |  |  |

| Function I             | in name        | Number of pins | I/O D | escr                                                                                                                                                                                                      |                                                 | iption                                             |                                                           |  |  |

|------------------------|----------------|----------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|----------------------------------------------------|-----------------------------------------------------------|--|--|

| Power supply           | VC5+ 3         |                | 0     | for voltage mul<br>Connect capac                                                                                                                                                                          | tiplication.<br>itors betweer<br>age multiplica | n VS1– and these p                                 | side of the capacitors<br>pins.<br>configured as inputs   |  |  |

| circuit                | VC6+ 3         |                | 0     | for voltage mul                                                                                                                                                                                           | tiplication.                                    | ecting the positive s                              | side of the capacitors                                    |  |  |

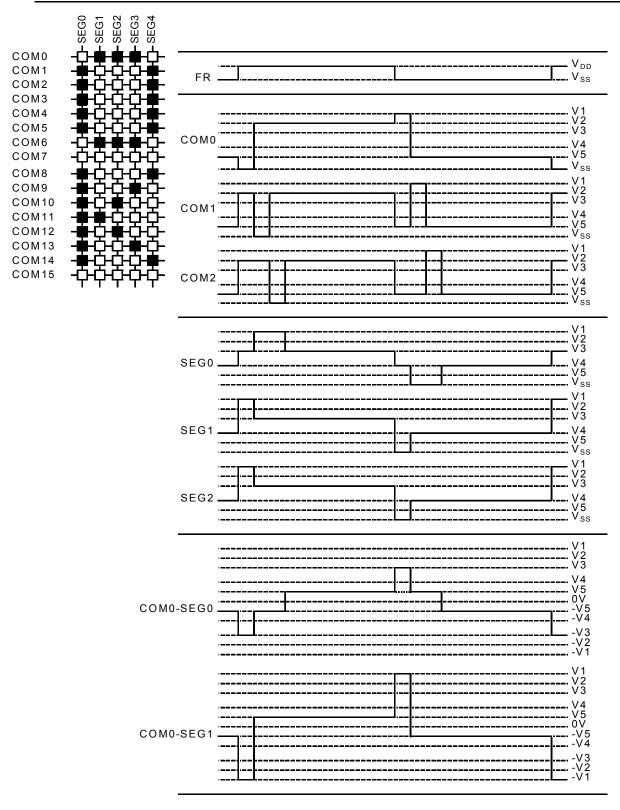

|                        |                |                |       | on the combina                                                                                                                                                                                            | ls among V1                                     | , V3, V4, and V <sub>SS</sub> is splay RAM content | s selected depending<br>and the FR signal<br>tput voltage |  |  |

|                        |                |                |       | RAM Data                                                                                                                                                                                                  | FR                                              | Forward dis                                        | play Reverse display                                      |  |  |

|                        | SEG0 to        | 422.0          |       | Н                                                                                                                                                                                                         | Н                                               | V1                                                 | V3                                                        |  |  |

|                        | SEG131         | 132 O          |       | Н                                                                                                                                                                                                         | L                                               | V <sub>SS</sub>                                    | V4                                                        |  |  |

|                        |                |                |       | L                                                                                                                                                                                                         | Н                                               | V3                                                 | V1                                                        |  |  |

|                        |                |                |       | L                                                                                                                                                                                                         | L                                               | V4                                                 | V <sub>SS</sub>                                           |  |  |