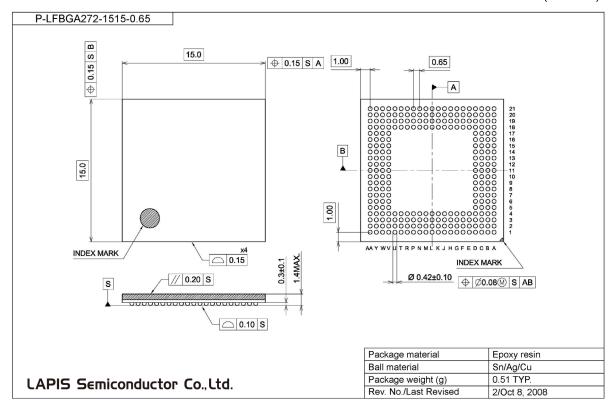

# ML696201/69Q6203 User's Manual

32-bit General Purpose Single-chip Microcontroller

Issue Date: March 27, 2009

#### **NOTICE**

No copying or reproduction of this document, in part or in whole, is permitted without the consent of LAPIS Semiconductor Co., Ltd.

The content specified herein is subject to change for improvement without notice.

The content specified herein is for the purpose of introducing LAPIS Semiconductor's products (hereinafter "Products"). If you wish to use any such Product, please be sure to refer to the specifications, which can be obtained from LAPIS Semiconductor upon request.

Examples of application circuits, circuit constants and any other information contained herein illustrate the standard usage and operations of the Products. The peripheral conditions must be taken into account when designing circuits for mass production.

Great care was taken in ensuring the accuracy of the information specified in this document. However, should you incur any damage arising from any inaccuracy or misprint of such information, LAPIS Semiconductor shall bear no responsibility for such damage.

The technical information specified herein is intended only to show the typical functions of and examples of application circuits for the Products. LAPIS Semiconductor does not grant you, explicitly or implicitly, any license to use or exercise intellectual property or other rights held by LAPIS Semiconductor and other parties. LAPIS Semiconductor shall bear no responsibility whatsoever for any dispute arising from the use of such technical information.

The Products specified in this document are intended to be used with general-use electronic equipment or devices (such as audio visual equipment, office-automation equipment, communication devices, electronic appliances and amusement devices).

The Products specified in this document are not designed to be radiation tolerant.

While LAPIS Semiconductor always makes efforts to enhance the quality and reliability of its Products, a Product may fail or malfunction for a variety of reasons.

Please be sure to implement in your equipment using the Products safety measures to guard against the possibility of physical injury, fire or any other damage caused in the event of the failure of any Product, such as derating, redundancy, fire control and fail-safe designs. LAPIS Semiconductor shall bear no responsibility whatsoever for your use of any Product outside of the prescribed scope or not in accordance with the instruction manual.

The Products are not designed or manufactured to be used with any equipment, device or system which requires an extremely high level of reliability the failure or malfunction of which may result in a direct threat to human life or create a risk of human injury (such as a medical instrument, transportation equipment, aerospace machinery, nuclear-reactor controller, fuel-controller or other safety device). LAPIS Semiconductor shall bear no responsibility in any way for use of any of the Products for the above special purposes. If a Product is intended to be used for any such special purpose, please contact a ROHM sales representative before purchasing.

If you intend to export or ship overseas any Product or technology specified herein that may be controlled under the Foreign Exchange and the Foreign Trade Law, you will be required to obtain a license or permit under the Law.

# **Preface**

This manual describes the hardware, software of the 32-bit microcontroller ML696201/69Q6203. The manuals shown below are also available, and should be consulted as necessary.

## **ARM Architecture Reference Manual**

\* Description of ARM instruction set architecture

### **ARM946E-S Technical Reference Manual**

The above documents are published by ARM Corporation. Please ensure that you refer to the latest versions.

# Notation

| Classification  | Notation                                                                                                 | Description                                                                                                                                                                                                          |

|-----------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ◆ Numeric value | xxh, xxH<br>xxb                                                                                          | Indicates a hexadecimal number. x: Any value in the range of 0 to F Indicates a binary number; "b" may be omitted. x: A value 0 or 1                                                                                 |

| ◆ Unit          | word, W byte, B nibble, N maga-, M kilo-, K kilo-, k milli-, m micro-, µ nano-, n second, s (lower case) | 1 word = 16 bits<br>1 byte = 2 nibbles = 8 bits<br>1 nibble = 4 bits<br>$10^6$<br>$2^{10} = 1024$<br>$10^3 = 1000$<br>$10^{-3}$<br>$10^{-6}$<br>$10^{-9}$<br>second                                                  |

| ◆ Symbol        | x0hex                                                                                                    | x indicates any value in the range of 0 to F of the high-order 4 bits.                                                                                                                                               |

| ◆ Terminology   | "H" level, "1" level "L" level, "0" level                                                                | Indicates high voltage signal levels $V_{IH}$ and $V_{OH}$ as specified by the electrical characteristics. Indicates low voltage signal levels $V_{IL}$ and $V_{OL}$ as specified by the electrical characteristics. |

# Table of Contents

| Chapter 1 Overview                                                                     |      |

|----------------------------------------------------------------------------------------|------|

| 1.1 Overview                                                                           | 1-1  |

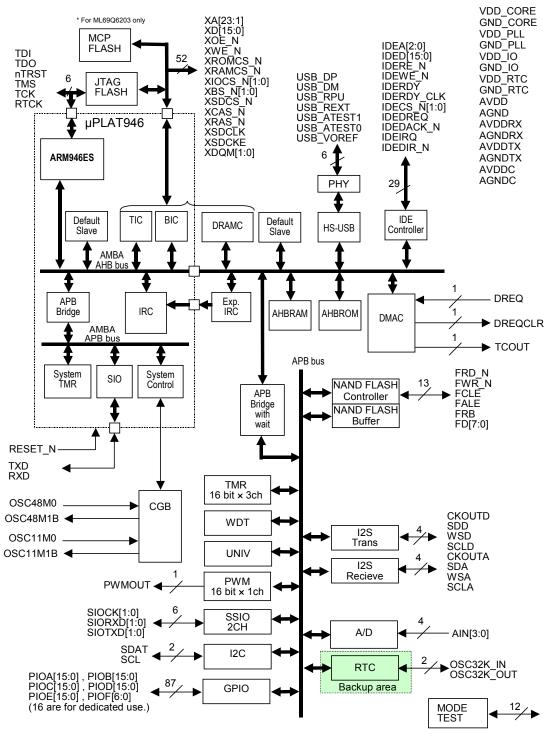

| 1.2 Functional Block Configuration.                                                    | 1-4  |

| 1.2.1 Block Diagram                                                                    |      |

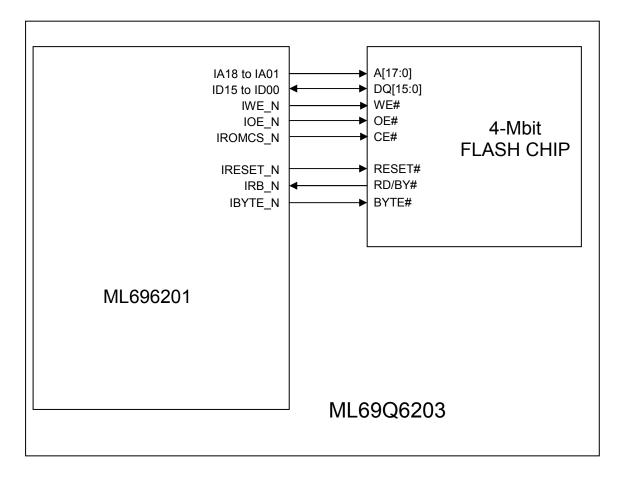

| 1.2.2 MCP Connection Diagram                                                           |      |

| 1.3 Pins                                                                               |      |

| 1.3.1 Pin Configuration                                                                |      |

| 1.3.1.1 Pin Configuration                                                              |      |

| 1.3.1.2 Pin Assignment Table                                                           |      |

| 1.3.2 Pin List                                                                         |      |

| 1.3.3 Pin Description                                                                  |      |

| 1.3.4 Status of Pins                                                                   |      |

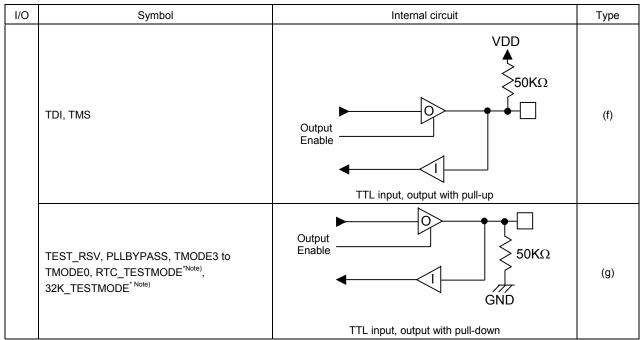

| 1.3.5.1 Pin Structure and Processing                                                   |      |

| 1.3.5.2 Connection Method of Unused Pins                                               |      |

| Chapter 2 CPU                                                                          |      |

| 2.1 Overview                                                                           | 2-1  |

| 2.2 Features                                                                           |      |

| 2.3 AHB Arbitration                                                                    |      |

| 2.4 Details of the CPU Core and the Cache Memory                                       |      |

| 2.5 Precautions When Using Caches                                                      |      |

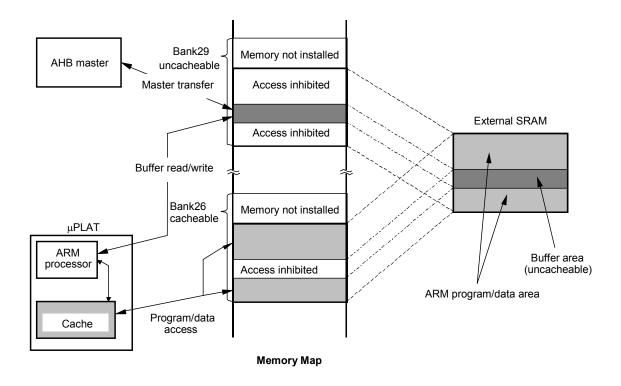

| 2.5.1 Precautions in Using AHB Master Functions such as DMA (See the Following Figure) | 2-4  |

| 2.5.2 Precautions for Remapping                                                        |      |

| 2.5.3 Precautions in Setting Cacheable and Bufferable Areas                            |      |

| 2.5.4 Notes on Memory Cache and Write Buffer                                           |      |

| 2.5.4.1 Setting of Cache Policy                                                        |      |

| 2.5.4.2 DMA Region                                                                     |      |

| 2.5.4.3 Prevention of Data Loss during Power OFF and Reset                             | 2-7  |

| 2.5.4.4 Prevention of Data Loss During Use of a Memory Controller with Memory Access   | • •  |

| Disable Mode                                                                           |      |

| 2.5.4.5 Rewriting the Program                                                          |      |

| 2.5.4.6 Order of Write Access to a Bufferable Region                                   | 2-12 |

| Chapter 3 Address Map                                                                  |      |

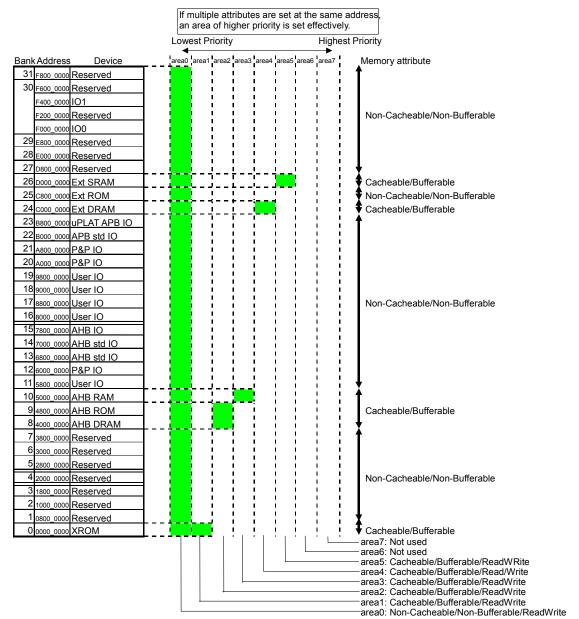

| 3.1 Overall Address Map                                                                | 3-1  |

| 3.2 Detailed Address Map of the AHB Section                                            | 3-2  |

| 3.3 Detailed Address Map of the APB Section                                            |      |

| 3.4 Remapping                                                                          | 3-4  |

| Chapter 4 Mode Settings                                                                |      |

| 4.1 Overview                                                                           | 4-1  |

| 4.1.1 Pin List                                                                         |      |

| 4.2 Mode Setting Pins                                                                  |      |

| Chapter 5 Clock Control                                                                |      |

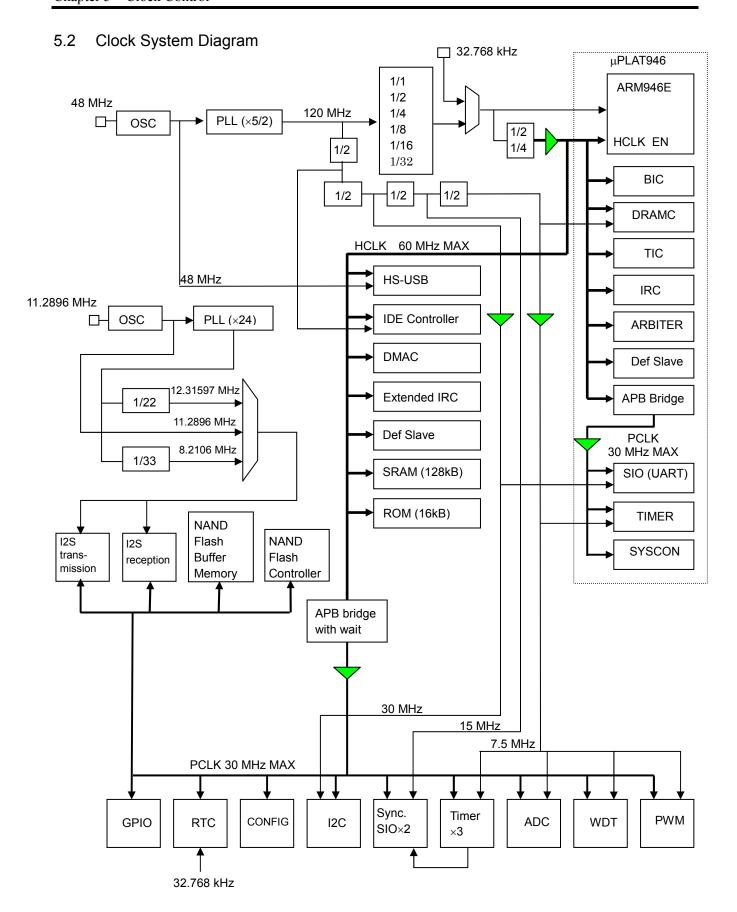

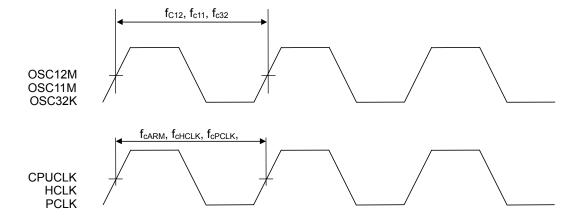

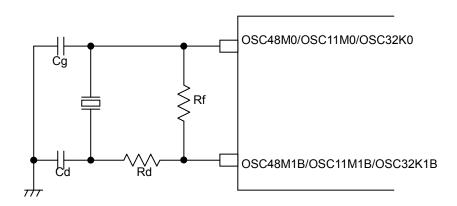

| 5.1 Overview                                                                           |      |

| 5.1.1 Configuration                                                                    |      |

| 5.2 Clock System Diagram                                                               |      |

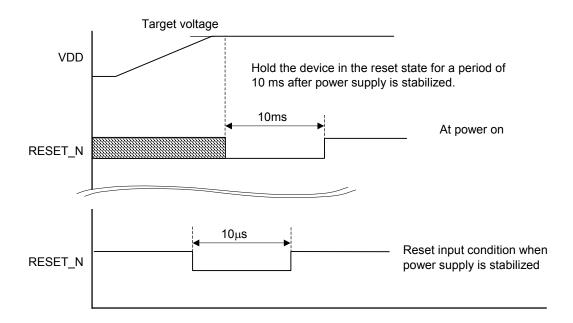

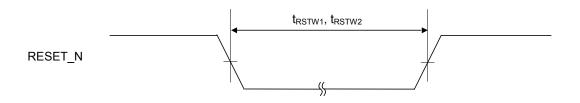

| Chapter 6 Reset Control                                                                               |      |

|-------------------------------------------------------------------------------------------------------|------|

| 6.1 Overview                                                                                          | 6-1  |

| 6.1.1 Pin List                                                                                        |      |

| 6.2 Reset Methods                                                                                     |      |

| 6.2.1 Reset by an External Pin                                                                        |      |

| 6.2.2 Resetting by Watchdog Timer Overflow                                                            |      |

| 6.3 Reset Sequence                                                                                    |      |

| Chapter 7 Power Consumption Control and System Control                                                |      |

| 7.1 Overview                                                                                          | 7-1  |

| 7.2 Power Consumption Control Function.                                                               |      |

| 7.2.1 RTC (Real Time Clock) Module Backup Mode                                                        |      |

| 7.2.1.1 Procedure for Transiting to the Backup Mode                                                   |      |

| 7.2.1.2 Procedure for Recovering from the Backup Mode                                                 |      |

| 7.2.2 Clock Stop Modes                                                                                |      |

| 7.2.2.1 STOP Mode                                                                                     |      |

| 7.2.2.1.1 Method of Recovering from the STOP Mode                                                     |      |

| 7.2.2.1.2 Method of Recovering from the STOP Mode When the 32 kHz Clock is Selected for the CPU Clock |      |

| 7.2.2.2 Clock STOP Mode in Functional Block Units                                                     |      |

| 7.2.2.3 Clock Gear                                                                                    |      |

| 7.3 List of Registers                                                                                 |      |

| 7.3.1 SYSCON Module                                                                                   |      |

| 7.3.2 Configuration Register Module                                                                   |      |

| 7.4 Description of Registers                                                                          |      |

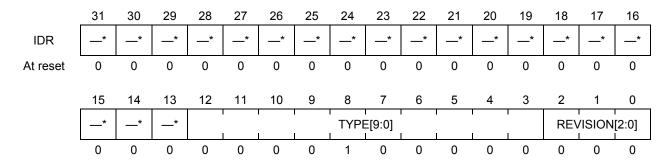

| 7.4.1 ID Register (IDR)                                                                               |      |

| 7.4.2 Clock Stop Register (CLKSTP)                                                                    |      |

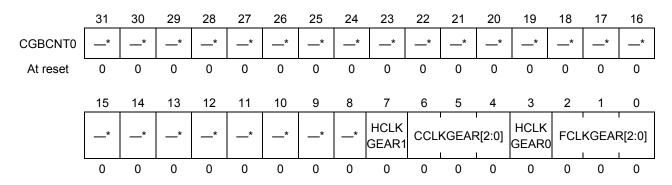

| 7.4.3 Clock (CGB) Control Register 0 (CGBCNT0)                                                        |      |

| 7.4.4 Clock Supply Wait Time Control Register (CKWT)                                                  |      |

| 7.4.5 Remap Control Register (RMPCON)                                                                 |      |

| 7.4.6 Clock (CGB) Control Register 1 (CGBCNT1)                                                        | 7-15 |

| 7.4.7 Clock (CGB) Control Register 2 (CGBCNT2)                                                        | 7-16 |

| 7.5 Procedures, Cautions, and Restrictions on the Use of Power Management                             | 7-17 |

| 7.5.1 On Power Management by Stopping the 48 MHz Clock                                                | 7-17 |

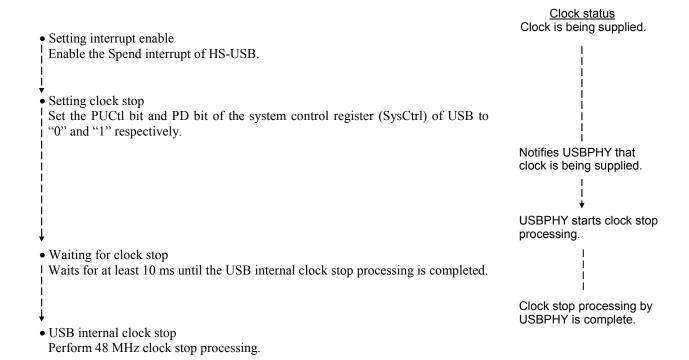

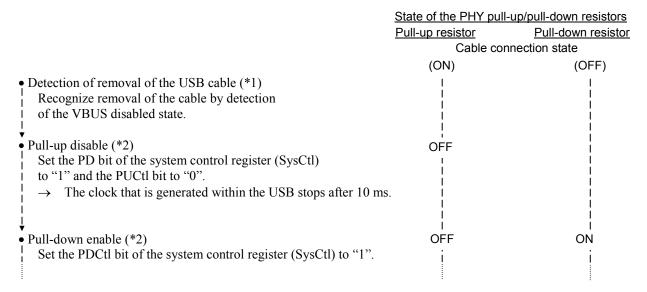

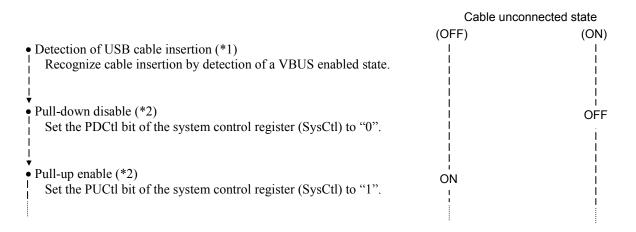

| 7.5.2 Power Management by Stopping USB Clock While USB Is Idle                                        | 7-18 |

| 7.5.3 SDRAM Power Management                                                                          |      |

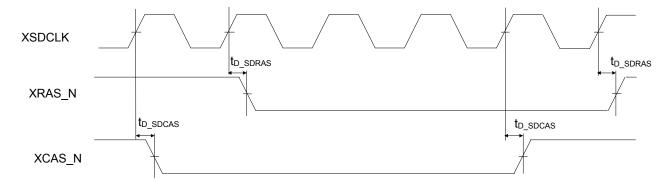

| 7.5.3.1 Power Down due to Stopping of the XSDCLK when SDRAM Is Not Accessed                           |      |

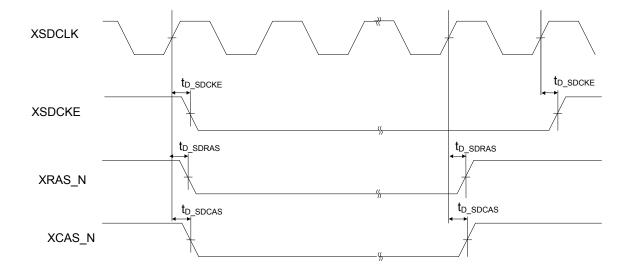

| 7.5.3.2 Power Down due to Transition to the Self-Refresh State                                        | 7-19 |

| 7.5.4 Power Management by Stopping the Clock of an Unused Module                                      |      |

| 7.5.5 Power Management by Stopping CPU Operation                                                      | 7-19 |

| Chapter 8 Interrupt Controller                                                                        |      |

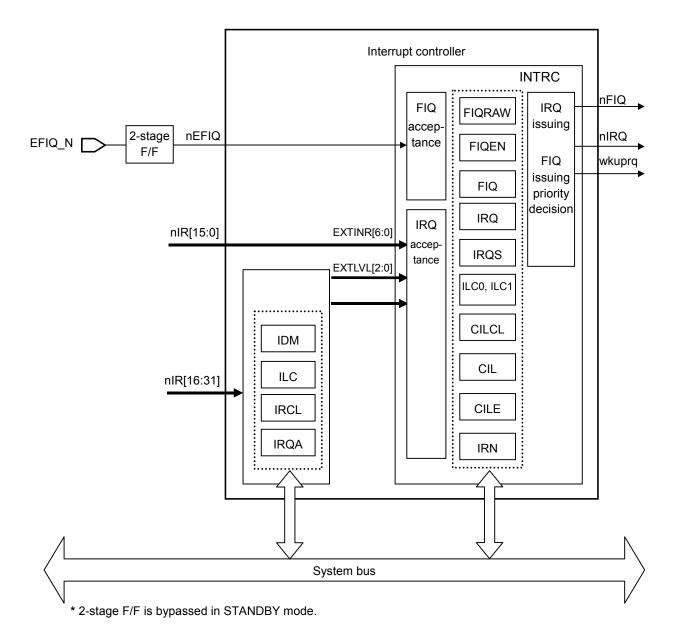

| 8.1 Overview                                                                                          | 8-1  |

| 8.1.1 Configuration                                                                                   |      |

| 8.1.2 List of Pins                                                                                    |      |

| 8.1.3 List of Registers                                                                               |      |

| 8.2 Interrupt Sources                                                                                 |      |

| 8.3 Interrupt Levels                                                                                  |      |

| 8.4 Description of Registers                                                                          |      |

| 8.4.1 IRQ Register (IRQ)                                                                              |      |

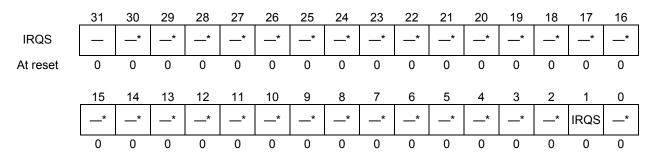

| 8.4.2 IRQ Software Register (IRQS)                                                                    |      |

| 8.4.3 FIQ Register (FIQ)                                                                              |      |

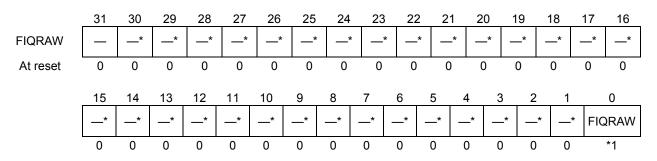

| 8.4.4 FIQRAW Register (FIQRAW)                                                                        |      |

| 8.4.5 FIQ Enable Register (FIQEN)                                                                     |      |

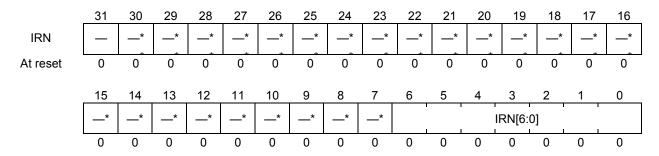

| 8.4.6 IRQ Number Register (IRN)                                                                       |      |

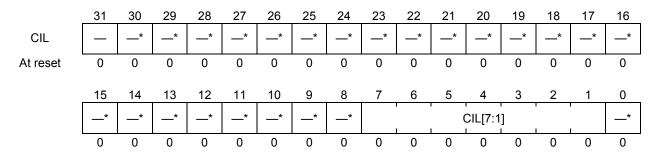

| 8.4.7 Current IRQ Level Register (CIL)                                                                |      |

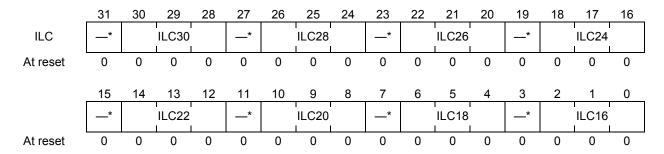

| 8.4.8                                | IRQ Level Control Register 0 (ILC0)                                 |                         |

|--------------------------------------|---------------------------------------------------------------------|-------------------------|

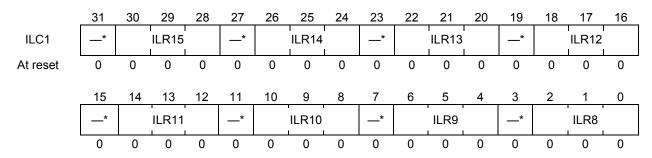

| 8.4.9                                | IRQ Level Control Register 1 (ILC1)                                 | 8-15                    |

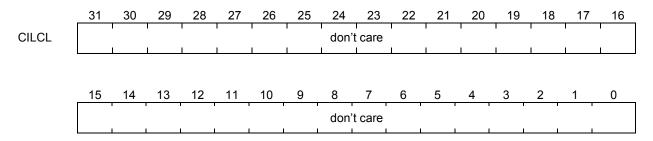

| 8.4.10                               | Current IRQ Level Clear Register (CILCL)                            | 8-17                    |

| 8.4.11                               | Current IRQ Level Encode Register (CILE)                            | 8-18                    |

| 8.4.12                               | IRQ Clear Register (IRCL)                                           | 8-19                    |

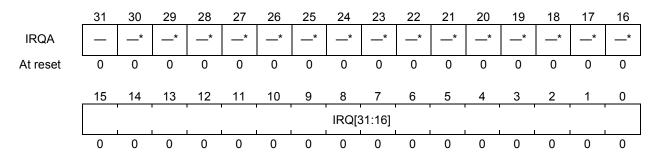

| 8.4.13                               | IRQA Register (IRQA)                                                | 8-20                    |

| 8.4.14                               | IRQ Detect Mode Setting Register (IDM)                              | 8-22                    |

| 8.4.15                               | IRQ Level Control Register (ILC)                                    | 8-24                    |

| 8.4.16                               | Correspondence between Interrupt Sources and Registers that Are Set | 8-26                    |

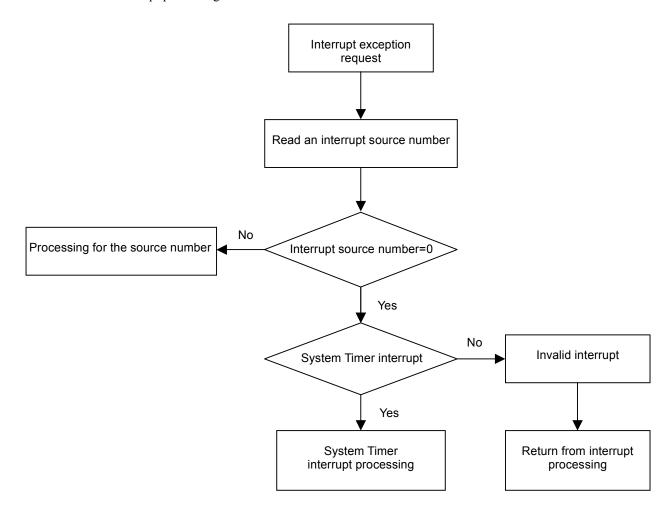

| 8.5 Des                              | cription of Operation                                               | 8-27                    |

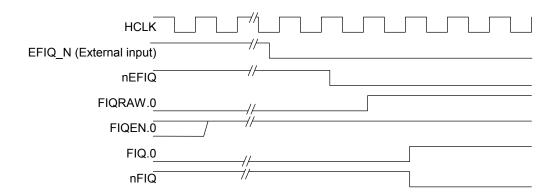

| 8.5.1                                | External FIQ Interrupt                                              |                         |

| 8.5.1.1                              |                                                                     |                         |

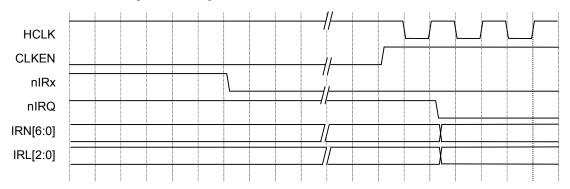

| 8.5.2                                | External Interrupt and Internal Interrupt                           |                         |

| 8.5.2.1                              |                                                                     |                         |

| 8.5.2.2                              |                                                                     |                         |

| 8.5.3                                | Reentrant Interrupt Control                                         |                         |

| 8.5.4                                | Cautions Pertaining to Interrupts                                   |                         |

| 8.5.4.1                              | · · · · · · · · · · · · · · · · · · ·                               |                         |

| 8.5.4.2                              | · · · · · · · · · · · · · · · · · · ·                               |                         |

| 8.5.4.3                              | 1                                                                   |                         |

| 8.5.5                                | Returning from the HALT/STANDBY Mode (Hardware Requirement)         |                         |

| 8.5.6                                | Generating Error Responses.                                         |                         |

| 8.5.7                                | Interrupt Response Time                                             |                         |

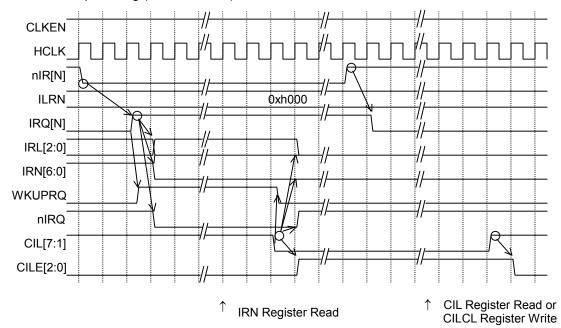

|                                      | rrupt Acceptance Timing Diagram                                     |                         |

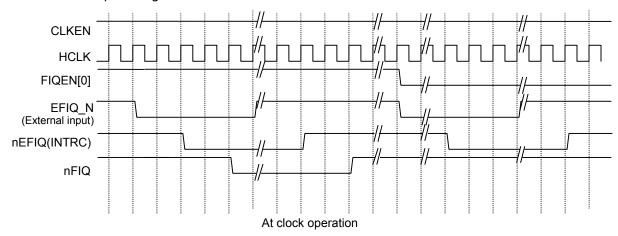

| 8.6.1                                | FIQ Interrupt Timing                                                |                         |

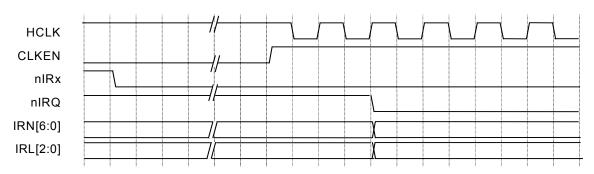

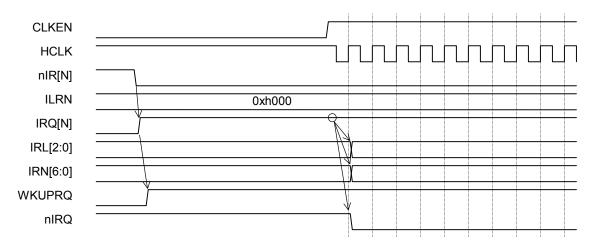

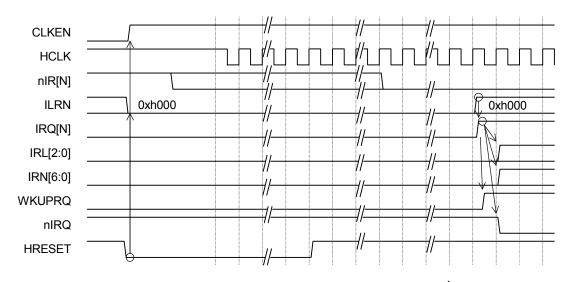

| 8.6.2                                | IRQ Interrupt Timing (nIR0 to nIR15)                                |                         |

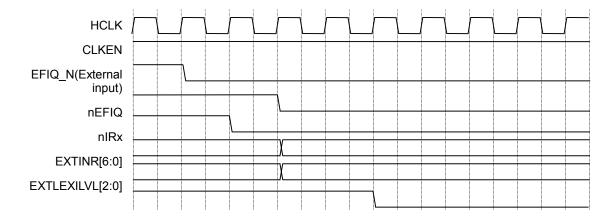

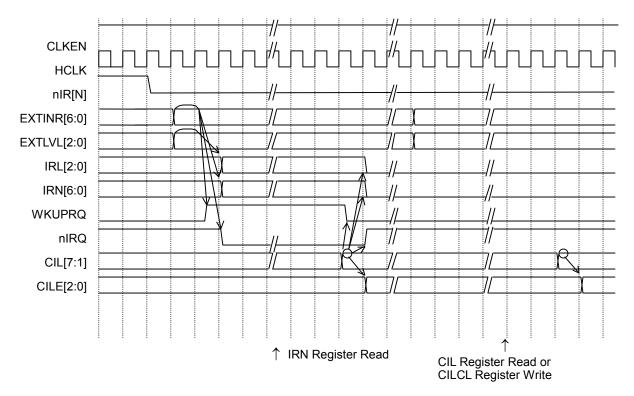

| 8.6.3                                | IRQ Interrupt Timing (IIRO to IIRT)                                 |                         |

|                                      | tures                                                               |                         |

| Chapter 1                            | 0 External Memory Controller                                        |                         |

| 10.1 Ove                             | rview                                                               | 10-1                    |

| 10.1.1                               | List of Pins                                                        | 10-1                    |

| 10.1.2                               | List of Registers                                                   | 10-2                    |

| 10.2 Reg                             | isters                                                              |                         |

| 10.2.1                               | Bus Width Control Register (BWC)                                    | 10-3                    |

| 10.2.2                               | External ROM Access Control Register (ROMAC)                        |                         |

| 10.2.3                               | External SRAM Access Control Register (RAMAC)                       | 10-7                    |

| 10.2.4                               | External I/O Bank 0 Access Control Register (IO0AC)                 | 10-8                    |

| 10.2.5                               | External I/O bank 1 Access Control Register (IO1AC)                 | 10-9                    |

| 10.2.6                               | DRAM Bus Width Control Register (DBWC)                              | 10-10                   |

| 10.2.7                               | DRAM Control Register (DRMC)                                        | 10-11                   |

| 10.2.8                               | DRAM Property Parameter Control Register (DRPC)                     |                         |

| 10.2.9                               | SDRAM Mode Register (SDMD)                                          |                         |

| 10.2.10                              | DRAM Command Register (DCMD)                                        |                         |

| 10.2.11                              | DRAM Refresh Cycle Control Register 0 (RFSH0)                       |                         |

|                                      | DRAM Refresh Cycle Control Register 1(RFSH1)                        |                         |

|                                      |                                                                     |                         |

|                                      | DRAM Power Down Control Register (PDWC)                             | 10-18                   |

| 10.5 Me                              | DRAM Power Down Control Register (PDWC)                             |                         |

|                                      | mory Access Control                                                 | 10-19                   |

| 10.3 Mei<br>10.3.1<br>10.3.2         | mory Access Control                                                 | 10-19<br>10-19          |

| 10.3.1<br>10.3.2                     | Bus Width                                                           | 10-19<br>10-19<br>10-19 |

| 10.3.1<br>10.3.2<br>10.3.3           | Bus Width                                                           |                         |

| 10.3.1<br>10.3.2<br>10.3.3<br>10.3.4 | Bus Width                                                           |                         |

| 10.3.1<br>10.3.2<br>10.3.3           | Bus Width                                                           |                         |

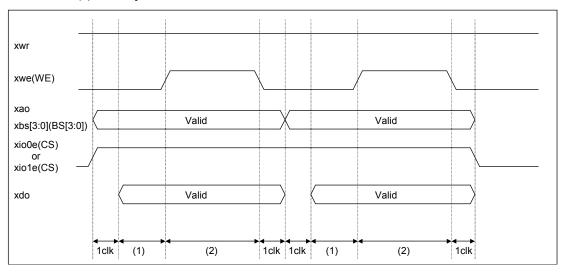

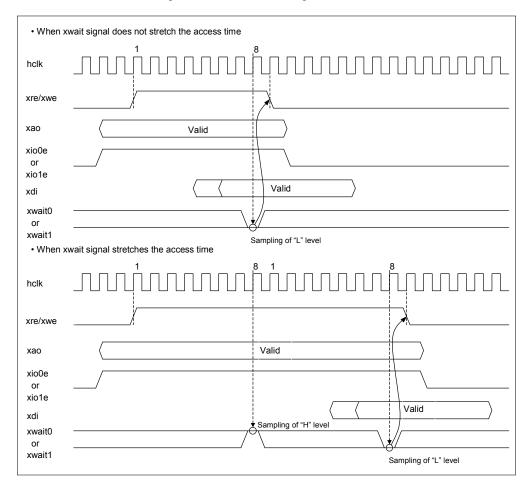

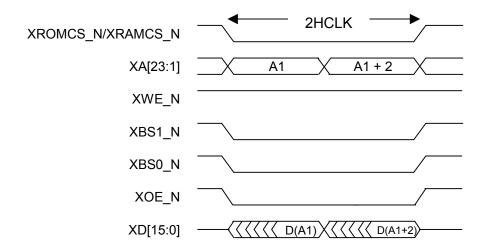

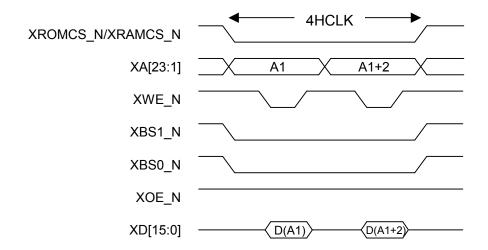

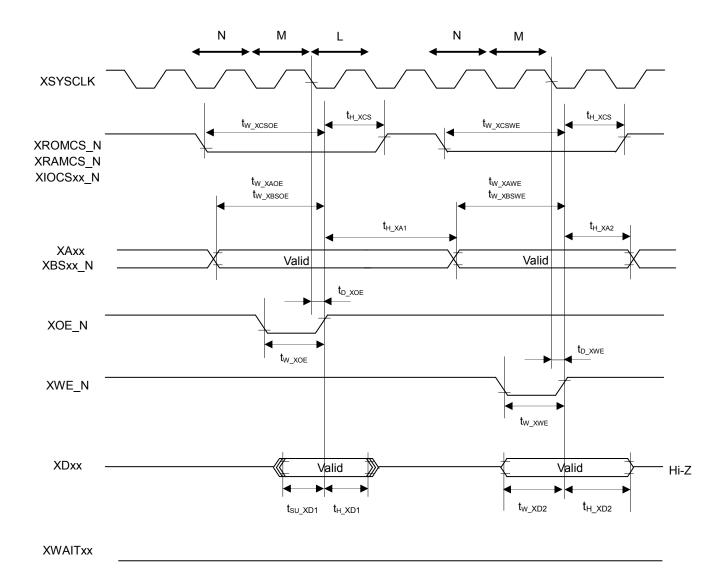

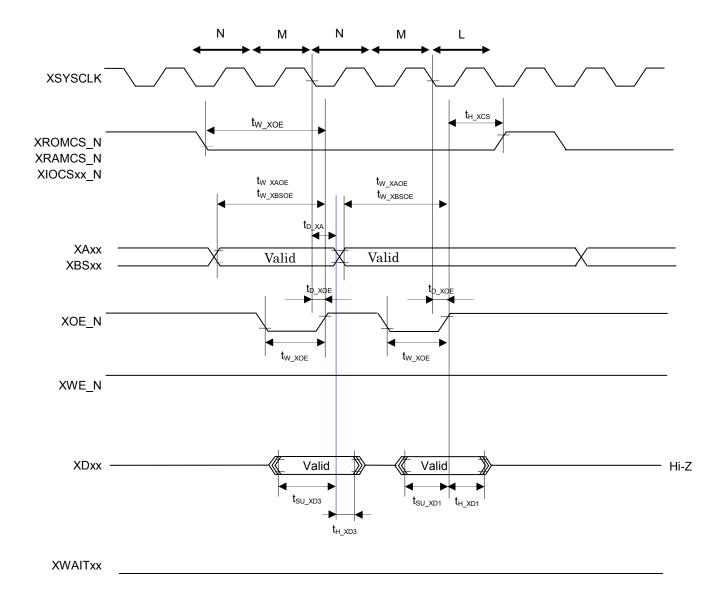

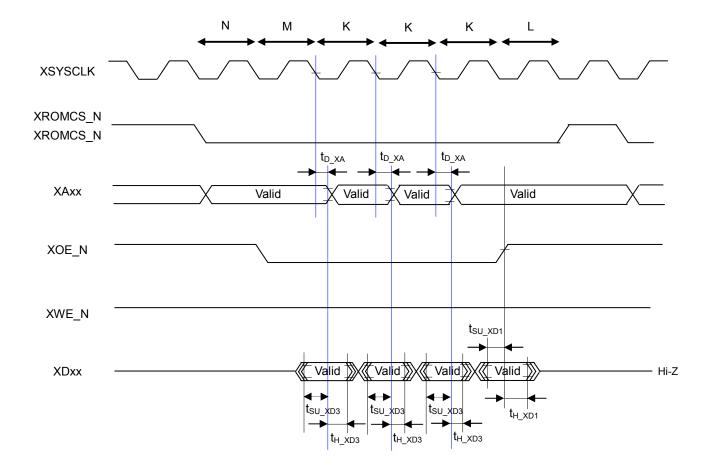

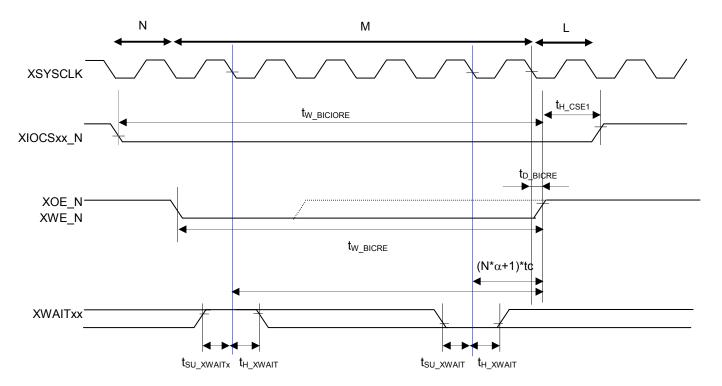

| 10.3.7           | Timing Settings                                                  | 10-24 |

|------------------|------------------------------------------------------------------|-------|

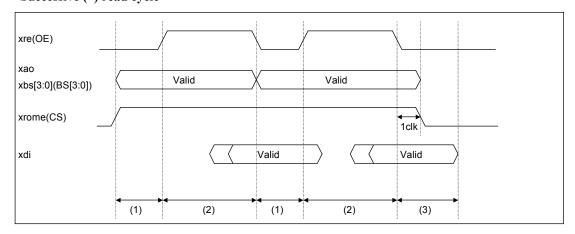

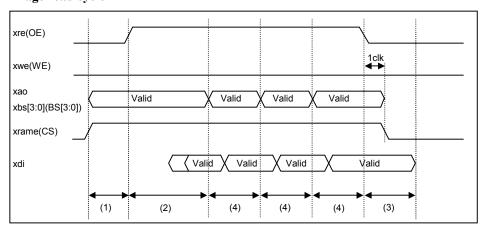

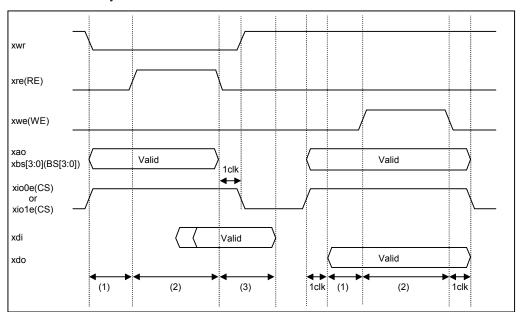

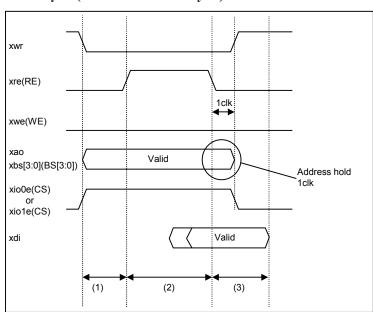

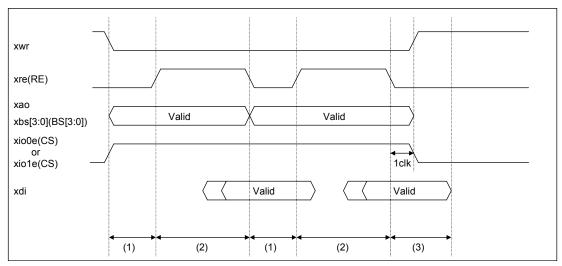

| 10.3.7           | 7.1 External ROM access function                                 | 10-24 |

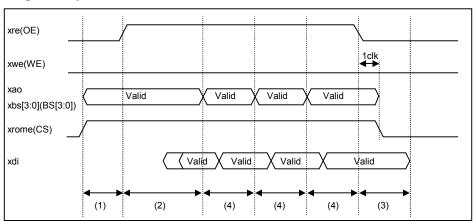

| 10.3.            | 7.2 External SRAM access function                                | 10-26 |

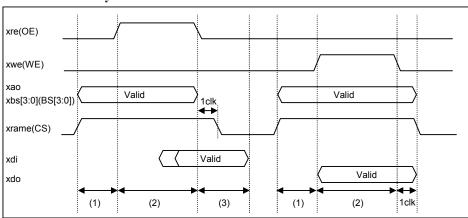

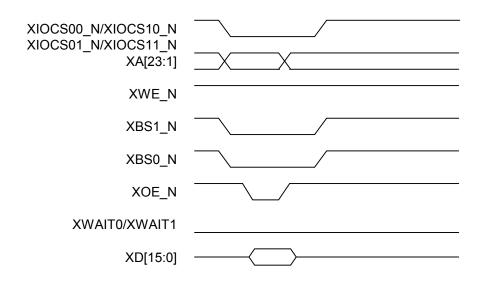

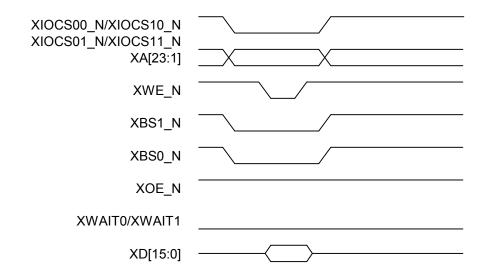

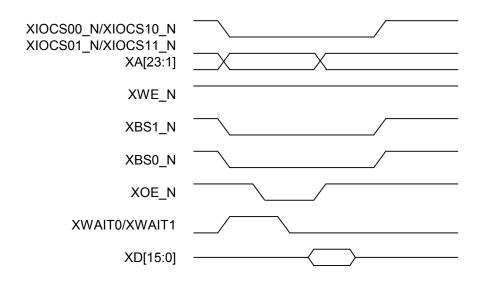

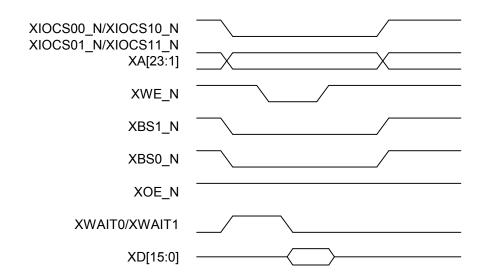

| 10.3.            | 7.3 External IO access function                                  | 10-28 |

| 10.3.8           | Data Off Time Control                                            | 10-32 |

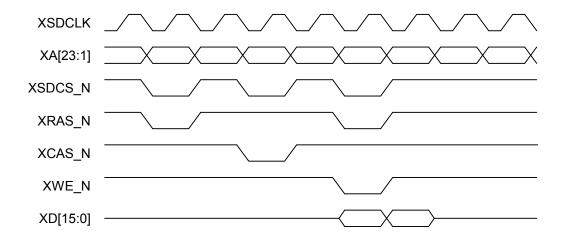

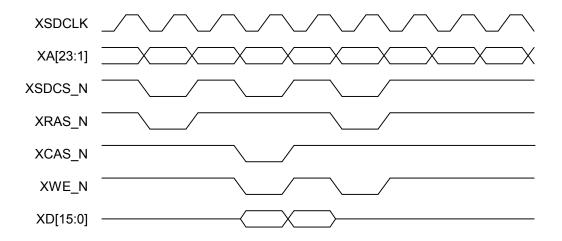

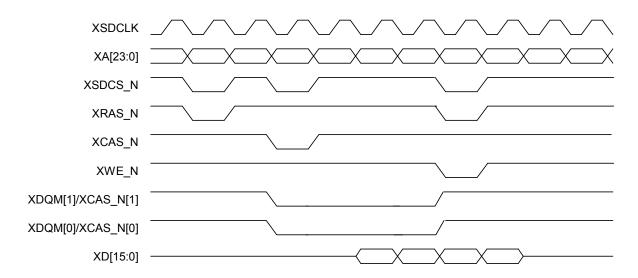

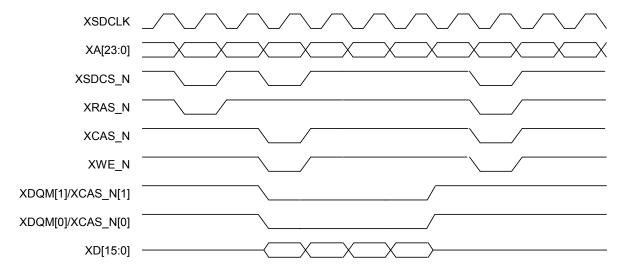

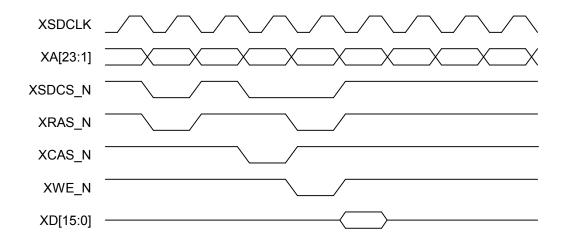

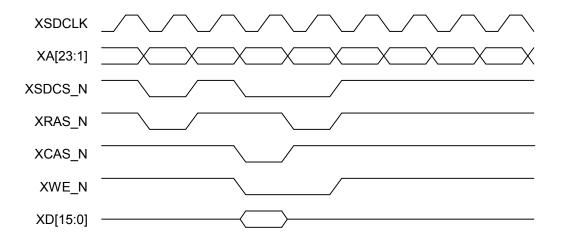

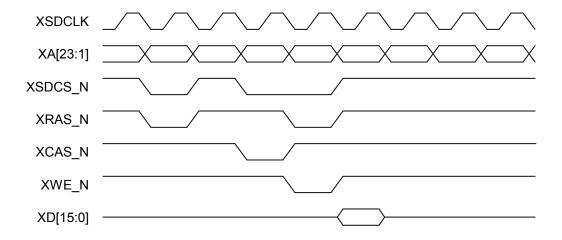

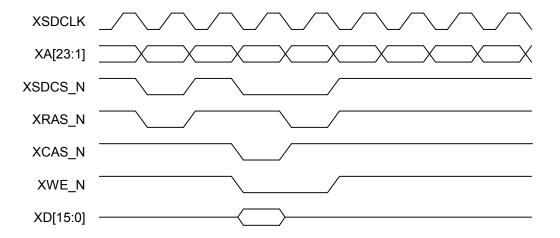

| 10.4 Ac          | cess Timing Examples                                             | 10-33 |

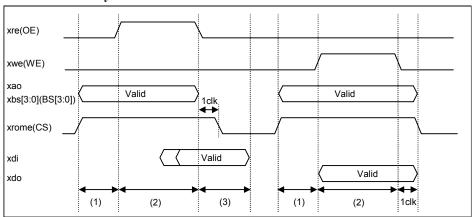

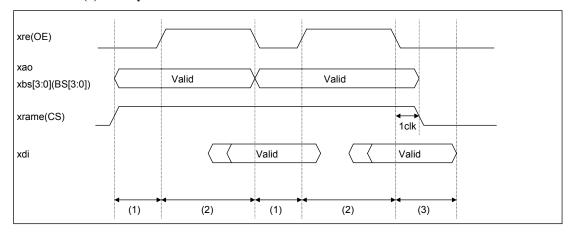

| 10.4.1           | Accessing External Devices                                       | 10-33 |

| 10.5 Po          | wer Management of DRAM                                           | 10-40 |

| 10.6 Pre         | ecautions in Using SDRAM with Self-Refresh Setting               | 10-40 |

| 10.7 Ex          | amples of Connection with External Memory                        | 10-42 |

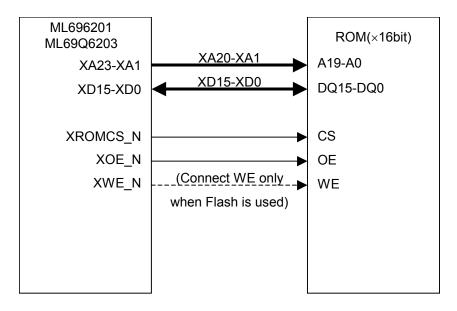

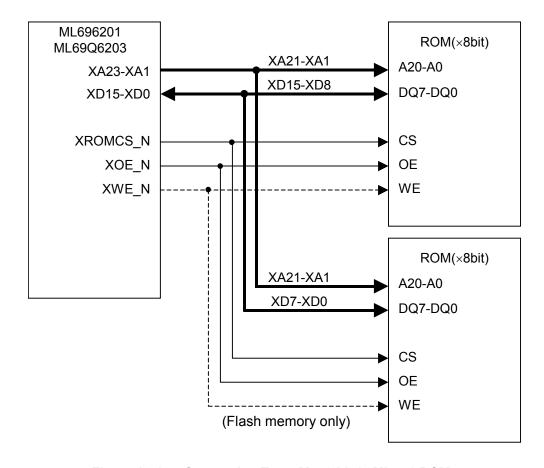

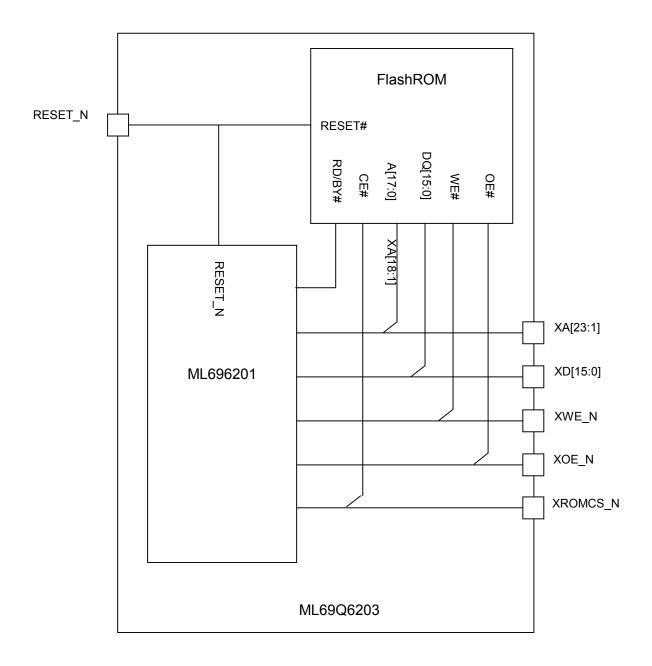

| 10.7.1           | Connection of ROM                                                | 10-43 |

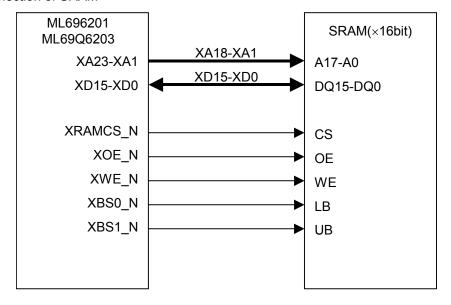

| 10.7.2           | Connection of SRAM                                               |       |

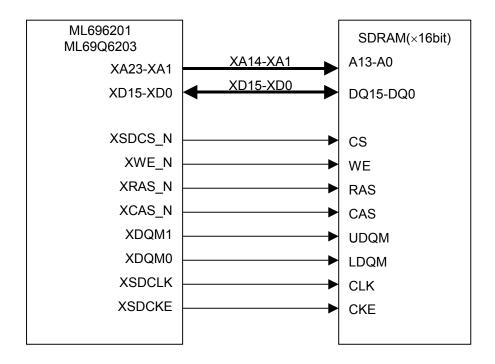

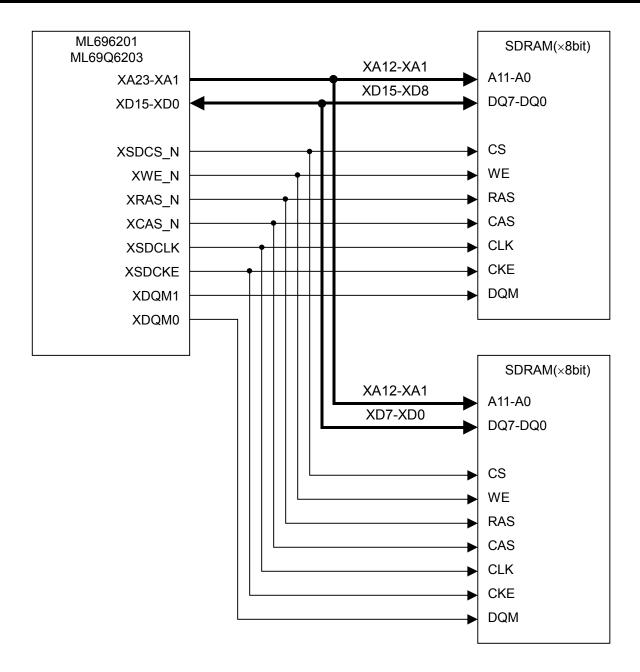

| 10.7.3           | Connection of SDRAM                                              | 10-44 |

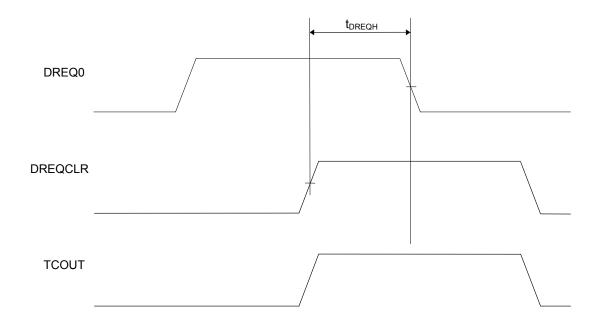

| Chapter 1        | 1 Direct Memory Access Controller                                |       |

|                  | <u>-</u>                                                         | 11.1  |

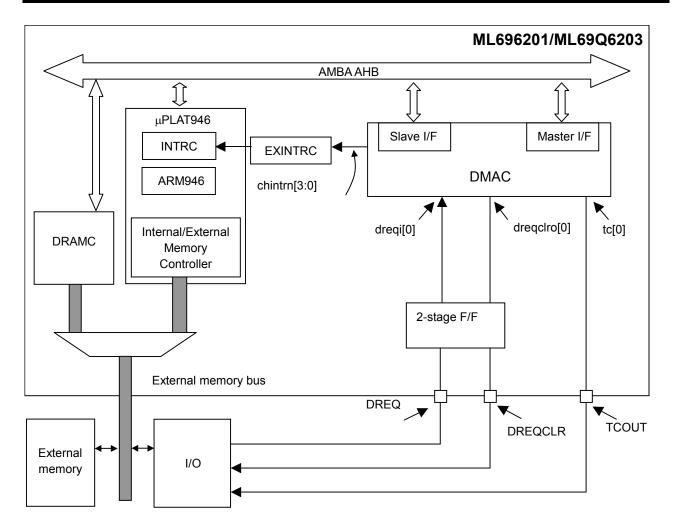

|                  | erview                                                           |       |

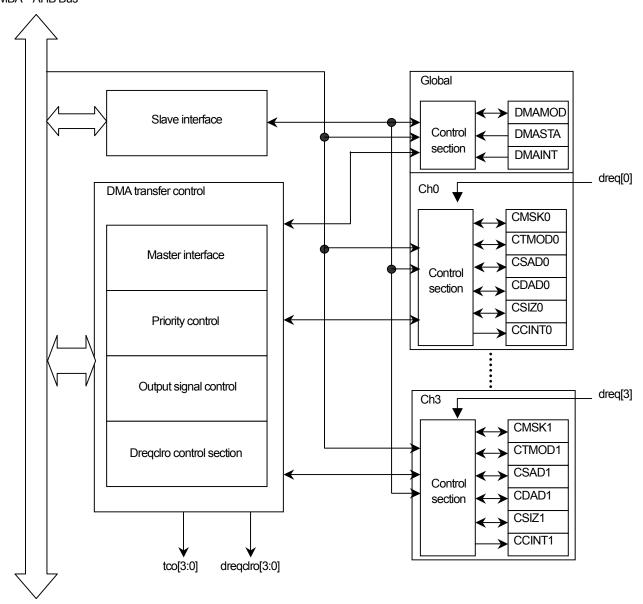

| 11.1.1           | Configuration                                                    |       |

| 11.1.2           | List of Pins                                                     |       |

| 11.1.3           | List of Registers                                                |       |

|                  | gisters                                                          |       |

| 11.2.1           | DMA Mode Register (DMAMOD)                                       |       |

| 11.2.2           | DMA Status Register (DMASTA)                                     |       |

| 11.2.3           | DMA Termination Status Register (DMAINT)                         |       |

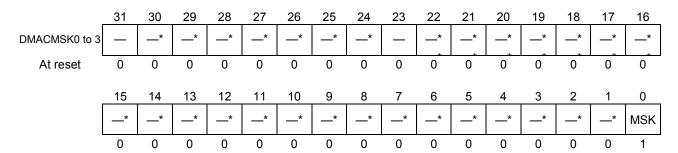

| 11.2.4           | DMA Channel Mask Registers (DMACMSK0 to 3)                       |       |

| 11.2.5           | DMA Transfer Mode Registers (DMACTMOD0 to 3)                     |       |

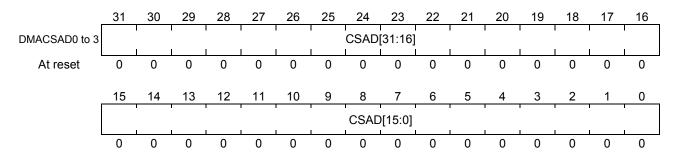

| 11.2.6           | DMA Transfer Source Address Register (DMACSAD0 to 3)             | 11-13 |

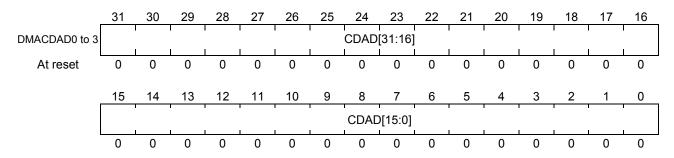

| 11.2.7           | DMA Transfer Destination Address Registers (DMACDAD0 to 3)       |       |

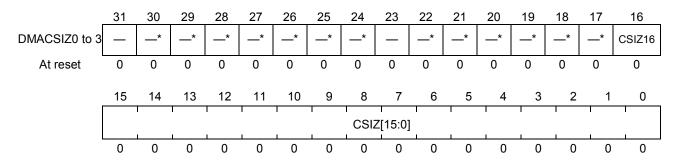

| 11.2.8           | DMA Transfer Count Register (DMACSIZ0 to 3)                      |       |

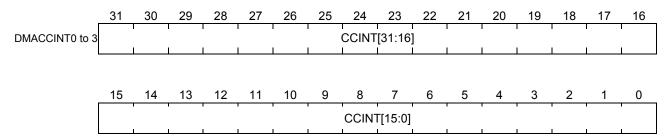

| 11.2.9           | DMA Termination Status Clear Registers (DMACCINT0 to 3)          |       |

|                  | eration Description                                              |       |

| 11.3.1           | DMA Transfer Mode                                                |       |

| 11.3.2           | DMA Activation Factors                                           |       |

| 11.3.3           | Activating DMA Transfer                                          |       |

| 11.3.4           | End of DMA Transfer                                              |       |

| 11.3.5           | DMA Channel Priority Order                                       |       |

| 11.3.6           | Notes on Use                                                     |       |

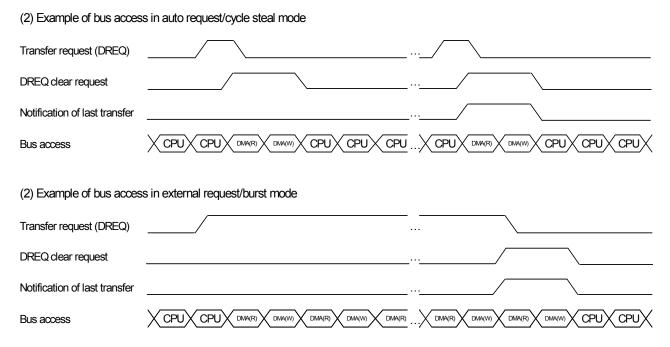

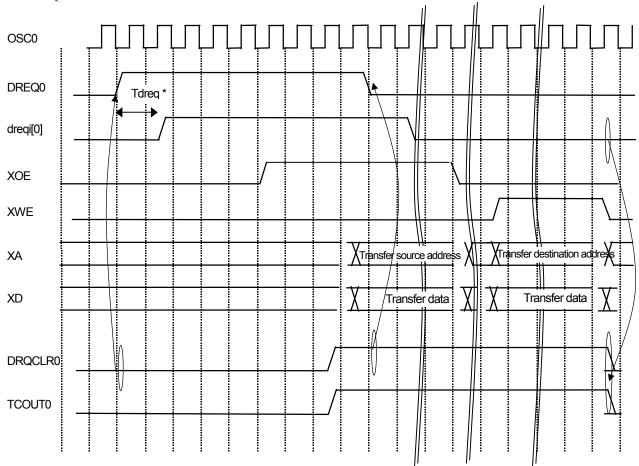

| 11.4 DN          | AA Transfer Timing                                               |       |

| 11.4.1           | Transfer Start Timing                                            |       |

| 11.4.2           | Transfer Timing                                                  | 11-22 |

| Chapter 1        | 2 GPIO                                                           |       |

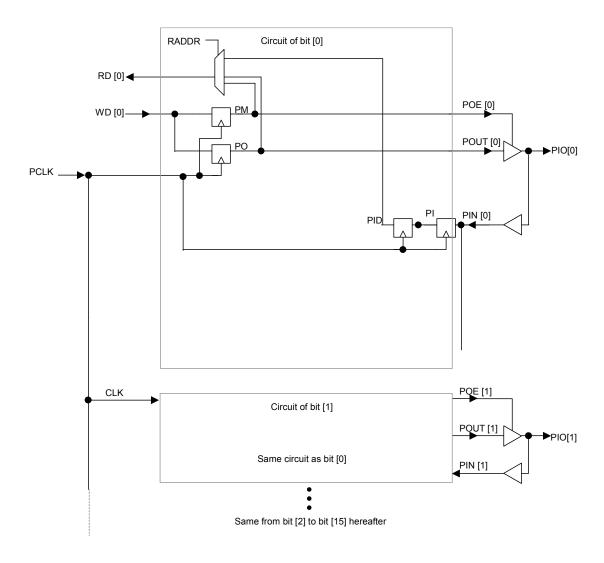

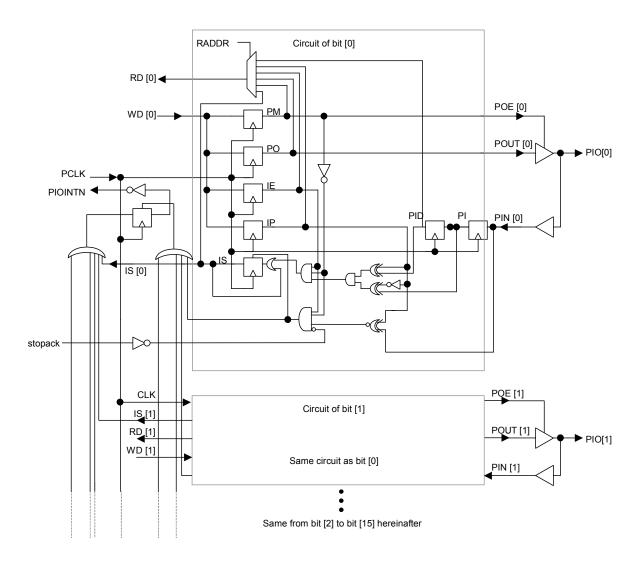

| 12.1 Ox          | erview                                                           | 12-1  |

| 12.1.1           | Configuration                                                    |       |

| 12.1.1           | Pin List                                                         |       |

| 12.1.2           | Register List                                                    |       |

|                  | gister Description                                               |       |

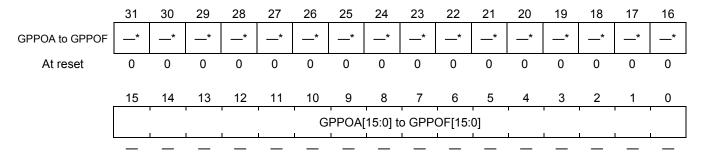

| 12.2.1           | Port Output Registers (GPPOA, GPPOB, GPPOC, GPPOD, GPPOE, GPPOF) |       |

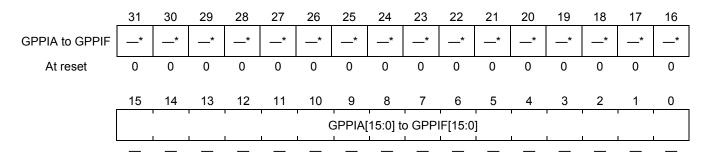

| 12.2.2           | Port Input Registers (GPPIA, GPPIB, GPPIC, GPPID, GPPIE, GPPIF)  |       |

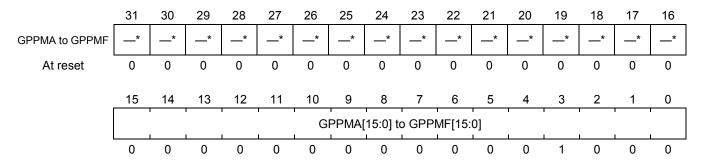

| 12.2.3           | Port Mode Registers (GPPMA, GPPMB, GPPMC, GPPMD, GPPME, GPPMF)   |       |

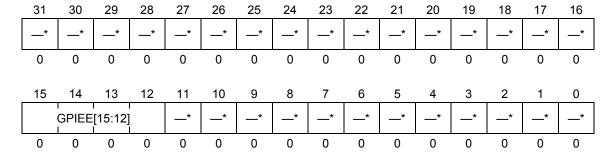

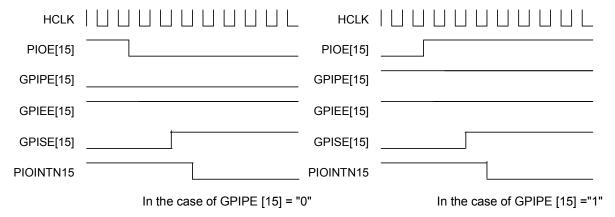

| 12.2.3           | Port E Interrupt Enable Register (GPIEE)                         |       |

| 12.2.5           | Port E Interrupt Polarity Register (GPIPE)                       |       |

| 12.2.5           | Port E Interrupt Status Register (GPISE)                         |       |

| 12.2.7           | Port E Interrupt Mode Register (GPIME)                           |       |

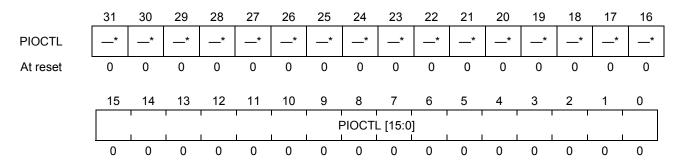

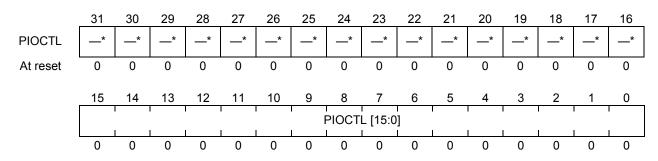

| 12.2.7           | PIO Pin Switching Register (PIOCTL)                              |       |

|                  | erational Description                                            |       |

| -                |                                                                  |       |

| 12.3.1<br>12.3.2 | Interrupt Request                                                |       |

| 14.3.4           | 1 milar y/secondary Function Control                             | 1∠-1/ |

| Chapter 1 | 3 Watchdog Timer (WDT)                                             |       |

|-----------|--------------------------------------------------------------------|-------|

| 13.1 Ov   | erview                                                             | 13_1  |

| 13.1.1    | Configuration                                                      |       |

| 13.1.2    | Register List                                                      |       |

|           | gister Description                                                 |       |

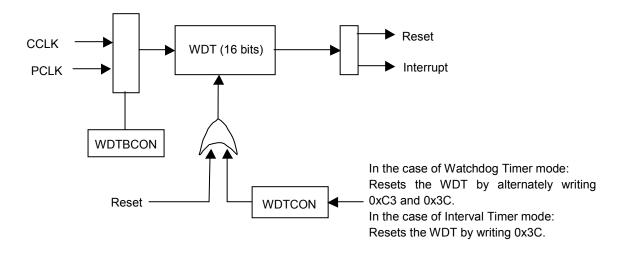

| 13.2.1    | Watchdog Timer Control Register (WDTCON)                           |       |

| 13.2.1    | Time Base Counter Control Register (WDTBCON)                       |       |

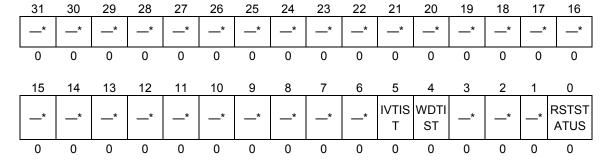

| 13.2.2    | Status Register (WDSTAT)                                           |       |

|           | erational Description                                              |       |

| 13.3.1    | Operating Mode                                                     |       |

| 13.3.2    | Interval Timer Mode                                                |       |

| 13.3.3    | Watchdog Timer Mode                                                |       |

| 13.3.4    | Starting the Watchdog Timer                                        |       |

| Chapter 1 | 4 Timers                                                           |       |

| 14.1 Ov   | erview                                                             | 14-1  |

| 14.1.1    | Configuration                                                      |       |

| 14.1.2    | Register List                                                      |       |

| 14.2 Re   | gister Description                                                 |       |

| 14.2.1    | System Timer Enable Register (TMEN)                                |       |

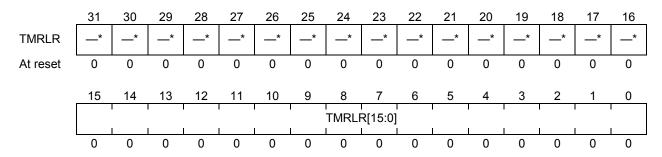

| 14.2.2    | System Timer Reload Register (TMRLR)                               |       |

| 14.2.3    | System Timer Overflow Register (TMOVFR)                            |       |

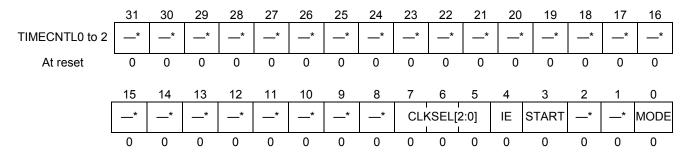

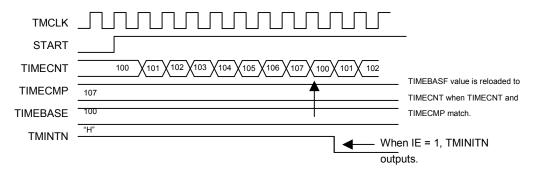

| 14.2.4    | Timer Control Registers (TIMECNTL0-2)                              |       |

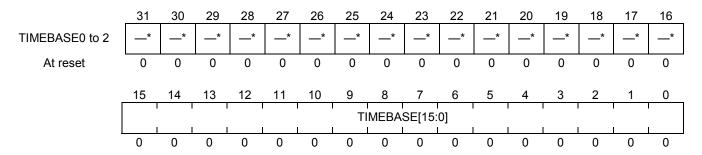

| 14.2.5    | Timer Base Registers (TIMEBASE0-2)                                 |       |

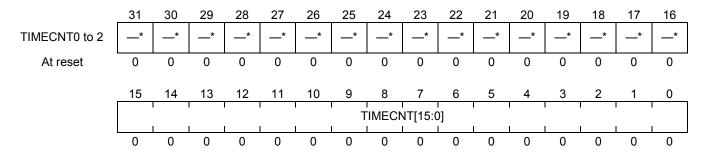

| 14.2.6    | Timer Counter Registers (TIMECNT0-2)                               |       |

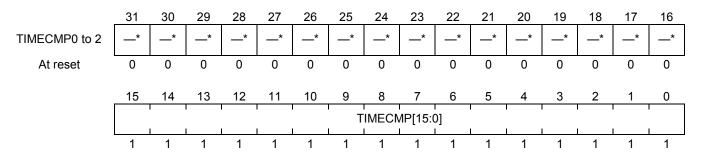

| 14.2.7    | Timer Compare Registers (TIMECMP0-2)                               |       |

| 14.2.8    | Timer Status Registers (TIMESTAT0-2)                               |       |

| 14.3 Op   | erational Description                                              |       |

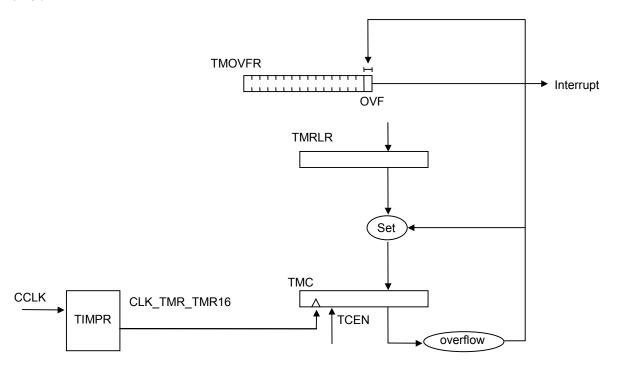

| 14.3.1    | System Timer                                                       |       |

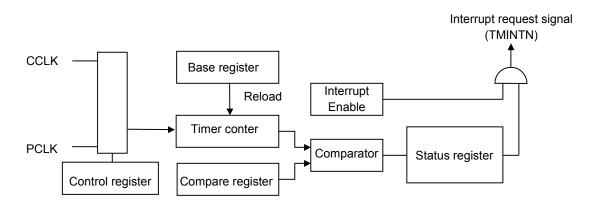

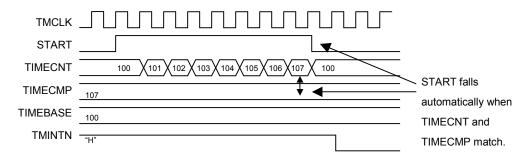

| 14.3.2    | Auto Reload Timer                                                  | 14-13 |

| 14.3.3    | Selecting a Clock and Starting the Application Timer               | 14-14 |

| Chapter 1 | 5 PWM                                                              |       |

| 15.1 Ov   | erview                                                             |       |

| 15.1.1    | Configuration                                                      |       |

| 15.1.2    | Pin List                                                           |       |

| 15.1.3    | Register List                                                      |       |

| 15.2 Re   | gister Description                                                 | 15-3  |

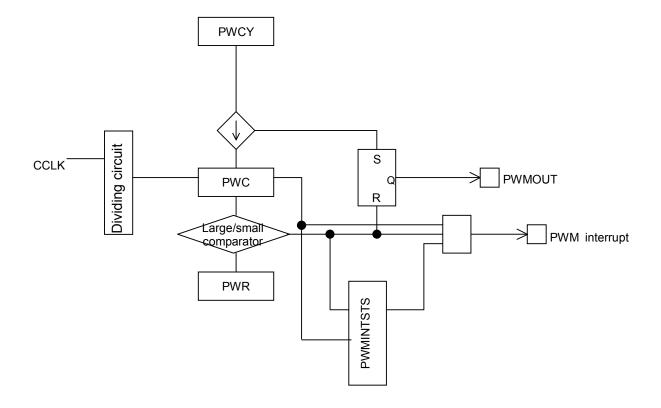

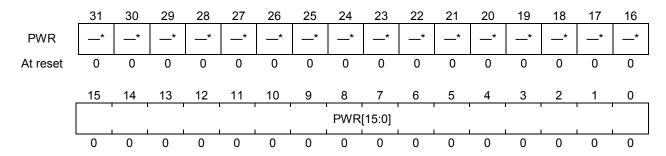

| 15.2.1    | PWM Register (PWR)                                                 |       |

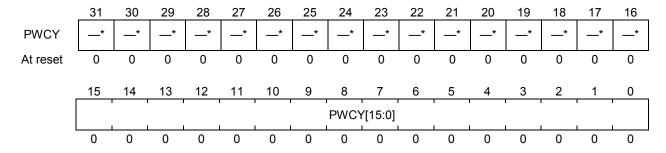

| 15.2.2    | PWM Cycle Register (PWCY)                                          |       |

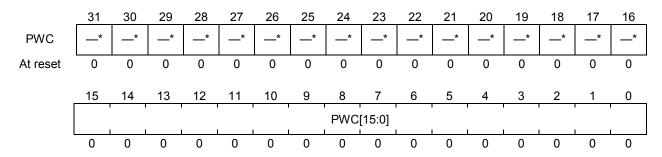

| 15.2.3    | PWM Counter (PWC)                                                  |       |

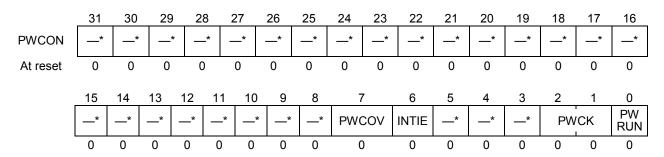

| 15.2.4    | PWM Control Register (PWCON)                                       |       |

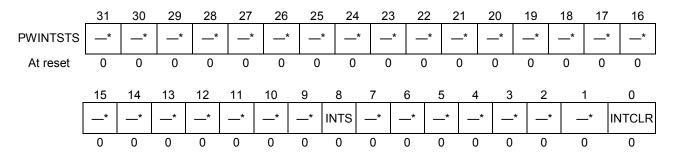

| 15.2.5    | PWM Interrupt Status Register (PWINTSTS)                           | 15-8  |

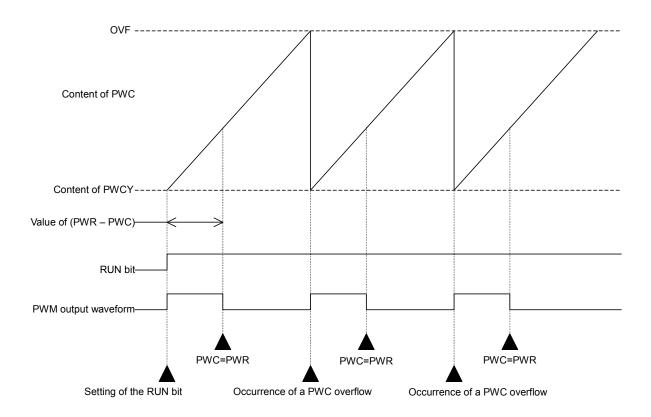

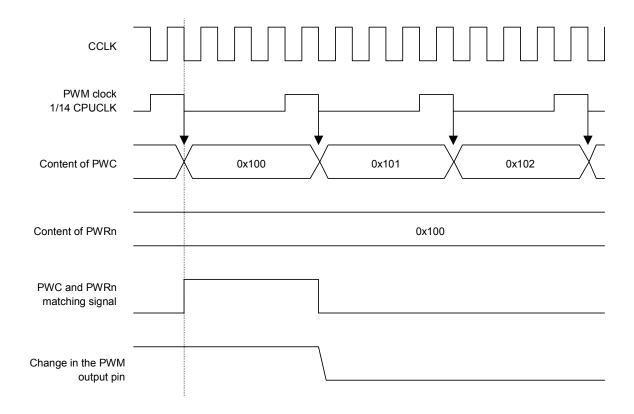

| 15.3 Op   | erational Description                                              | 15-9  |

| 15.3.1    | Operation of PWM                                                   | 15-9  |

| 15.3.2    | Operation When the Setting of the PWC/PWR/PWCY Register Is Changed |       |

|           | During a PWM Operation                                             | 15-9  |

| 15.3.3    | How to Use the PWM Module                                          |       |

| 15.3.4    | Example of Timing                                                  |       |

| Chapter 1 | 6 μPLAT-SIO (UART)                                                 |       |

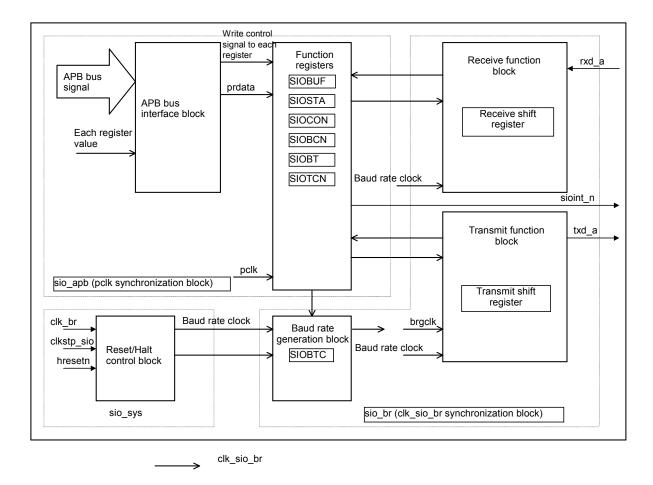

| 16.1 Ov   | erview                                                             | 16-1  |

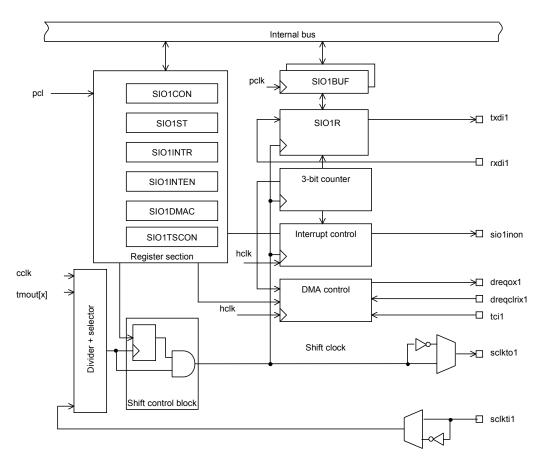

| 16.1.1    | Configuration                                                      |       |

| 16 1 2    | Din List                                                           | 16.3  |

| 16.1.3    | Control Register List                                         |       |

|-----------|---------------------------------------------------------------|-------|

| 16.2 Co   | ntrol Register Description                                    |       |

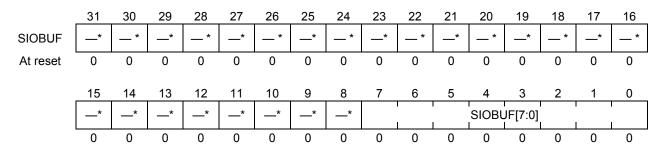

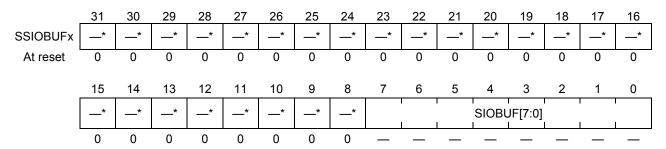

| 16.2.1    | Transmit/Receive Buffer Register (SIOBUF)                     | 16-3  |

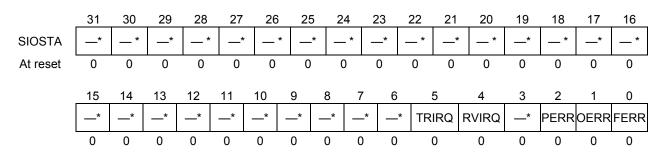

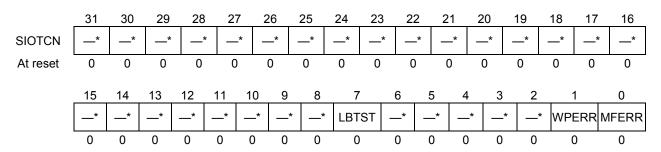

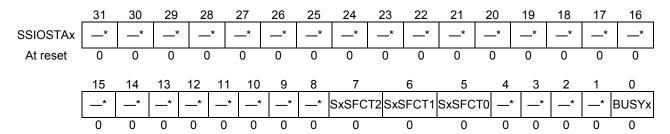

| 16.2.2    | SIO Status Register (SIOSTA)                                  | 16-4  |

| 16.2.3    | SIO Control Register (SIOCON)                                 | 16-6  |

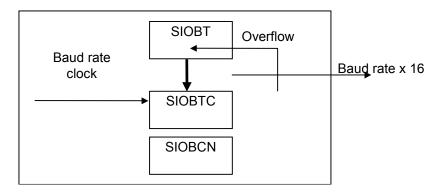

| 16.2.4    | Baud Rate Control Register (SIOBCN)                           | 16-8  |

| 16.2.5    | Baud Rate Timer Register (SIOBT)                              |       |

| 16.2.6    | SIO Test Control Register (SIOTCN)                            |       |

|           | erational Description                                         |       |

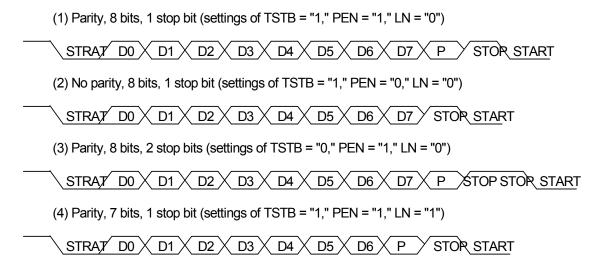

| 16.3.1    | Data Transmission                                             |       |

| 16.3.2    | Data Reception                                                |       |

| 16.3.3    | Baud Rate Clock Generation                                    |       |

| 16.3.4    | Reception Interrupt.                                          |       |

| 16.3.5    | Transmission Interrupt                                        |       |

|           | tes on Use                                                    |       |

|           |                                                               | 10-13 |

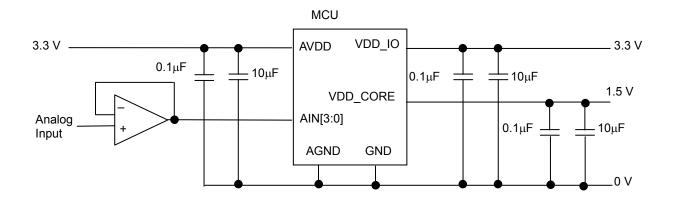

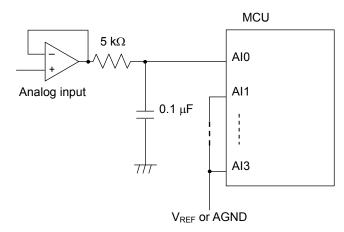

| Chapter 1 | 7 A/D Converter                                               |       |

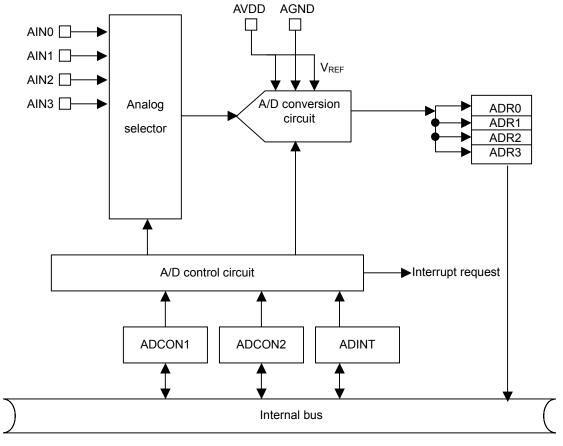

|           | erview                                                        |       |

| 17.1.1    | Configuration                                                 |       |

| 17.1.2    | Pin List                                                      |       |

| 17.1.3    | Control Register List                                         |       |

|           | ntrol Register Description                                    |       |

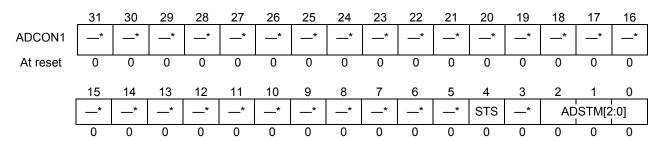

| 17.2.1    | A/D Control 1 Register (ADCON1)                               |       |

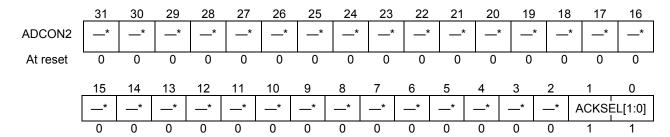

| 17.2.2    | A/D Control 2 Register (ADCON2)                               |       |

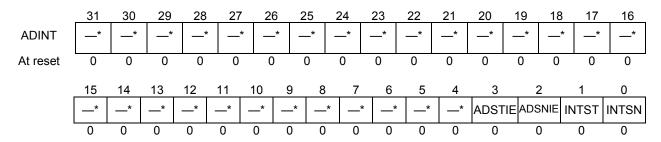

| 17.2.3    | A/D Interrupt Control Register (ADINT)                        |       |

| 17.2.4    | A/D Result (0 to 3) Registers (ADR0 to ADR3)                  |       |

| Chapter 1 | 8 Synchronous SIO                                             |       |

|           | erview                                                        | 18-1  |

| 18.1.1    | Configuration                                                 |       |

| 18.1.2    | Pin List                                                      |       |

| 18.1.3    | Control Register List                                         |       |

|           | ntrol Register Description.                                   |       |

| 18.2.1    | SSIO Transmit/Receive Buffer Registers (SSIOBUF1, SSIOBUF0)   |       |

| 18.2.1    | SSIO Transmit/Receive Buffer Registers (SSIOBOT1, SSIOBOT0)   |       |

| 18.2.3    | SSIO Transmit/Receive Status Registers (SSIOSTA1, SSIOSTA0)   |       |

| 18.2.3    | SSIO Transmit/Receive Status Registers (SSIOSTAT, SSIOSTAO)   |       |

| 18.2.4    |                                                               |       |

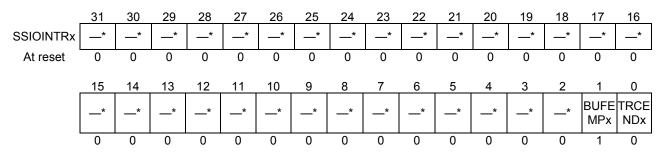

|           | SSIO Interrupt Request Registers (SSIOINTR1, SSIOINTR0)       |       |

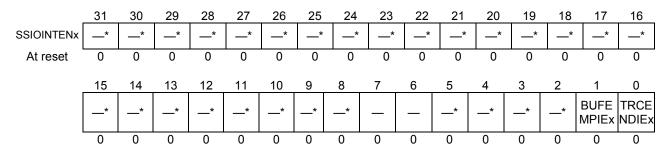

| 18.2.6    | SSIO Interrupt Enable Registers (SSIOINTEN1, SSIOINTEN0)      |       |

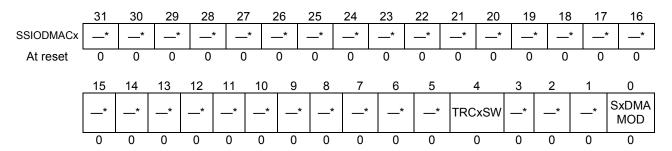

| 18.2.7    | SSIO Automatic Data Transfer Registers (SSIODMAC1, SSIODMAC0) |       |

| 18.2.8    | SSIO Test Control Registers (SSIOTSCON1, SSIOTSCON0)          |       |

|           | erational Description                                         |       |

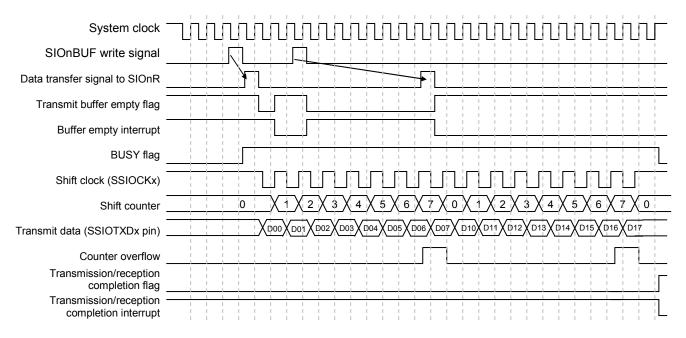

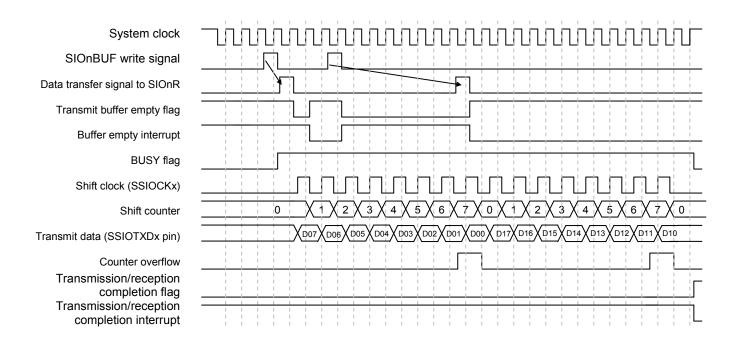

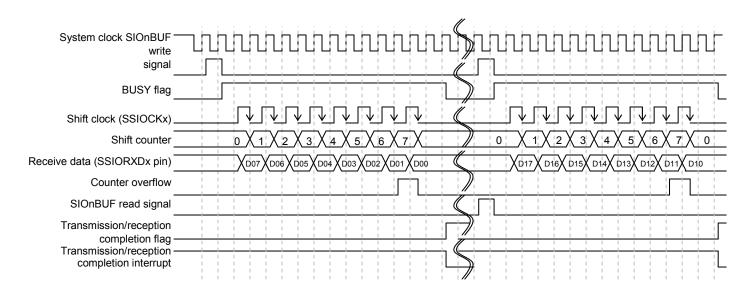

| 18.3.1    | Transmission Operation                                        |       |

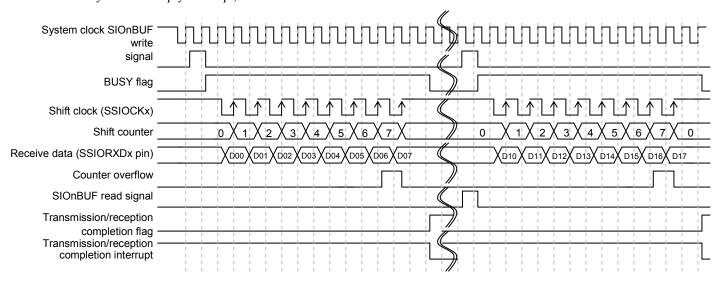

| 18.3.2    | Reception Operation                                           |       |

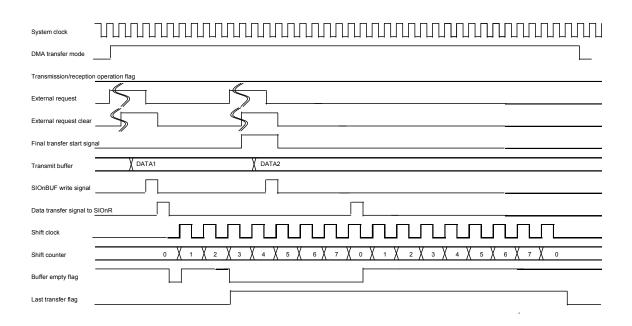

| 18.3.3    | Automatic Data Transfer Function                              | 18-16 |

| 18.3.3    |                                                               |       |

|           | on Channel 2 of Automatic Data Transfer)                      | 18-16 |

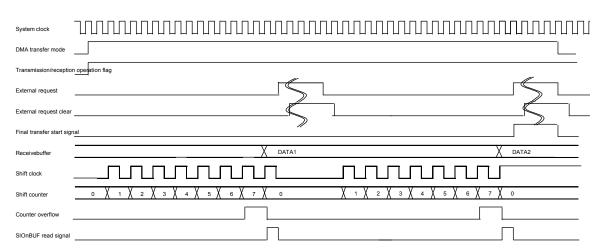

| 18.3.3    |                                                               |       |

|           | on Channel 2 of Automatic Data Transfer)                      |       |

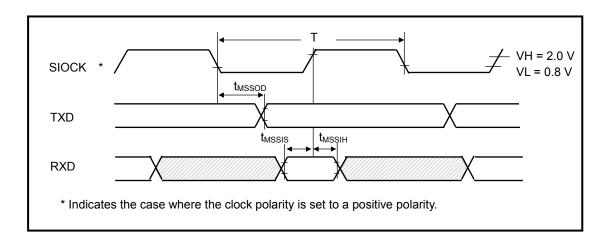

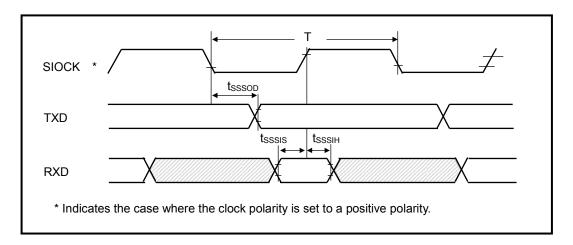

| 18.3.4    | Master Mode/Slave Mode                                        |       |

| 18.3.5    | Clock Polarity                                                | 18-19 |

| 18.3.6    | Timer Overflow Baud Rate Formula                              | 18-19 |

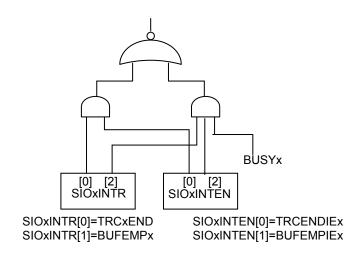

| 18.3.7    | About Interrupts                                              | 18-20 |

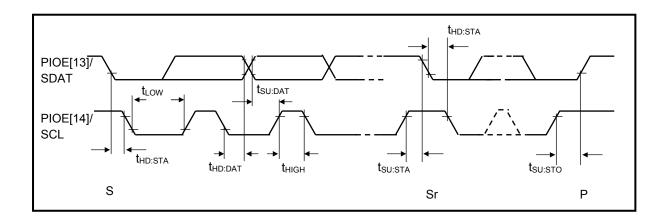

| Chapter 1 | 9 I2C                                                                  |       |

|-----------|------------------------------------------------------------------------|-------|

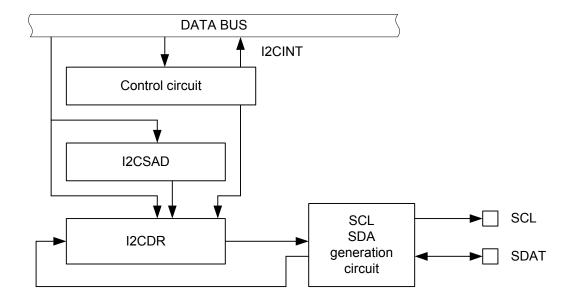

| 19.1 Ov   | erview                                                                 | 19_   |

| 19.1.1    | Configuration                                                          |       |

| 19.1.2    | Pin List                                                               |       |

| 19.1.3    | Control Register List                                                  |       |

|           | ntrol Register Description.                                            |       |

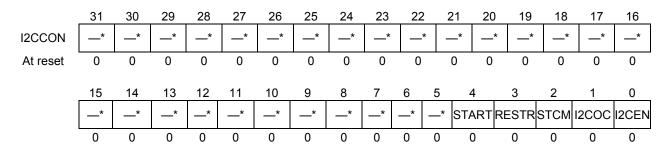

| 19.2.1    | I2C Bus Control Register (I2CCON)                                      |       |

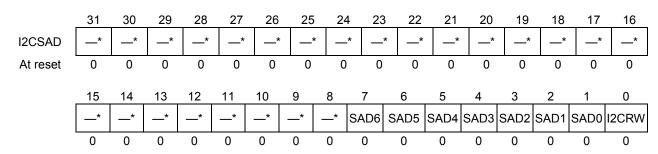

| 19.2.2    | I2C Bus Slave Address Mode Setting Register (I2CSAD)                   |       |

| 19.2.3    | I2C Bus Transfer Speed Setting Register (I2CCLR)                       |       |

| 19.2.4    | I2C Bus Status Register (I2CSR)                                        |       |

| 19.2.5    | I2C Bus Interrupt Request Register (I2CIR)                             |       |

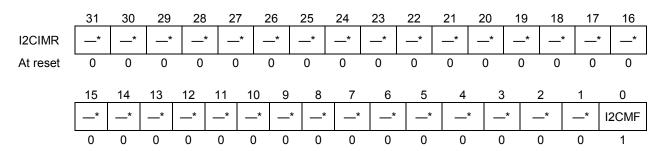

| 19.2.6    | I2C Bus Interrupt Mask Register (I2CIMR)                               |       |

| 19.2.7    | I2C Bus Transmit/Receive Data Setting Register (I2CDR)                 |       |

|           | erational Description                                                  |       |

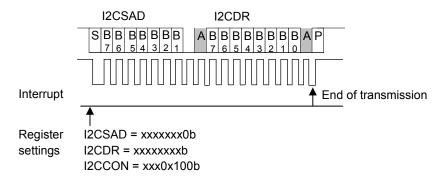

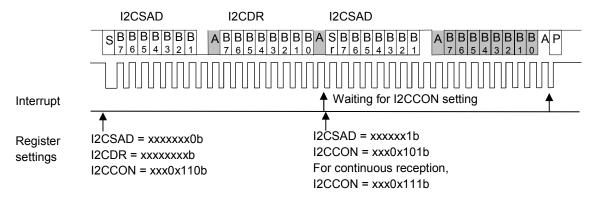

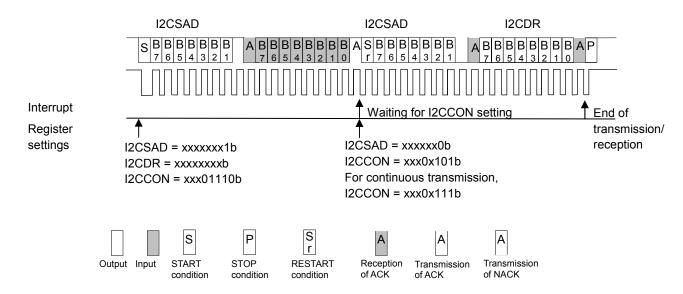

| 19.3.1    | When Transmitting 1-Byte Data                                          |       |

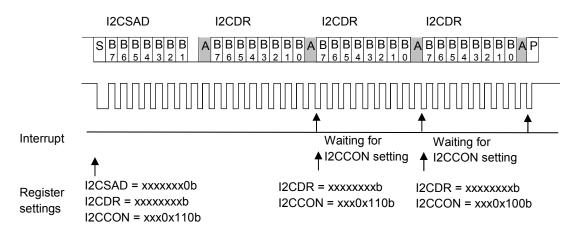

| 19.3.2    | When Transmitting Data of Two or More Bytes.                           |       |

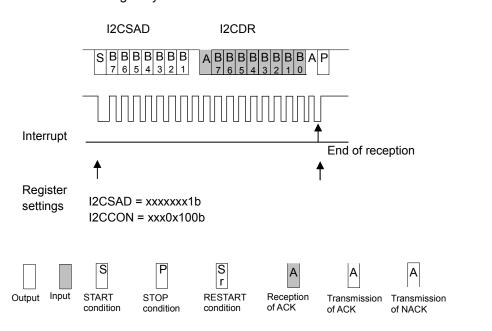

| 19.3.3    | When Receiving 1-Byte Data.                                            |       |

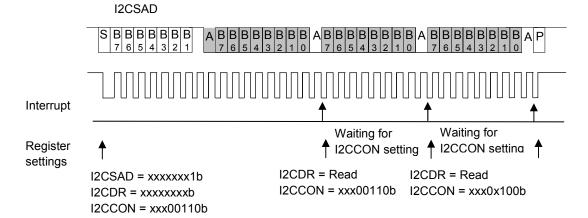

| 19.3.4    | When Receiving Data of Two or More Bytes.                              |       |

| 19.3.5    | When Continuously Receiving 1-Byte Data After Transmitting 1-Byte Data |       |

| 19.3.6    | When Continuously Transmitting 1-Byte Data After Receiving 1-Byte Data |       |

| 17.3.0    | when continuously transmitting I byte bata rater receiving I byte bata |       |

| Chapter 2 | O RTC                                                                  |       |

|           |                                                                        |       |

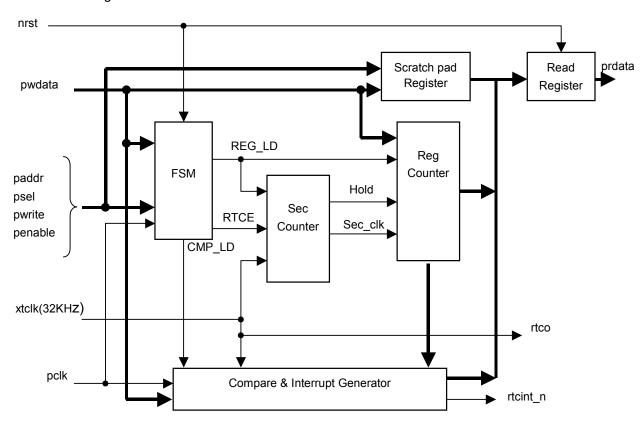

| 20.1 Ov   | erview                                                                 |       |

| 20.1.1    | Configuration                                                          |       |

| 20.1.2    | Pin List                                                               | 20-2  |

| 20.1.3    | Control Register List                                                  | 20-2  |

| 20.2 Co   | ntrol Register Description                                             | 20-3  |

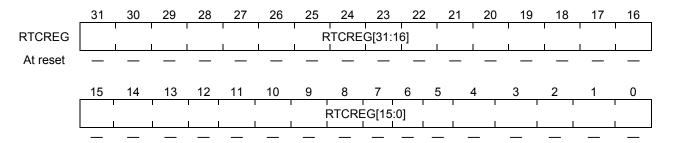

| 20.2.1    | RTC Register (RTCREG)                                                  | 20-3  |

| 20.2.2    | RTC Control Register (RTCCON)                                          | 20-4  |

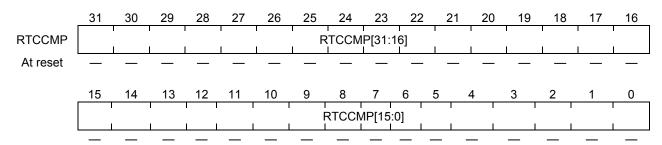

| 20.2.3    | RTC Compare Register (RTCCMP)                                          | 20-   |

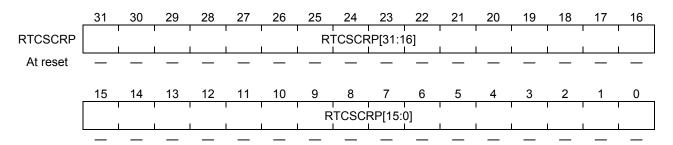

| 20.2.4    | RTC Scratch Pad Register (RTCSCRP)                                     | 20-0  |

| 20.2.5    | RTC Status Register (RTCST)                                            | 20-   |

| 20.3 Op   | erational Description                                                  |       |

| 20.3.1    | RTC Function.                                                          |       |

| 20.3.2    | Write Protect                                                          |       |

| 20.3.3    | Access Restrictions on the RTC.                                        |       |

| 20.3.4    | Note on Successive Accesses to Registers                               |       |

| 20.5.1    | The off Buccessive Treesses to Tregisters                              | 20    |

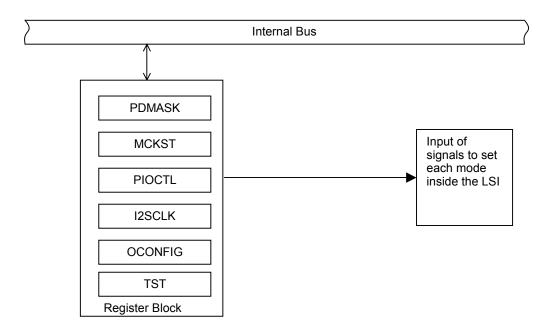

| Chapter 2 | 21 Configuration Registers                                             |       |

| 21.1 Ov   | erview                                                                 | 21-   |

| 21.1.1    | Configuration                                                          |       |

| 21.1.2    | Pin List                                                               |       |

| 21.1.3    | Configuration Register List                                            |       |

|           | gister Description                                                     |       |

| 21.2 RC   | Power Down Mask Register (PDMASK)                                      |       |

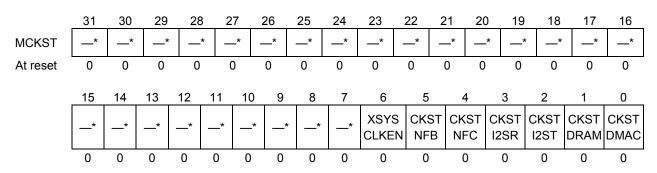

| 21.2.1    | Module Clock Stop Register (MCKST)                                     |       |

| 21.2.2    | PIO Pin Switching Register (PIOCTL)                                    |       |

|           |                                                                        |       |

| 21.2.4    | I2S Control Register (I2SCNTL)                                         |       |

| 21.2.5    | OTHER Configuration Register (OCONFIG).                                |       |

| 21.2.6    | Test Register (TST)                                                    | 21-12 |

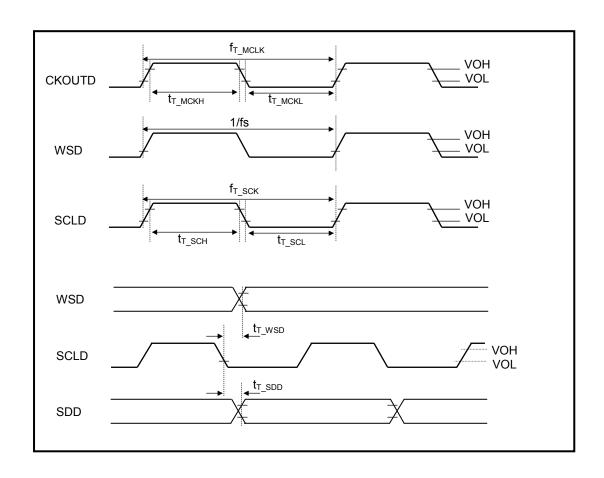

| Chapter 2 | 22 I2S Transmission                                                    |       |

| 22.1 Ov   | erview                                                                 | 22-   |

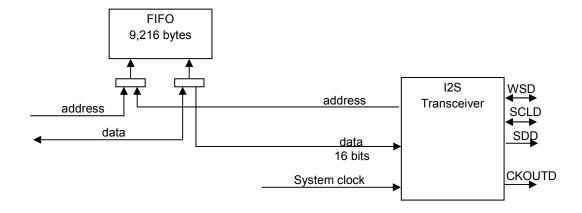

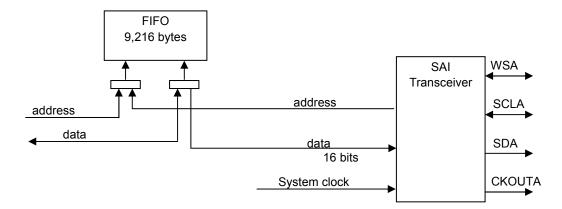

|           | Configuration                                                          | 22-   |

| 22.1.2    | List of Pins                                                            | 22_1  |

|-----------|-------------------------------------------------------------------------|-------|

| 22.1.2    | List of Control Registers                                               |       |

|           | ntrol Registers                                                         |       |

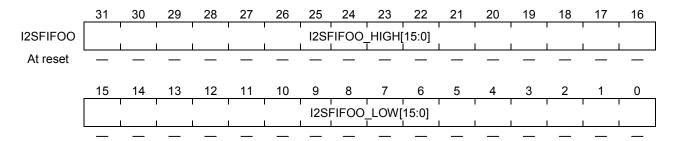

| 22.2.1    | I2S Transceiver FIFO Register (I2SFIFOO)                                |       |

| 22.2.2    | I2S Transceiver Control Register 0 (I2SCONO0)                           |       |

| 22.2.3    | I2S Transceiver Control Register 1 (I2SCONO1)                           |       |

| 22.2.4    | I2S Transceiver Almost Full Threshold Value Setting Register (I2SAFRO)  |       |

| 22.2.5    | I2S Transceiver Almost Empty Threshold Value Setting Register (I2SAERO) |       |

| 22.2.6    | I2S Transceiver Interrupt Mask Register (I2SIMRO)                       |       |

| 22.2.7    | I2S Transceiver Interrupt Status Register (I2SISTO)                     |       |

| 22.2.8    | I2S Transceiver FIFO Write Address Register (I2SWADRO)                  |       |

| 22.2.9    | I2S Transceiver FIFO Read Address Register (2SRADRO)                    |       |

|           | I2S Transceiver FIFO Occupied Data Size Register (I2SDNOO)              |       |

|           | erational Description                                                   |       |

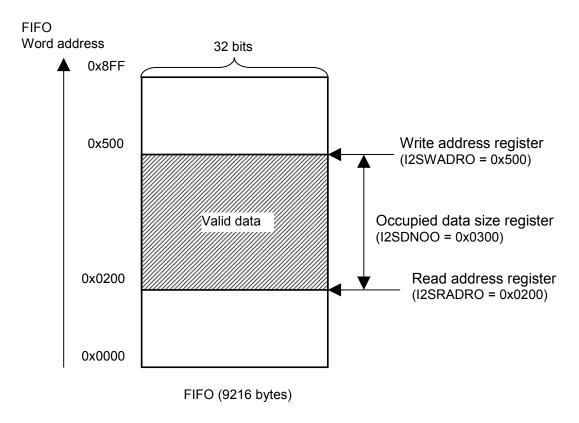

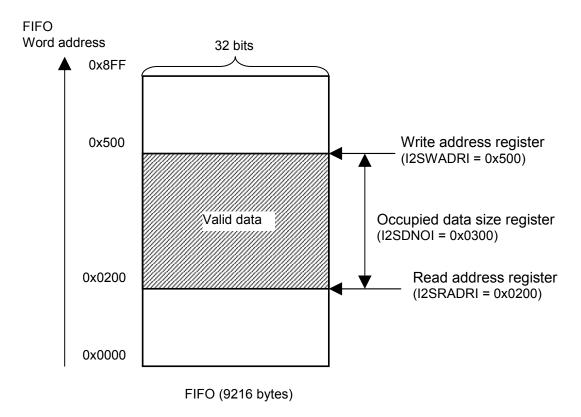

| 22.3.1    | FIFO Memory                                                             |       |

| 22.3.2    | Single-Port SRAM Access Contention between I2S and APB bus              |       |

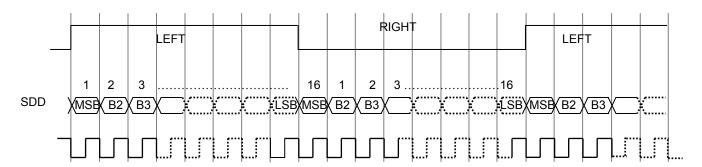

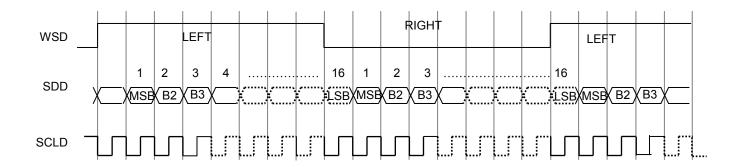

| 22.3.3    | Serial Data Format                                                      |       |

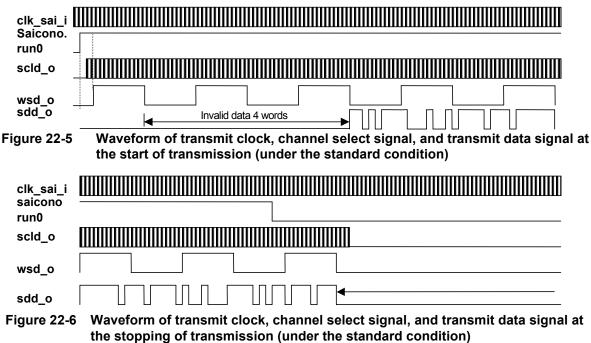

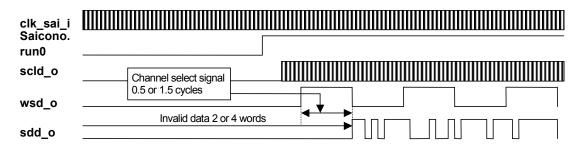

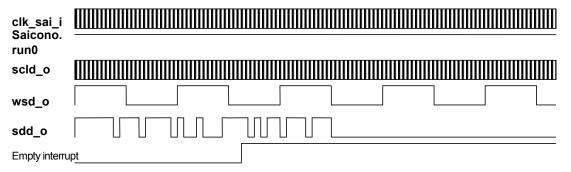

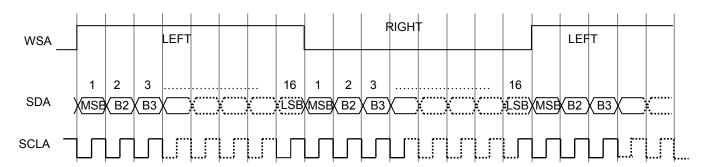

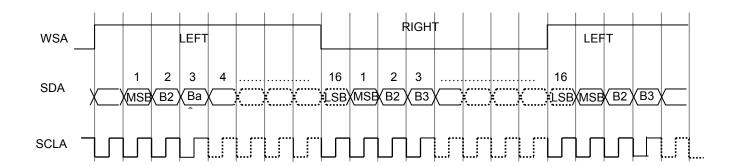

| 22.3.4    | Transmit/Receive Timing Diagrams                                        |       |

|           |                                                                         |       |

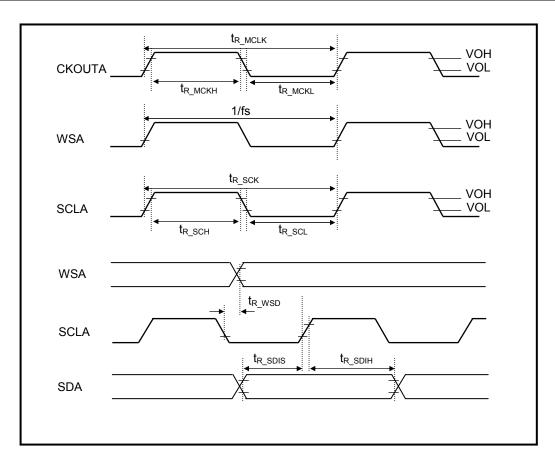

| Chapter 2 | 3 I2S Reception                                                         |       |

| 23.1 Ove  | erview                                                                  | 23-1  |

| 23.1.1    | Configuration                                                           |       |

| 23.1.2    | Pin List                                                                |       |

| 23.1.3    | Control Register List                                                   |       |

|           | ntrol Registers                                                         |       |

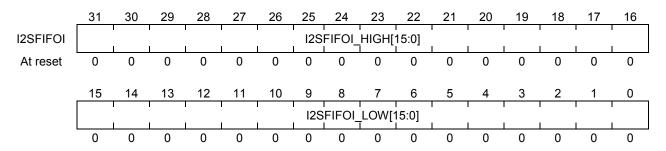

| 23.2.1    | I2S Receiver FIFO Register (I2SFIFOI)                                   |       |

| 23.2.2    | I2S Receiver Control Register 0 (I2SCONI0)                              |       |

| 23.2.3    | I2S Receiver Control Register 1 (I2SCONI1)                              |       |

| 23.2.4    | I2S Receiver Almost Full Threshold Value Setting Register (I2SAFRI)     |       |

| 23.2.5    | I2S Receiver Almost Empty Threshold Value Setting Register (I2SAERI)    |       |

| 23.2.6    | I2S Receiver Interrupt Mask Register (I2SIMRI)                          |       |

| 23.2.7    | I2S Receiver Interrupt Status Register (I2SISTI)                        |       |

| 23.2.8    | I2S Receiver FIFO Write Address Register (I2SWADRI)                     |       |

| 23.2.9    | I2S Receiver FIFO Read Address Register (I2SRADRI)                      |       |

| 23.2.10   | I2S Receiver FIFO Occupied Data Size Register (I2SDNOI)                 |       |

|           | erational Description                                                   |       |

| 23.3.1    | FIFO Memory                                                             |       |

| 23.3.2    | Single-port SRAM Access Contention between I2S and APB bus              | 23-14 |

| 23.3.3    | Serial Data Format                                                      |       |

| C1        | A MANDEL L.C. + II                                                      |       |

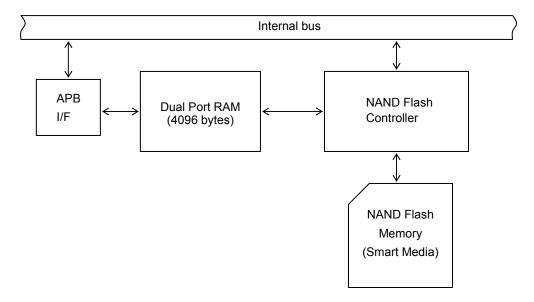

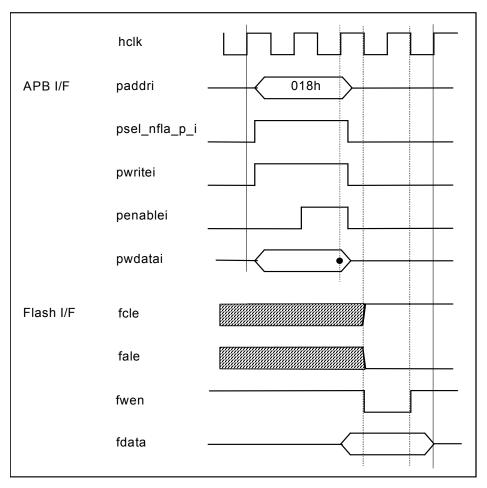

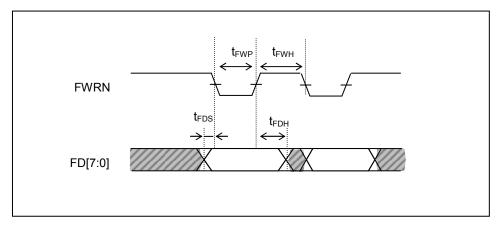

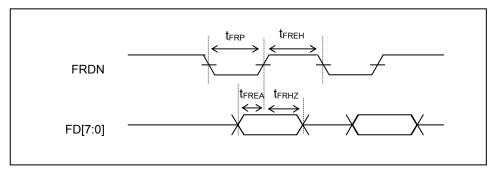

| Chapter 2 | 4 NAND Flash Controller                                                 |       |

| 24.1 Ove  | erview                                                                  |       |

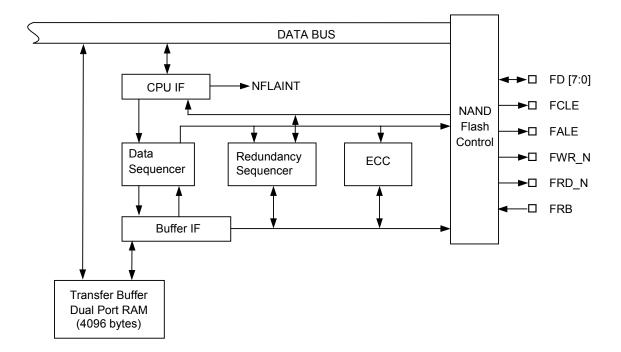

| 24.1.1    | Configuration                                                           | 24-2  |

| 24.1.2    | Pin List                                                                | 24-3  |

| 24.1.3    | Control Register List                                                   | 24-3  |

| 24.2 Co   | ntrol Register Description                                              | 24-5  |

| 24.2.1    | Media Bank Register (MBANK)                                             |       |

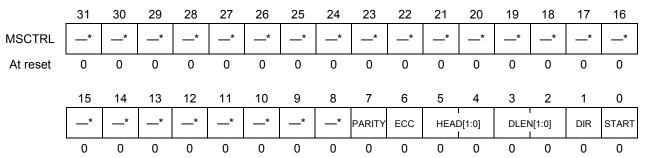

| 24.2.2    | Media Sequencer Control Register (MSCTRL)                               | 24-7  |

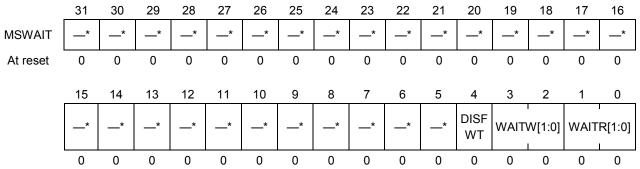

| 24.2.3    | Media Sequencer Wait Register (MSWAIT)                                  |       |

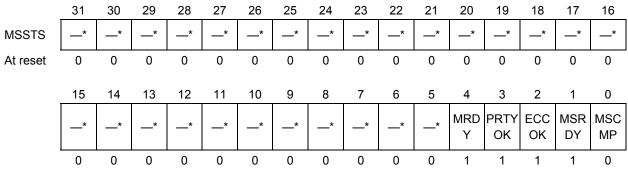

| 24.2.4    | Media Sequencer Status Register (MSSTS)                                 |       |

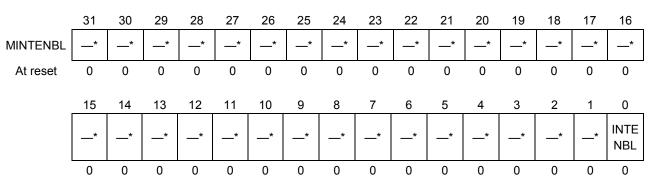

| 24.2.5    | Media Sequencer Interrupt Enable Register (MINTENBL)                    |       |

| 24.2.6    | Media Sequencer Error Status Register (MSERR)                           |       |

| 24.2.7    | Media Command Register (MMCMD)                                          |       |

| 24.2.8    | Media Address Register (MMADR)                                          |       |

| 24.2.9    | Media Select Register (MMSEL)                                           |       |

| 24.2.10   | Media Data Read Control Register (MMRDCTL)                              |       |

| 24.2.11   | Media Section Option Register (MOPTION)                                 | 24-19 |

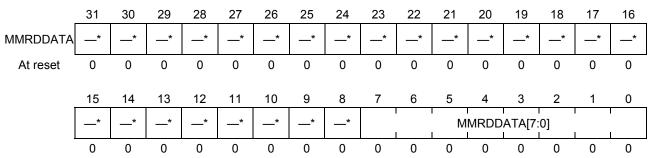

| 24.2.12 Media Section Read Data Storage Register (MMRDDATA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 24-20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

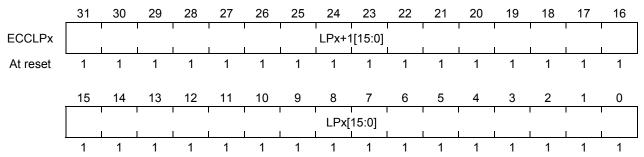

| 24.2.13 ECC Line Parity Register x (ECCLPx) (x = 1, 3, 5, 7)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

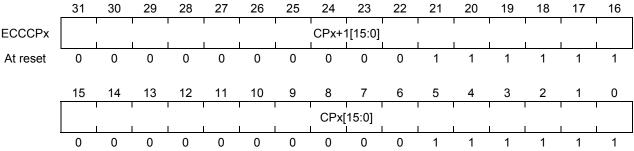

| 24.2.14 ECC Column Parity Register x (ECCCPx) (x = 1, 3, 5, 7)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

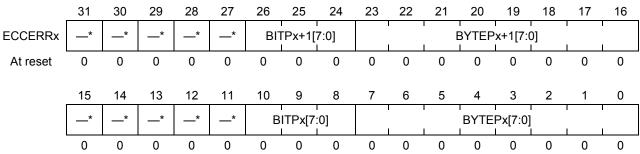

| 24.2.15 ECC Error Pointer Register x (ECCERRx) (x = 1, 3, 5, 7)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

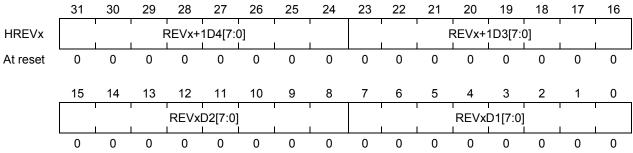

| 24.2.16 Redundancy Part Reserve Data Register x (HREVx) (x = 1, 3, 5, 7)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |