8-bit Microcontroller with a Built-in LCD driver

### **GENERAL DESCRIPTION**

This LSI is a high-performance 8-bit CMOS microcontroller into which rich peripheral circuits, such as synchronous serial port, UART, I2C bus interface (master), melody driver, battery level detect circuit, RC oscillation type A/D converter, and LCD driver, are incorporated around 8-bit CPU nX-U8/100.

The CPU nX-U8/100 is capable of efficient instruction execution in 1-instruction 1-clock mode by 3-stage pipe line architecture parallel processing. The Mask ROM is installed and is most suitable for battery-driven applications.

### FEATURES

- CPU

- 8-bit RISC CPU (CPU name: nX-U8/100)

- Instruction system: 16-bit instructions

- Instruction set: Transfer, arithmetic operations, comparison, logic operations, multiplication/division, bit manipulations, bit logic operations, jump, conditional jump, call return stack manipulations, arithmetic shift, and so on

- Minimum instruction execution time 30.5 μs (@32.768 kHz system clock) 0.24 4μs (@4.096 MHz system clock)

- Internal memory

- Internal 48KByte Mask ROM (24K×16 bits) (including unusable 1KByte TEST area)

- Internal 3KByte Data RAM (3072×8 bits), 1KByte Display Allocation RAM (1024 x 8bit)

- Internal 192-byte RAM for display

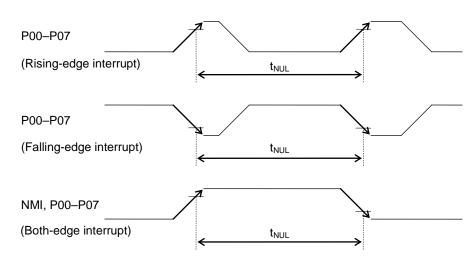

- Interrupt controller

- 2 non-maskable interrupt sources (Internal source: 1, External source: 1)

- 27 maskable interrupt sources (Internal sources: 19, External sources: 8)

- Time base counter

- Low-speed time base counter ×1 channel Frequency compensation (Compensation range: Approx. –488ppm to +488ppm. Compensation accuracy: Approx. 0.48ppm)

- High-speed time base counter ×1 channel

- Watchdog timer

- Non-maskable interrupt and reset

- Free running

- Overflow period: 4 types selectable (125ms, 500ms, 2s, and 8s)

- Timers

- 8 bits × 2 channels (16-bit configuration available)

- 1 kHz timer

- 10 Hz/1 Hz interrupt function

FEDL610429-05

Issue Date: Apr.24, 2015

- PWM

- Resolution 16 bits  $\times$  3 channel

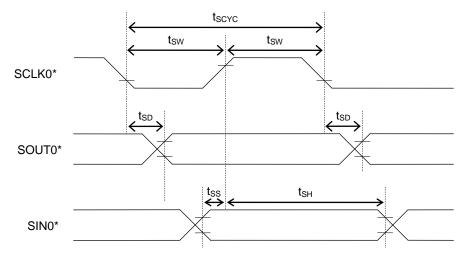

- Synchronous serial port

- Master/slave selectable

- LSB first/MSB first selectable

- 8-bit length/16-bit length selectable

- Timer interrupt is used as a serial clock and selection is possible

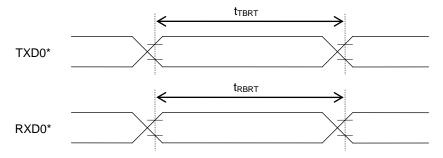

- UART

- TXD/RXD  $\times$  1 channel

- Bit length, parity/no parity, odd parity/even parity, 1 stop bit/2 stop bits

- Positive logic/negative logic selectable

- Built-in baud rate generator

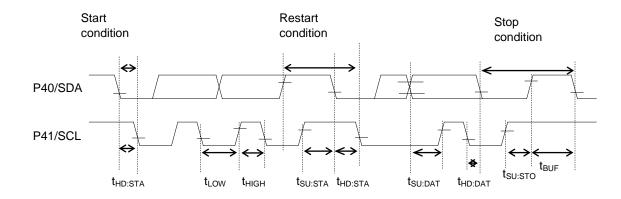

- I<sup>2</sup>C bus interface

- Master function only

- Fast mode (400 kbps@4MHz), standard mode (100 kbps@4MHz, 50kbps@500kHz)

- Melody driver

- Scale: 29 types (Melody sound frequency: 508 Hz to 32.768 kHz)

- Tone length: 63 types

- Tempo: 15 types

- Buzzer output mode (4 output modes, 8 frequencies, 16 duty levels)

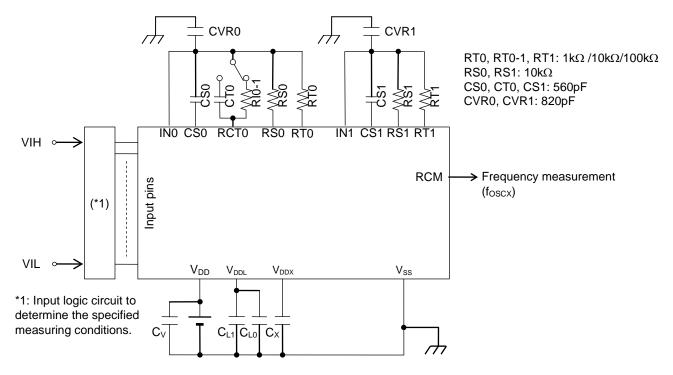

- RC oscillation type A/D converter

- 24-bit counter

- Time division  $\times$  2 channels

- General-purpose ports

- Non-maskable interrupt input port  $\times$  1 channel

- Input-only port  $\times$  10 channels (including secondary functions)

- Output-only port  $\times$  3 channels (including secondary functions)

- Input/output port: 20 channels (including secondary functions)

# • LCD driver

- Dot matrix can be supported: 512 dots max. (64 seg  $\times$  8 com), 1/1 to 1/8 duty

- 1/3 or 1/4 bias (built-in bias generation circuit)

- Frame frequency selectable (approx. 32Hz, 64 Hz, 73 Hz, 85 Hz, and 102 Hz)

- Bias voltage multiplying clock selectable (8 types)

- Contrast adjustment (1/3 bias: 32 steps, 1/4 bias: 20 steps)

- LCD drive stop mode, LCD display mode, all LCDs on mode, and all LCDs off mode selectable

- Programmable display allocation function (available only when  $1/1 \sim 1/8$  duty is selected)

# • Reset

- Reset through the RESET\_N pin

- Power-on reset generation when powered on

- Reset when oscillation stop of the low-speed clock is detected

- Reset by the watchdog timer (WDT) overflow

- Power supply voltage detect function

- Judgment voltages: One of 16 levels

- Judgment accuracy: ±2% (Typ.)

- Clock

- Low-speed clock: (This LSI can not guarantee the operation without low-speed clock) Crystal oscillation (32.768 kHz)

- High-speed clock: Built-in RC oscillation (2M/500kHz) Built-in PLL oscillation (8.192 MHz), crystal/ceramic oscillation (4.096 MHz), external clock

Selection of high speed clock mode by software:

- Selection of high-speed clock mode by software:

Built-in RC oscillation, built-in PLL oscillation, crystal/ceramic oscillation, external clock

- Power management

- HALT mode: Instruction execution by CPU is suspended (peripheral circuits are in operating states).

- STOP mode: Stop of low-speed oscillation and high-speed oscillation (Operations of CPU and peripheral circuits are stopped.)

- Clock gear: The frequency of high-speed system clock can be changed by software (1/1, 1/2, 1/4, or 1/8 of the oscillation clock)

- Block Control Function: Power down (reset registers and stop clock supply) the circuits of unused peripherals.

- Guaranteed operating range

- Operating temperature: –20°C to 70°C

- Operating voltage:  $V_{DD} = 1.1V$  to 3.6V

# • Product name – Supported Function

The line-up of the ML610Q429 is below.

| - Chip (Die) - | ROM type | Operating temperature | Product availability |

|----------------|----------|-----------------------|----------------------|

| ML610429-xxxWA | Mask ROM | -20°C to +70°C        | Yes                  |

xxx: ROM code number (xxx of the blank product is NNN) WA: Chip

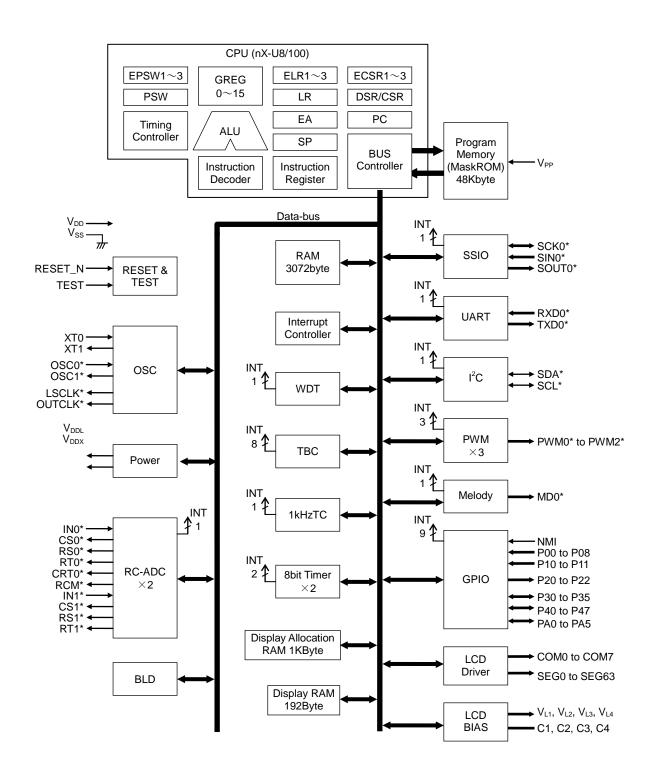

#### BLOCK DIAGRAM ML610429 Block Diagram

Figure 2 show the block diagram of the ML610429. "\*" indicates the secondary function of each port.

Figure 1 ML610429 Block Diagram

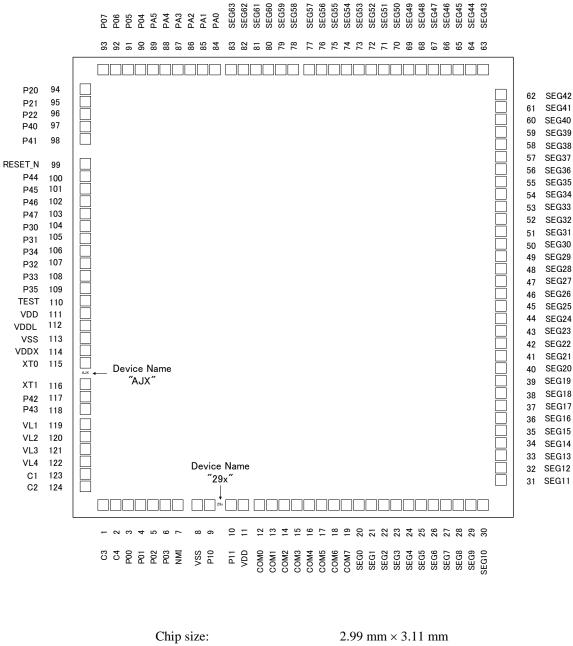

#### ML610429 Chip Dimension

PAD count:124 pinsMinimum PAD pitch: $80 \ \mu m$ PAD aperture: $70 \ \mu m \times 70 \ \mu m$ Chip thickness: $350 \ \mu m$ Voltage of the rear side of chip: $V_{ss}$  level

#### Figure 2 ML610429 Chip Dimension

Note:

Figure 6 is an image figure of the order of PAD, and it differs from an actual image. Refer to the PAD coordinate for detailed arrangement.

A chip angle can be checked by the distinguishing mark of three figures.

#### PIN LIST

| PAD No. |                            | Prima | ary function                                                                        | S        | Secor | ndary function         |          | Tert | tiary function |

|---------|----------------------------|-------|-------------------------------------------------------------------------------------|----------|-------|------------------------|----------|------|----------------|

| 429     | Pin name                   | I/O   | Function                                                                            | Pin name | -     | Function               | Pin name |      | Function       |

| 8,113   | Vss                        | _     | Negative power supply<br>pin                                                        |          | _     | _                      | _        |      | _              |

| 11,111  | V <sub>DD</sub>            | _     | Positive power supply pin                                                           |          | _     | _                      | _        |      | _              |

| 112     | V <sub>DDL</sub>           |       | Power supply pin for<br>internal logic (internally<br>generated)                    | _        |       | _                      | _        | _    | _              |

| 114     | V <sub>DDX</sub>           | _     | Power supply pin for<br>low-speed oscillation<br>(internally generated)             |          |       | _                      | _        | _    | _              |

| 119     | V <sub>L1</sub>            |       | Power supply pin for<br>LCD bias (internally<br>generated)                          | _        | —     | —                      | _        | _    | —              |

| 120     | V <sub>L2</sub>            |       | Power supply pin for<br>LCD bias (internally<br>generated)                          | _        | —     | _                      | _        |      | _              |

| 121     | V <sub>L3</sub>            | —     | Power supply pin for<br>LCD bias (internally<br>generated)                          | _        | _     | _                      | _        |      | _              |

| 122     | V <sub>L4</sub>            |       | Power supply pin for<br>LCD bias (internally<br>generated)                          |          | _     | _                      | _        |      |                |

| 123     | C1                         | _     | Capacitor connection<br>pin for LCD bias<br>generation                              | _        | _     | _                      | —        | —    | _              |

| 124     | C2                         | —     | Capacitor connection<br>pin for LCD bias<br>generation                              | _        | _     | _                      | —        | —    | _              |

| 1       | C3                         | —     | Capacitor connection<br>pin for LCD bias<br>generation                              | _        | —     |                        | —        | _    | _              |

| 2       | C4                         | —     | Capacitor connection<br>pin for LCD bias<br>generation                              | _        | _     | _                      | —        | _    | _              |

| 110     | TEST                       | I/O   | Input/output pin for testing                                                        | _        | —     |                        | —        | —    | _              |

| 99      | RESET_N                    | Ι     | Reset input pin                                                                     |          | —     | —                      |          | —    | —              |

| 115     | XT0                        | I     | Low-speed clock<br>oscillation pin                                                  | _        | _     |                        | _        | —    |                |

| 116     | XT1                        | 0     | Low-speed clock<br>oscillation pin                                                  |          | —     |                        | —        | —    |                |

| 7       | NMI                        | Ι     | Non-maskable interrupt<br>pin                                                       | —        | —     | —                      | —        | —    | _              |

| 3       | P00/EXI0                   | I     | Input port, External<br>interrupt 0 input                                           |          | _     |                        | _        | —    |                |

| 4       | P01/EXI1                   | I     | Input port, External<br>interrupt 1 input                                           |          | —     | _                      | —        | —    | _              |

| 5       | P02/EXI2<br>/RXD0<br>/P2CK | I     | Input port, External<br>interrupt 2, UART0<br>receive, PWM2<br>external clock input |          | _     | _                      |          |      | _              |

| 6       | P03/EXI3                   | I     | Input port, External<br>interrupt 3                                                 | _        |       | _                      | _        |      | _              |

| 90      | P04/EXI4                   | I/O   | Input port, External<br>interrupt 4                                                 | _        | _     | _                      | _        |      | _              |

| 91      | P05/EXI5                   | I/O   | Input port, External<br>interrupt 5                                                 | _        | _     | —                      | —        | —    | —              |

| 92      | P06/EXI6                   | I/O   | Input port, External<br>interrupt 6                                                 |          |       | —                      | _        |      | _              |

| 93      | P07/EXI7                   | I/O   | Input port, External<br>interrupt 7                                                 |          | _     | _                      |          | —    |                |

| 9       | P10                        | I     | Input port                                                                          | OSC0     | I     | High-speed oscillation | —        | —    | —              |

| PAD No. | D. Primary function |     |                                                                    | Secondary function |     |                                                             |          | Tertiary function |                            |  |

|---------|---------------------|-----|--------------------------------------------------------------------|--------------------|-----|-------------------------------------------------------------|----------|-------------------|----------------------------|--|

| 429     | Pin name            | 1/0 | Function                                                           | Pin name           | 1/0 | Function                                                    | Pin name |                   | Function                   |  |

| 10      | P11                 | 1/0 | Input port                                                         | OSC1               | 0   | High-speed oscillation                                      |          | 1/0               | T difetion                 |  |

| 94      | P20/LED0            | 0   | Output port                                                        | LSCLK              | 0   | Low-speed clock output                                      | PWM2     | 0                 | PWM2 output                |  |

| 95      | P21/LED1            | 0   | Output port                                                        | OUTCLK             | 0   | High-speed clock<br>output                                  |          |                   | _                          |  |

| 96      | P22/LED2            | 0   | Output port                                                        | MD0                | 0   | Melody output                                               | _        |                   |                            |  |

| 104     | P30                 | I/O | Input/output port                                                  | IN0                | Ι   | RC type ADC0 oscillation input pin                          | PWM2     | 0                 | PWM2 output                |  |

| 105     | P31                 | I/O | Input/output port                                                  | CS0                | 0   | RC type ADC0<br>reference capacitor<br>connection pin       | _        | _                 | _                          |  |

| 107     | P32                 | I/O | Input/output port                                                  | RS0                | 0   | RC type ADC0<br>reference resistor<br>connection pin        | _        |                   | _                          |  |

| 108     | P33                 | I/O | Input/output port                                                  | RT0                | 0   | RC type ADC0 resistor sensor connection pin                 |          | _                 | _                          |  |

| 106     | P34                 | I/O | Input/output port                                                  | RCT0               | 0   | RC type ADC0<br>resistor/capacitor<br>sensor connection pin | PWM0     | 0                 | PWM0 output                |  |

| 109     | P35                 | I/O | Input/output port                                                  | RCM                | 0   | RC type ADC oscillation monitor                             | PWM1     | 0                 | PWM1 output                |  |

| 97      | P40                 | I/O | Input/output port                                                  | SDA                | I/O | I <sup>2</sup> C data input/output                          | SIN0     | Ι                 | SSIO data input            |  |

| 98      | P41                 | I/O | Input/output port                                                  | SCL                | I/O | I <sup>2</sup> C clock input/output                         | SCK0     | I/O               | SSIO synchronous clock     |  |

| 117     | P42                 | I/O | Input/output port                                                  | RXD0               | Ι   | UART data input                                             | SOUT0    | 0                 | SSIO data output           |  |

| 118     | P43                 | I/O | Input/output port                                                  | TXD0               | 0   | UART data output                                            | PWM0     | 0                 | PWM0 output                |  |

| 100     | P44/T02P<br>0CK     | I/O | Input/output port, Timer<br>0/Timer 2/PWM0<br>external clock input | IN1                | I   | RC type ADC1 oscillation input pin                          | SIN0     | Ι                 | SSIO0 data input           |  |

| 101     | P45/T13P<br>1CK     | I/O | Input/output port, Timer<br>1/Timer 3/PWM1<br>external clock input | CS1                | 0   | RC type ADC1<br>reference capacitor<br>connection pin       | SCK0     | I/O               | SSIO0 synchronous<br>clock |  |

| 102     | P46/T46P<br>2CK     | I/O | Input/output port,<br>PWM2 external clock<br>input                 | RS1                | 0   | RC type ADC1<br>reference resistor<br>connection pin        | SOUT0    | 0                 | SSIO0 data output          |  |

| 103     | P47                 | I/O | Input/output port                                                  | RT1                | 0   | RC type ADC1 resistor sensor connection pin                 | PWM1     | 0                 | PWM1 output                |  |

| 84      | PA0                 | I/O | Input/output port                                                  | _                  | _   | _                                                           |          | _                 |                            |  |

| 85      | PA1                 | I/O | Input/output port                                                  | _                  | —   | _                                                           | _        |                   | —                          |  |

| 86      | PA2                 | I/O | Input/output port                                                  |                    |     |                                                             |          |                   | —                          |  |

| 87      | PA3                 | I/O | Input/output port                                                  | _                  |     | _                                                           |          |                   | _                          |  |

| 88      | PA4                 | I/O | Input/output port                                                  |                    |     | _                                                           |          |                   | _                          |  |

| 89      | PA5                 | I/O | Input/output port                                                  | _                  |     |                                                             | _        | _                 |                            |  |

| 12      | COM0                | 0   | LCD common pin                                                     | _                  |     | _                                                           |          |                   |                            |  |

| 13      | COM1                | 0   | LCD common pin                                                     |                    | _   | —                                                           |          | _                 | _                          |  |

| 14      | COM2                | 0   | LCD common pin                                                     |                    | _   | —                                                           |          | _                 | _                          |  |

| 15      | COM3                | 0   | LCD common pin                                                     | _                  | _   | —                                                           | _        | _                 | _                          |  |

| 16      | COM4                | 0   | LCD common pin                                                     | _                  |     | _                                                           | _        | _                 | _                          |  |

| 17      | COM5                | 0   | LCD common pin                                                     |                    | _   |                                                             |          | _                 | _                          |  |

| 18      | COM6                | 0   | LCD common pin                                                     |                    | _   |                                                             |          | _                 |                            |  |

| 10      | COM7                | 0   | LCD common pin                                                     |                    |     |                                                             |          | _                 |                            |  |

|         | COM8                | 0   | LCD common pin                                                     |                    |     |                                                             |          | _                 |                            |  |

|         | COM9                | 0   | LCD common pin                                                     |                    |     |                                                             |          |                   |                            |  |

|         | COMI9<br>COM10      | 0   | LCD common pin                                                     |                    |     |                                                             |          |                   |                            |  |

|         | COM10<br>COM11      | 0   | LCD common pin                                                     |                    | -   |                                                             |          |                   |                            |  |

|         | COM12               | 0   | LCD common pin                                                     |                    |     |                                                             |          | _                 |                            |  |

|         |                     |     | LCD common pin                                                     |                    |     |                                                             |          |                   | —                          |  |

|         | COM13<br>COM14      | 0   | LCD common pin                                                     | _                  |     |                                                             |          |                   | —                          |  |

|         |                     |     |                                                                    |                    |     |                                                             |          |                   | —                          |  |

|         | COM15               | 0   | LCD common pin                                                     |                    | _   |                                                             |          |                   |                            |  |

|         | COM16               | 0   | LCD common pin                                                     |                    | —   |                                                             |          | —                 | —                          |  |

|         | COM17               | 0   | LCD common pin                                                     |                    | —   |                                                             |          | —                 | —                          |  |

| 429      | D'             |     |                  | 1        |     |          |          |     | tiary function |

|----------|----------------|-----|------------------|----------|-----|----------|----------|-----|----------------|

|          | Pin name       | I/O | Function         | Pin name | I/O | Function | Pin name | I/O | Function       |

|          | COM18          | 0   | LCD common pin   |          | _   |          |          |     | _              |

| _        | COM19          | 0   | LCD common pin   | _        |     | _        | _        | _   | —              |

|          | COM20          | 0   | LCD common pin   | _        |     |          | _        | _   |                |

| _        | COM21          | 0   | LCD common pin   | _        | _   | _        | _        |     |                |

|          | COM22          | 0   | LCD common pin   |          |     | _        |          | _   |                |

|          | COM23          | 0   | LCD common pin   | _        | _   | _        | _        |     |                |

| 20       | SEG0           | 0   | LCD segment pin  | _        | _   | _        | _        |     | _              |

| 21       | SEG1           | 0   | LCD segment pin  | _        | _   | _        | _        |     | _              |

| 22       | SEG2           | 0   | LCD segment pin  | _        |     | _        | _        |     | _              |

| 23       | SEG3           | 0   | LCD segment pin  | _        |     |          |          |     | _              |

| 24       | SEG4           | 0   | LCD segment pin  | _        |     |          | _        |     |                |

| 25       | SEG5           | 0   | LCD segment pin  | _        | _   |          |          |     |                |

| 26       | SEG6           | 0   | LCD segment pin  | _        | _   |          |          | _   |                |

| 27       | SEG7           | 0   | LCD segment pin  | _        | _   |          | _        |     |                |

| 28       | SEG8           | 0   | LCD segment pin  |          |     |          |          |     |                |

| 20       | SEG9           | 0   | LCD segment pin  | _        | _   |          |          | _   |                |

| 29<br>30 | SEG10          | 0   | LCD segment pin  |          |     |          |          | -   |                |

| 30<br>31 | SEG10<br>SEG11 | 0   | LCD segment pin  |          |     |          |          | _   |                |

| 31       | SEG12          | 0   | LCD segment pin  |          |     |          |          |     |                |

|          |                | 0   | LCD segment pin  |          |     |          |          |     |                |

| 33<br>34 | SEG13<br>SEG14 | 0   | LCD segment pin  |          |     |          |          | —   | —              |

|          |                | -   |                  | —        | _   |          |          | _   |                |

| 35       | SEG15          | 0   | LCD segment pin  |          | —   |          |          |     |                |

| 36       | SEG16          | 0   | LCD segment pin  | —        | —   |          |          |     | —              |

| 37       | SEG17          | 0   | LCD segment pin  |          | —   |          |          |     | —              |

| 38       | SEG18          | 0   | LCD segment pin  |          | —   |          |          |     | —              |

| 39       | SEG19          | 0   | LCD segment pin  |          | —   | —        |          |     | —              |

| 40       | SEG20          | 0   | LCD segment pin  | —        | —   |          | —        | _   | —              |

| 41       | SEG21          | 0   | LCD segment pin  | —        | —   |          |          | —   | —              |

| 42       | SEG22          | 0   | LCD segment pin  | —        | —   |          |          |     | —              |

| 43       | SEG23          | 0   | LCD segment pin  |          | —   |          |          | —   | —              |

| 44       | SEG24          | 0   | LCD segment pin  | —        | —   |          |          | _   | —              |

| 45       | SEG25          | 0   | LCD segment pin  | —        | —   |          |          | _   | —              |

| 46       | SEG26          | 0   | LCD segment pin  | —        | —   | _        | —        | —   | —              |

| 47       | SEG27          | 0   | LCD segment pin  | —        | —   | —        | —        | —   | —              |

| 48       | SEG28          | 0   | LCD segment pin  | _        | —   | _        | —        | _   | —              |

| 49       | SEG29          | 0   | LCD segment pin  | —        | —   |          | —        | _   | —              |

| 50       | SEG30          | 0   | LCD segment pin  | —        |     |          | —        | _   | —              |

| 51       | SEG31          | 0   | LCD segment pin  | —        | _   | _        | —        | _   | —              |

| 52       | SEG32          | 0   | LCD segment pin  | —        | _   | _        | —        | _   | —              |

| 53       | SEG33          | 0   | LCD segment pin  |          |     |          | —        | _   |                |

| 54       | SEG34          | 0   | LCD segment pin  |          |     |          |          |     | _              |

| 55       | SEG35          | 0   | LCD segment pin  |          | _   |          |          | _   | _              |

| 56       | SEG36          | 0   | LCD segment pin  |          | _   | _        | _        | _   |                |

| 57       | SEG37          | 0   | LCD segment pin  | _        | _   | _        | _        | _   |                |

| 58       | SEG38          | 0   | LCD segment pin  | _        | _   |          |          |     | —              |

| 59       | SEG39          | 0   | LCD segment pin  | _        | _   | _        |          | _   | —              |

| 60       | SEG40          | 0   | LCD segment pin  | _        | _   |          |          | _   |                |

| 61       | SEG41          | 0   | LCD segment pin  |          | _   |          | _        | _   |                |

| 62       | SEG42          | 0   | LCD segment pin  |          |     |          |          |     |                |

| 63       | SEG43          | 0   | LCD segment pin  | _        | _   |          | _        | _   |                |

| 64       | SEG43          | 0   | LCD segment pin  |          | _   |          |          | _   |                |

| 65       | SEG44<br>SEG45 | 0   | LCD segment pin  |          |     |          |          |     |                |

|          | 02040          |     | LOD boginent pin | I —      | ·   |          |          |     |                |

| PAD No. |          | Prima | ary function    | S        | Secor | ndary function |          | Ter | tiary function |

|---------|----------|-------|-----------------|----------|-------|----------------|----------|-----|----------------|

| 429     | Pin name | I/O   | Function        | Pin name | I/O   | Function       | Pin name | I/O | Function       |

| 67      | SEG47    | 0     | LCD segment pin |          |       | _              | _        |     | _              |

| 68      | SEG48    | 0     | LCD segment pin |          |       | _              | _        |     | _              |

| 69      | SEG49    | 0     | LCD segment pin |          | —     | _              | _        | _   | _              |

| 70      | SEG50    | 0     | LCD segment pin |          |       | _              | _        |     | _              |

| 71      | SEG51    | 0     | LCD segment pin |          |       | _              | _        |     | _              |

| 72      | SEG52    | 0     | LCD segment pin |          | —     | _              | _        | _   | _              |

| 73      | SEG53    | 0     | LCD segment pin |          |       | _              | _        |     | _              |

| 74      | SEG54    | 0     | LCD segment pin |          |       | _              | _        |     |                |

| 75      | SEG55    | 0     | LCD segment pin |          |       | _              |          |     |                |

| 76      | SEG56    | 0     | LCD segment pin |          | _     | _              |          |     | _              |

| 77      | SEG57    | 0     | LCD segment pin |          |       | _              | _        |     | _              |

| 78      | SEG58    | 0     | LCD segment pin |          |       | —              |          |     | _              |

| 79      | SEG59    | 0     | LCD segment pin |          | _     | _              |          |     |                |

| 80      | SEG60    | 0     | LCD segment pin |          |       |                |          |     |                |

| 81      | SEG61    | 0     | LCD segment pin |          |       | _              | _        |     | _              |

| 82      | SEG62    | 0     | LCD segment pin |          |       | _              |          |     |                |

| 83      | SEG63    | 0     | LCD segment pin |          |       |                | _        |     |                |

#### **PIN DESCRIPTION**

|              |        |                                                                                  | Primary/    |           |

|--------------|--------|----------------------------------------------------------------------------------|-------------|-----------|

| Pin name     | I/O    | Description                                                                      | Secondary/  | Logic     |

| 1 in name    | "0     | Description                                                                      | Tertiary    | Logic     |

| System       |        |                                                                                  | Tertiary    |           |

| RESET_N      | 1      | Reset input pin. When this pin is set to a "L" level, system reset mode is       |             | Negative  |

| RESET_N      | '      | set and the internal section is initialized. When this pin is set to a "H" level |             | Negative  |

|              |        | subsequently, program execution starts. A pull-up resistor is internally         |             |           |

|              |        | connected.                                                                       |             |           |

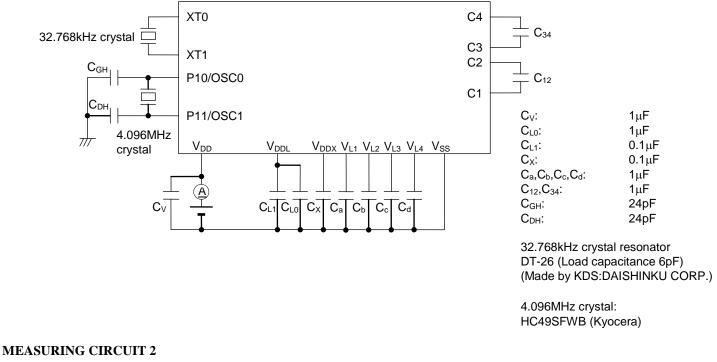

| XT0          | 1      | Crystal connection pin for low-speed clock.                                      |             |           |

| XT1          | 0      | A 32.768 kHz crystal oscillator (see measuring circuit 1) is connected to        |             |           |

|              |        | this pin. Capacitors CDL and CGL are connected across this pin and $V_{SS}$      |             |           |

|              |        | as required.                                                                     |             |           |

| OSC0         | Ι      | Crystal/ceramic connection pin for high-speed clock.                             | Secondary   |           |

| OSC1         | 0      | A crystal or ceramic is connected to this pin (4.1 MHz max.). Capacitors         | Secondary   |           |

|              |        | CDH and CGH (see measuring circuit 1) are connected across this pin              |             |           |

|              |        | and V <sub>SS</sub> .                                                            |             |           |

|              |        | This pin is used as the secondary function of the P10 pin(OSC0) and P11          |             |           |

|              |        | pin(OSC1).                                                                       |             |           |

| LSCLK        | 0      | Low-speed clock output pin. This pin is used as the secondary function of        | Secondary   | _         |

|              | _      | the P20 pin.                                                                     |             |           |

| OUTCLK       | 0      | High-speed clock output pin. This pin is used as the secondary function of       | Secondary   | _         |

| General-purp | ose in | the P21 pin.                                                                     |             |           |

| P00-P03      |        | General-purpose input port.                                                      | Drimon      | Positive  |

| P00-P03      | 1      | Since these pins have secondary functions, the pins cannot be used as a          | Primary     | Positive  |

|              |        | port when the secondary functions are used.                                      |             |           |

| P04-P07      | 1      | General-purpose input port.                                                      | Primary     | Positive  |

| F04-F07      | '      | Since these pins have secondary functions, the pins cannot be used as a          | Fiindry     | FUSILIVE  |

|              |        | port when the secondary functions are used.                                      |             |           |

| P10-P11      | 1      | General-purpose input port.                                                      | Primary     | Positive  |

| 110-111      |        | Since these pins have secondary functions, the pins cannot be used as a          | Thinary     | 1 0311100 |

|              |        | port when the secondary functions are used.                                      |             |           |

| General-purp | ose oi |                                                                                  |             |           |

| P20-P22      | 0      | General-purpose output port.                                                     | Primary     | Positive  |

| . 20 . 22    | Ũ      | Since these pins have secondary functions, the pins cannot be used as a          | 1 million y | 1 001110  |

|              |        | port when the secondary functions are used.                                      |             |           |

| General-purp | ose in | put/output port                                                                  |             |           |

| P30-P35      | I/O    | General-purpose input/output port.                                               | Primary     | Positive  |

|              |        | Since these pins have secondary functions, the pins cannot be used as a          |             |           |

|              |        | port when the secondary functions are used.                                      |             |           |

| P40-P47      | I/O    | General-purpose input/output port.                                               | Primary     | Positive  |

|              |        | Since these pins have secondary functions, the pins cannot be used as a          |             |           |

|              |        | port when the secondary functions are used.                                      |             |           |

| PA0-PA5      | I/O    | General-purpose input/output port.                                               | Primary     | Positive  |

| Pin name                     | I/O    | Description                                                                                                                                                                                                               | Primary/<br>Secondary/<br>Tertiary | Logic                 |

|------------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-----------------------|

| UART                         | 1      |                                                                                                                                                                                                                           |                                    |                       |

| TXD0                         | 0      | UART data output pin. This pin is used as the secondary function of the P43 pin.                                                                                                                                          | Secondary                          | Positive              |

| RXD0                         | I      | UART data input pin. This pin is used as the secondary function of the P42 or the primary function of the P02 pin.                                                                                                        | Primary/Se<br>condary              | Positive              |

| I <sup>2</sup> C bus interfa | ace    |                                                                                                                                                                                                                           |                                    |                       |

| SDA                          | I/O    | $I^2C$ data input/output pin. This pin is used as the secondary function of the P40 pin. This pin has an NMOS open drain output. When using this pin as a function of the $I^2C$ , externally connect a pull-up resistor. | Secondary                          | Positive              |

| SCL                          | 0      | $I^2C$ clock output pin. This pin is used as the secondary function of the P41 pin. This pin has an NMOS open drain output. When using this pin as a function of the $I^2C$ , externally connect a pull-up resistor.      | Secondary                          | Positive              |

| Synchronous                  | serial | (SSIO)                                                                                                                                                                                                                    |                                    |                       |

| SCK0                         | I/O    | Synchronous serial clock input/output pin. This pin is used as the tertiary function of the P41 or P45 pin.                                                                                                               | Tertiary                           | —                     |

| SIN0                         | I      | Synchronous serial data input pin. This pin is used as the tertiary function of the P40 or P44 pin.                                                                                                                       | Tertiary                           | Positive              |

| SOUT0                        | 0      | Synchronous serial data output pin. This pin is used as the tertiary function of the P42 or P46 pin.                                                                                                                      | Tertiary                           | Positive              |

| PWM                          |        |                                                                                                                                                                                                                           |                                    |                       |

| PWM0                         | 0      | PWM0 output pin. This pin is used as the tertiary function of the P43 or P34 pin.                                                                                                                                         | Tertiary                           | Positive              |

| T0P0CK                       | I      | PWM0 external clock input pin. This pin is used as the primary function of the P44 pin.                                                                                                                                   | Primary                            | _                     |

| PWM1                         | 0      | PWM1 output pin. This pin is used as the tertiary function of the P47 or P35 pin.                                                                                                                                         | Tertiary                           | Positive              |

| T1P1CK                       | Ι      | PWM1 external clock input pin. This pin is used as the primary function of the P45 pin.                                                                                                                                   | Primary                            | _                     |

| PWM2                         | 0      | PWM2 output pin. This pin is used as the tertiary function of the P20 or P30 pin.                                                                                                                                         | Tertiary                           | Positive              |

| P2CK                         | I      | PWM2 external clock input pin. This pin is used as the primary function of the P02 pin.                                                                                                                                   | Primary                            |                       |

| External inter               | rupt   |                                                                                                                                                                                                                           |                                    |                       |

| NMI                          | I      | External non-maskable interrupt input pin. An interrupt is generated on both edges.                                                                                                                                       | Primary                            | Positive/<br>negative |

| EXI0-7                       | Ι      | External maskable interrupt input pins. Interrupt enable and edge selection can be performed for each bit by software. These pins are used as the primary functions of the P00-P07 pins.                                  | Primary                            | Positive/<br>negative |

| Timer                        |        |                                                                                                                                                                                                                           |                                    |                       |

| T0P0CK                       | I      | External clock input pin used for Timer 0. This pin is used as the primary function of the P44 pin.                                                                                                                       | Primary                            |                       |

| T1P1CK                       | I      | External clock input pin used for Timer 1. This pin is used as the primary function of the P45 pin.                                                                                                                       | Primary                            | _                     |

| Melody                       |        |                                                                                                                                                                                                                           |                                    |                       |

| MD0                          | 0      | Melody/buzzer signal output pin. This pin is used as the secondary function of the P22 pin.                                                                                                                               | Secondary                          | Positive/<br>negative |

| LED drive                    |        |                                                                                                                                                                                                                           |                                    |                       |

| LED0-2                       | 0      | Nch open drain output pins to drive LED.                                                                                                                                                                                  | Primary                            | Positive/<br>negative |

| .ogic<br> |

|-----------|

|           |

|           |

|           |

|           |

|           |

|           |

|           |

|           |

| <u> </u>  |

|           |

|           |

|           |

|           |

| _         |

|           |

| —         |

|           |

| —         |

|           |

| _         |

|           |

| _         |

|           |

| _         |

| _         |

| _         |

|           |

| _         |

| _         |

| _         |

| _         |

| _         |

|           |

| _         |

| _         |

|           |

|           |

|           |

|           |

|           |

|           |

|           |

|           |

|           |

|           |

|           |

|           |

#### TERMINATION OF UNUSED PINS

Table 3 shows methods of terminating the unused pins.

| Pin                              | Recommended pin termination        |

|----------------------------------|------------------------------------|

| V <sub>PP</sub>                  | Open                               |

| $V_{L1}, V_{L2}, V_{L3}, V_{L4}$ | Open                               |

| C1, C2, C3, C4                   | Open                               |

| RESET_N                          | Open                               |

| TEST                             | Open                               |

| NMI                              | Open                               |

| P00 to P07                       | V <sub>DD</sub> or V <sub>SS</sub> |

| P10 to P11                       | V <sub>DD</sub>                    |

| P20 to P22                       | Open                               |

| P30 to P35                       | Open                               |

| P40 to P47                       | Open                               |

| PA0 to PA5                       | Open                               |

| COM0 to 23                       | Open                               |

| SEG0 to 63                       | Open                               |

#### Table 3 Termination of Unused Pins

Note:

It is recommended to set the unused input ports and input/output ports to the inputs with pull-down resistors/pull-up resistors or the output mode since the supply current may become excessively large if the pins are left open in the high impedance input setting.

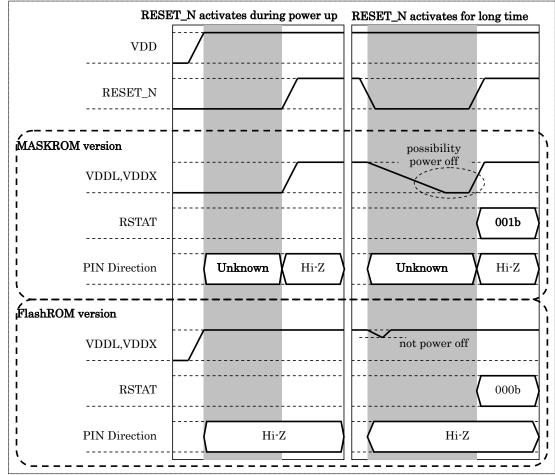

### DIFFERENCES BETWEEN MASKROM VERSION and FLASHROM VERSION

This section describes differences between ML610429 (MaskROM version) and ML610Q429 (FlashROM version).

#### PAD Number

The PAD number is changed.

In MaskROM version, VPP pin which is power supply pin for Flash ROM was deleted.

#### On-Chip debug function

There is not On-Chip debug dunction in MaskROM version.

#### Chip behavior by RESET\_N pin

The following table describes the difference of ML610429 and ML610Q428/ML610Q429 about RESET\_N.

#### Table 5 Differences of ML610429 and ML610Q428/ML610Q429 about RESET\_N

|                        | ML610429                                   | ML610Q428/ML610Q429                   |

|------------------------|--------------------------------------------|---------------------------------------|

|                        | (MaskROM version)                          | (FlashROM version)                    |

| Internal power supply  | is shutdown by RESET_N.                    | is not shutdown by RESET_N.           |

| (vddl, vddx)           |                                            | vddl and vddx keep power on.          |

| POR bit of RSTAT       | is set to "1" after negating RESET_N, if   | is set nothing.                       |

|                        | activating period is long.                 | There is no register flag by RESET_N. |

| ALL LSI pin directions | are not fixed during RESET_N is activated. | are fixed to "Z" by RESET_N.          |

|                        | After negating, those pin are fixed to "Z" |                                       |

|                        | normally.                                  |                                       |

#### Figure 7 show Chip behavior by RESET\_N pin.

Figure 7 Chip behavior by RESET\_N pin

# **ELECTRICAL CHARACTERISTICS**

# ABSOLUTE MAXIMUM RATINGS

|                        |                   |                    |                              | $(V_{SS} = 0V)$ |

|------------------------|-------------------|--------------------|------------------------------|-----------------|

| Parameter              | Symbol            | Condition          | Rating                       | Unit            |

| Power supply voltage 1 | V <sub>DD</sub>   | Ta = 25°C          | -0.3 to +4.6                 | V               |

| Power supply voltage 3 | V <sub>DDL</sub>  | Ta = 25°C          | -0.3 to +3.6                 | V               |

| Power supply voltage 4 | V <sub>DDX</sub>  | Ta = 25°C          | -0.3 to +3.6                 | V               |

| Power supply voltage 5 | V <sub>L1</sub>   | Ta = 25°C          | -0.3 to +1.75                | V               |

| Power supply voltage 6 | V <sub>L2</sub>   | Ta = 25°C          | -0.3 to +3.5                 | V               |

| Power supply voltage 7 | V <sub>L3</sub>   | Ta = 25°C          | -0.3 to +5.25                | V               |

| Power supply voltage 8 | V <sub>L4</sub>   | Ta = 25°C          | -0.3 to +7.0                 | V               |

| Input voltage          | V <sub>IN</sub>   | Ta = 25°C          | –0.3 to V <sub>DD</sub> +0.3 | V               |

| Output voltage         | V <sub>OUT</sub>  | Ta = 25°C          | –0.3 to V <sub>DD</sub> +0.3 | V               |

| Output current 1       | I <sub>OUT1</sub> | Port3–A, Ta = 25°C | -12 to +11                   | mA              |

| Output current 2       | I <sub>OUT2</sub> | Port2, Ta = 25°C   | -12 to +20                   | mA              |

| Power dissipation      | PD                | Ta = 25°C          | 122                          | mW              |

| Storage temperature    | T <sub>STG</sub>  | _                  | -55 to +150                  | °C              |

# **RECOMMENDED OPERATING CONDITIONS**

|                                                                                       |                                  |                               |             | $(V_{SS} = 0V)$ |

|---------------------------------------------------------------------------------------|----------------------------------|-------------------------------|-------------|-----------------|

| Parameter                                                                             | Symbol                           | Condition                     | Range       | Unit            |

| Operating temperature                                                                 | T <sub>OP</sub>                  |                               | -20 to +70  | °C              |

| Operating voltage                                                                     | V <sub>DD</sub>                  |                               | 1.1 to 3.6  | V               |

|                                                                                       |                                  | V <sub>DD</sub> = 1.1 to 3.6V | 30k to 36k  |                 |

| Operating frequency (CPU)                                                             | f <sub>OP</sub>                  | V <sub>DD</sub> = 1.3 to 3.6V | 30k to 650k | Hz              |

|                                                                                       |                                  | V <sub>DD</sub> = 1.8 to 3.6V | 30k to 4.2M |                 |

| Capacitor externally connected to                                                     | C <sub>L0</sub>                  |                               | 1.0±30%     |                 |

| V <sub>DDL</sub> pin                                                                  | C <sub>L1</sub>                  |                               | 0.1±30%     | μF              |

| Capacitor externally connected to $V_{\text{DDX}}$ pin                                | C <sub>x</sub>                   |                               | 0.1±30%     | μF              |

| Capacitors externally connected to $V_{L1, 2, 3, 4}$ pins                             | Ca, b, c, d                      |                               | 1.0±30%     | μF              |

| Capacitors externally connected<br>across C1 and C2 pins and across<br>C3 and C4 pins | C <sub>12,</sub> C <sub>34</sub> |                               | 1.0±30%     | μF              |

# CLOCK GENERATION CIRCUIT OPERATING CONDITIONS

|                                                                                       | 01 21011110                      | 00121101                                                       |      |               |      | $(V_{SS} = 0V)$ |

|---------------------------------------------------------------------------------------|----------------------------------|----------------------------------------------------------------|------|---------------|------|-----------------|

| Demonster                                                                             | Quarteral                        | Ocardition                                                     |      | Rating        |      | 1.1             |

| Parameter                                                                             | Symbol                           | Condition                                                      | Min. | Тур.          | Max. | Unit            |

| Low-speed crystal oscillation<br>frequency                                            | f <sub>XTL</sub>                 | _                                                              |      | 32.768k       |      | Hz              |

| Recommended equivalent series<br>resistance value of low-speed<br>crystal oscillation | R∟                               | _                                                              |      | _             | 40k  | Ω               |

|                                                                                       |                                  | C <sub>L</sub> =6pF of<br>crystal<br>oscillation <sup>*2</sup> |      | 0             |      |                 |

| Low-speed crystal oscillation external capacitor <sup>*1</sup>                        | C <sub>DL</sub> /C <sub>GL</sub> | C <sub>L</sub> =9pF of<br>crystal<br>oscillation               | _    | 6             | _    | pF              |

|                                                                                       |                                  | C <sub>L</sub> =12pF of<br>crystal<br>oscillation              |      | 12            | _    |                 |

| High-speed crystal/ceramic<br>oscillation frequency                                   | f <sub>XTH</sub>                 | _                                                              | _    | 4.0M / 4.096M | _    | Hz              |

| High-speed crystal oscillation                                                        | C <sub>DH</sub>                  | —                                                              |      | 24            |      | pF              |

| external capacitor                                                                    | C <sub>GH</sub>                  | —                                                              | —    | 24            |      | P               |

<sup>\*1</sup>: The external C<sub>DL</sub> and C<sub>GL</sub> need to be adjusted in consideration of variation of internal loading capacitance C<sub>D</sub> and C<sub>G</sub>, and other additional capacitance such as PCB layout.

<sup>\*2</sup>: When using a crystal oscillator  $C_L = 6pF$ , there is a possibility that can not be adjusted by external  $C_{DL}$  and  $C_{GL}$ .

# **DC CHARACTERISTICS (1/5)**

|                                                            | /                 | V <sub>DD</sub> = 1.1 t                            | to 3.6V, $V_{SS} = 0V$ , | Ta = -20     | to +70°C | , unless c   | otherwise | specified) (1/5) |

|------------------------------------------------------------|-------------------|----------------------------------------------------|--------------------------|--------------|----------|--------------|-----------|------------------|

| Parameter                                                  | Symbol            | (                                                  | Condition                |              | Rating   |              |           | Measuring        |

|                                                            | Symbol            |                                                    | Condition                |              | Тур.     | Max.         | Unit      | circuit          |

| 500kHz PC assillation fraguency                            | f                 | $V_{DD} =$                                         | Ta = 25°C                | Тур.<br>–10% | 500      | Typ.<br>+10% | kHz       |                  |

| 500kHz RC oscillation frequency                            | f <sub>RC</sub>   | 1.3 to<br>3.6V                                     | Ta = −20 to<br>+70°C     | Тур.<br>–25% | 500      | Тур.<br>+25% | kHz       |                  |

| PLL oscillation frequency*4                                | f <sub>PLL</sub>  | LSCLK = 32.768kHz<br>V <sub>DD</sub> = 1.8 to 3.6V |                          | -2.5%        | 8.192    | +2.5%        | MHz       |                  |

| Low-speed crystal oscillation start time* <sup>2</sup>     | T <sub>XTL</sub>  | —                                                  |                          | _            | 0.3      | 2            | s         |                  |

| 500kHz RC oscillation start time                           | T <sub>RC</sub>   |                                                    |                          | —            | 50       | 500          | μS        |                  |

| High-speed crystal oscillation<br>start time* <sup>3</sup> | T <sub>XTH</sub>  | V <sub>DD</sub> :                                  | = 1.8 to 3.6V            | _            | 2        | 20           |           | 1                |

| PLL oscillation start time                                 | T <sub>PLL</sub>  | V <sub>DD</sub> :                                  | = 1.8 to 3.6V            | _            | 1        | 10           | ms        |                  |

| Low-speed oscillation stop detect time <sup>*1</sup>       | T <sub>STOP</sub> |                                                    | _                        | 0.2          | 3        | 20           |           |                  |

| Reset pulse width                                          | P <sub>RST</sub>  | —                                                  |                          | 200          |          |              |           |                  |

| Reset noise elimination<br>pulse width                     | P <sub>NRST</sub> | _                                                  |                          | —            |          | 0.3          | μS        |                  |

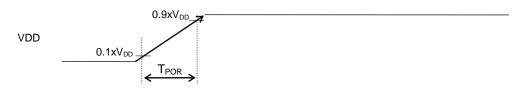

| Power-on reset activation<br>power rise time               | T <sub>POR</sub>  |                                                    | _                        | _            |          | 10           | ms        |                  |

\*1: When low-speed crystal oscillation stops for a duration more than the low-speed oscillation stop detect time, the system is reset to shift to system reset mode.

$*^{2}$ : Use 32.768kHz crystal resonator DT-26 (Load capacitance 6pF) (made by KDS:DAISHINKU CORP.) is used (C<sub>GL</sub>=C<sub>DL</sub>=12pF).

\*<sup>3</sup>: Use 4.096MHz Crystal Oscillator CHC49SFWB (Kyocera).

\*<sup>4</sup> : 1024 clock average.

[Reset pulse width]

VIL1 VIL1 RESET\_N PRST Reset pulse width (P<sub>RST</sub>)

[Power-on reset activation power rise time]

Power-on reset activation power rise time (TPOR)

#### **DC CHARACTERISTICS (2/5)**

LCD bias voltage

generation time

$\mathsf{T}_{\mathsf{BIAS}}$

| Parameter                             | Symbol          | C                                                 | dition                                                 |              | Rating                                   |             | Unit  | Measuring |

|---------------------------------------|-----------------|---------------------------------------------------|--------------------------------------------------------|--------------|------------------------------------------|-------------|-------|-----------|

| Parameter                             | Symbol          | Cor                                               | lation                                                 | Min.         | Тур.                                     | Max.        | Unit  | circuit   |

|                                       |                 |                                                   | CN4–0 = 00H                                            | 0.89         | 0.94                                     | 0.99        |       |           |

|                                       |                 |                                                   | CN4–0 = 01H                                            | 0.91         | 0.96                                     | 1.01        |       |           |

|                                       |                 |                                                   | CN4–0 = 02H                                            | 0.93         | 0.98                                     | 1.03        |       |           |

|                                       |                 |                                                   | CN4–0 = 03H                                            | 0.95         | 1.00                                     | 1.05        |       |           |

|                                       |                 |                                                   | CN4–0 = 04H                                            | 0.97         | 1.02                                     | 1.07        |       |           |

|                                       |                 |                                                   | CN4–0 = 05H                                            | 0.99         | 1.04                                     | 1.09        |       |           |

|                                       |                 |                                                   | CN4–0 = 06H                                            | 1.01         | 1.06                                     | 1.11        |       |           |

|                                       |                 |                                                   | CN4–0 = 07H                                            | 1.03         | 1.08                                     | 1.13        |       |           |

|                                       |                 |                                                   | CN4–0 = 08H                                            | 1.05         | 1.10                                     | 1.15        |       |           |

|                                       |                 |                                                   | CN4-0 = 09H                                            | 1.07         | 1.12                                     | 1.17        |       |           |

|                                       |                 |                                                   | CN4-0 = 0AH                                            | 1.09         | 1.14                                     | 1.19        |       |           |

|                                       |                 |                                                   | CN4-0 = 0BH                                            | 1.11         | 1.16                                     | 1.21        |       |           |

|                                       |                 |                                                   | CN4-0 = 0CH                                            | 1.13         | 1.18                                     | 1.23        |       |           |

|                                       |                 |                                                   | CN4-0 = 0DH                                            | 1.15         | 1.20                                     | 1.25        |       |           |

|                                       |                 |                                                   | CN4-0 = 0EH                                            | 1.17         | 1.22                                     | 1.27        |       |           |

|                                       |                 | $V_{DD} = 3.0V$ ,                                 | CN4-0 = 0FH                                            | 1.19         | 1.24                                     | 1.29        | V     |           |

| V <sub>L1</sub> voltage               | V <sub>L1</sub> | Tj = 25°C                                         | CN4–0 = 10H                                            | 1.21         | 1.26                                     | 1.31        | V     |           |

|                                       |                 | CN4–0 = 11H                                       | 1.23                                                   | 1.28         | 1.33                                     |             |       |           |

|                                       |                 | CN4–0 = 12H                                       | 1.25                                                   | 1.30         | 1.35                                     |             |       |           |

|                                       |                 |                                                   | CN4–0 = 13H                                            | 1.27         | 1.32                                     | 1.37        |       |           |

|                                       |                 |                                                   | CN4–0 = 14H <sup>*1</sup>                              | 1.29         | 1.34                                     | 1.39        |       |           |

|                                       |                 |                                                   | CN4–0 = 15H <sup>*1</sup>                              | 1.31         | 1.36                                     | 1.41        |       | 1         |

|                                       |                 |                                                   | CN4–0 = 16H <sup>*1</sup>                              | 1.33         | 1.38                                     | 1.43        |       |           |

|                                       |                 |                                                   | CN4–0 = 17H <sup>*1</sup>                              | 1.35         | 1.40                                     | 1.45        |       |           |

|                                       |                 |                                                   | CN4–0 = 18H <sup>*1</sup>                              | 1.37         | 1.42                                     | 1.47        |       |           |

|                                       |                 |                                                   | CN4–0 = 19H <sup>*1</sup>                              | 1.39         | 1.44                                     | 1.49        |       |           |

|                                       |                 |                                                   | CN4–0 = 1AH <sup>*1</sup>                              | 1.41         | 1.46                                     | 1.51        |       |           |

|                                       |                 |                                                   | $CN4-0 = 1BH^{*1}$                                     | 1.43         | 1.48                                     | 1.53        |       |           |

|                                       |                 |                                                   | CN4–0 = 1CH <sup>*1</sup>                              | 1.45         | 1.50                                     | 1.55        |       |           |

|                                       |                 |                                                   | CN4–0 = 1DH <sup>*1</sup>                              | 1.47         | 1.52                                     | 1.57        |       |           |

|                                       |                 |                                                   | $CN4-0 = 1EH^{*1}$                                     | 1.49         | 1.54                                     | 1.59        |       |           |

|                                       |                 |                                                   | CN4–0 = 1FH <sup>*1</sup>                              | 1.51         | 1.56                                     | 1.61        |       |           |

| V <sub>L1</sub> temperature deviation | $\Delta V_{L1}$ | V <sub>DD</sub>                                   | = 3.0V                                                 |              | -1.5                                     |             | mV/°C |           |

| V <sub>L1</sub> voltage<br>dependency | $\Delta V_{L1}$ | $V_{DD} = 1$                                      | .3 to 3.6V                                             |              | 5                                        | 20          | mV/V  |           |

| V <sub>L2</sub> voltage               | V <sub>L2</sub> |                                                   | V, Tj = 25°C<br>ad (V <sub>L4</sub> –V <sub>SS</sub> ) | Typ.<br>-10% | V <sub>L1</sub> ×2                       | Тур.<br>+4% |       |           |

| V <sub>L3</sub> voltage               | $V_{L3}$        | V <sub>DD</sub> = 3.0V,<br>Tj = 25°C              | 1/3 bias<br>1/4 bias                                   | Typ.<br>-10% | V <sub>L1</sub> ×2<br>V <sub>L1</sub> ×3 | Тур.<br>+4% | V     |           |

| V <sub>L4</sub> voltage               | $V_{L4}$        | 300kΩ load<br>(V <sub>L4</sub> –V <sub>SS</sub> ) | 1/3 bias<br>1/4 bias                                   | Typ.<br>–10% | V <sub>L1</sub> ×3<br>V <sub>L1</sub> ×4 | Тур.<br>+5% |       |           |

|                                       | -               | (-1                                               | 17 + 0103                                              | .070         | VLIAT                                    | . 370       |       |           |

\*1: When using 1/4 bias, the  $V_{L1}$  voltage is set to typ. 1.32 V (same voltage as in CN4–0 = 13H).

\_\_\_\_

600

\_\_\_\_

ms

### **DC CHARACTERISTICS (3/5)**

| Parameter                                            | Symbol           | Con                                                      | dition                                    |                      |      | Rating |      | Unit | Measuring<br>circuit |

|------------------------------------------------------|------------------|----------------------------------------------------------|-------------------------------------------|----------------------|------|--------|------|------|----------------------|

|                                                      | -,               |                                                          |                                           |                      | Min. | Тур.   | Max. |      |                      |

|                                                      |                  |                                                          | LD2–0 = 0H<br>LD2–0 = 1H                  |                      |      | 1.35   |      |      |                      |

|                                                      |                  |                                                          |                                           |                      |      | 1.4    |      |      |                      |