Configurable PMIC, Five-Channel Buck Regulator Plus One-Boost with HyperLight Load<sup>®</sup> and I<sup>2</sup>C Control

### **General Description**

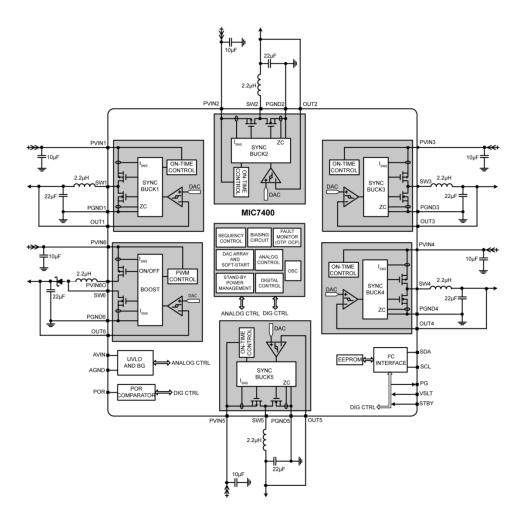

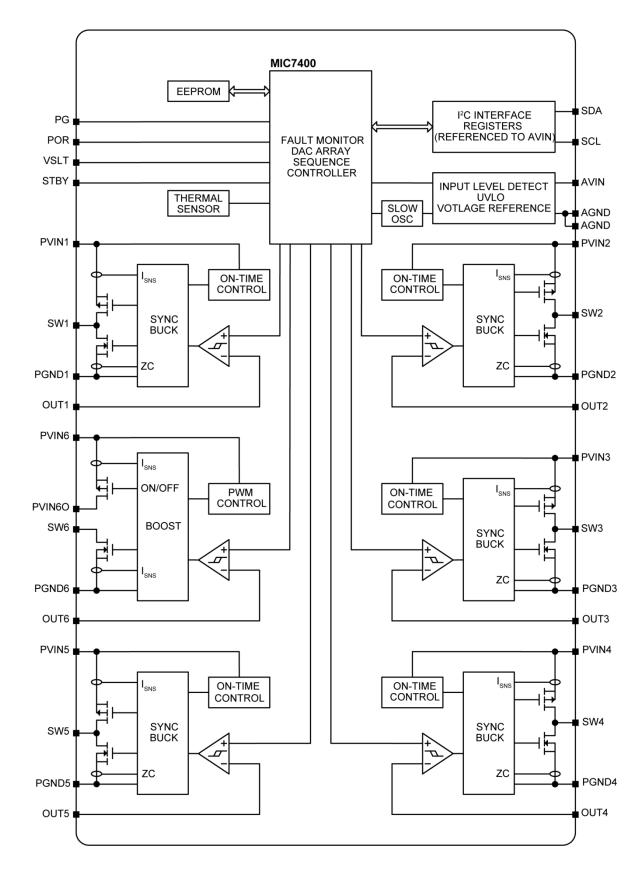

The MIC7400 is a powerful, highly integrated, configurable, power-management IC (PMIC) featuring five synchronous buck regulators, one boost regulator and high-speed  $I^2C$  interface with an internal EEPROM.

The device offers two distinct modes of operation "standby mode" and "normal mode" intended to provide an energy optimized solution suitable for portable handheld, and infotainment applications.

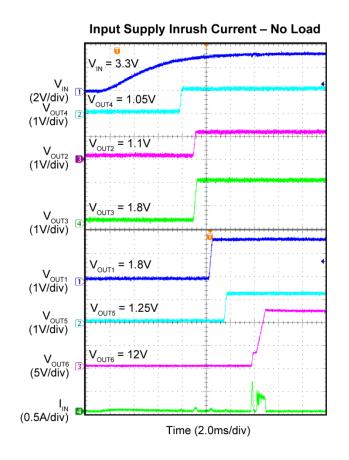

In normal mode, the programmable switching converters can be configured to support a variety of features, including start-up sequencing, timing, soft-start ramp, output voltage levels, current limit levels and output discharge for each channel.

In stand-by mode the PMIC can configured in a low power state by either disabling an output or by changing the output voltage to a lower level. Independent exit from stand-by mode can be achieved either by I<sup>2</sup>C communication or the external STBY pin.

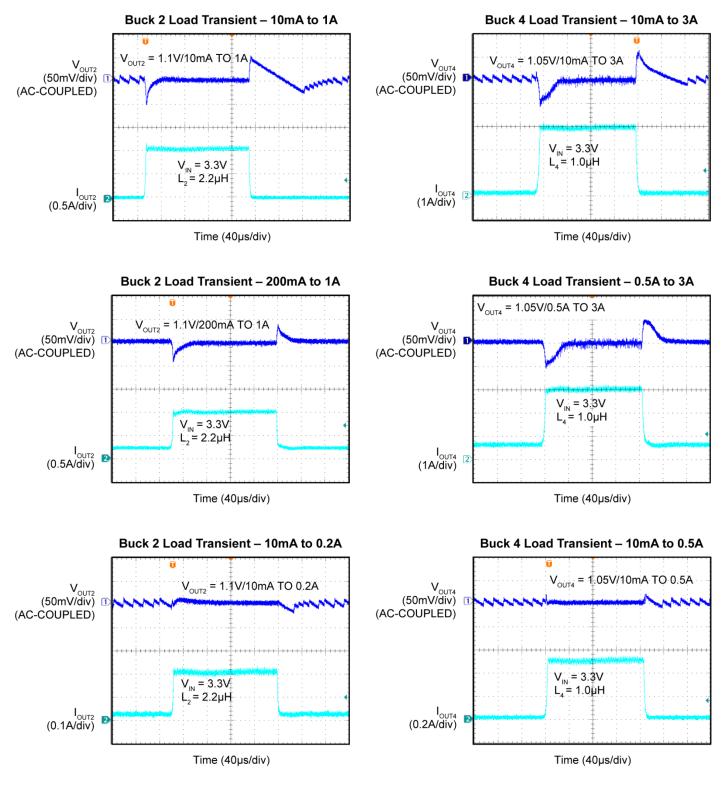

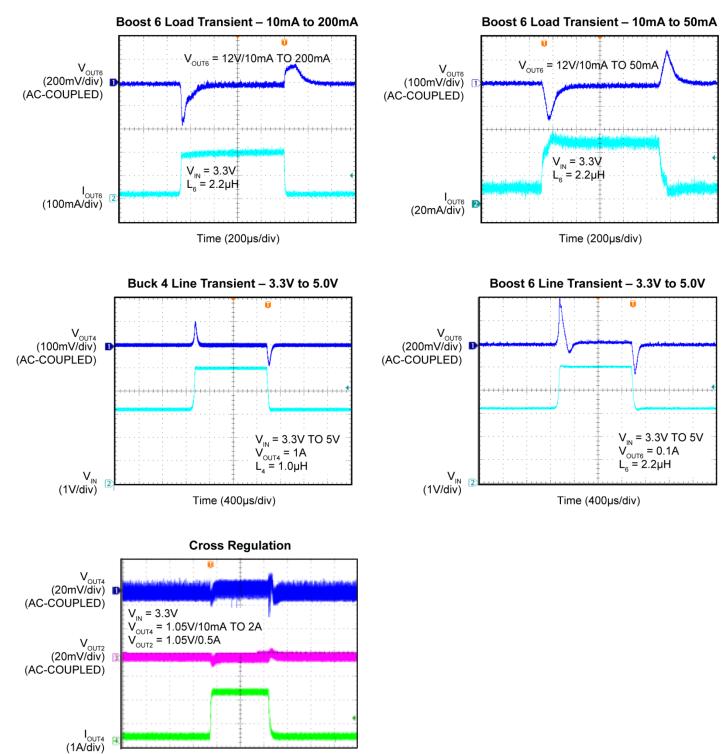

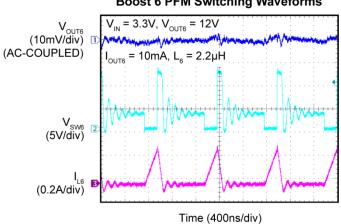

The device has five synchronous buck regulators with high-speed adaptive on-time control supporting even the challenging ultra-fast transient requirement for Core supplies. One boost regulator provides a flash-memory programming supply that delivers up to 200mA of output current. The boost is equipped with an output disconnect switch that opens if a short-to-ground fault is detected.

An internal EEPROM enables a single-chip solution across many platforms by allowing the designer to customize the PMIC for their design. Modifications can be made without the need to re-approve a new PMIC, saving valuable design resources and time.

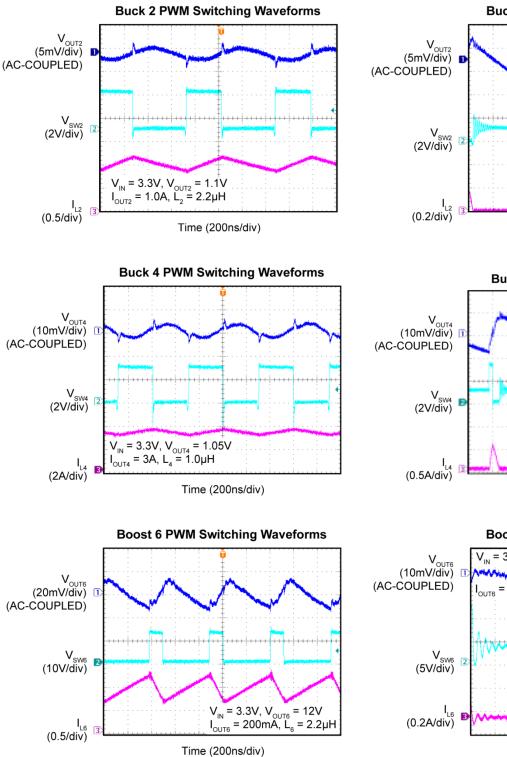

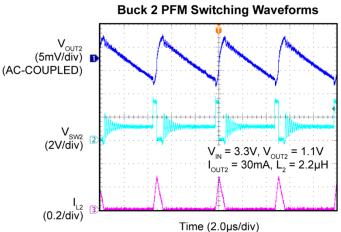

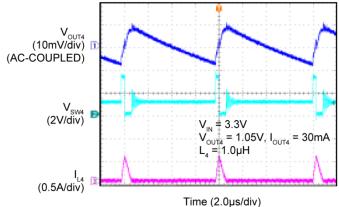

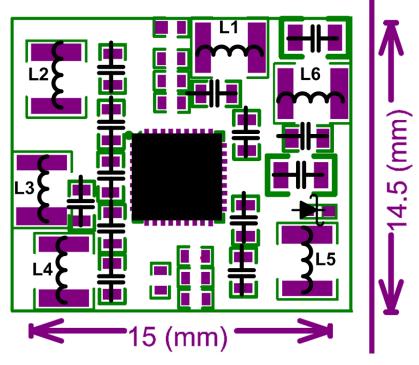

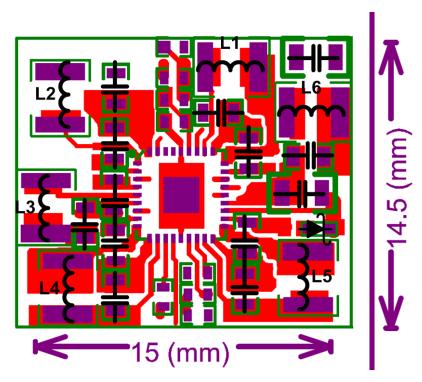

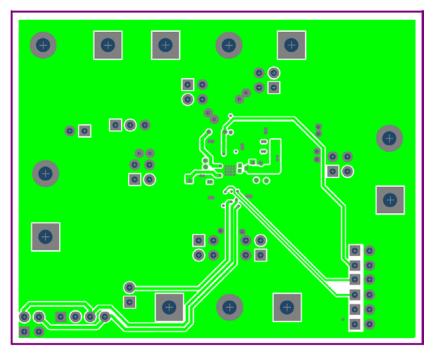

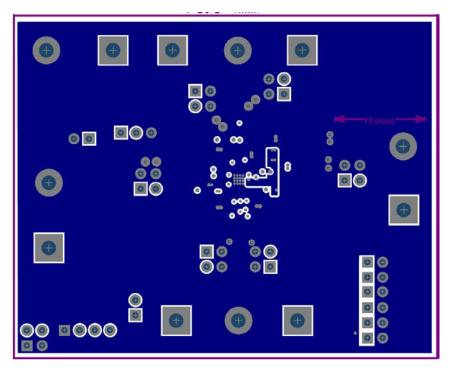

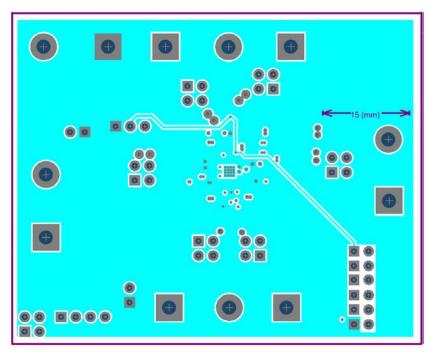

All switchers provide light-load efficiency with HyperLight Load<sup>®</sup> mode for buck and PFM mode for boost. An additional benefit of this proprietary architecture is very-low output ripple voltage throughout the entire load range with the use of small output capacitors. The MIC7400 is designed for use with a small inductors (down to 0.47µH for buck, 1.5µH for boost), and an output capacitor as small as 10µF for buck, enabling a total solution size of 15mm × 15mm and less than 1mm height.

The datasheet and other support documentation can be found on Micrel's website at: <u>www.micrel.com</u>.

### Features

- Input voltage: 2.4V to 5.5V

- Five independent synchronous bucks up to 3A

- One independent non-synchronous boost 200mA

- 200µA quiescent current (all regulators on)

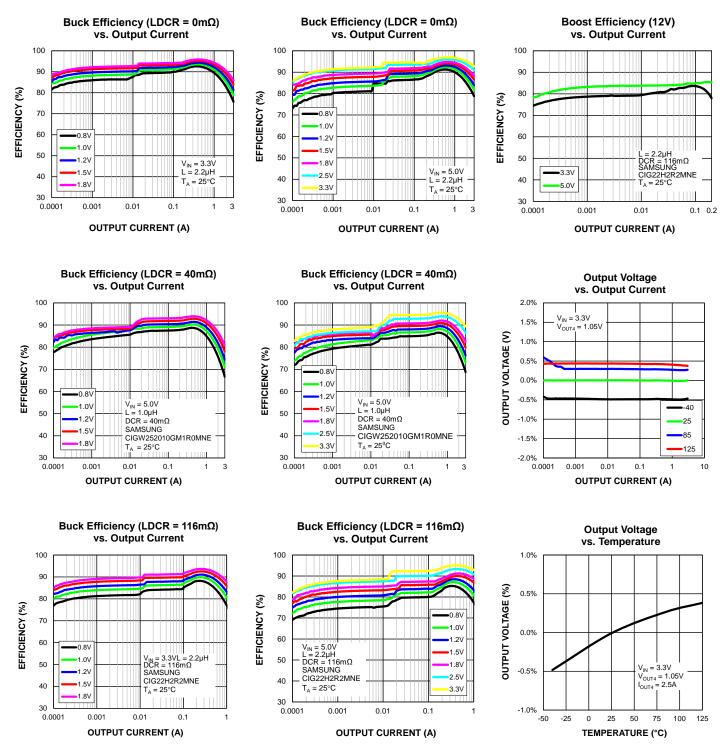

- 93% peak buck efficiency, 85% typical efficiency at 1mA

- Dual power mode: stand-by and normal mode

- I<sup>2</sup>C interface up to 3.4MHz

- I<sup>2</sup>C on-the-fly EEPROM programmability, featuring:

- Buck and boost output voltage scaling

- Power-on-reset threshold and delay

- Power-up sequencing/sequencing delay

- Buck and boost current limit

- Buck and boost pull-down when disabled

- Individual ON, OFF, and standby modes

- Soft-start and global power-good masking

- 23µA buck typical quiescent current

- 70µA boost typical quiescent current

- 1.5% output accuracy over temperature/line/load

- 2.0MHz boost switching frequency

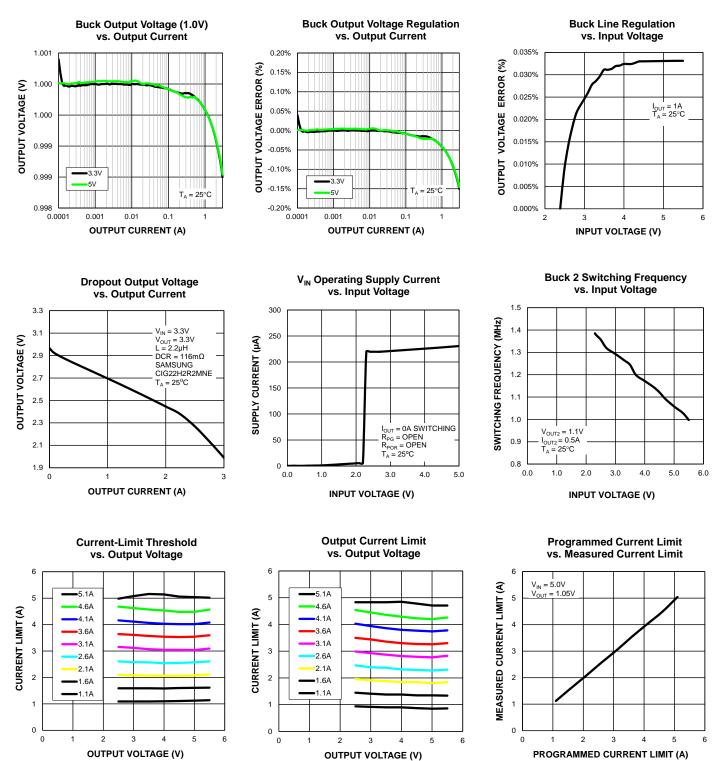

- 1.3MHz buck operation in continuous mode

- Ultra-fast buck transient response

- 15mm × 15mm × 1.25mm solution size

- · Thermal-shutdown and current-limit protection

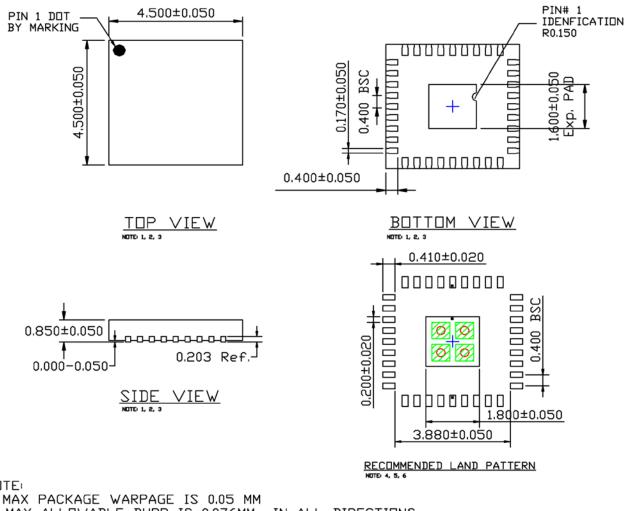

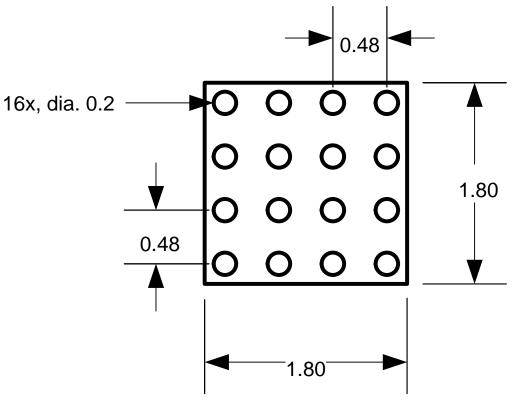

- 36-pin 4.5mm × 4.5mm × 0.85mm FQFN package (0.4mm pitch)

- -40°C to +125°C junction temperature range

#### **Applications**

- Client and enterprise solid state drives (SSD)

- Consumer and in-vehicle infotainment devices

- Multimedia devices

- Portable handheld devices

- Security camera

- Gaming machines

- · Service provider gateways

Micrel Inc. • 2180 Fortune Drive • San Jose, CA 95131 • USA • tel +1 (408) 944-0800 • fax + 1 (408) 474-1000 • http://www.micrel.com

HyperLight Load is a registered trademark of Micrel, Inc.

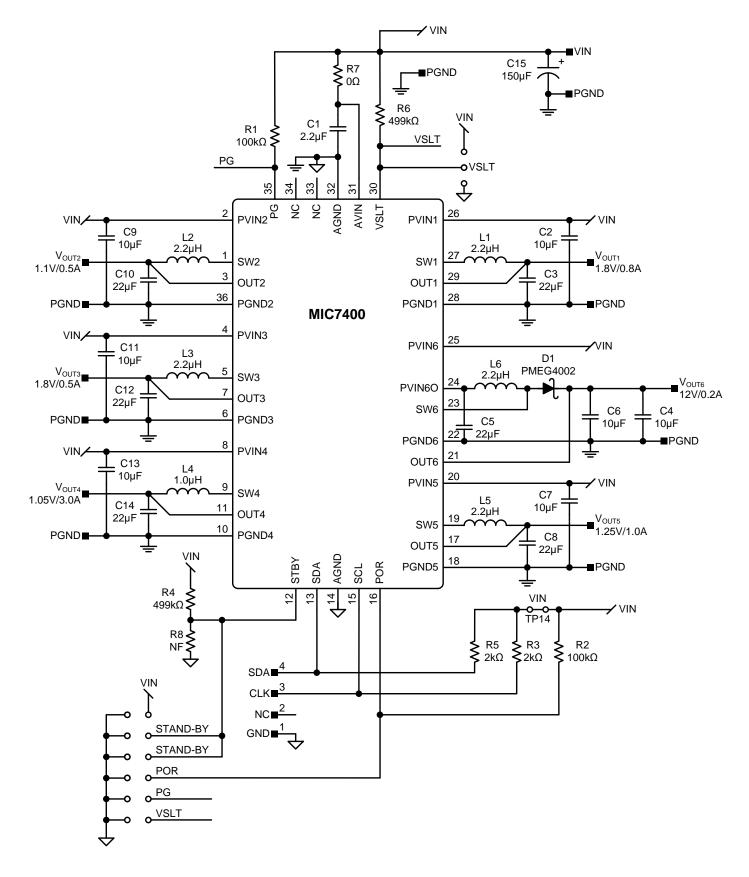

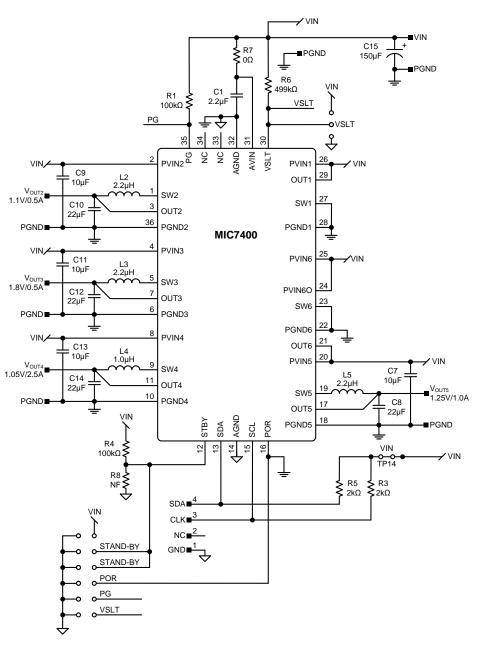

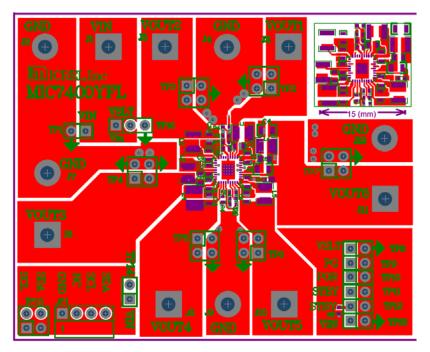

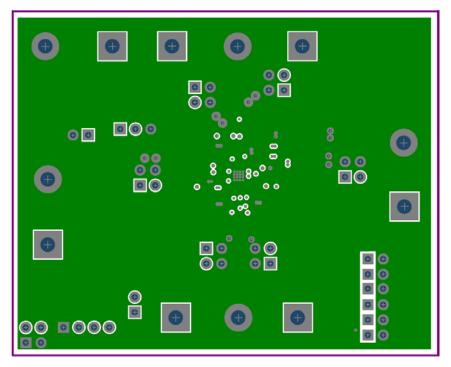

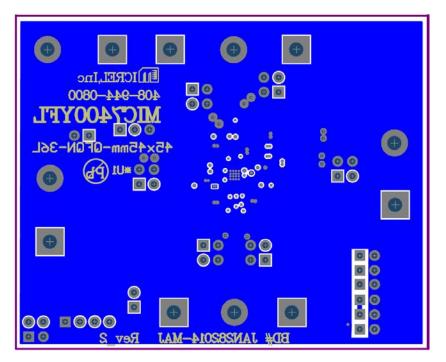

# **Typical Application**

## **Ordering Information**

| Part Number                    | Marking                    | Output Voltages                       | Features                                    | Package <sup>(1)</sup>       | Lead<br>Finish |

|--------------------------------|----------------------------|---------------------------------------|---------------------------------------------|------------------------------|----------------|

| MIC7400YFL                     | 7400<br>YWWS               | 1.8V, 1.1V, 1.8V<br>1.05V, 1.25V, 12V | STBY – Active Low<br>Falling Edge (DEFAULT) | 36-Pin<br>4.5mm × 4.5mm FQFN | Pb-<br>Free    |

| MIC7400-XXXXYFL <sup>(2)</sup> | X<br>X 7400<br>X YYWW<br>X | Configurable                          | Configurable                                | 36-Pin<br>4.5mm × 4.5mm FQFN | Pb-<br>Free    |

Notes:

1. GREEN, RoHS-compliant package. Lead finish is Matte Tin. Mold compound is Halogen Free.

2. Configurable options available upon request. Contact Marketing.

## **Table of Contents**

| List of Figures                         | 5  |

|-----------------------------------------|----|

| List of Tables                          | 6  |

| Pin Configuration                       | 7  |

| Pin Description                         | 7  |

| Absolute Maximum Ratings                | 10 |

| Operating Ratings                       | 10 |

| Electrical Characteristics              | 10 |

| Typical Characteristics                 | 15 |

| Functional Characteristics              | 17 |

| MIC7400 Block Diagram                   | 24 |

| Functional Description                  | 25 |

| Programmable Buck Soft-Start Control    | 25 |

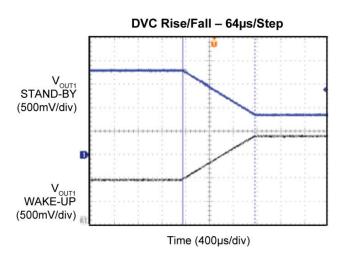

| Buck Digital Voltage Control (DVC)      | 26 |

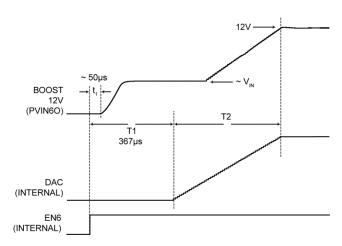

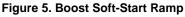

| Programmable Boost Soft-Start Control   | 27 |

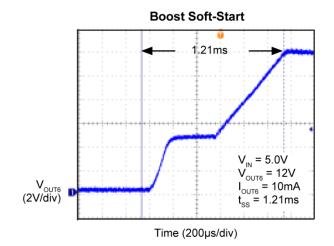

| Boost Digital Voltage Control (DVC)     | 28 |

| Buck Current Limit                      | 28 |

| Boost Current Limit                     | 29 |

| Global Power Good Pin                   | 29 |

| Standard Delay                          | 29 |

| Power-Up Sequencing                     | 29 |

| Programmable Power-on-Reset (POR) Delay |    |

| Power-Down Sequencing                   |    |

| Stand-By Mode                           | 31 |

| Resistive Discharge                     | 31 |

| STBY Pin                                | 31 |

| Safe Start-Up into a Pre-Biased Output  | 32 |

| Buck Regulator Power Dissipation        | 32 |

| Total Power Dissipation                 | 32 |

| Power Derating                          | 33 |

| Overtemperature Fault                   | 33 |

| Thermal Measurements                    | 34 |

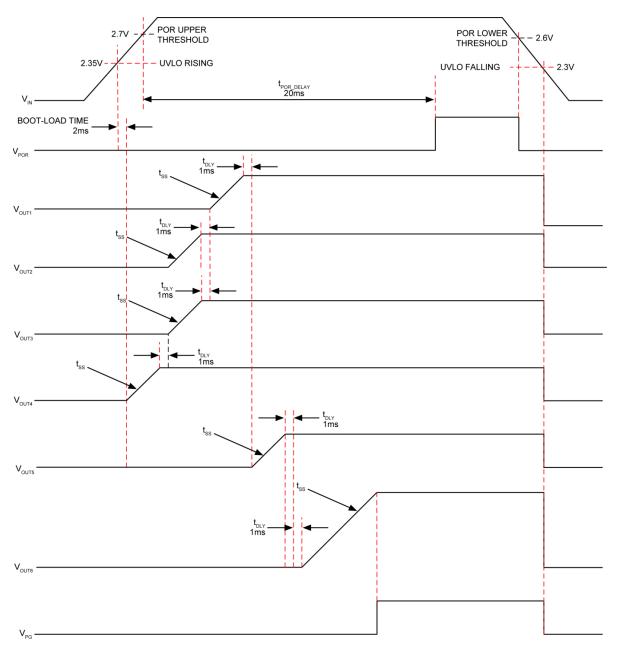

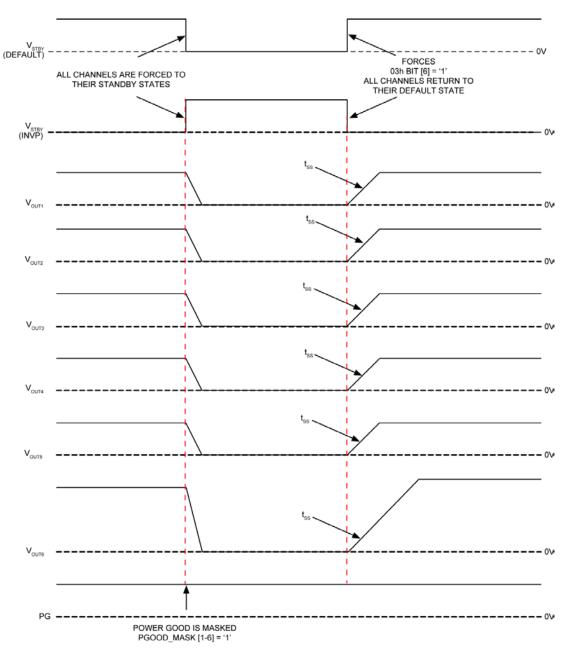

| Timing Diagrams                         | 35 |

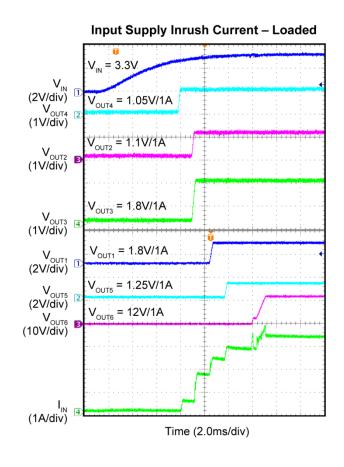

| Normal Power-Up Sequence for Outputs    | 35 |

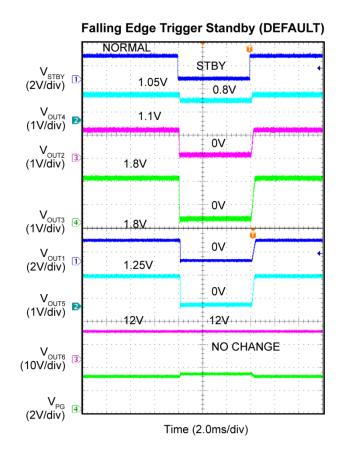

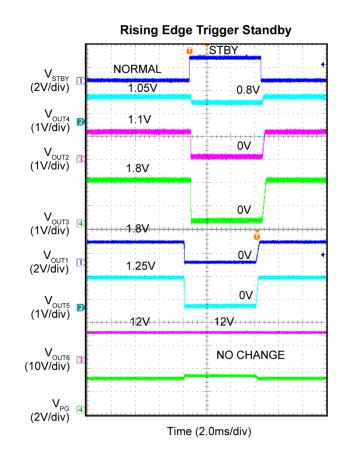

| Standby (STBY) Pin (Wake-Up)            | 36 |

| Evaluation Board Schematic              | 37 |

| Bill of Materials                       |    |

# Table of Contents (Continued)

| PCB Layout Guidelines<br>General                                        | 30 |

|-------------------------------------------------------------------------|----|

|                                                                         |    |

| Input Capacitor                                                         |    |

| Inductor                                                                |    |

| Output Capacitor                                                        |    |

| Proper Termination of Unused Pins                                       |    |

| PCB Layout Recommendations                                              |    |

| Package Information and Recommended Landing Pattern                     |    |

| Appendix A                                                              |    |

| I <sup>2</sup> C Control Register                                       |    |

| Serial Port Operation                                                   |    |

| External Host Interface                                                 |    |

| Special Host I <sup>2</sup> C Commands                                  |    |

| Special Keys                                                            |    |

| Appendix B                                                              |    |

| Register Settings Descriptions                                          |    |

| Power Good Register (00'h)                                              |    |

| EEPROM-Ready Register (01'h)                                            |    |

| Fault Registers (02'h)                                                  | 51 |

| Standby Register (03'h)                                                 |    |

| Enable/Disable Register (04'h)                                          |    |

| Regulator Output Voltage Setting NORMAL Mode (05'h – 09'h)              |    |

| Boost Regulator Output Voltage Setting NORMAL Mode (0A'h)               |    |

| Regulator Voltage Setting STBY Mode (0B'h – 0F'h)                       |    |

| Boost Regulator Output Voltage Setting STBY Mode (10'h)                 | 57 |

| Sequence Register (11'h)                                                |    |

| Delay Register (17'h)                                                   | 61 |

| Soft-Start Registers (18'h – 1A'h)                                      | 62 |

| Current-Limit (Normal Mode) Registers (1B'h – 1D'h)                     | 63 |

| Current-Limit (STBY Mode) Registers (1E – 20'h)                         | 65 |

| Power-on-Reset (POR) Threshold Voltage Setting Register (21'h and 22'h) |    |

| Pull-Down when Disabled Register (23'h)                                 | 67 |

# List of Figures

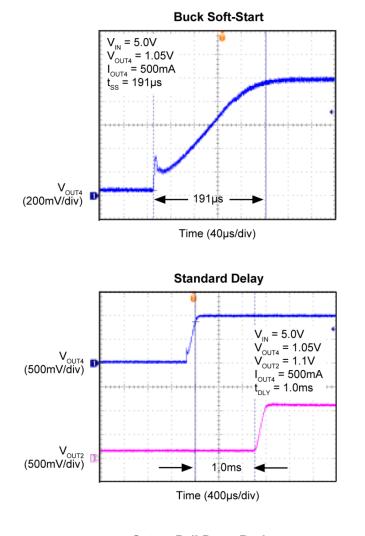

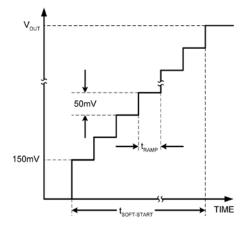

| Figure 1. | Buck Soft-Start                       | 25 |

|-----------|---------------------------------------|----|

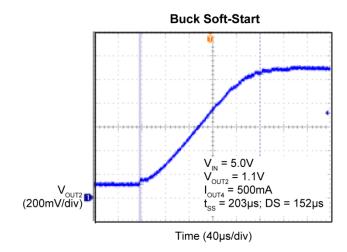

| Figure 2. | Buck Soft-Start                       | 26 |

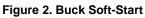

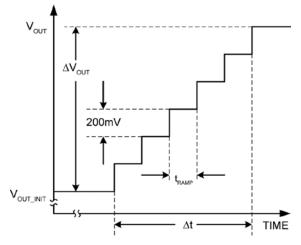

| Figure 3. | Buck DVC Control Ramp                 | 26 |

| Figure 4. | Buck DVC Control Ramp                 | 27 |

| Figure 5. | Boost Soft-Start Ramp                 | 27 |

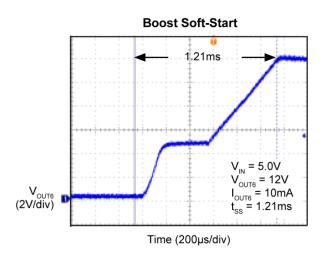

| Figure 6. | Boost Soft-Start                      | 27 |

| Figure 7. | Boost DVC Control Ramp                | 28 |

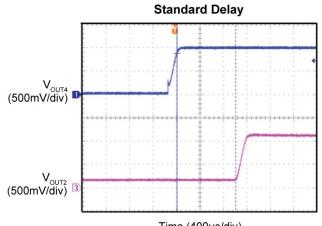

| Figure 8. | Standard Delay Time                   | 29 |

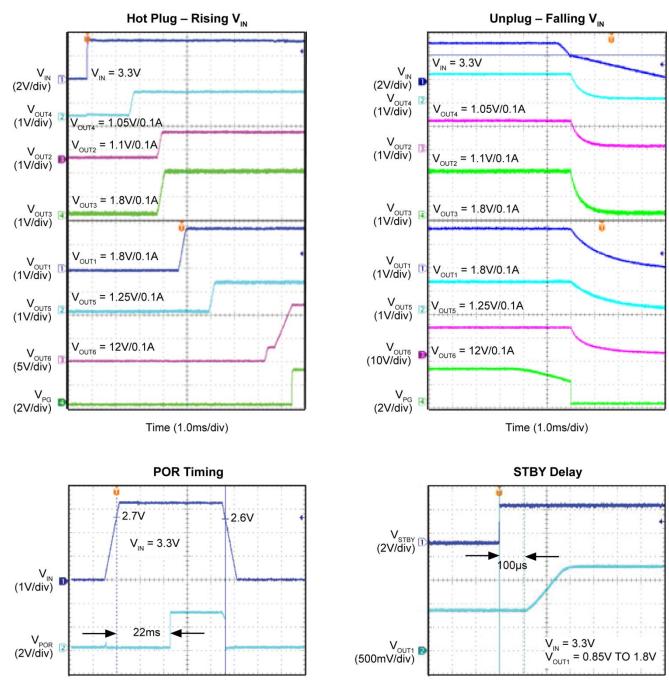

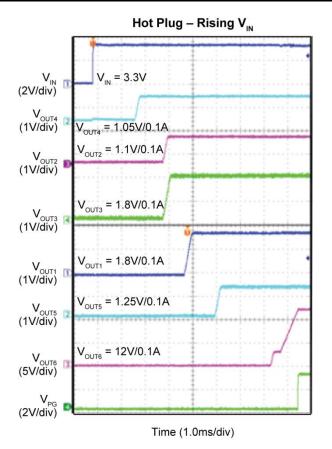

| Figure 9. | Hot Plug – V <sub>IN</sub> Rising     | 30 |

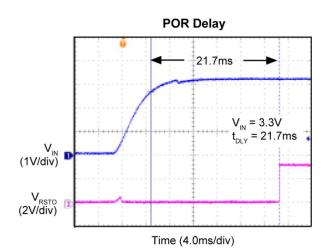

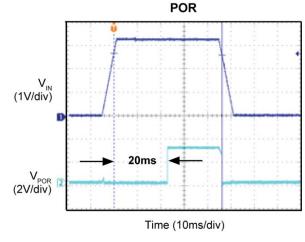

| Figure 10 | POR                                   | 30 |

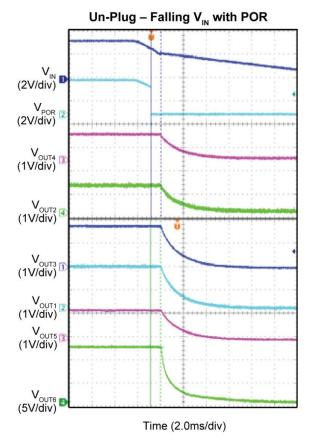

| Figure 11 | Hot Un-Plug – V <sub>IN</sub> Falling | 30 |

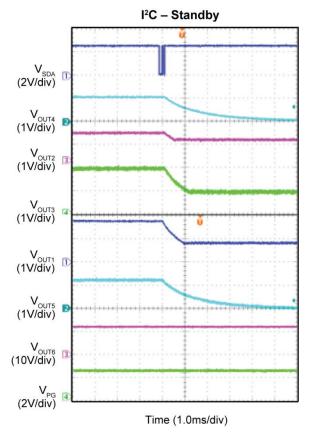

| Figure 12 | I <sup>2</sup> C Stand-By Mode        | 31 |

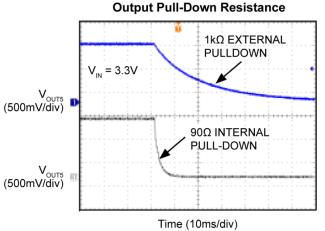

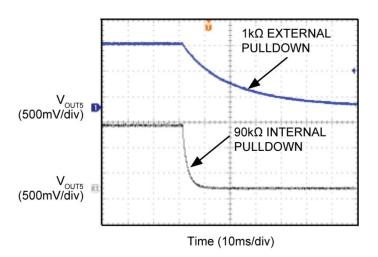

| Figure 13 | Output Pull-Down Resistance           | 31 |

| Figure 14 | STBY-to-NORMAL Transition (DEFAULT)   | 32 |

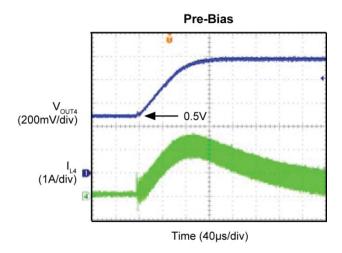

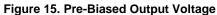

| Figure 15 | Pre-Biased Output Voltage             | 32 |

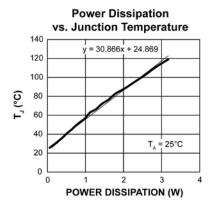

| Figure 16 | Power Dissipation                     | 33 |

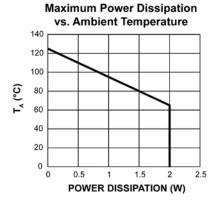

| Figure 17 | Power Derating Curve                  | 33 |

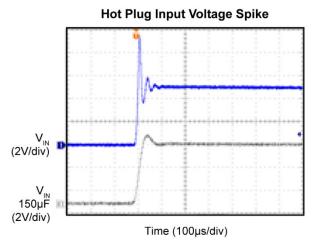

| Figure 18 | Hot Plug Input Voltage Spike          | 34 |

| Figure 19 | MIC7400 Power-Up/Down                 | 35 |

| Figure 20 | MIC7400 STBY Function (DEFAULT)       | 36 |

| Figure 21 | Connections for Unused Pins           | 40 |

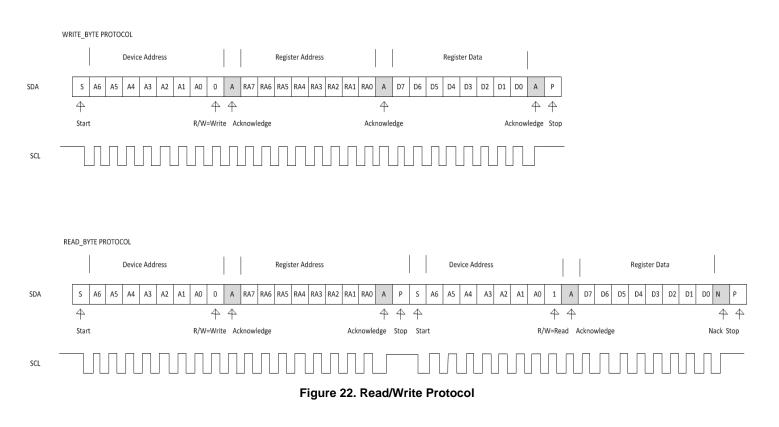

| Figure 22 | Read/Write Protocol                   | 47 |

### List of Tables

| Table 1. Buck Outputs Default Soft-Start Time (DEFAULT)                          |    |

|----------------------------------------------------------------------------------|----|

| Table 2. Boost Output Default Soft-Start Time                                    |    |

| Table 3. Buck Current Limit Register Settings                                    |    |

| Table 4. Summarization of Unused Pin Connections                                 |    |

| Table 5. Power Good Status Register                                              |    |

| Table 6. EEPROM Status Register                                                  | 50 |

| Table 7. Overcurrent Status Fault Register                                       | 51 |

| Table 8. Standby Register                                                        |    |

| Table 9. Enable Register                                                         | 53 |

| Table 10. DVC Registers for OUT[1 – 5]                                           | 54 |

| Table 11. DVC Registers for OUT6                                                 | 55 |

| Table 12. Standby Registers                                                      | 56 |

| Table 13. Standby DVC Register for OUT6                                          | 57 |

| Table 14. Sequence State 1 Register                                              | 59 |

| Table 15. Sequence State 2 Register                                              | 59 |

| Table 16. Sequence State 3 Register                                              | 59 |

| Table 17. Sequence State 4 Register                                              | 60 |

| Table 18. Sequence State 5 Register                                              | 60 |

| Table 19. Sequence State 6 Register                                              | 61 |

| Table 20. Delay Register                                                         | 61 |

| Table 21. Soft-Start Register Speed Settings                                     | 62 |

| Table 22. Soft-Start Register OUT1 and OUT2                                      | 62 |

| Table 23. Soft-Start Register OUT3 and OUT4                                      | 62 |

| Table 24. Soft-Start Register OUT5 and OUT6                                      | 63 |

| Table 25. Current-Limit Register I <sub>OUT1</sub> and I <sub>OUT2</sub>         | 63 |

| Table 26. Current-Limit Register I <sub>OUT3</sub> and I <sub>OUT4</sub>         | 64 |

| Table 27. Current-Limit Register I <sub>OUT 5</sub> and I <sub>OUT6</sub>        | 64 |

| Table 28. Standby Current-Limit Register I <sub>OUT1</sub> and I <sub>OUT2</sub> | 65 |

| Table 29. Standby Current-Limit Register I <sub>OUT3</sub> and I <sub>OUT4</sub> | 65 |

| Table 30. Standby Current-Limit Register I <sub>OUT5</sub> and I <sub>OUT6</sub> | 66 |

| Table 31. Rising and Falling Power-on-Reset Threshold Voltage Settings           | 66 |

| Table 32. Power-on-Reset Rising Threshold Voltage Setting Register (21'h)        | 67 |

| Table 33. Power-on-Reset Falling Threshold Voltage Setting Register (22'h)       | 67 |

| Table 34. Pull-Down when Disabled Register                                       | 67 |

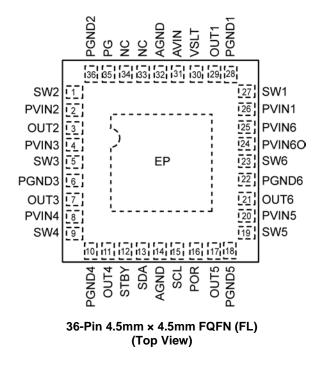

## **Pin Configuration**

### **Pin Description**

| Pin Number | Pin Name | Description                                                                                                                                                                                                                                                                                                                                |

|------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | SW2      | Switch Pin 2 (Output): Inductor connection for the synchronous step-down regulator. Connect the inductor between the output capacitor and the SW2 pin.                                                                                                                                                                                     |

| 2          | PVIN2    | Power Supply Voltage 2 (Input): Input supply to the source of the internal high-side P-channel MOSFET. An input capacitor between PVIN2 and the power ground PGND2 pin is required and to be placed as close as possible to the IC.                                                                                                        |

| 3          | OUT2     | Output Voltage Sense 2 (Input): This pin is used to sense the output voltage. Connect OUT2 as close to the output capacitor as possible to sense output voltage. Also provides the path to discharge the output through an internal $90\Omega$ resistor when disabled. This pull-down feature is programmed through the PULLD[x] register. |

| 4          | PVIN3    | Power Supply Voltage 3 (Input): Input supply to the source of the internal high-side P-channel MOSFET. An input capacitor between PVIN3 and the power ground PGND3 pin is required and to be placed as close as possible to the IC.                                                                                                        |

| 5          | SW3      | Switch Pin 3 (Output): Inductor connection for the synchronous step-down regulator. Connect the inductor between the output capacitor and the SW3 pin.                                                                                                                                                                                     |

| 6          | PGND3    | Power Ground 3: The power ground for the synchronous buck converter power stage. The PGND pin connects to the sources of the internal low-side N-Channel MOSFET, the negative terminals of input capacitors, and the negative terminals of output capacitors.                                                                              |

| 7          | OUT3     | Output Voltage Sense 3 (Input): This pin is used to sense the output voltage. Connect OUT3 as close to the output capacitor as possible to sense output voltage. Also provides the path to discharge the output through an internal $90\Omega$ resistor when disabled. This pull-down feature is programmed through the PULLD[x] register. |

| 8          | PVIN4    | Power Supply Voltage 4 (Input): Input supply to the source of the internal high-side P-channel MOSFET. An input capacitor between PVIN4 and the power ground PGND4 pin is required and to be placed as close as possible to the IC.                                                                                                        |

# **Pin Description (Continued)**

| Pin Number | Pin Name | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9          | SW4      | Switch Pin 4 (Output): Inductor connection for the synchronous step-down regulator. Connect the inductor between the output capacitor and the SW4 pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 10         | PGND4    | Power Ground 4: The power ground for the synchronous buck converter power stage. The PGND pin connects to the source of the internal low-side N-Channel MOSFET, the negative terminals of input capacitors, and the negative terminals of output capacitors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 11         | OUT4     | Output Voltage Sense 4 (Input): This pin is used to sense the output voltage. Connect the OUT4 as close to the output capacitor as possible to sense output voltage. Also provides the path to discharge the output through an internal $90\Omega$ resistor when disabled. This pull-down feature is programmed through the PULLD[x] register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 12         | STBY     | Standby Reset (Input): Standby mode allows the total power consumption to be reduced by either lowering a supply voltage or turning it off. The IC can be placed in standby mode while operating in normal mode by a high-to-low transition (DEFAULT) on the STBY input. When this occurs, the STBY_MODEB bit will be set to logic "0". Either a low-to-high transition on the STBY pin or an I <sup>2</sup> C write command to the STBY_MODEB bit sets all of the regulators to their normal mode default settings. This pin can be driven with either a digital signal or open collector output. Do not let this pin float. Connect to ground or V <sub>IN</sub> . A pull-down resistor of 100k $\Omega$ or less can also be used. There are both a high-to-low (DEFAULT) and low-to-high normal to standby trigger options available. |

| 13         | SDA      | High-Speed Mode 3.4MHz I <sup>2</sup> C Data (Input/Output): This is an open drain, bidirectional data pin. Data is read on the rising edge of the SCL and data is clocked out on the falling edge of the SCL. External pull-up resistors are required.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 14         | AGND     | Analog Ground: Internal signal ground for all low power circuits. Connect to ground plane for best operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 15         | SCL      | High-Speed Mode 3.4MHz I <sup>2</sup> C Clock (Input): I <sup>2</sup> C serial clock line open drain input. External pull-up resistors are required.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 16         | POR      | Power-on-Reset (Output): This is an open drain output that goes high after the POR delay time elapses. The POR delay time starts as soon as the AVIN pin voltage rises above the upper threshold set by the PORUP register. The POR output goes low without delay when AVIN falls below the lower threshold set by the PORDN register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 17         | OUT5     | Output Voltage Sense 5 (Input): This pin is used to sense the output voltage. Connect OUT5 as close to the output capacitor as possible to sense output voltage. Also provides the path to discharge the output through an internal $90\Omega$ resistor when disabled. This pull-down feature is programmed through the PULLD[x] register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 18         | PGND5    | Power Ground 5: The power ground for the synchronous buck converter power stage. The PGND pin connects to the source of the internal low-side N-Channel MOSFET, the negative terminals of input capacitors, and the negative terminals of output capacitors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 19         | SW5      | Switch Pin 5 (Output): Inductor connection for the synchronous step-down regulator. Connect the inductor between the output capacitor and the SW5 pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 20         | PVIN5    | Power Supply Voltage 5 (Input): Input supply to the source of the internal high-side P-channel MOSFET. An input capacitor between PVIN5 and the power ground PGND5 pin is required and to be placed as close as possible to the IC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 21         | OUT6     | Output Voltage 6 Sense (Input): This pin is used to sense the output voltage. Connect OUT6 as close to the output capacitor as possible to sense output voltage. Also provides the path to discharge the output through an internal programmable current source when disabled. This pull-down feature is programmed through the PULLD[x] register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 22         | PGND6    | Power Ground 6: The power ground for the boost converter power stage. The PGND pin connects to the source of the internal low-side N-Channel MOSFET, the negative terminals of input capacitors, and the negative terminals of output capacitors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 23         | SW6      | Switch Pin 6 (Input): Inductor connection for the boost regulator. Connect the inductor between the PVIN6O and SW6 pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

# **Pin Description (Continued)**

| 24         Power Supply Voltage 6 (Output): This pin is the output of the power disconnect switch for the boost inductor. In shutdown, an internal Wich provides a current path for the boost output from the input supply. This feature eliminates current draw from the input supply during shutdown. An input capacitor between PVINBO and the power ground PGNDb pin is required and place as close as possible to the IC.           25         PVIN6         Power Supply Voltage 6 (Input): Input supply to the internal disconnect switch.           26         PVIN1         Power Supply Voltage 6 (Input): Input supply to the source of the internal high-side P-channel MOSFET An input capacitor between PVIN1 and the power ground PGNDT pin is required and to be placed as close as a possible to the IC.           27         SW1         Switch Pin 1 (Output): Inductor connection for the synchronous step-down regulator. Connect the inductor between the output capacitor and the SW1 pin.           28         PGND1         Power Supply voltage Signal with and the synchronous buck converter power stage. The PGND pin connects to the source of the internal low-side N-Channel MOSFET, the negative terminals of output capacitors.           29         OUT1         Output Voltage Sense 1(Input): This pin is used to sense the output voltage remotely. Connect OUT1 as close to output capacitor as possible to sense output voltage. The FoRD pin connects to the output capacitors.           30         VSLT         POR Selection Threshold (Input): This pin is used to sense the output voltage remotely. Connect OUT1 as close to output capacitor spossible to sense output voltage. The pull-down feature is programmed through the PULLD[X] register.                                                                                                                                                              | Pin Number | Pin Name | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 26         PVIN1         Power Supply Voltage 1 (Input): Input supply to the source of the internal high-side P-channel MOSFET. An input capacitor between PVIN1 and the power ground PGND1 pin is required and to be placed as close as possible to the IC.           27         SW1         Switch Pin 1 (Output): Inductor connection for the synchronous step-down regulator. Connect the inductor between the output capacitor and the SW1 pin.           28         PGND1         Power Ground 1: The power ground for the synchronous buck converter power stage. The PGND pin connects to the source of the internal low-side N-Channel MOSFET, the negative terminals of input capacitors, and the negative terminals of output capacitors.           29         OUT1         Output Voltage Sense 1(Input): This pin is used to sense the output voltage remotely. Connect OUT1 as close to output capacitors ap cosible to sense output voltage. This feature also provides the path to discharge the output through an internal 900 resistor when disabled. The pull-down feature is programmed through the PULLD[x] register.           30         VSLT         POR Selection Threshold (Input): The start-up sequence begins as soon as the AVIN pin voltage rises above the IC's UVLO upper threshold. The outputs do not turn off until AVIN pin voltage falls below the lower threshold limit. A 2.2µF ceramic capacitor from the AVIN pin to AGND pin must be placed next to the IC.           32         AGND         Analog Ground: Internal signal ground for all low power circuits. Connect directly to the layer 2 ground plane. Layer 2 is the point where all the PGNDs and AGND are connected. Do not connect PGND and AGND together on the top layer.           33         NC                                                                                                                                                       | 24         | PVIN6O   | regulator. When the boost regulator is on, an internal switch provides a current path for the boost inductor. In shutdown, an internal P-channel MOSFET is turned off and disconnects the boost output from the input supply. This feature eliminates current draw from the input supply during shutdown. An input capacitor between PVIN6O and the power ground PGND6 pin is required and place as close as                                                                                                |

| 26         PVIN1         MOSFET: An input capacitor between PVIN1 and the power ground PGND1 pin is required and to be placed as close as possible to the IC.           27         SW1         Switch Pin 1 (Output): Inductor connection for the synchronous step-down regulator. Connect the inductor between the output capacitor and the SW1 pin.           28         PGND1         Power Ground 1: The power ground for the synchronous buck converter power stage. The PGND pin connects to the source of the internal low-side N-Channel MOSFET, the negative terminals of input capacitors, and the negative terminals of output capacitors.           29         OUT1         Output Voltage Sense 1(Input): This pin is used to sense the output voltage remotely. Connect OUT1 as close to output capacitor as possible to sense output voltage. This feature also provides the path to discharge the output through an internal 900 resistor when disabled. The pull-down feature is programmed through the PULLD[x] register.           30         VSLT         POR Selection Threshold (Input): A high on this pin sets the PORUP and PORDN registers to their upper threshold limits. Analog Voltage Supply (Input): The start-up sequence begins as son as the AVIN pin voltage rises above the IC's UVLO upper threshold. The outputs do not turn off until AVIN pin voltage fails below the lower threshold limit. A 2.2µF ceramic capacitor from the AVIN pin to AGND pin must be placed next to the IC.           32         AGND         Analog Ground: Internal signal ground for all low power circuits. Connect directly to the layer 2 ground plane. Layer 2 is the point where all the PGNDs and AGND are connected. Do not connect PGND and AGND together on the top layer.           33                                                                                                                                            | 25         | PVIN6    | Power Supply Voltage 6 (Input): Input supply to the internal disconnect switch.                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 27       SW1       inductor between the output capacitor and the SW1 pin.         28       PGND1       Power Ground 1: The power ground for the synchronous buck converter power stage. The PGND pin connects to the source of the internal low-side N-Channel MOSFET, the negative terminals of input capacitors, and the negative terminals of output capacitors.         29       OUT1       Output Voltage Sense 1(Input): This pin is used to sense the output voltage remotely. Connect OUT1 as close to output capacitor as possible to sense output voltage. This feature also provides the path to discharge the output through an internal 900 resistor when disabled. The pull-down feature is programmed through the PULLD[x] register.         30       VSLT       POR Selection Threshold (Input): A high on this pin sets the PORUP and PORDN registers to their upper threshold limits and a low to their lower threshold limits. Do not leave floating.         31       AVIN       Analog Voltage Supply (Input): The start-up sequence begins as soon as the AVIN pin voltage falls below the lower threshold limit. A 2.2µF ceramic capacitor from the AVIN pin voltage falls below the lower threshold limit. A 2.2µF ceramic capacitor from the AVIN pin voltage falls below the lower threshold limit. A 2.2µF ceramic capacitor from the AVIN pin voltage falls below the lower threshold limit. A 2.2µF ceramic capacitor from the AVIN pin voltage falls below the lower threshold ECS UVL) upper threshold. The output that is pulled high when all the regulator power good flags are high. If an output falls below the power good threshold or a thermal fault occurs, the global power good flags are high. If an output falls below the power good threshold or a thermal fault occurs, the global power good flags are high. If an output falls below the po                                                                   | 26         | PVIN1    | MOSFET. An input capacitor between PVIN1 and the power ground PGND1 pin is required and to be                                                                                                                                                                                                                                                                                                                                                                                                               |

| 28       PGND1       connects to the source of the internal low-side N-Channel MOSFET, the negative terminals of input capacitors, and the negative terminals of output capacitors.         29       OUT1       Output Voltage Sense 1 (Input): This pin is used to sense the output voltage remotely. Connect OUT1 as close to output capacitor as possible to sense output voltage. This feature also provides the path to discharge the output through an internal 90Ω resistor when disabled. The pull-down feature is programmed through the PULLD[x] register.         30       VSLT       POR Selection Threshold (Input): A high on this pin sets the PORUP and PORDN registers to their upper threshold limits and a low to their lower threshold limits. Do not leave floating.         31       AVIN       Analog Voltage Supply (Input): The start-up sequence begins as soon as the AVIN pin voltage rises above the IC's UVLO upper threshold. The outputs do not turn off until AVIN pin voltage falls below the lower threshold limit. A 2.2µF ceramic capacitor from the AVIN pin to AGND pin must be placed next to the IC.         32       AGND       Analog Ground: Internal signal ground for all low power circuits. Connect directly to the layer 2 ground plane. Layer 2 is the point where all the PGNDs and AGND are connected. Do not connect PGND and AGND together on the top layer.         33       NC       No Connect. Must be left floating.         34       NC       No Connect. Must be left floating.         35       PG       Global Power Good (Output). This is an open drain output that is pulled high when all the regulator power good flags are high. If an output falls below the power good flags are                                                                                                                                                                                                         | 27         | SW1      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 29OUT1as close to output capacitor as possible to sense output voltage. This feature also provides the path to<br>discharge the output through an internal 900 resistor when disabled. The pull-down feature is<br>programmed through the PULLD[x] register.30VSLTPOR Selection Threshold (Input): A high on this pin sets the PORUP and PORDN registers to their<br>upper threshold limits and a low to their lower threshold limits. Do not leave floating.31AVINAnalog Voltage Supply (Input): The start-up sequence begins as soon as the AVIN pin voltage falls below<br>the lower threshold limit. A 2.2µF ceramic capacitor from the AVIN pin voltage falls below<br>the lower threshold limit. A 2.2µF ceramic capacitor from the AVIN pin voltage falls below<br>the lower threshold limit. A 2.2µF ceramic capacitor from the AVIN pin voltage falls below<br>the lower threshold limit. A 2.2µF ceramic capacitor from the AVIN pin voltage falls below<br>the lower threshold limit. A 2.2µF ceramic capacitor from the AVIN pin voltage falls below<br>the lower threshold limit. A 2.2µF ceramic capacitor from the AVIN pin voltage falls below<br>the lower threshold limit. A 2.2µF ceramic capacitor from the AVIN pin voltage falls below<br>the lower threshold limit. A 2.2µF ceramic capacitor from the AVIN pin voltage falls below<br>the lower threshold limit. A 2.2µF ceramic capacitor from the AVIN pin voltage falls below<br>the lower threshold limit. A 2.2µF ceramic capacitor from the AVIN pin voltage falls below<br>the lower threshold limit. A 2.2µF ceramic capacitor from the AVIN pin voltage falls below<br>the lower threshold limit. A 2.2µF ceramic capacitor from the AVIN pin voltage falls below<br>the lower to to he IC.32AGNDAlatog Ground: Internal signal ground for all low power circuits. Connect directly to the layer 2 ground<br>plane. Layer 2 is the point where all the PGNDs and AGND are conn | 28         | PGND1    | connects to the source of the internal low-side N-Channel MOSFET, the negative terminals of input                                                                                                                                                                                                                                                                                                                                                                                                           |

| 30VSL1upper threshold limits and a low to their lower threshold limits. Do not leave floating.31AVINAnalog Voltage Supply (Input): The start-up sequence begins as soon as the AVIN pin voltage rises<br>above the IC's UVLO upper threshold. The outputs do not turn off until AVIN pin voltage falls below<br>the lower threshold limit. A 2.2µF ceramic capacitor from the AVIN pin to AGND pin must be placed<br>next to the IC.32AGNDAnalog Ground: Internal signal ground for all low power circuits. Connect directly to the layer 2 ground<br>plane. Layer 2 is the point where all the PGNDs and AGND are connected. Do not connect PGND<br>and AGND together on the top layer.33NCNo Connect. Must be left floating.34NCNo Connect. Must be left floating.35PGGlobal Power Good (Output): This is an open drain output that is pulled high when all the regulator<br>power good flags are high. If an output falls below the power good threshold or a thermal fault occurs,<br>the global power good flag is pulled low. There is a falling edge de-glitch time of 50µs to prevent false<br>triggering on output voltage transients. A power good mask feature programmed through the<br>PGOD_MASK[x] registers can be used to ignore a power good fault. When masked an individual<br>power good fault will not cause the global power good output to de-assert. Do not connect the power<br>good pull-up resistor to a voltage higher than AV <sub>IN</sub> .36PGND2Power Ground 2: The power ground for the synchronous buck converter power stage. The PGND pin<br>connects to the source of the internal low-side N-Channel MOSFET, the negative terminals of input<br>capacitors, and the negative terminals of output capacitors.                                                                                                                                                                                                             | 29         | OUT1     | as close to output capacitor as possible to sense output voltage. This feature also provides the path to discharge the output through an internal $90\Omega$ resistor when disabled. The pull-down feature is                                                                                                                                                                                                                                                                                               |

| 31AVINabove the IC's UVLO upper threshold. The outputs do not turn off until AVIN pin voltage falls below<br>the lower threshold limit. A 2.2µF ceramic capacitor from the AVIN pin to AGND pin must be placed<br>next to the IC.32AGNDAnalog Ground: Internal signal ground for all low power circuits. Connect directly to the layer 2 ground<br>plane. Layer 2 is the point where all the PGNDs and AGND are connected. Do not connect PGND<br>and AGND together on the top layer.33NCNo Connect. Must be left floating.34NCNo Connect. Must be left floating.35PGGlobal Power Good (Output): This is an open drain output that is pulled high when all the regulator<br>power good flags are high. If an output falls below the power good threshold or a thermal fault occurs,<br>the global power good flag is pulled low. There is a falling edge de-glitch time of 50µs to prevent false<br>triggering on output voltage transients. A power good mask feature programmed through the<br>PGODD_MASK[X] registers can be used to ignore a power good fault. When masked an individual<br>power good fault will not cause the global power good output to de-assert. Do not connect the power<br>good pull-up resistor to a voltage higher than AV <sub>IN</sub> .36PGND2Power Ground 2: The power ground for the synchronous buck converter power stage. The PGND pin<br>connects to the source of the internal low-side N-Channel MOSFET, the negative terminals of input<br>capacitors, and the negative terminals of output capacitors.                                                                                                                                                                                                                                                                                                                                                                                                               | 30         | VSLT     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 32AGNDplane. Layer 2 is the point where all the PGNDs and AGND are connected. Do not connect PGND<br>and AGND together on the top layer.33NCNo Connect. Must be left floating.34NCNo Connect. Must be left floating.35PGGlobal Power Good (Output): This is an open drain output that is pulled high when all the regulator<br>power good flags are high. If an output falls below the power good threshold or a thermal fault occurs,<br>the global power good flag is pulled low. There is a falling edge de-glitch time of 50µs to prevent false<br>triggering on output voltage transients. A power good mask feature programmed through the<br>PGOOD_MASK[x] registers can be used to ignore a power good fault. When masked an individual<br>power good fault will not cause the global power good output to de-assert. Do not connect the power<br>good pull-up resistor to a voltage higher than AV <sub>IN</sub> .36PGND2Power Ground 2: The power ground for the synchronous buck converter power stage. The PGND pin<br>capacitors, and the negative terminals of output capacitors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 31         | AVIN     | above the IC's UVLO upper threshold. The outputs do not turn off until AVIN pin voltage falls below the lower threshold limit. A $2.2\mu$ F ceramic capacitor from the AVIN pin to AGND pin must be placed                                                                                                                                                                                                                                                                                                  |

| 34       NC       No Connect. Must be left floating.         35       PG       Global Power Good (Output): This is an open drain output that is pulled high when all the regulator power good flags are high. If an output falls below the power good threshold or a thermal fault occurs, the global power good flag is pulled low. There is a falling edge de-glitch time of 50µs to prevent false triggering on output voltage transients. A power good mask feature programmed through the PGOOD_MASK[x] registers can be used to ignore a power good fault. When masked an individual power good fault will not cause the global power good output to de-assert. Do not connect the power good pull-up resistor to a voltage higher than AV <sub>IN</sub> .         36       PGND2       Power Ground 2: The power ground for the synchronous buck converter power stage. The PGND pin connects to the source of the internal low-side N-Channel MOSFET, the negative terminals of input capacitors, and the negative terminals of output capacitors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 32         | AGND     | plane. Layer 2 is the point where all the PGNDs and AGND are connected. Do not connect PGND                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 35PGGlobal Power Good (Output): This is an open drain output that is pulled high when all the regulator<br>power good flags are high. If an output falls below the power good threshold or a thermal fault occurs,<br>the global power good flag is pulled low. There is a falling edge de-glitch time of 50µs to prevent false<br>triggering on output voltage transients. A power good mask feature programmed through the<br>PGOOD_MASK[x] registers can be used to ignore a power good fault. When masked an individual<br>power good fault will not cause the global power good output to de-assert. Do not connect the power<br>good pull-up resistor to a voltage higher than AV <sub>IN</sub> .36PGND2Power Ground 2: The power ground for the synchronous buck converter power stage. The PGND pin<br>connects to the source of the internal low-side N-Channel MOSFET, the negative terminals of input<br>capacitors, and the negative terminals of output capacitors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 33         | NC       | No Connect. Must be left floating.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 35PGpower good flags are high. If an output falls below the power good threshold or a thermal fault occurs,<br>the global power good flag is pulled low. There is a falling edge de-glitch time of 50µs to prevent false<br>triggering on output voltage transients. A power good mask feature programmed through the<br>PGOOD_MASK[x] registers can be used to ignore a power good fault. When masked an individual<br>power good fault will not cause the global power good output to de-assert. Do not connect the power<br>good pull-up resistor to a voltage higher than AVIN.36PGND2Power Ground 2: The power ground for the synchronous buck converter power stage. The PGND pin<br>connects to the source of the internal low-side N-Channel MOSFET, the negative terminals of input<br>capacitors, and the negative terminals of output capacitors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 34         | NC       | No Connect. Must be left floating.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 36 PGND2 connects to the source of the internal low-side N-Channel MOSFET, the negative terminals of input capacitors, and the negative terminals of output capacitors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 35         | PG       | power good flags are high. If an output falls below the power good threshold or a thermal fault occurs, the global power good flag is pulled low. There is a falling edge de-glitch time of 50µs to prevent false triggering on output voltage transients. A power good mask feature programmed through the PGOOD_MASK[x] registers can be used to ignore a power good fault. When masked an individual power good fault will not cause the global power good output to de-assert. Do not connect the power |

| EP ePad Exposed Pad: Must be connected to the GND plane for full output power to be realized.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 36         | PGND2    | connects to the source of the internal low-side N-Channel MOSFET, the negative terminals of input                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | EP         | ePad     | Exposed Pad: Must be connected to the GND plane for full output power to be realized.                                                                                                                                                                                                                                                                                                                                                                                                                       |

### Absolute Maximum Ratings<sup>(3)</sup>

| Supply Voltages (PV <sub>IN[1-6]</sub> )                   | 0.3V to 6V               |

|------------------------------------------------------------|--------------------------|

| Analog Supply Voltage (AV <sub>IN</sub> )                  | 0.3V to 6V               |

| Buck Output Voltages (V <sub>OUT[1-5]</sub> )              |                          |

| Boost Output Voltage (V <sub>OUT6</sub> )                  | 0.3V to 20V              |

| Buck Switch Voltages (V <sub>SW[1-5]</sub> )               |                          |

| Boost Switch Voltage (V <sub>SW6</sub> ).                  | 0.3V to 20V              |

| Power Good Voltage (V <sub>PG</sub> )                      |                          |

| Power-On Reset Output (V <sub>POR</sub> )                  | 0.3V to 6V               |

| POR Threshold Voltage (V <sub>VSLT</sub> )                 | 0.3V to 6V               |

| Standby Voltage (V <sub>STBY</sub> )                       | 0.3V to 6V               |

| I <sup>2</sup> C IO (V <sub>SDA</sub> , V <sub>SCL</sub> ) | 0.3V to AV <sub>IN</sub> |

| AGND to PGND[1-6]                                          | 0.3V to 0.3V             |

| Ambient Storage Temperature (Ts)                           | 40°C to +150°C           |

| ESD HBM Rating <sup>(6)</sup>                              | 2kV                      |

| ESD MM Rating                                              |                          |

|                                                            |                          |

## **Operating Ratings**<sup>(4)</sup>

| Input Voltage (PV <sub>IN[1-6]</sub> )<br>Analog Input Voltage (AV <sub>IN</sub> ) |             |

|------------------------------------------------------------------------------------|-------------|

| Buck Output Voltage Range (V <sub>OUT[1-5]</sub> )                                 |             |

| Boost Output Voltage Range (V <sub>OUT[1-5]</sub> )                                |             |

| Power Good Voltage (V <sub>PG</sub> )                                              |             |

| Power-On Reset Output (V <sub>PG</sub> )                                           |             |

| POR Threshold Voltage (V <sub>VSLT</sub> )                                         |             |

| Standby Voltage (V <sub>STBY</sub> )                                               |             |

| $I^2C IO (V_{SDA}, V_{SCL})$                                                       |             |

| Junction Temperature $(T_{,j})^{(5)}$ 40°                                          |             |

| Junction Thermal Resistance                                                        | 0 10 1 20 0 |

| 4.5mm × 4.5mm FQFN-36 (θ <sub>JA</sub> )                                           | 30°C/W      |

# Electrical Characteristics<sup>(7)</sup>

$V_{IN} = AV_{IN} = PV_{IN(1-6)} = 5.0V$ ;  $V_{OUT1} = 1.8V$ ;  $V_{OUT2} = 1.1V$ ;  $V_{OUT3} = 1.8V$ ;  $V_{OUT4} = 1.05V$ ;  $V_{OUT5} = 1.25V$ ;  $V_{OUT6} = 12V$  (refer to the *Evaluation Board Schematic* for component values). T<sub>A</sub> = 25°C, unless otherwise noted. **Bold** values indicate  $-40°C \le T_J \le +125°C$ .

| Parameter                                                              | Conditions                                    | Min. | Тур. | Max. | Unit |

|------------------------------------------------------------------------|-----------------------------------------------|------|------|------|------|

| Input Supply (VIN)                                                     |                                               |      |      |      |      |

| Input Voltage Range (AV <sub>IN</sub> , PV <sub>IN[1-6]</sub> )        |                                               | 2.4  |      | 5.5  | V    |

| Operating Quiescent Current<br>into AV <sub>IN</sub> <sup>(8, 9)</sup> | V <sub>IN</sub> = 5.0V; I <sub>OUT</sub> = 0A |      | 200  | 240  | μA   |

| Operating Quiescent Current<br>into PV <sub>IN</sub> <sup>(8)</sup>    | V <sub>IN</sub> = 5.0V; I <sub>OUT</sub> = 0A |      | 0.3  | 1    | μA   |

| Undervoltage Lockout Threshold                                         | AV <sub>IN</sub> Rising                       | 2.15 | 2.25 | 2.35 | V    |

| Undervoltage Lockout Hysteresis                                        |                                               |      | 150  |      | mV   |

| Standby Input (STBY)                                                   |                                               |      |      |      |      |

| Logic Level High                                                       |                                               | 1.2  |      |      | V    |

| Logic Level Low                                                        |                                               |      |      | 0.4  | V    |

| Bias Current into Pin                                                  | V <sub>STBY</sub> = V <sub>IN</sub>           |      |      | 200  | nA   |

| Bias Current out of Pin                                                | $V_{STBY} = 0V$                               |      |      | 200  | nA   |

| Rising/Falling Edge Reset Deglitch                                     |                                               |      | 100  |      | μs   |

#### Notes:

3. Absolute maximum ratings indicate limits beyond which damage to the component may occur.

4. The device is not guaranteed to function outside its operating rating.

5. The maximum allowable power dissipation is a function of the maximum junction temperature,  $T_{J(Max)}$ , the junction-to-ambient thermal resistance,  $\theta_{JA}$ , and the ambient temperature,  $T_A$ . The maximum allowable power dissipation will result in excessive die temperature, and the regulator will go into thermal shutdown.

$6. \quad \text{Devices are ESD sensitive. Handling precautions recommended. Human body model, } 1.5 \text{k}\Omega \text{ in series with } 100 \text{pF.}$

7. Specification for packaged product only.

8. Tested in a non-switching configuration.

9. When all outputs are configured to the minimum programmable voltage.

$V_{IN} = AV_{IN} = PV_{IN(1-6)} = 5.0V; V_{OUT1} = 1.8V; V_{OUT2} = 1.1V; V_{OUT3} = 1.8V; V_{OUT4} = 1.05V; V_{OUT5} = 1.25V; V_{OUT6} = 12V \text{ (refer to the Evaluation Board Schematic} for component values). T_A = 25°C, unless otherwise noted.$ **Bold** $values indicate <math>-40°C \le T_J \le +125°C$ .

| Parameter                               | Conditions                             | Min.  | Тур.     | Max.  | Unit              |

|-----------------------------------------|----------------------------------------|-------|----------|-------|-------------------|

| POR Threshold Input (VSLT)              |                                        |       |          |       | -                 |

| Logic Level High                        |                                        | 1.2   |          |       | V                 |

| Logic Level Low                         |                                        |       |          | 0.4   | V                 |

| Bias Current Into Pin                   | $V_{VSLT} = V_{IN}$                    |       |          | 200   | nA                |

| Bias Current Out of Pin                 | $V_{VSLT} = 0V$                        |       |          | 200   | nA                |

| Power-On-Reset (POR) Comparator         |                                        |       |          |       | -                 |

| POR Upper Comparator Range              | $AV_{IN}$ Rising, $V_{VSLT} = 0V$      | 2.646 | 2.7      | 2.754 | V                 |

| POR Lower Comparator Range              | $AV_{IN}$ Falling, $V_{VSLT} = 0V$     | 2.548 | 2.6      | 2.652 | V                 |