# **MIC45404**

## 19V 5A Ultra-Low Profile DC-to-DC Power Module

#### Features

- Input Voltage Range: 4.5V to 19V

- · Output Current: Up to 5A

- 82% Peak Efficiency at 12 V<sub>IN</sub>, 0.9 V<sub>OUT</sub>

- Pin-Selectable Output Voltages: 0.7V, 0.8V, 0.9V, 1.0V, 1.2V, 1.5V, 1.8V, 2.5V, 3.3V

- ±1% Output Voltage Accuracy

- Supports Safe Pre-Biased Start-up

- Pin-Selectable Current Limit

- Pin-Selectable Switching Frequency

- · Internal Soft Start

- · Thermal Shutdown

- Hiccup Mode Short-Circuit Protection

- Available in a 54-Lead 6 mm x 10 mm QFN

Package

- · Ultra-Low Profile: 2.0 mm Height

- -40°C to +125°C Junction Temperature Range

#### Applications

- · Servers, Data Storage, Routers and Base Stations

- · FPGAs, DSP and Low-Voltage ASIC Power

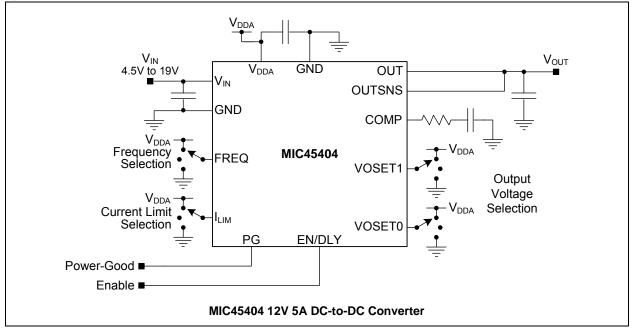

#### **Typical Application**

#### **General Description**

The MIC45404 device is an ultra-low profile, synchronous step-down regulator module, featuring a unique 2.0 mm height. The module incorporates a DC-to-DC regulator, bootstrap capacitor, high-frequency input capacitor and an inductor in a single package. The module pinout is optimized to simplify the Printed Circuit Board (PCB) layout process.

This highly integrated solution expedites system design and improves product time to market. The internal MOSFETs and inductor are optimized to achieve high efficiency at low output voltage. Due to the fully optimized design, MIC45404 can deliver up to 5A current with a wide input voltage range of 4.5V to 19V.

The MIC45404 is available in a 54-lead 6 mm x 10 mm x 2.0 mm QFN package with a junction operating temperature range from  $-40^{\circ}$ C to  $+125^{\circ}$ C, which makes an excellent solution for systems in which PCB real-estate and height are important limiting factors, and air flow is restricted.

## **MIC45404**

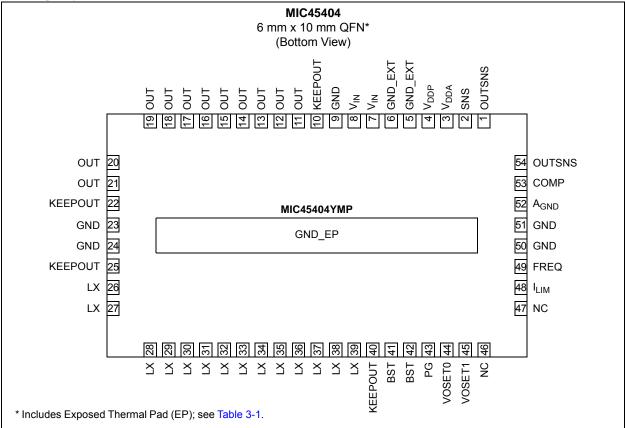

#### **Package Types**

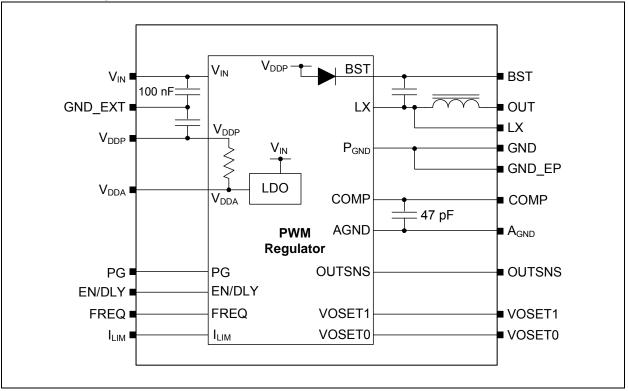

#### **Functional Diagram**

#### 1.0 ELECTRICAL CHARACTERISTICS

#### Absolute Maximum Ratings†

| V <sub>IN</sub> to A <sub>GND</sub>                     | 0.3V to +20V                         |

|---------------------------------------------------------|--------------------------------------|

| V <sub>DDP</sub> , V <sub>DDA</sub> to A <sub>GND</sub> | -0.3V to +6V                         |

| V <sub>DDP</sub> to V <sub>DDA</sub>                    | 0.3V to +0.3V                        |

| VOSETX, FREQ, I <sub>LIM</sub> , to A <sub>GND</sub>    | -0.3V to +6V                         |

| BST to LX                                               | -0.3V to +6V                         |

| BST to A <sub>GND</sub>                                 | 0.3V to +26V                         |

| EN/DLY to A <sub>GND</sub>                              |                                      |

| PG to A <sub>GND</sub>                                  | -0.3V to +6V                         |

| COMP, OUTSNS to A <sub>GND</sub>                        | 0.3V to V <sub>DDA</sub> + 0.3V, +6V |

| A <sub>GND</sub> to GND                                 | -0.3V to +0.3V                       |

| Junction Temperature                                    | +150°C                               |

| Storage Temperature (T <sub>S</sub> )                   | 65°C to +150°C                       |

| Lead Temperature (soldering, 10s)                       |                                      |

| ESD Rating <sup>(1)</sup>                               |                                      |

| НВМ                                                     | 2kV                                  |

| MM                                                      |                                      |

| CDM                                                     | 1500V                                |

**hotice:** Stresses above those listed under "Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operational sections of this specification is not intended. Exposure to maximum rating conditions for extended periods may affect device reliability.

Note 1: Devices are ESD-sensitive. Handling precautions are recommended. Human body model, 1.5 k $\Omega$  in series with 100 pF.

#### Operating Ratings<sup>(1)</sup>

| Supply Voltage (V <sub>IN</sub> )                                                     | 4.5V to 19V            |

|---------------------------------------------------------------------------------------|------------------------|

| Externally Applied Analog and Drivers Supply Voltage ( $V_{IN} = V_{DDA} = V_{DDP}$ ) | 4.5V to 5.5V           |

| Enable Voltage (EN/DLY)                                                               | 0V to V <sub>DDA</sub> |

| Power Good (PG) Pull-up Voltage (VPU_PG)                                              | 0V to 5.5V             |

| Output Current                                                                        | 5A                     |

| Junction Temperature (T <sub>J</sub> )                                                | 40°C to +125°C         |

| <b>Note 1:</b> The device is not ensured to function outside the operating range.     |                        |

### ELECTRICAL CHARACTERISTICS<sup>(1)</sup>

**Electrical Specifications:** unless otherwise specified,  $V_{IN} = 12V$ ;  $C_{VDDA} = 2.2 \ \mu$ F,  $T_A = +25^{\circ}$ C. **Boldface** values indicate -40°C < T + +125°C.

| <b>Boldface</b> values indicate $-40^{\circ}C \le T_{J} \le +125^{\circ}C$ . |                        |      |                        |      |                 |                                                                      |

|------------------------------------------------------------------------------|------------------------|------|------------------------|------|-----------------|----------------------------------------------------------------------|

| Parameter                                                                    | Symbol                 | Min. | Тур.                   | Max. | Units           | Test Conditions                                                      |

| V <sub>IN</sub> Supply                                                       |                        |      |                        |      |                 |                                                                      |

| Input Range                                                                  | V <sub>IN</sub>        | 4.5  |                        | 19   | V               |                                                                      |

| Disable Current                                                              | I <sub>VINQ</sub>      | _    | 33                     | 60   | μA              | EN/DLY = 0V                                                          |

| Operating Current                                                            | I <sub>VINOp</sub>     | _    | 5.35                   | 8.5  | mA              | EN/DLY > 1.28V,<br>OUTSNS = 1.15 x $V_{OUT(NOM)}$ ,<br>no switching  |

| V <sub>DDA</sub> 5V Supply                                                   |                        |      |                        |      |                 |                                                                      |

| Operating Voltage                                                            | V <sub>DDA</sub>       | 4.8  | 5.1                    | 5.4  | V               | EN/DLY > 0.58V,<br>I <sub>VDDA</sub> = 0 mA to 10 mA                 |

| Dropout Operation                                                            |                        | 3.6  | 3.75                   | _    | V               | V <sub>IN</sub> = 4.5V, EN/DLY > 0.58V,<br>I <sub>VDDA</sub> = 10 mA |

| V <sub>DDA</sub> Undervoltage Lockout                                        |                        |      |                        |      |                 |                                                                      |

| V <sub>DDA</sub> UVLO Rising                                                 | UVLO_R                 | 3.1  | 3.5                    | 3.9  | V               | V <sub>DDA</sub> Rising, EN/DLY > 1.28V                              |

| V <sub>DDA</sub> UVLO Falling                                                | UVLO_F                 | 2.87 | 3.2                    | 3.45 | V               | V <sub>DDA</sub> Falling, EN/DLY > 1.28V                             |

| V <sub>DDA</sub> UVLO Hysteresis                                             | UVLO_H                 | _    | 300                    | _    | mV              |                                                                      |

| EN/DLY Control                                                               |                        |      |                        |      |                 |                                                                      |

| LDO Enable Threshold                                                         | EN_LDO_R               | _    | 515                    | 600  | mV              | Turns on V <sub>DDA</sub> LDO                                        |

| LDO Disable Threshold                                                        | EN_LDO_F               | 450  | 485                    |      | mV              | Turns off V <sub>DDA</sub> LDO                                       |

| LDO Threshold Hysteresis                                                     | EN_LDO_H               | _    | 30                     |      | mV              |                                                                      |

| EN/DLY Rising Threshold                                                      | EN_R                   | 1.14 | 1.21                   | 1.28 | V               | Initiates power stage operation                                      |

| EN/DLY Falling Threshold                                                     | EN_F                   | _    | 1.06                   | _    | V               | Stops power stage operation                                          |

| EN/DLY Hysteresis                                                            | EN_H                   | _    | 150                    | _    | mV              |                                                                      |

| EN/DLY Pull-up Current                                                       | EN_I                   | 1    | 2                      | 3    | μA              |                                                                      |

| Switching Frequency                                                          |                        |      |                        |      |                 |                                                                      |

| Programmable<br>Frequency (High Z)                                           | f <sub>SZ</sub>        | 360  | 400                    | 440  | kHz             | FREQ = High Z (open)                                                 |

| Programmable Frequency 0                                                     | f <sub>S0</sub>        | 500  | 565                    | 630  | kHz             | FREQ= Low (GND)                                                      |

| Programmable Frequency 1                                                     | f <sub>S1</sub>        | 700  | 790                    | 880  | kHz             | FREQ = High (V <sub>DDA</sub> )                                      |

| Overcurrent Protection                                                       |                        |      |                        |      |                 |                                                                      |

| HS Current Limit 0                                                           | I <sub>LIM_HS0</sub>   | 6.0  | 7.1                    | 8.1  | А               | I <sub>LIM</sub> = Low (GND)                                         |

| HS Current Limit 1                                                           | I <sub>LIM_HS1</sub>   | 8.1  | 9.3                    | 10.3 | А               | I <sub>LIM</sub> = High (V <sub>DDA</sub> )                          |

| HS Current Limit High Z                                                      | I <sub>LIM_HSZ</sub>   | 9.3  | 10.5                   | 11.9 | А               | I <sub>LIM</sub> = High Z (open)                                     |

| Top FET Current Limit<br>Leading-Edge Blanking Time                          | LEB                    | _    | 108                    | _    | ns              |                                                                      |

| LS Current Limit 0                                                           | I <sub>LIM_LS0</sub>   | 3.0  | 4.6                    | 6.3  | А               | I <sub>LIM</sub> = Low (GND)                                         |

| LS Current Limit 1                                                           | I <sub>LIM_LS1</sub>   | 4.0  | 6.2                    | 7.9  | А               | I <sub>LIM</sub> = High (V <sub>DDA</sub> )                          |

| LS Current Limit High Z                                                      | I <sub>LIM_LSZ</sub>   | 5.0  | 6.8                    | 8.6  | А               | I <sub>LIM</sub> = High Z (Open)                                     |

| OC Events Count for Hiccup                                                   | IN <sub>HICC_DE</sub>  | —    | 15                     | _    | Clock<br>Cycles | Number of subsequent cycles                                          |

| Hiccup Wait Time                                                             | <sup>t</sup> HICC_WAIT |      | 3 x Soft<br>Start Time |      |                 | Duration of the High Z state on LX before new soft start.            |

**Note 1:** Specification for packaged product only.

### ELECTRICAL CHARACTERISTICS<sup>(1)</sup> (CONTINUED)

**Electrical Specifications:** unless otherwise specified,  $V_{IN} = 12V$ ;  $C_{VDDA} = 2.2 \ \mu\text{F}$ ,  $T_A = +25^{\circ}\text{C}$ . **Boldface** values indicate -40°C  $\leq T_{I} \leq +125^{\circ}\text{C}$ .

| Boldface values indicate -40°                 | $C \le T_J \le +125^\circ$ | C.   |       |      |       |                                                                                                                                                   |

|-----------------------------------------------|----------------------------|------|-------|------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameter                                     | Symbol                     | Min. | Тур.  | Max. | Units | Test Conditions                                                                                                                                   |

| Pulse-Width Modulation (PV                    | VM)                        |      |       |      |       |                                                                                                                                                   |

| Minimum LX On Time                            | T <sub>ON(MIN)</sub>       | _    | 26    | _    | ns    | $T_A = T_J = +25^{\circ}C$                                                                                                                        |

| Minimum LX Off time                           | T <sub>OFF(MIN)</sub>      | 90   | 135   | 190  | ns    | $V_{IN} = V_{DDA} = 5V$ , OUTSNS = 3V,<br>FREQ = Open (400 kHz setting),<br>VOSET0 = VOSET1 = 0V<br>(3.3V setting),<br>$T_A = T_J = +25^{\circ}C$ |

| Minimum Duty Cycle                            | D <sub>MIN</sub>           | _    | 0     | —    | %     | OUTSNS > $1.1 \times V_{OUT(NOM)}$                                                                                                                |

| Gm Error Amplifier                            |                            |      |       |      |       |                                                                                                                                                   |

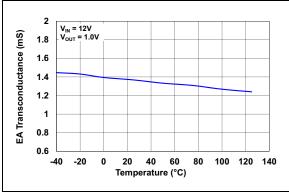

| Error Amplifier<br>Transconductance           | Gm <sub>EA</sub>           | —    | 1.4   | —    | mS    |                                                                                                                                                   |

| Error Amplifier DC Gain                       | A <sub>EA</sub>            | —    | 50000 | —    | V/V   |                                                                                                                                                   |

| Error Amplifier Source/Sink<br>Current        | I <sub>SR_SNK</sub>        | -400 | _     | +400 | μA    | $T_A = T_J = +25^{\circ}C$                                                                                                                        |

| COMP Output Swing High                        | COMP_H                     | _    | 2.5   | —    | V     |                                                                                                                                                   |

| COMP Output Swing Low                         | COMP_L                     | —    | 0.8   | —    | V     |                                                                                                                                                   |

| COMP-to-Inductor Current<br>Transconductance  | Gm <sub>PS</sub>           | —    | 12.5  | —    | A/V   | V <sub>OUT</sub> = 1.2V, I <sub>OUT</sub> = 4A                                                                                                    |

| Output Voltage DC Accuracy                    | y                          |      |       |      |       |                                                                                                                                                   |

| Output Voltage Accuracy for<br>Ranges 1 and 2 | OutErr12                   | -1   | _     | 1    | %     |                                                                                                                                                   |

| Output Voltage Accuracy for<br>Range 3        | OutErr3                    | -1.5 | _     | 1.5  | %     |                                                                                                                                                   |

| Load Regulation                               | LoadReg                    | —    | 0.03  | —    | %     | I <sub>OUT</sub> = 0A to 5A                                                                                                                       |

| Line Regulation                               | LineReg                    | _    | 0.01  | —    | %     | 6V < V <sub>IN</sub> < 19V, I <sub>OUT</sub> = 2A                                                                                                 |

| Internal Soft Start                           |                            |      |       |      |       |                                                                                                                                                   |

| Reference Soft Start<br>Slew Rate             | SS_SR                      | —    | 0.42  | —    | V/ms  | V <sub>OUT</sub> = 0.7V, 0.8V, 0.9V,<br>1.0V, 1.2V                                                                                                |

| Power Good (PG)                               |                            |      |       |      |       | ·                                                                                                                                                 |

| PG Low Voltage                                | PG_V <sub>OL</sub>         | _    | 0.17  | 0.4  | V     | I <sub>PG</sub> = 4 mA                                                                                                                            |

| PG Leakage Current                            | PG_I <sub>LEAK</sub>       | -1   | 0.02  | 1    | μA    | PG = 5V                                                                                                                                           |

| PG Rise Threshold                             | PG_R                       | 90   | 92    | 95   | %     | V <sub>OUT</sub> Rising                                                                                                                           |

| PG Fall Threshold                             | PG_F                       | 87.5 | 90    | 92.5 | %     | V <sub>OUT</sub> Falling                                                                                                                          |

| PG Rise Delay                                 | PG_R_DLY                   |      | 0.45  |      | ms    | V <sub>OUT</sub> Rising                                                                                                                           |

| PG Fall Delay                                 | PG_F_DLY                   | _    | 80    | _    | μs    | V <sub>OUT</sub> Falling                                                                                                                          |

**Note 1:** Specification for packaged product only.

### ELECTRICAL CHARACTERISTICS<sup>(1)</sup> (CONTINUED)

**Electrical Specifications:** unless otherwise specified,  $V_{IN}$  = 12V;  $C_{VDDA}$ = 2.2 µF,  $T_A$  = +25°C. **Boldface** values indicate -40°C  $\leq T_J \leq$  +125°C.

|                                | 0 - 1 - 1 - 1 - 1 - 2 0 | 0.   |      |      |       |                                                                                                                   |

|--------------------------------|-------------------------|------|------|------|-------|-------------------------------------------------------------------------------------------------------------------|

| Parameter                      | Symbol                  | Min. | Тур. | Max. | Units | Test Conditions                                                                                                   |

| Thermal Shutdown               |                         |      |      |      |       |                                                                                                                   |

| Thermal Shutdown               | T <sub>SHDN</sub>       | —    | 160  | —    | °C    |                                                                                                                   |

| Thermal Shutdown<br>Hysteresis | T <sub>SHDN_HYST</sub>  | —    | 25   | —    | °C    |                                                                                                                   |

| Efficiency                     | Efficiency              |      |      |      |       |                                                                                                                   |

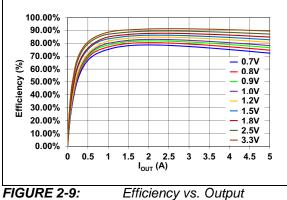

| Efficiency                     | η                       | —    | 82   | —    | %     | $V_{IN} = 12V, V_{OUT} = 0.9V,$<br>$I_{OUT} = 2A, f_S = f_{SZ} = 400 \text{ kHz},$<br>$T_A = +25^{\circ}\text{C}$ |

Note 1: Specification for packaged product only.

#### **TEMPERATURE SPECIFICATIONS**

| <b>Electrical Specifications:</b> unless otherwise specified, $V_{IN}$ = 12V; $C_{VDDA}$ = 2.2 µF, $T_A$ = +25°C.<br><b>Boldface</b> values indicate -40°C $\leq T_J \leq$ +125°C. |                |      |      |      | +25°C. |                                                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------|------|------|--------|-------------------------------------------------|

| Parameters                                                                                                                                                                         | Sym.           | Min. | Тур. | Max. | Units  | Conditions                                      |

| Temperature Ranges                                                                                                                                                                 |                |      |      |      |        |                                                 |

| Operating Ambient Junction Range                                                                                                                                                   | TJ             | -40  | _    | +125 | °C     |                                                 |

| Storage Temperature Range                                                                                                                                                          | T <sub>A</sub> | -65  | —    | +150 | °C     |                                                 |

| Maximum Junction Temperature                                                                                                                                                       | TJ             | -40  | _    | +150 | °C     |                                                 |

| Package Thermal Resistances                                                                                                                                                        |                |      |      |      |        |                                                 |

| Thermal Resistance, 54 Lead,<br>6 mm x10 mm QFN                                                                                                                                    | $\theta_{JA}$  | _    | 20   | —    | °C/W   | See "MIC45404 Evaluation<br>Board User's Guide" |

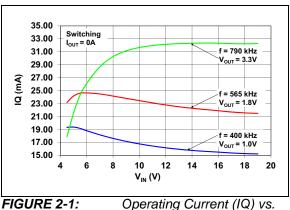

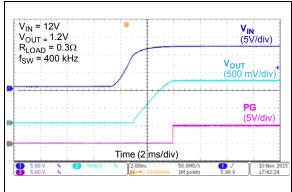

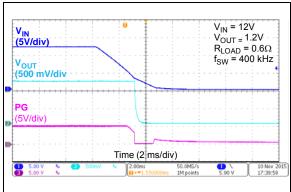

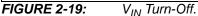

#### 2.0 TYPICAL PERFORMANCE CURVES

Note: Unless otherwise indicated, V<sub>IN</sub> = 12V; C<sub>VDDA</sub>= 2.2 µF, T<sub>A</sub> = +25°C.

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore outside the warranted range.

FIGURE 2-1: Input Voltage.

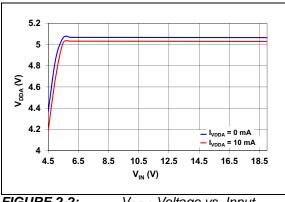

FIGURE 2-2: V<sub>DDA</sub> Voltage vs. Input Voltage.

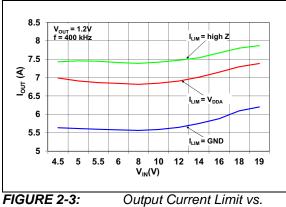

Input Voltage.

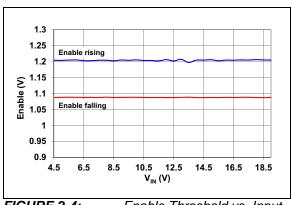

FIGURE 2-4: Enable Threshold vs. Input Voltage.

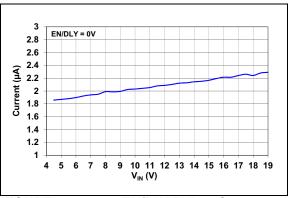

FIGURE 2-5: EN/DLY Pull-up Current vs. Input Voltage.

## **MIC45404**

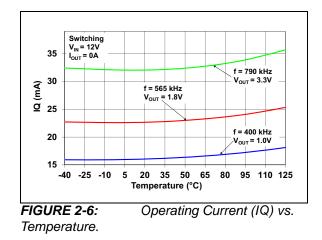

Note: Unless otherwise indicated,  $V_{IN}$  = 12V;  $C_{VDDA}$ = 2.2 µF,  $T_A$  = +25°C.

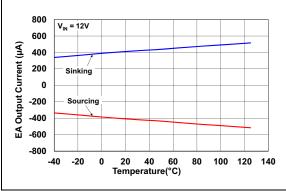

**FIGURE 2-7:** EA Output Current vs. Temperature.

FIGURE 2-8: EA Transconductance vs. Temperature.

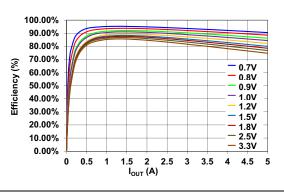

**FIGURE 2-9:** Efficience Current ( $V_{IN} = 12V$ ).

**FIGURE 2-10:** Efficiency vs. Output Current ( $V_{IN} = 5V$ ).

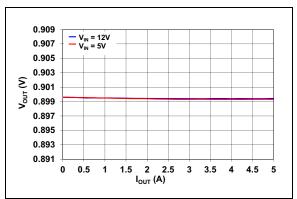

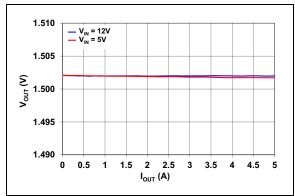

**FIGURE 2-11:** Output Voltage vs. Output Current ( $V_{OUT} = 0.9V$ ).

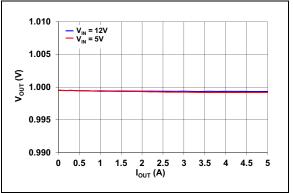

**FIGURE 2-12:** Output Voltage vs. Output Current ( $V_{OUT} = 1.0V$ ).

Note: Unless otherwise indicated, V<sub>IN</sub> = 12V; C<sub>VDDA</sub>= 2.2  $\mu$ F, T<sub>A</sub> = +25°C.

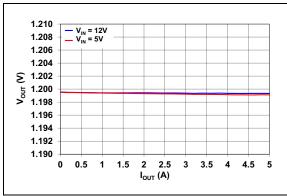

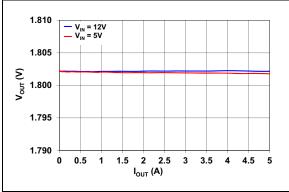

**FIGURE 2-13:** Output Voltage vs. Output Current ( $V_{OUT} = 1.2V$ ).

**FIGURE 2-14:** Output Voltage vs. Output Current ( $V_{OUT} = 1.5V$ ).

**FIGURE 2-15:** Output Voltage vs. Output Current ( $V_{OUT} = 1.8V$ ).

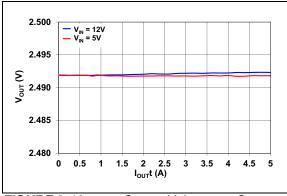

**FIGURE 2-16:** Output Voltage vs. Output Current ( $V_{OUT} = 2.5V$ ).

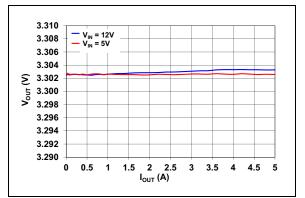

**FIGURE 2-17:** Output Voltage vs. Output Current ( $V_{OUT} = 3.3V$ ).

## MIC45404

Note: Unless otherwise indicated,  $V_{IN}$  = 12V;  $C_{VDDA}$ = 2.2 µF,  $T_A$  = +25°C.

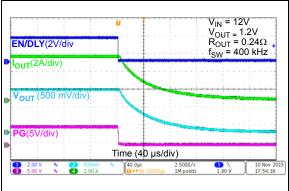

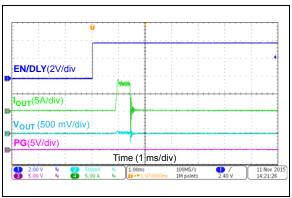

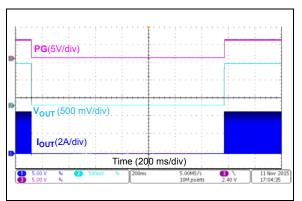

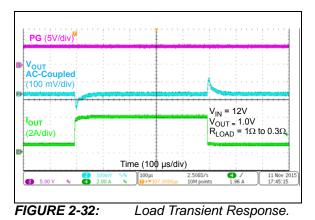

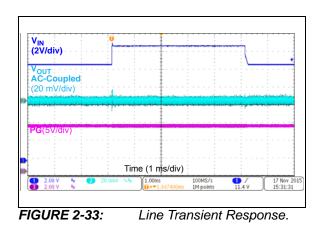

FIGURE 2-20: Enable Turn-On.

FIGURE 2-21: Enable Turn-Off.

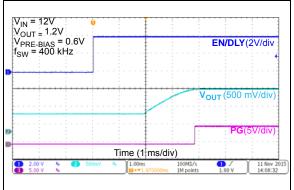

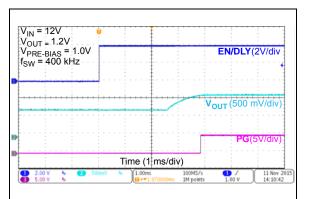

FIGURE 2-22: Enable Start-up w/Pre-Biased Output.

FIGURE 2-23: Enable Start-up w/Pre-Biased Output.

Note: Unless otherwise indicated, V<sub>IN</sub> = 12V; C<sub>VDDA</sub>= 2.2  $\mu$ F, T<sub>A</sub> = +25°C.

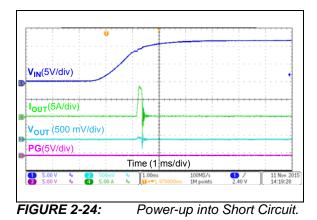

FIGURE 2-25:

Enable into Short Circuit.

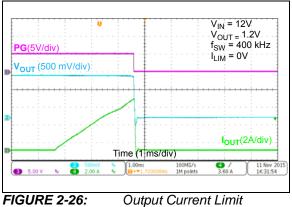

**FIGURE 2-26** (*I*<sub>LIM</sub> = 0V).

Output Curren

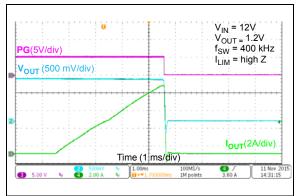

**FIGURE 2-27:** Output Current Limit  $(I_{LIM} = High Z)$ .

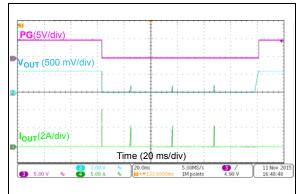

FIGURE 2-28: Hiccup Mode Short Circuit and Output Recovery.

**FIGURE 2-29:** Thermal Shutdown and Thermal Recovery.

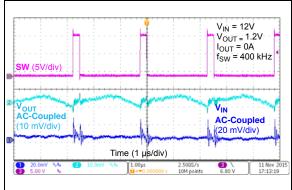

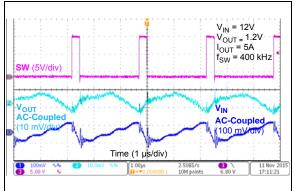

Note: Unless otherwise indicated, V\_{IN} = 12V; C\_{VDDA}= 2.2 \ \mu\text{F}, T\_A = +25^{\circ}\text{C}.

**FIGURE 2-31:** Switching Waveforms  $(I_{OUT} = 5A)$ .

#### 3.0 PIN DESCRIPTION

The descriptions of the pins are listed in Table 3-1.

| MIC45404                                                  | Symbol           | Pin Function                              |

|-----------------------------------------------------------|------------------|-------------------------------------------|

| 1, 54                                                     | OUTSNS           | Output Sensing Pin                        |

| 2                                                         | EN/DLY           | Precision Enable/Turn-On Delay Input Pin  |

| 3                                                         | V <sub>DDP</sub> | MOSFET Drivers Internal Supply Pin        |

| 4                                                         | V <sub>DDA</sub> | Internal LDO Output and Analog Supply Pin |

| 5, 6                                                      | GND_EXT          | Ground Extension Pins                     |

| 7, 8                                                      | V <sub>IN</sub>  | Input Voltage Pins                        |

| 9, 23, 24, 50, 51                                         | GND              | Power Ground Pins                         |

| 11, 12, 13, 14, 15, 16, 17, 18,<br>19, 20, 21             | OUT              | Output Side Connection Pins               |

| 10, 22, 25, 40                                            | KEEPOUT          | Depopulated Pin Positions                 |

| 26, 27, 28, 29, 30, 31, 32, 33,<br>34, 35, 36, 37, 38, 39 | LX               | Switch Node Pins                          |

| 41, 42                                                    | BST              | Bootstrap Capacitor Pin                   |

| 43                                                        | PG               | Power Good Output Pin                     |

| 44                                                        | VOSET0           | Output Voltage Selection Pins             |

| 45                                                        | VOSET1           |                                           |

| 46, 47                                                    | NC               | Not Connected Pins                        |

| 48                                                        | I <sub>LIM</sub> | Current Limit Selection Pin               |

| 49                                                        | FREQ             | Switching Frequency Selection Pin         |

| 52                                                        | A <sub>GND</sub> | Analog Ground Pin                         |

| 53                                                        | COMP             | Compensation Network Pin                  |

| 55                                                        | GND_EP           | Ground Exposed Pad.                       |

#### TABLE 3-1: PIN FUNCTION TABLE

#### 3.1 Output Sensing Pins (OUTSNS)

Connect these pins directly to the Buck Converter output voltage. These pins are the top side terminal of the internal feedback divider.

#### 3.2 Precision Enable/Turn-On Delay Input Pin (EN/DLY)

The EN/DLY pin is first compared against a 515 mV threshold to turn on the on-board LDO regulator. The EN/DLY pin is then compared against a 1.21V (typical) threshold to initiate output power delivery. A 150 mV typical hysteresis prevents chattering when power delivery is started. A 2  $\mu$ A (typical) current source pulls up the EN/DLY pin. Turn-on delay can be achieved by connecting a capacitor from EN/DLY to ground, while using an open-drain output to drive the EN/DLY pin.

#### 3.3 MOSFET Drivers Internal Supply Pin (V<sub>DDP</sub>)

Internal supply rail for the MOSFET drivers, fed by the  $V_{DDA}$  pin. An internal resistor (10 $\Omega$ ) between the  $V_{DDP}$  and  $V_{DDA}$  pins, and an internal decoupling capacitor are provided in the module in order to implement an RC filter for switching noise suppression.

#### 3.4 Internal Regulator Output Pin (V<sub>DDA</sub>)

Output of the internal linear regulator and internal supply for analog control. A 1  $\mu$ F minimum ceramic capacitor should be connected from this pin to GND; a 2.2  $\mu$ F nominal value is recommended.

#### 3.5 Ground Extension Pins (GND\_EXT)

These pins are used for the bottom terminal connection of the internal V<sub>IN</sub> and V<sub>DDP</sub> decoupling capacitors. The GND\_EXT pins should be connected to the GND net, directly at the top layer, using a wide copper connection.

#### 3.6 Input Voltage Pins (V<sub>IN</sub>)

Input voltage for the Buck Converter power stage and input of the internal linear regulator. These pins are the drain terminal of the internal high-side N-channel MOSFET. A 10  $\mu F$  (minimum) ceramic capacitor should be connected from  $V_{IN}$  to GND, as close as possible to the device.

#### 3.7 Power Ground Pins (GND)

Connect the output capacitors to GND Pins 23 and 24, as close as possible to the module.

Connect the input capacitors to GND Pin 9, as close as possible to the module.

#### 3.8 Output-Side Connection Pins (OUT)

Output side connection of the internal inductor. The output capacitors should be connected from this pin group to GND (Pins 23 and 24), as close to the module as possible.

#### 3.9 Switch Node Pins (LX)

Switch Node: Drain (low-side MOSFET) and source (high-side MOSFET) connection of the internal power N-channel FETs. The internal inductor switched side and the bootstrap capacitor are connected to LX. Leave this pin floating.

#### 3.10 Bootstrap Capacitor Pin (BST)

Connection to the internal bootstrap capacitor and high-side power MOSFET drive circuitry. Leave this pin floating.

#### 3.11 Power Good Output Pin (PG)

When the output voltage is within 92.5% of the nominal set point, this pin will go from logic low to logic high through an external pull-up resistor. This pin is the drain connection of an internal N-channel FET.

## 3.12 Output Voltage Selection Pins (VOSET0 and VOSET1)

Three-state pin (low, high and High Z) for output voltage programming. Both VOSET0 and VOSET1 define 9 logic values, corresponding to nine output voltage selections.

#### 3.13 Not Connected Pins (NC)

These pins are not internally connected. Leave them floating.

#### 3.14 Current Limit Pin (ILIM)

This pin allows the selection of the current limit state: low, high and High Z.

#### 3.15 Switching Frequency Pin (FREQ)

This pin allows the selection of the frequency state: low, high and High Z.

#### 3.16 Analog Ground Pin (A<sub>GND</sub>)

This pin is a quiet ground for the analog circuitry of the internal regulator and a return terminal for the external compensation network.

#### 3.17 Compensation Network Pin (COMP)

Connect a compensation network from this pin to  $\mathsf{A}_{\text{GND}}.$

#### 3.18 GND Exposed Pad

Connect to ground plane with thermal vias.

#### 4.0 FUNCTIONAL DESCRIPTION

The MIC45404 is a pin-programmable, 5A Valley Current mode controlled power module, with an input voltage range from 4.5V to 19V.

The MIC45404 requires a minimal amount of external components. Only two supply decoupling capacitors and a compensation network are external. The flexibility in designing the external compensation allows the user to optimize the design across the entire input voltage and selectable output voltages range.

#### 4.1 Theory of Operation

Valley Current mode control is a fixed frequency, leading-edge modulated Pulse-Width Modulation (PWM) Current mode control. Differing from the Peak Current mode, the Valley Current mode clock marks the turn-off of the high-side switch. Upon this instant, the MIC45404 low-side switch current level is compared against the reference current signal from the error amplifier. When the falling low-side switch current signal drops below the current reference signal, the high-side switch is turned on. As a result, the inductor valley current is regulated to a level dictated by the output of the error amplifier.

The feedback loop includes an internal programmable reference and output voltage sensing attenuator, thus removing the need for external feedback components and improving regulation accuracy. Output voltage feedback is achieved by connecting the OUTSNS pin directly to the output. The high-performance transconductance error amplifier drives an external compensation network at the COMP pin. The COMP pin voltage represents the reference current signal. This pin voltage is fed to the Valley Current mode modulator, which also adds slope compensation to ensure current loop stability.

Internal inductor, power MOSFETs and internal bootstrap diode complete the power train.

Overcurrent protection and thermal shutdown protect the MIC45404 from Faults or abnormal operating conditions.

#### 4.2 Supply Rails (V<sub>IN</sub>, V<sub>DDA</sub>, V<sub>DDP</sub>) and Internal LDO

$V_{\rm IN}$  pins represent the power train input. These pins are the drain connection of the internal high-side MOSFET and should be bypassed to GND, at least with a X5R or X7R 10  $\mu F$  ceramic capacitor, placed as close as possible to the module. Multiple capacitors are recommended.

An internal LDO provides a clean supply (5.1V typical) for the analog circuits at the V<sub>DDA</sub> pin. The internal LDO is also powered from V<sub>IN</sub>, as shown in the Functional Diagram. The internal LDO is enabled when the voltage at the EN/DLY pin exceeds about 0.51V, and regulation takes place as soon as enough voltage has been established between the V<sub>IN</sub> and V<sub>DDA</sub> pins. An internal Undervoltage Lockout (UVLO) circuit monitors the level of V<sub>DDA</sub>. The V<sub>DDA</sub> pin needs external bypassing to GND by means of a 2.2  $\mu$ F X5R or X7R ceramic capacitor, placed as close as possible to the module.

$V_{DDP}$  is the power supply rail for the gate drivers and bootstrap circuit. This pin is bypassed to GND\_EXT by means of an internal high-frequency ceramic capacitor. For this reason, the GND\_EXT pins should be routed with a low-inductance path to the GND net. An internal  $10\Omega$  resistor is provided between  $V_{DDA}$  and  $V_{DDP}$ allowing the implementation of a switching noise attenuation RC filter with the minimum amount of external components. It is possible, although typically not necessary, to lower the RC time constant by connecting an external resistor between  $V_{DDA}$  and  $V_{DDP}$ .

If the input rail is within 4.5V to 5.5V, it is possible to bypass the internal LDO by connecting  $V_{IN}$ ,  $V_{DDA}$  and  $V_{DDP}$  together. Local decoupling of the  $V_{DDA}$  pin is still recommended.

#### 4.3 Pin-Strapping Programmability (VOSET0, VOSET1, FREQ, I<sub>LIM</sub>)

The MIC45404 uses pin strapping to set the output voltage (VOSET0, VOSET1), switching frequency (FREQ) and current limit ( $I_{LIM}$ ). No external passives are needed, therefore, the external component count is minimized. Each pin is a three-state input (connect to GND for LOW logic level, connect to V<sub>DDA</sub> for HIGH logic level or leave unconnected for High Z). The logic level of the pins is read and frozen in the internal configuration logic immediately after the V<sub>DDA</sub> rail comes up and becomes stabilized. After this instant, any change of the input logic level on the pins will have no effect until the V<sub>DDA</sub> power is cycled again. The values corresponding to each particular pin strapping configuration are detailed in Section 5.0 "Application Information".

#### 4.4 Enable/Delay (EN/DLY)

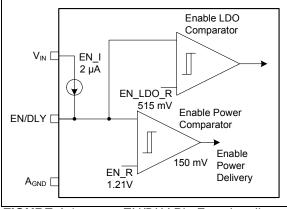

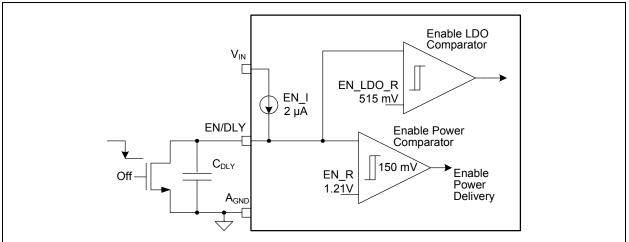

The EN/DLY pin is a dual threshold pin that turns the internal LDO on/off and starts/stops the power delivery to the output, as shown in Figure 4-1.

FIGURE 4-1: EN/DLY Pin Functionality.

The threshold for LDO enable is 515 mV (typical) with a hysteresis of approximately 30 mV. This hysteresis is enough because at the time of LDO activation, there is still no switching activity.

The threshold for power delivery is a precise 1.21V,  $\pm$ 70 mV. A 150 mV typical hysteresis prevents chattering due to switching noise and/or slow edges.

A 2  $\mu$ A typical pull-up current, with ±1  $\mu$ A accuracy, permits the implementation of a start-up delay by means of an external capacitor. In this case, it is necessary to use an open-drain driver to disable the MIC45404 while maintaining the start-up delay function.

#### 4.5 Power Good (PG)

The PG pin is an open-drain output that requires an external pull-up resistor to a pull-up voltage ( $V_{PU}_{PG}$ ), lower than 5.5V, for being asserted to a logic HIGH level. The PG pin is asserted with a typical delay of 0.45 ms when the output voltage (OUTSNS) reaches 92.5% of its target regulation voltage. This pin is deasserted with a typical delay of 80 µs when the output voltage falls below 90% of its target regulation voltage. The PG falling delay acts as a deglitch timer against very short spikes. The PG output is always immediately deasserted when the EN/DLY pin is below the power delivery enable threshold (EN\_R/EN\_F). The pull-up resistor should be large enough to limit the PG pin current to below 2 mA.

#### 4.6 Inductor (LX, OUT) and Bootstrap (BST) Pins

The internal inductor is connected across the LX and OUT pins. The high-side MOSFET driver circuit is powered between BST and LX by means of an internal capacitor that is replenished from rail  $V_{DDP}$  during the low-side MOSFET on time. The bootstrap diode is internal.

#### 4.7 Output Sensing (OUTSNS) and Compensation (COMP) Pins

OUTSNS should be connected exactly to the desired Point-of-Load (POL) regulation, avoiding parasitic resistive drops. The impedance seen into the OUTSNS pin is high (tens of  $k\Omega$  or more, depending on the selected output voltage value), therefore, its loading effect is typically negligible. OUTSNS is also used by the slope compensation generator.

The COMP pin is the connection for the external compensation network. COMP is driven by the output of the transconductance error amplifier. Care must be taken to return the compensation network ground directly to  $A_{GND}$ .

#### 4.8 Soft Start

The MIC45404 internal reference is ramped up at a 0.42 V/ms rate. Note that this is the internal reference soft start slew rate and that the actual slew rate seen at the output should take into account the internal divider attenuation, as detailed in the Section 5.0 "Application Information".

#### 4.9 Switching Frequency (FREQ)

The MIC45404 features three different selectable switching frequencies (400 kHz, 565 kHz and 790 kHz). Frequency selection is tied with a specific output voltage selection, as described in Section 5.5 "Permissible MIC45404 Settings Combinations".

#### 4.10 Pre-Biased Output Start-up

The MIC45404 is designed to achieve safe start-up into a pre-biased output without discharging the output capacitors.

#### 4.11 Thermal Shutdown

The MIC45404 has a thermal shutdown protection that prevents operation at excessive temperature. The thermal shutdown threshold is typically set at +160°C, with a hysteresis of +25°C.

#### 4.12 Overcurrent Protection (I<sub>LIM</sub>) and Hiccup Mode Short-Circuit Protection

The MIC45404 features instantaneous cycle-by-cycle current limit with current sensing, both on the low-side and high-side switches. It also offers a Hiccup mode for prolonged overloads or short-circuit conditions.

The low-side cycle-by-cycle protection detects the current level of the inductor current during the low-side MOSFET on time. The high-side MOSFET turn-on is inhibited as long as the low-side MOSFET current limit is above the overcurrent threshold level. The inductor current will continue decaying until the current falls below the threshold, where the high-side MOSFET will be enabled again, according to the duty cycle requirement from the PWM modulator.

The low-side current limit has three different programmable levels (for 3A, 4A and 5A loads) in order to fit different application requirements. Since the low-side current limit acts on the valley current, the DC output current level ( $I_{OUT}$ ), where the low-side cycle-by-cycle current limit is engaged, will be higher than the current limit value by an amount equal to  $\Delta IL_{PP}/2$ , where  $\Delta IL_{PP}$ is the peak-to-peak inductor ripple current.

The high-side current limit is approximately 1.4-1.5 times greater than the low-side current limit (typical values). The high-side cycle-by-cycle current limit immediately truncates the high-side on time without waiting for the off clocking event.

A Leading-Edge Blanking (LEB) timer (108 ns, typical) is provided on the high-side cycle-by-cycle current limit to mask the switching noise and to prevent falsely triggering the protection. The high-side cycle-by-cycle current limit action cannot take place before the LEB timer expires.

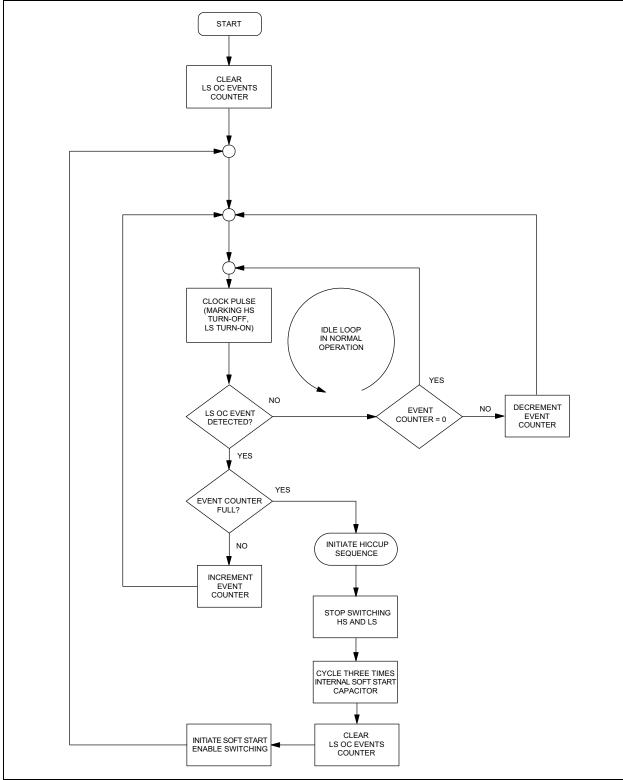

Hiccup mode protection reduces power dissipation in permanent short-circuit conditions. On each clock cycle, where a low-side cycle-by-cycle current limit event is detected, a 4-bit up/down counter is incremented. On each clock cycle without a concurrent low-side current limit event, the counter is decremented or left at zero. The counter cannot wraparound below '0000' and above '1111'. High-side current limit events do not increment the counter. Only detections from low-side current limit events trigger the counter.

If the counter reaches '1111' (or 15 events), the high and low-side MOSFETs become tri-stated, and power delivery to the output is inhibited for the duration of three times the soft start time. This digital integration mechanism provides immunity to momentary overloading of the output. After the wait time, the MIC45404 retries entering operation and initiates a new soft start sequence. Figure 4-2 illustrates the Hiccup mode short-circuit protection logic flow. Note that Hiccup mode short-circuit protection is active at all times, including the soft start ramp.

FIGURE 4-2: Hiccup Mode Short-Circuit Protection Logic.

#### 5.0 APPLICATION INFORMATION

#### 5.1 Programming Start-up Delay and External UVLO

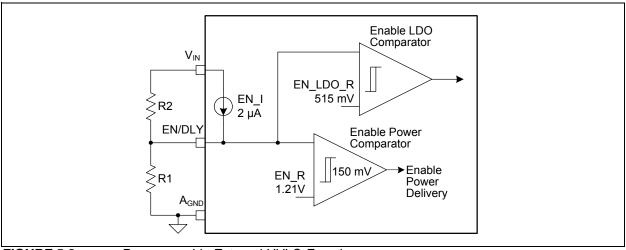

The EN/DLY pin allows programming an external start-up delay. In this case, the driver for the EN/DLY pin should be an open-drain/open-collector type, as shown in Figure 5-1.

FIGURE 5-1: Programmable Start-up Delay Function.

The start-up delay is the delay time from the off falling edge to the assertion of the enable power delivery signal. It can be calculated as shown in Equation 5-1:

The EN/DLY pin can also be used to program a UVLO threshold for power delivery by means of an external resistor divider, as described in Figure 5-2.

#### **EQUATION 5-1:**

$t_{SU\_DLY} = \frac{EN\_R \times C_{DLY}}{EN\_I}$ Where: EN\_R = 1.21V EN\_I = 2  $\mu$ A C<sub>DLY</sub> = Delay programming external capacitor

FIGURE 5-2: Programmable External UVLO Function.

The programmed  $V_{\text{IN}}$  UVLO threshold,  $V_{\text{IN}\_\text{RISE}}\text{,}$  is given by:

#### **EQUATION 5-2:**

$V_{IN\_RISE} = EN\_R \times \left(1 + \frac{R_2}{R_1}\right) - EN\_I \times R_2$ Where: EN\\_R = 1.21V EN\_I = 2 µA R\_1 and R\_2 = External resistors

To desensitize the V<sub>IN</sub> UVLO threshold against variations of the pull-up current, EN\_I, it is recommended to run the  $R_1 - R_2$  voltage divider at a significantly higher current level than the EN\_I current.

The corresponding V\_{IN} UVLO hysteresis, V\_{IN\\_HYS}, is calculated as follows:

#### **EQUATION 5-3:**

$$V_{IN\_HYS} = 150 \ mV \times \left(1 + \frac{R_2}{R_I}\right)$$

Similar calculations also apply to the internal LDO activation threshold.

#### 5.2 Setting the Switching Frequency

The MIC45404 switching frequency can be programmed using FREQ, as shown in Table 5-1.

TABLE 5-1: SWITCHING FREQUENCY SETTINGS

| FREQ Pin Setting      | Frequency |

|-----------------------|-----------|

| High Z (open)         | 400 kHz   |

| 0 (GND)               | 565 kHz   |

| 1 (V <sub>DDA</sub> ) | 790 kHz   |

The switching frequency setting is not arbitrary, but it needs to be adjusted according to the particular output voltage selection due to peak-to-peak inductor ripple requirements. This is illustrated in Section 5.5 "Permissible MIC45404 Settings Combinations".

#### 5.3 Setting the Output Voltage

TABLE 5-2

The MIC45404 output voltage can be programmed by setting pins, VOSET0 and VOSET1, as shown in Table 5-2.

OUTPUT VOL TAGE SETTINGS

| TADLE J-2.            |                       | AGE SET TINGS  |

|-----------------------|-----------------------|----------------|

| VOSET1                | VOSET0                | Output Voltage |

| 0 (GND)               | 0 (GND)               | 3.3V           |

| 0 (GND)               | 1 (V <sub>DDA</sub> ) | 2.5V (2.49V)   |

| 1 (V <sub>DDA</sub> ) | 0 (GND)               | 1.8V           |

| 1 (V <sub>DDA</sub> ) | 1 (V <sub>DDA</sub> ) | 1.5V           |

| 0 (GND)               | High Z (open)         | 1.2V           |

| High Z (open)         | 0 (GND)               | 1.0V           |

| 1 (V <sub>DDA</sub> ) | High Z (open)         | 0.9V           |

| High Z (open)         | 1 (V <sub>DDA</sub> ) | 0.8V           |

| High Z (open)         | High Z (open)         | 0.7V           |

To achieve accurate output voltage regulation, the OUTSNS pin (internal feedback divider top terminal) should be Kelvin-connected as close as possible to the point of regulation top terminal. Since both the internal reference and the internal feedback divider's bottom terminal refer to  $A_{GND}$ , it is important to minimize voltage drops between the  $A_{GND}$  and the point of

#### 5.4 Setting the Current Limit

regulation return terminal.

The MIC45404's valley-mode current limit on the low-side MOSFET can be programmed by means of  $I_{LIM} \mbox{ as shown in Table 5-3}.$

| I <sub>LIM</sub>      | Valley Current Limit<br>(Typical Value) | Rated Output<br>Current |

|-----------------------|-----------------------------------------|-------------------------|

| 0 (GND)               | 4.6 A                                   | 3A                      |

| 1 (V <sub>DDA</sub> ) | 6.2 A                                   | 4A                      |

| High Z (open)         | 6.8 A                                   | 5A                      |

TABLE 5-3: CURRENT LIMIT SETTINGS

Note that the programmed current limit values act as pulse-by-pulse, current limit thresholds on the valley inductor current. If the inductor current has not decayed below the threshold at the time the PWM requires a new on time, the high-side MOSFET turn-on is either delayed, until the valley current recovers below the threshold, or skipped. Each time the high-side MOSFET turn-on is skipped, a 4-bit up-down counter is incremented. When the counter reaches the configuration '1111', a hiccup sequence is invoked in order to reduce power dissipation under prolonged short-circuit conditions.

The highest current limit setting (6.8A) is intended to comfortably accommodate a 5A application. Ensure that the value of the operating junction temperature does not exceed the maximum rating in high output power applications.

#### 5.5 Permissible MIC45404 Settings Combinations

The MIC45404 allowable settings are constrained by the values in Table 5-4.

## TABLE 5-4:PERMISSIBLE MIC45404SETTINGS COMBINATIONS

| Output Voltage | Frequency |

|----------------|-----------|

| 3.3V           | 790 kHz   |

| 2.5V (2.49V)   |           |

| 1.8V           | 565 kHz   |

| 1.5V           |           |

| 1.2V           | 400 kHz   |

| 1.0V           |           |

| 0.9V           |           |

| 0.8V           |           |

| 0.7V           |           |

#### 5.6 Output Capacitor Selection

Two main requirements determine the size and characteristics of the output capacitor,  $C_{O}$ :

- · Steady-state ripple

- · Maximum voltage deviation during load transient

For steady-state ripple calculation, both the ESR and the capacitive ripple contribute to the total ripple amplitude. The MIC45404 utilizes a low loss inductor, whose nominal value is 1.2  $\mu$ H. From the switching frequency, input voltage, output voltage setting and load current, the peak-to-peak inductor current ripple and the peak inductor current can be calculated as:

#### **EQUATION 5-4:**

$$\Delta I_{L_PP} = V_O \times \left(\frac{I - \frac{V_O}{V_{IN}}}{f_S \times L}\right)$$

#### **EQUATION 5-5:**

$$I_{L,PEAK} = I_O + \frac{\Delta I_{L_PP}}{2}$$

The capacitive ripple,  $\Delta V_{r,C},$  and the ESR ripple,  $\Delta V_{r,ESR},$  are given by:

#### EQUATION 5-6:

$$\Delta V_{R,C} = \frac{\Delta I_{L_PP}}{8 \times f_S \times C_O}$$

#### **EQUATION 5-7:**

$$\Delta V_{R,ESR} = ESR \times \Delta I_{L PP}$$

The total peak-to-peak output ripple is then conservatively estimated as:

#### **EQUATION 5-8:**

$$\Delta V_R \cong \Delta V_{R,C} + \Delta V_{R,ESR}$$

The output capacitor value and ESR should be chosen such that  $\Delta V_R$  is within specifications. Capacitor tolerance should be considered for worst-case calculations. In case of ceramic output capacitors, factor into account the decrease of effective capacitance versus applied DC bias.

The worst-case load transient for output capacitor calculation is an instantaneous 100% to 0% load release when the inductor current is at its peak value. In this case, all the energy stored in the inductor is absorbed by the output capacitor, while the converter stops switching and keeps the low-side FET on.

The peak output voltage overshoot ( $\Delta V_O$ ) happens when the inductor current has decayed to zero. This can be calculated with Equation 5-9:

#### **EQUATION 5-9:**

$$\Delta V_O = \sqrt{V_O^2 + \frac{L}{C_O} \times I_{L,PEAK}^2} - V_O$$

Equation 5-10 calculates the minimum output capacitance value ( $C_{O(MIN)}$ ) needed to limit the output overshoot below  $\Delta V_O$ .

#### EQUATION 5-10:

$$C_{O(MIN)} = \frac{L \times I_{L,PEAK}^2}{\left(\Delta V_O + V_O\right)^2 - V_O^2}$$

The result from the minimum output capacitance value for load transient is the most stringent requirement found for capacitor value in most applications. Low Equivalent Series Resistance (ESR) ceramic output capacitors, with X5R or X7R temperature ratings, are recommended.

For low output voltage applications with demanding load transient requirements, using a combination of polarized and ceramic output capacitors may be the most convenient option for smallest solution size.

#### 5.7 Input Capacitor Selection

Two main requirements determine the size and characteristics of the input capacitor:

- Steady-State Ripple

- · RMS Current

The Buck Converter input current is a pulse train with very fast rising and falling times, so low-ESR ceramic capacitors are recommended for input filtering because of their good high-frequency characteristics.

By assuming an ideal input filter (which can be assimilated to a DC input current feeding the filtered buck power stage) and by neglecting the contribution of the input capacitor ESR to the input ripple (which is typically possible for ceramic input capacitors), the minimum capacitance value,  $C_{IN(MIN)}$ , needed for a given input peak-to-peak ripple voltage,  $\Delta V_{r, IN}$ , can be estimated as shown in Equation 5-11:

#### EQUATION 5-11:

$$C_{IN(MIN)} = \frac{I_O \times D \times (1 - D)}{\Delta V_{r,IN} \times f_S}$$

Where:

D is the duty cycle at the given operating point.

The RMS current,  $I_{IN,RMS}$ , of the input capacitor is estimated as in Equation 5-12:

#### EQUATION 5-12:

$$I_{IN,RMS} = I_O \times \sqrt{D \times (1-D)}$$

Note that, for a given output current,  $I_{\text{O}},$  worst-case values are obtained at D = 0.5.

Multiple input capacitors can be used to reduce input ripple amplitude and/or individual capacitor RMS current.

#### 5.8 Compensation Design

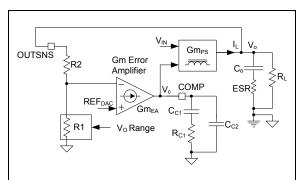

As a simple first-order approximation, the Valley Current mode controlled buck power stage can be modeled as a voltage controlled current source, feeding the output capacitor and load. The inductor current state variable is removed and the power stage transfer function from COMP to the inductor current is modeled as a transconductance ( $Gm_{PS}$ ). The simplified model of the control loop is shown in Figure 5-3. The power stage transconductance,  $Gm_{PS}$ , shows some dependence on current levels and it is also somewhat affected by process variations, therefore, some design margin is recommended against the typical value,  $Gm_{PS} = 12.5$ A/V (see Section 1.0 "Electrical Characteristics").

FIGURE 5-3: Simplified Small Signal Model of the Voltage Regulation Loop.

This simplified approach disregards all issues related to the inner current loop, like its stability and bandwidth. This approximation is good enough for most operating scenarios, where the voltage loop bandwidth is not pushed to aggressively high frequencies.

Based on the model shown in Figure 5-3, the control-to-output transfer function is:

#### **EQUATION 5-13:**

$$G_{CO(S)} = \frac{V_{O(S)}}{V_{C(S)}} = Gm_{PS} \times R_L \times \frac{\left(1 + \frac{s}{2\pi \times f_Z}\right)}{\left(1 + \frac{s}{2\pi \times f_P}\right)}$$

Where  $f_Z$  and  $f_P$  = the frequencies associated with the output capacitor ESR zero and with the load pole, respectively:

$$f_{Z} = \frac{1}{2\pi \times C_{O} \times ESR}$$

$$f_{P} = \frac{1}{2\pi \times C_{O} \times (ESR + R_{L})}$$

The MIC45404 module uses a transconductance (Gm<sub>EA</sub> = 1.4 mA/V) error amplifier. Frequency compensation is implemented with a Type-II network (R<sub>C1</sub>, C<sub>C1</sub> and  $C_{C2}$ ) connected from the COMP to  $A_{GND}$ . The compensator transfer function consists of an integrator for zero DC voltage regulation error, a zero to boost the phase margin of the overall loop gain around the crossover frequency and an additional pole that can be used to cancel the output capacitor ESR zero, or to further attenuate switching frequency ripple. In both cases, the additional pole makes the regulation loop less susceptible to switching frequency noise. The additional pole is created by capacitor C<sub>C2</sub> (internally provided, C<sub>C2</sub> value is 47 pF). Equation 5-14 details the compensator transfer function, H<sub>C(S)</sub> (from OUTSNS to COMP).

#### **EQUATION 5-14:**

$$H_{C(S)} = -\frac{RI}{RI + R2} \times Gm_{EA} \times \frac{1}{S \times (C_{CI} + C_{C2})}$$

$$\times \frac{(I + S \times R_{CI} \times C_{CI})}{\left(1 + S \times R_{CI} \times \frac{C_{CI} \times C_{C2}}{C_{CI} + C_{C2}}\right)}$$

The overall voltage loop gain,  $\mathsf{T}_{\mathsf{V}(\mathsf{S})}$ , is the product of the control-to-output and the compensator transfer functions:

#### EQUATION 5-15:

$T_{V(S)} = G_{CO(S)} \times H_{C(S)}$

The value of the attenuation ratio, R1/(R1 + R2), depends on the output voltage selection and can be retrieved as illustrated in Table 5-5:

#### TABLE 5-5: INTERNAL FEEDBACK DIVIDER ATTENUATION VALUES

| V <sub>O</sub> Range | R1/(R1 + R2) | A<br>(A = 1 + R2/R1) |

|----------------------|--------------|----------------------|

| 0.7V-1.2V            | 1            | 1                    |

| 1.5V-1.8V            | 0.5          | 2                    |

| 2.5V(2.49V)-3.3V     | 0.333        | 3                    |

The compensation design process is as follows:

1. Set the  $T_{V(s)}$  loop gain crossover frequency,  $f_{XO}$ , in the range of  $f_S/20$  to  $f_S/10$ . Lower values of  $f_{XO}$  allow a more predictable and robust phase margin. Higher values of  $f_{XO}$  would involve additional considerations about the current loop bandwidth in order to achieve a robust phase margin. Taking a more conservative approach is highly recommended.

#### EQUATION 5-16:

$$\frac{f_S}{20} \leq f_{XO} \leq \frac{f_S}{10}$$

2. Select  $R_{C1}$  to achieve the target crossover frequency,  $f_{XO}$ , of the overall voltage loop. This typically happens where the power stage transfer function,  $G_{CO(S)}$ , is rolling off at -20 dB/decade. The compensator transfer function,  $H_{C(S)}$ , is in the so-called midband gain region, where  $C_{C1}$  can be considered a DC blocking short circuit, while  $C_{C2}$  can still be considered as an open circuit, as calculated in Equation 5-17:

#### **EQUATION 5-17:**

$$R_{CI} = \left(\frac{RI + R2}{RI}\right) \times \frac{2\pi \times C_O \times f_{XO}}{Gm_{EA} \times Gm_{PS}}$$

3. Select capacitor  $C_{C1}$  to place the compensator zero at the load pole. The load pole moves around with load variations, so to calculate the load pole use as a load resistance  $R_L$ , the value determined by the nominal output current,  $I_{O}$ , of the application, as shown in Equation 5-18 and Equation 5-19:

#### EQUATION 5-18:

$$R_L = \frac{V_O}{I_O}$$

#### **EQUATION 5-19:**

$$C_{C1} = \frac{C_O \times (ESR + R_L)}{R_{C1}}$$

4. Knowing that an internal  $C_{C2}$  capacitor of 47 pF is provided already, find out if any additional capacitance is needed to augment the overall value of the capacitor,  $C_{C2}$ .

The  $C_{C2}$  (total value) is intended for placing the compensator pole at the frequency of the output capacitor ESR zero and/or achieve additional switching ripple/noise attenuation.

If the output capacitor is a polarized one, its ESR zero will typically occur at low enough frequencies to cause the loop gain to flatten out and not roll off at a -20 dB/decade slope, around or just after the crossover frequency,  $f_{\rm XO}$ . This causes undesirable scarce compensation design robustness and switching noise susceptibility. The compensator pole is then used to cancel the output capacitor ESR zero and achieve a well-behaved roll-off of the loop gain above the crossover frequency.

If the output capacitors are only ceramic, then the ESR zeros frequencies could be very high. In many cases, the frequencies could even be above the switching frequency itself. Loop gain roll-off at -20 dB/decade is ensured well beyond the crossover frequency, but even in this case, it is good practice to still make use of the compensator pole to further attenuate switching noise, while conserving phase margin at the crossover frequency.

For example, setting the compensator pole at 5  $f_{\rm XO}$  will limit its associated phase loss at the crossover frequency to about 11°. Placement at even higher frequencies, N ×  $f_{\rm XO}$  (N > 5), will reduce phase loss even further at the expense of less noise/ripple attenuation at the switching frequency. Some attenuation of the switching frequency noise/ripple is achieved as long as N ×  $f_{\rm XO}$  <br/> $f_{\rm S}$ .

For the polarized output capacitor, compensator pole placement at the ESR zero frequency is achieved, as shown in Equation 5-20:

#### EQUATION 5-20:

$$C_{C2} = \frac{1}{\frac{R_{C1}}{C_O \times ESR} - \frac{1}{C_{C1}}}$$

For the ceramic output capacitor, compensator pole placement at N ×  $f_{XO}$  (N  $\ge$  5, N ×  $f_{XO}$  <  $f_S$ ) is achieved, as detailed in Equation 5-21:

#### EQUATION 5-21:

$$C_{C2} = \frac{1}{2\pi \times R_{C1} \times N \times f_{XO} - \frac{1}{C_{C1}}}$$

The MIC45404 already provides an internal  $C_{C2}$  capacitor of 47 pF. Therefore, the external capacitance,  $C_{C2\_EXT}$ , that should be added is given by Equation 5-22:

#### EQUATION 5-22:

$$C_{C2\_EXT} = max(C_{C2} - 47 \, pF, \, 0 \, pF)$$

If the result,  $C_{C2}$  – 47 pF, yields to zero or to a negative number, no additional external capacitance is needed for  $C_{C2}$ .

#### 5.9 Output Voltage Soft Start Rate

The MIC45404 features an internal analog soft start, such that the output voltage can be smoothly increased to the target regulation voltage. The soft start rate given in **Section 1.0 "Electrical Characteristics**" is referred to the error amplifier reference, and therefore, the effective soft start rate value, seen at the output of the module, has to be scaled according to the internal feedback divider attenuation values listed in Table 5-5. To calculate the effective output voltage soft start slew rate, SS\_SR<sub>OUT</sub>, based on the particular output voltage setting and the reference soft start slew rate, SS\_SR, use the following formula:

#### **EQUATION 5-23:**

$$SS\_SR_{OUT} = A \times SS\_SR$$

Where:

A = Amplification

For the value of A, see the right column of Table 5-5.

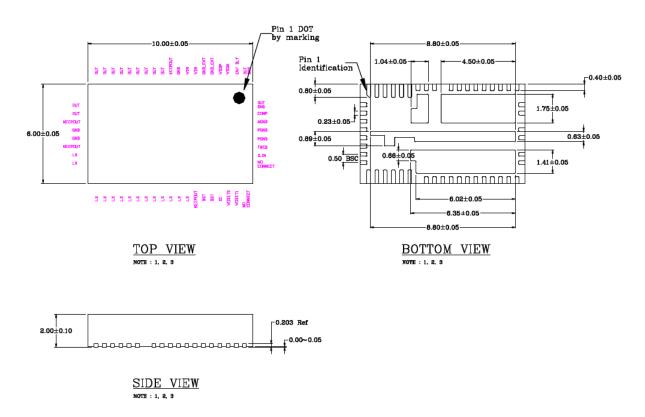

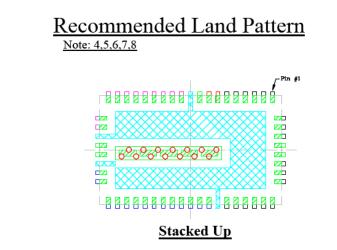

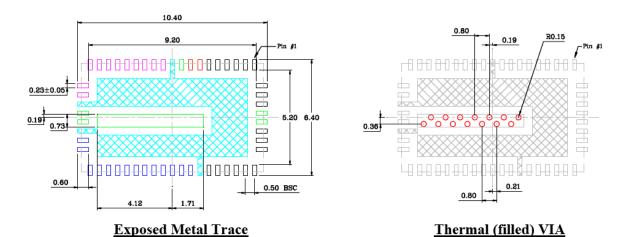

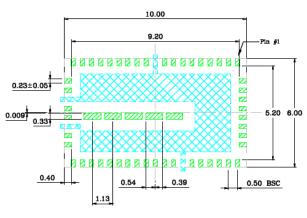

#### 6.0 PACKAGING INFORMATION

#### TITLE

54 LEAD P2QFN 10x6mm PACKAGE (PIP Module) OUTLINE & RECOMMENDED LAND PATTERN

| DRAWING #  | P2QFN106-54LD-PL-1 | UNIT        | MM        |

|------------|--------------------|-------------|-----------|

| Lead Frame | Copper             | Lead Finish | Matte Tin |

NOTE:

1. MAX PACKAGE WARPAGE IS 0.05mm.

2. MAX ALLOWABLE BURR IS 0.076mm IN ALL DIRECTIONS.

3. PIN #1 IS ON TOP WILL BE LASER MARKED.

4. RED CIRCLES IN LAND PATTERN REPRESENTS THERMAL VIA. RECOMMENDED SIZE IS 0.30-0.35mm, AT 0.80mm PITCH & SHOULD BE CONNECTED TO GND FOR MAXIMUM PERFORMANCE.

5. GREEN RECTANGLES (SHADED AREA) REPRESENT SOLDER STENCIL OPENING ON EXPOSED PAD AREA.

6. CYAN COLORED (SHADED) PAD REPRESENT EXPOSED TRACE KEEP OUT AREA.

7. RECOMMENDED LAND PATTERN TOLERANCE IS 0.020mm UNLESS SPECIFIED.

8. SEE RECOMMENDED LAND PATTERN ON PAGE 2.

POD-Land Pattern Doc #: P2QFN106-54LD-PL-1-A

Solder Stencil Opening

#### APPENDIX A: REVISION HISTORY

#### **Revision A (December 2015)**

• Original release of this document.

NOTES:

#### **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| ¥                 | <u>xx</u>                               | <u>-xx</u> (1)                                                                                                                                |                                                                                                                                                                                                                                                                                                                 | Exampl                                                                                                                                                                                                                                      | les:                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Lead Finish       | Package Code                            | Tape and Reel<br>Option                                                                                                                       |                                                                                                                                                                                                                                                                                                                 | a) MIC4                                                                                                                                                                                                                                     | 45404YMP-TR: Pb-Free, 54 Lead<br>6 x 10 x 2 mm QFN Package<br>Tape and Reel.                                                                                                                                                                            | 9,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                   |                                         | ronous step-down                                                                                                                              |                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Y =               | Pb-Free with Industria                  | al Temperature Grade                                                                                                                          |                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| MP =              | Module Package, thic                    | kness ≥ 2.0 mm                                                                                                                                |                                                                                                                                                                                                                                                                                                                 | Note 1:                                                                                                                                                                                                                                     | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| TR = <sup>-</sup> | Tape and Reel <sup>(1)</sup>            |                                                                                                                                               |                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                             | catalog part number description. This iden<br>fier is used for ordering purposes and is r<br>printed on the device package. Check wit<br>your Microchip Sales Office for package<br>availability with the Tape and Reel option.                         | not<br>h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |