## E1 Line Interface Unit (LIU) Data Sheet

**Features**

- Complete primary rate 2048kbit/s E1line driver and receiver with clock recovery

- Meets ETSI requirements (ETSI ETS 300 011, NET 5)

- Onboard pulse transformers for transmit and receive

- No external crystal required for clock recovery

- · Loss of signal indication

- Programmable polarity of extracted clock and receive data

- Compatible with MT8979, MT9079 and other E1 framers

- Single +5V operation

- Single In-Line (SIL) package occupying only 490mm<sup>2</sup> area

#### **Applications**

- · Primary rate ISDN network Interfaces

- Multiplexer equipment

DS5712 Issue 4 March 2002

#### **Ordering Information**

MH89792-1 20 Pin SIL Package MH89792-2 20 Pin SIL Package

#### -40°C to 85°C

- E1 Digital Loop Carrier (DLC) equipment

- Digital Cross-connect Systems (DCS)

#### **Description**

The Zarlink MH89792 is an E1 line interface unit (LIU) designed to meet the requirements of G.703 2048 kbit/s transmission. It incorporates all of the analog front-end components necessary to realize a complete, fully compliant short-haul E1 analog termination. These include, clock extractor, line driver/receiver, impedance matching resistors, and line transformers. No external components, such as crystals, inductors or transformers are required. An external clock reference is also not required. Two line impedance versions are available for 75 $\Omega$  and  $120\Omega$  applications. See ordering information for details.

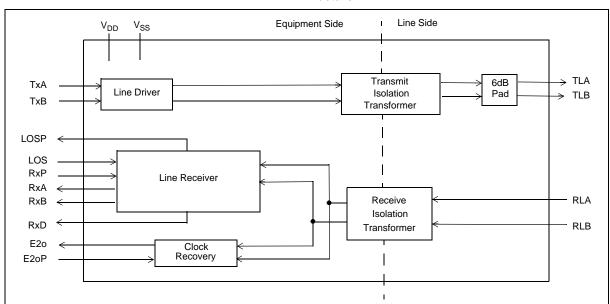

Figure 1 - Functional Block Diagram

MH89792 Data Sheet

The MH89792 is compatible with the Zarlink MT8979 and MT9079 E1 digital framers, as well as other commercially available E1 framers. The MH89792 requires only a single +5 volt supply. The device is manufactured in a 20 pin Single In-Line (SIL) package. This package uses minimal board space area, making it optimal for high density E1 line card designs.

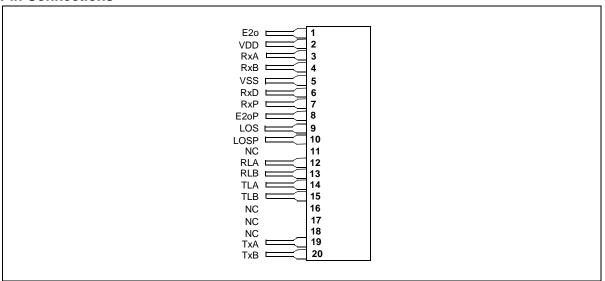

#### **Pin Connections**

Figure 2 - Pin Connections

## **Pin Description**

| Pin # | Name            | Description                                                                                                                                                                                                                                                                                                                                                |

|-------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | E2o             | <b>2048kHz Extracted clock (Output).</b> This clock is extracted by the device from the received signal. It is used internally to clock in data received from RLA and RLB.                                                                                                                                                                                 |

| 2     | $V_{DD}$        | Positive Power Supply (Input). +5V supply                                                                                                                                                                                                                                                                                                                  |

| 3     | RxA             | <b>Receiver A (Output).</b> The E1 signal received by the device at the RLA and RLB inputs is converted to return to zero (RZ) format and output at this pin. This output should be connected to the RxA or RxA of the E1 framer.                                                                                                                          |

| 4     | RxB             | <b>Receiver B (Output).</b> The E1 signal received by the device at the RLA and RLB inputs is converted to return to zero (RZ) format and output at this pin. This output should be connected to the RxB or RxB of the E1 framer.                                                                                                                          |

| 5     | V <sub>SS</sub> | Negative Power supply (Input). Ground.                                                                                                                                                                                                                                                                                                                     |

| 6     | RxD             | <b>Received Data (Output).</b> This signal is the logically "OR" ed product of the RxA and RxB signals and should be connected to RxD of the MT8979.                                                                                                                                                                                                       |

| 7     | RxP             | <b>RxA/RxB Polarity Select (Input).</b> A logic low applied to this pin will invert the outputs RxA and RxB (MT8979 application). A logic high should be applied if no inversion is required (MT9079 application).                                                                                                                                         |

| 8     | E2oP            | Clock Polarity Select (Input). A logic low selects E2o with a falling edge in the centre of RxD. A logic high selects E2o with a rising edge in the centre of RxD.                                                                                                                                                                                         |

| 9     | LOS             | Loss of Signal (Output). This pin goes low when 128 consecutive zeros are received on the RLA and RLB inputs. If a loss of signal condition is detected (LOS is low) then RxA and RxB are forced high if RxP is low. RxA and RxB are forced low if RxP is high. When 64 ones are received in 512 a bit period, the LOS condition is cleared (LOS is high). |

MH89792

#### Pin Description (continued)

| Pin # | Name | Description                                                                                                                                                     |

|-------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10    | LOSP | Loss of Signal Polarity Select (Input). A logic low applied to this pin will invert the polarity of the LOS output signal.                                      |

| 11    | NC   | No connection. This pin is not fitted.                                                                                                                          |

| 12    | RLA  | Received Line A (Input). The A wire or Tip Connection of the E1 receive line should be connected to this pin.                                                   |

| 13    | RLB  | Receive Line B (Input). The B wire or Ring connection of the E1 receive line should be connected to this pin.                                                   |

| 14    | TLA  | <b>Transmit Line A(Output).</b> The A wire or Tip connection of the E1 transmit line should be connected to this pin.                                           |

| 15    | TLB  | <b>Transmit Line B (Output).</b> The B wire or Ring connection of the E1 transmit line should be connected to this pin.                                         |

| 16    | NC   | No Connection. This pin is not fitted.                                                                                                                          |

| 17    | NC   | No Connection. This pin is not fitted.                                                                                                                          |

| 18    | NC   | No Connection. This pin is not fitted.                                                                                                                          |

| 19    | TxA  | <b>Transmit A (Input).</b> This input should be connected to the TxA output of the framer. This signal must be a return to zero (RZ) form of the transmit data. |

| 20    | TxB  | <b>Transmit B (Input).</b> This input should be connected to the TxB output of the framer. This signal must be a return to zero (RZ) form of the transmit data. |

## **Functional Description**

The MH89792 is an E1 digital trunk interface, which when used with an MT8979 and MT9079 framer will conform to CCITT recommendation G.703 for PCM30 and I.431 for ISDN. The functions provided include line driver and receiver circuitry, clock recovery, loss of signal indication, as well as data and clock polarity selection.

#### **Bipolar Line Receiver**

The MH89792 receiver interfaces to the transmission line through an internal pulse transformer, which isolates the line side from the equipment side of the circuit. These two signals are combined by internal logic to form a new signal, which represents the received data, RxD. The signals RxA and RxB may be inverted where required by applying a logic low signal permanently to pin 7, (RxP). RxD will not be affected by use of this pin.

The input impedance of the MH89792 receiver is nominally  $120\Omega$  when using the -1 variant (twisted pair applications), and nominally  $75\Omega$  when using the -2 variant (coaxial cable applications).

The receiver input sensitivity exceeds G.703 requirements.

#### **Clock Extractor**

The MH89792 contains a clock extraction circuit which generates the E2o clock from the received data without the use of an external crystal or tunable inductor.

The edge of the E2o extracted clock aligns approximately with the centre of the received data pulse and can be configured as either a rising or falling edge format by the use of pin 8 (E2oP).

MH89792 Data Sheet

During a loss of signal condition, the E2o clock output will free-run at a nominal frequency of 2.048 kHz  $\pm$  200 ppm.

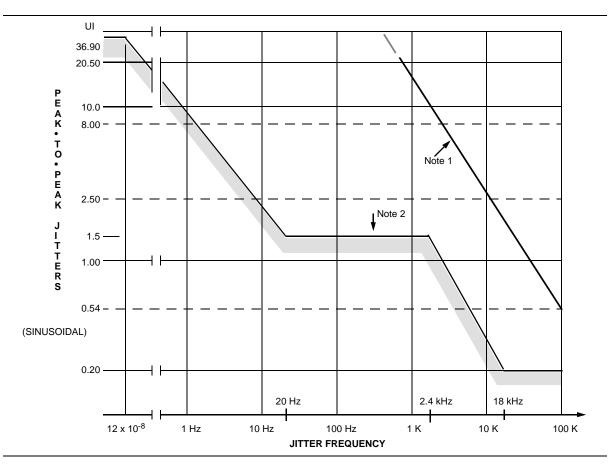

The input jitter tolerance of the MH89792 exceeds the minimum jitter tolerance as specified in CCITT I.431 and G.823 (see Figure 3).

### **Loss of Signal**

The circuitry on the MH89792 is capable of detecting 128 continuous ZEROs received on RLA and RLB and indicating this condition as a logic low on pin 9, (LOS). If a loss of signal condition is detected (LOS is low) then RxA and RxB are forced high if RxP is low. RxA and RxB are forced low if RxP is high. LOS will not reset until 64 ONEs are received in a 512 bit period. The action of LOS may be inverted by applying a logic low to pin 10 (LOSP).

A zero level is defined by voltage on the line, being less than 1.5V.

Figure 3 - Typical Input Jitter Tolerance of MH89792

Note 1 - Typical jitter tolerance of receiver

Note 2 - Minimum jitter tolerance specified by G.823 and I.431

Data Sheet MH89792

## **Bipolar Line Transmitter**

The MH89792 transmitter interfaces to the transmission line through an internal pulse transformer which combines the TxA and TxB data into an AMI line coded signal. This is then passed through the 6dB pad prior to being applied to the line to meet return loss requirements.

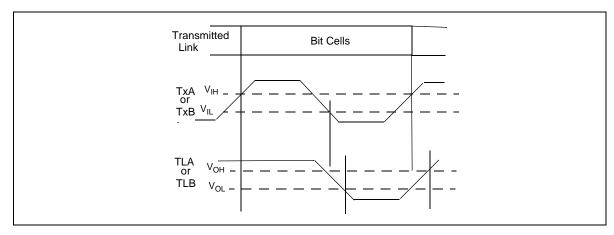

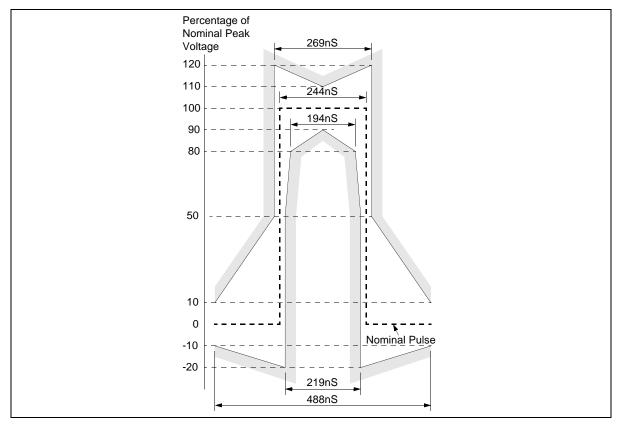

Functional timing for the transmitter is shown in Figure 4.

The template for the transmitted pulse is shown in Figure 5. The nominal peak voltage of a mark is 3 volts for  $120\Omega$  twisted pair applications and 2.37 volts for  $75\Omega$  coax applications. The ratio of the amplitude of the positive and negative pulses of the transmit signals is between 0.95 and 1.05.

No jitter is added by the transmitter circuitry.

Figure 4 - Functional Timing for Transmitter

Figure 5 - Pulse Template (CCITT G.703)

## **Applications**

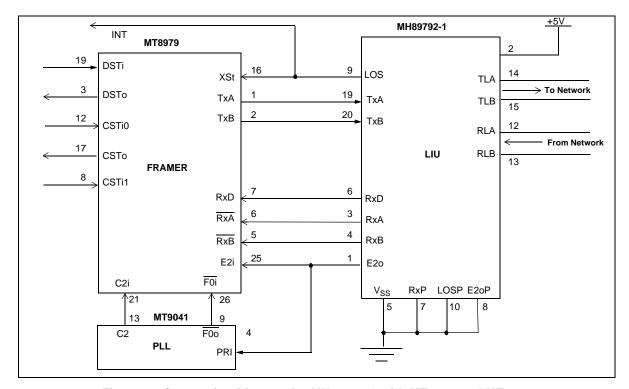

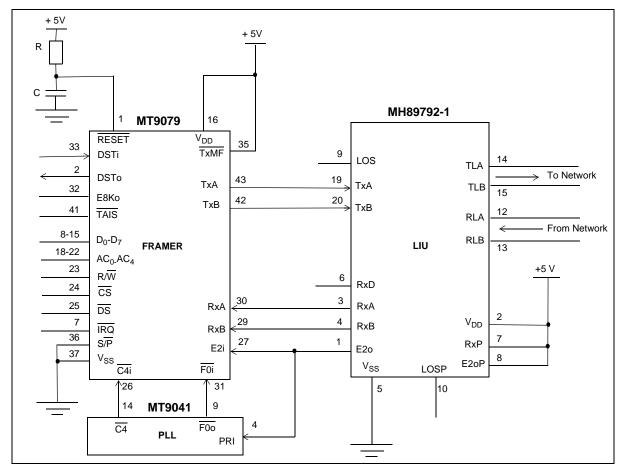

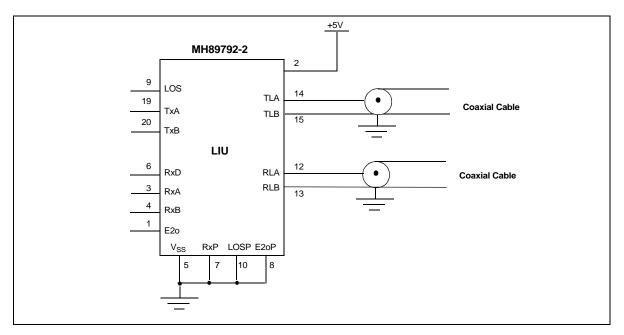

Three typical 2.048 MHz E1/CEPT application are shown in Figures 6 and 7. Figure 6 shows the MH89792-1(120 $\Omega$ ) with the MT8979 framer . Figure 7 shows the MH89792-1 (120 $\Omega$ ) with the MT9079 advanced framer. Figure 8 shows the configuration of MH89792-2 (75 $\Omega$ ).

Figure 6 - Connection Diagram for MH89792-1 with MT8979 and MT9041

Figure 7 - Connection Diagram for MH89792-1 with MT9079 and MT9041

Figure 8 - Configuration of MH89792-2 for 75W Coaxial Cable

## **Line Protection Circuitry**

The MH89792 possesses minimal line protection capability. In order to meet relevant standards governing overvoltage/overcurrent stresses from lightening strikes and other surges, an external protection network is required.

For information on suggested external line protection circuitry, please consult the factory.

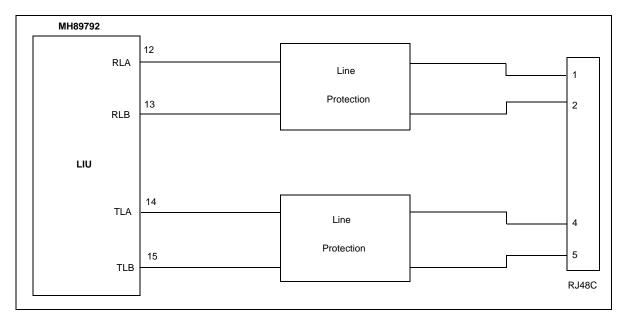

Figure 9 - Protection Circuitry Requirement

## **Absolute Maximum Ratings\***

|   | Parameter                                      | Symbol          | Min                  | Max                  | Units |

|---|------------------------------------------------|-----------------|----------------------|----------------------|-------|

| 1 | Supply Voltage with respect to V <sub>SS</sub> | $V_{DD}$        | -                    | 6                    | V     |

| 2 | Voltage on any pin other than supplies         |                 | V <sub>SS</sub> -0.3 | V <sub>DD</sub> +0.3 | V     |

| 3 | Current at any pin other than supplies         |                 | -                    | 40                   | mA    |

| 4 | Storage Temperature                            | T <sub>ST</sub> | -40                  | 85                   | °C    |

| 5 | Package Power Dissipation                      | P <sub>D</sub>  |                      | 1                    | W     |

<sup>\*</sup> Exceeding these values may cause permanent damage. Functional operation under these conditions is not implied.

## $\textbf{Recommended Operating Conditions} \text{ - Voltages are with respect to ground (V}_{SS}) \text{ unless otherwise stated.}$

|   | Characteristics       | Symbol          | Min  | Typ <sup>‡</sup> | Max  | Units |

|---|-----------------------|-----------------|------|------------------|------|-------|

| 1 | Operating Temperature | T <sub>OP</sub> | 0    | -                | 70   | °C    |

| 2 | Supply Voltage        | $V_{DD}$        | 4.75 | 5.0              | 5.25 | V     |

## DC Electrical Characteristics - Clocked operation over recommended temperature ranges and power supply voltages

|   | Parameters            | Sym             | Min             | Typ <sup>‡</sup> | Max             | Units | Conditions                                      |

|---|-----------------------|-----------------|-----------------|------------------|-----------------|-------|-------------------------------------------------|

| 1 | Supply Current        | I <sub>DD</sub> |                 | 10               | 30              | mA    | Outputs Unloaded                                |

| 2 | Input High Voltage    | V <sub>IH</sub> | 2.0             |                  | V <sub>DD</sub> | V     |                                                 |

| 3 | Input Low Voltage     | V <sub>IL</sub> | 0.0             |                  | 0.8             | V     |                                                 |

| 4 | Input Leakage Current | I <sub>IL</sub> |                 | <u>+</u> 1       | <u>+</u> 10     | μΑ    | $V_I = 0$ to $V_{DD}$                           |

| 5 | Output High Voltage   | V <sub>OH</sub> | 2.4             |                  | V <sub>DD</sub> | V     | I <sub>OH</sub> =7 mA @ V <sub>OH</sub> =2.4 V  |

|   | Output High Current   | I <sub>OH</sub> | 7               | 20               |                 | mA    | Source V <sub>OH</sub> =2.4 V                   |

| 6 | Output Low Voltage    | V <sub>OL</sub> | V <sub>SS</sub> |                  | 0.4             | V     | I <sub>OL</sub> = 2 mA @ V <sub>OL</sub> =0.4 V |

|   | Output Low Current    | I <sub>OL</sub> | 2               | 10               |                 | mA    | Sink V <sub>OL</sub> =0.4 V                     |

## **AC Electrical Characteristics - Timing Parameter Measurement Voltage Levels**

|   | Characteristics                  | Sym             | Level                     | Units  | Conditions  |

|---|----------------------------------|-----------------|---------------------------|--------|-------------|

| 1 | TTL Threshold Voltage            | V <sub>TT</sub> | 1.5                       | V      | See Note 1  |

| 2 | CMOS Threshold Voltage           | V <sub>CT</sub> | 0.5V <sub>DD</sub>        | V      | See Note 1  |

| 3 | Rise/Fall Threshold Voltage High | V <sub>HM</sub> | 2.0<br>0.7V <sub>DD</sub> | V<br>V | TTL<br>CMOS |

| 4 | Rise/Fall Threshold Voltage Low  | V <sub>LM</sub> | 0.8<br>0.3V <sub>DD</sub> | V<br>V | TTL<br>CMOS |

#### Notes:

<sup>1.</sup> Timing for output signals is based on the worst case result of the combination of TTL and CMOS threshold.

## **AC Electrical Characteristics - Capacitance**

|   | Characteristics        | Sym            | Min | Typ <sup>‡</sup> | Max | Units |

|---|------------------------|----------------|-----|------------------|-----|-------|

| 1 | Input Pin Capacitance  | C <sub>1</sub> |     | 10               |     | pF    |

| 2 | Output Pin Capacitance | C <sub>0</sub> |     | 10               |     | pF    |

## AC Electrical Characteristics $^{\dagger}$ - Line Transmitter (T<sub>ST</sub> = 0 °C to 70 °C; V<sub>DD</sub> = 5.0 V $\pm$ 5%; V<sub>SS</sub> = 0V)

|   | Parameter                                                                     | Min           | Typ <sup>‡</sup> | Max         | Units          | Conditions                                                                                                        |

|---|-------------------------------------------------------------------------------|---------------|------------------|-------------|----------------|-------------------------------------------------------------------------------------------------------------------|

| 1 | AMI Output Pulse Amplitudes MH89792-2 (75 $\Omega$ ) MH89792-1(120 $\Omega$ ) | 2.14<br>2.7   | 2.37<br>3        | 2.6<br>3.3  | V<br>V         | Terminated with a 75 $\Omega$ Load Terminated with a 120 $\Omega$ Load                                            |

| 2 | Transmitter Return Loss (for 75 $\Omega$ )                                    | 8<br>14<br>10 | 13<br>18<br>15   | -           | dB<br>dB<br>dB | Measured with transmitter in<br>idle state<br>51 KHz to 102 KHz<br>102 KHz to 2.048 MHz<br>2.048 MHz to 3.072 MHz |

| 3 | Transmitter Return Loss (for $120\Omega$ )                                    | 8<br>14<br>10 | 14<br>18<br>15   | -<br>-<br>- | dB<br>dB<br>dB | Measured with transmitter in<br>idle state<br>51 KHz to 102 KHz<br>102 KHz to 2.048 MHz<br>2.048 MHz to 3.072 MHz |

| 4 | Isolation Voltage                                                             | 1.5           |                  |             | KVrm<br>s      |                                                                                                                   |

## AC Electrical Characteristics $^{\dagger}$ - Line Receiver (T<sub>ST</sub> = 0 °C to 70 °C; V<sub>DD</sub> = 5.0 V $\pm$ 5%; V<sub>SS</sub> = 0V)

|   | Parameter                       | Min            | Typ <sup>‡</sup> | Max | Units          | Conditions                                                          |

|---|---------------------------------|----------------|------------------|-----|----------------|---------------------------------------------------------------------|

| 1 | Receiver Input Jitter Tolerance | 0.2<br>1.5     | 1.7<br>11        |     | UI<br>UI       | 18 KHz - 100 KHz<br>2.4KHz                                          |

| 2 | Receiver Return Loss (for 75Ω)  | 12<br>18<br>14 | 23<br>27<br>20   |     | dB<br>dB<br>dB | 51 KHz to 102 KHz<br>102 KHz to 2.048 MHz<br>2.048 MHz to 3.072 MHz |

| 3 | Receiver Return Loss (for 120Ω) | 12<br>18<br>14 | 23<br>28<br>25   |     | dB<br>dB<br>dB | 51 KHz to 102 KHz<br>102 KHz to 2.048 MHz<br>2.048 MHz to 3.072 MHz |

| 4 | Loss of Signal Threshold        | 1.5            |                  |     | V              |                                                                     |

| 5 | Receive Sensitivity             | 6              |                  |     | dB             |                                                                     |

MH89792 Data Sheet

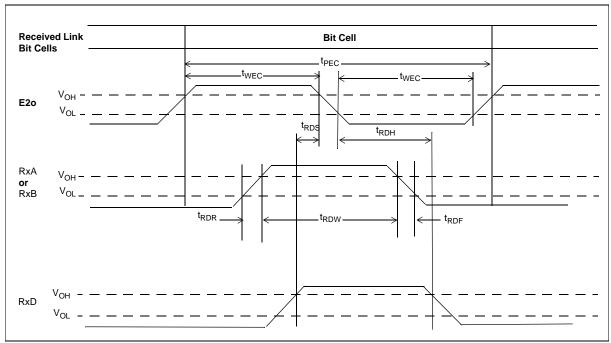

## **AC Electrical Characteristics**<sup>†</sup> - Link Timing (Figure 10)

|   | Characteristics             | Sym              | Min | Typ <sup>‡</sup> | Max | Units | Conditions |

|---|-----------------------------|------------------|-----|------------------|-----|-------|------------|

| 1 | E2o Clock Period            | t <sub>PEC</sub> | 439 | 488              | 537 | ns    |            |

| 2 | E2o Clock Width High or Low | t <sub>WEC</sub> | 195 | 244              | 293 | ns    |            |

| 3 | Receive Data Setup Time     | t <sub>RDS</sub> | 98  |                  |     | ns    | Note 1     |

| 4 | Receive Data Hold Time      | t <sub>RDH</sub> | 49  |                  |     | ns    | Note 1     |

| 5 | Receive Data Pulse Width    | t <sub>RDW</sub> | 195 | 244              | 293 | ns    |            |

| 6 | Receive Data Fall Time      | t <sub>RDF</sub> |     |                  | 20  | ns    |            |

| 7 | Receive Data Rise Time      | t <sub>RDR</sub> |     |                  | 30  | ns    |            |

Note 1: The parameter  $t_{\mbox{\scriptsize RDS}}$  and  $t_{\mbox{\scriptsize RDH}}$  are related to device functionality

<sup>‡</sup> Typical figures are at 25°C and are for design aid only: not guaranteed and not subject to production testing.

Figure 10 - Receive Timing Link

Note: 1. RxP is High and E2oP is High.

<sup>†</sup> Timing is over recommended operating temperature and power supply voltage ranges.

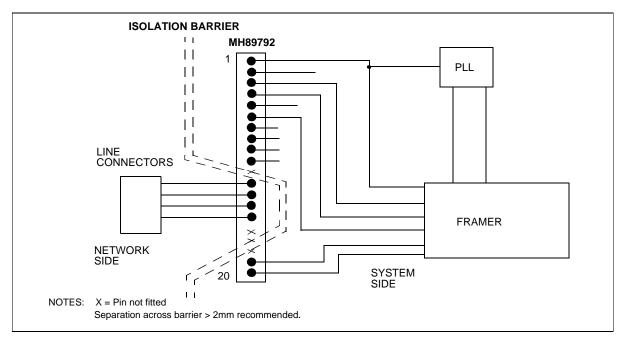

**Figure 11 - Recommended Component Placement**

# For more information about all Zarlink products visit our Web Site at www.zarlink.com

Information relating to products and services furnished herein by Zarlink Semiconductor Inc. trading as Zarlink Semiconductor or its subsidiaries (collectively "Zarlink") is believed to be reliable. However, Zarlink assumes no liability for errors that may appear in this publication, or for liability otherwise arising from the application or use of any such information, product or service or for any infringement of patents or other intellectual property rights owned by third parties which may result from such application or use. Neither the supply of such information or purchase of product or service conveys any license, either express or implied, under patents or other intellectual property rights owned by Zarlink or licensed from third parties by Zarlink, whatsoever. Purchasers of products are also hereby notified that the use of product in certain ways or in combination with Zarlink, or non-Zarlink furnished goods or services may infringe patents or other intellectual property rights owned by Zarlink.

This publication is issued to provide information only and (unless agreed by Zarlink in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. The products, their specifications, services and other information appearing in this publication are subject to change by Zarlink without notice. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. Manufacturing does not necessarily include testing of all functions or parameters. These products are not suitable for use in any medical products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to Zarlink's conditions of sale which are available on request.

Purchase of Zarlink's  $I^2C$  components conveys a licence under the Philips  $I^2C$  Patent rights to use these components in and  $I^2C$  System, provided that the system conforms to the  $I^2C$  Standard Specification as defined by Philips.

Zarlink, ZL and the Zarlink Semiconductor logo are trademarks of Zarlink Semiconductor Inc.

Copyright Zarlink Semiconductor Inc. All Rights Reserved.

TECHNICAL DOCUMENTATION - NOT FOR RESALE