# **MELPS 740**

#### SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

#### MELPS 740 CPU CORE BASIC FUNCTIONS

Each series of the MELPS 740 Family uses the standard MELPS 740 instruction set. The functions of the MELPS 740 CPU core are explained below. The multiply and divide instructions are not available in every microcomputer, and the clock control instructions differ in each microcomputer. For details, refer to the table of machine instruction or the functional explanation of each microcomputer.

# CENTRAL PROCESSING UNIT (CPU) INTERNAL REGISTERS

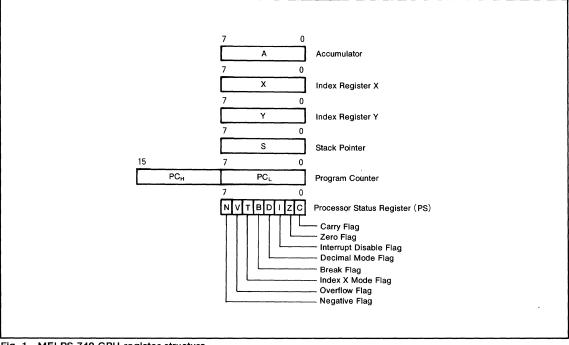

The central processing unit (CPU) has the six registers. Accumulator (A)

The accumulator is an 8-bit register. Data operations such as data transfer, etc., are executed mainly through the accumulator.

#### Index register X (X), Index register Y (Y)

Both index register X and index register Y are 8-bit registers. In the index addressing modes, the value of the OPERAND is added to the contents of register X or register Y and specifies the real address.

These index registers also have increment, decrement, comparison, and data transfer functions to allow these registers to take some of the functions of the accumulator.

When the T flag in the processor status register is set to

"1", the value contained in index register X becomes the address for the second OPERAND.

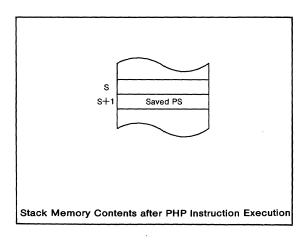

#### Stack pointer (S)

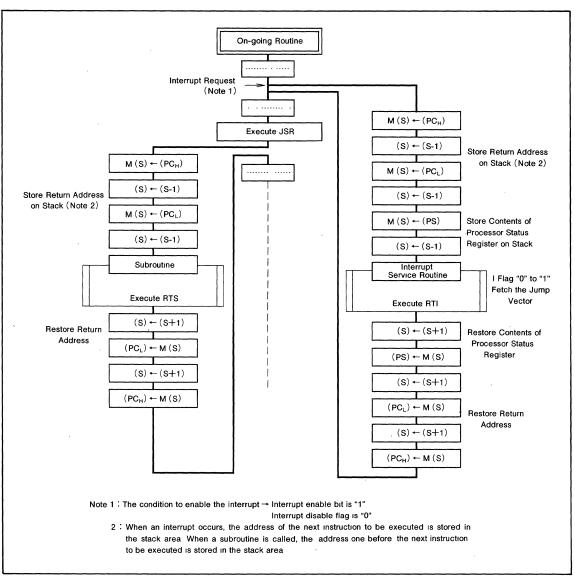

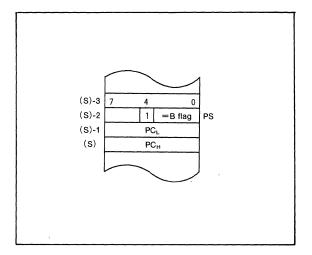

The stack pointer is an 8-bit register used during subroutine calls and interrupts. The stack is used to store the current address data and processor status when branching to subroutines or interrupt routines.

The lower eight bits of the stack address are determined by the contents of the stack pointer. The upper eight bits of the stack address are determined by the Stack Page Selection Bit. If the Stack Page Selection Bit is "0", then the RAM in the zero page is used as the stack area. If the Stack Page Selection Bit is "1", then RAM in page 1 is used as the stack area.

The Stack Page Selection Bit is located in the SFR area in the zero page. Note that the initial value of the Stack Page Selection Bit varies with each microcomputer type. Also some microcomputer types have no Stack Page Selection Bit and the upper eight bits of the stack address are fixed.

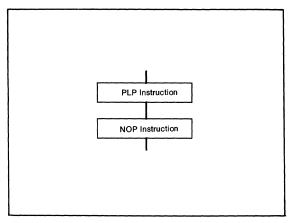

The operations of pushing register contents onto the stack and popping them from the stack are shown in Fig. 2.

#### Program counter (PC)

The program counter is a 16-bit counter consisting of two 8-bit registers  $PC_H$  and  $PC_L$ . It is used to indicate the address of the next instruction to be executed.

Fig. 1 MELPS 740 CPU register structure

| Table 1. Fush and pop instructions of accumulator of processor status regis | Table 1. | ructions of accumulator or processor status regis |

|-----------------------------------------------------------------------------|----------|---------------------------------------------------|

|-----------------------------------------------------------------------------|----------|---------------------------------------------------|

|                           | Push instruction to stack | Pop instruction from stack |

|---------------------------|---------------------------|----------------------------|

| Accumulator               | PHA                       | PLA                        |

| Processor status register | PHP                       | PLP                        |

#### SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

#### Processor status register (PS)

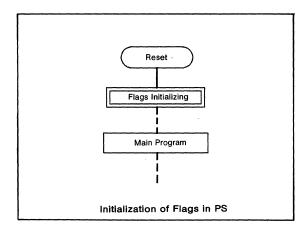

The processor status register is an 8-bit register consisting of flags which indicate the status of the processor after an arithmetic operation. Branch operations can be performed by testing the Carry (C) flag, Zero (Z) flag, Overflow (V) flag, or the Negative (N) flag. In decimal mode, the Z, V, N flags are not valid.

After reset, the Interrupt disable (I) flag is set to "1", but all other flags are undefined. Since the Index X mode (T) and Decimal mode (D) flags directly affect arithmetic operations, they should be initialized in the beginning of a program.

(1) Carry flag (C)

The C flag contains a carry or borrow generated by the arithmetic logic unit (ALU) immediately after an arithmetic operation. It can also be changed by a shift or rotate instruction.

(2) Zero flag (Z)

The Z flag is set if the result of an immediate arithmetic operation or a data transfer is "0", and cleared if the result is anything other than "0".

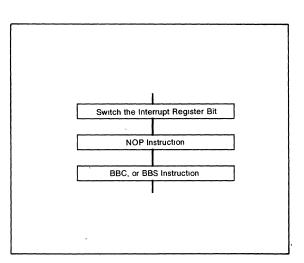

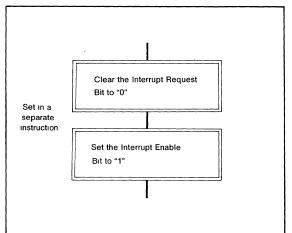

(3) Interrupt disable flag (1)

The I flag disables all interrupts except for the interrupt generated by the BRK instruction.

Interrupts are disabled when the I flag is "1".

When an interrupt occurs, this flag is automatically set to "1" to prevent other interrupts from interfering until the current interrupt is serviced.

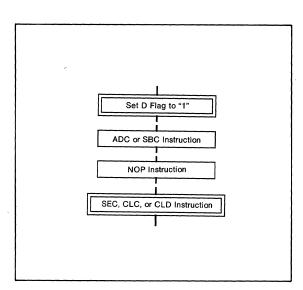

(4) Decimal mode flag (D)

The D flag determines whether additions and subtractions are executed in binary or decimal. Binary arithmetic is executed when this flag is "0"; decimal arithmetic is executed when it is "1". Decimal correction is automatic in decimal mode. Only the ADC and SBC instructions can be used for decimal arithmetic. (5) Break flag (B)

The B flag is used to indicate that the current interrupt was generated by the BRK instruction. The BRK flag in the processor status register is always "0". When the BRK instruction is used to generate an interrupt, the processor status register is pushed onto the stack with the break flag set to "1". The saved processor status is the only place where the break flag is ever set.

(6) Index X mode flag (T)

When the T flag is "0", arithmetic operations are performed between accumulator and memory, e.g. the results of an operation between two memory locations is stored in the accumulator. When the T flag is "1", direct arithmetic operations and direct data transfers are enabled between memory locations, i.e. between memory and memory, memory and I/O, and I/O and I/O. In this case, the result of an arithmetic operation performed on data in memory location 1 and memory location 2 is stored in memory location 2. The address of memory location 1 is specified by index register X, and the address of memory location 2 is specified by normal addressing modes.

(7) Overflow flag (V)

The V flag is used during the addition or subtraction of one byte of signed data. It is set if the result exceeds +127 to -128. When the BIT instruction is executed, bit 6 of the memory location operated on by the BIT instruction is stored in the overflow flag.

(8) Negative flag (N)

The N flag is set if the result of an arithmetic operation or data transfer is negative. When the BIT instruction is executed, bit 7 of the memory location operated on by the BIT instruction is stored in the negative flag.

#### Table 2. Set and clear instructions of each bit of processor status register

|                   | C flag | Z flag | I flag | D flag | B flag | T flag | V flag | N flag |

|-------------------|--------|--------|--------|--------|--------|--------|--------|--------|

| Set instruction   | SEC    |        | SEI    | SED    |        | SET    | _      | _      |

| Clear instruction | CLC    |        | CLI    | CLD    |        | CLT    | CLV    |        |

#### SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

#### ADDRESSING MODE

The MELPS 740 Family has 17 addressing modes and a powerful memory access capability.

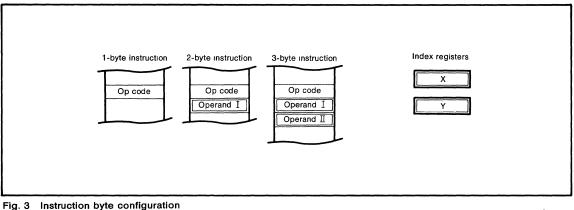

When extracting data required for arithmetic and logic operations from memory or when storing the results of such operations in memory, a memory address must be specified. The specification of the memory address is called addressing. The MELPS 740 Family instructions can be classified as 1-byte, 2-byte, and 3-byte instructions. In each case, the first byte is known as the OPCODE which forms the basis of the instruction. A second or third byte is called an OPERAND which affects the addressing. The contents of index registers X and Y can also effect the addressing.

Although there are many addressing modes, there is always a particular memory location specified. What differs is whether the operand, the index register contents, or a combination of both should be used to specify the memory or jump destination. Based on these 3 types of instructions, the range of variation is increased and operation is enhanced by combinations of the bit operation instructions, jump instruction, and arithmetic instructions.

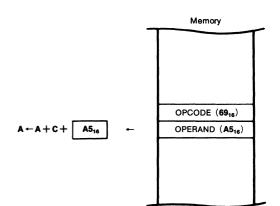

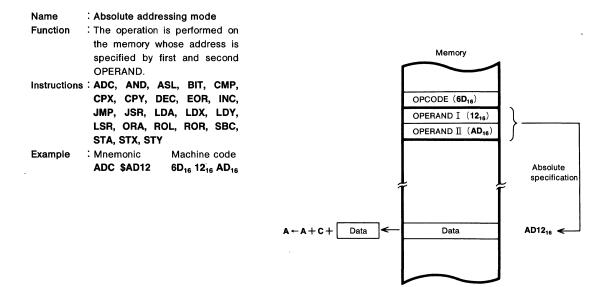

| Name         | Immediate addressing mode                   |

|--------------|---------------------------------------------|

| Function     | The OPERAND follows im-                     |

|              | mediately after the OPCODE.                 |

| Instructions | ADC, AND, CMP, CPX, CPY,                    |

|              | EOR, LDA, LDX, LDY, ORA,                    |

|              | SBC                                         |

| Example      | : Mnemonic Machine code                     |

|              | ADC #\$A5 69 <sub>16</sub> A5 <sub>16</sub> |

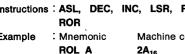

| Name         | : Accumulator addressing mode   |

|--------------|---------------------------------|

| Function     | : The operation is performed on |

|              | the accumulator.                |

| Instructions | : ASL, DEC, INC, LSR, ROL,      |

|              | ROR                             |

| Example      | : Mnemonic Machine code         |

|            | Bit 7 |      |        |   | <br>Bit 0 |

|------------|-------|------|--------|---|-----------|

|            |       |      |        |   |           |

| Carry flag |       | Accu | mulato | r |           |

| Machine          | әс |

|------------------|----|

| 2A <sub>16</sub> |    |

#### SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

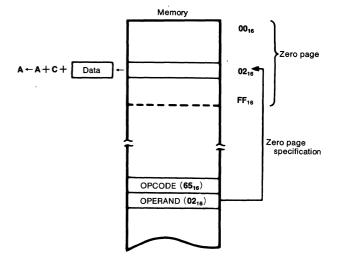

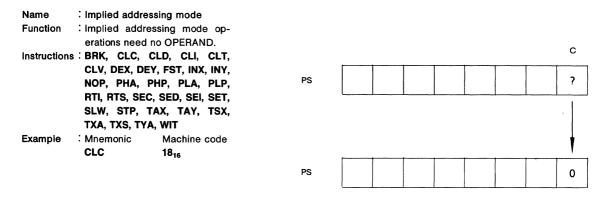

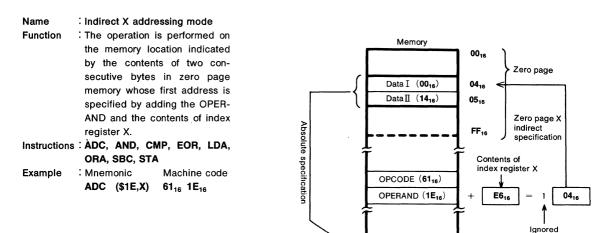

Name

: Zero page addressing mode

Function

: The operation is performed in zero page memory (00<sub>16</sub> to FF<sub>16</sub>)

Instructions

: ADC, AND, ASL, BIT, CMP, COM, CPX, CPY, DEC, EOR, INC, LDA, LDM, LDX, LDY, LSR. ORA. ROL. ROR. RRF.

|         | SBC, STA, STX, STY, TST |                                   |  |  |

|---------|-------------------------|-----------------------------------|--|--|

| Example | : Mnemonic              | Machine code                      |  |  |

|         | ADC \$02                | 65 <sub>16</sub> 02 <sub>16</sub> |  |  |

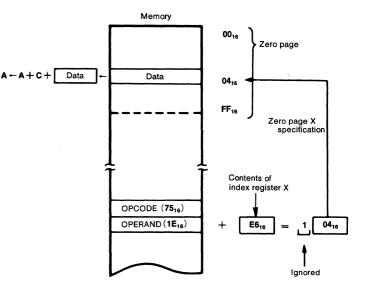

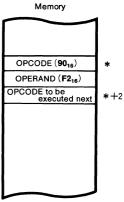

| Name        | Zero page X addressing mode     |

|-------------|---------------------------------|

| Function    | : The operation is performed on |

|             | the zero page memory location   |

|             | whose address is specified by   |

|             | adding the OPERAND to the       |

|             | contents of index register X.   |

| Instruction | S ADC, AND, ASL, CMP, DEC,      |

- DIV, EOR, INC, LDA, LDY, LSR, MUL, ORA, ROL, ROR, SBC, STA, STY Example : Mnemonic Machine code

- ADC \$1E,X 75<sub>16</sub> 1E<sub>16</sub>

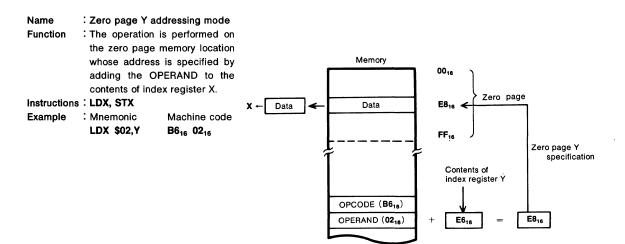

Contents of index register Y

EE<sub>16</sub>

AE0016

AE0016

Absolute Y specification

#### SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

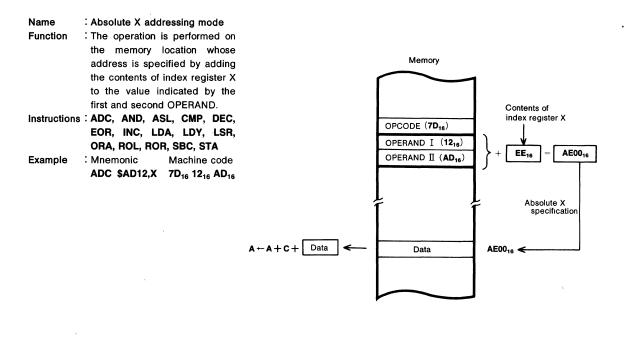

| Name<br>Funçtion       | : Absolute Y addressing mode<br>: The operation is performed on<br>the memory location whose<br>address is specified by adding<br>the contents of index register Y<br>to the value indicated by the | Memory                                                                                                             |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| Instruction<br>Example | first and second OPERAND.<br>s : ADC, AND, CMP, EOR, LDA,<br>LDX, ORA, SBC, STA<br>: Mnemonic Machine code<br>ADC \$AD12,Y 79 <sub>16</sub> 12 <sub>16</sub> AD <sub>16</sub>                       | OPCODE ( <b>79<sub>16</sub></b> )<br>OPERAND I ( <b>12<sub>16</sub></b> )<br>OPERAND II ( <b>AD<sub>16</sub></b> ) |

|                        |                                                                                                                                                                                                     | $\hat{f}$ $\hat{f}$                                                                                                |

$A \leftarrow A + C +$

Data

Data

### SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

Carry flag reset

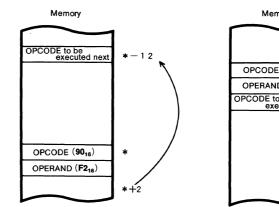

- Name

: Relative addressing mode

Function

: Conditionally jumps to the address produced by adding the Program Counter to the OPERAND.

Instructions

: BCC, BCS, BEQ, BMI, BNE,

- BPL, BRA, BVC, BVS Example : Mnemonic Machine code

- Example : Mnemonic Machine code BCC \*-12 90<sub>16</sub> F2<sub>16</sub>

Jumps to \* -12 address when carry flag(C) is cleared.

Proceed to next address when carry flag(C) is set.

### SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

A ← A + C +

Data

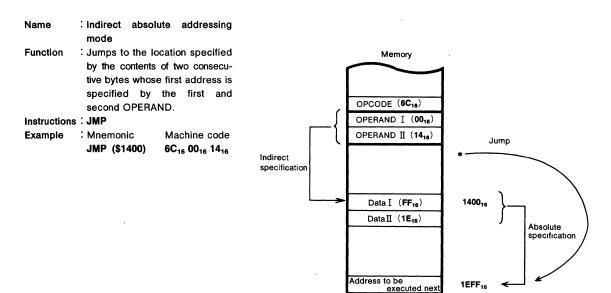

In this example, data  $\rm I~(00_{16})$  and data  $\rm II~(14_{16})$  have been stored beforehand.

1400<sub>16</sub>

Data

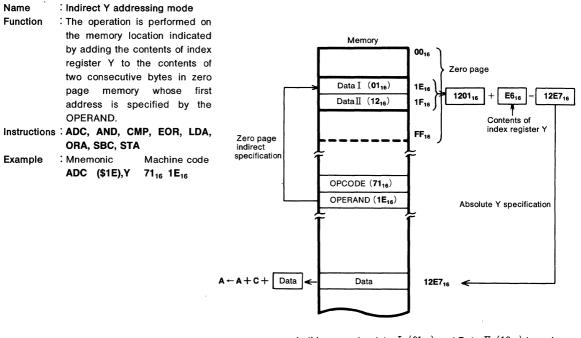

In this example, data  $I \hspace{.1in} (01_{16})$  and Data  $II \hspace{.1in} (12_{16})$  have been stored beforehand.

### SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

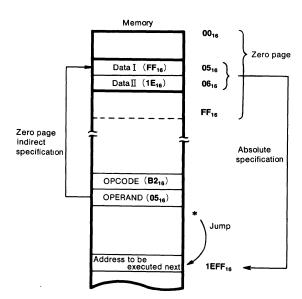

: Zero page indirect absolute

: Jumps to the location specified

by the contents of two con-

secutive bytes in zero page

memory whose first address is

Machine code

B216 0516

specified by the OPERAND.

addressing mode

Name

Function

Example

Instructions : JMP, JSR

: Mnemonic

JMP (\$05)

In this example,  $FF_{16}\,as$  data  $\,I\,$  and  $1E_{16}\,as$  data  $\,I\,$  have been stored beforehand.

In this example,  $\text{FF}_{\text{16}}$  as data I and  $\text{1E}_{\text{16}}$  as data II have been stored beforehand.

#### SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

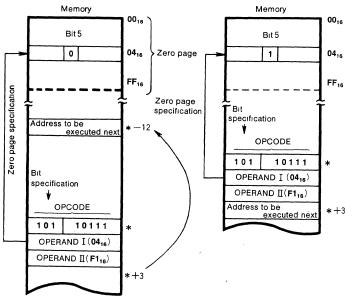

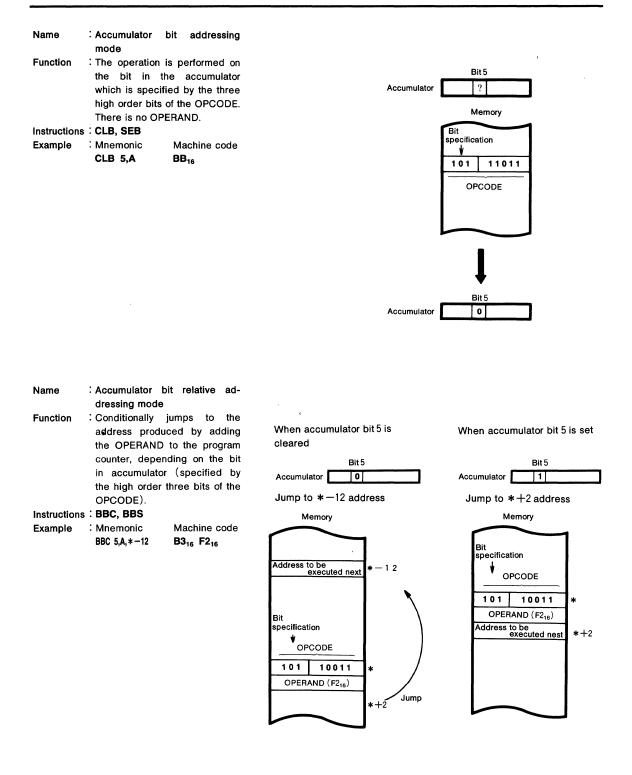

| Name         | Zero page<br>mode                                                     | bit addressing                                                                               |                            | Maman                                                                      | ×                                              |

|--------------|-----------------------------------------------------------------------|----------------------------------------------------------------------------------------------|----------------------------|----------------------------------------------------------------------------|------------------------------------------------|

| Function     | The operation<br>the bit (specif<br>high order bits<br>on the zero pa | is performed on<br>fied by the three<br>of the OPCODE),<br>ge memory loca-<br>y the OPERAND. | [ <del>-</del>             | Bit 5                                                                      | 00 <sub>16</sub><br>04 <sub>16</sub> Zero page |

| Instructions | CLB, SEB                                                              |                                                                                              |                            |                                                                            | FF <sub>16</sub>                               |

| Example      | : Mnemonic<br>CLB 5,\$04                                              | Machine code<br>BF <sub>16</sub> 04 <sub>16</sub>                                            | Zero page<br>specification | Bit<br>specification<br>OPCODE<br>101 11111<br>OPERAND (04 <sub>16</sub> ) |                                                |

Name : Zero page bit relative addressing mode Function : Conditionally jumps to the address specified by adding the second OPERAND to the program counter, depending on the bit (specified by the three higher order bits of the OPCODE) in the zero page memory location specified by the first OPERAND. Instructions : BBC, BBS

Example : Mnemonic Machine code BBC 5,\$04,\*-12 B7<sub>16</sub> 04<sub>16</sub> F1<sub>16</sub> Jump to \* - 12 address when  $04_{16}$  address bit 5 is cleared.

Advance to \*+3 address when  $04_{16}$  address bit 5 is set.

0416

Bit 5

#### SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

۰.

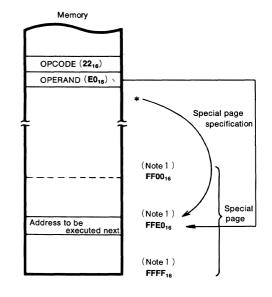

| Name         | Special page addressing mode     |

|--------------|----------------------------------|

| Function     | : Jumps to the specified address |

|              | in the special page area. The    |

|              | lower eight bits are specified   |

|              | by the OPERAND and the up-       |

|              | per eight bits are defined by    |

|              | the special page (see Note 1).   |

| Instructions | : JSR                            |

| Example      | Mnemonic Machine code            |

JSR \\$FFE0 22<sub>16</sub> E0<sub>16</sub>

Note 1 : Note that the special page is defined as the highest addressable 256 bytes of any given microcomputer and may be "FF16", "1F16", "2F16", etc

### SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

### LIST OF INSTRUCTION CODES

| $\langle \rangle$ | $D_3 \sim D_0$       | 0000  | 0001   | 0010           | 0011 | 0100  | 0101  | 0110  | 0111   | 1000 | 1001   | 1010 | 1011 | 1100  | 1101   | 1110                                                                                                                                | 1111  |

|-------------------|----------------------|-------|--------|----------------|------|-------|-------|-------|--------|------|--------|------|------|-------|--------|-------------------------------------------------------------------------------------------------------------------------------------|-------|

|                   | adecimal<br>notation | 0     | 1      | 2              | 3    | 4     | 5     | 6     | 7      | 8    | 9      | A    | в    | с     | D      | E                                                                                                                                   | F     |

| 0000              | 0                    | 0.01/ | ORA    | JSR            | BBS  |       | ORA   | ASL   | BBS    | РНР  | ORA    | ASL  | SEB  | _     | OBA    | ASL                                                                                                                                 | SEB   |

| 0000              | 0                    | BRK   | IND, X | ZP, IND        | 0, A | _     | ZP    | ZP    | 0, ZP  | РПР  | ІММ    | A    | 0, A |       | ABS    | ABS                                                                                                                                 | 0, ZP |

| 0001              | 1                    | BPL   | ORA    | CLT            | BBC  | _     | ORA   | ASL   | BBC    | CLC  | ORA    | DEC  | CLB  | _     | ORA    | ASL                                                                                                                                 | CLB   |

|                   |                      |       | IND, Y |                | 0, A |       | ZP, X | ZP, X | 0, ZP  |      | ABS, Y | A    | 0, A | 20.00 | ABS, X | ABS, X                                                                                                                              | 0, ZP |

| 0010              | 2                    | JSR   | AND    | JSR            | BBS  | BIT   | AND   | ROL   | BBS    | PLP  | AND    | ROL  | SEB  | BIT   | AND    | ROL                                                                                                                                 | SEB   |

|                   |                      | ABS   | IND, X | SP             | 1, A | ZP    | ZP    | ZP    | 1, ZP  |      | IMM    | Α    | 1, A | ABS   | ABS    | ABS                                                                                                                                 | 1, ZP |

| 0011              | 3                    | вмі   | AND    | SET            | BBC  | _     | AND   | ROL   | BBC    | SEC  | AND    | INC  | CLB  | LDM   | AND    | ROL                                                                                                                                 | CLB   |

|                   |                      |       | IND, Y | 021            | 1, A |       | ZP, X | ZP, X | 1, ZP  |      | ABS, Y | Α    | 1, A | ZP    | ABS, X | ABS, X                                                                                                                              | 1, ZP |

| 0100              | 4                    | RTI   | EOR    | STP            | BBS  | сом   | EOR   | LSR   | BBS    | РНА  | EOR    | LSR  | SEB  | JMP   | EOR    | LSR                                                                                                                                 | SEB   |

|                   |                      |       | IND, X | (Note)         | 2, A | ZP    | ZP    | ZP    | 2, ZP. |      | IMM    | Α    | 2, A | ABS   | ABS    | ABS                                                                                                                                 | 2, ZP |

| 0101              | 5                    | BVC   | EOR    | _              | BBC  |       | EOR   | LSR   | BBC    | CLI  | EOR    | _    | CLB  | _     | EOR    | LSR                                                                                                                                 | CLB   |

| 0101              |                      | BVC   | IND, Y |                | 2, A |       | ZP, X | ZP, X | 2, ZP  | ULI  | ABS, Y |      | 2, A |       | ABS, X | ABS, X                                                                                                                              | 2, ZP |

| 0110              | 6                    | RTS   | ADC    | MUL            | BBS  | TST   | ADC   | ROR   | BBS    | PLA  | ADC    | ROR  | SEB  | JMP,  | ADC    | ROR                                                                                                                                 | SEB   |

| 0110              | Ů                    | nio   | IND, X | (Note)         | 3, A | ZP    | ZP    | ZP    | 3, ZP  | FLA  | IMM    | А    | 3, A | IND   | ABS    | ABS                                                                                                                                 | 3, ZP |

| 0111              | -                    | 51/0  | ADC    |                | BBC  |       | ADC   | ROR   | BBC    | 051  | ADC    | _    | CLB  |       | ADC    | ROR                                                                                                                                 | CLB   |

| 0111              | 7                    | BVS   | IND, Y | _              | 3, A | _     | ZP, X | ZP, X | 3, ZP  | SEI  | ABS, Y |      | 3, A | _     | ABS, X | ABS, X                                                                                                                              | 3, ZP |

| 1000              |                      |       | STA    | RRF            | BBS  | STY   | STA   | STX   | BBS    |      |        |      | SEB  | STY   | STA    | STX                                                                                                                                 | SEB   |

| 1000              | 8                    | BRA   | IND, X | ZP             | 4, A | ZP    | ZP    | ZP    | 4 ZP   | DEY  | _      | ТХА  | 4, A | ABS   | ABS    | ABS                                                                                                                                 | 4, ZP |

|                   |                      |       | STA    |                | BBC  | STY   | STA   | STX   | BBC    |      | STA    |      | CLB  |       | STA    | 1                                                                                                                                   | CLB   |

| 1001              | 9                    | BCC   | IND, Y | -              | 4, A | ZP, X | ZP, X | ZP, Y | 4, ZP  | ΤΥΑ  | ABS, Y | TXS  | 4, A | -     | ABS, X | 198 (A. 1997)<br>1997 - 1997 - 1997<br>1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1 | 4, ZP |

|                   |                      | LDY   | LDA    | LDX            | BBS  | LDY   | LDA   | LDX   | BBS    |      | LDA    |      | SEB  | LDY   | LDA    | LDX                                                                                                                                 | SEB   |

| 1010              | A                    | IMM   | IND, X | імм            | 5, A | ZP    | ZP    | ZP    | 5. ZP  | TAY  | ІММ    | ТАХ  | 5, A | ABS   | ABS    | ABS                                                                                                                                 | 5, ZP |

|                   | _                    |       | LDA    | JMP            | BBC  | LDY   | LDA   | LDX   | BBG    |      | LDA .  |      | CLB  | LDY   | LQA    | LDX                                                                                                                                 | CLB   |

| 1011              | В                    | BCS   | IND, Y | ZP, IND        | 5, A | ZP, X | ZP, X | ZP. Y | 5, ZP  | CLV  | ABS, Y | TSX  | 5, A | ABS X | ABS, X | ABS, Y                                                                                                                              | 5, ZP |

|                   |                      | CPY   | CMP    | SLW            | BBS  | CPY   | CMP   | DEC   | BBS.   |      | CMP    |      | SEB  | CPY   | CMP    | DEC                                                                                                                                 | SEB   |

| 1100              | С                    | IMM   | IND, X | (Note)<br>∠WIT | 6, A | ZP    | ZP    | ZP    | 6 ZP   | INY  | ІММ    | DEX  | 6, A | ABS   | ABS    | ABS                                                                                                                                 | 6, ZP |

|                   |                      |       | CMP    |                | BBC  |       | CMP   | DEC   | BBC    |      | CMP    |      | CLB  |       | CMP    | DEC                                                                                                                                 | CLB   |

| 1101              | D                    | BNE   | IND, Y | -              | 6. A | -     | ZP, X | ZP, X | 6, ZP  | CLD  | ABS, Y |      | 6, A | -     | ABS. X | ABS, X                                                                                                                              | 6, ZP |

|                   |                      | CPX   | SBC    | FST            | BBS  | CPX   | SBC   | INC   | BBS    |      | SBC    |      | SEB  | CPX   | SBC    | INC                                                                                                                                 | SEB   |

| 1110              | E                    | ІММ   | IND, X | (Note)<br>∠DIV | 7, A | ZP    | ZP    | ZP    | 7, 2P  | INX  | імм    | NOP  | 7, A | ABS   | ABŠ    | ABS                                                                                                                                 | 7, ZP |

|                   |                      |       | SBC    | × =            | BBC  |       | SBC   | INC   | BBC    |      | SBC    |      | CLB  |       | SBC    | INC                                                                                                                                 | CLB   |

| 1111              | F                    | BEQ   | IND, Y | -              | 7, A | -     | ZP. X | ZP, X | 7. ZP  | SED  | ABS. Y | _    | 7, A | -     | ADO V  | ABS. X                                                                                                                              | 7. ZP |

#### Note Support of these instructions depends on the microcomputer type

| Instruction | Supported in the following microcomputer types |

|-------------|------------------------------------------------|

| FST         | M50740A-XXXSP, M50740ASP,                      |

|             | M50741-XXXSP, M50752-XXXSP,                    |

| SLW         | M50757-XXXSP, M50758-XXXSP                     |

| MUL         | Series 7450, Series 38000,                     |

|             | M37424M8-XXXSP,                                |

| DIV         | M37524M4-XXXSP                                 |

| Instruction | Not supported in the following microcomputer types |

|-------------|----------------------------------------------------|

|             | M50740A-XXXSP, M50740ASP,                          |

| WIT         | M50741-XXXSP, M50752-XXXSP,                        |

|             | M50757-XXXSP, M50758-XXXSP                         |

|             | M50752-XXXSP, M50757-XXXSP,                        |

| STP         | M50758-XXXSP, M37424M8-XXXSP,                      |

|             | M37524M4-XXXSP                                     |

3-byte instruction

2-byte instruction

1-byte instruction

### SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

### MACHINE INSTRUCTIONS

|                             |                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                     | L  |   |   |      |    |   |    | ٩dd | ress | ing ı    | mod  | e | ,<br> |    |   |                |     |

|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|---|---|------|----|---|----|-----|------|----------|------|---|-------|----|---|----------------|-----|

| Symbol                      | Function                                                                                                                                               | Details                                                                                                                                                                                                                                                                                                                                             |    | м | Р |      | м  | м |    | A   |      | E        | ЗIT, | A |       | ZΡ |   | в              | T,Z |

|                             |                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                     | 0P | n | # | F OF | 'n | # | 0P | n   | #    | 0P       | n    | # | 0P    | n  | # | 0P             | n   |

| ADC<br>(Note 1)<br>(Note 6) | When T=0<br>A←A+M+C                                                                                                                                    | Adds the carry, accumulator and memory con-<br>tents. The results are entered into the accumu-<br>lator.                                                                                                                                                                                                                                            |    |   |   | 69   | 2  | 2 |    |     |      |          |      |   | 65    | 3  | 2 |                |     |

|                             | When T=1<br>M(X) $\leftarrow$ M(X) +M+C                                                                                                                | Adds the contents of the memory in the<br>address indicated by index register X, the con-<br>tents of the memory specified by the addres-<br>sing mode and the carry The results are en-<br>tered into the memory at the address indicated<br>by index register X                                                                                   |    |   |   |      |    |   |    |     |      |          |      |   |       |    |   |                |     |

| AND<br>(Note 1)             | When T=0           A←A ∧ M           When T=1           M(X) ← M(X) ∧ M                                                                                | "AND's" the accumulator and memory contents<br>The results are entered into the accumulator<br>"AND's" the contents of the memory of the address<br>indicated by index register X and the contents of the<br>memory specified by the addressing mode The re-<br>sults are entered into the memory at the address in-<br>dicated by index register X |    |   |   | 29   | 2  | 2 |    |     |      |          |      |   | 25    | 3  | 2 |                |     |

| ASL                         | 7 0<br>C ← ←0                                                                                                                                          | Shifts the contents of accumulator or contents of<br>memory one bit to the left The low order bit of<br>the accumulator or memory is cleared and the<br>high order bit is shifted into the carry flag                                                                                                                                               |    |   |   |      |    |   | 0A | 2   | 1    |          |      |   | 06    | 5  | 2 |                |     |

| BBC<br>(Note 4)             | Ab or Mb=0?                                                                                                                                            | Branches when the contents of the bit specified in the accumulator or memory is "0"                                                                                                                                                                                                                                                                 |    |   |   |      |    |   |    |     |      | 13<br>2i | 4    | 2 |       |    |   | 17<br>17<br>2i | 5   |

| BBS<br>(Note 4)             | Ab or Mb=1?                                                                                                                                            | Branches when the contents of the bit specified in the accumulator or memory is "1"                                                                                                                                                                                                                                                                 |    |   |   |      |    |   |    |     |      | 03<br>2i | 4    | 2 |       |    |   | 07<br>+<br>2i  | 5   |

| BCC<br>(Note 4)             | C=0?                                                                                                                                                   | Branches when the contents of carry flag is "0"                                                                                                                                                                                                                                                                                                     |    |   |   |      |    |   |    |     |      |          |      |   |       |    |   |                |     |

| BCS<br>(Note 4)             | C=1?                                                                                                                                                   | Branches when the contents of carry flag is "1"                                                                                                                                                                                                                                                                                                     |    |   |   |      |    |   |    |     |      |          |      |   |       |    |   |                |     |

| BEQ<br>(Note 4)             | Z=1?                                                                                                                                                   | Branches when the contents of zero flag is "1"                                                                                                                                                                                                                                                                                                      |    |   |   | -    |    |   |    |     |      |          |      |   |       |    | - |                |     |

| BIT                         | AAM                                                                                                                                                    | "AND's" the contents of accumulator and mem-<br>ory The results are not entered anywhere                                                                                                                                                                                                                                                            |    |   |   |      |    |   |    |     |      |          |      |   | 24    | 3  | 2 |                |     |

| BMI<br>(Note 4)             | N=1?                                                                                                                                                   | Branches when the contents of negative flag is "1"                                                                                                                                                                                                                                                                                                  |    |   |   |      |    |   |    |     |      |          |      |   |       |    |   |                |     |

| BNE<br>(Note 4)<br>BPL      | Z=0?                                                                                                                                                   | Branches when the contents of zero flag is "0"                                                                                                                                                                                                                                                                                                      | _  |   |   |      |    |   |    |     |      |          |      |   |       |    |   |                |     |

| (Note 4)<br>BRA             | PC←PC±offset                                                                                                                                           | Branches when the contents of negative flag is<br>"0"<br>Jumps to address specified by adding offset to                                                                                                                                                                                                                                             |    |   | - |      |    |   |    |     |      | -        |      |   |       |    |   |                |     |

| BILA                        |                                                                                                                                                        | the program counter                                                                                                                                                                                                                                                                                                                                 |    |   |   |      |    |   |    |     |      |          |      |   |       |    |   |                |     |

| BRK                         | $B \leftarrow 1$ $M(S) \leftarrow PC_{H}$ $S \leftarrow S - 1$ $M(S) \leftarrow PC_{L}$ $S \leftarrow S - 1$ $M(S) \leftarrow PS$ $S \leftarrow S - 1$ | Executes a software interrupt                                                                                                                                                                                                                                                                                                                       | 00 | 7 | 1 |      |    |   |    |     |      |          |      |   |       |    |   |                |     |

|                             | PCL←ADL<br>PCH←ADH                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                     |    |   |   |      |    |   |    |     |      |          |      |   |       |    |   |                |     |

|    |      |   |    |     |   |    |     |     |   |    |    |   |    |    | Ad | dres | sind | amo      | ode     |      |    |    |     |   |    |     |   |    |     |   |    |    |   |    | Proc           | ess | or st | atus | rec | iste | r  |

|----|------|---|----|-----|---|----|-----|-----|---|----|----|---|----|----|----|------|------|----------|---------|------|----|----|-----|---|----|-----|---|----|-----|---|----|----|---|----|----------------|-----|-------|------|-----|------|----|

|    | (P,) | < |    | ZP, | Y | Т  | AE  | 3S  |   | Α  | BS | X | A  | BS |    | T    | INE  |          | <b></b> | P,II | 1D |    | ND, | x | 1  | ND, | Y | 1  | REL |   |    | SP |   | 7  | 6              | 5   | 4     | 3    | 2   | 1    | 0  |

| 0P | n    |   | 0P | T T | T | 0  |     | -7  |   | 0P |    | # | 0P | 1  | #  | 0P   | r    | <u> </u> |         | n    | #  | 0P | T   | # | 0P |     | # | 0P |     |   | 0P |    | # | N  | v              | т   | в     | D    | 1   | z    | c  |

| 75 | 4    | 2 |    |     |   | 61 |     | -+- |   | 7D |    | 3 | 79 |    | 3  |      |      |          |         |      |    | 61 | 6   | 2 | 71 | 6   | 2 |    |     |   |    |    |   | N  | V              | •   | •     | •    | •   | Z    | С  |

| 35 | 4    | 2 |    |     |   | 21 | D 4 | 1   | 3 | 3D | 5  | 3 | 39 | 5  | 3  |      |      |          |         |      |    | 21 | 6   | 2 | 31 | 6   | 2 |    |     |   |    |    |   | N  | •              | •   | •     | •    | •   | z    | •  |

| 16 | 6    | 2 |    |     |   | 0  | EE  | 5   | 3 | 1E | 7  | 3 |    |    |    |      |      |          |         |      |    |    |     |   |    |     |   |    |     |   |    |    |   | N  | •              | •   | •     | •    | •   | z    | С  |

|    |      |   |    |     |   |    |     |     |   |    |    |   |    |    |    |      |      |          |         |      |    |    |     |   |    |     |   |    |     |   |    |    |   | •  | •              | •   | •     | •    | •   | •    | •  |

|    |      |   |    |     |   |    |     |     |   |    |    |   |    |    |    |      |      |          |         |      |    |    |     |   |    |     |   |    |     |   |    |    |   | •  | •              | •   | •     | •    | •   | •    | •  |

|    |      |   |    |     |   |    |     |     |   |    |    |   |    |    |    |      |      |          |         |      |    |    |     |   |    |     |   | 90 | 2   | 2 |    |    |   | •  | •              | •   | •     | •    | •   | •    | •  |

|    |      |   |    |     |   |    |     |     |   |    |    |   |    |    |    |      |      |          |         |      |    |    |     |   |    |     |   | в0 | 2   | 2 |    |    |   | •  | •              | •   | •     | •    | •   | •    | •, |

|    |      |   |    |     |   |    |     |     |   |    |    |   |    |    |    |      |      |          |         |      |    |    |     |   |    |     |   | F0 | 2   | 2 |    |    |   | •  | •              | •   | •     | •    | •   | •    | •  |

|    |      |   |    |     |   | 20 |     | 1   | 3 |    |    |   |    |    |    |      |      |          |         |      |    |    |     |   |    |     |   |    |     |   |    |    |   | M7 | M <sub>6</sub> | •   | •     | •    | •   | z    | •  |

|    |      |   |    |     |   |    |     |     |   |    |    |   |    |    |    |      |      |          |         |      |    |    |     |   |    |     |   | 30 |     | 2 |    |    |   | •  | •              | •   | •     | •    | •   | •    | •  |

|    |      |   |    |     |   |    |     |     |   |    |    |   |    |    |    |      |      |          |         |      |    |    |     |   |    |     |   | D0 |     | 2 |    |    |   | •  | •              | •   | •     | •    | •   | •    | •  |

|    |      |   |    |     |   |    |     |     |   |    |    |   |    |    |    |      |      |          |         |      |    |    |     |   |    |     |   | 10 |     | 2 |    |    |   | •  | •              | •   | •     | •    | •   | •    | •  |

|    |      |   |    |     |   |    |     |     |   |    |    |   |    |    |    |      |      |          |         |      |    |    |     |   |    |     |   | 80 | 4   | 2 |    |    |   | •  | •              | •   | •     | •    | •   | •    | •  |

|    |      |   |    |     |   |    |     |     |   |    |    |   |    |    |    |      |      |          |         |      |    |    |     |   |    |     |   |    |     |   |    |    |   | •  | •              |     |       | •    |     |      |    |

|                 |                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                            |    |     |   |    |    |   | A  | ddro | essi | ing r         | nod  | e |           |    |   |          |     |     |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-----|---|----|----|---|----|------|------|---------------|------|---|-----------|----|---|----------|-----|-----|

| Symbol          | Function                                                                                                                                          | Details                                                                                                                                                                                                                                                                                                                                                                    |    | IMF | > |    | MN | / |    | Α    |      | E             | ЗIT, | A |           | ZΡ |   | в        | T,Z | Р   |

|                 |                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                            | 0P | n   | # | 0P | n  | # | 0P | n    | #    | 0P            | n    | # | 0P        | n  | # | 0P       | n   | #   |

| BVC<br>(Note 4) | V=0?                                                                                                                                              | Branches when the contents of overflow flag is "0 " $$                                                                                                                                                                                                                                                                                                                     |    |     |   |    |    |   |    |      |      |               |      |   |           |    |   |          |     |     |

| BVS<br>(Note 4) | V=1?                                                                                                                                              | Branches when the contents of overflow flag is "1"                                                                                                                                                                                                                                                                                                                         |    |     |   |    |    |   |    |      |      |               |      |   |           |    |   |          |     |     |

| CLB             | A <sub>b</sub> or M <sub>b</sub> ←0                                                                                                               | Clears the contents of the bit specified in the accumulator or memory to "0"                                                                                                                                                                                                                                                                                               |    |     |   |    |    |   |    |      |      | 1B<br>1<br>2i | 2    | 1 |           |    |   | 1F<br>2i | 5   | 2   |

| CLC             | C←0                                                                                                                                               | Clears the contents of the carry flag to "0"                                                                                                                                                                                                                                                                                                                               | 18 | 2   | 1 |    |    |   |    |      |      |               |      |   |           |    |   |          |     | _   |

| CLD             | D <b>←</b> 0                                                                                                                                      | Clears the contents of decimal mode flag to "0."                                                                                                                                                                                                                                                                                                                           | D8 | 2   | 1 |    |    |   |    |      |      |               |      |   |           |    |   |          |     |     |

| CLI             | 0→1                                                                                                                                               | Clears the contents of interrupt disable flag to "0"                                                                                                                                                                                                                                                                                                                       | 58 | 2   | 1 |    |    |   |    |      |      |               |      |   |           |    |   |          |     |     |

| CLT             | T⊷0                                                                                                                                               | Clears the contents of index X mode flag to "0"                                                                                                                                                                                                                                                                                                                            | 12 | 2   | 1 |    |    |   |    |      |      |               |      |   |           |    |   |          |     |     |

| CLV             | V <b>←</b> 0                                                                                                                                      | Clears the contents overflow flag to "0"                                                                                                                                                                                                                                                                                                                                   | В8 | 2   | 1 |    |    |   |    |      |      |               |      |   |           |    |   |          |     |     |

| CMP<br>(Note 3) | When T=0<br>A-M<br>When T=1<br>M(X)-M                                                                                                             | Compares the contents of accumulator and<br>memory<br>Compares the contents of the memory speci-<br>fied by the addressing mode with the contents<br>of the address indicated by index register X                                                                                                                                                                          |    |     |   | CS | 2  | 2 |    |      |      |               |      |   | C5        | 3  | 2 |          |     |     |

| СОМ             | M←M                                                                                                                                               | Forms a one's complement of the contents of<br>memory, and stores it into memory                                                                                                                                                                                                                                                                                           |    |     |   |    |    |   |    |      |      |               |      |   | 44        | 5  | 2 |          |     |     |

| СРХ             | Х—М                                                                                                                                               | Compares the contents of index register X and memory.                                                                                                                                                                                                                                                                                                                      |    |     |   | EO | 2  | 2 |    |      |      |               |      |   | E4        | 3  | 2 |          |     |     |

| CPY             | Ү—М                                                                                                                                               | Compares the contents of index register Y and memory                                                                                                                                                                                                                                                                                                                       |    |     |   | cc | 2  | 2 |    |      |      |               |      |   | C4        | 3  | 2 |          |     |     |

| DEC             | A←A—1 or<br>M←M—1                                                                                                                                 | Decrements the contents of the accumulator or memory by 1                                                                                                                                                                                                                                                                                                                  |    |     |   |    |    |   | 1A | 2    | 1    |               |      |   | C6        | 5  | 2 |          |     | No. |

| DEX             | x←x−1                                                                                                                                             | Decrements the contents of index register X by 1                                                                                                                                                                                                                                                                                                                           | CA | 2   | 1 |    |    |   |    |      |      |               |      |   |           |    |   |          |     |     |

| DEY             | <b>Y</b> ← <b>Y</b> −1                                                                                                                            | Decrements the contents of index register Y by 1                                                                                                                                                                                                                                                                                                                           | 88 | 2   | 1 |    |    |   |    |      |      |               |      |   |           |    |   |          |     |     |

| DIV<br>(Note 5) | $\begin{array}{l} A \leftarrow (M(zz+X+1)), \\ M(zz+X))/A \\ M(S) \leftarrow 1's \ complement \ of \ Remainder \\ S \leftarrow S - 1 \end{array}$ | Divides the 16-bit data that is the contents of $M(zz+x+1)$ for high byte and the contents of $M(zz+x)$ for low byte by the accumulator Stores the quotient in the accumulator and the 1's complement of the remainder on the stack                                                                                                                                        |    |     |   |    |    |   |    |      |      |               |      |   |           |    |   |          |     |     |

| EOR<br>(Note 1) | When T=0<br>A←A $\forall$ M<br>When T=1<br>M(X)←M(X) $\forall$ M                                                                                  | "Exclusive-ORs" the contents of accumulator<br>and memory The results are stored in the<br>accumulator.<br>"Exclusive-ORs" the contents of the memory<br>specified by the addressing mode and the con-<br>tents of the memory at the address indicated by<br>index register X The results are stored into the<br>memory at the address indicated by index reg-<br>ister X. |    |     |   | 49 | 2  | 2 |    |      |      |               |      |   | 45        | 3  | 2 |          |     |     |

| FST<br>(Note 5) |                                                                                                                                                   | Connects oscillator output to the $X_{\text{OUTF}}$ pin                                                                                                                                                                                                                                                                                                                    | E2 | 2   | 1 |    |    |   |    |      |      |               |      |   |           |    |   |          |     |     |

| INC             | A←A+1 or<br>M←M+1                                                                                                                                 | Increments the contents of accumulator or<br>memory by 1                                                                                                                                                                                                                                                                                                                   |    |     |   |    |    |   | ЗА | 2    | 1    |               | T    |   | E6        | 5  | 2 |          |     |     |

| INX             | X←X+1                                                                                                                                             | Increments the contents of index register X by 1                                                                                                                                                                                                                                                                                                                           | E8 | 2   | 1 |    |    |   |    |      |      | T             | T    |   | T         |    |   |          |     | ,   |

| INY             | Y⊷Y+1                                                                                                                                             | Increments the contents of index register Y by                                                                                                                                                                                                                                                                                                                             | С  | 3 2 | 1 |    |    |   |    | 1    | 1    |               | T    | 1 | $\square$ | -  |   |          |     | -   |

|    |     |   |          |     |          |    |    |   |           |    |    |              |    | Ad | dres     | sing | g mo | ode |      |          |    |     |   |    |     |    |    |     |   |    |    |   |   | Proc | ess | or st | atus | s reg | giste | r |

|----|-----|---|----------|-----|----------|----|----|---|-----------|----|----|--------------|----|----|----------|------|------|-----|------|----------|----|-----|---|----|-----|----|----|-----|---|----|----|---|---|------|-----|-------|------|-------|-------|---|

| Z  | ZP, | x |          | ZP, | Y        |    | AB | s | A         | BS | ,х | A            | BS | Y, |          | INC  | )    | zı  | P,IN | ١D       | П  | ٧D, | х | П  | ND, | Y, |    | REI | _ |    | SP |   | 7 | 6    | 5   | 4     | 3    | 2     | 1     | 0 |

| 0P | n   | # | 0P       | n   | #        | 0P | n  | # | 0P        | n  | #  | 0P           | n  | #  | 0P       | n    | #    | 0P  | n    | #        | 0P | n   | # | 0P | n   | #  | 0P | n   | # | 0P | n  | # | N | v    | т   | в     | D    | 1     | z     | С |

|    |     |   |          |     |          |    |    |   |           |    |    |              |    |    |          |      |      |     |      |          |    |     |   |    |     |    | 50 | 2   | 2 |    |    |   | • | •    | •   | •     | •    | •     | •     | • |

|    | -   | - | -        |     | -        |    | -  | - | -         |    | -  |              |    | -  | -        |      |      | -   |      | $\vdash$ | -  | -   | - |    |     |    | 70 | 2   | 2 |    |    |   | • | •    | •   | •     | •    | •     | •     | • |

|    |     | - | ļ        |     | -        | -  |    |   |           |    |    |              |    | -  |          |      |      | -   |      |          |    |     |   |    |     |    | -  |     |   | -  |    |   |   |      |     |       |      |       |       |   |

|    |     |   |          |     |          |    |    |   |           |    |    | ł            |    | }  |          |      |      |     |      | ł        |    |     |   |    |     |    |    |     |   |    |    |   | • | •    | •   | •     | •    | •     | •     | • |

|    |     | _ |          |     |          |    |    |   |           |    |    |              |    |    |          |      |      |     |      |          |    |     |   |    |     |    |    |     |   |    |    |   | • | •    | •   | •     | •    | •     | •     | 0 |

|    |     |   |          |     |          |    |    |   |           |    |    |              |    | }  |          |      |      |     |      |          |    |     |   |    |     |    |    | {   |   |    |    |   | • | •    | •   | •     | 0    | •     | •     | • |

|    |     |   |          |     |          |    |    |   |           |    |    |              |    |    |          |      |      |     |      |          |    |     |   |    |     |    |    |     |   |    |    |   | • | •    | •   | •     | •    | 0     | •     | • |

|    |     | - |          |     | -        | -  | -  | - |           | -  | -  | -            |    | -  | -        | -    |      |     |      |          |    |     | - |    |     | -  | -  |     | - | -  |    | - | • | •    | 0   | •     | •    |       |       |   |

|    |     |   |          |     |          |    |    |   |           |    |    |              |    |    |          |      |      |     |      |          |    |     |   |    |     |    |    |     |   |    |    |   |   |      |     |       |      |       |       |   |

|    |     |   |          |     |          |    |    |   |           |    |    |              |    |    |          |      |      |     |      |          |    |     |   |    |     |    |    |     |   |    |    |   | • | 0    | •   | •     | •    | •     | •     | • |

| D5 | 4   | 2 |          |     |          | СD | 4  | 3 | DD        | 5  | 3  | D9           | 5  | 3  |          |      |      |     |      |          | C1 | 6   | 2 | D1 | 6   | 2  |    |     |   |    |    |   | N | •    | •   | •     | •    | •     | z     | С |

|    |     |   |          |     |          |    |    |   |           |    |    |              |    |    |          |      |      |     |      |          |    |     |   |    |     |    |    |     |   |    |    |   |   |      |     |       |      |       |       |   |

|    |     |   |          |     |          |    |    |   |           |    |    |              |    | }  |          |      |      |     |      |          |    | ł   |   |    |     |    |    |     |   |    |    |   |   |      |     |       |      |       |       |   |

|    |     |   |          |     |          |    |    |   |           |    |    |              |    |    |          |      |      |     |      |          |    |     |   |    |     |    |    |     |   |    |    |   |   |      |     |       |      |       |       |   |

|    |     |   |          |     |          |    |    |   |           |    |    |              |    |    |          |      |      | ł   |      | }        |    |     |   |    |     |    |    |     |   |    |    |   | Ν | •    | •   | •     | •    | •     | z     | • |

|    |     | - |          | -   |          | EC | 4  | 3 | $\square$ |    |    |              |    |    |          | -    |      |     |      |          |    |     |   |    |     |    |    |     |   |    |    |   | N | •    | •   | •     | •    | •     | z     | С |

|    |     | - | $\vdash$ |     | $\vdash$ | cc | 4  | 3 | -         | -  |    |              | -  |    | $\vdash$ |      |      | -   |      |          |    |     |   |    |     |    |    |     |   | -  |    |   | N | •    | •   | •     | •    | •     | z     | С |

| D6 | 6   | 2 | -        | -   |          | CE | 6  | 3 | DE        | 7  | 3  |              |    | -  |          |      |      | -   |      |          | -  |     | - |    |     |    |    |     |   |    |    | - | N | •    | •   | •     | •    | •     | z     |   |

|    | _   | _ |          |     |          |    |    |   |           |    |    | $\downarrow$ |    |    |          |      |      |     |      |          |    |     |   |    |     |    |    |     |   |    |    |   |   |      |     |       |      |       |       |   |

|    |     |   |          |     |          |    |    |   |           |    |    |              |    |    |          |      |      |     |      |          |    |     |   |    |     |    |    |     |   |    |    |   | N | •    | •   | •     | •    | •     | z     | • |

|    |     |   |          |     |          |    |    |   |           |    |    |              |    |    |          |      |      |     |      |          |    |     |   |    |     |    |    |     |   |    |    |   | N | •    | •   | •     | •    | •     | Z     | • |

| E2 | 16  | 2 |          |     | -        | 1  | 1  |   | -         |    |    |              | -  | -  |          |      |      |     |      |          |    |     | - |    |     | -  |    |     |   |    |    |   | • | •    | •   | •     | •    | •     | •     | • |

|    |     | Į |          |     |          |    |    |   |           |    |    |              |    |    |          |      |      |     |      |          |    |     |   |    |     |    |    |     |   |    |    |   |   |      |     |       |      |       |       |   |

|    |     |   |          |     |          |    |    |   |           |    |    |              |    |    |          |      |      |     |      |          |    |     |   |    |     |    |    |     |   |    |    |   |   |      |     |       |      |       |       |   |

|    |     |   |          |     |          |    |    |   |           |    |    |              |    |    |          |      |      |     |      |          |    |     |   |    |     |    |    |     |   |    |    |   |   | 1    |     |       |      |       |       |   |

| 55 | 4   | 2 |          |     | -        | 4D | 4  | 3 | 5D        | 5  | 3  | 59           | 5  | 3  |          |      |      |     |      |          | 41 | 6   | 2 | 51 | 6   | 2  |    |     |   |    |    |   | N | •    | •   | •     | •    | •     | z     | • |

|    |     |   |          |     |          |    |    |   |           |    |    |              |    |    | ļ        |      |      |     |      |          |    |     |   |    |     |    |    |     |   |    |    |   |   |      |     |       |      |       |       |   |

|    |     |   |          |     |          |    |    |   |           |    |    |              |    |    |          |      |      |     |      |          |    |     |   |    |     |    |    |     |   |    |    |   |   |      |     |       |      |       |       |   |

|    |     |   |          |     |          |    |    |   |           |    |    |              |    |    |          |      |      |     |      |          |    |     |   |    |     |    |    |     |   |    |    |   |   |      |     |       |      |       |       |   |

|    |     |   |          |     |          |    |    |   |           |    |    |              |    |    |          |      |      |     |      |          |    |     |   |    |     |    |    |     |   |    |    |   |   |      |     |       |      |       |       |   |

| _  |     |   |          |     |          |    |    |   |           |    |    |              |    |    | {        |      |      |     |      |          |    |     |   |    |     |    |    |     |   |    |    |   |   |      |     |       |      |       |       |   |

|    |     |   |          |     |          |    |    |   |           |    |    |              |    |    |          |      |      |     |      |          |    |     |   |    |     |    |    |     |   |    |    |   | • | •    | •   | •     | •    | •     | •     | • |

| F6 | 6   | 2 |          |     |          | EE | 6  | 3 | FE        | 7  | 3  | t            |    |    |          |      |      |     |      |          | -  | -   |   |    |     | -  | -  |     |   |    |    |   | N | •    | •   | •     | •    | •     | z     | • |

|    |     |   | -        | -   | -        | -  | -  |   | -         | -  | -  | 1            |    | -  | -        |      | -    | -   |      | -        | -  |     | - |    |     | -  |    |     |   |    |    |   | N | •    | •   | •     | •    | •     | z     | • |

|    |     |   |          |     | -        | -  |    |   | -         | -  |    | -            |    |    |          |      | -    |     |      |          | -  |     | - |    |     | -  |    |     |   |    |    |   | L |      |     |       |      |       |       |   |

|    |     |   |          |     |          |    |    |   |           |    |    |              |    |    |          |      |      |     |      |          |    |     |   | Ì  |     |    |    |     |   |    |    |   | N | •    | •   | •     | •    | •     | z     | • |

|                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                         |    |     |   |    |            |   |    | Addr | ess | ing | mod  | le |    |    |   |    |       |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-----|---|----|------------|---|----|------|-----|-----|------|----|----|----|---|----|-------|

| Symbol          | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Details                                                                                                                                                                                                                                                                                                                 |    | імі | > | Γ  | IM         | м |    | Α    |     |     | BIT, | A  |    | ZP |   | в  | IT,ZP |

|                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | · · · · ·                                                                                                                                                                                                                                                                                                               | 0P | n   | # | OF | n r        | # | 0P | n    | #   | OF  | 'n   | #  | 0P | n  | # | 0P | n #   |