# LINK(IEEE 1394) MD8412B

**User's Manual**

**FUJIFILM MICRODEVICES CO., LTD**

Ver 1.10

# **MEMO**

| History |

|---------|

|---------|

| Revision | Date    | Modified                          |  |

|----------|---------|-----------------------------------|--|

| 1.10     | 6/17/99 | First revision of English manual. |  |

# Keys:

MSB, LSB of data : MSB on the right and LBS on the left

Negative logic signal description : Attached with # at the last end of signal name

Numeraldescription : Binary \*\*\*\*b or \*\*\*\*

Decimal \*\*\*\*

Hexadecimal \*\*\*\*h or 0x\*\*\*\*

Terminology : Byte Data in 8-bit width

Word Data in 16-bit width

Quadlet Data in 32-bit width

Octlet Data in 64-bit width

# **Associated Material**

IEEE P1394-1995 Standard for a High Performance Serial Bus P1394a Draft Standard for a High Performance Serial Bus IEEE Std 1212-1991 Command and Status Register architecture

# **Contents**

| 1 | General | Description | ns                                         | 1    |

|---|---------|-------------|--------------------------------------------|------|

|   | 1-1     | Features .  |                                            | 1    |

|   | 1-2     | Applicati   | ons                                        | 1    |

|   | 1-3     | Internal b  | lock diagram                               | 2    |

|   | 1-4     | Function    | al outlines                                | 3    |

|   |         | 1-4-1       | Host interface                             | 3    |

|   |         | 1-4-2       | PHY interface                              | 3    |

|   |         | 1-4-3       | Transmitter                                | 3    |

|   |         | 1-4-4       | Receiver                                   | 3    |

|   |         | 1-4-5       | Built-in buffer                            | 3    |

|   |         | 1-4-6       | Isochronous transfer functions             | 4    |

| _ | m ·     | 15          |                                            | _    |

| 2 |         | _           | on                                         |      |

|   | 2-1     | Function    | al description for terminals               | 5    |

| 3 | Control | Register    |                                            | 7    |

|   | 3-1     | Method o    | f register access                          | 7    |

|   | 3-2     | Contents    | of register                                | 8    |

|   |         | 3-2-1       | Version Register                           | 8    |

|   |         | 3-2-2       | Control Register                           | 8    |

|   |         | 3-2-3       | Node Identification Register               | . 11 |

|   |         | 3-2-4       | Reset Register                             | . 12 |

|   |         | 3-2-5       | Asyncronous Buffer Size Set Register       | . 13 |

|   |         | 3-2-6       | Isochronous Buffer Size Set Register       | . 14 |

|   |         | 3-2-7       | Packet Control Register                    | . 15 |

|   |         | 3-2-8       | Diagnostic Status Register                 | . 17 |

|   |         | 3-2-9       | Phy Control Register.                      | . 19 |

|   |         | 3-2-10      | ATRetries Register                         | . 20 |

|   |         | 3-2-11      | Cycle Timer Register                       | . 21 |

|   |         | 3-2-12      | Isochronous Packet Length Register         | . 22 |

|   |         | 3-2-13      | Isochronous Configuration Register 1,2,3,4 | . 22 |

|   |         | 3-2-14      | ATF Data Register                          | . 25 |

|   |         | 3-2-15      | ARF Data Register                          | . 25 |

|   |         | 3-2-16      | ITF/IRF Data Register                      | . 26 |

|   |         | 3-2-17      | IRF Data Register                          | . 26 |

|   |         | 3-2-18      | Buffer Status and Control Register         | . 27 |

|   |         |             |                                            |      |

# MD8412B

|   |          | 3-2-19     | Interrupt Register          | 28 |

|---|----------|------------|-----------------------------|----|

|   |          | 3-2-20     | Interrupt Mask Register     | 31 |

|   |          | 3-2-21     | TGo Register                | 31 |

|   |          | 3-2-22     | Bus Time Register           | 32 |

|   |          | 3-2-23     | AtRetries Register          | 33 |

|   | 3-3      | Registers  | S                           | 34 |

| 4 | Data Fo  | rmat       |                             | 36 |

|   | 4-1      | Asynchr    | onous                       | 36 |

|   |          | 4-1-1      | Quadlet Transmit            | 36 |

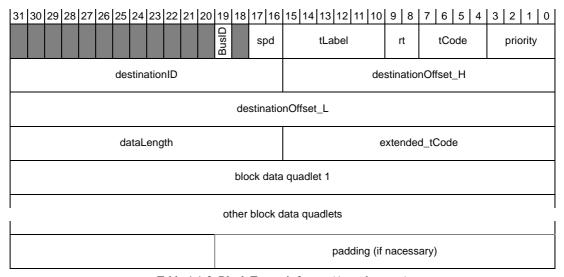

|   |          | 4-1-2      | Block Transmit              | 37 |

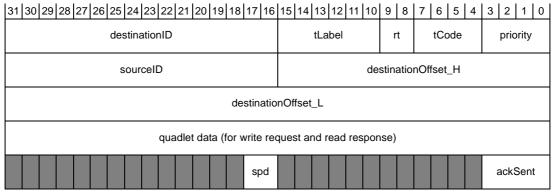

|   |          | 4-1-3      | Quadlet Receive             | 38 |

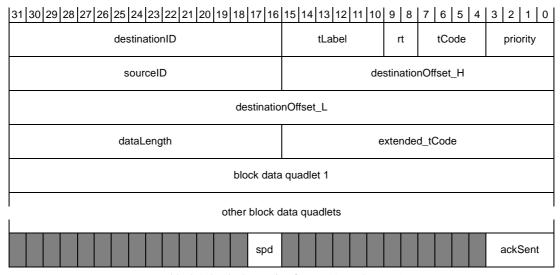

|   |          | 4-1-4      | Block Receive               | 40 |

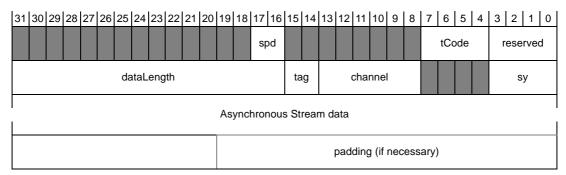

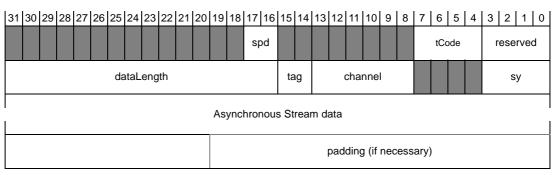

|   | 4-2      | Asynchr    | onous Stream                | 42 |

|   |          | 4-2-1      | Transmit                    | 42 |

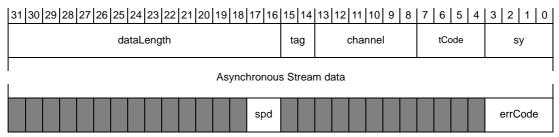

|   |          | 4-2-2      | Receive                     | 43 |

|   | 4-3      | Isochron   | ous                         | 44 |

|   |          | 4-3-1      | Normal Mode                 | 44 |

|   |          |            | 4-3-1-1 Transmit            | 44 |

|   |          |            | 4-3-1-2 Receive             | 45 |

|   |          | 4-3-2      | Auto-Mode                   | 46 |

|   |          |            | 4-3-2-1 Transmit            | 46 |

|   |          |            | 4-3-2-2 Receive             | 46 |

|   | 4-4      | Snoop      |                             | 47 |

|   | 4-5      | SelfID P   | acket                       | 48 |

|   | 4-6      | PHY Co     | ntrol Packet                | 50 |

|   |          | 4-6-1      | PHY Control Packet Transmit | 50 |

|   |          | 4-6-2      | PHY Control Packet Receive  | 50 |

|   | 4-7      | Code       |                             | 50 |

| 5 | Function | nal Descri | ption                       | 54 |

|   | 5-1      | Host inte  | erface                      | 54 |

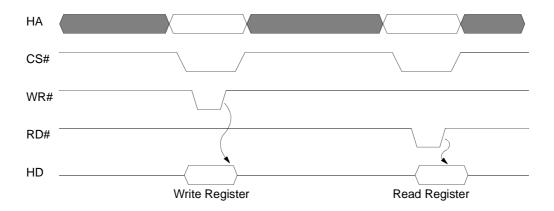

|   |          | 5-1-1      | Register access timing      | 54 |

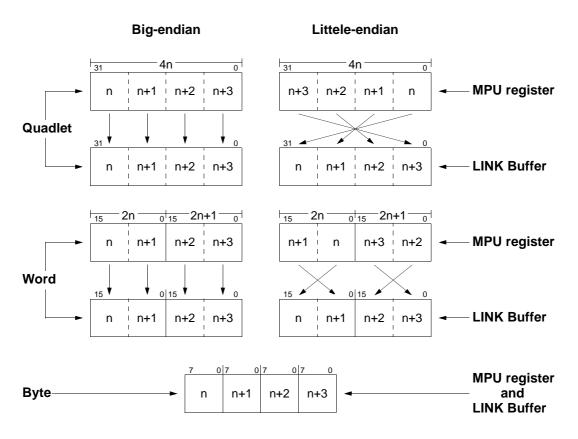

|   |          | 5-1-2      | Host bus width              | 55 |

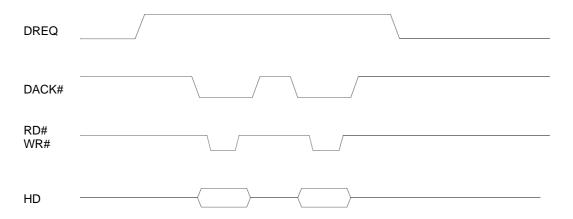

|   |          | 5-1-3      | DMA transfer                | 56 |

|   |          | 5-1-4      | Interrupt processing        |    |

|   | 5-2      | PHY-chi    | ip interface                |    |

|   |          | 5-2-1      | Connecting method           |    |

|   |          | 5-2-2      | PHY-chip control            |    |

|   |          | 5-2-3      | Request                     |    |

|   |          |            | -                           |    |

|      |          | 5-2-3-1         | LREQ                          | 60 |

|------|----------|-----------------|-------------------------------|----|

|      | 5-2-4    | Transfer        |                               | 62 |

|      |          | 5-2-4-1         | Status Request                | 62 |

|      |          | 5-2-4-2         | SinglePacketTransmit          | 63 |

|      |          | 5-2-4-3         | Concatenated Packet Transmit  | 64 |

|      |          | 5-2-4-4         | Receive                       | 65 |

|      | 5-2-5    | PHY-LINK        | I/F Reset Timing              | 66 |

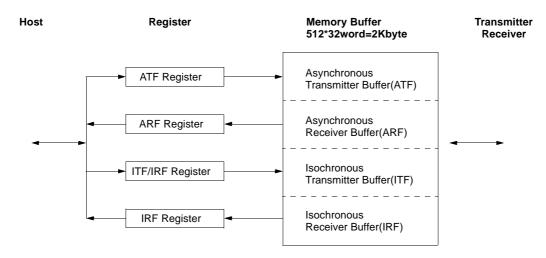

| 5-3  | Buffer a | ccess           |                               | 68 |

|      | 5-3-1    | Buffer config   | guration                      | 68 |

|      | 5-3-2    | Size setting f  | or each sub-buffer            | 69 |

|      | 5-3-3    | Buffer acces    | s by bus width                | 70 |

|      |          | 5-3-3-1         | Soft access                   | 70 |

|      |          | 5-3-3-2         | DMA access                    | 71 |

|      | 5-3-4    | Buffer contro   | lc                            | 73 |

|      |          | 5-3-4-1         | Asynchronous buffer control   | 73 |

|      |          |                 | 5-3-4-1-1 Transmission buffer | 74 |

|      |          |                 | 5-3-4-1-2 Reception buffer    | 75 |

|      |          | 5-3-4-2         | Isochronous buffer control    | 76 |

|      |          |                 | 5-3-4-2-1 Normal mode         | 76 |

|      |          |                 | 5-3-4-2-2 Auto-mode           | 76 |

| 5-4  | Isochron | ous transfer co | ontrol (auto-mode)            | 77 |

|      | 5-4-1    | Length contr    | ol                            | 77 |

|      | 5-4-2    | Transmission    | n start / stop control        | 77 |

|      | 5-4-3    | Sync control    |                               | 77 |

| 5-5  | Cycle M  | aster           |                               | 78 |

| 5-6  | 32-bit C | RC              |                               | 78 |

| 5-7  | Control  | flow            |                               | 78 |

|      | 5-7-1    | Asynchronou     | ıs Transmission               | 79 |

|      | 5-7-2    | Asynchronou     | ıs Reception                  | 81 |

|      | 5-7-3    | Isochronous     | Transmission                  | 84 |

|      | 5-7-4    | Isochronous     | Reception                     | 85 |

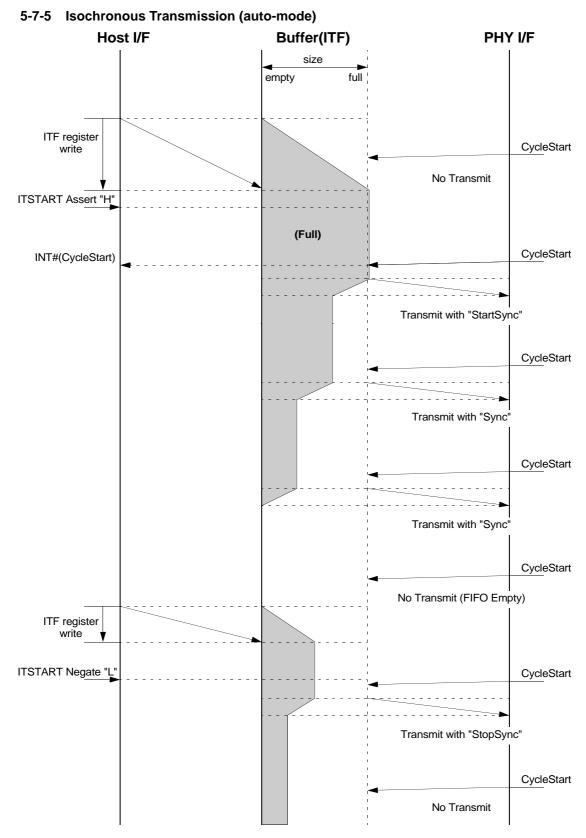

|      | 5-7-5    | Isochronous     | Transmission (auto-mode)      | 86 |

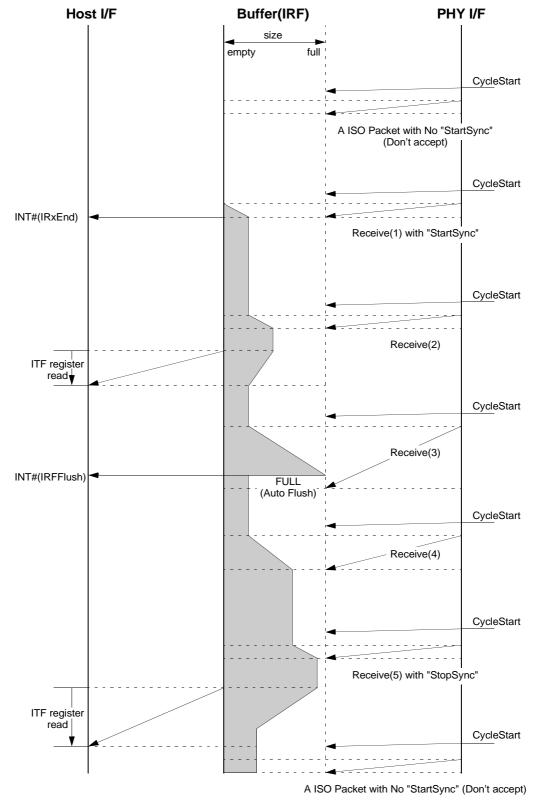

|      | 5-7-6    | Isochronous     | Reception (auto-mode)         | 87 |

| 5-8  | Asynchr  | onous stream t  | ransfer flow                  | 89 |

|      | 5-8-1    | Asynchronou     | is stream transmission        | 89 |

|      | 5-8-2    | Asynchronoi     | ıs stream reception           | 89 |

| 5-9  | Commar   | nd-Reset Packe  | et processing                 | 90 |

| 5-10 | Bus Nun  | nber for asyncl | nronous packet transmission   | 90 |

# MD8412B

| 6  |           | al Characteristics                |    |

|----|-----------|-----------------------------------|----|

|    | 6-1       | Absolute Rating                   | 1  |

|    | 6-2       | Recommended Operating Condition   | 1  |

|    | 6-3       | DC Characteristics                | 12 |

|    | 6-4       | AC Characteristics.               | 13 |

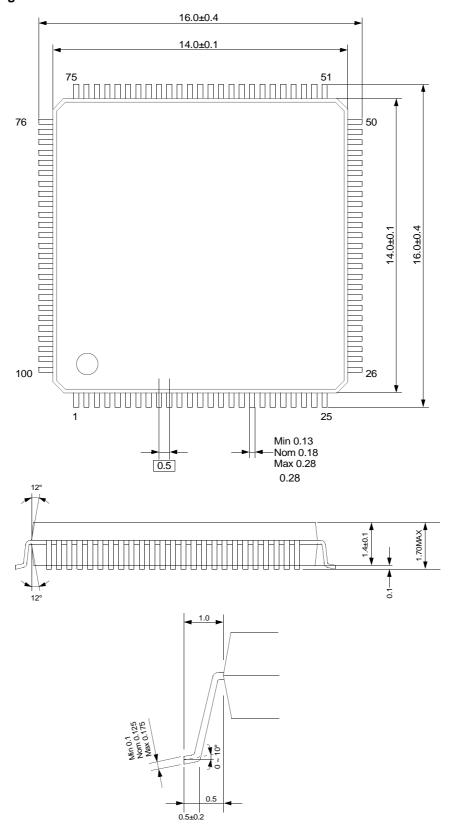

| 7  | Pin Assi  | gnment and Package Outline        | 20 |

| ,  |           |                                   |    |

|    | 7-1       | Pin Assignment                    |    |

|    | 7-2       | Package Outline                   | 19 |

|    |           |                                   |    |

| Ap | pendix 1  | I/O Status                        | 0  |

| Ap | ppendix 2 | Example circuit for AC connection | )1 |

| No | otes      |                                   | )2 |

# **Figure and Table Contents**

| Figure 1-3-1  | MD8412B Block Diagram                                      | 2  |

|---------------|------------------------------------------------------------|----|

| Figure 3-1-1  | Register Address on 8-Bit Bus                              |    |

| Figure 3-1-2  | Register Address on 16-Bit Bus                             |    |

| Figure 5-1-1  | Host Access Timing                                         | 54 |

| Figure 5-1-2  | DMA Transfer Timing                                        | 50 |

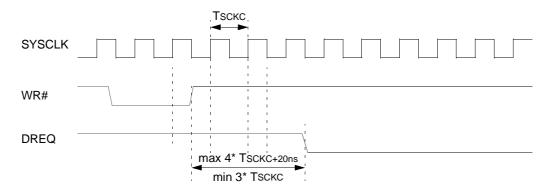

| Figure 5-1-3  | DREQ Negate Timing (WR#)                                   | 57 |

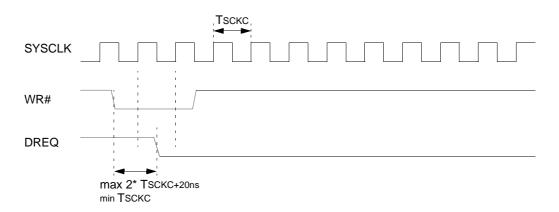

| Figure 5-1-4  | DREQ Negate Timing (RD#)                                   | 57 |

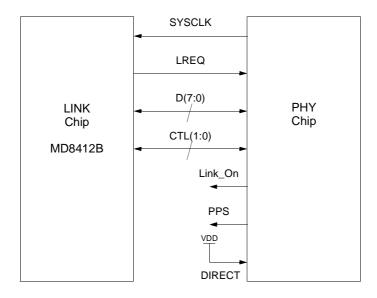

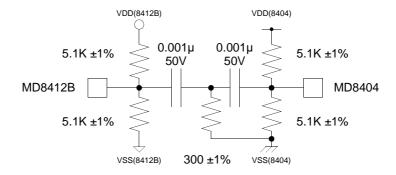

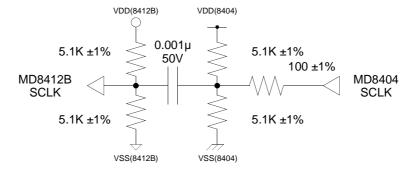

| Figure 5-2-1  | Connection between MD8412B and PHY-Chip                    | 58 |

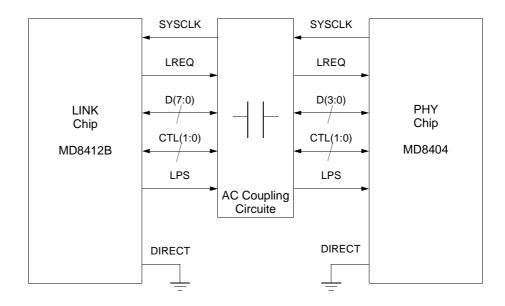

| Figure 5-2-2  | Connection between MD8412B and MD8404                      | 59 |

| Figure 5-2-3  | LREQ Stream                                                | 60 |

| Figure 5-2-4  | Status Request                                             | 62 |

| Figure 5-2-5  | SinglePacketTransmit                                       | 63 |

| Figure 5-2-6  | Concatenated Packet Transmit                               | 64 |

| Figure 5-2-7  | Receive                                                    | 65 |

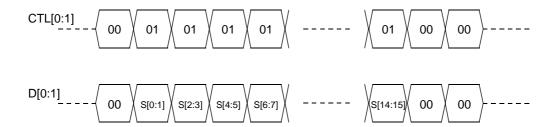

| Figure 5-2-8  | Speed Code (SP[0:7])                                       | 65 |

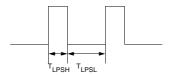

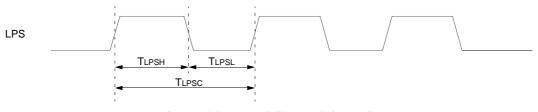

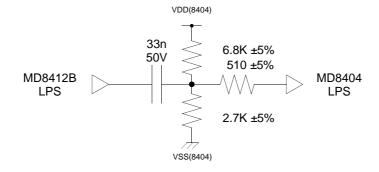

| Figure 5-2-9  | LPS output waveform in AC connection                       | 60 |

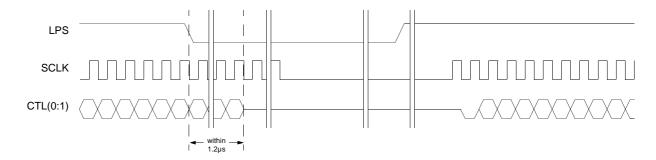

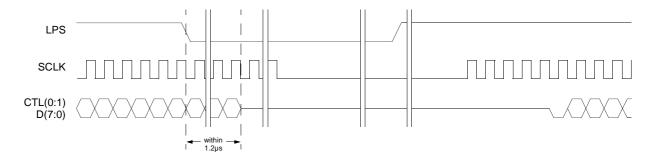

| Figure 5-2-10 | PHYIFRST="0"; PHY-LINK I/F Reset Sequence in AC connection | 67 |

| Figure 5-2-11 | PHYIFRST="1"; PHY-LINK I/F Reset Sequence in AC connection | 67 |

| Figure 5-3-1  | Buffer Assignment in Cases Other than IsoMode="011b"       | 68 |

| Figure 5-3-2  | Buffer Assignment in the Case of IsoMode="011b"            | 69 |

| Figure 5-3-3  | Sub-Buffer Size Assignment                                 | 70 |

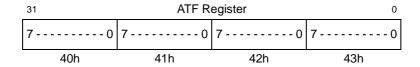

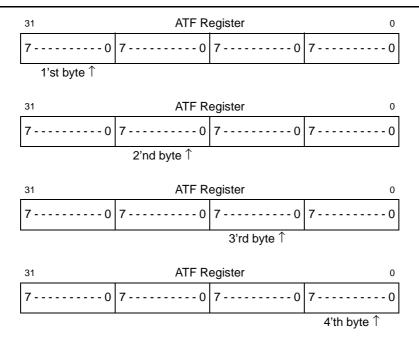

| Figure 5-3-4  | Register Operation (ATF) for 8-Bit Width Soft Access       | 70 |

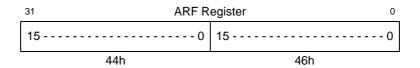

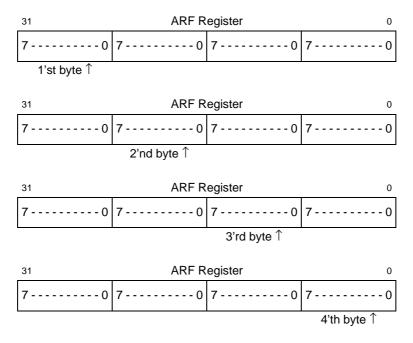

| Figure 5-3-5  | Register Operation (ARF) for 8-Bit Width Soft Access       | 7  |

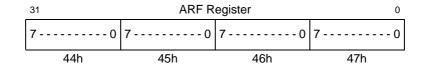

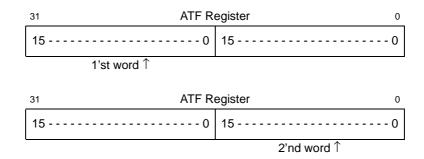

| Figure 5-3-6  | Register Operation (ATF) for 16-Bit Width Soft Access      | 71 |

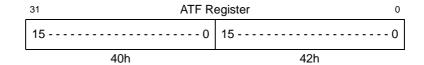

| Figure 5-3-7  | Register Operation (ARF) for 16-Bit Width Soft Access      | 71 |

| Figure 5-3-8  | Register Operation (ATF) for 8-Bit Width DMA Access        | 72 |

| Figure 5-3-9  | Register Operation (ARF) for 8-Bit Width DMA Access        | 72 |

| Figure 5-3-10 | Register Operation (ATF) for 16-Bit Width DMA Access       | 73 |

| Figure 5-3-11 | Register Operation (ARF) for 16-Bit Width DMA Access       | 73 |

| Figure 5-3-12 | Concept of ATF Operation                                   | 74 |

| Figure 5-3-13 | Concept of ARF Operation                                   | 75 |

| Figure 5-7-1  | ATF Transmission Flow -1                                   | 79 |

| Figure 5-7-2  | ATF Transmission Flow -2                                   | 80 |

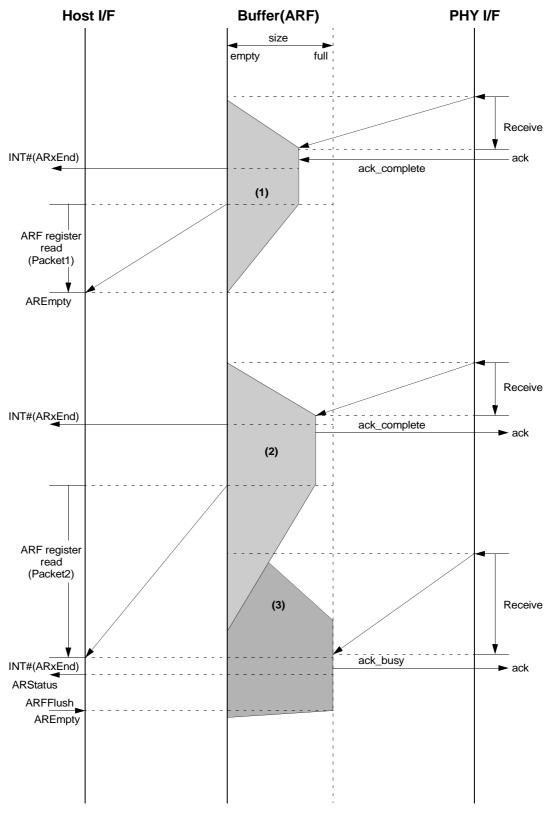

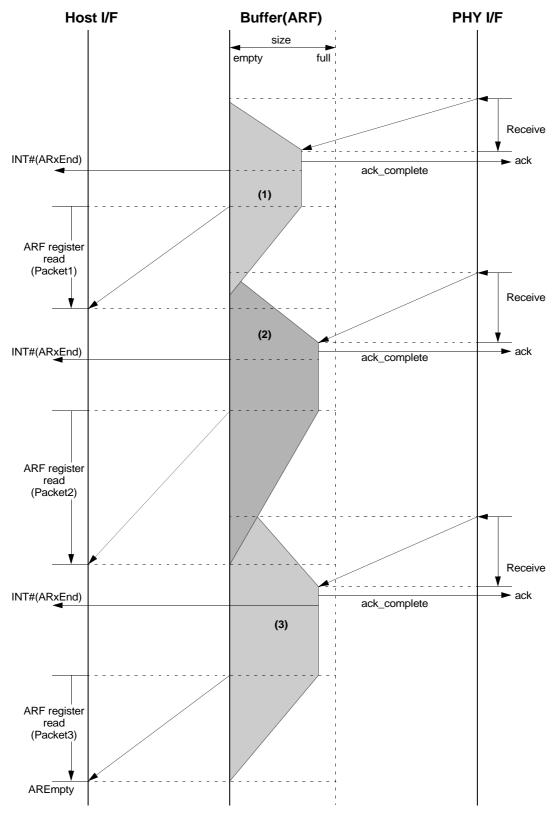

| Figure 5-7-3  | ARF Reception Flow -1                                      | 81 |

| Figure 5-7-4  | ARF Reception Flow -2                                      | 82 |

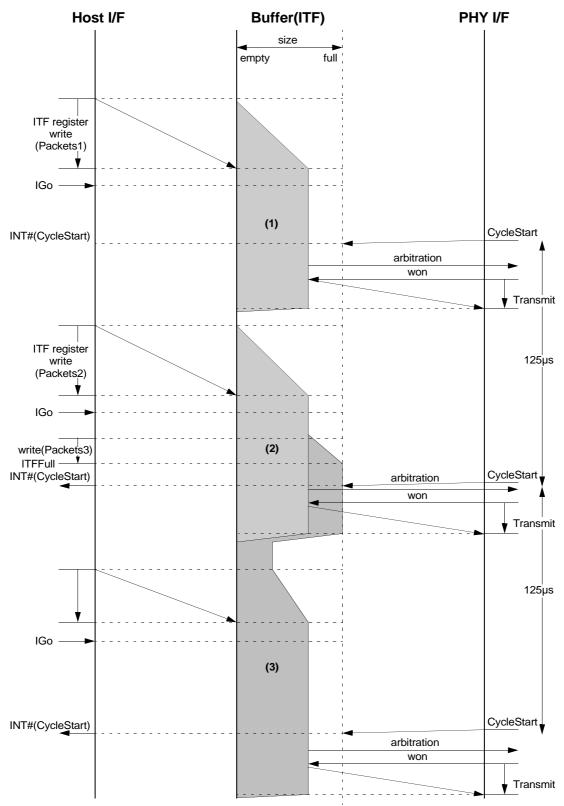

| Figure 5-7-5  | ITF Transmission Flow                                      | 84 |

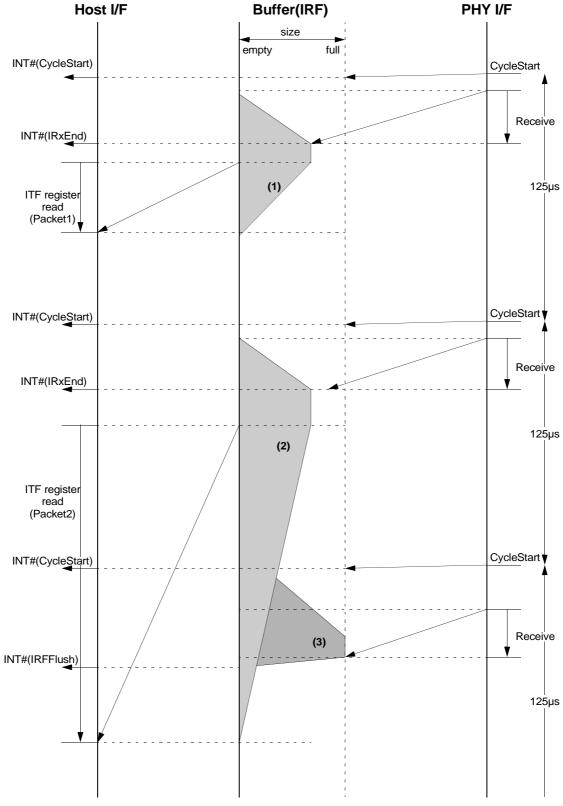

| Figure 5-7-6 | IRF Reception Flow                                        | 85 |

|--------------|-----------------------------------------------------------|----|

| Figure 5-7-7 | ITF Transmission Flow (auto-mode & SyncEn="1")            | 86 |

| Figure 5-7-8 | IRF Reception Flow (auto-mode & SyncEn="1")               | 87 |

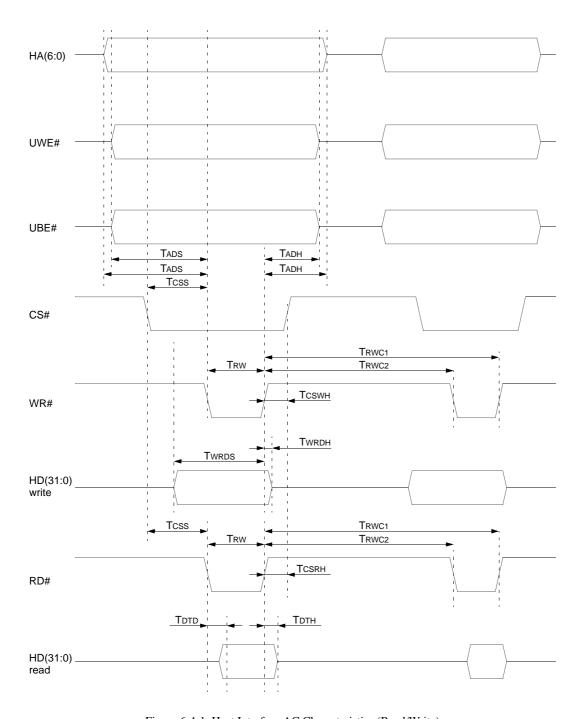

| Figure 6-4-1 | Host Interface AC Characteristics (Read/Write)            | 94 |

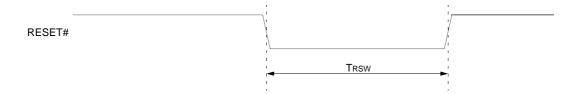

| Figure 6-4-2 | Host Interface AC Characteristics (Reset)                 | 95 |

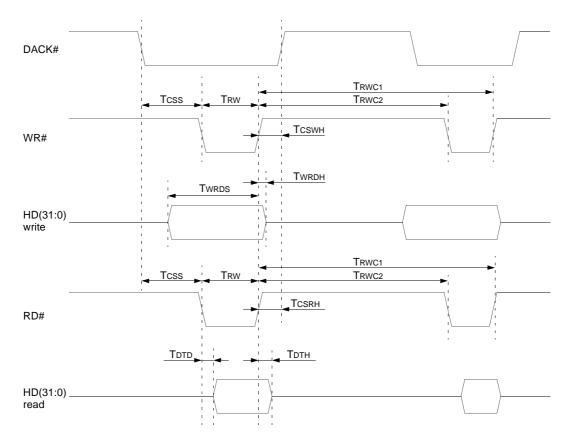

| Figure 6-4-3 | Interface AC Characteristics (DMA)                        | 95 |

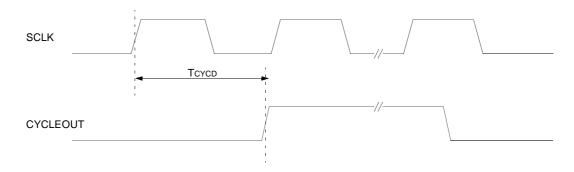

| Figure 6-4-4 | Host Interface AC Characteristics (CYCLEIN/OUT)           | 95 |

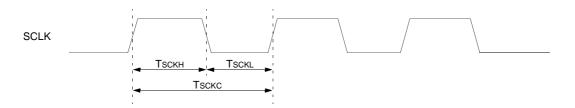

| Figure 6-4-5 | PHY AC Characteristics (SCLK)                             | 96 |

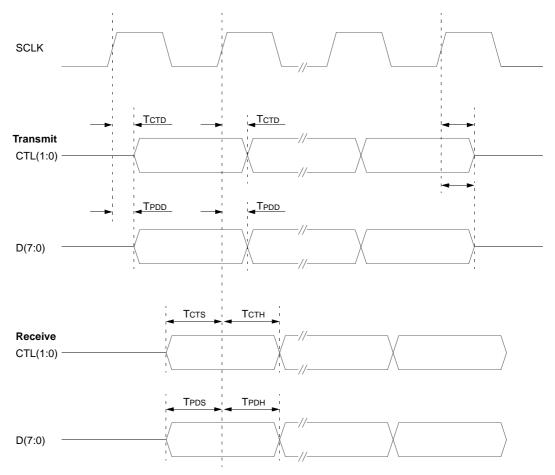

| Figure 6-4-6 | PHY AC Characteristics (CTL, D)                           | 97 |

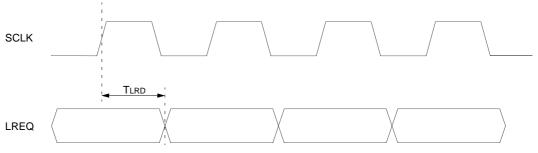

| Figure 6-4-7 | PHY AC Characteristics (LREQ)                             | 97 |

| Figure 6-4-8 | PHY AC Characteristics (LPS)                              | 97 |

| Table 2-1-1  | MD8412B Terminal Table (1)                                | 5  |

| Table 2-1-2  | MD8412B Terminal Table (2)                                | 6  |

| Table 3-3-1  | Registers 1                                               | 34 |

| Table 3-3-2  | Registers 2                                               | 35 |

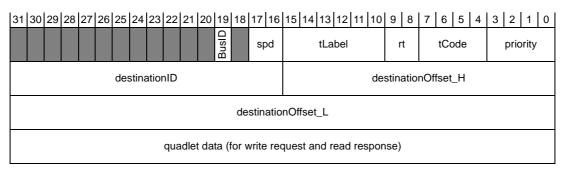

| Table 4-1-1  | Quadlet Transmit format (Asynchronous)                    | 36 |

| Table 4-1-2  | Block Transmit format (Asynchronous)                      | 37 |

| Table 4-1-3  | Quadlet Receive format (Asynchronous)                     | 38 |

| Table 4-1-4  | Block Receive format (Asynchronous)                       | 40 |

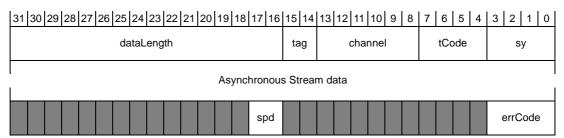

| Table 4-2-1  | Asynchronous Stream Transmit format                       | 42 |

| Table 4-2-2  | Asynchronous Stream Receive format                        | 43 |

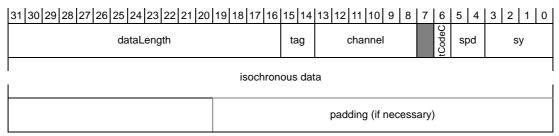

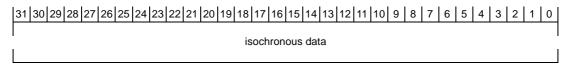

| Table 4-3-1  | Block Transmit format (Isochronous: normal)               | 44 |

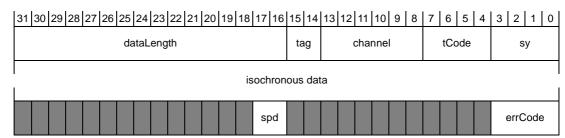

| Table 4-3-2  | Block Receive format (Isochronous: normal)                | 45 |

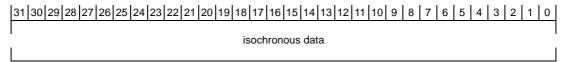

| Table 4-3-3  | Block Transmit format (Isochronous: auto)                 | 46 |

| Table 4-3-4  | Block Receive format (Isochronous: auto)                  | 46 |

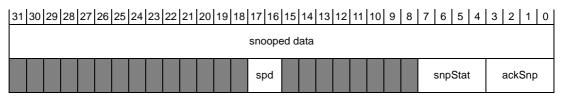

| Table 4-4-1  | Snoop Receive format                                      | 47 |

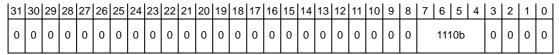

| Table 4-5-1  | SelfID Packet Receive format (first quadlet)              | 48 |

| Table 4-5-2  | SelfID Packet Receive format (SelfID Packet #0)           | 48 |

| Table 4-5-3  | SelfID Packet Receive format (SelfID Packet #1, #2, & #3) | 48 |

| Table 4-5-4  | SelfID Packet Receive format (last quadlet)               | 48 |

| Table 4-5-5  | SelfID Packet Receive format (pn)                         | 48 |

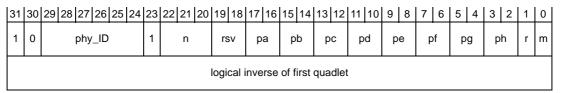

| Table 4-6-1  | PHY control packet format (first quadlet)                 | 50 |

| Table 4-7-1  | List of Retry code                                        | 50 |

| Table 4-7-2  | List of Transaction code (tCode)                          | 51 |

| Table 4-7-3  | List of Bus Number / Node Number                          | 51 |

| Table 4-7-4  | List of Data Length (Data Length)                         | 51 |

| Table 4-7-5  | List of Extension Transaction Code (Extend tCode)         | 52 |

| Table 4-7-6  | List of Speed Codes (spd)                                 | 52 |

|              |                                                           |    |

| Table 4-7-7  | List of Acknowledge Codes (Ack)                           | 53 |

|--------------|-----------------------------------------------------------|----|

| Table 5-1-2  | Little / Big Endian Mode                                  | 55 |

| Table 5-1-1  | Valid Host Data Bus Accessed from the Host                | 55 |

| Table 5-1-3  | DREQ Signal Assert / Negate Conditions                    | 56 |

| Table 5-2-1  | PHY-Chip Control Mode 1                                   | 59 |

| Table 5-2-2  | PHY-Chip Control Mode 2                                   | 59 |

| Table 5-2-3  | Request Format                                            | 60 |

| Table 5-2-4  | Speed Format                                              | 60 |

| Table 5-2-5  | Read Register Format                                      | 61 |

| Table 5-2-6  | Write Register Format                                     | 61 |

| Table 5-2-7  | Acceleration Control Format                               | 61 |

| Table 5-2-8  | Request Type                                              | 61 |

| Table 5-2-9  | Status Request Format                                     | 62 |

| Table 5-2-10 | LPS output                                                | 66 |

| Table 5-2-11 | LPS Output Characteristics in AC Connection               | 66 |

| Table 5-7-1  | Status of Interrupt and FIFO during ARF Reception         | 83 |

| Table 5-7-2  | Status of Interrupt and FIFO during IRF, TF/IRF Reception | 88 |

| Table 5-8-1  | Asynchronous Stream Transmit format                       | 89 |

| Table 5-8-2  | Asynchronous Stream Receive format                        | 89 |

| Table 6-4-1  | Host Interface AC Characteristics                         | 93 |

| Table 6-4-2  | PHY AC Characteristics                                    | 96 |

# **MEMO**

# 1 General Descriptions

The MD8412B is a link layer controller for high-speed serial buses, designed in accordance with the IEEE draft standard, IEEE 1394-1995. It involves all necessary functions for the link layer, and also functions to relieve the burden of the system for isochronous transfer. Therefore, it is suitable for being incorporated in equipment on the side of peripheral terminals.

#### 1-1 Features

- Packing for transmission and unpacking for reception, according to IEEE 1394-1995 and P1394a.

- Cycle master support

- Parity generation and error detection by 32-bit CRC

- Detection of dropped cycle start messages

- Direct with PHY chip (MD8402) and interface by AC coupling

- 3-speed support of 100/200/400Mb/sec.

- Control of the No. of transfers in each cycle during isochronous transfer

- Automatic insertion of a header in isochronous packet during transmission and automatic header separation and routing during reception

- Support of outbound retry sequence

- $\ Feasibility \ of selecting \ a \ host-bus \ width \ from \ 8/16/32-bit, \ enabling \ easy \ connection \ with \ a \ general-purpose \ MPU/micro-computer$

- Support of both big and little-endians during selection of host bus 16/32-bit

# 1-2 Applications

- Digital camera Digital VTR Digital audio

- Electronic musical instruments Scanner Printer

- Various storages

# 1-3 Internal block diagram

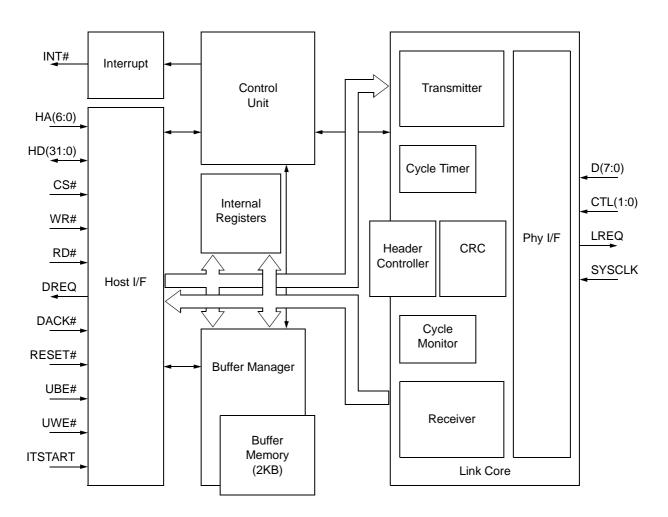

Figure 1-3-1 MD8412B Block Diagram

#### 1-4 Functional outlines

#### 1-4-1 Host interface

The host interface is composed of asynchronous buses in a width of SRAM-style 8/16/32-bit. Since DMA control functions are provided inside, DREQ signals can be generated according to the state of a buffer, enabling high-speed data transfer.

Bus width changeover of 8/16/32 can be controlled by a signal of UWE#, UBE#, A1, or A0. It is possible to change register and buffer access operation. All registers can be directly accessed from the host. In DMA transfer, internal buffer selection is effected to enable gaining access to the selected buffer.

#### 1-4-2 PHY interface

An interface is available, which enables direct connection with the PHY chip to process a physical layer according to IEEE 1394. Either 100Mbps or 200Mbps is acceptable for the PHY chip to be connected.

In the IEEE1394 Draft, the connection mode for the PHY and LINK chips is classified to the following two kinds:

- DC connection

- AC connection

This IC supports both kinds of connections.

#### 1-4-3 Transmitter

The transmitter reads out data from an asynchronous transmission buffer or an isochronous transmission buffer in the MD8412B, and sends out a PHY interface packet through formatting into each packet format defined by IEEE P1394. If the cycle master bit is "1" and the node using the MD8412B is a route, then a cycle start packet is also sent out to indicate the head of the isochronous cycle.

#### 1-4-4 Receiver

The receiver receives a packet from the PHY interface and identifies if this packet is the one to be acquired by the node of MD8412B. If it is found as an asynchronous packet, it is identified with a node address of MD8412B. If it is an isochronous packet, it is identified with a preset channel number. If a packet is headed to this node, routing is effected toward the asynchronous reception buffer or the isochronous reception buffer by writing the data therein. For a broadcast packet and the snoop mode, no judgment is effected and data are written in their buffer.

#### 1-4-5 Built-in buffer

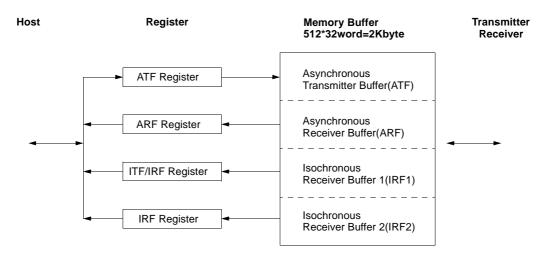

The MD8412B incorporates a buffer in 512 32(bit) configuration with a capacity of 2K-byte in total. This is a temporary buffer intended for data rate absorption between transmitter and host bus. The host performs data access to this buffer.

The MD8412B controls this buffer by dividing it into a maximum of 4 areas. Two of the divided areas are used at random for asynchronous transmission and reception. The remaining two areas depend on isochronous modal setting. Each buffer size is designated at the register. Status information, such as full or empty in the buffer, can be known at the host in the divided unit.

#### 1-4-6 Isochronous transfer functions

The MD8412B possesses isochronous functions. It incorporates a cycle timer so that a cycle start packet can be transmitted in the unit of 125\(\text{a}\)iec when the node seizing the MD8412B is of the cycle master. Its trigger is an 8KHz signal entered through the CYCLEIN pin, obtained as a result of generation of a clock signal of 49.152MHz, coming from the PHY chip.

When the above-mentioned node is not of the cycle master, synchronism with the cycle master is secured through compensation of the cycle master within the MD8412B, based on the value of that packet, each time a cycle start packet is received from another cycle master node.

The MD8412B is provided with two types of isochronous modes. One is a mode intended to gain access to the host with a packet image. The other is a mode for host access with an image of data themselves. (To be described in detail later)

The user determines the mode, according to the nature of data source to be handled in the isochronous transfer mode.

# 2 Terminal Description

# 2-1 Functional description for terminals

| Signal         | Туре | Pin                                                                                    | No. of<br>Pin |                                                                                                                                                                                       |                                                  | Contents                                 | ;                                                                       |         |  |

|----------------|------|----------------------------------------------------------------------------------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|------------------------------------------|-------------------------------------------------------------------------|---------|--|

| PHY Interface  |      |                                                                                        |               | •                                                                                                                                                                                     |                                                  |                                          |                                                                         |         |  |

| SCLK           | I    | 72                                                                                     | 1             | MD841<br>to this s                                                                                                                                                                    | 2B employs this o                                | clock as a master<br>PHY chip.           | fed from the PHY chip. T<br>r clock signal. Usually cor                 | nnected |  |

| LREQ           | 0    | 74                                                                                     | 1             | register<br>connec                                                                                                                                                                    | r access in the Plated to this signal            | HY chip and whe pin of the PHY c         |                                                                         | ally    |  |

| CTL(1:0)       | I/O  | 69, 70                                                                                 | 2             | reception<br>PHY ch                                                                                                                                                                   | on with the PHY only.                            | chip. Usually con                        | ignal for data transmission<br>Inected to this signal pin               | of the  |  |

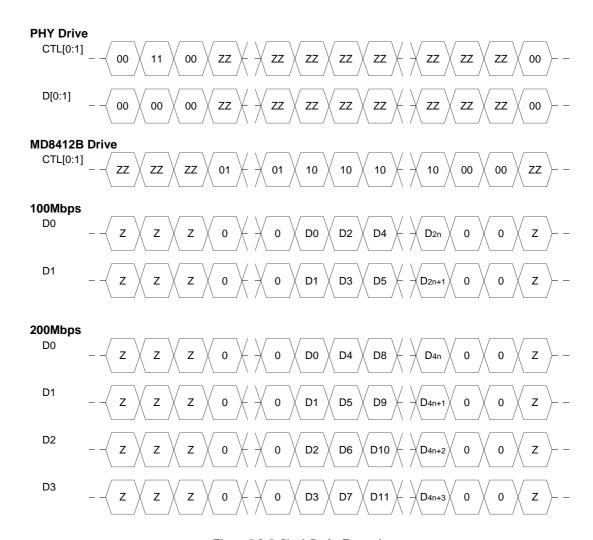

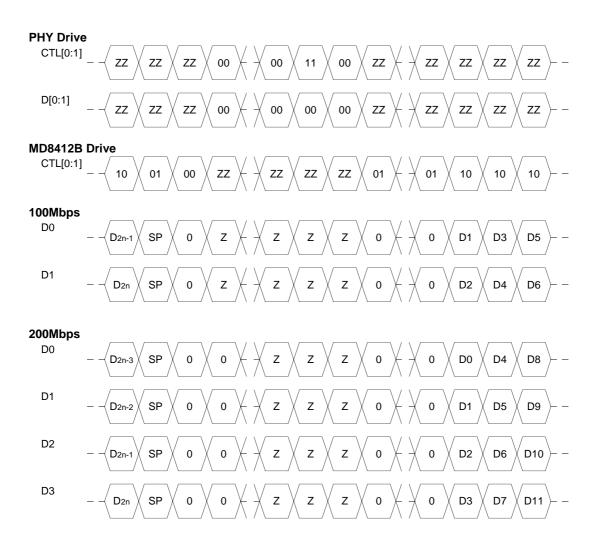

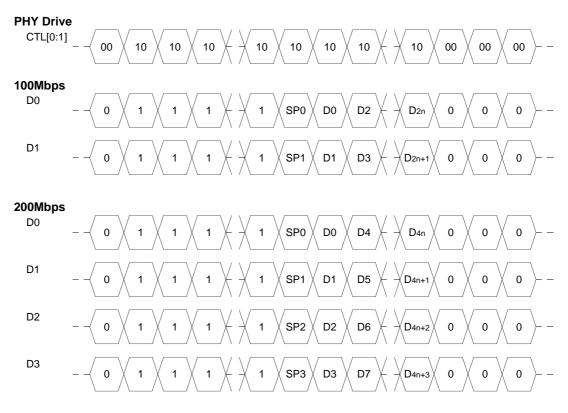

| D(7:0)         | I/O  | 57, 58, 60, 61,<br>63, 64, 66, 67                                                      | 8             | PHY ch<br>D(3:0) i                                                                                                                                                                    | nip. D(1:0) is used<br>is used at 200Mb          | d for packet trans<br>ps, and all bits a | transmission/reception was mission/reception at 100 re used at 400Mbps. | )Mbps,  |  |

| LPS            | 0    | 75                                                                                     |               | Link Status: A LPS signal to PHY. Output in the following combinat available by register setting.  DIRECT Input                                                                       |                                                  |                                          |                                                                         |         |  |

| Host Interface |      |                                                                                        |               |                                                                                                                                                                                       |                                                  |                                          |                                                                         |         |  |

| HA(6:0)        | I    | 92, 93, 95, 96,<br>97, 99, 100                                                         | 7             | Host ac                                                                                                                                                                               | ddress: A host ad                                | dress for registe                        | r selection                                                             |         |  |

| HD(31:0)       | I/O  | 1, 2, 4~6,<br>8~10, 12~14,<br>16~18, 20~22,<br>24~26, 28~30,<br>32~34, 36~38,<br>40~42 | 32            | Host data bus: A data bus for register data access. In combination with other signals, effective bit width is changeable among 31, 16, and 8 bits. Combinations will described later. |                                                  |                                          |                                                                         |         |  |

| WR#            | I    | 89                                                                                     | 1             | Write enable: A writing signal for host data bus.                                                                                                                                     |                                                  |                                          |                                                                         |         |  |

| RD#            | I    | 88                                                                                     | 1             | Read e                                                                                                                                                                                | Read enable: A reading signal for host data bus. |                                          |                                                                         |         |  |

| CS#            | I    | 91                                                                                     | 1             | Chip Se                                                                                                                                                                               | elect: chip selecti                              | on signal for hos                        | t data bus                                                              |         |  |

Table 2-1-1 MD8412B Terminal Table (1)

| Signal                                                              | Туре         | Pin                                         | No. of<br>Pin | Contents                                                                                                                                                                                                                    |  |

|---------------------------------------------------------------------|--------------|---------------------------------------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| UWE#                                                                | I            | 87                                          | 1             | Upper write enable: An enable signal of the upper word (16-bit) for a 32-bit data bus. With active low of this signal, the upper 16-bit is also asserted on the data bus.                                                   |  |

| UBE#                                                                | I            | 85                                          | 1             | Upper byte enable: An enable signal of the upper byte in 16-bit of the upper/lower word for a 32-bit data bus. With active low of this signal, the upper 8-bit is also asserted in the upper and lower words, respectively. |  |

| DREQ                                                                | 0            | 83                                          | 1             | Data request: A request signal for DMA transfer. Asserted only for packet and data transfer.                                                                                                                                |  |

| DACK#                                                               | I            | 84                                          | 1             | Data acknowledge: An acknowledge signal for DMA transfer. Asserted only for packet and data transfer.                                                                                                                       |  |

| INT#                                                                | 0            | 81                                          | 1             | Interrupt signal: An interrupt signal for announcement to the host. This signal is asserted when any factor arises in the interrupt register.                                                                               |  |

| RESET#                                                              | I            | 80                                          | 1             | Reset: A system reset signal of the MD8412B.                                                                                                                                                                                |  |

| Others                                                              |              |                                             |               |                                                                                                                                                                                                                             |  |

| CYCLEIN                                                             | CYCLEIN I 77 |                                             |               | Isochronous cycle input: An external clock for counting the internal cycle timer in 8KHz unit. When CycleSource bit is "1" in the control register, this clock becomes valid.                                               |  |

| CYCLEOUT                                                            | 0            | 78                                          | 1             | Isochronous cycle output: A cycle clock output generated by counting the internal cycle timer of the MD8412B.                                                                                                               |  |

| ITSTART                                                             | I            | 44                                          | 1             | Isochronous Transmission Start Signal in ITSTART auto-Mode.                                                                                                                                                                 |  |

| DIRECT                                                              | I            | 55                                          | 1             | PHY I / F direct select signal: A changeover signal used to select direct isolation connection of I / F with PHY.  0: Isolation connection  1: Direct connection                                                            |  |

| Test Terminals                                                      | I            |                                             |               |                                                                                                                                                                                                                             |  |

| INP(2:0)                                                            | I            | 45, 51, 52                                  | 1             | A signal for testing. In general, INP (2:0) is to be connected to the VSS.                                                                                                                                                  |  |

| TESTEN                                                              | I            | 46                                          | 1             | A signal for testing. In general, TESTEN is to be connected to the VSS.                                                                                                                                                     |  |

| TLINK                                                               | I            | 47                                          | 1             | A signal for testing. In general, TLINK is to be connected to the VSS.                                                                                                                                                      |  |

| TLINKSEP                                                            | I            | 49                                          | 1             | A signal for testing. In general, TLINKSEP is to be connected to the VSS.                                                                                                                                                   |  |

| TRFUL                                                               | I            | 50                                          | 1             | A signal for testing. In general, TRFUL is to be connected to the VSS.                                                                                                                                                      |  |

| TEST(1:0)                                                           | I            | 53, 54                                      | 1             | A signal for testing. In general, TEST(1:0) is to be connected to the VSS.                                                                                                                                                  |  |

| Po                                                                  | wer sup      | ply                                         |               |                                                                                                                                                                                                                             |  |

| VDD                                                                 | I            | 7, 19, 31, 39,<br>56, 62, 68, 79,<br>86, 94 | 7             | 3.3V power supply.                                                                                                                                                                                                          |  |

| VSS I 3, 11, 15, 23, 27, 35, 43, 48, 59, 65, 71, 73, 76, 82, 90, 98 |              | 32                                          | GND           |                                                                                                                                                                                                                             |  |

Table 2-1-2 MD8412B Terminal Table (2)

# 3 Control Register

# 3-1 Method of register access

For 32-bit access, each register gains a description of header address only. Accordingly, the following addresses are used for 8- and 16-bit.

The read-only register should be used for the read-out operation only. The writing operation should not be performed at that time. If this operation is actually attempted, the result from such an operation is not assured.

|             | 7            | 6  | 5  | 4    | 3      | 2  | 1  | 0  |  |  |

|-------------|--------------|----|----|------|--------|----|----|----|--|--|

| Index<br>+3 | BYTE(adrs+3) |    |    |      |        |    |    |    |  |  |

|             | 15           | 14 | 13 | 12   | 11     | 10 | 9  | 8  |  |  |

| Index<br>+2 | BYTE(adrs+2) |    |    |      |        |    |    |    |  |  |

|             | 23           | 22 | 21 | 20   | 19     | 18 | 17 | 16 |  |  |

| Index<br>+1 | BYTE(adrs+1) |    |    |      |        |    |    |    |  |  |

|             | 31           | 30 | 29 | 28   | 27     | 26 | 25 | 24 |  |  |

| Index       |              |    |    | BYTE | (adrs) |    |    |    |  |  |

Figure 3-1-1 Register Address on 8-Bit Bus

|             | 7              | 6  | 5  | 4     | 3        | 2  | 1  | 0  |  |  |  |

|-------------|----------------|----|----|-------|----------|----|----|----|--|--|--|

| Index<br>+2 | WORD-L(adrs+2) |    |    |       |          |    |    |    |  |  |  |

|             | 15             | 14 | 13 | 12    | 11       | 10 | 9  | 8  |  |  |  |

|             | WORD-H(adrs+2) |    |    |       |          |    |    |    |  |  |  |

|             | 23             | 22 | 21 | 20    | 19       | 18 | 17 | 16 |  |  |  |

| Index       |                |    |    | WORD- | ·L(adrs) |    |    |    |  |  |  |

|             | 31             | 30 | 29 | 28    | 27       | 26 | 25 | 24 |  |  |  |

|             |                |    |    | WORD- | H(adrs)  |    |    |    |  |  |  |

Figure 3-1-2 Register Address on 16-Bit Bus

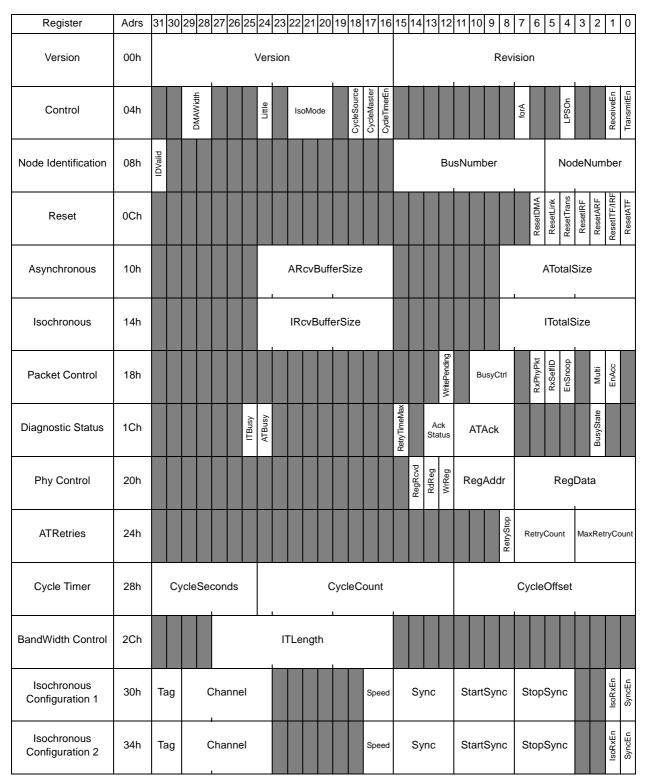

# 3-2 Contents of register

# 3-2-1 Version Register

Index 00h

Initial value 0001 0002h

This register provides chip version and revision number. It is effective in software for IEEE 1394-LINK chip control in the future.

| 7  | 6        | 5  | 4    | 3    | 2  | 1  | 0  |  |  |  |

|----|----------|----|------|------|----|----|----|--|--|--|

|    | Revision |    |      |      |    |    |    |  |  |  |

| 15 | 14       | 13 | 12   | 11   | 10 | 9  | 8  |  |  |  |

|    | Revision |    |      |      |    |    |    |  |  |  |

| 23 | 22       | 21 | 20   | 19   | 18 | 17 | 16 |  |  |  |

|    |          |    | Vers | sion |    |    |    |  |  |  |

| 31 | 30       | 29 | 28   | 27   | 26 | 25 | 24 |  |  |  |

|    | Version  |    |      |      |    |    |    |  |  |  |

#### Bit 15~0 Revision: Revision number of IC chip (R-initial value: 0002h)

Indicates the revision number of MD8412B. This figure begins with "0" and increases each time revision is made.

#### Bit 31~16 version: Version number of IC chip (R-initial value: 0001h)

Indicates the version number of MD8412B. "0001h" is always read out of the MD8412B.

### 3-2-2 Control Register

Index 04h

Initial value 0003 0001h

This register makes settings for each operational configuration of the chip, enable, etc. Generally, this register setting is made shortly after the closure of the POWER switch. The MD8412B configuration should have been defined in advance.

| 7        | 6  | 5       | 4     | 3  | 2           | 1           | 0            |

|----------|----|---------|-------|----|-------------|-------------|--------------|

| PHYIFRST |    |         | LPSON |    |             | ReceiveEn   | TransmitEn   |

| 15       | 14 | 13      | 12    | 11 | 10          | 9           | 8            |

|          |    |         |       |    |             |             |              |

| 23       | 22 | 21      | 20    | 19 | 18          | 17          | 16           |

|          |    | IsoMode |       |    | CycleSource | CycleMaster | CycleTimerEn |

| 31       | 30 | 29      | 28    | 27 | 26          | 25          | 24           |

|          |    | DMA     | Width |    |             |             | Little       |

#### Bit 0 TransmitEn: Transmit Enable bit (RW- Initial value: 1b)

- 0 = Transmitter disabled

- 1 = Transmitter enabled

Setting is made to decide if the MD8412B transmitter is enabled or not. In the case of enable, the following transmission is performed:

- Asynchronous packet

- Cycle start packet with a cycle master bit enabled

- Isochronous packet for cycle start

This bit is automatically set at "1" when a request for bus reset is received from the PHY chip.

#### Bit 1 Receive Enable bit (RW- Initial value: 0b)

- 0 = Receiver disabled

- 1 = Receiver enabled

Setting is made to decide if the MD8412B receiver is enabled or not. In the case of enable, the following reception is performed:

- Synchronous packet addressed from another node to this node

- Isochronous packet of the designated channel

- Reception in snoop mode

## Bit 4 LPSOn: Ink power status on bit (RW- initial value: 0b)

This bit is used to control the LPS signal supplied to the PHY chip. According to the status of the DIRECT terminal, contents of output are different.

| DIRECT | LPSOn | LPS output                             |

|--------|-------|----------------------------------------|

| 1      | 0     | 0                                      |

| 1      | 1     | 1                                      |

| 0      | 0     | 0                                      |

| 0      | 1     | Approx. 0.6 to 3.6MHz clock (Duty 33%) |

#### Bit 7 PhylFRST: PHY-LINK I/F Reset bit (RW- Initial value: 0b)

Selection is made to determine whether the initialization of PHY-LINK I/F is performed at the time of default or at the timing defined by P1394a.

- 0 = Selection is performed at the timing of Default.

- 1 = Selection is performed at the timing defined by P1394a.

#### Bit 16 CycleTimerEn: Cycle Timer Enable bit (RW- Initial value: 1b)

- 0 = Cycle timer disabled

- 1 = Cycle timer enabled

Setting is made to decide if the MD8412B cycle timer is enabled or not.

# Bit 17 Cycle Master: Cycle Master bit (RW- Initial value: 1b)

- 0 = Receiving a cycle start packet from a node in another route, cycle timer control is effected. To be set at "1" when this node cannot belong to an ordinary route.

- 1 = When this bit is "1" cycle start packet is generated each time the MD8412B cycle timer carries.

#### Bit 18 CycleSource: Cycle Source bit (RW- Initial value: 0b)

- 0 = The cycle timer is counted with 24.576MHz of the master clock that is a clock signal fed from the PHY chip, in order to control the isochronous cycle.

- 1 = The cycle timer is updated at the rising point of a signal entered from the CYCLEIN terminal.

The updating source is set up for the internal timer that is in charge of isochronous time control.

#### Bit 22~20 IsoMode: Isochronous Mode bit (RW- Initial value: 000b)

| Isochronous Mode | Transmission | Reception |  |

|------------------|--------------|-----------|--|

| 000              | Normal       | Normal    |  |

| 001              | Normal       | Auto      |  |

| 010              | Auto         | Normal    |  |

| 011              | -            | Auto      |  |

| 100              | Auto         | Auto      |  |

| 101              | -            | Normal    |  |

| 1xx              | Reserved     |           |  |

Settings of normal mode and auto-mode are made for both isochronous transmission and reception. The number of corresponding isochronous channels is as specified below, according to the mode of transmission or reception:

| Transmission in normal mode | No. of channels for packets where buffer areas are not full for each isochronous cycle. For each cycle, however, the number of packets for each channel is limited to 1.                                |

|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Transmission in auto-mode   | Limited to 1 channel. A normal mode is used if more channels are needed to support.                                                                                                                     |

| Reception in normal mode    | For "101", packets for maximum of 4 channels can be received. For "010", however, the number of channels is limited to 3. Setting for channel designation is made at the IsoConfigReg.                  |

| Reception in auto-mode      | Limited to 1 channel. Only for "011", however, 2-channel reception is possible. In this case, routing is effected on the buffer for each channel. (At that time, Isochronous transmission is disabled.) |

# Bit 24 Little: Little-endian bit (RW- Initial value: 0b)

- 0 = Data of ATF, ARF, ITF, IRF buffer are handled as a Big-endian.

- 1 = Data of ATF, ARF, ITF, IRF buffer are handled as a Little-endian.

#### Bit 29~28 DMAWidth: DMA Transfer Data Width bit (RW- Initial value: 00b)

00 = 8-bit (Byte) transfer

01 = 16-bit (Word) transfer

10 = 32-bit (Quadlet) transfer

11 = Reservation

# 3-2-3 Node Identification Register

Index 08h

Initial value 0000 FFFFh

| 7       | 6           | 5          | 4  | 3  | 2  | 1  | 0  |  |

|---------|-------------|------------|----|----|----|----|----|--|

| BusNu   | mber-L      | NodeNumber |    |    |    |    |    |  |

| 15      | 14          | 13         | 12 | 11 | 10 | 9  | 8  |  |

|         | BusNumber-H |            |    |    |    |    |    |  |

| 23      | 22          | 21         | 20 | 19 | 18 | 17 | 16 |  |

|         |             |            |    |    |    |    |    |  |

| 31      | 30          | 29         | 28 | 27 | 26 | 25 | 24 |  |

| IDValid |             |            |    |    |    |    |    |  |

# Bit 5~0 NodeNumber: Node Number bit (RW- Initial value: 3Fh)

This value is used to set up a 6-bit node number to be defined in the IEEE1212 space. During transmission, this value is used in the source area of the IEEE P1394 packet format header. When receiving a packet, the destination node number of this packet is examined and when found to coincide with this value, the packet is received. It is rejected in otherwise case.

Usually, the node number is read from the PHY chip and setting is made at this register after the completion of bus reset and end of self-identification phase.

#### Bit 15~6 BusNumber: Bus Number bit (RW- Initial value: 3FFh)

This value is used to set up a 10-bit bus number to be defined in the IEEE1212 space. During transmission, this value is used in the source area of the header area in the IEEE P1394 packet format header. During reception, this BusNumber bit is disregarded.

#### Bit 31 IDValid: ID Valid bit (RW- Initial value: 00b)

- Only the packet (broadcast packet) is received, where the value of NodeNumber is addressed as "3Fh" In other cases, the packet is rejected.

- 1 = Only the packet is received, for which the value of NodeNumber is addressed in the IEEE1212 address space set by the above-mentioned register. A broadcast packet is also received.

When the state of bus reset arises, this register is automatically cleared to "0" The node number is generally determined after the completion of bus reset and end of self-identification phase. Accordingly, this value is set up after the host has set it in the NodeNumber register.

## 3-2-4 Reset Register

Index 0Ch

Initial value 0000 0000h

| 7  | 6        | 5         | 4       | 3        | 2        | 1            | 0        |

|----|----------|-----------|---------|----------|----------|--------------|----------|

|    | ResetDMA | ResetLink | ResetTx | ResetIRF | ResetARF | ResetITF/IRF | ResetATF |

| 15 | 14       | 13        | 12      | 11       | 10       | 9            | 8        |

|    |          |           |         |          |          |              |          |

| 23 | 22       | 21        | 20      | 19       | 18       | 17           | 16       |

|    |          |           |         |          |          |              |          |

| 31 | 30       | 29        | 28      | 27       | 26       | 25           | 24       |

|    |          |           |         |          |          |              |          |

#### Bit 0 ResetATF: Reset ATF bit: (RW- Initial value: 0b)

0 = Normal condition

1 = Buffer area initialized for asynchronous transmission

Only the buffer area for asynchronous transmission is returned to initial state. At that time, however, all data in that area are lost. All status flags of this buffer are also returned to their initial state.

When "1" is set, and when internal initialization is completed later, this bit is automatically set at "0".

#### Bit 1 ResetITF/IRF: Reset ITF/IRF bit (RW- Initial value: 0b)

0 = Normal condition

1 = Buffer area initialized for isochronous transmission/reception

When IsoMode setting is for other than "011" isochronous transmission buffer is restored to initial conditions. When it is for "011" mode, only the buffer area is restored to initial conditions for isochronous channel reception designated by isochronous configuration 2,3 register. At that time, however, all data in that area are lost. All status flags of this buffer are also returned to their initial state.

When "1" set, and when internal initialization is completed later, this bit is automatically set at "0".

#### Bit 2 ResetARF: Reset ARF bit (RW- Initial value: 0b)

0 = Normal condition

1 = Buffer area initialized for asynchronous reception

Only the buffer area for asynchronous reception is returned to initial state. At that time, however, all data in that area are lost. All status flags of this buffer are also returned to their initial state.

When "1" is set, and when internal initialization is completed later, this bit is automatically set at "0".

#### Bit 3 ResetIRF: Reset IRF bit (RW- Initial value: 0b)

0 = Normal condition

1 = Buffer area initialized for isochronous reception

Only the buffer area for isochronous channel reception specified by the isochronous configuration register is returned to initial state. At that time, however, all data in that area are lost. All status flags of this buffer are also returned to their initial state.

When "1" set, and when internal initialization is completed later, this bit is automatically set at "0".

#### Bit 4 ResetTx: Reset Transmitter bit (RW- Initial value: 0b)

0 = Normal condition

1 = Transmitter being reset

Transmitter is reset to set up a transmission-enabled condition. If a packet is being transmitted, that transmission is supported. When "1" set, and when internal initialization is completed later, this bit is automatically set at "0".

#### Bit 5 ResetLink: Reset Link Core bit (RW- Initial value: 0b)

0 = Normal condition

1 = Link core being reset

Link Core is reset to support all operation. When "1" set, and when internal initialization is completed later, this bit is automatically set at "0".

#### Bit 6 Reset DMA: Reset DMA bit (RW- Initial value: 0b)

0 = Normal condition

1 = DMA control being reset

DMA control is reset to set up a condition enabling DMA transfer. DMA is required to complete transfer in the Quadlet unit. The DMA transfer pointer in the Quadlet unit is cleared with this bit and the pointer is set in the header position in the Quadlet unit. When "1" is set, and when internal initialization is completed later, this bit is automatically set at "0".

## 3-2-5 Asyncronous Buffer Size Set Register

Index 10h

Initial value 007F 00FFh

In this register, an assignment size is specified to assign an asynchronous area to the internal buffer having a 2KB capacity. This size is specified in the Quadlet unit. Max configuration size is 511Quadlet.

| 7  | 6          | 5  | 4     | 3        | 2  | 1  | 0             |  |  |

|----|------------|----|-------|----------|----|----|---------------|--|--|

|    | ATotalSize |    |       |          |    |    |               |  |  |

| 15 | 14         | 13 | 12    | 11       | 10 | 9  | 8             |  |  |

|    |            |    |       |          |    |    | ATotalSize    |  |  |

| 23 | 22         | 21 | 20    | 19       | 18 | 17 | 16            |  |  |

|    |            |    | ARxBu | fferSize |    |    |               |  |  |

| 31 | 30         | 29 | 28    | 27       | 26 | 25 | 24            |  |  |

|    |            |    |       |          |    |    | ARxBufferSize |  |  |

### Bit 8~0 ATotalSize: Asynchronous Total Buffer bit (RW- Initial value: 0FFh)

All buffer sizes for asynchronous transmission and reception are specified in the Quadlet unit. All data (iso-chronous also) remaining in the buffer before modification are abandoned.

#### Bit 24~16 ARxBufferSize: Asynchronous Receive Buffer Size bit (RW- Initial value: 07Fh)

Buffer size for asynchronous reception is specified in the Quadlet unit. In this case, this value must always be smaller than the one set by TotalSize. And configuration beyond 5Quadlet. If this value is changed, all data remaining in the asynchronous transmission/reception buffer are abandoned. There is no influence in the isochronous domain.

By the above-mentioned two setting values, the transmission buffer size is defined as:

ATansmitBufferSize = ATotalSize - ARxBufferSize

## 3-2-6 Isochronous Buffer Size Set Register

Index 14h

Initial value 007F 00FFh

| 7  | 6             | 5  | 4  | 3  | 2  | 1  | 0             |  |  |

|----|---------------|----|----|----|----|----|---------------|--|--|

|    | lTotalSize    |    |    |    |    |    |               |  |  |

| 15 | 14            | 13 | 12 | 11 | 10 | 9  | 8             |  |  |

|    |               |    |    |    |    |    | lTotalSize    |  |  |

| 23 | 22            | 21 | 20 | 19 | 18 | 17 | 16            |  |  |

|    | IRxBufferSize |    |    |    |    |    |               |  |  |

| 31 | 30            | 29 | 28 | 27 | 26 | 25 | 24            |  |  |

|    |               |    |    |    |    |    | IRxBufferSize |  |  |

In this register, an assignment size is specified to assign an isochronous area to the internal buffer having a 2KB capacity. This size is specified in the Quadlet unit. Max configuration size is 511Quadlet.

#### Bit 8~0 ITotalSize: Isochronous Total Buffer bit (RW- Initial value: 0FFh)

All buffer sizes for isochronous transmission and reception are specified in the Quadlet unit. When IsoMode is "011" however, transmission buffer is lost and setting is made in the receiving buffer for two channels.

#### Bit 24~16 IRxBufferSize: Isochronous Receive Buffer Size bit (RW- Initial value: 07Fh)

Buffer size for isochronous reception is specified in the Quadlet unit. In this case, this value must always be smaller than the one set by TotalSize. If this value is changed, all data remaining in the isochronous transmission/reception buffer are abandoned.

If IsoMode is not "011" the transmission buffer size is defined as follows by the above-mentioned two setting values:

ITansmitBufferSize = ITotalSize - IRxBufferSize

When IsoMode is "011b" contents of the Isochronous Configuration 3 register are stored in the buffer being set by the IRxBufferSize, and contents of the Isochronous Configuration 2 register are stored in the buffer being set by the ITransmitBufferSize.

When IsoMode is "101b" ITotalSize and IRxBufferSize must be set at the same value.

# 3-2-7 Packet Control Register

Index 18h

Initial value 0000 1020h

| 7  | 6        | 5        | 4            | 3  | 2     | 1        | 0  |

|----|----------|----------|--------------|----|-------|----------|----|

|    | RxPhyPkt | RxSelfID | EnSnoop      |    | Multi | EnAcc    |    |

| 15 | 14       | 13       | 12           | 11 | 10    | 9        | 8  |

|    |          |          | WritePending |    |       | BusyCtrl |    |

| 23 | 22       | 21       | 20           | 19 | 18    | 17       | 16 |

|    |          |          |              |    |       |          |    |

| 31 | 30       | 29       | 28           | 27 | 26    | 25       | 24 |

|    |          |          |              |    |       |          |    |

#### Bit 1 EnAcc: Ack Acceleration On bit (RW- Initial value: 0b)

- 0 = Transmission of an asynchronous packet by AckAcceleration is disabled.

- 1 = Transmission of an asynchronous packet by AckAcceleration is enabled.

Setting is made to determine whether the transmission of an asynchronous packet by AckAcceleration is enabled or not.

IsoMode becomes effective only when "000b", "001b", "011b", "101b" are set up.

#### Bit 2 Multi: Multi Speed Concatination On bit (RW- Initial value: 0b)

- 0 = Multi-speed concatenation transmission of isochronous packet is disabled.

- 1 = Multi-speed concatenation transmission of isochronous packet is enabled.

Setting is made to determine whether the multi-speed concatenation transmission of isochronous packet is enabled or not.

Transmission of multi-speed concatenation is valid at the time of IsoMode transmission in normal mode. In the auto-mode transmission, no function of multi-speed concatenation is supported.

Even when the reversal data for a PHY control packet are different, this PHY control packet is not stored in the ARF buffer.

# Bit 4 EnSnoop: Enable Snoop bit (RW- Initial value: 0b)

- 0 = Normally, only the packet mapped in this node address is received.

- 1 = Snoop mode assumed.

Regardless of the node address assumed, a snoop mode is set up so that all packets carried on the serial bus, can be received. When a packet is received, the Ack code is not returned. All packets received in this mode are stored in the IRF buffer.

#### Bit 5 RxSelfID: Receive Self ID bit (RW- Initial value: 1b)

- 0 = No SelfID packet is inserted in the buffer.

- 1 = SelfID packet is input in the buffer.

This bit makes setting to decide whether the SelfID packet received in the Self ID phase after bus reset should be put in the buffer area for reception Async.

#### Bit6 RxPhyPkt: Receive Phy Packet bit (RW -initial value: 0b)

- 0 = Phy Packet isn't stored in the buffer.

- 1 = Phy Packet is stored in the buffer.

It is configured by this bit whether it isn't put if received PHY control packet is put in the buffer area for the reception.

When the PHY received PingPacket has more than 4 port, that SelfID Packet isn't stored in the ARF buffer.

And, that PHY Control Packet isn't stored in the ARF buffer when the invert data of the PHY Control Packet is different.

#### Bit 10~8 BusyCtrl: Busy Control bit (RW- Initial value: 000b)

- 000 = A Busy Acknowledge is returned according to the dual phase retry protocol only if there is no vacancy of one packet to be received at the internal Async reception buffer.

- 001 = An Acknowledge is returned in BusyA status only if there is no vacancy of one packet to be received at the internal Async reception buffer.

- 010 = An Acknowledge is returned in BusyB status only if there is no vacancy of one packet to be received at the internal Async reception buffer.

- 011 = An Acknowledge is returned in BusyX status only if there is no vacancy of one packet to be received at the internal Async reception buffer.

- 100 = A Busy Acknowledge is returned according to the dual phase retry protocol irrespective of whether there is vacancy of one packet to be received at the internal Async reception buffer.

- 101 = An Acknowledge is returned in BusyA status for all packets received irrespective of whether there is vacancy of one packet to be received at the internal Async reception buffer.

- 110 = An Acknowledge is returned in BusyB status for all packets received irrespective of whether there is vacancy of one packet to be received at the internal Async reception buffer.

- 111 = An Acknowledge is returned in BusyX status for all packets received irrespective of whether there is vacancy of one packet to be received at the internal Async reception buffer.

When the MD8412B node is of inbound and a busy status acknowledge is returned for the packet from the outbound node transmitted to MD8412B, contents of that status are set in this register.

#### Bit 12 WritePending: Write Request Ack-Pending bit (RW- Initial value: 1b)

- 0 = Ack-Complete is returned when reception is normal with Ack code for Write Request packet.

- 1 = Ack-Pending is returned when reception is normal with Ack code for Write Request packet.

When a Write Request packet is normally received, the Ack code generally returns Ack-Complete. If the packet cannot be received normally, due to lack of buffer capacity or the like, Ack-Busy is returned. When this bit is set at "1" the Ack code returns Ack-Pending under the condition that reception is normal. In other words, Split Transaction of Write Request is to be executed. Upon completion of Write Request processing, the host is required to transmit a Write Response packet. The table below shows types of Ack codes to be sent back for each packet. Items mark by O are Ack codes.

| Packet         | Wi           | ritePending = '0b'   |   | WritePending = '1b' |             |          |  |

|----------------|--------------|----------------------|---|---------------------|-------------|----------|--|

| racket         | ack_complete | ack_pending ack_busy |   | ack_complete        | ack_pending | ack_busy |  |

| Write Request  | 0            | -                    | 0 | -                   | 0           | 0        |  |

| Read Request   | -            | 0                    | 0 | -                   | 0           | 0        |  |

| Write Response | 0            | -                    | 0 | 0                   | -           | 0        |  |

| Read Response  | 0            | -                    | 0 | 0                   | -           | 0        |  |

| Lock Request   | -            | 0                    | 0 | -                   | 0           | 0        |  |

| Lock Response  | 0            | -                    | 0 | 0                   | -           | 0        |  |

# 3-2-8 Diagnostic Status Register

Index 1Ch

Initial value 0000 0000h (Read-only register)

It is possible to know various status information in this register.

| 7            | 6  | 5    | 4     | 3     | 2         | 1      | 0      |  |

|--------------|----|------|-------|-------|-----------|--------|--------|--|

|              |    |      |       |       | BusyState |        |        |  |

| 15           | 14 | 13   | 12    | 11    | 10        | 9      | 8      |  |

| RetryTimeMax |    | AckS | tatus | ATAck |           |        |        |  |

| 23           | 22 | 21   | 20    | 19    | 18        | 17     | 16     |  |

|              |    |      |       |       |           |        |        |  |

| 31           | 30 | 29   | 28    | 27    | 26        | 25     | 24     |  |

|              |    |      |       |       |           | ITBusy | ATBusy |  |

# Bit 2 BusyState: Busy State bit (R- Initial value: 0b)

0 = Acknowledge is returned with BusyA

1 = Acknowledge is returned with BusyB

When Busy Acknowledge is to be issued at the next opportunity, this node indicates the type of this Acknowledge.

#### Bit 11~8 ATAck: AT Ack bit (R- Initial value: 0000b)

0000

= No Ack

0001

= ack\_complete

0010

= ack\_pending

0011

= Reserved

0100

= ack\_busy\_X

0101

= ack\_busy\_A

0110 = ack\_busy\_B 0111~1100 = Reserve 1101 = ack\_data\_error 1110 = ack\_type\_error 1111 = Reserve

For the packet sent from the transmitter during transmission, contents of Acknowledge (Ack code) returned from the destination node are reflected in this register. The reflection timing is when a busy flag for showing the packet being processed in the transmitting asynchronous buffer is negated. This value is held until this Busy is negated for the next packet transmission.

#### Bit 13~12 AckStatus: Ack Status bit (R- Initial value: 00b)

00 = Normal reception

01 = Parity error

10 = Packet lost (indicating that no Acknowledge packet has been sent in the specified time)

11 = Reserve

For the transmitted Asynchronous packet, the status of Acknowledge packet returned from the destination node is indicated.

#### Bit 15 RetryTimeMax: Retry Time Max bit (R- Initial value: 0b)

0 = Normal

1 = Max. number of retries

This bit is used to indicate the situation in regard to the maximum number of retries for the retry count setting in the ATRetry register at the beginning of a certain retry phase. Whether the said retry phase has been finished or is still busy at that time can be identified with the ATAck bit. This value is maintained until the next packet transmission is carried out.

#### Bit 24 ATBusy: AT Busy bit (R- Initial value: 0b)

- 0 = Indicates that ATGo issuing is possible.

- 1 = Indicates that ATGo issuing is impossible, and that a packet is presently being processed for the previously issued ATGo.

This bit is asserted upon the issuing of ATGo for Asynchronous transmission. It is negated when return of this Acknowledge has been set in the ATAck register. The host cannot issue the next ATGo while this bit is being asserted. Even though it is attempted, it is disregarded. When a packet transmission turns to be a retry operation, this bit is never negated until the said Retry is finished.

#### Bit 25 ITBusy: IT Busy bit (R- Initial value: 0b)

- 0 = Indicates that ITGo issuing is possible.

- 1 = Indicates that ITGo issuing is impossible, and that a packet is presently being processed for the previously issued ITGo.

For isochronous transmission in normal IsoMode, this bit is asserted with ITGo issued, and negated upon completion of packet transmission. The host cannot issue the next ITGo until this bit is being asserted. Even though it is attempted, it is disregarded.

### 3-2-9 Phy Control Register

Index 20h

Initial value 0000 0000h

Using this register, a register in PHY chip is accessed. When reading a certain register, its register address is set in the RegAddr register and the RdReg bit is made active. With the RdReg bit being active, a read request for the addressed register is made to the PHY chip and the RdReg bit is then cleared. Contents of the addressed register from the PHY chip are entered in the RegData register. The write request to the PHY register for the data in the RegData register is also made by triggering the WrReg bit of the PHY address set in the RegAddr register.

| 7       | 6       | 5     | 4     | 3       | 2  | 1  | 0  |  |  |  |  |

|---------|---------|-------|-------|---------|----|----|----|--|--|--|--|

| RegData |         |       |       |         |    |    |    |  |  |  |  |

| 15      | 14      | 13    | 12    | 11      | 10 | 9  | 8  |  |  |  |  |

|         | RegRcvd | RdReg | WrReg | RegAddr |    |    |    |  |  |  |  |

| 23      | 22      | 21    | 20    | 19      | 18 | 17 | 16 |  |  |  |  |

|         |         |       |       |         |    |    |    |  |  |  |  |

| 31      | 30      | 29    | 28    | 27      | 26 | 25 | 24 |  |  |  |  |

|         |         |       |       |         |    |    |    |  |  |  |  |

# Bit 7~0 RegData: Register Data bit (RW- Initial value: 00h)

With a Write request, data being transferred to PHY are stored. With Read request also, data transferred from PHY are stored. When reading out the contents of this register, contents of RegData are read out, the value taken from PHY with the previous Read request. In other words, the value taken from the host cannot be directly read out. To read out, a Read request must be sent to PHY.

#### Bit 11~8 RegAddr: Register Address bit (RW- Initial value: 00h)

The address value of PHY being accessed is set.

# Bit 12 WrReg: Write Register bit (RW- Initial value: 0b)

- 0 = Normal condition

- 1 = Write request issued

A Write request is issued toward the PHY register. After this Write request, this bit is cleared.

#### **Bit 13** RdReg: Read Register bit (RW- Initial value: 0b)

- 0 = Normal condition

- 1 = Read request issued

A Read request is issued toward the PHY register. After this Read request, this bit is cleared.

#### **Bit 14** RegRcvd: Register Data Received bit (RW- Initial value: 0b)

- 0 = Normal condition

- 1 = Indicating that data from PHY have been stored in RegData after the issuing of Read request

After a Read request has been issued toward the PHY register, "1" set upon the storage of PHY data in Reg-Data. Since then, "1" signal for testing.

cleared to "0" when reading is attempted once from this register.

# 3-2-10 ATRetries Register

Index 24h

Initial value 0000 0001h

There is a function of performing automatic retry when asynchronous packet transmission is attempted by the MD8412B node and Busy Acknowledge is returned from this destination node. The number of retries is set in this register. Once a retry phase is assumed, a busy flag of the ATGo register is never negated until any Acknowledge other than Busy is returned from the destination node or the preset number of retries is attained. In this state, the next packet transmission is disabled.

| 7  | 6           | 5     | 4  | 3             | 2  | 1  | 0         |  |

|----|-------------|-------|----|---------------|----|----|-----------|--|

|    | Retry       | Count |    | MaxRetryCount |    |    |           |  |

| 15 | 15 14 13 12 |       |    | 11            | 10 | 9  | 8         |  |

|    |             |       |    |               |    |    | RetryStop |  |

| 23 | 22          | 21    | 20 | 19            | 18 | 17 | 16        |  |

|    |             |       |    |               |    |    |           |  |

| 31 | 30          | 29    | 28 | 27            | 26 | 25 | 24        |  |

|    |             |       |    |               |    |    |           |  |

### Bit 3~0 MaxRetryCount: Maximum Retry Count bit (RW- Initial value: 01h)

This register sets up the maximum number of retries for Busy Acknowledge from the destination node. If the retry phase is not completed within this set value, a retry time-out status flag is given in the ATAck register to complete the retry phase attempted by the MD8412B. Since then, packet data are flushed within the ATF buffer. The maximum number that can be set is 15. When "0000" is set, the MD8412B does not assume a retry phase automatically. In this case, packet data are flushed for Busy Acknowledge. When an error Acknowledge is returned in the retry phase, retry is suspended at that time point and contents of the buffer are flushed. Further operation is halted by presenting a flag (AckErr).

#### Bit 7~4 RetryCount: Retry Count bit (R- Initial value: 00h)

The number of present retries is indicated in the middle of a retry attempted from MD8412B.

## Bit 8 RetryStop: Retry Stop Bit (RW- Initial value: 0b)

When the MD8412B automatically assumes the retry phase and the limit value is not attained yet during this retry action, this bit is used to perform the forced end of this retry. When this bit is set at "1", it is automatically cleared after the completion of the retry phase.

- 0: Normal condition

- 1: Forced end

# 3-2-11 Cycle Timer Register

Index 28h

Initial value 0000 0000h

The present cycle timer value is indicated. As described below, this register is divided into three areas. When the node employing MD8412B is of CycleMaster and a cycle start packet is being transmitted, this register value is loaded. In otherwise case, the cycle timer value in the received cycle start packet is loaded in this register in order to update the cycle timer. Timing to load is when the Lo byte of CycleOffset has been written.

| 7  | 6                    | 5     | 4  | 3           | 2  | 1 | 0 |  |  |  |  |

|----|----------------------|-------|----|-------------|----|---|---|--|--|--|--|

|    | CycleOffset          |       |    |             |    |   |   |  |  |  |  |

| 15 | 14                   | 13    | 12 | 11          | 10 | 9 | 8 |  |  |  |  |

|    | Cycle                | Count |    | CycleOffset |    |   |   |  |  |  |  |

| 23 | 22 21 20 19 18 17    |       |    |             | 16 |   |   |  |  |  |  |

|    | CycleCount           |       |    |             |    |   |   |  |  |  |  |

| 31 | 31 30 29 28 27 26 25 |       |    |             |    |   |   |  |  |  |  |

|    | CycleSeconds         |       |    |             |    |   |   |  |  |  |  |

# Bit 11~0 CycleOffset: Cycle Offset bit (RW- Initial value: 00h)

This area is used for counting up with a 24.576MHz clock. It is actuated with Modulo3072.

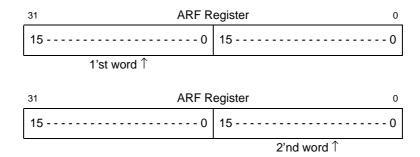

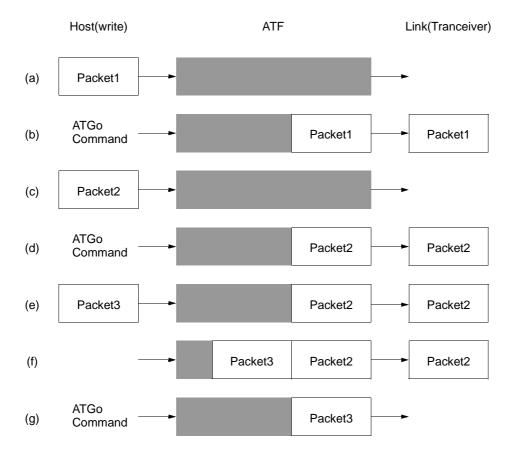

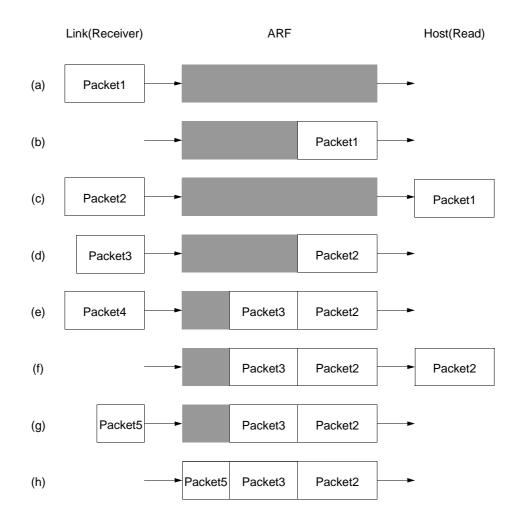

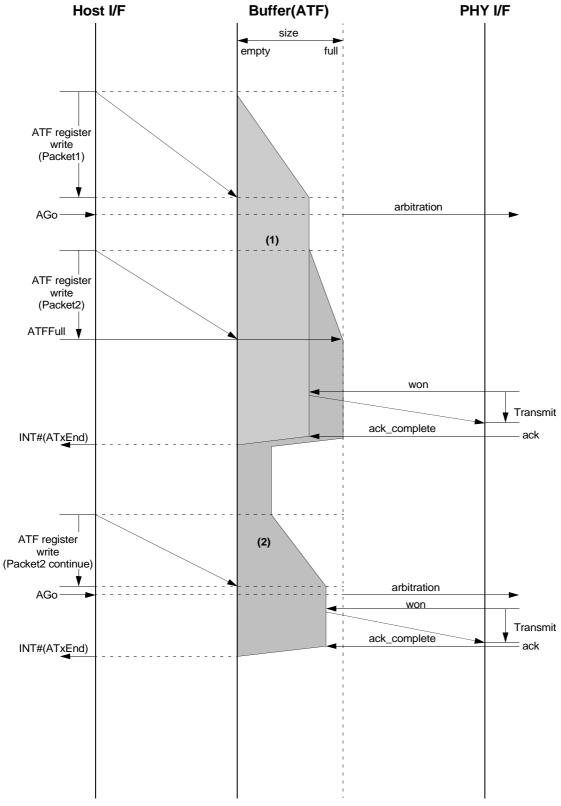

# Bit 24 CycleCount: Cycle Count bit (RW- Initial value: 00h)