4-Bank×4,194,304 -Word×16-Bit SYNCHRONOUS DYNAMIC RAM

# DESCRIPTION

The MD56V82160A-xxTA is a 4-Bank  $\times$  4,194,304-word  $\times$  16-bit Synchronous dynamic RAM. The device operates at 3.3V. The inputs and outputs are LVTTL compatible.

# **FEATURES**

| Product Name            | MD56V82160A-xxTA xx indicates speed rank.        |

|-------------------------|--------------------------------------------------|

| Organization            | 4Bank x 4,194,304Word x 16Bit                    |

| Address Size            | 8,192Row x 512Column                             |

| Power Supply VCC (Core) | 3.3V±0.3V                                        |

| Power Supply VCCQ (I/O) | 3.3V±0.3V                                        |

| Interface               | LVTTL compatible                                 |

| Operating Frequency     | Max. 166MHz (Speed Rank 6)                       |

| Operating Temperature   | 0 to 70°C                                        |

| Function                | Standard SDRAM command interface                 |

| /CAS Latency            | Mode register CL setting: 2, 3                   |

| Burst Length            | Mode register BL setting:1, 2, 4, 8, Full page   |

| Burst Type              | Mode register BT setting: Sequential, Interleave |

| Write Mode              | Mode register WM setting: Burst, Single          |

| Refresh                 | Auto-Refresh, 8,192cycle/64ms, Self-Refresh      |

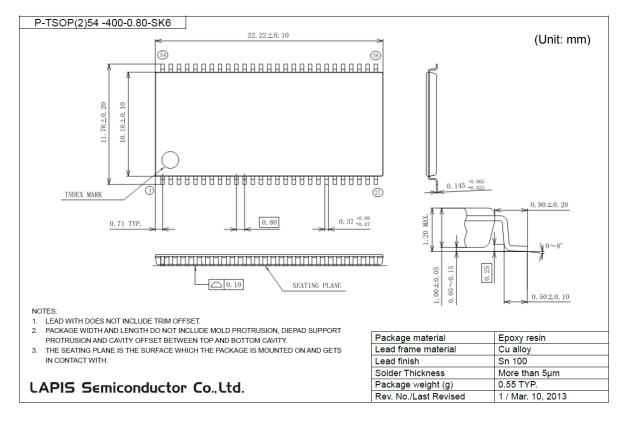

| Package                 | 54 pin 400 mil Plastic TSOP(2)                   |

|                         | Cu Frame, Halogen-Free, Pb-Free                  |

|                         | (P-TSOP(2)54-400-0.80-SK6)                       |

# **PRODUCT FAMILY**

| VCC            | Family            | Output       | Max.      | Access Time (Max.) |       |  |

|----------------|-------------------|--------------|-----------|--------------------|-------|--|

| VCC            | Family            | Drivability  | Frequency | tAC2               | tAC3  |  |

|                | MD56V82160A -6TA  | EMRS setting | 166MHz    | 5.4ns              | 5.4ns |  |

| 2.0)/ to 2.0)/ | MD56V82160A -7TA  | EMRS setting | 143MHz    | 5.4ns              | 5.4ns |  |

| 3.0V to 3.6V   | MD56V82160A -75TA | EMRS setting | 133MHz    | 5.4ns              | 5.4ns |  |

|                | MD56V82160A -10TA | EMRS setting | 100MHz    | 6ns                | 6ns   |  |

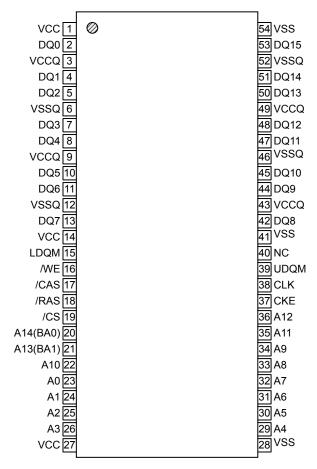

# **PIN CONFIGURATION (TOP VIEW)**

54-Pin Plastic TSOP(II) (K Type)

| Pin Name               | Function              | Pin Name   | Function                        |

|------------------------|-----------------------|------------|---------------------------------|

| CLK                    | System Clock          | UDQM, LDQM | Data Input / Output Mask        |

| /CS                    | Chip Select           | DQi        | Data Input / Output             |

| CKE                    | Clock Enable          | VCC        | Power Supply (3.3V)             |

| A0 to A12              | Address               | VSS        | Ground (0V)                     |

| A13,A14<br>( BA1,BA0 ) | Bank Select Address   | VCCQ       | Data Output Power Supply (3.3V) |

| /RAS                   | Row Address Strobe    | VSSQ       | Data Output Ground (0V)         |

| /CAS                   | Column Address Strobe | NC         | No Connection                   |

| /WE                    | Write Enable          |            |                                 |

Note: The same power supply voltage must be provided to every VCC pin.

The same power supply voltage must be provided to every VCCQ pin.

The same GND voltage level must be provided to every VSS pin and VSSQ pin.

# **PIN DESCRIPTION**

| CLK                  | Clock (Input)<br>Fetches all inputs at the "H" edge.                                                                                                                                                                                                                             |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CKE                  | Clock Enable (Input)<br>Masks system clock to deactivate the subsequent CLK operation.<br>If CKE is deactivated, system clock will be masked so that the subsequent CLK operation is<br>deactivated. CKE should be asserted at least one cycle prior to a new command.           |

| /CS                  | Chip Select (Input)<br>Disables or enables device operation by asserting or deactivating all inputs except CLK, CKE<br>and UDQM, LDQM.                                                                                                                                           |

| /RAS                 | Row Address Strobe (Input)<br>Functionality depends on the combination with other signals. For detail, see the function truth<br>table.                                                                                                                                          |

| /CAS                 | Column Address Strobe (Input)<br>Functionality depends on the combination with other signals. For detail, see the function truth<br>table.                                                                                                                                       |

| /WE                  | Write Enable (Input)<br>Functionality depends on the combination with other signals. For detail, see the function truth<br>table.                                                                                                                                                |

| A13,A14<br>(BA1,BA0) | Bank Address (Input)<br>Slects bank to be activated during row address latch time and selects bank for precharge and read/write during column address latch time.                                                                                                                |

| A0 to A12            | Row & column multiplexed. (Input)<br>Row address : RA0 – RA12<br>Column Address : CA0 – CA8                                                                                                                                                                                      |

| DQ0 to DQ15          | 3-state Data Bus (Input/Output)                                                                                                                                                                                                                                                  |

| UDQM, LDQM           | DQ Mask (Input)<br>Masks the read data of two clocks later when DQM are set "H" at the "H" edge of the clock<br>signal. Masks the write data of the same clock when DQM are set "H" at the "H" edge of the<br>clock signal. UDQM controls DQ15 to DQ8, LDQM controls DQ7 to DQ0. |

| VCC, VSS             | Power Supply (Core), Ground (Core)<br>The same power supply voltage must be provided to every VCC pin.<br>The same GND voltage level must be provided to every VSS pin.                                                                                                          |

| VCCQ, VSSQ           | Power Supply (I/O), Ground (I/O)<br>The same power supply voltage must be provided to every VCCQ pin.<br>The same GND voltage level must be provided to every VSSQ pin.                                                                                                          |

| NC                   | No Connection                                                                                                                                                                                                                                                                    |

# **ELECTRICAL CHARACTERISTICS**

#### **Absolute Maximum Ratings**

| Parameter                                   | Symbol    | Value       | Unit |

|---------------------------------------------|-----------|-------------|------|

| Voltage on Input/Output Pin Relative to VSS | VIN, VOUT | -0.5 to 4.6 | V    |

| VCC Supply Voltage                          | VCC       | -0.5 to 4.6 | V    |

| VCCQ Supply Voltage                         | VCCQ      | -0.5 to 4.6 | V    |

| Power Dissipation (Ta=25°C)                 | PD        | 1000        | mW   |

| Short Circuit Output Current                | IOS       | 50          | mA   |

| Storage Temperature                         | Tstg      | –55 to 150  | °C   |

| Operating Temperature                       | Та        | 0 to 70     | °C   |

Notes: 1. Permanent device damage may occur if Absolute Maximum Ratings are exceeded.

2. Functional operation should be restricted to recommended operating condition.

3. Exposure to higher than recommended voltage for extended periods of time could affect device reliability.

4. The voltages are referenced to VSS.

#### **Recommended Operating Conditions (1/2)**

|                             |           |      |      |      | Ta= 0 | to 70°C |

|-----------------------------|-----------|------|------|------|-------|---------|

| Parameter                   | Symbol    | Min. | Тур. | Max. | Unit  | Note    |

| Power Supply Voltage (Core) | VCC       | 3.0  | 3.3  | 3.6  | V     | 1,2     |

| Power Supply Voltage (I/O)  | VCCQ      | 3.0  | 3.3  | 3.6  | V     | 1,2     |

| Ground                      | VSS, VSSQ | 0    | 0    | 0    | V     |         |

Notes: 1. The voltages are referenced to VSS.

2. The power supply voltages should input stable voltage. The power supply voltages should not input oscillated voltage. If voltages are oscillating, please insert capacitor near the power supply pins and stop oscillation of voltage.

#### **Recommended Operating Conditions (2/2)**

|                    |        |      |           | Ta=  | 0 to 70°C |

|--------------------|--------|------|-----------|------|-----------|

| Parameter          | Symbol | Min. | Max.      | Unit | Note      |

| Input High Voltage | VIH    | 2.0  | VCC + 0.3 | V    | 1, 2      |

| Input Low Voltage  | VIL    | -0.3 | 0.8       | V    | 1, 3      |

Notes: 1. The voltages are referenced to VSS.

2. The input voltage is VCC + 0.5V when the pulse width is less than 20ns (the pulse width is with respect to the point at which VCC is applied).

3. The input voltage is -0.5V when the pulse width is less than 20ns (the pulse width respect to the point at which VSS and VSSQ are applied).

## **Pin Capacitance**

#### Ta = 25°C, VCC=VCCQ=3.3V, f=1MHz Symbol Parameter Min. Max. Unit CCLK Input Capacitance (CLK) 4 pF \_\_\_\_ Input Capacitance CIN 5 pF (A0 to A14, /RAS, /CAS, /WE, /CS, CKE, UDQM, LDQM)

COUT

\_\_\_\_

## **DC Characteristics (Input/Output)**

Input/Output Capacitance (DQ0 to DQ15)

Ta= 0 to 70°C VCC = VCCO = 3 3V+0 3V

pF

6.5

|                        |        |                         |      | VCC = V | $CCQ = 3.3V \pm 0.3V$ |

|------------------------|--------|-------------------------|------|---------|-----------------------|

| Parameter              | Symbol | Condition               | Min. | Max.    | Unit                  |

| Output High Voltage    | VOH    | IOH = -2mA              | 2.4  |         | V                     |

| Output Low Voltage     | VOL    | IOL = 2mA               |      | 0.4     | V                     |

| Input Leakage Current  | ILI    | $0V{\leq}VIN{\leq}VCCQ$ | -10  | 10      | μA                    |

| Output Leakage Current | ILO    |                         | -10  | 10      | μA                    |

Note : The voltages are referenced to VSS.

# DC Characteristics (Power Supply Current)

| $Ta=0 \text{ to } 70^{\circ}0$ $VCC = VCCQ = 3.3V\pm0.3^{\circ}$ |        |                        |                       |                                                              |     |      |      |     |    |      |

|------------------------------------------------------------------|--------|------------------------|-----------------------|--------------------------------------------------------------|-----|------|------|-----|----|------|

|                                                                  |        |                        | Μ                     | D56V82                                                       | A   | Unit | Note |     |    |      |

| Parameter                                                        | Symbol |                        | Condition             |                                                              | -6  | -7   | -75  | -10 |    |      |

|                                                                  |        | Bank CKE Others        |                       | Others                                                       | Max | Max. | Max. | Max |    |      |

| Average Power<br>Supply Current<br>(Operating)                   | ICC1   | One Bank<br>Active     | $CKE \geq V_{IH}$     | t <sub>CC</sub> = Min.<br>t <sub>RC</sub> = Min.<br>No Burst | 150 | 140  | 130  | 110 | mA | 1, 2 |

| Power Supply<br>Current<br>(Standby)                             | ICC2   | All Banks<br>Precharge | CKE ≥ VIH             | t <sub>CC</sub> = Min.                                       | 40  | 40   | 40   | 40  | mA | 3    |

| Average Power<br>Supply Current<br>(Clock<br>Suspension)         | ICC3S  | All Banks<br>Active    | CKE ≤ VIL             | t <sub>CC</sub> = Min.                                       | 35  | 35   | 35   | 35  | mA | 2    |

| Average Power<br>Supply Current<br>(Active Standby)              | ICC3   | One Bank<br>Active     | CKE ≥ VIH             | t <sub>CC</sub> = Min.                                       | 65  | 60   | 55   | 55  | mA | 3    |

| Power Supply<br>Current (Burst)                                  | ICC4   | All Banks<br>Active    | CKE ≥ VIH             | t <sub>CC</sub> = Min.                                       | 165 | 160  | 150  | 130 | mA | 1, 2 |

| Power Supply<br>Current<br>(Auto-Refresh)                        | ICC5   | All Bank<br>Active     | CKE ≥ V <sub>IH</sub> | t <sub>CC</sub> = Min.<br>t <sub>RC</sub> = Min.             | 200 | 180  | 160  | 140 | mA | 2    |

| Average Power<br>Supply Current<br>(Self-Refresh)                | ICC6   | All Banks<br>Precharge | CKE ≤ VIL             | t <sub>CC</sub> = Min.                                       | 4   | 4    | 4    | 4   | mA |      |

| Average Power<br>Supply Current<br>(Power Down)                  | ICC7   | All Banks<br>Precharge | CKE ≤ VIL             | t <sub>CC</sub> = Min.                                       | 3   | 3    | 3    | 3   | mA |      |

Notes: 1. Measured with outputs open.

2. The address and data can be changed once or left unchanged during one cycle.

3. The address and data can be changed once or left unchanged during two cycles.

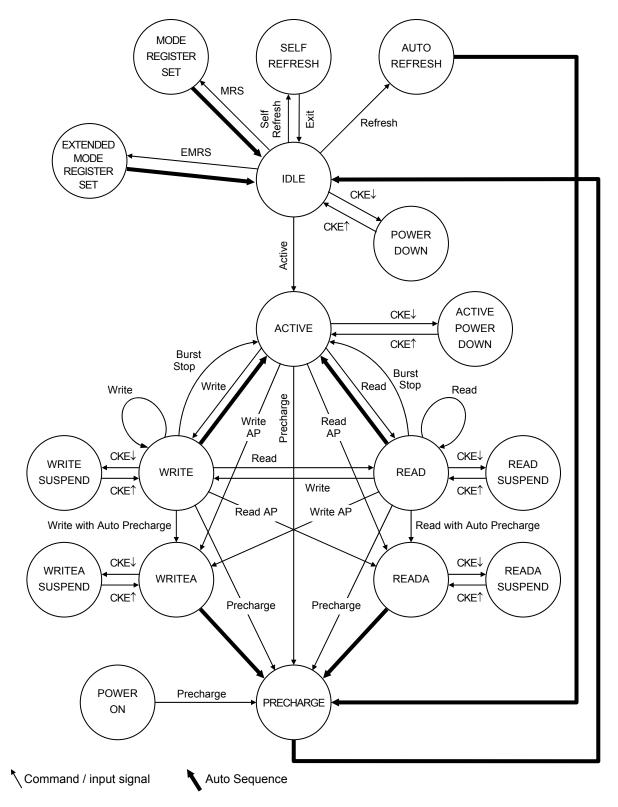

# AC Characteristics (1/2)

# $Ta=0 \text{ to } 70^{\circ}\text{C}$ $VCC = VCCQ = 3.3V \pm 0.3V$ Note 1.2

| h                                 |         | 1                | 1                         |                 |                           |                 |                           |                 |              |                 | 1     | Note1,2 |

|-----------------------------------|---------|------------------|---------------------------|-----------------|---------------------------|-----------------|---------------------------|-----------------|--------------|-----------------|-------|---------|

|                                   |         |                  | MD56V82160A-xxTA          |                 |                           |                 |                           |                 |              | Unit            | Note  |         |

| Parameter                         |         | Symbol           | (                         | -6              |                           | -7              |                           | -75             |              | -10             |       |         |

|                                   |         |                  | Min.                      | Max.            | Min.                      | Max.            | Min.                      | Max.            | Min.         | Max.            |       |         |

| Clock Cycle                       | CL=3    | t <sub>CC3</sub> | 6                         |                 | 7                         |                 | 7.5                       |                 | 10           |                 | ns    |         |

| Time                              | CL=2    | t <sub>CC2</sub> | 10                        |                 | 10                        | —               | 10                        |                 | 10           |                 | ns    |         |

| Access<br>Time from               | CL=3    | t <sub>AC3</sub> | —                         | 5.4             | _                         | 5.4             |                           | 5.4             |              | 6               | ns    | 3,4     |

| Clock                             | CL=2    | t <sub>AC2</sub> | —                         | 5.4             | —                         | 5.4             |                           | 5.4             | —            | 6               | ns    | 3,4     |

| Clock High<br>Time                |         | t <sub>CH</sub>  | 2                         |                 | 2                         |                 | 2.5                       |                 | 3            |                 | ns    | 4       |

| Clock Low Pul                     | se Time | t <sub>CL</sub>  | 2                         |                 | 2                         |                 | 2.5                       |                 | 3            |                 | ns    | 4       |

| Input Setup                       | Time    | tsı              | 1.5                       |                 | 1.5                       |                 | 1.5                       |                 | 2            |                 | ns    |         |

| Input Hold                        | Time    | t <sub>HI</sub>  | 0.8                       | _               | 0.8                       | _               | 0.8                       | _               | 1            | _               | ns    |         |

| Output L<br>Impedance<br>from Clo | Time    | tolz             | 1                         |                 | 1                         |                 | 1                         |                 | 2            |                 | ns    |         |

| Output F<br>Impedance<br>from Clo | Time    | t <sub>OHZ</sub> | _                         | 5.4             | _                         | 5.4             | _                         | 5.4             | _            | 6               | ns    |         |

| Output Hol<br>Clock               |         | <sup>t</sup> он  | 2                         |                 | 2                         | _               | 2.5                       | _               | 2.5          | _               | ns    | 3       |

| Random Re<br>Write Cycle          |         | t <sub>RC</sub>  | 60                        |                 | 60                        |                 | 65                        |                 | 70           |                 | ns    |         |

| RAS Prech<br>Time                 |         | t <sub>RP</sub>  | 18                        |                 | 18                        |                 | 18                        |                 | 20           |                 | ns    |         |

| RAS Pulse                         | Width   | t <sub>RAS</sub> | 42                        | 10 <sup>5</sup> | 42                        | 10 <sup>5</sup> | 45                        | 10 <sup>5</sup> | 50           | 10 <sup>5</sup> | ns    |         |

| /RAS to /CAS<br>Time              |         | t <sub>RCD</sub> | 18                        |                 | 18                        | _               | 18                        | _               | 20           | _               | ns    |         |

| Write Reco                        |         | two              | 2                         |                 | 2                         |                 | 2                         |                 | 2            |                 | Cycle | 6       |

| Time                              | Time    | <sup>t</sup> WR  | 12                        |                 | 14                        |                 | 15                        |                 | 20           |                 | ns    | 0       |

| /RAS to /RA<br>Active Dela        |         | t <sub>RRD</sub> | 12                        |                 | 12                        |                 | 15                        |                 | 20           |                 | ns    |         |

| Refresh 1                         | ime     | t <sub>REF</sub> | _                         | 64              | _                         | 64              | _                         | 64              |              | 64              | ms    | 5       |

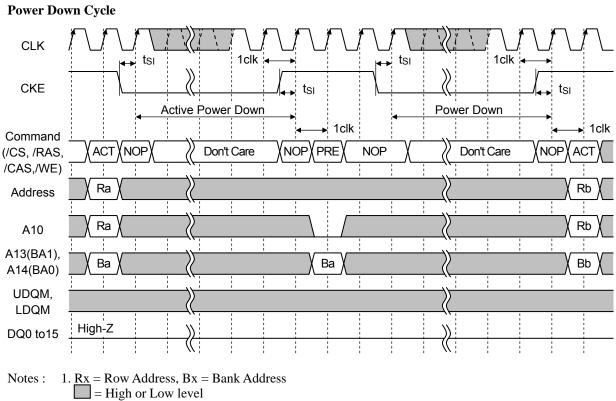

| Power-dow<br>setup Ti             |         | t <sub>PDE</sub> | t <sub>SI</sub> +1C<br>LK | _               | t <sub>SI</sub> +1C<br>LK | _               | t <sub>SI</sub> +1<br>CLK | _               | tSI+1<br>CLK | _               | ns    |         |

| Refresh cycl                      | e Time  | t <sub>RCA</sub> | 60                        | _               | 60                        | _               | 65                        |                 | 70           |                 | ns    |         |

# AC Characteristics (2/2)

| $Ta=0$ to $70^{\circ}C$      |

|------------------------------|

| $VCC = VCCQ = 3.3V \pm 0.3V$ |

| Note1,2                      |

|                                                                             |                  |    |    |     |     |       | Note 1,2 |

|-----------------------------------------------------------------------------|------------------|----|----|-----|-----|-------|----------|

|                                                                             |                  |    |    |     |     |       |          |

| Parameter                                                                   | Symbol           | -6 | -7 | -75 | -10 | Unit  | Note     |

| /CAS to /CAS Delay Time<br>(Min.)                                           | ICCD             | 1  | 1  | 1   | 1   | Cycle |          |

| Clock Disable Time from CKE                                                 | ICKE             | 1  | 1  | 1   | 1   | Cycle |          |

| Data Output High Impedance<br>Time from UDQM, LDQM                          | I <sub>DOZ</sub> | 2  | 2  | 2   | 2   | Cycle |          |

| Dada Input Mask Time from<br>UDQM, LDQM                                     | IDOD             | 0  | 0  | 0   | 0   | Cycle |          |

| Data Input Mask Time from Write<br>Command                                  | IDWD             | 0  | 0  | 0   | 0   | Cycle |          |

| Data Output High Impedance<br>Time from Precharge Command                   | IROH             | CL | CL | CL  | CL  | Cycle |          |

| Active Command Input Time<br>from Mode Register Set<br>Command Input (Min.) | I <sub>MRD</sub> | 2  | 2  | 2   | 2   | Cycle |          |

| Write Command Input Time from<br>Output                                     | IOWD             | 2  | 2  | 2   | 2   | Cycle |          |

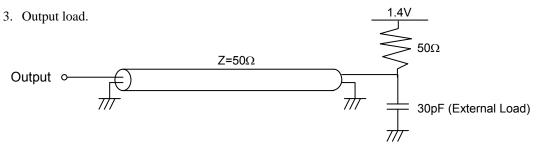

# Notes: 1. AC measurements assume that tT = 1ns,.

2. Test condition

| Parameter                                           | Test Condition    |  | Unit |

|-----------------------------------------------------|-------------------|--|------|

| Input voltage for AC measurement                    | 2.4 0.4           |  | V    |

| Transition Time for AC measurement                  | tT=1              |  | ns   |

| Reference level for timing of input signal (tT≤1ns) | 1.4               |  | V    |

| Reference level for timing of input signal (tT>1ns) | VIH Min. VIL Max. |  | V    |

| Reference level for timing of output signal         | 1.4               |  | V    |

- 4. If tT is longer than 1ns, then the reference level for timing of input signals is VIH and VIL.

- 5. It is necessary to operate auto-refresh 8,192 cycles within tREF.

- 6.  $t_{WR}$  can be used at one cycle when the clock cycle ( $t_{CC}$ ) is more than  $t_{CC}$ Min. x two cycles.

# POWER ON AND INITIALIZE

Be sure to do the following initialization sequence to initialize the inside of the memory after the power supply was turned on and to set up the mode.

#### **Power on Sequence**

- (1) Turn on the power after you make input a state of NOP, and input a system clock.

- (2) Take a pose of 200µs and more with making input a state of NOP after VCC and VCCQ reach it in the regular condition.

- (3) Issue the row precharge all bank command (PALL), and secure the row precharge time (tRP).

- (4) Issue the standard Mode Register Set command (MRS), and secure the mode register set command delay time (tMRD).

- (5). Issue the Extended Mode Register set command (EMRS), and secure the mode register set command delay time (tMRD).

- (6) Issue 2 or more auto-refresh commands (REF), and Secure the refresh cycle time (tRCA).

#### Note:

- 1. (4), (5) or (6): in no special order.

- 2. (5) can be omitted. When it is omitted, it becomes default settings.

- 3. Carry out an initialization sequence after each input terminal reaches a regulation voltage when other input terminals were the undefined setup input (High-Z) at the CKE= "H" time. And, the undefined setup input period of the CKE= "H" time can't hold data. It becomes more effective than writing data after the initialization sequence.

#### Mode Register Set Command (MRS)

The mode register stores the data for controlling the various operating modes. It programs the /CAS latency, burst type, burst length and write mode. The default value of the mode register is not defined, therefore the mode register must be written after power up to operate the SDRAM. The mode register is written by mode register set command MRS. The state of address pins A0 to A12 and BA1(A13), BA0(A14) in the same cycle as MRS is the data written in the mode register. Refer to the table for specific codes for various /CAS latencies, burst type, burst length and write mode.

| <u>MRS</u>                        |        |        |  |  |

|-----------------------------------|--------|--------|--|--|

| CLK                               | n-1    | l<br>n |  |  |

| CKE                               | Н      | Х      |  |  |

| /CS                               |        | L      |  |  |

| /RAS                              | Х      | L      |  |  |

| /CAS                              | (Idle) | L      |  |  |

| /WE                               |        | L      |  |  |

| BA1(A13)                          | Х      | 0      |  |  |

| BA0(A14)                          | Х      | 0      |  |  |

| A0 to A12                         | Х      | V      |  |  |

| V: The value of mode register set |        |        |  |  |

V: The value of mode register set

#### **Extended Mode Register Set Command (EMRS)**

MD56V82160A-xxTA sets up output drivability by the extended mode register.

The EMRS register input control is same as MRS settings except for inputting 1 to A14.

If an extended mode register isn't set up, output drivability is full power as default settings.

| EMRS      |        |         |

|-----------|--------|---------|

| CLK       | n-1    | ام<br>م |

| CKE       | Н      | Х       |

| /CS       |        | L       |

| /RAS      | Х      | L       |

| /CAS      | (Idle) | L       |

| /WE       |        | L       |

| BA1(A13)  | Х      | 0       |

| BA0(A14)  | Х      | 1       |

| A0 to A12 | Х      | v       |

V: The value of extended mode register set

| Wri | Write Burst Mode |    | /CAS Latency |    | E        | Burst Type |            |    | В  | urst Length |           |          |

|-----|------------------|----|--------------|----|----------|------------|------------|----|----|-------------|-----------|----------|

| A9  | WM               | A6 | A5           | A4 | CL       | A3         | BT         | A2 | A1 | A0          | BT = 0    | BT = 1   |

| 0   | Burst            | 0  | 0            | 0  | Reserved | 0          | Sequential | 0  | 0  | 0           | 1         | 1        |

| 1   | Single           | 0  | 0            | 1  | Reserved | 1          | Interleave | 0  | 0  | 1           | 2         | 2        |

|     |                  | 0  | 1            | 0  | 2        |            |            | 0  | 1  | 0           | 4         | 4        |

|     |                  | 0  | 1            | 1  | 3        |            |            | 0  | 1  | 1           | 8         | 8        |

|     |                  | 1  | 0            | 0  | Reserved |            |            | 1  | 0  | 0           | Reserved  | Reserved |

|     |                  | 1  | 0            | 1  | Reserved |            |            | 1  | 0  | 1           | Reserved  | Reserved |

|     |                  | 1  | 1            | 0  | Reserved |            |            | 1  | 1  | 0           | Reserved  | Reserved |

|     |                  | 1  | 1            | 1  | Reserved |            |            | 1  | 1  | 1           | Full Page | Reserved |

# Mode Register Field Table To Program Mode

Notes: 1. Objects are all family products.

2. A13 and A14 should stay "0" during mode set cycle.

- 3. A7, A8, A10, A11 and A12 should stay "0" during mode set cycle.

- 4. Don't set address keys of "Reserved".

#### **Extended Mode Register Set Address Keys**

| Output Driver Strength |    |                |  |  |

|------------------------|----|----------------|--|--|

| A6                     | A5 | DS             |  |  |

| 0                      | 0  | Full (Default) |  |  |

| 0                      | 1  | 1/2            |  |  |

| 1                      | 0  | 1/8            |  |  |

| 1                      | 1  | 1/4            |  |  |

Notes: 1. A13 should stay "0" and A14 should stay "1" during mode set cycle. 2. A0 to A4, A7to A12 should stay "0" during mode set cycle.

- 3. Don't set address keys of "Reserved".

- 4. If don't set EMRS, DS is set to default (Full).

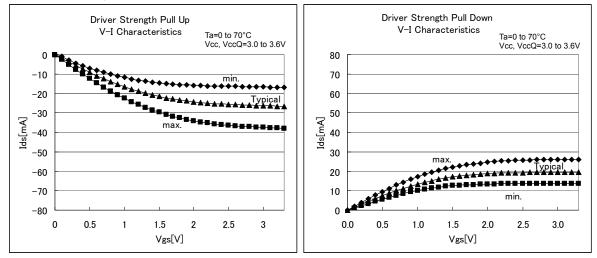

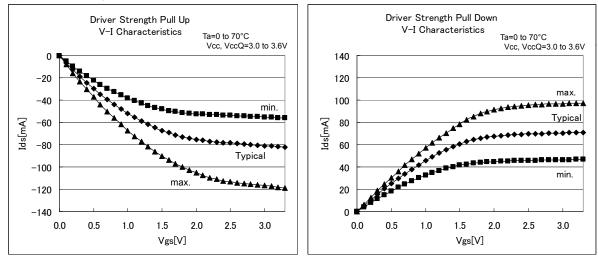

# • Output Driver Characteristics (1/2)

#### Output Driver Strength=1/8

#### Output Driver Strength=1/4

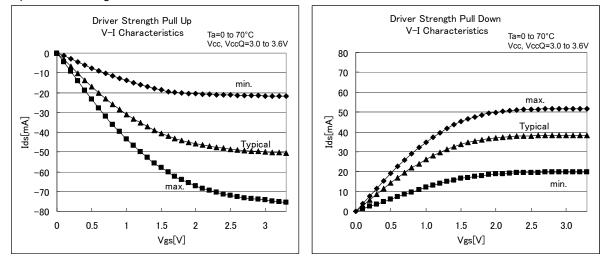

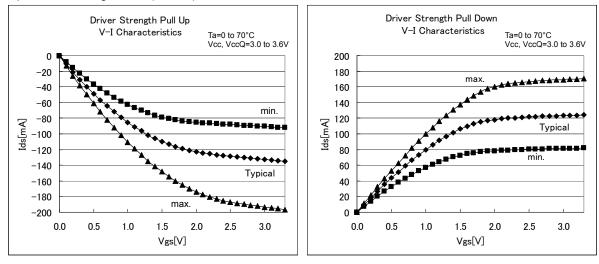

# • Output Driver Characteristics (2/2)

#### Output Driver Strength=1/2

#### Output Driver Strength= Full (Default)

# **Burst Mode**

Burst operation is the operation to continuously increase a column address inputted during read or write command. The upper bits select a column address block,

|              | /            |               |           | Ac | cess order in column address l | olock                  |  |

|--------------|--------------|---------------|-----------|----|--------------------------------|------------------------|--|

|              |              | Start Address |           |    | Burst Type                     |                        |  |

|              |              | (             | Lower bit | )  | BT=Sequential                  | BT=Interleave          |  |

|              |              |               |           | A0 |                                |                        |  |

|              | BL=2         |               |           | 0  | 0, 1                           | 0, 1                   |  |

|              |              |               |           | 1  | 1, 0                           | 1, 0                   |  |

|              |              |               | A1        | A0 |                                |                        |  |

|              |              |               | 0         | 0  | 0, 1, 2, 3                     | 0, 1, 2, 3             |  |

|              | BL=4         |               | 0         | 1  | 1, 2, 3, 0                     | 1, 0, 3, 2             |  |

|              |              |               | 1         | 0  | 2, 3, 0, 1                     | 2, 3, 0, 1             |  |

|              |              |               | 1         | 1  | 3, 0, 1, 2                     | 3, 2, 1, 0             |  |

| ÷            |              | A2            | A1        | A0 |                                |                        |  |

| Burst Length |              | 0             | 0         | 0  | 0, 1, 2, 3, 4, 5, 6, 7         | 0, 1, 2, 3, 4, 5, 6, 7 |  |

| st Le        |              | 0             | 0         | 1  | 1, 2, 3, 4, 5, 6, 7, 0         | 1, 0, 3, 2, 5, 4, 7, 6 |  |

| Bur          |              | 0             | 1         | 0  | 2, 3, 4, 5, 6, 7, 0, 1         | 2, 3, 0, 1, 6, 7, 4, 5 |  |

|              | BL=8         | 0             | 1         | 1  | 3, 4, 5, 6, 7, 0, 1, 2         | 3, 2, 1, 0, 7, 6, 5, 4 |  |

|              |              | 1             | 0         | 0  | 4, 5, 6, 7, 0, 1, 2, 3         | 4, 5, 6, 7, 0, 1, 2, 3 |  |

|              |              | 1             | 0         | 1  | 5, 6, 7, 0, 1, 2, 3, 4         | 5, 4, 7, 6, 1, 0, 3, 2 |  |

|              |              | 1             | 1         | 0  | 6, 7, 0, 1, 2, 3, 4, 5         | 6, 7, 4, 5, 2, 3, 0, 1 |  |

|              |              | 1             | 1         | 1  | 7, 0, 1, 2, 3, 4, 5, 6         | 7, 6, 5, 4, 3, 2, 1, 0 |  |

|              |              |               | A8~A0     |    |                                |                        |  |

|              | BL=Full Page |               | 0         |    | 0, 1 511                       |                        |  |

|              | (512)        |               | Yn        |    | Yn, Yn+1 511, 0<br>Yn-1        | Non Support            |  |

#### **READ / WRITE OPERATION**

#### Bank

This SDRAM is organized as four independent banks of 1,048,576 words x 16 bits memory arrays. The A13(BA1) and A14(BA0) input is latched at the time of assertion of /RAS and /CAS to select the bank to be used for operation. The bank address A13 and A14 are latched at bank active, read, write, mode register set and precharge operations.

| Bank Address |          |      |  |  |  |

|--------------|----------|------|--|--|--|

| A13(BA1)     | A14(BA0) | Bank |  |  |  |

| 0            | 0        | А    |  |  |  |

| 0            | 1        | В    |  |  |  |

| 1            | 0        | С    |  |  |  |

| 1            | 1        | D    |  |  |  |

Activate

Precharge

The precharge operation is

performed on an active bank by precharge command (PRE) with

valid A13 and A14 of the bank to

be precharged. The precharge

command can be asserted anytime

after tRAS(min) is satisfied from

the bank active command in the

desired bank. All bank can

precharged at the same time by

using precharge all command

(PALL). Asserting low on /CS,

/RAS and /WE with high on A10

after all banks have satisfied tRAS(min) requirement, performs

The bank activate command is used to select a random row in an idle bank. By asserting low on /RAS and /CS with desired row and bank address, a row access is initiated. The read or write operation can occur after a time delay of tRCD(min) from the time of bank activation.

PRE

CLK

CKE

/CS

/RAS

/CAS

/WE

A13(BA1),

A14(BA0)

A10

A0 to A9.

A11,A12

| ACT |  |

|-----|--|

|     |  |

| CLK                   | n-1    | l₄- <sub>1</sub> c |

|-----------------------|--------|--------------------|

| CKE                   | Н      | Х                  |

| /CS                   |        | L                  |

| /RAS                  | Х      | L                  |

| /CAS                  | (Idle) | н                  |

| /WE                   |        | н                  |

| A13(BA1),<br>A14(BA0) | х      | ВА                 |

| A0 to A12             | Х      | RA                 |

BA: Bank Address RA: Row Address (Page)

# PALL

| CLK                   | <br>n-1        | l₄┐ ╸ |

|-----------------------|----------------|-------|

| CKE                   | Н              | Х     |

| /CS                   |                | L     |

| /RAS                  | Х              | L     |

| /CAS                  | (Page<br>Open) | н     |

| /WE                   | opony          | L     |

| A13(BA1),<br>A14(BA0) | х              | x     |

| A10                   | Х              | 1     |

| A0 to A9,<br>A11,A12  | ×              | x     |

BA: Bank Address

precharge on al banks. At the end of tRP after performing precharge to all banks, all banks are in idle state.

\_₹

n-1

Н

Х

(Page

Open)

Х

Х

Х

\_1

n

Х

L

L

н

L

BA

0

Х

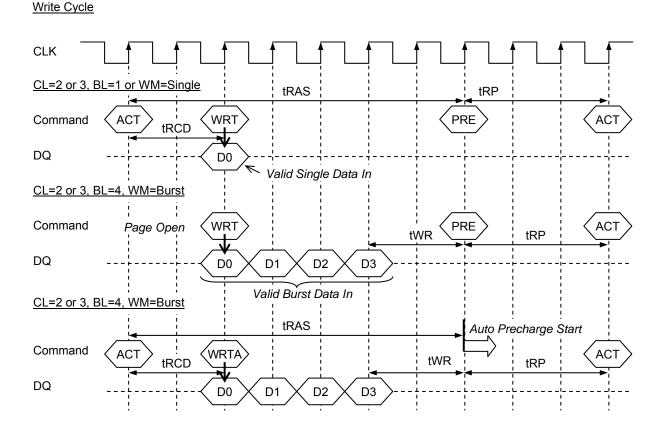

# Write / Write with Auto-Precharge

The write command is used to write data into the SDRAM on consecutive clock cycles in adjacent address depending on burst length and burst sequence. By asserting low on /CS, /CAS and /WE with valid column address, a write burst is initiated. The data inputs are provided for the initial address in the same clock cycle as the burst write command. The input buffer is deselected at the end of the burst length, even through the internal writing can be completed yet. The writing can be completed by issuing a burst read and DQM for blocking data inputs or burst write in the same or another active bank. The burst stop command is valid at every burst length.

|       | ام ا                                              |

|-------|---------------------------------------------------|

| Н     | Х                                                 |

| X     | L                                                 |

|       | н                                                 |

|       | L                                                 |

| Open) | L                                                 |

| х     | ВА                                                |

| Х     | 0                                                 |

| Х     | Х                                                 |

| Х     | CA                                                |

| Х     | D-in                                              |

|       | H<br>X<br>(Page<br>Open)<br>X<br>X<br>X<br>X<br>X |

BA: Bank Address CA: Column Address D-in: Data inputs

| <u>WRTA</u>           |                |      |  |  |

|-----------------------|----------------|------|--|--|

| CLK                   | <br>n-1        | l₄┐¤ |  |  |

| CKE                   | Н              | Х    |  |  |

| /CS                   | X              | L    |  |  |

| /RAS                  | X              | н    |  |  |

| /CAS                  | (Page<br>Open) | L    |  |  |

| /WE                   | Open)          | L    |  |  |

| A13(BA1),<br>A14(BA0) | х              | ВА   |  |  |

| A10                   | Х              | 1    |  |  |

| A9 to A12             | Х              | Х    |  |  |

| A0 to A8              | Х              | CA   |  |  |

| DQ                    | Х              | D-in |  |  |

| BA: Bank Address      |                |      |  |  |

CA: Column Address

D-in: Data inputs

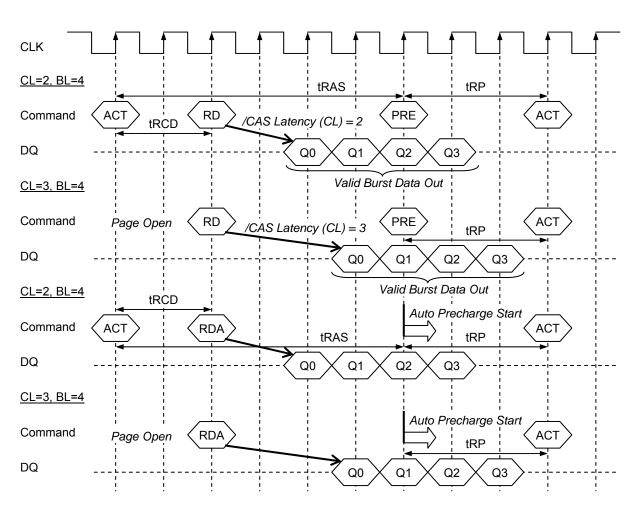

#### **Read / Read with Auto-Precharge**

The read command is used to access burst of data on consecutive clock cycles from an active row in an active bank. The read command is issued by asserting low on /CS and /CAS with /WE being high on the positive edge of the clock. The bank must be active for at least tRCD(min) before the read command is issued. The first output appears in /CAS latency number of clock cycles after the issue of read command. The burst length, burst sequence and latency from the read command are determined by the mode register that is already programmed.

| RD                    |                                        |      |  |  |  |  |  |  |

|-----------------------|----------------------------------------|------|--|--|--|--|--|--|

| CLK                   |                                        | l₄┐∝ |  |  |  |  |  |  |

| CKE                   | Н                                      | Х    |  |  |  |  |  |  |

| /CS                   |                                        | L    |  |  |  |  |  |  |

| /RAS                  | Х                                      | н    |  |  |  |  |  |  |

| /CAS                  | (Page<br>Open)                         | L    |  |  |  |  |  |  |

| /WE                   | Openij                                 | н    |  |  |  |  |  |  |

| A13(BA1),<br>A14(BA0) | х                                      | ВА   |  |  |  |  |  |  |

| A10                   | Х                                      | 0    |  |  |  |  |  |  |

| A9 to A12             | Х                                      | Х    |  |  |  |  |  |  |

| A0 to A8              | Х                                      | CA   |  |  |  |  |  |  |

| DQ                    | Х                                      | Х    |  |  |  |  |  |  |

|                       | BA: Bank Address<br>CA: Column Address |      |  |  |  |  |  |  |

| <u>RDA</u>            |                     |       |  |  |  |

|-----------------------|---------------------|-------|--|--|--|

| CLK                   |                     | le je |  |  |  |

| CKE                   | Н                   | Х     |  |  |  |

| /CS                   | L                   |       |  |  |  |

| /RAS                  | X<br>(Page<br>Open) |       |  |  |  |

| /CAS                  |                     |       |  |  |  |

| /WE                   |                     | н     |  |  |  |

| A13(BA1),<br>A14(BA0) | х                   | ВА    |  |  |  |

| A10                   | Х                   | 1     |  |  |  |

| A9 to A12             | Х                   | Х     |  |  |  |

| A0 to A8              | Х                   | CA    |  |  |  |

| DQ                    | Х                   | Х     |  |  |  |

| BA: Bank Addı         | ess                 |       |  |  |  |

CA: Column Address

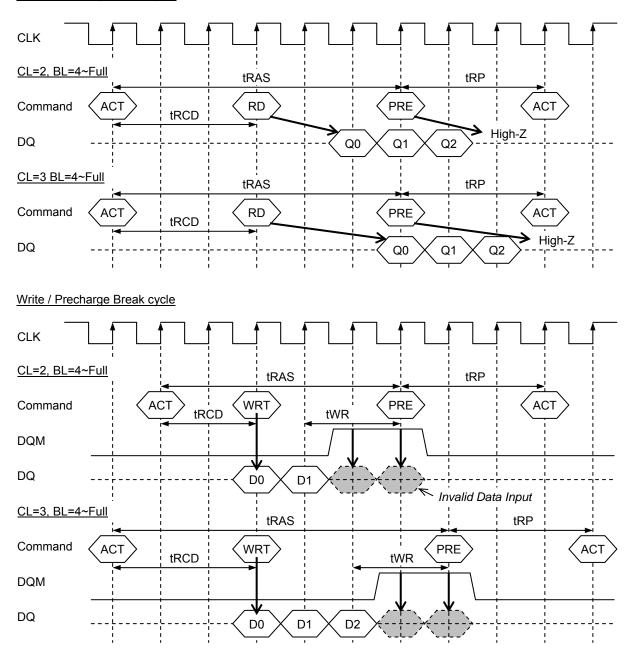

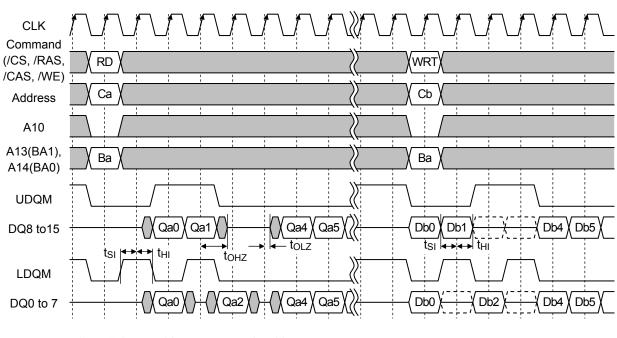

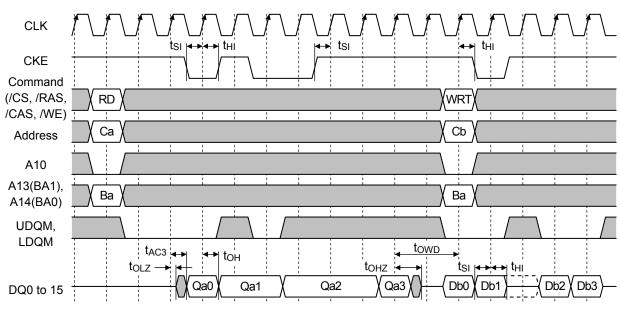

#### Read Cycle

#### Write / Write interrupt

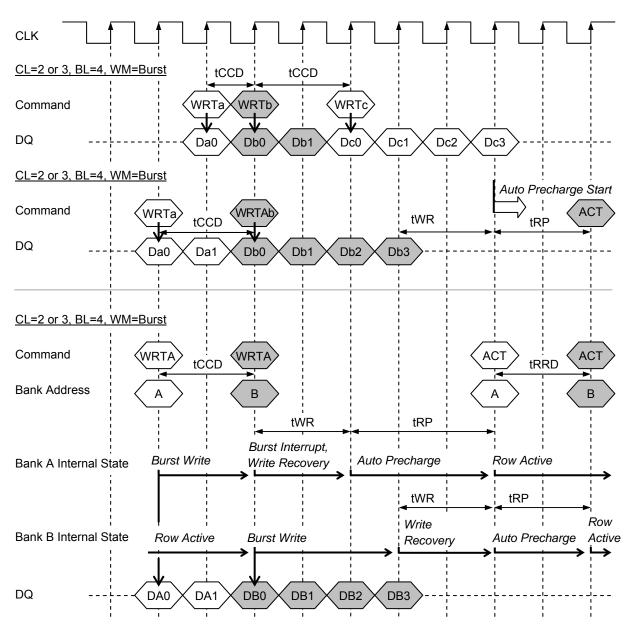

When a new write command is issued to same bank during write cycle or another active bank, current burst write is terminated and new burst write start. When a new write command is issued to another bank during a write with auto-precharge cycle, current burst is terminated and a new write command start. Then, current bank is precharged after specified time. Don't issue a new write command to same bank during write with auto-precharge cycle.

Write / Write interrupt cycle

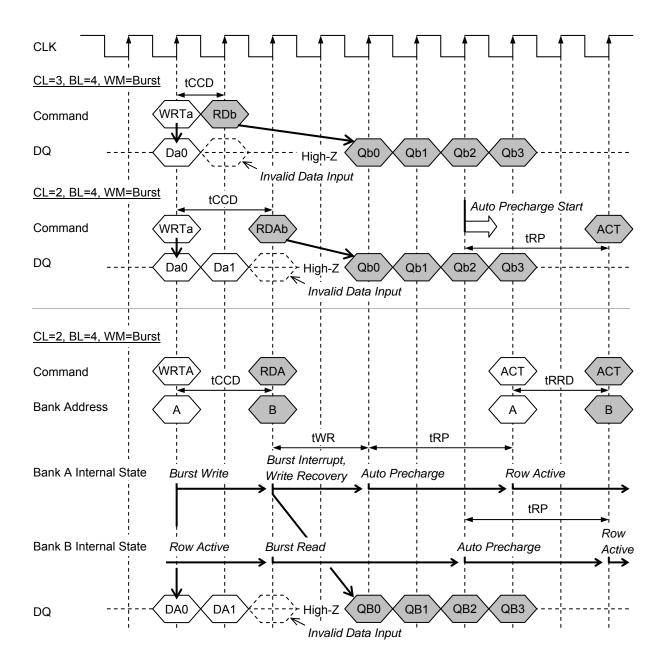

#### Read / Read interrupt

When a new read command is issued to same bank during read cycle or another active bank, current burst read is terminated after the cycle same as /CAS latency and new burst read start. When a new read command is issued to another bank during a read with auto-precharge cycle, current burst is terminated after the cycle same as /CAS latency and a new read command start. Then, current bank is precharged after specified time. Don't issue a new read command to same bank during read with auto-precharge cycle.

#### CLK CL=2, BL=4 tCCD tCCD RDb RDc RDa Command High-Z DQ Qa0 Qb0 Qb1 Qc0 Qc1 Qc2 Qc3 CL=3, BL=4 tCCD Auto Precharge Start Command RDAb RDa ACT tRP DQ Qb0 Qa0 Qa1 Qb1 Qb2 Qb3 High-Z CL=2, BL=4 Command RDA RDA ACT ACT tCCD tRRD Bank Address В В A A tRP + 1clk Burst Bank A Internal State Burst Read Auto Precharge Row Active Interrupt tRP Row Row Active Burst Read Auto Precharge Bank B Internal State Active DQ QA0 QA1 QB0 QB1 QB2 QB3

#### Read / Read interrupt cycle

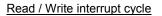

#### Write / Read interrupt

When a new read command is issued to same bank during write cycle or another active bank, current burst write is terminated and new burst read start. When a new read command is issued to another bank during a write with auto-precharge cycle, current burst is terminated and a new read command start. Then, current bank is precharged after specified time. Don't issue a new read command to same bank during write with auto-precharge cycle. DQ must be hi-Z till 1 or more clock from first read data.

#### Write / Read interrupt cycle

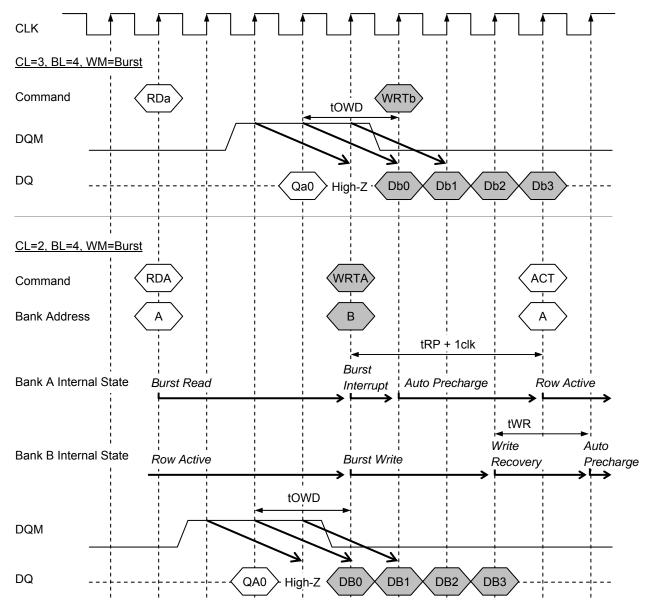

#### **Read / Write interrupt**

When a new write command is issued to same bank during read cycle or another active bank, current burst read is terminated and new burst write start. When a new write command is issued to another bank during a read with auto-precharge cycle, current burst is terminated and a new write command start. Then, current bank is precharged after specified time. Don't issue a new write command to same bank during read with auto-precharge cycle. DQ must be Hi-Z till 1 or more clock from new write command. Therefore, DQM must be high till 3 clocks from new write command.

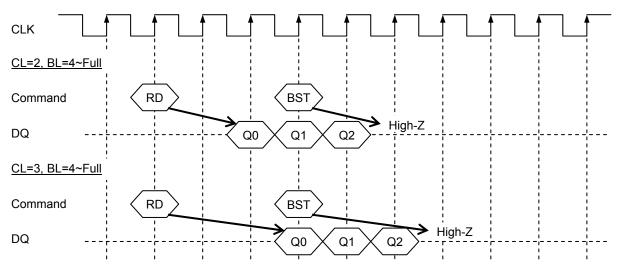

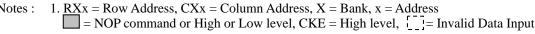

#### **Burst Stop**

When a burst stop command is issued during read cycle, current burst read is terminated. The DQ is to Hi-Z after the cycle same as /CAS latency and page keep open. When a burst stop command is issued during write cycle, current burst write is terminated. The input data is ignored after burst stop command. Don't issue burst stop command during read with auto-precharge cycle or write with auto-precharge cycle.

| <u>BST</u>            |         |      |

|-----------------------|---------|------|

| CLK                   | <br>n-1 | ام ا |

| CKE                   | Н       | Х    |

| /CS                   |         | L    |

| /RAS                  | Х       | Н    |

| /CAS                  | (Burst) | Н    |

| /WE                   |         | L    |

| A13(BA1),<br>A14(BA0) | ×       | x    |

| A0 to A12             | Х       | Х    |

Write / Burst Stop cycle

Read / Burst Stop cycle

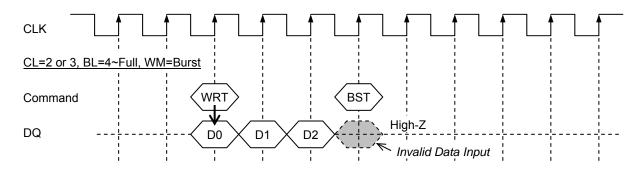

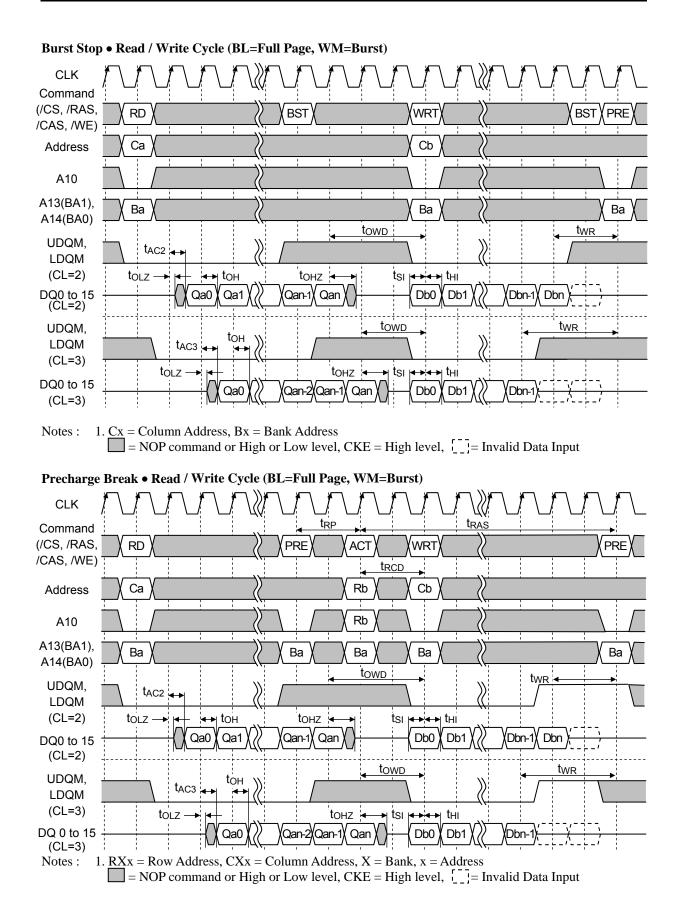

#### **Precharge Break**

When a precharge command is issued to the same bank during read cycle or precharge all command is issued, current burst read is terminated and DQ is to Hi-Z after the cycle same as /CAS latency. The objected bank is precharged. When a precharge command is issued to the same bank during write cycle or precharge all command is issued, current burst write is terminated and the objected bank is precharged. The input data after precharge command is ignored.

#### Read / Precharge Break cycle

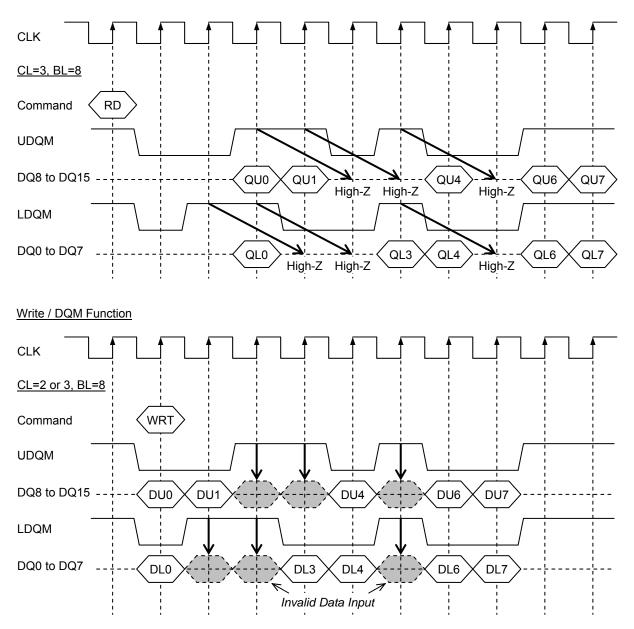

## **DQM Function**

DQM masks input / output data at every byte. UDQM controls DQ8 to DQ15 and LDQM controls DQ0 to DQ7. During read cycle, DQM mask output data after 2 clocks. During write cycle, DQM mask input data at same clock.

#### Read / DQM Function

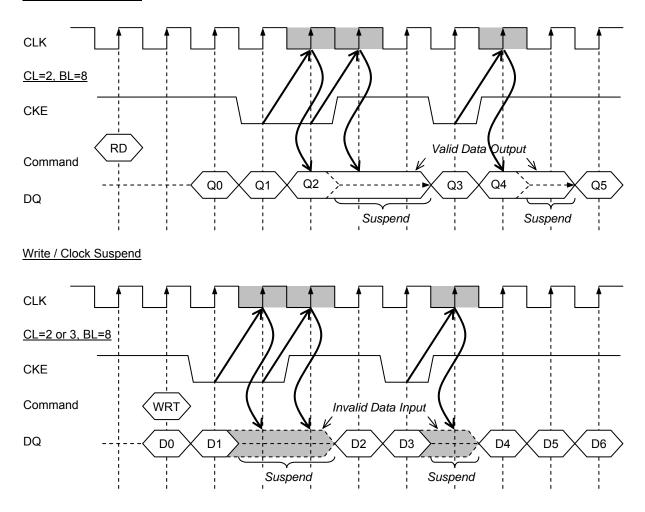

#### **Clock Suspend**

The read / write operation can be stopped by CKE temporarily. When CKE is set low, the next clock is ignored. When CKE is set low during read cycle, the burst read is stopped temporarily and the current output data is kept. When CKE is set high, burst read is resumed. When CKE is set low during write cycle, the burst write is stopped temporarily. When CKE is set high, burst write is resumed.

#### Read / Clock Suspend

#### REFRESH

The data of memory cells are maintained by refresh operation. The refresh operation is to activate all row addresses within a refresh time. The method that row addresses are activated by activate and precharge command is called RAS only refresh cycle. This method needs to input row address with activate command. But, auto-refresh and self refresh don't need to input address. Because, row addresses are generated in SDRAM automatically.

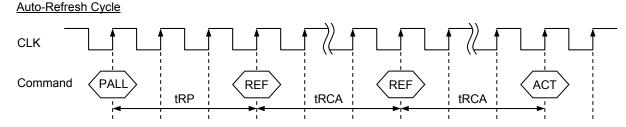

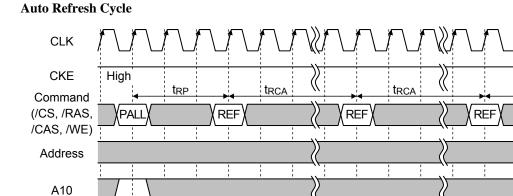

#### **Auto Refresh**

All memory area is refreshed by 8,192 times refresh command REF. The refresh command REF can be entered only when all the banks are in an idle state. SDRAM is in idle state after refresh cycle time tRCA.

| REF                   |         |   |

|-----------------------|---------|---|

| CLK                   | <br>n-1 | n |

| CKE                   | Н       | Н |

| /CS                   |         | L |

| /RAS                  | Х       | L |

| /CAS                  | (Idle)  | L |

| /WE                   |         | н |

| A13(BA1),<br>A14(BA0) | х       | x |

| A0 to A12             | Х       | Х |

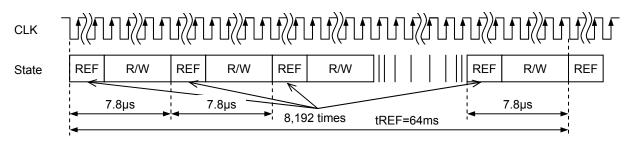

#### Intensive Refresh

8,192 times refresh command can be entered every refresh time t<sub>REF</sub>.

| CLK   |               |              |               |              |

|-------|---------------|--------------|---------------|--------------|

| State | Read or Write | Auto Refresh | Read or Write | Auto Refresh |

|       | tREF=64ms     | REF x 8,192  | tREF=64ms     | REF x 8,192  |

|       |               | >            |               | ¥            |

# Dispersed Refresh

Refresh command can be entered every7.8µs (tREF 64ms / 8,192 cycles).

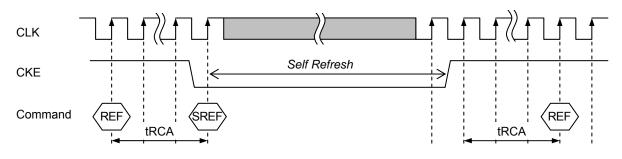

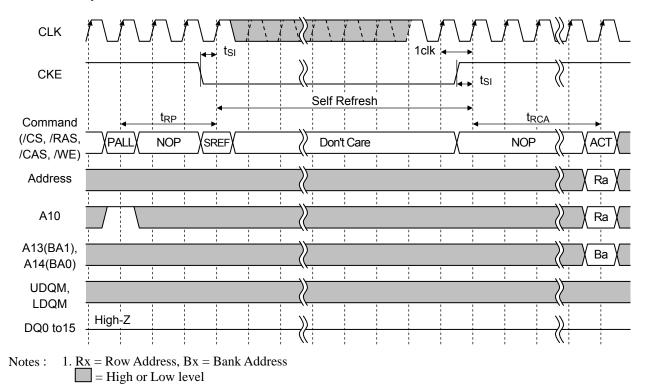

#### Self Refresh

When read or write is not operated in the long period, self refresh can reduce power consumption for refresh operation. Refresh operation is controlled automatically by refresh timer and row address counter during self refresh mode. All signals except CKE are ignored and data bus DQ is set Hi-Z during self refresh mode.

When CKE is set to high level, self refresh mode is finished. Then, CLK must be operated before 1 clock or more. And, maintain NOP condition within a period of tRCA(Min.) after CKE is set to be high level.

| <u>SREF</u>           |        |      |

|-----------------------|--------|------|

| CLK                   | n-1    | l₄⊣c |

| CKE                   | Н      | L    |

| /CS                   |        | L    |

| /RAS                  | Х      | L    |

| /CAS                  | (Idle) | L    |

| /WE                   |        | H    |

| A13(BA1),<br>A14(BA0) | х      | х    |

| A0 to A12             | Х      | Х    |

# Self Refresh Cycle

Notes : 1. When intensive refresh is used, 8,192 times refresh must be issued before and after the self refresh.

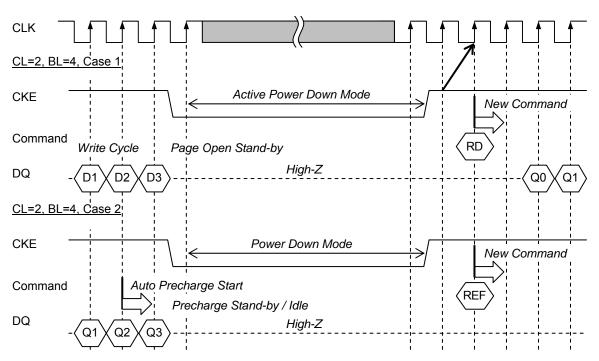

## **Power Down**

SDRAM can be set to low power consumption condition with CKE function. CKE is reflected at 2 clocks later regardless /CAS latency. When CKE is set to low level, SDRAM go into power down mode. All signals except CKE are ignored and DQ is set to High impedance in this state. When CKE is set to high level, SDRAM exit power down mode. Then, Clock must be resumed before 2 or more clocks.

Power Down

#### Signal Condition in Power Down Mode

| Signal              | Input to SDRAM | Output from SDRAM |

|---------------------|----------------|-------------------|

| CLK                 | Don't Care     | _                 |

| CKE                 | "L" level      | _                 |

| /CS,/RAS, /CAS, /WE | Don't Care     | —                 |

| A0 to A12,          | Don't Care     |                   |

| A13(BA1), A14(BA0)  | Dont Care      |                   |

| DQ0 to DQ15         | Don't Care     | High-Z            |

| UDQM,LDQM           | Don't Care     |                   |

| VCC,VCCQ,VSS,VSSQ   | Power Supply   |                   |

Notes : 1. "Don't Care" means high or low level input.

| MD56V82160A-xxTA |

|------------------|

|------------------|

| Current<br>State * <sup>1</sup> | /CS | /RAS | /CAS | /WE | ADDR               | Command  | Action                               |

|---------------------------------|-----|------|------|-----|--------------------|----------|--------------------------------------|

| Idle                            | Н   | Х    | Х    | Х   | Х                  | NOP      | NOP                                  |

|                                 | L   | Н    | Н    | Х   | X NOP/BST          |          | NOP                                  |

|                                 | L   | Н    | L    | Н   | BA, CA, A10        | RD/RDA   | ILLEGAL <sup>*2</sup>                |

|                                 | L   | Н    | L    | L   | BA, CA, A10        | WRT/WRTA | ILLEGAL <sup>*2</sup>                |

|                                 | L   | L    | Н    | Н   | BA, RA             | ACT      | Row Active                           |

|                                 | L   | L    | Н    | L   | BA, A10            | PRE/PALL | NOP *3                               |

|                                 | L   | L    | L    | Н   | Х                  | REF      | Auto-Refresh or Self-Refresh *4      |

|                                 | L   | L    | L    | L   | V, A13=0,<br>A14=0 | MRS      | Mode Register Set *4                 |

|                                 | L   | L    | L    | L   | V, A13=0,<br>A14=1 | EMRS     | Extended Mode Register Set *4        |

| Row                             | Н   | Х    | Х    | Х   | Х                  | NOP      | NOP                                  |

| Active                          | L   | Н    | Н    | Х   | Х                  | NOP/BST  | NOP                                  |

|                                 | L   | Н    | L    | Н   | BA, CA, A10        | RD/RDA   | Read                                 |

|                                 | L   | Н    | L    | L   | BA, CA, A10        | WRT/WRTA | Write                                |

|                                 | L   | L    | Н    | Н   | BA, RA             | ACT      | ILLEGAL *6                           |

|                                 | L   | L    | Н    | L   | BA, A10            | PRE/PALL | Precharge                            |

|                                 | L   | L    | L    | Н   | Х                  | REF      | ILLEGAL                              |

|                                 | L   | L    | L    | L   | Х                  | MRS/EMRS | ILLEGAL                              |

| Read                            | Н   | Х    | Х    | Х   | Х                  | NOP      | Continue Row Active after Burst ends |

|                                 | L   | Н    | Н    | Н   | х                  | NOP      | Continue Row Active after Burst ends |

|                                 | L   | Н    | Н    | L   | х                  | BST      | Term Burst> Row Active               |

|                                 | L   | Н    | L    | Н   | BA, CA, A10        | RD/RDA   | Term Burst, start new Burst Read     |

|                                 | L   | Н    | L    | L   | BA, CA, A10        | WRT/WRTA | Term Burst, start new Burst Write    |

|                                 | L   | L    | Н    | H   | BA, RA             | ACT      | ILLEGAL *6                           |

|                                 | L   | L    | Н    | L   | BA, A10            | PRE/PALL | Term Burst, execute Row Precharge    |

|                                 | L   | L    | L    | Н   | Х                  | REF      | ILLEGAL                              |

|                                 | L   | L    | L    | L   | Х                  | MRS/EMRS | ILLEGAL                              |

| Write                           | Н   | Х    | Х    | Х   | Х                  | Х        | Continue Row Active after Burst ends |

|                                 | L   | Н    | Н    | Н   | Х                  | Х        | Continue Row Active after Burst ends |

|                                 | L   | Н    | Н    | L   | Х                  | Х        | Term Burst> Row Active               |

|                                 | L   | Н    | L    | Н   | BA, CA, A10        | CA, A10  | Term Burst, start new Burst Read     |

|                                 | L   | Н    | L    | L   | BA, CA, A10        | CA, A10  | Term Burst, start new Burst Write    |

|                                 | L   | L    | Н    | Н   | BA, RA             | RA       | ILLEGAL <sup>*6</sup>                |

|                                 | L   | L    | Н    | L   | BA, A10            | A10      | Term Burst, execute Row Precharge    |

|                                 | L   | L    | L    | Н   | Х                  | REF      | ILLEGAL                              |

|                                 | L   | L    | L    | L   | Х                  | MRS/EMRS | ILLEGAL                              |

# FUNCTION TRUTH TABLE (Table 1) (1/3)

| Current<br>State <sup>*1</sup> | /CS | /RAS | /CAS | /WE | ADDR        | Command  | Action                                        |

|--------------------------------|-----|------|------|-----|-------------|----------|-----------------------------------------------|

| Read with                      | Н   | Х    | Х    | Х   | Х           | NOP      | Continue Burst to End and enter Row Precharge |

| Auto                           | L   | Н    | Н    | Н   | X NOP       |          | Continue Burst to End and enter Row Precharge |

| Precharge                      | L   | Н    | Н    | L   | Х           | BST      | ILLEGAL                                       |

|                                | L   | Н    | L    | Н   | BA, CA, A10 | RD/RDA   | ILLEGAL *7                                    |

|                                | L   | Н    | L    | L   | BA, CA, A10 | WRT/WRTA | ILLEGAL *7                                    |

|                                | L   | L    | Н    | Н   | BA, RA      | ACT      | ILLEGAL *6                                    |

|                                | L   | L    | Н    | L   | BA, A10     | PRE/PALL | ILLEGAL *8                                    |

|                                | L   | L    | L    | Н   | Х           | REF      | ILLEGAL                                       |

|                                | L   | L    | L    | L   | Х           | MRS/EMRS | ILLEGAL                                       |

| Write with                     | Н   | Х    | Х    | Х   | Х           | NOP      | Continue Burst to End and enter Row Precharge |

| Auto                           | L   | Н    | Н    | Н   | Х           | NOP      | Continue Burst to End and enter Row Precharge |

| Precharge                      | L   | Н    | Н    | L   | Х           | BST      | ILLEGAL                                       |

|                                | L   | Н    | L    | Н   | BA, CA, A10 | RD/RDA   | ILLEGAL *7                                    |

|                                | L   | Н    | L    | L   | BA, CA, A10 | WRT/WRTA | ILLEGAL *7                                    |

|                                | L   | L    | Н    | H   | BA, RA      | ACT      | ILLEGAL *6                                    |

|                                | L   | L    | Н    | L   | BA, A10     | PRE/PALL | ILLEGAL *8                                    |

|                                | L   | L    | L    | Н   | Х           | REF      | ILLEGAL                                       |

|                                | L   | L    | L    | L   | Х           | MRS/EMRS | ILLEGAL                                       |

| Precharge                      | Н   | Х    | Х    | Х   | Х           | NOP      | Idle after t <sub>RP</sub>                    |

|                                | L   | Н    | Н    | Н   | Х           | NOP      | Idle after t <sub>RP</sub>                    |

|                                | L   | Н    | Н    | L   | Х           | BST      | ILLEGAL                                       |

|                                | L   | Н    | L    | Н   | BA, CA, A10 | RD/RDA   | ILLEGAL *2                                    |

|                                | L   | Н    | L    | L   | BA, CA, A10 | WRT/WRTA | ILLEGAL *2                                    |

|                                | L   | L    | Н    | Н   | BA, RA      | ACT      | ILLEGAL <sup>*6</sup>                         |

|                                | L   | L    | Н    | L   | BA, A10     | PRE/PALL | ILLEGAL *3                                    |

|                                | L   | L    | L    | Н   | Х           | REF      | ILLEGAL                                       |

|                                | L   | L    | L    | L   | Х           | MRS/EMRS | ILLEGAL                                       |

| Write                          | Н   | Х    | Х    | Х   | Х           | NOP      | Row Active after tWR                          |

| Recovery *9                    | L   | Н    | Н    | Н   | Х           | NOP      | Row Active after t <sub>WR</sub>              |

|                                | L   | Н    | Н    | L   | Х           | BST      | ILLEGAL                                       |

|                                | L   | Н    | L    | Н   | BA, CA, A10 | RD/RDA   | ILLEGAL <sup>*2</sup>                         |

|                                | L   | Н    | L    | L   | BA, CA, A10 | WRT/WRTA | ILLEGAL <sup>*2</sup>                         |

|                                | L   | L    | Н    | Н   | BA, RA      | ACT      | ILLEGAL *6                                    |

|                                | L   | L    | Н    | L   | BA, A10     | PRE/PALL | ILLEGAL *8                                    |

|                                | L   | L    | L    | Н   | Х           | REF      | ILLEGAL                                       |

|                                | L   | L    | L    | L   | Х           | MRS/EMRS | ILLEGAL                                       |

# FUNCTION TRUTH TABLE (Table 1) (2/3)

| Current<br>State <sup>*1</sup> | /CS | /RAS | /CAS | /WE | ADDR        | Command  | Action                        |

|--------------------------------|-----|------|------|-----|-------------|----------|-------------------------------|

| Write                          | Н   | Х    | Х    | Х   | Х           | NOP      | enter Row Precharge after tWR |

| Recovery in                    | L   | Н    | Н    | Н   | Х           | NOP      | enter Row Precharge after tWR |

| Auto *0                        | L   | Н    | Н    | L   | Х           | BST      | ILLEGAL                       |

| Precharge *9                   | L   | Н    | L    | Н   | BA, CA, A10 | RD/RDA   | ILLEGAL *7                    |

|                                | L   | Н    | L    | L   | BA, CA, A10 | WRT/WRTA | ILLEGAL *7                    |

|                                | L   | L    | Н    | Н   | BA, RA      | ACT      | ILLEGAL <sup>*6</sup>         |

|                                | L   | L    | Н    | L   | BA, A10     | PRE/PALL | ILLEGAL *8                    |

|                                | L   | L    | L    | Н   | Х           | REF      | ILLEGAL                       |

|                                | L   | L    | L    | L   | Х           | MRS/EMRS | ILLEGAL                       |

| Auto                           | Н   | Х    | Х    | Х   | Х           | NOP      | Idle after t <sub>RCA</sub>   |

| Refresh                        | L   | Н    | Н    | Н   | Х           | NOP      | Idle after t <sub>RCA</sub>   |

|                                | L   | Н    | Н    | L   | Х           | BST      | ILLEGAL                       |

|                                | L   | Н    | L    | Н   | BA, CA, A10 | RD/RDA   | ILLEGAL                       |

|                                | L   | Н    | L    | L   | BA, CA, A10 | WRT/WRTA | ILLEGAL                       |

|                                | L   | L    | Н    | Н   | BA, RA      | ACT      | ILLEGAL                       |

|                                | L   | L    | Н    | L   | BA, A10     | PRE/PALL | ILLEGAL                       |

|                                | L   | L    | L    | Н   | Х           | REF      | ILLEGAL                       |

|                                | L   | L    | L    | L   | Х           | MRS/EMRS | ILLEGAL                       |

| Mode                           | Н   | Х    | Х    | Х   | Х           | NOP      | Idle after tMRD               |

| Register                       | L   | Н    | Н    | Н   | Х           | NOP      | Idle after tMRD               |

| Access                         | L   | Н    | Н    | L   | Х           | BST      | ILLEGAL                       |

|                                | L   | Н    | L    | Н   | BA, CA, A10 | RD/RDA   | ILLEGAL                       |

|                                | L   | Н    | L    | L   | BA, CA, A10 | WRT/WRTA | ILLEGAL                       |

|                                | L   | L    | Н    | Н   | BA, RA      | ACT      | ILLEGAL                       |

|                                | L   | L    | Н    | L   | BA, A10     | PRE/PALL | ILLEGAL                       |

|                                | L   | L    | L    | Н   | Х           | REF      | ILLEGAL                       |

|                                | L   | L    | L    | L   | Х           | MRS/EMRS | ILLEGAL                       |

#### FUNCTION TRUTH TABLE (Table 1) (3/3)

#### ABBREVIATIONS

ADDR = Address RA = Row Address NOP = No OPeration command BA = Bank Address CA = Column Address V = Value of Mode Register Set

\*Notes :1. All inputs are enabled when CKE is set high for at least 1 cycle prior to the inputs.

- 2. RD/RDA or WRT/WRTA command to same bank is forbidden. But RD/RDA or WRT/WRTA command to activated page in another bank is valid.

- 3. PRE command to another activated bank is valid. PALL command is valid to only activated bank.

- 4. Illegal if any bank is not idle.

- 5. RD/RDA or WRT/WRTA command to activated bank is valid after tRCD(min.) from ACT command.

- 6. Activate command to the same bank is forbidden. But activate command to another bank in idle state is valid.

- 7. RD/RDA or WRT/WRTA command to same bank is forbidden. But RD/RDA or WRT/WRTA command to activated page in another bank is valid.

- 8. PRE to same bank is forbidden. PRE to another bank must be issued after tRAS(min.). PALL command is forbidden.

- 9. Write recovery states means a period from last data to the time that tWR(min.) passed.

# **FUNCTION TRUTH TABLE for CKE (Table 2)**

| FUNCTION IKC    |     | DLE IU | UNE | able | <u> </u> |     |        |                                        |

|-----------------|-----|--------|-----|------|----------|-----|--------|----------------------------------------|

| Current State   | CKE | CKE    | /CS | /RAS | /CAS     | /WE | ADDR   | Action                                 |

| <u>n-1</u>      | n-1 | n      | n   | n    | n        | n   | n      |                                        |

| All Banks Idle  | Н   | Н      | Х   | Х    | Х        | Х   | Х      | Refer to Table 1                       |

| (ABI)           | Н   | L      | Н   | Х    | Х        | Х   | Х      | Enter Power Down                       |

|                 | Н   | L      | L   | Н    | Н        | Н   | Х      | Enter Power Down                       |

|                 | Н   | L      | L   | Н    | Н        | L   | Х      | ILLEGAL                                |

|                 | Н   | L      | L   | Н    | L        | Х   | Х      | ILLEGAL                                |

|                 | Н   | L      | L   | L    | Н        | Н   | BA, RA | Enter Active Power Down after Activate |

|                 | Н   | L      | L   | L    | Н        | L   | Х      | ILLEGAL                                |

|                 | Н   | L      | L   | L    | L        | Н   | Х      | Enter Self Refresh *2                  |

|                 | Н   | L      | L   | L    | L        | L   | BA, V  | Enter Power Down after MRS             |

|                 | L   | х      | Х   | Х    | Х        | Х   | Х      | INVALID                                |

| Self Refresh    | Н   | Х      | Х   | Х    | Х        | Х   | Х      | INVALID                                |

|                 | L   | Н      | Н   | Х    | Х        | Х   | Х      | Exit Self Refresh> ABI *3              |

|                 | L   | Н      | L   | Н    | Н        | Н   | Х      | Exit Self Refresh> ABI *3              |

|                 | L   | Н      | L   | Н    | Н        | L   | Х      | ILLEGAL                                |

|                 | L   | Н      | L   | Н    | L        | Х   | Х      | ILLEGAL                                |

|                 | L   | Н      | L   | L    | Х        | Х   | Х      | ILLEGAL                                |

|                 | L   | L      | Х   | Х    | Х        | Х   | Х      | NOP (Maintain Self Refresh)            |

| Power Down      | Н   | Х      | Х   | Х    | Х        | Х   | Х      | INVALID                                |

|                 | L   | Н      | Х   | Х    | Х        | Х   | Х      | Exit Power Down> ABI *4                |

|                 | L   | L      | Х   | Х    | Х        | Х   | Х      | NOP (Continue Power Down)              |

| Active Power    | Н   | Х      | Х   | Х    | Х        | Х   | Х      | INVALID                                |

| Down            | L   | Н      | Х   | Х    | Х        | Х   | Х      | Exit Active Power Down> Row Active *4  |

|                 | L   | L      | Х   | Х    | Х        | Х   | Х      | NOP (Continue Active Power Down)       |

| Row Active      | Н   | Н      | Х   | Х    | Х        | Х   | Х      | Refer to Table 1                       |

|                 | Н   | L      | Н   | Х    | Х        | Х   | Х      | Enter Active Power Down                |

|                 | Н   | L      | L   | Н    | Н        | Н   | Х      | Enter Active Power Down                |

|                 | Н   | L      | L   | Н    | Н        | L   | Х      | ILLEGAL                                |

|                 | Н   | L      | L   | Н    | L        | Х   | Х      | Clock Suspension (Refer to Table 1)    |

|                 | Н   | L      | L   | L    | Н        | Х   | Х      | Clock Suspension (Refer to Table 1)    |

|                 | Н   | L      | L   | L    | L        | Х   | Х      | ILLEGAL                                |

|                 | L   | Х      | Х   | Х    | Х        | Х   | Х      | INVALID                                |

| Any State Other | Н   | Н      | Х   | Х    | Х        | Х   | Х      | Refer to Table 1                       |

| than Listed     | Н   | L      | Х   | Х    | Х        | Х   | Х      | Begin Clock Suspend Next Cycle         |

| Above           | L   | Н      | Х   | Х    | Х        | Х   | Х      | Enable Clock of Next Cycle             |

|                 | L   | L      | Х   | Х    | Х        | Х   | Х      | Continue Clock Suspension              |

| ABBREVIATION    | c   |        | -   |      |          | •   |        | •                                      |

# ABBREVIATIONS

ADDR = Address RA = Row Address V = Value of Mode Register Set BA = Bank Address ABI = All Banks Idle NOP = No OPeration command

\*Notes :1. Deep Power Down can be entered only when all the banks are in an idle state.

2. Self Refresh can be entered only when all the banks are in an idle state.

- 3. tRCA must be set after exit self refresh.

- 4. New command is enabled in the next clock.

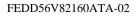

# SIMPLIFIED STATE DIAGRAM

# TIMING CHART

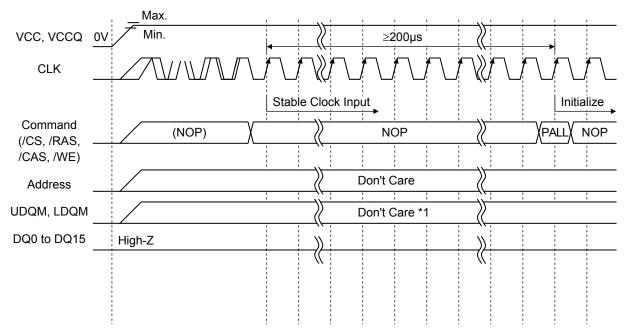

**Power on Sequence**

Notes : 1. It is advisable that UDQM and LDQM are set to high for set DQ to high impedance during power on sequence.

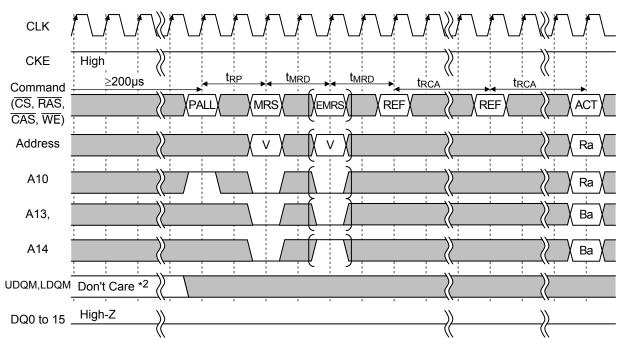

#### Initialization

- Notes : 1. V = Value of mode register, Rx = Row Address, Bx = Bank Address  $\square =$  NOP command or High or Low

- 2. It is advisable that UDQM to LDQM are set to be high level for setting DQ to high impedance during power on sequence.

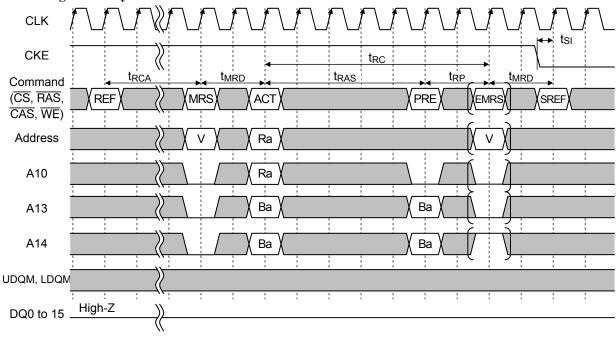

#### Mode Register Set cycle

Notes : 1. V = Value of mode register, Rx = Row Address, Bx = Bank Address= NOP command or High or Low

#### Burst Write Cycle (BL=4, WM=Burst)

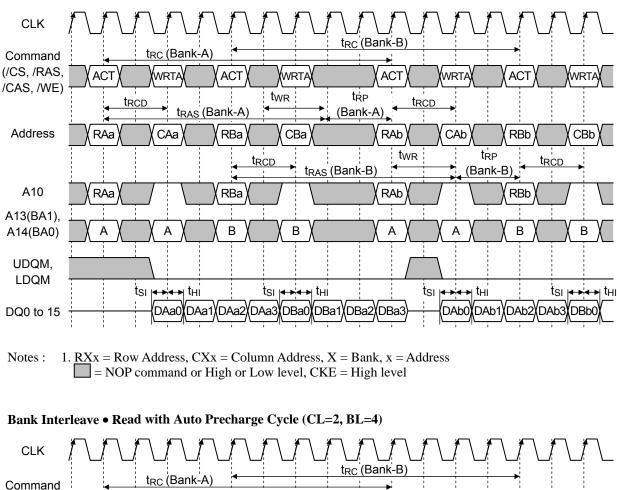

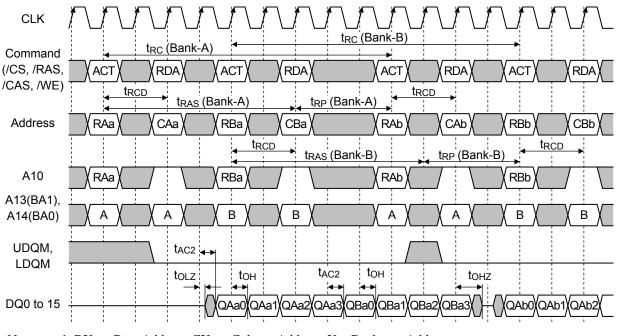

# Bank Interleave • Write with Auto Precharge Cycle (CL=2, BL=4, WM=Burst)

Notes : 1. RXx = Row Address, CXx = Column Address, X = Bank, x = Address $\blacksquare = NOP$  command or High or Low level, CKE = High level

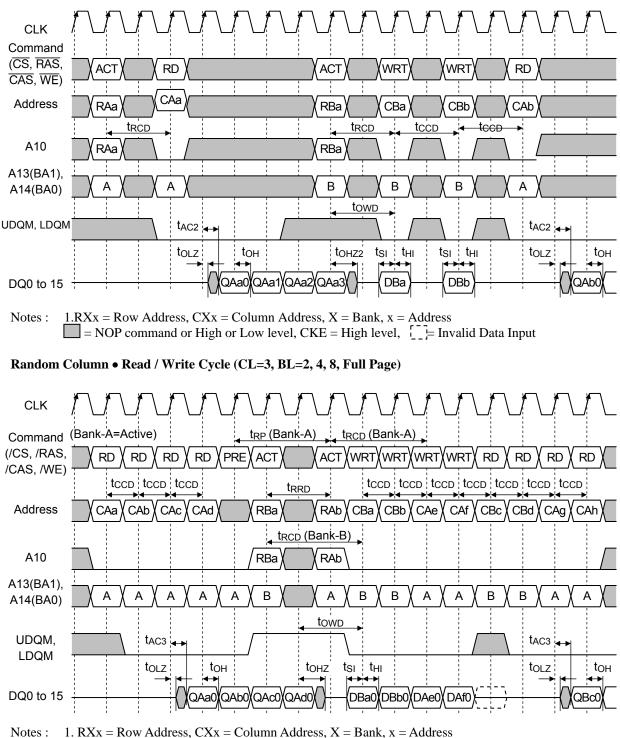

# Burst Read • Single Write Cycle (CL=2, BL=4,WM=Single)

## Byte Read / Byte Write Cycle (CL=2, BL=8, WM=Burst)

Notes : 1. Cx = Column Address, Bx = Bank Address = NOP command or High or Low level, CKE = High level, [] = Invalid Data Input

Clock Suspend • Read / Write Cycle (CL=3, BL=4, WM=Burst)

Notes : 1. Cx = Column Address, Bx = Bank Address $\square = NOP command or High or Low level, CKE = High level, [] = Invalid Data Input$

((

ACT

Ra

Ra

Ba

**t**RCA

ł

ł

-

-

1

1

ł

ł

High-Z

1

-

# Notes : 1. Rx = Row Address, Bx = Bank Address $\square = NOP$ command or High or Low level, CKE = High level, $\boxed{\ } = Invalid$ Data Input

1

-

1

-

ł

1

1

ł

# Self Refresh Cycle

A13(BA1),

A14(BA0)

UDQM, LDQM

DQ0 to15

# PACKAGE DIMENSIONS

Notes for Mounting the Surface Mount Type Package

The surface mount type packages are very susceptible to heat in reflow mounting and humidity absorbed in storage. Therefore, before you perform reflow mounting, contact ROHM's responsible sales person for the product name, package name, pin number, package code and desired mounting conditions (reflow method, temperature and times).

# **REVISION HISTORY**

| Document<br>No.    | Date          | Page           |                 |                                                      |

|--------------------|---------------|----------------|-----------------|------------------------------------------------------|

|                    |               | Previous       | Current         | Description                                          |

|                    |               | Edition        | Edition         |                                                      |

| FEDD56V82160ATA-01 | Sep. 30, 2013 | -              | -               | Final edition 1                                      |

| FEDD56V82160ATA-02 | Nov.29, 2013  | 9,10,<br>28,34 | 9, 10,<br>28,34 | Corrected BA function at EMRS chart.<br>A13=0, A14=1 |

|                    |               |                |                 |                                                      |

|                    |               |                |                 |                                                      |

|                    |               |                |                 |                                                      |

|                    |               |                |                 |                                                      |

|                    |               |                |                 |                                                      |

|                    |               |                |                 |                                                      |

|                    |               |                |                 |                                                      |

|                    |               |                |                 |                                                      |

|                    |               |                |                 |                                                      |

|                    |               |                |                 |                                                      |

|                    |               |                |                 |                                                      |

|                    |               |                |                 |                                                      |

#### NOTICE

No copying or reproduction of this document, in part or in whole, is permitted without the consent of LAPIS Semiconductor Co., Ltd.

The content specified herein is subject to change for improvement without notice.

Examples of application circuits, circuit constants and any other information contained herein illustrate the standard usage and operations of the Products. The peripheral conditions must be taken into account when designing circuits for mass production.

Great care was taken in ensuring the accuracy of the information specified in this document. However, should you incur any damage arising from any inaccuracy or misprint of such information, LAPIS Semiconductor shall bear no responsibility for such damage.