# **MCP2510**

# Stand-Alone CAN Controller with SPI<sup>®</sup> Interface

# FEATURES

- Implements Full CAN V2.0A and V2.0B at 1 Mb/s

- 0 8 byte message length

- Standard and extended data frames

- Programmable bit rate up to 1 Mb/s

- Support for remote frames

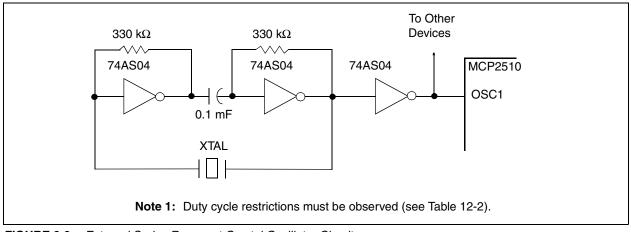

- Two receive buffers with prioritized message storage

- Six full acceptance filters

- Two full acceptance filter masks

- Three transmit buffers with prioritization and abort features

- Loop-back mode for self test operation

- Hardware Features

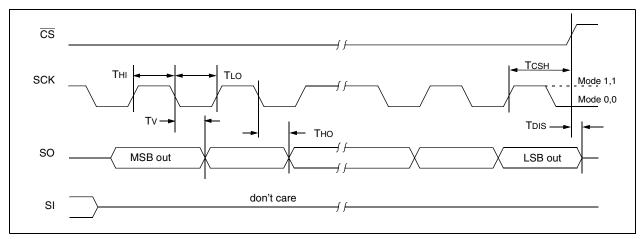

- High Speed SPI Interface (5 MHz at 4.5V I temp)

- Supports SPI modes 0,0 and 1,1

- Clock out pin with programmable prescaler

- Interrupt output pin with selectable enables

- 'Buffer full' output pins configureable as interrupt pins for each receive buffer or as general purpose digital outputs

- 'Request to Send' input pins configureable as control pins to request immediate message transmission for each transmit buffer or as general purpose digital inputs

- Low Power Sleep mode

- Low power CMOS technology

- Operates from 3.0V to 5.5V

- 5 mA active current typical

- 10 μA standby current typical at 5.5V

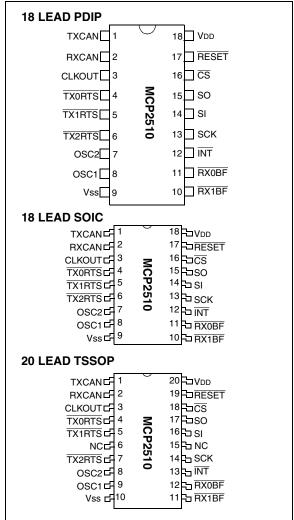

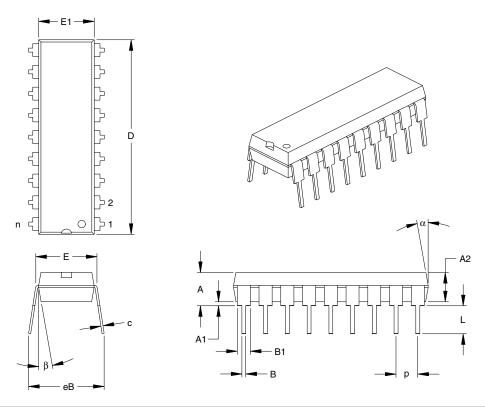

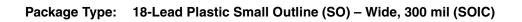

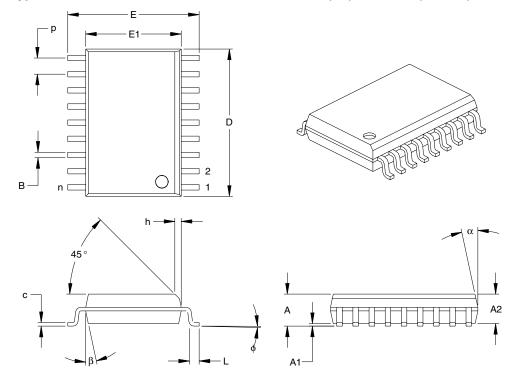

- 18-pin PDIP/SOIC and 20-pin TSSOP packages

- Temperature ranges supported:

| <ul> <li>Industrial (I):</li> </ul> | -40°C to +85°C |

|-------------------------------------|----------------|

|-------------------------------------|----------------|

- Extended (E): -40°C to +125°C

# DESCRIPTION

The Microchip Technology Inc. MCP2510 is a Full Controller Area Network (CAN) protocol controller implementing CAN specification V2.0 A/B. It supports CAN 1.2, CAN 2.0A, CAN 2.0B Passive, and CAN 2.0B Active versions of the protocol, and is capable of transmitting and receiving standard and extended messages. It is also capable of both acceptance filtering and message management. It includes three transmit buffers and two receive buffers that reduce the amount of microcontroller (MCU) management required. The MCU communication is implemented via an industry standard Serial Peripheral Interface (SPI) with data rates up to 5Mb/s.

# PACKAGE TYPES

SPI is a registered trademark of Motorola Inc.

#### **Table of Contents**

| 1.0         | Device Functionality            |

|-------------|---------------------------------|

| 2.0         | Can Message Frames              |

| 3.0         | Message Transmission            |

| 4.0         | Message Reception               |

| 5.0         | Bit Timing                      |

| 6.0         | Error Detection                 |

| 7.0         | Interrupts                      |

| 8.0         | Oscillator                      |

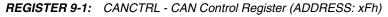

| 9.0         | Modes of Operation              |

| 10.0        | Register Map                    |

| 11.0        | SPI Interface                   |

| 12.0        | Electrical Characteristics      |

| 13.0        | Packaging Information           |

| On-Line S   | Support                         |

| Reader R    | esponse                         |

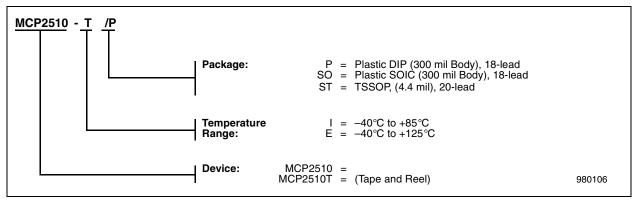

| MCP2510     | ) Product Identification System |

| Index       |                                 |

| List Of Fig | gures                           |

| List Of Ta  | bles                            |

| List Of Re  | agisters                        |

| Worldwide   | e Sales and Service             |

#### To Our Valued Customers

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please check our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number. e.g., DS30000A is version A of document DS30000.

#### Errata

An errata sheet may exist for current devices, describing minor operational differences (from the data sheet) and recommended workarounds. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

- The Microchip Corporate Literature Center; U.S. FAX: (480) 786-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### Corrections to this Data Sheet

We constantly strive to improve the quality of all our products and documentation. We have spent a great deal of time to ensure that this document is correct. However, we realize that we may have missed a few things. If you find any information that is missing or appears in error, please:

• Fill out and mail in the reader response form in the back of this data sheet.

• E-mail us at webmaster@microchip.com.

We appreciate your assistance in making this a better document.

# 1.0 DEVICE FUNCTIONALITY

#### 1.1 <u>Overview</u>

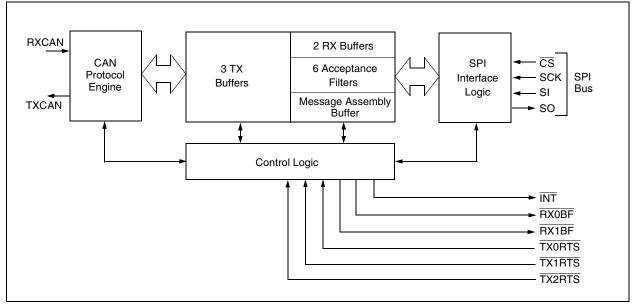

The MCP2510 is a stand-alone CAN controller developed to simplify applications that require interfacing with a CAN bus. A simple block diagram of the MCP2510 is shown in Figure 1-1. The device consists of three main blocks:

- 1. the CAN protocol engine,

- the control logic and SRAM registers that are used to configure the device and its operation, and

- 3. the SPI protocol block.

A typical system implementation using the device is shown in Figure 1-2.

The CAN protocol engine handles all functions for receiving and transmitting messages on the bus. Messages are transmitted by first loading the appropriate message buffer and control registers. Transmission is initiated by using control register bits, via the SPI interface, or by using the transmit enable pins. Status and errors can be checked by reading the appropriate registers. Any message detected on the CAN bus is checked for errors and then matched against the user defined filters to see if it should be moved into one of the two receive buffers.

The MCU interfaces to the device via the SPI interface. Writing to and reading from all registers is done using standard SPI read and write commands.

Interrupt pins are provided to allow greater system flexibility. There is one multi-purpose interrupt pin as well as specific interrupt pins for each of the receive registers that can be used to indicate when a valid message has been received and loaded into one of the receive buffers. Use of the specific interrupt pins is optional, and the general purpose interrupt pin as well as status registers (accessed via the SPI interface) can also be used to determine when a valid message has been received.

There are also three pins available to initiate immediate transmission of a message that has been loaded into one of the three transmit registers. Use of these pins is optional and initiating message transmission can also be done by utilizing control registers accessed via the SPI interface.

Table 1-1 gives a complete list of all of the pins on the MCP2510.

FIGURE 1-1: Block Diagram

FIGURE 1-2: Typical System Implementation

| Name            | DIP/<br>SOIC<br>Pin # | TSSOP<br>Pin # | I/O/P<br>Type | Description                                                               |

|-----------------|-----------------------|----------------|---------------|---------------------------------------------------------------------------|

| TXCAN           | 1                     | 1              | 0             | Transmit output pin to CAN bus                                            |

| RXCAN           | 2                     | 2              | I             | Receive input pin from CAN bus                                            |

| CLKOUT          | 3                     | 3              | 0             | Clock output pin with programmable prescaler                              |

| TXORTS          | 4                     | 4              | I             | Transmit buffer TXB0 request to send or general purpose digital input100K |

| TX1RTS          | 5                     | 5              | I             | Transmit buffer TXB1 request to send or general purpose digital input100K |

| TX2RTS          | 6                     | 7              | I             | Transmit buffer TXB2 request to send or general purpose digital input100K |

| OSC2            | 7                     | 8              | 0             | Oscillator output                                                         |

| OSC1            | 8                     | 9              | Ι             | Oscillator input                                                          |

| V <sub>SS</sub> | 9                     | 10             | Р             | Ground reference for logic and I/O pins                                   |

| RX1BF           | 10                    | 11             | 0             | Receive buffer RXB1 interrupt pin or general purpose digital output       |

| RX0BF           | 11                    | 12             | 0             | Receive buffer RXB0 interrupt pin or general purpose digital output       |

| INT             | 12                    | 13             | 0             | Interrupt output pin                                                      |

| SCK             | 13                    | 14             | I             | Clock input pin for SPI interface                                         |

| SI              | 14                    | 16             | I             | Data input pin for SPI interface                                          |

| SO              | 15                    | 17             | 0             | Data output pin for SPI interface                                         |

| CS              | 16                    | 18             | I             | Chip select input pin for SPI interface                                   |

| RESET           | 17                    | 19             | I             | Active low device reset input                                             |

| V <sub>DD</sub> | 18                    | 20             | Р             | Positive supply for logic and I/O pins                                    |

| NC              | —                     | 6,15           | _             | No internal connection                                                    |

Note: Type Identification: I=Input; O=Output; P=Power

**TABLE 1-1:**Pin Descriptions

#### 1.2 <u>Transmit/Receive Buffers</u>

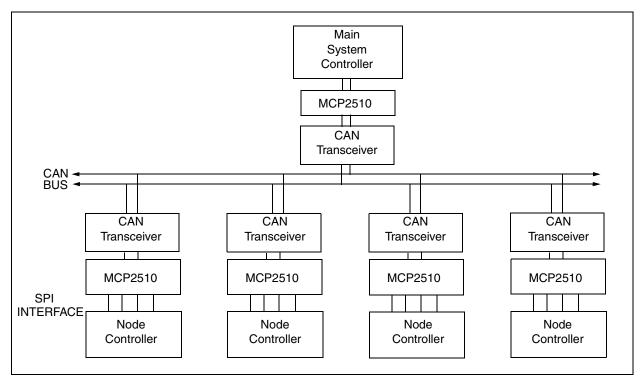

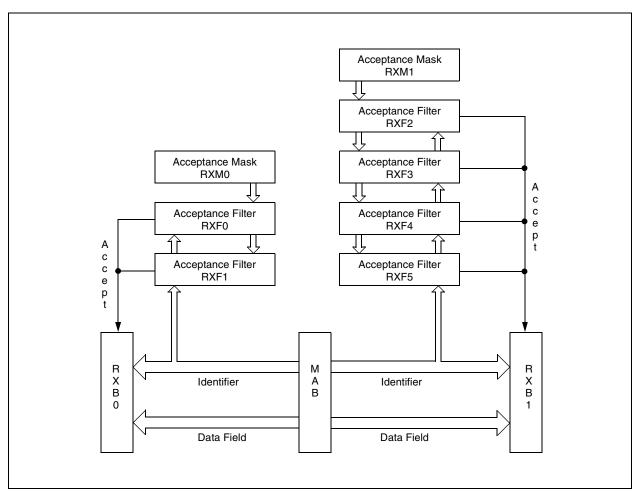

The MCP2510 has three transmit and two receive buffers, two acceptance masks (one for each receive buffer), and a total of six acceptance filters. Figure 1-3 is a block diagram of these buffers and their connection to the protocol engine.

FIGURE 1-3: CAN Buffers and Protocol Engine Block Diagram

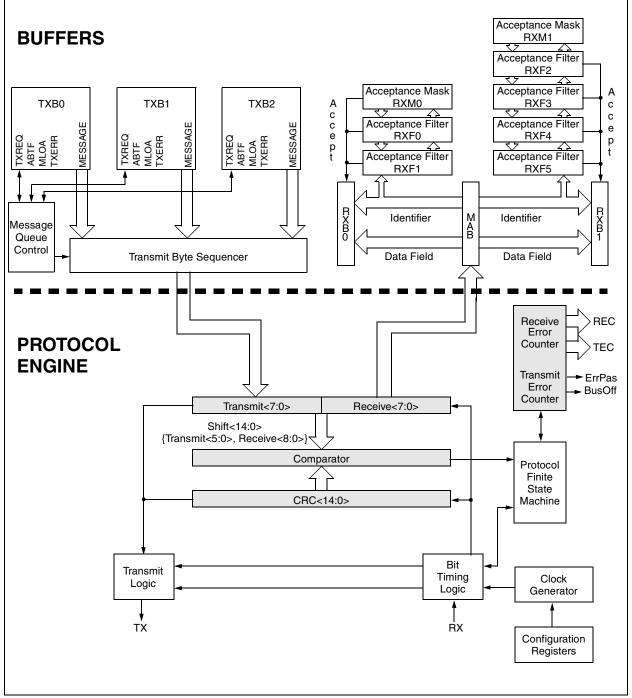

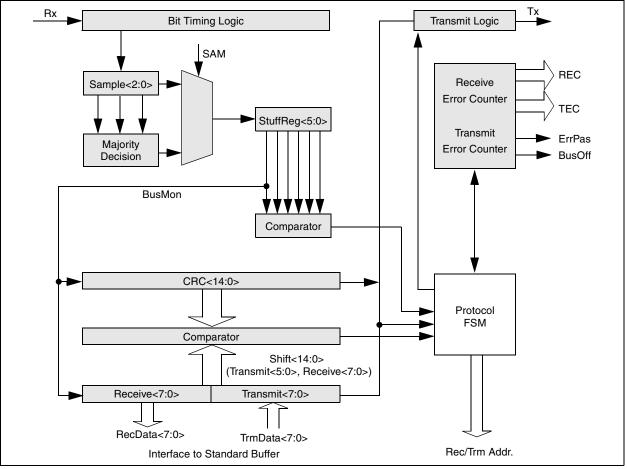

#### 1.3 CAN Protocol Engine

The CAN protocol engine combines several functional blocks, shown in Figure 1-4. These blocks and their functions are described below.

#### 1.4 Protocol Finite State Machine

The heart of the engine is the Finite State Machine (FSM). This state machine sequences through messages on a bit by bit basis, changing states as the fields of the various frame types are transmitted or received. The FSM is a sequencer controlling the sequential data stream between the TX/RX Shift Register, the CRC Register, and the bus line. The FSM also controls the Error Management Logic (EML) and the parallel data stream between the TX/RX Shift Registers and the buffers. The FSM insures that the processes of reception, arbitration, transmission, and error signaling are performed according to the CAN protocol. The automatic retransmission of messages on the bus line is also handled by the FSM.

#### 1.5 Cyclic Redundancy Check

The Cyclic Redundancy Check Register generates the Cyclic Redundancy Check (CRC) code which is transmitted after either the Control Field (for messages with 0 data bytes) or the Data Field, and is used to check the CRC field of incoming messages.

#### 1.6 Error Management Logic

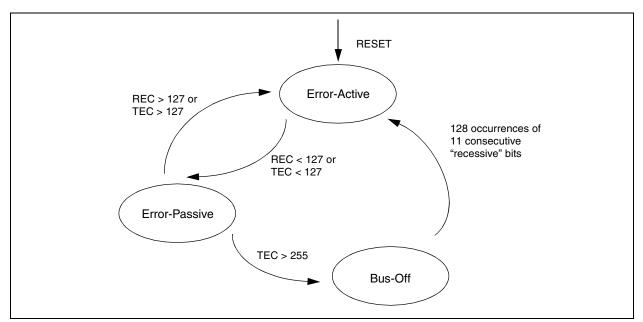

The Error Management Logic is responsible for the fault confinement of the CAN device. Its two counters, the Receive Error Counter (REC) and the Transmit Error Counter (TEC), are incremented and decremented by commands from the Bit Stream Processor. According to the values of the error counters, the CAN controller is set into the states error-active, error-passive or bus-off.

#### 1.7 <u>Bit Timing Logic</u>

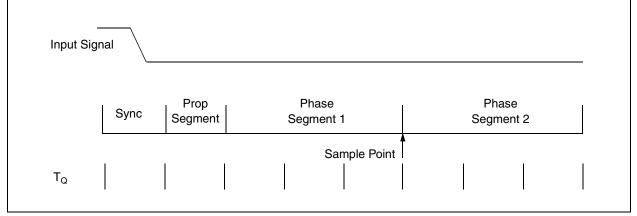

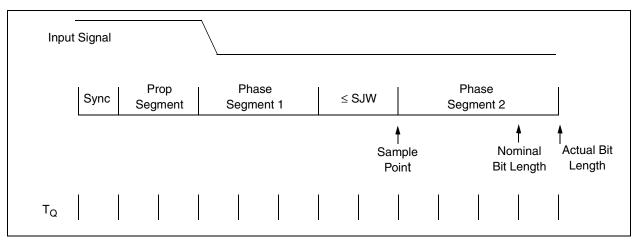

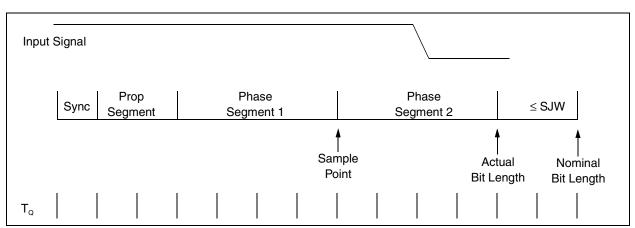

The Bit Timing Logic (BTL) monitors the bus line input and handles the bus related bit timing according to the CAN protocol. The BTL synchronizes on a recessive to dominant bus transition at Start of Frame (hard synchronization) and on any further recessive to dominant bus line transition if the CAN controller itself does not transmit a dominant bit (resynchronization). The BTL also provides programmable time segments to compensate for the propagation delay time, phase shifts, and to define the position of the Sample Point within the bit time. The programming of the BTL depends upon the baud rate and external physical delay times.

FIGURE 1-4: CAN Protocol Engine Block Diagram

# 2.0 CAN MESSAGE FRAMES

The MCP2510 supports Standard Data Frames, Extended Data Frames, and Remote Frames (Standard and Extended) as defined in the CAN 2.0B specification.

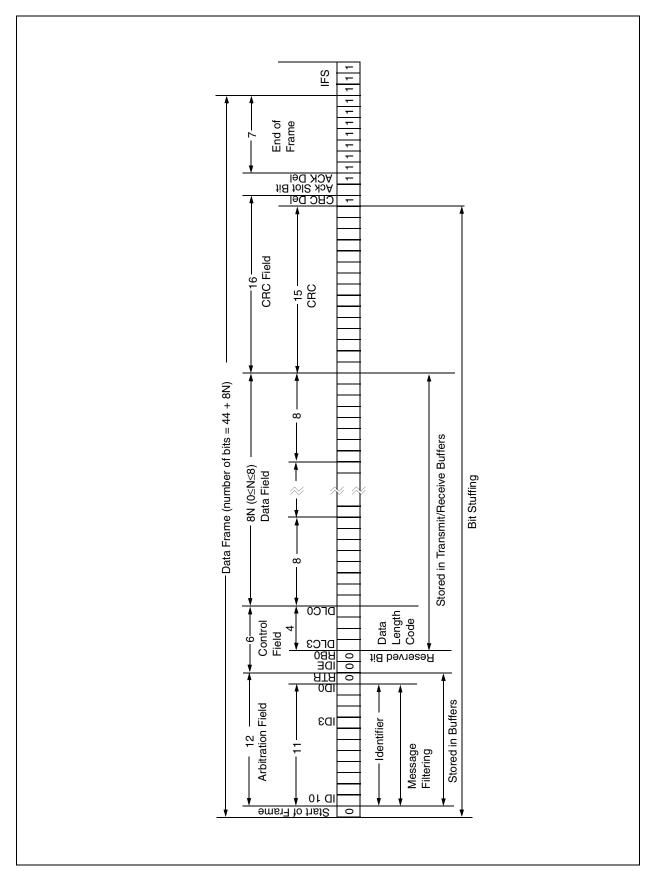

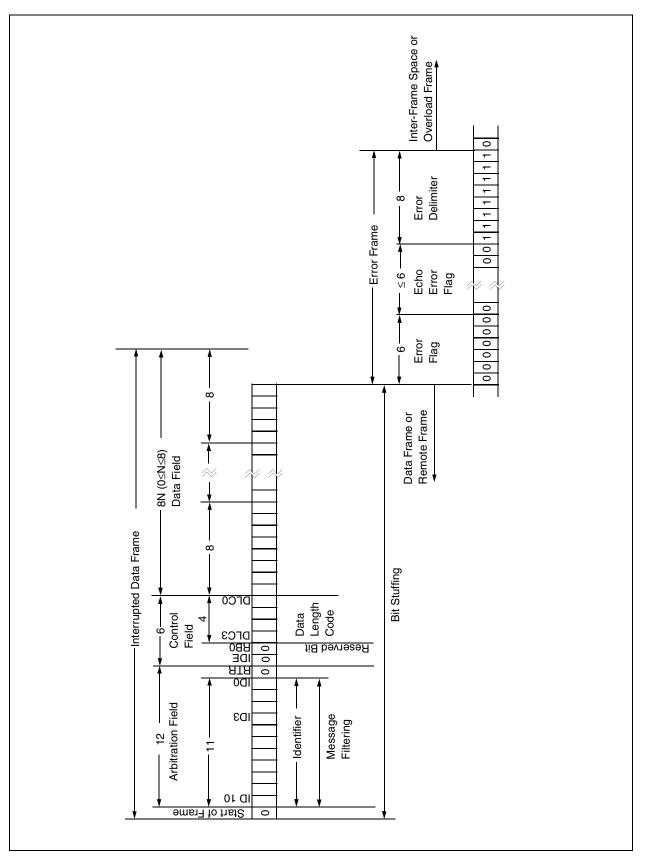

#### 2.1 Standard Data Frame

The CAN Standard Data Frame is shown in Figure 2-1. In common with all other frames, the frame begins with a Start Of Frame (SOF) bit, which is of the dominant state, which allows hard synchronization of all nodes.

The SOF is followed by the arbitration field, consisting of 12 bits; the 11-bit Identifier and the Remote Transmission Request (RTR) bit. The RTR bit is used to distinguish a data frame (RTR bit dominant) from a remote frame (RTR bit recessive).

Following the arbitration field is the control field, consisting of six bits. The first bit of this field is the Identifier Extension (IDE) bit which must be dominant to specify a standard frame. The following bit, Reserved Bit Zero (RB0), is reserved and is defined to be a dominant bit by the can protocol. the remaining four bits of the control field are the Data Length Code (DLC) which specifies the number of bytes of data contained in the message.

After the control field is the data field, which contains any data bytes that are being sent, and is of the length defined by the DLC above (0-8 bytes).

The Cyclic Redundancy Check (CRC) Field follows the data field and is used to detect transmission errors. The CRC Field consists of a 15-bit CRC sequence, followed by the recessive CRC Delimiter bit.

The final field is the two-bit acknowledge field. During the ACK Slot bit, the transmitting node sends out a recessive bit. Any node that has received an error free frame acknowledges the correct reception of the frame by sending back a dominant bit (regardless of whether the node is configured to accept that specific message or not). The recessive acknowledge delimiter completes the acknowledge field and may not be overwritten by a dominant bit.

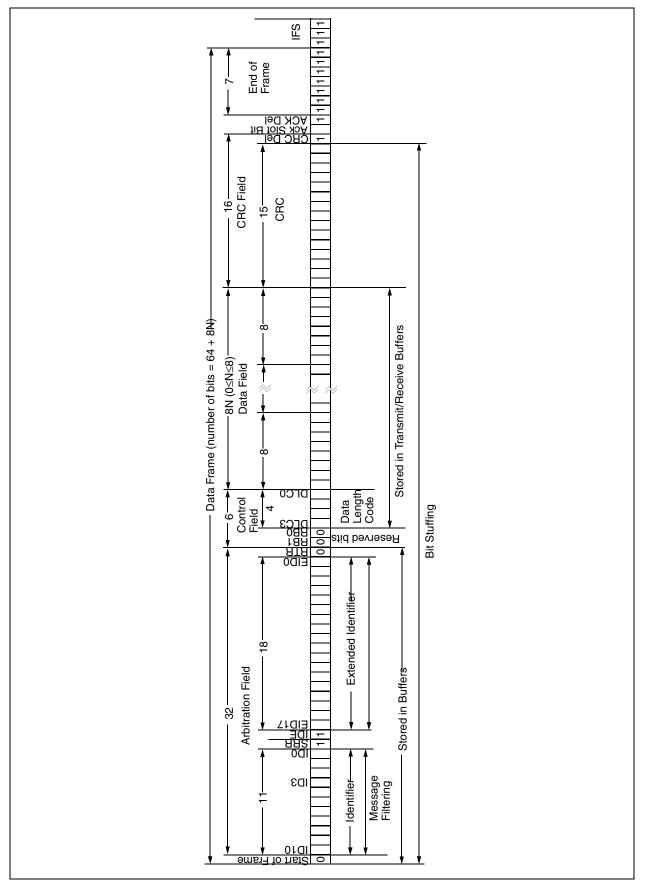

### 2.2 Extended Data Frame

In the Extended CAN Data Frame, shown in Figure 2-2, the SOF bit is followed by the arbitration field which consists of 32 bits. The first 11 bits are the most significant bits (Base-ID) of the 29-bit identifier. These 11 bits are followed by the Substitute Remote Request (SRR) bit which is defined to be recessive. The SRR bit is followed by the IDE bit which is recessive to denote an extended CAN frame.

It should be noted that if arbitration remains unresolved after transmission of the first 11 bits of the identifier, and one of the nodes involved in the arbitration is sending a standard CAN frame (11-bit identifier), then the standard CAN frame will win arbitration due to the assertion of a dominant IDE bit. Also, the SRR bit in an extended CAN frame must be recessive to allow the assertion of a dominant RTR bit by a node that is sending a standard CAN remote frame.

The SRR and IDE bits are followed by the remaining 18 bits of the identifier (Extended ID) and the remote transmission request bit.

To enable standard and extended frames to be sent across a shared network, it is necessary to split the 29-bit extended message identifier into 11-bit (most significant) and 18-bit (least significant) sections. This split ensures that the IDE bit can remain at the same bit position in both standard and extended frames.

Following the arbitration field is the six-bit control field. the first two bits of this field are reserved and must be dominant. the remaining four bits of the control field are the Data Length Code (DLC) which specifies the number of data bytes contained in the message.

The remaining portion of the frame (data field, CRC field, acknowledge field, end of frame and Intermission) is constructed in the same way as for a standard data frame (see Section 2.1).

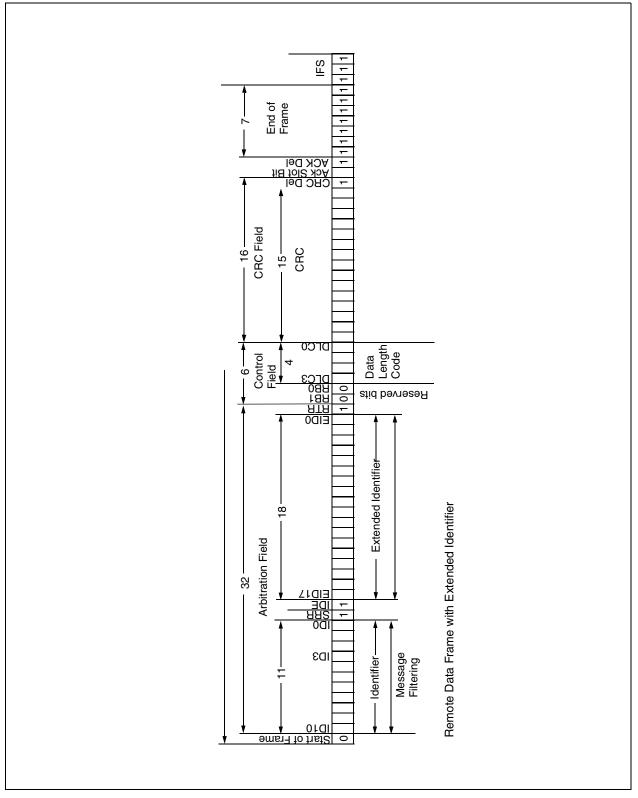

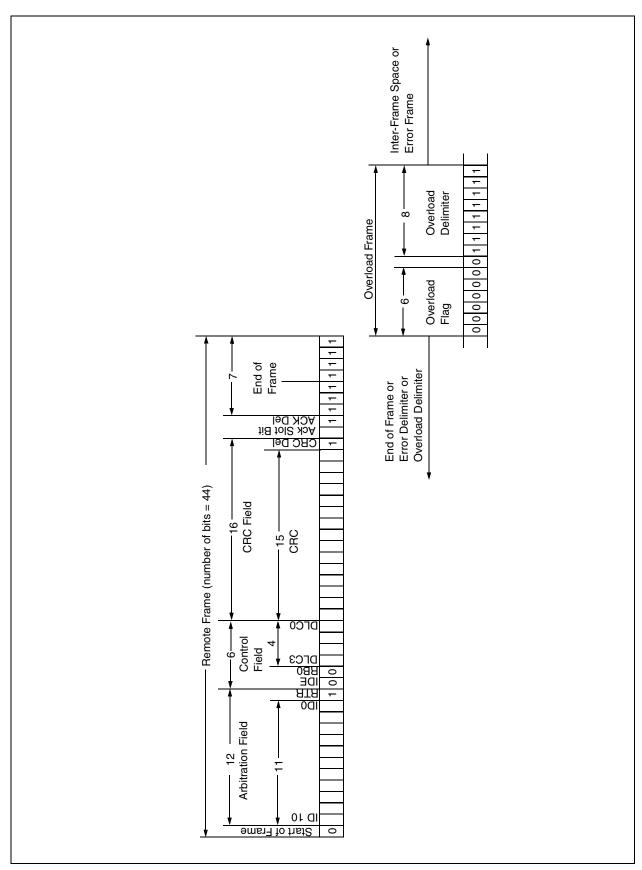

#### 2.3 <u>Remote Frame</u>

Normally, data transmission is performed on an autonomous basis by the data source node (e.g. a sensor sending out a data frame). It is possible, however, for a destination node to request data from the source. To accomplish this, the destination node sends a remote frame with an identifier that matches the identifier of the required data frame. The appropriate data source node will then send a data frame in response to the remote frame request.

There are two differences between a remote frame (shown in Figure 2-3) and a data frame. First, the RTR bit is at the recessive state, and second, there is no data field. In the event of a data frame and a remote frame with the same identifier being transmitted at the same time, the data frame wins arbitration due to the dominant RTR bit following the identifier. In this way, the node that transmitted the remote frame receives the desired data immediately.

#### 2.4 Error Frame

An Error Frame is generated by any node that detects a bus error. An error frame, shown in Figure 2-4, consists of two fields, an error flag field followed by an error delimiter field. There are two types of error flag fields. Which type of error flag field is sent depends upon the error status of the node that detects and generates the error flag field.

If an error-active node detects a bus error then the node interrupts transmission of the current message by generating an active error flag. The active error flag is composed of six consecutive dominant bits. This bit sequence actively violates the bit stuffing rule. All other stations recognize the resulting bit stuffing error and in turn generate error frames themselves, called error echo flags. The error flag field, therefore, consists of between six and twelve consecutive dominant bits (generated by one or more nodes). The error delimiter field completes the error frame. After completion of the error frame, bus activity returns to normal and the interrupted node attempts to resend the aborted message.

If an error-passive node detects a bus error then the node transmits an error-passive flag followed by the error delimiter field. The error-passive flag consists of six consecutive recessive bits, and the error frame for an error-passive node consists of 14 recessive bits. From this, it follows that unless the bus error is detected by the node that is actually transmitting, the transmission of an error frame by an error-passive node will not affect any other node on the network. If the transmitting node generates an error-passive flag then this will cause other nodes to generate error frames due to the resulting bit stuffing violation. After transmission of an error frame, an error-passive node must wait for six consecutive recessive bits on the bus before attempting to rejoin bus communications.

The error delimiter consists of eight recessive bits and allows the bus nodes to restart bus communications cleanly after an error has occurred.

#### 2.5 Overload Frame

An Overload Frame, shown in Figure 2-5, has the same format as an active error frame. An overload frame, however can only be generated during an Interframe space. In this way an overload frame can be differentiated from an error frame (an error frame is sent during the transmission of a message). The overload frame consists of two fields, an overload flag followed by an overload delimiter. The overload flag consists of six dominant bits followed by overload flags generated by other nodes (and, as for an active error flag, giving a maximum of twelve dominant bits). The overload delimiter consists of eight recessive bits. An overload frame can be generated by a node as a result of two conditions. First, the node detects a dominant bit during the interframe space which is an illegal condition. Second, due to internal conditions the node is not yet able to start reception of the next message. A node may generate a maximum of two sequential overload frames to delay the start of the next message.

#### 2.6 Interframe Space

The Interframe Space separates a preceeding frame (of any type) from a subsequent data or remote frame. The interframe space is composed of at least three recessive bits called the Intermission. This is provided to allow nodes time for internal processing before the start of the next message frame. After the intermission, the bus line remains in the recessive state (bus idle) until the next transmission starts.

FIGURE 2-1: Standard Data Frame

© 1999 Microchip Technology Inc.

FIGURE 2-2: Extended Data Frame

FIGURE 2-3: Remote Data Frame

FIGURE 2-4: Error Frame

FIGURE 2-5: Overload Frame

NOTES:

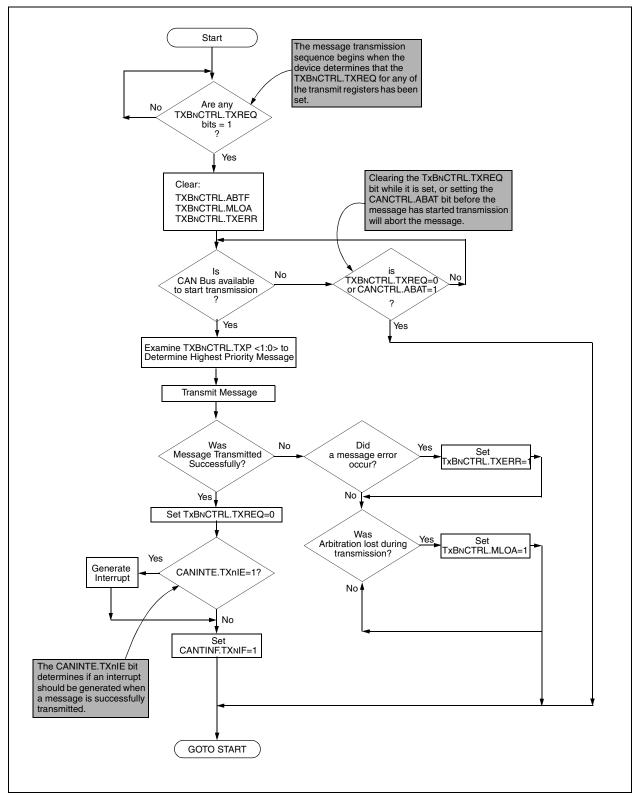

# 3.0 MESSAGE TRANSMISSION

#### 3.1 <u>Transmit Buffers</u>

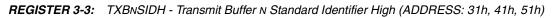

The MCP2510 implements three Transmit Buffers. Each of these buffers occupies 14 bytes of SRAM and are mapped into the device memory maps. The first byte, TXBNCTRL, is a control register associated with the message buffer. The information in this register determines the conditions under which the message will be transmitted and indicates the status of the message transmission. (see Register 3-2). Five bytes are used to hold the standard and extended identifiers and other message arbitration information (see Register 3-3 through Register 3-8). The last eight bytes are for the eight possible data bytes of the message to be transmitted (see Register 3-8).

For the MCU to have write access to the message buffer, the TXBNCTRL.TXREQ bit must be clear, indicating that the message buffer is clear of any pending message to be transmitted. At a minimum, the TXBNSIDH, TXBNSIDL, and TXBNDLC registers must be loaded. If data bytes are present in the message, the TXBNDm registers must also be loaded. If the message is to use extended identifiers, the TXBNEIDm registers must also be loaded and the TXBNSIDL.EXIDE bit set.

Prior to sending the message, the MCU must initialize the CANINTE.TXINE bit to enable or disable the generation of an interrupt when the message is sent. The MCU must also initialize the TXBNCTRL.TXP priority bits (see Section 3.2).

### 3.2 <u>Transmit Priority</u>

Transmit priority is a prioritization, within the MCP2510, of the pending transmittable messages. This is independent from, and not necessarily related to, any prioritization implicit in the message arbitration scheme built into the CAN protocol. Prior to sending the SOF, the priority of all buffers that are queued for transmission is compared. The transmit buffer with the highest priority will be sent first. For example, if transmit buffer 0 has a higher priority setting than transmit buffer 1, buffer 0 will be sent first. If two buffers have the same priority setting, the buffer with the highest buffer number will be sent first. For example, if transmit buffer 1 has the same priority setting as transmit buffer 0, buffer 1 will be sent first. There are four levels of transmit priority. If TXBNCTRL.TXP<1:0> for a particular message buffer is set to 11, that buffer has the highest possible priority. If TXBNC-TRL.TXP<1:0> for a particular message buffer is 00, that buffer has the lowest possible priority.

#### 3.3 Initiating Transmission

To initiate message transmission the TXBNCTRL.TXREQ bit must be set for each buffer to be transmitted. This can be done by writing to the register via the SPI interface or by setting the TXNRTS pin low for the particular transmit buffer(s) that are to be transmitted. If transmission is initiated via the SPI interface, the TXREQ bit can be set at the same time as the TXP priority bits. When TXBNCTRL.TXREQ is set, the TXBNCTRL.ABTF, TXBNCTRL.MLOA and TXBNCTRL.TXERR bits will be cleared.

Setting the TXBNCTRL.TXREQ bit does not initiate a message transmission, it merely flags a message buffer as ready for transmission. Transmission will start when the device detects that the bus is available. The device will then begin transmission of the highest priority message that is ready.

When the transmission has completed successfully the TXBNCTRL.TXREQ bit will be cleared, the CAN-INTF.TXNIF bit will be set, and an interrupt will be generated if the CANINTE.TXNIE bit is set.

If the message transmission fails, the TXBNCTRL.TXREQ will remain set indicating that the message is still pending for transmission and one of the following condition flags will be set. If the message started to transmit but encountered an error condition, the TXBNCTRL. TXERR and the CANINTF.MERRF bits will be set and an interrupt will be generated on the INT pin if the CANINTE.MERRE bit is set. If the message lost arbitration the TXBNCTRL.MLOA bit will be set.

# 3.4 <u>TXnRTS Pins</u>

The TXNRTS Pins are input pins that can be configured as request-to-send inputs, which provides a secondary means of initiating the transmission of a message from any of the transmit buffers, or as standard digital inputs. Configuration and control of these pins is accomplished using the TXRTSCTRL register (see Register 3-2). The TXRTSCTRL register can only be modified when the MCP2510 is in configuration mode (see Section 9.0). If configured to operate as a request to send pin, the pin is mapped into the respective TXBNCTRL.TXREQ bit for the transmit buffer. The TXREQ bit is latched by the falling edge of the TXNRTS pin. The TXNRTS pins are designed to allow them to be tied directly to the RXNBF pins to automatically initiate a message transmission when the RXNBF pin goes low. The TXNRTS pins have internal pullup resistors of 100K ohms (nominal).

#### 3.5 Aborting Transmission

The MCU can request to abort a message in a specific message buffer by clearing the associated TXBnC-TRL.TXREQ bit. Also, all pending messages can be requested to be aborted by setting the CAN-CTRL.ABAT bit. If the CANCTRL.ABAT bit is set to abort all pending messages, the user MUST reset this bit (typically after the user verifies that all TXREQ bits have been cleared) to continue trasmit messages. The CANCTRL.ABTF flag will only be set if the abort was requested via the CANCTRL.ABAT bit. Aborting a message by resetting the TXREQ bit does NOT cause the ATBF bit to be set.

Only messages that have not already begun to be transmitted can be aborted. Once a message has begun transmission, it will not be possible for the user to reset the TXBnCTRL.TXREQ bit. After transmission of a message has begun, if an error occurs on the bus or if the message loses arbitration, the message will be retransmitted regardless of a request to abort.

FIGURE 3-1: Transmit Message Flowchart

# **MCP2510**

| U-0      | R-0                      | R-0                                      | R-0                                                    | R/W-0                    | U-0        | R/W-0                      | R/W-0          |                                                                                                                                                                             |

|----------|--------------------------|------------------------------------------|--------------------------------------------------------|--------------------------|------------|----------------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| _        | ABTF                     | MLOA                                     | TXERR                                                  | TXREQ                    |            | TXP1                       | TXP0           | R = Readable bit                                                                                                                                                            |

| bit 7    |                          |                                          |                                                        |                          |            |                            | bit 0          | <ul> <li>W = Writable bit</li> <li>C = Bit can be cleared by<br/>MCU but not set</li> <li>U = Unimplemented -<br/>reads as '0'</li> <li>- n = Value at POR reset</li> </ul> |

| bit 7:   | Unimple                  | emented:                                 | Reads as                                               | '0'                      |            |                            |                |                                                                                                                                                                             |

| bit 6:   | ABTF: N                  | /lessage A                               | borted Fla                                             | ıg                       |            |                            |                |                                                                                                                                                                             |

|          |                          | sage was<br>sage com                     | aborted<br>pleted tran                                 | smission s               | successful | lly                        |                |                                                                                                                                                                             |

| bit 5:   | MLOA: N                  | Message L                                | ost Arbitra                                            | ation                    |            |                            |                |                                                                                                                                                                             |

|          |                          | •                                        | arbitration<br>ot lose art                             |                          | •          | sent                       |                |                                                                                                                                                                             |

| bit 4:   | TXERR:                   | Transmiss                                | sion Error                                             | Detected                 |            |                            |                |                                                                                                                                                                             |

|          |                          |                                          |                                                        |                          | •          | being tran<br>Is being tra |                |                                                                                                                                                                             |

| bit 3:   | TXREQ:                   | Message                                  | Transmit I                                             | Request                  |            |                            |                |                                                                                                                                                                             |

|          | (MC)<br>the<br>0 = Buffe | CU sets thi<br>message i<br>er is not cu |                                                        | nding tran               | age be tra |                            | · bit is autor | natically cleared when                                                                                                                                                      |

| bit 2:   | Unimple                  | emented:                                 | Reads as                                               | '0'                      |            |                            |                |                                                                                                                                                                             |

| bit 1-0: | TXP<1:0                  | <b>)&gt;</b> : Transm                    | nit Buffer F                                           | Priority                 |            |                            |                |                                                                                                                                                                             |

|          | 10 = Hig<br>01 = Lov     | h Interme<br>v Intermed                  | sage Priori<br>diate Mess<br>diate Mess<br>age Priorit | age Priori<br>age Priori |            |                            |                |                                                                                                                                                                             |

**REGISTER 3-1:** TXBNCTRL Transmit Buffer N Control Register (ADDRESS: 30h, 40h, 50h)

| U-0    | U-0                      | R-x       | R-x       | R-x        | R/W-0                        | R/W-0       | R/W-0            |                                                                                                                                     |

|--------|--------------------------|-----------|-----------|------------|------------------------------|-------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| —      | —                        | B2RTS     | B1RTS     | B0RTS      | B2RTSM                       | B1RTSM      | B0RTSM           | R = Readable bit                                                                                                                    |

| bit 7  |                          |           |           |            |                              |             | bit 0            | W = Writable bit<br>C = Bit can be cleared by<br>MCU but not set<br>U = Unimplemented - reads<br>as '0'<br>- n = Value at POR reset |

| bit 7: | Unimple                  | mented:   | Reads as  | '0'        |                              |             |                  |                                                                                                                                     |

| bit 6: | Unimple                  | mented:   | Reads as  | '0'        |                              |             |                  |                                                                                                                                     |

| bit 5: | B2RTS:                   | TX2RTS F  | Pin State |            |                              |             |                  |                                                                                                                                     |

|        |                          |           |           |            | digital input<br>to send' mo |             |                  |                                                                                                                                     |

| bit 4: | B1RTS:                   | TX1RTX F  | Pin State |            |                              |             |                  |                                                                                                                                     |

|        |                          |           |           |            | digital input<br>to send' mo |             |                  |                                                                                                                                     |

| bit 3: | BORTS:                   | TXORTS F  | Pin State |            |                              |             |                  |                                                                                                                                     |

|        |                          |           |           |            | digital input<br>to send' mo |             |                  |                                                                                                                                     |

| bit 2: | B2RTSM                   | I: TX2RTS | Pin Mod   | е          |                              |             |                  |                                                                                                                                     |

|        | 1 = Pin is<br>0 = Digita |           | equest m  | essage tra | ansmission                   | of TXB2 but | ffer (on falling | l edge)                                                                                                                             |

| bit 1: | B1RTSM                   | I: TX1RTS | Pin Mod   | е          |                              |             |                  |                                                                                                                                     |

|        | 1 = Pin is<br>0 = Digita |           | equest m  | essage tra | ansmission                   | of TXB1 but | ffer (on falling | edge)                                                                                                                               |

| bit 0: | <b>BORTSM</b>            | I: TX0RTS | Pin Mod   | e          |                              |             |                  |                                                                                                                                     |

|        | 1 = Pin is<br>0 = Digita |           | equest m  | essage tra | ansmission                   | of TXB0 but | ffer (on falling | l edge)                                                                                                                             |

**REGISTER 3-2:** TXRTSCTRL - TXNRTS Pin Control and Status Register (ADDRESS: 0Dh)

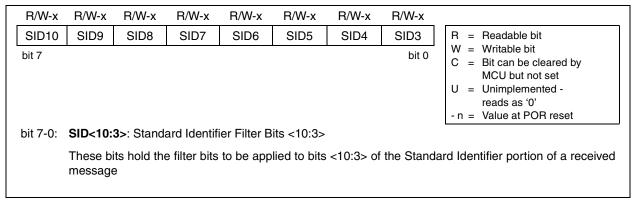

| R/W-x    | R/W-x    | R/W-x     | R/W-x       | R/W-x       | R/W-x | R/W-x | R/W-x |                                                                                                                                     |

|----------|----------|-----------|-------------|-------------|-------|-------|-------|-------------------------------------------------------------------------------------------------------------------------------------|

| SID10    | SID9     | SID8      | SID7        | SID6        | SID5  | SID4  | SID3  | R = Readable bit                                                                                                                    |

| bit 7    |          |           |             |             |       |       | bit 0 | W = Writable bit<br>C = Bit can be cleared by<br>MCU but not set<br>U = Unimplemented -<br>reads as '0'<br>- n = Value at POR reset |

| bit 7-0: | SID<10:3 | >: Standa | ard Identif | ier Bits <1 | 10:3> |       |       |                                                                                                                                     |

| R/W-x    | R/W-x                | R/W-x                       | R/W-x                  | R/W-x         | R/W-x   | R/W-x | R/W-x |                                                                                                                                     |  |  |  |  |

|----------|----------------------|-----------------------------|------------------------|---------------|---------|-------|-------|-------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| SID2     | SID1                 | SID0                        |                        | EXIDE         |         | EID17 | EID16 | R = Readable bit                                                                                                                    |  |  |  |  |

| bit 7    |                      |                             |                        |               |         |       | bit 0 | W = Writable bit<br>C = Bit can be cleared by<br>MCU but not set<br>U = Unimplemented -<br>reads as '0'<br>- n = Value at POR reset |  |  |  |  |

| bit 7-5: | SID<2:0>             | : Standar                   | d Identifie            | er Bits <2:   | 0>      |       |       |                                                                                                                                     |  |  |  |  |

| bit 4:   | Unimple              | Inimplemented: Reads as '0' |                        |               |         |       |       |                                                                                                                                     |  |  |  |  |

| bit 3:   | EXIDE: E             | Extended I                  | dentifier E            | Enable        |         |       |       |                                                                                                                                     |  |  |  |  |

|          | 1 = Mess<br>0 = Mess | age will tr<br>age will tr  |                        |               |         |       |       |                                                                                                                                     |  |  |  |  |

| bit 2:   | Unimple              | mented: I                   | Reads as               | '0'           |         |       |       |                                                                                                                                     |  |  |  |  |

| bit 1-0: | EID<17:1             | 6>: Exter                   | nded Iden <sup>.</sup> | tifier Bits - | <17:16> |       |       |                                                                                                                                     |  |  |  |  |

REGISTER 3-4: TXBNSIDL - Transmit Buffer N Standard Identifier Low (ADDRESS: 32h, 42h, 52h)

| R/W-x    | R/W-x    | R/W-x      | R/W-x      | R/W-x       | R/W-x | R/W-x | R/W-x |                                                                                                                                                                             |

|----------|----------|------------|------------|-------------|-------|-------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EID15    | EID14    | EID13      | EID12      | EID11       | EID10 | EID9  | EID8  | R = Readable bit                                                                                                                                                            |

| bit 7    |          |            |            |             |       |       | bit 0 | <ul> <li>W = Writable bit</li> <li>C = Bit can be cleared by<br/>MCU but not set</li> <li>U = Unimplemented -<br/>reads as '0'</li> <li>- n = Value at POR reset</li> </ul> |

| bit 7-0: | EID<15:8 | B>: Extend | ded Identi | fier Bits < | 15:8> |       |       |                                                                                                                                                                             |

**REGISTER 3-5:** TXBNEID8 - Transmit Buffer N Extended Identifier High (ADDRESS: 33h, 43h, 53h)

| <br>R/W-x | R/W-x    | R/W-x     | R/W-x       | R/W-x       | R/W-x | R/W-x | R/W-x |                                                                                                                                                                             |

|-----------|----------|-----------|-------------|-------------|-------|-------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EID7      | EID6     | EID5      | EID4        | EID3        | EID2  | EID1  | EID0  | R = Readable bit                                                                                                                                                            |

| bit 7     |          |           |             |             |       |       | bit 0 | <ul> <li>W = Writable bit</li> <li>C = Bit can be cleared by<br/>MCU but not set</li> <li>U = Unimplemented -<br/>reads as '0'</li> <li>- n = Value at POR reset</li> </ul> |

| bit 7-0:  | EID<7:0> | : Extende | ed Identifi | er Bits <7: | :0>   |       |       |                                                                                                                                                                             |

REGISTER 3-6: TXBNEID0 - Transmit Buffer N Extended Identifier LOW (ADDRESS: 34h, 44h, 54h)

| R/W-x    | R/W-x            | R/W-x                  | R/W-x     | R/W-x      | R/W-x     | R/W-x      | R/W-x    |                                                                                                                                     |

|----------|------------------|------------------------|-----------|------------|-----------|------------|----------|-------------------------------------------------------------------------------------------------------------------------------------|

| —        | RTR              |                        | _         | DLC3       | DLC2      | DLC1       | DLC0     | R = Readable bit                                                                                                                    |

| bit 7    |                  |                        |           |            |           |            | bit 0    | W = Writable bit<br>C = Bit can be cleared by<br>MCU but not set<br>U = Unimplemented -<br>reads as '0'<br>- n = Value at POR reset |

| bit 7:   | Unimple          | mented:                | Reads as  | '0'        |           |            |          |                                                                                                                                     |

| bit 6:   | RTR: Rei         | mote Tran              | smission  | Request I  | Bit       |            |          |                                                                                                                                     |

|          |                  | mitted Me              | -         |            |           | nsmit Req  | uest     |                                                                                                                                     |

| bit 5-4: | Unimple          | mented:                | Reads as  | '0'        |           |            |          |                                                                                                                                     |

| bit 3-0: | DLC<3:0          | >: Data L              | ength Coo | de         |           |            |          |                                                                                                                                     |

|          |                  | number o<br>is possibl | -         |            |           | •          | • •      | er only 8 bytes are transmitted                                                                                                     |

| REGISTE  | <b>я 3-7:</b> ТХ | (BNDLC -               | Transmit  | Buffer n E | Data Leng | th Code (. | ADDRESS. | : 35h, 45h, 55h)                                                                                                                    |

| R/W-x    | R/W->            | R/W                    | -x R/\    | V-x R      | /W-x      | R/W-x      | R/W-x    | R/W-x                                                                                                                               |

| TXBNDm   |                  |                        | )m5 TXB   | JDm4 TXF   | 3NDm3 T   | (BNDm2]    | [XBNDm1] | XBNDm0 R = Readable bit                                                                                                             |

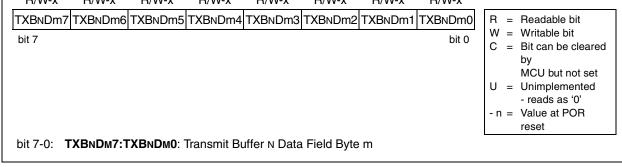

**REGISTER 3-8:** TXBNDM - Transmit Buffer N Data Field Byte m (ADDRESS: 36h-3Dh, 46h-4Dh, 56h-5Dh)

# 4.0 MESSAGE RECEPTION

#### 4.1 <u>Receive Message Buffering</u>

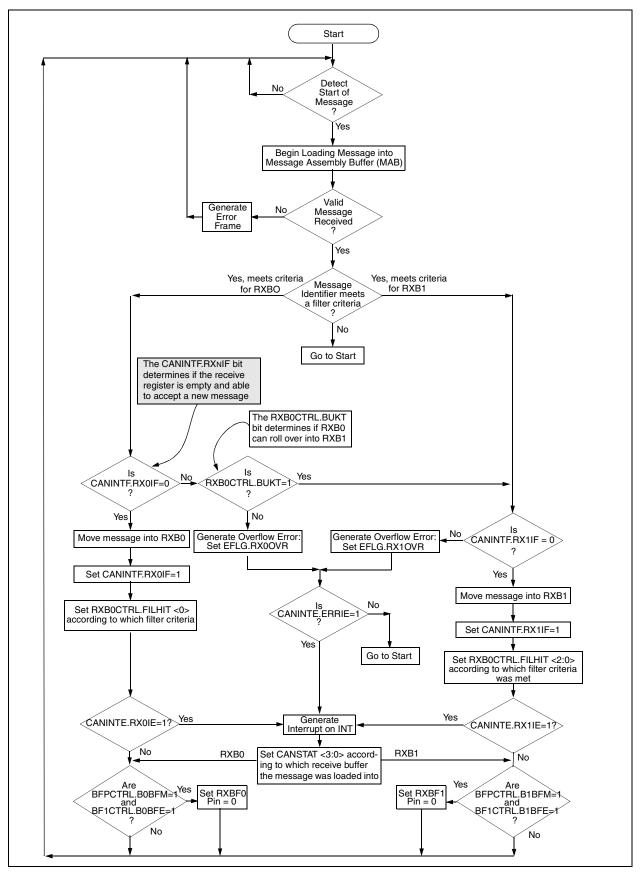

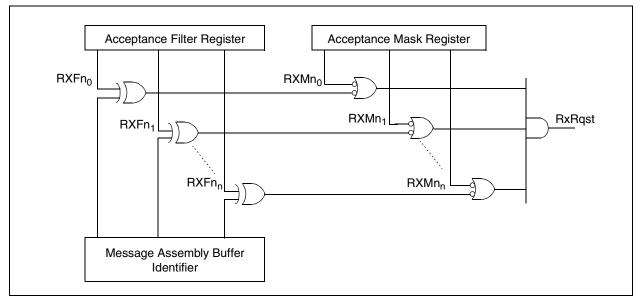

The MCP2510 includes two full receive buffers with multiple acceptance filters for each. There is also a separate Message Assembly Buffer (MAB) which acts as a third receive buffer (see Figure 4-1).

#### 4.2 <u>Receive Buffers</u>

Of the three Receive Buffers, the MAB is always committed to receiving the next message from the bus. The remaining two receive buffers are called RXB0 and RXB1 and can receive a complete message from the protocol engine. The MCU can access one buffer while the other buffer is available for message reception or holding a previously received message.

The MAB assembles all messages received. These messages will be transferred to the RXBN buffers (See Register 4-4 to Register 4-9) only if the acceptance filter criteria are met.

**Note:** The entire contents of the MAB is moved into the receive buffer once a message is accepted. This means that regardless of the type of identifier (standard or extended) and the number of data bytes received, the entire receive buffer is overwritten with the MAB contents. Therefore the contents of all registers in the buffer must be assumed to have been modified when any message is received.

When a message is moved into either of the receive buffers the appropriate CANINTF.RXNIF bit is set. This bit must be cleared by the MCU, when it has completed processing the message in the buffer, in order to allow a new message to be received into the buffer. This bit provides a positive lockout to ensure that the MCU has finished with the message before the MCP2510 attempts to load a new message into the receive buffer. If the CANINTE.RXNIE bit is set an interrupt will be generated on the INT pin to indicate that a valid message has been received.

#### 4.3 <u>Receive Priority</u>

RXB0 is the higher priority buffer and has two message acceptance filters associated with it. RXB1 is the lower priority buffer and has four acceptance filters associated with it. The lower number of acceptance filters makes the match on RXB0 more restrictive and implies a higher priority for that buffer. Additionally, the RXB0CTRL register can be configured such that if RXB0 contains a valid message, and another valid message is received, an overflow error will not occur and the new message will be moved into RXB1 regardless of the acceptance criteria of RXB1. There are also two programmable acceptance filter masks available, one for each receive buffer (see Section 4.5). When a message is received, bits <3:0> of the RXBNCTRL Register will indicate the acceptance filter number that enabled reception, and whether the received message is a remote transfer request.

The RXBNCTRL.RXM bits set special receive modes. Normally, these bits are set to 00 to enable reception of all valid messages as determined by the appropriate acceptance filters. In this case, the determination of whether or not to receive standard or extended messages is determined by the RFXNSIDL.EXIDE bit in the acceptance filter register. If the RXBNCTRL.RXM bits are set to 01 or 10, the receiver will accept only messages with standard or extended identifiers respectively. If an acceptance filter has the RFXNSIDL.EXIDE bit set such that it does not correspond with the RXBNCTRL.RXM mode, that acceptance filter is rendered useless. These two modes of RXBNCTRL.RXM bits can be used in systems where it is known that only standard or extended messages will be on the bus. If the RXBNCTRL.RXM bits are set to 11, the buffer will receive all messages regardless of the values of the acceptance filters. Also, if a message has an error before the end of frame, that portion of the message assembled in the MAB before the error frame will be loaded into the buffer. This mode has some value in debugging a CAN system and would not be used in an actual system environment.

#### 4.4 RX0BF and RX1BF Pins

In addition to the INT pin which provides an interrupt signal to the MCU for many different conditions, the receive buffer full pins (RX0BF and RX1BF) can be used to indicate that a valid message has been loaded into RXB0 or RXB1, respectively.

The RXBNBF full pins can be configured to act as buffer full interrupt pins or as standard digital outputs. Configuration and status of these pins is available via the BFPCTRL register (Register 4-3). When set to operate in interrupt mode (by setting BFPCTRL.BxBFE and BFPCTRL.BxBFM bits to a 1), these pins are active low and are mapped to the CANINTF.RXNIF bit for each receive buffer. When this bit goes high for one of the receive buffers, indicating that a valid message has been loaded into the buffer, the corresponding RXNBF pin will go low. When the CANINTF.RXNIF bit is cleared by the MCU, then the corresponding interrupt pin will go to the logic high state until the next message is loaded into the receive buffer.

When used as digital outputs the BFPCTRL.BxBFM and BFPCTRL.BxBFE bits must be set to a '1' for the associated buffer. In this mode the state of the pin is controlled by the BFPCTRL.BxBFS bits. Writting a '1' to the BxBFS bit will cause a high level to be driven on the assicated buffer full pin, and a '0' will cause the pin to drive low. When using the pins in this mode the state of the pin should be modified only by using the Bit Modify SPI command to prevent glitches from occuring on either of the buffer full pins.

FIGURE 4-1: Receive Buffer Block Diagram

FIGURE 4-2: Message Reception Flowchart

| U-0      | R/W-0                | R/W-0                       | U-0                    | R-0                      | R/W-0                | R-0          | R-0                                       |            |                                                                                                                   |

|----------|----------------------|-----------------------------|------------------------|--------------------------|----------------------|--------------|-------------------------------------------|------------|-------------------------------------------------------------------------------------------------------------------|

|          | RXM1                 | RXM0                        | —                      | RXRTR                    | BUKT                 | BUKT1        | FILHIT0                                   |            | Readable bit                                                                                                      |

| bit 7    |                      |                             |                        |                          |                      |              | bit 0                                     | C =<br>U = | Writable bit<br>Bit can be cleared by<br>MCU but not set<br>Unimplemented -<br>reads as '0'<br>Value at POR reset |

| bit 7:   | Unimple              | emented:                    | Reads as               | '0'                      |                      |              |                                           |            |                                                                                                                   |

| bit 6-5: | RXM<1:               | <b>0</b> >: Receiv          | ve Buffer (            | Operating                | Mode                 |              |                                           |            |                                                                                                                   |

|          | 10 = Red<br>01 = Red | ceive only<br>ceive only    | valid mes<br>valid mes | sages with               | extended<br>standard | identifiers  | s that meet<br>that meet f<br>xtended ide | ilter crit |                                                                                                                   |

| bit 4:   | Unimple              | emented:                    | Reads as               | '0'                      |                      |              |                                           |            |                                                                                                                   |

| bit 3:   | RXRTR:               | Received                    | Remote <sup>-</sup>    | Fransfer Re              | equest               |              |                                           |            |                                                                                                                   |

|          |                      |                             |                        | st Receive<br>quest Rece |                      |              |                                           |            |                                                                                                                   |

| bit 2:   | BUKT: F              | Rollover Er                 | nable                  |                          |                      |              |                                           |            |                                                                                                                   |

|          |                      | 0 messag<br>over disabl     |                        | ver and be               | e written to         | RXB1 if F    | RXB0 is full                              |            |                                                                                                                   |

| bit 1:   | BUKT1:               | Read Onl                    | y Copy of              | BUKT Bit                 | (used inte           | rnally by th | ne MCP251                                 | 0).        |                                                                                                                   |

| bit 0:   | FILHIT<              | 0>: Filter I                | Hit - indica           | tes which                | acceptanc            | e filter en  | abled recep                               | tion of    | message                                                                                                           |

|          |                      | eptance Fi<br>eptance Fi    |                        |                          |                      |              |                                           |            |                                                                                                                   |

|          |                      | a rollover f<br>t rolled ov |                        | ) to RXB1                | occurs, th           | e FILHIT k   | oit will reflec                           | t the fil  | ter that accepted the mes-                                                                                        |

|          |                      |                             |                        |                          |                      |              |                                           |            |                                                                                                                   |

REGISTER 4-1: RXB0CTRL - Receive Buffer 0 Control Register (ADDRESS: 60h)

| U-0      | R/W-0 R/W-0                                                                        | U-0                    | R-0                      | R-0                      | R-0          | R-0              |                                              |

|----------|------------------------------------------------------------------------------------|------------------------|--------------------------|--------------------------|--------------|------------------|----------------------------------------------|

|          | RXM1 RXM0                                                                          | —                      | RXRTR                    | FILHIT2                  | FILHIT1      | FILHIT0<br>bit 0 | R = Readable bit<br>W = Writable bit         |

| DIL 7    |                                                                                    |                        |                          |                          |              | DILU             | C = Bit can be cleared by<br>MCU but not set |

|          |                                                                                    |                        |                          |                          |              |                  | U = Unimplemented -<br>reads as '0'          |

|          |                                                                                    |                        |                          |                          |              |                  | - n = Value at POR reset                     |

| bit 7:   | Unimplemented:                                                                     | Reads as               | '0'                      |                          |              |                  |                                              |

| bit 6-5: | RXM<1:0>: Recei                                                                    | ive Buffer (           | Operating                | Mode                     |              |                  |                                              |

|          | 11 = Turn mask/fil<br>10 = Receive only<br>01 = Receive only<br>00 = Receive all v | valid mes<br>valid mes | sages with<br>sages with | n extended<br>n standard | identifiers  | that meet fi     |                                              |

| bit 4:   | Unimplemented:                                                                     | Reads as               | '0'                      |                          |              |                  |                                              |

| bit 3:   | RXRTR: Received                                                                    | d Remote               | Transfer R               | equest                   |              |                  |                                              |

|          | 1 = Remote Trans<br>0 = No Remote Tr                                               | •                      |                          |                          |              |                  |                                              |

| bit 2-0: | FILHIT<2:0>: Filte                                                                 | ər Hit - indi          | cates whic               | ch accepta               | nce filter e | nabled rece      | eption of message                            |

|          | 101 = Acceptance                                                                   |                        |                          |                          |              |                  |                                              |

|          | 100 = Acceptance<br>011 = Acceptance                                               |                        |                          |                          |              |                  |                                              |

|          | 010 = Acceptance                                                                   | •                      | RXF2)                    |                          |              |                  |                                              |

|          | 001 = Acceptance                                                                   |                        |                          |                          |              |                  |                                              |

REGISTER 4-2: RXB1CTRL - Receive Buffer 1 Control Register (ADDRESS: 70h)

| U-0    | U-0     | R/W-0                      | R/W-0       | R/W-0       | R/W-0        | R/W-0                                  | R/W-0        |                                                                                                                                     |

|--------|---------|----------------------------|-------------|-------------|--------------|----------------------------------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------|

|        | —       | B1BFS                      | B0BFS       | B1BFE       | <b>B0BFE</b> | B1BFM                                  | <b>B0BFM</b> | R = Readable bit                                                                                                                    |

| bit 7  |         |                            |             |             |              |                                        | bit 0        | W = Writable bit<br>C = Bit can be cleared by<br>MCU but not set<br>U = Unimplemented -<br>reads as '0'<br>- n = Value at POR reset |

| bit 7: | Unimple | emented:                   | Reads as    | '0'         |              |                                        |              |                                                                                                                                     |

| bit 6: | Unimple | emented:                   | Reads as    | '0'         |              |                                        |              |                                                                                                                                     |

| bit 5: | B1BFS:  | RX1BF P                    | in State (d | igital outp | ut mode o    | nly)                                   |              |                                                                                                                                     |

|        | Reads a | as 0 when                  | RX1BF is    | configured  | d as interru | upt pin                                |              |                                                                                                                                     |

| bit 4: | B0BFS:  | RX0BF P                    | in State (d | igital outp | ut mode o    | nly)                                   |              |                                                                                                                                     |

|        | Reads a | as 0 when                  | RX0BF is    | configured  | d as interru | upt pin                                |              |                                                                                                                                     |

| bit 3: | B1BFE:  | RX1BF P                    | in Functio  | n Enable    |              |                                        |              |                                                                                                                                     |

|        |         |                            |             |             |              | nined by B <sup>.</sup><br>lance state |              |                                                                                                                                     |

| bit 2: | B0BFE:  | RX0BF P                    | in Functio  | n Enable    |              |                                        |              |                                                                                                                                     |

|        |         |                            | •           |             |              | nined by Bo<br>dance stat              |              |                                                                                                                                     |

| bit 1: | B1BFM   | RX1BF P                    | 'in Operati | on Mode     |              |                                        |              |                                                                                                                                     |

|        |         | is used as<br>tal output r |             | vhen valid  | message      | loaded into                            | o RXB1       |                                                                                                                                     |

| bit 0: | B0BFM   | RX0BF P                    | in Operati  | on Mode     |              |                                        |              |                                                                                                                                     |

|        |         | is used as<br>tal output r | •           | vhen valid  | message      | loaded into                            | o RXB0       |                                                                                                                                     |

**REGISTER 4-3:** BFPCTRL - RXNBF Pin Control and Status Register (ADDRESS: 0Ch)

| R-x      | R-x      | R-x               | R-x         | R-x         | R-x         | R-x         | R-x         |                                                                                                                                     |

|----------|----------|-------------------|-------------|-------------|-------------|-------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------|

| SID10    | SID9     | SID8              | SID7        | SID6        | SID5        | SID4        | SID3        | R = Readable bit                                                                                                                    |

| bit 7    |          |                   |             |             |             |             | bit 0       | W = Writable bit<br>C = Bit can be cleared by<br>MCU but not set<br>U = Unimplemented -<br>reads as '0'<br>- n = Value at POR reset |

| bit 7-0: | SID<10:  | <b>3</b> >: Stand | ard Identif | ier Bits <1 | 0:3>        |             |             |                                                                                                                                     |

|          | These bi | its contain       | the eight   | most signi  | ficant bits | of the Star | ndard Ident | tifier for the received message                                                                                                     |

| R-x      | R-x      | R-x                                                                                                            | R-x          | R-x          | U-0          | R-x         | R-x          |                                                                                                                                     |  |  |  |

|----------|----------|----------------------------------------------------------------------------------------------------------------|--------------|--------------|--------------|-------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| SID2     | SID1     | SID0                                                                                                           | SRR          | IDE          |              | EID17       | EID16        | R = Readable bit                                                                                                                    |  |  |  |

| bit 7    |          |                                                                                                                |              |              |              |             | bit 0        | W = Writable bit<br>C = Bit can be cleared by<br>MCU but not set<br>U = Unimplemented -<br>reads as '0'<br>- n = Value at POR reset |  |  |  |

| bit 7-5: | SID<2:0  | >: Standa                                                                                                      | rd Identifie | r Bits <2:0  | )>           |             |              |                                                                                                                                     |  |  |  |

|          | These b  | its contain                                                                                                    | the three    | least signi  | ificant bits | of the Star | ndard Ident  | ifier for the received message                                                                                                      |  |  |  |

| bit 4:   | SRR: St  | SRR: Standard Frame Remote Transmit Request Bit (valid only if IDE bit = '0')                                  |              |              |              |             |              |                                                                                                                                     |  |  |  |

|          |          | <ul><li>1 = Standard Frame Remote Transmit Request Received</li><li>0 = Standard Data Frame Recieved</li></ul> |              |              |              |             |              |                                                                                                                                     |  |  |  |

| bit 3:   | IDE: Ext | ended Ide                                                                                                      | ntifier Flag | 9            |              |             |              |                                                                                                                                     |  |  |  |

|          | 1 = Rece | ndicates v<br>eived mes<br>eived mes                                                                           | sage was     | an Extend    | ed Frame     | was a Sta   | ndard or ar  | n Extended Frame                                                                                                                    |  |  |  |

| bit 2:   | Unimple  | emented:                                                                                                       | Reads as     | '0'          |              |             |              |                                                                                                                                     |  |  |  |

| bit 1-0: | EID<17:  | 16>: Exte                                                                                                      | nded Ident   | ifier Bits < | :17:16>      |             |              |                                                                                                                                     |  |  |  |

|          | These bi | its contain                                                                                                    | the two m    | iost signifi | cant bits o  | f the Exter | nded Identif | ier for the received message                                                                                                        |  |  |  |

**REGISTER 4-5:** RXBNSIDL - Receive Buffer N Standard Identifier Low (ADDRESS: 62h, 72h)

| R-x      | R-x     | R-x          | R-x        | R-x         | R-x        | R-x          | R-x          |                                                                                                                                     |

|----------|---------|--------------|------------|-------------|------------|--------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------|

| EID15    | EID14   | EID13        | EID12      | EID11       | EID10      | EID9         | EID8         | R = Readable bit                                                                                                                    |

| bit 7    |         |              |            |             |            |              | bit 0        | W = Writable bit<br>C = Bit can be cleared by<br>MCU but not set<br>U = Unimplemented -<br>reads as '0'<br>- n = Value at POR reset |

| bit 7-0: | EID<15: | 8>: Exten    | ded Identi | ier Bits <1 | 5:8>       |              |              |                                                                                                                                     |

|          | These b | its hold bit | s 15 throu | gh 8 of the | e Extendeo | d Identifier | for the rece | eived message                                                                                                                       |

| R-x      | R-x      | R-x          | R-x          | R-x          | R-x          | R-x       | R-x          |                                                                                                                                                                             |

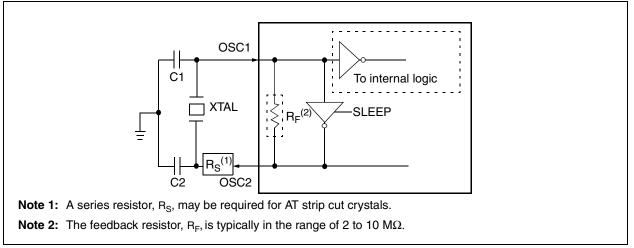

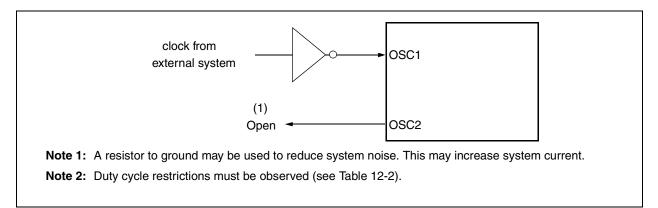

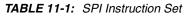

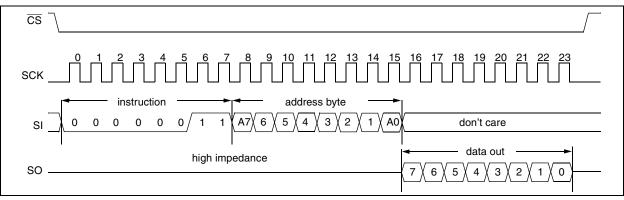

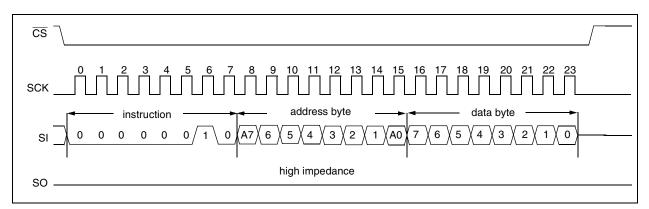

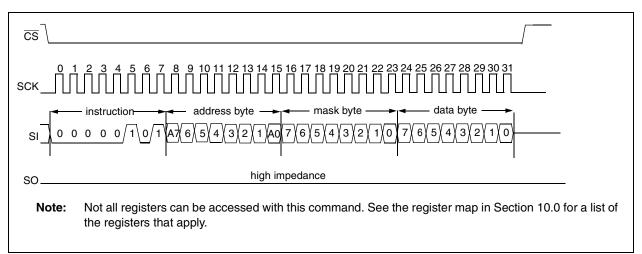

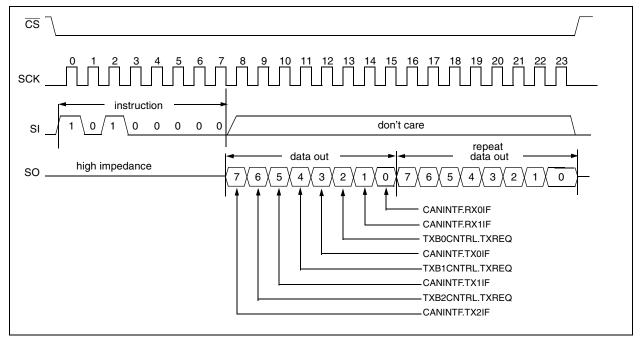

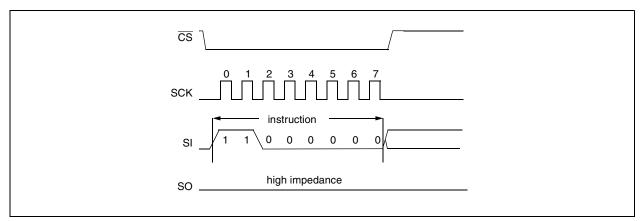

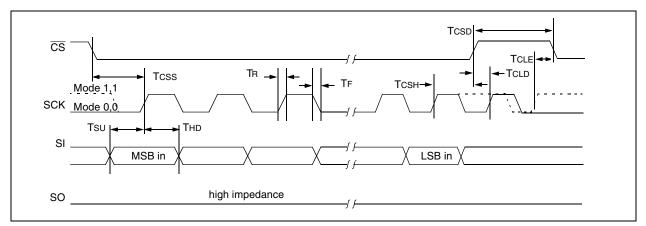

|----------|----------|--------------|--------------|--------------|--------------|-----------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|