# Freescale Semiconductor, Inc.

Addendum

HC908LJ12AD/D Rev. 0, 6/2003

Addendum to MC68HC908LJ12 Technical Data

This addendum provides information to the following MCU devices:

- **MC68HLC908LJ12** (see page 1)

- MC68HC08LJ12 (see page 9)

The entire MC68HC908LJ12 Technical Data, Rev. 2 (Motorola document number MC68HC908LJ12/D) applies to the these two devices, with exceptions outlined in this addendum.

Amendments to MC68HC908LJ12/D, Rev. 2, are documented on page 13.

## MC68HLC908LJ12

The MC68HLC908LJ12 is a low-voltage version of the MC68HC908LJ12, with

an operating voltage range of 2.4 to 3.3 V.

**FLASH Memory** The FLASH memory can be read at operating voltages from 2.4 to 3.3 V.

Program or erase operations require a minimum operating voltage of 2.7V.

Low-Voltage Inhibit

(LVI)

The LVI module is not designed for the MC68HLC908LJ12. After an MCU reset, the LVI module is disabled (LVIPWRD = 1 in CONFIG1). The LVIPWRD

bit should be left as logic 1 (the default setting).

Electrical **Specifications**

Electrical specifications for the MC68HLC908LJ12 device are given in the

following tables.

Functional Operating Range

**Table 1. Operating Range**

| Characteristic                                                  | Symbol          | Value      |            | Unit |

|-----------------------------------------------------------------|-----------------|------------|------------|------|

| Operating temperature range                                     | T <sub>A</sub>  | -40 to +85 |            | °C   |

| Operating voltage range                                         | $V_{DD}$        | 2.4 to 2.7 | 2.7 to 3.3 | V    |

| Maximum internal operating frequency                            | f <sub>OP</sub> | 2          | 4          | MHz  |

| Operating voltage for FLASH memory program and erase operations | V <sub>DD</sub> | 2.7 to 3.3 |            | V    |

DC Electrical Characteristics

Table 2. DC Electrical Characteristics (2.4 to 2.7V)

| Characteristic <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                       | Symbol          | Min                        | Typ <sup>(2)</sup>    | Max                                              | Unit                             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------------------|-----------------------|--------------------------------------------------|----------------------------------|

| Output high voltage (I <sub>LOAD</sub> = -1.0 mA) All ports                                                                                                                                                                                                                                                                                                         | V <sub>OH</sub> | V <sub>DD</sub> -0.4       | _                     | _                                                | V                                |

| Output low voltage (I <sub>LOAD</sub> = 0.8mA) All ports (I <sub>LOAD</sub> = 4.0 mA) PTB2-PTB5 (I <sub>LOAD</sub> = 10.0 mA) PTB0/TxD-PTB1                                                                                                                                                                                                                         | V <sub>OL</sub> | _                          | _                     | 0.4                                              | V                                |

| Input high voltage All ports, RST, IRQ, OSC1                                                                                                                                                                                                                                                                                                                        | V <sub>IH</sub> | $0.7 \times V_{DD}$        | _                     | V <sub>DD</sub>                                  | V                                |

| Input low voltage All ports, RST, IRQ, OSC1                                                                                                                                                                                                                                                                                                                         | V <sub>IL</sub> | V <sub>SS</sub>            | _                     | $0.3 \times V_{DD}$                              | V                                |

| $V_{DD}$ supply current $Run^{(3)}$ , $f_{OP} = 2$ MHz with all modules on with ADC on with ADC off Wait <sup>(4)</sup> , $f_{OP} = 2$ MHz (all modules off) Stop, $f_{OP} = 8$ kHz <sup>(5)</sup> $25^{\circ}$ C (with OSC, RTC, LCD <sup>(6)</sup> , LVI on) $25^{\circ}$ C (with OSC, RTC on) $25^{\circ}$ C (with OSC, RTC on) $25^{\circ}$ C (all modules off) | I <sub>DD</sub> | —<br>—<br>—<br>—<br>—<br>— | —<br>—<br>—<br>—<br>— | 5.2<br>3.8<br>2.8<br>2.3<br>200<br>27<br>15<br>1 | mA<br>mA<br>mA<br>μA<br>μA<br>μA |

| Digital I/O ports Hi-Z leakage current<br>All ports, RST                                                                                                                                                                                                                                                                                                            | I <sub>IL</sub> | _                          | _                     | ± 10                                             | μА                               |

Table 2. DC Electrical Characteristics (2.4 to 2.7V) (Continued)

| Characteristic <sup>(1)</sup>                                                         | Symbol                               | Min                 | Typ <sup>(2)</sup> | Max               | Unit     |

|---------------------------------------------------------------------------------------|--------------------------------------|---------------------|--------------------|-------------------|----------|

| Input current IRQ                                                                     | I <sub>IN</sub>                      | _                   | _                  | ± 1               | μА       |

| Capacitance Ports (as input or output)                                                | C <sub>OUT</sub><br>C <sub>IN</sub>  | _                   | _                  | 12<br>8           | pF       |

| POR re-arm voltage <sup>(7)</sup>                                                     | V <sub>POR</sub>                     | 0                   | _                  | 100               | mV       |

| POR rise-time ramp rate <sup>(8)</sup>                                                | R <sub>POR</sub>                     | 0.02                | _                  | _                 | V/ms     |

| Monitor mode entry voltage (at IRQ pin)                                               | V <sub>HI</sub>                      | $1.5 \times V_{DD}$ | _                  | $2 \times V_{DD}$ | V        |

| Pullup resistors <sup>(9)</sup> PTA0-PTA3, PTD4-PTD7 configured as KBI0-KBI7 RST, IRQ | R <sub>PU1</sub><br>R <sub>PU2</sub> |                     | 25<br>27           |                   | kΩ<br>kΩ |

- 1.  $V_{DD}$  = 2.4 to 2.7 Vdc,  $V_{SS}$  = 0 Vdc,  $T_A$  =  $T_L$  to  $T_H$ , unless otherwise noted.

- 2. Typical values reflect average measurements at midpoint of voltage range, 25 °C only.

3. Run (operating) I<sub>DD</sub> measured using external square wave clock source. All inputs 0.2 V from rail. No dc loads. Less than 100 pF on all outputs.  $C_1 = 20$  pF on OSC2. All ports configured as inputs. OSC2 capacitance linearly affects run  $I_{DD}$ .

- 4. Wait I<sub>DD</sub> measured using external square wave clock source. All inputs 0.2 V from rail. No dc loads. Less than 100 pF on all outputs.  $C_L = 20$  pF on OSC2. All ports configured as inputs. OSC2 capacitance linearly affects wait  $I_{DD}$ .

- 5. The 8kHz clock is from a 32kHz clock input at OSC1, for the driving the RTC.

- 6. LCD driver configured for low current mode.

- 7. Maximum is highest voltage that POR is guaranteed.

- 8. If minimum V<sub>DD</sub> is not reached before the internal POR reset is released, RST must be driven low externally until minimum V<sub>DD</sub> is reached.

- 9.  $R_{PU1}^{-2}$  and  $R_{PU2}$  are measured at  $V_{DD} = 2.6 V$ .

Table 3. DC Electrical Characteristics (2.7 to 3.3 V)

| Characteristic <sup>(1)</sup>                                                                                                               | Symbol          | Min                  | Typ <sup>(2)</sup> | Max                 | Unit |

|---------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------------|--------------------|---------------------|------|

| Output high voltage (I <sub>LOAD</sub> = -1.0 mA) All ports                                                                                 | V <sub>OH</sub> | V <sub>DD</sub> -0.4 | _                  | _                   | V    |

| Output low voltage (I <sub>LOAD</sub> = 0.8mA) All ports (I <sub>LOAD</sub> = 4.0 mA) PTB2-PTB5 (I <sub>LOAD</sub> = 10.0 mA) PTB0/TxD-PTB1 | V <sub>OL</sub> | _                    | _                  | 0.4                 | V    |

| Input high voltage All ports, RST, IRQ, OSC1                                                                                                | V <sub>IH</sub> | $0.7 \times V_{DD}$  | _                  | V <sub>DD</sub>     | V    |

| Input low voltage All ports, RST, IRQ, OSC1                                                                                                 | V <sub>IL</sub> | V <sub>SS</sub>      | _                  | $0.3 \times V_{DD}$ | V    |

Table 3. DC Electrical Characteristics (2.7 to 3.3 V) (Continued)

| Characteristic <sup>(1)</sup>                                                         | Symbol                               | Min                 | Typ <sup>(2)</sup> | Max               | Unit     |

|---------------------------------------------------------------------------------------|--------------------------------------|---------------------|--------------------|-------------------|----------|

| V <sub>DD</sub> supply current                                                        |                                      |                     |                    |                   |          |

| $Run^{(3)}$ , $f_{OP} = 4 MHz$                                                        |                                      |                     |                    |                   |          |

| with all modules on                                                                   |                                      | _                   | _                  | 8                 | mA       |

| with ADC on<br>with ADC off                                                           |                                      | _                   | _                  | 6<br>5            | mA<br>m^ |

| Wait <sup>(4)</sup> , $f_{OP} = 4$ MHz (all modules off)                              |                                      | _                   | _                  | 3.5               | mA<br>mA |

|                                                                                       | I <sub>DD</sub>                      | _                   | _                  | 3.5               | IIIA     |

| Stop, $f_{OP} = 8 \text{ kHz}^{(5)}$                                                  |                                      |                     |                    | 000               |          |

| 25°C (with OSC, RTC, LCD <sup>(6)</sup> , LVI on)                                     |                                      | _                   |                    | 280               | μΑ       |

| 25°C (with OSC, RTC, LCD <sup>(6)</sup> on)                                           |                                      | _                   |                    | 38<br>15          | μA<br>μA |

| 25°C (with OSC, RTC on)<br>25°C (all modules off)                                     |                                      |                     | _                  | 1                 | μΑ       |

| ,                                                                                     |                                      |                     |                    |                   |          |

| Digital I/O ports Hi-Z leakage current All ports, RST                                 | I <sub>IL</sub>                      | _                   | _                  | ± 10              | μΑ       |

| Input current IRQ                                                                     | I <sub>IN</sub>                      | _                   | _                  | ± 1               | μА       |

| Capacitance                                                                           | C <sub>OUT</sub>                     | _                   | _                  | 12                | C        |

| Ports (as input or output)                                                            | C <sub>IN</sub>                      | _                   | _                  | 8                 | pF       |

| POR re-arm voltage <sup>(7)</sup>                                                     | V <sub>POR</sub>                     | 0                   | _                  | 100               | mV       |

| POR rise-time ramp rate <sup>(8)</sup>                                                | R <sub>POR</sub>                     | 0.02                | _                  | _                 | V/ms     |

| Monitor mode entry voltage (at IRQ pin)                                               | V <sub>HI</sub>                      | $1.5 \times V_{DD}$ | _                  | $2 \times V_{DD}$ | V        |

| Pullup resistors <sup>(9)</sup> PTA0-PTA3, PTD4-PTD7 configured as KBI0-KBI7 RST, IRQ | R <sub>PU1</sub><br>R <sub>PU2</sub> |                     | 25<br>27           | _<br>_            | kΩ<br>kΩ |

- V<sub>DD</sub> = 2.7 to 3.3 Vdc, V<sub>SS</sub> = 0 Vdc, T<sub>A</sub> = T<sub>L</sub> to T<sub>H</sub>, unless otherwise noted.

Typical values reflect average measurements at midpoint of voltage range, 25 °C only.

Run (operating) I<sub>DD</sub> measured using external square wave clock source. All inputs 0.2 V from rail. No dc loads. Less than

- 100 pF on all outputs. C<sub>L</sub> = 20 pF on OSC2. All ports configured as inputs. OSC2 capacitance linearly affects run I<sub>DD</sub>.

4. Wait I<sub>DD</sub> measured using external square wave clock source. All inputs 0.2 V from rail. No dc loads. Less than 100 pF on all outputs. C<sub>L</sub> = 20 pF on OSC2. All ports configured as inputs. OSC2 capacitance linearly affects wait I<sub>DD</sub>.

- 5. The 8kHz clock is from a 32kHz clock input at OSC1, for the driving the RTC.

- 6. LCD driver configured for low current mode.

- 7. Maximum is highest voltage that POR is guaranteed.

- 8. If minimum V<sub>DD</sub> is not reached before the internal POR reset is released, RST must be driven low externally until minimum V<sub>DD</sub> is reached.

- 9.  $R_{PU1}$  and  $R_{PU2}$  are measured at  $V_{DD} = 3V$ .

HC908LJ12AD/D MC68HLC908LJ12

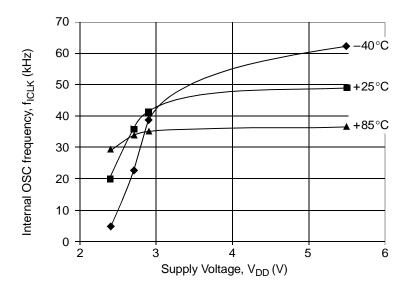

## Oscillator Characteristics

Table 4. Oscillator Specifications (2.4 to 2.7V)

| Characteristic                                  | Symbol            | Min | Тур                      | Max     | Unit |

|-------------------------------------------------|-------------------|-----|--------------------------|---------|------|

| Internal oscillator clock frequency             | f <sub>ICLK</sub> | _   | See Figure 1.            | _       | Hz   |

| External reference clock to OSC1 <sup>(1)</sup> | f <sub>OSC</sub>  | dc  | _                        | 8M      | Hz   |

| Crystal reference frequency <sup>(2)</sup>      | f <sub>XCLK</sub> |     | 32.768k                  | 4.9152M | Hz   |

| Crystal load capacitance <sup>(3)</sup>         | C <sub>L</sub>    | _   | _                        | _       |      |

| Crystal fixed capacitance                       | C <sub>1</sub>    | _   | 2 × C <sub>L</sub> (25p) | _       | F    |

| Crystal tuning capacitance                      | C <sub>2</sub>    | _   | 2 × C <sub>L</sub> (25p) | _       | F    |

| Feedback bias resistor                          | R <sub>B</sub>    | _   | 10M                      | _       | Ω    |

| Series resistor <sup>(4)</sup>                  | R <sub>S</sub>    | _   | 100k                     | _       | Ω    |

- 1. No more than 10% duty cycle deviation from 50%.

- 2. Fundamental mode crystals only.

- 3. Consult crystal manufacturer's data.

- 4. Not Required for high frequency crystals.

Table 5. Oscillator Specifications (2.7 to 3.3 V)

| Characteristic                                  | Symbol            | Min | Тур                      | Max     | Unit |

|-------------------------------------------------|-------------------|-----|--------------------------|---------|------|

| Internal oscillator clock frequency             | f <sub>ICLK</sub> | _   | See Figure 1.            | _       | Hz   |

| External reference clock to OSC1 <sup>(1)</sup> | fosc              | dc  | _                        | 16M     | Hz   |

| Crystal reference frequency <sup>(2)</sup>      | f <sub>XCLK</sub> |     | 32.768k                  | 4.9152M | Hz   |

| Crystal load capacitance <sup>(3)</sup>         | C <sub>L</sub>    | _   | _                        | _       |      |

| Crystal fixed capacitance                       | C <sub>1</sub>    | _   | 2 × C <sub>L</sub> (25p) | _       | F    |

| Crystal tuning capacitance                      | C <sub>2</sub>    | _   | 2 × C <sub>L</sub> (25p) | _       | F    |

| Feedback bias resistor                          | R <sub>B</sub>    | _   | 10M                      | _       | Ω    |

| Series resistor <sup>(4)</sup>                  | R <sub>S</sub>    | _   | 100k                     |         | Ω    |

- 1. No more than 10% duty cycle deviation from 50%.

- 2. Fundamental mode crystals only.

- 3. Consult crystal manufacturer's data.

- 4. Not Required for high frequency crystals.

Figure 1. Typical Internal Oscillator Frequency

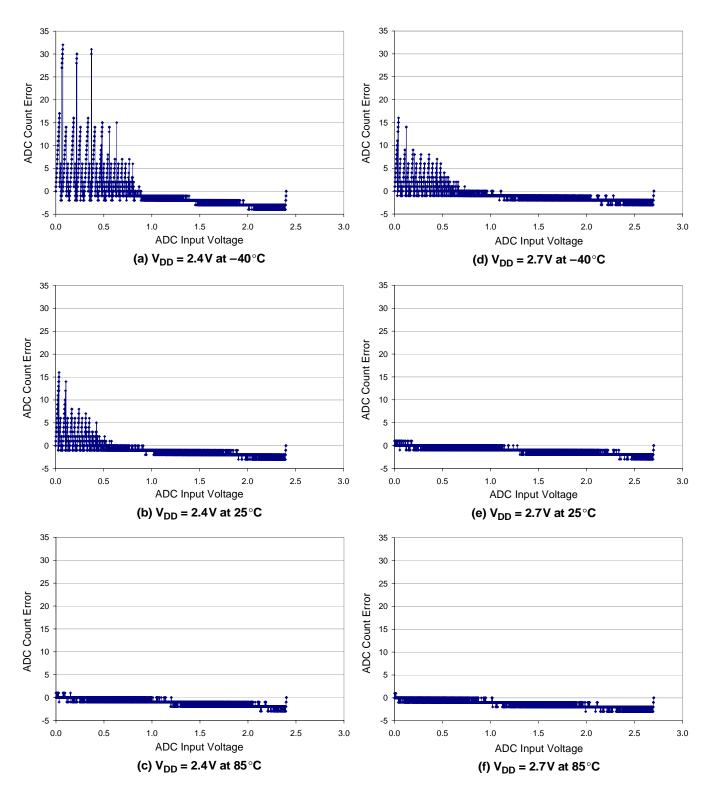

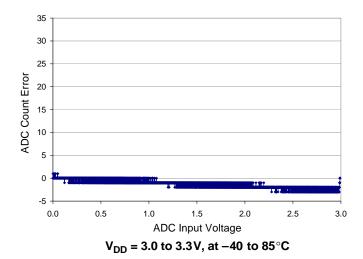

ADC Electrical Characteristics

Table 6. ADC Electrical Characteristics (2.4 to 3.3 V)

| Characteristic                       | Symbol            | Min                    | Max                    | Unit                     | Notes                                             |

|--------------------------------------|-------------------|------------------------|------------------------|--------------------------|---------------------------------------------------|

| Supply voltage                       | $V_{DDA}$         | 2.4                    | 3.3                    | V                        |                                                   |

| Input range                          | V <sub>ADIN</sub> | 0                      | $V_{DDA}$              | V                        | $V_{ADIN} \le V_{DDA}$                            |

| Resolution                           | B <sub>AD</sub>   | 10                     | 10                     | bits                     | 1,024 counts                                      |

| Absolute accuracy                    | A <sub>AD</sub>   | See Figure 2           | and Figure 3.          |                          | Includes quantization.<br>±1 ADC count = ±0.5 LSB |

| ADC internal clock                   | f <sub>ADIC</sub> | 32 k                   | 2 M                    | Hz                       | $t_{ADIC} = 1/f_{ADIC}$                           |

| Conversion range                     | R <sub>AD</sub>   | $V_{REFL}$             | $V_{REFH}$             | V                        |                                                   |

| ADC voltage reference high           | V <sub>REFH</sub> | _                      | V <sub>DDA</sub> + 0.1 | V                        |                                                   |

| ADC voltage reference low            | V <sub>REFL</sub> | V <sub>SSA</sub> - 0.1 | _                      | V                        | $V_{\rm SSA}$ is tied to $V_{\rm SS}$ internally. |

| Conversion time                      | t <sub>ADC</sub>  | 16                     | 17                     | t <sub>ADIC</sub> cycles |                                                   |

| Sample time                          | t <sub>ADS</sub>  | 5                      | _                      | t <sub>ADIC</sub> cycles |                                                   |

| Monotonically                        | M <sub>AD</sub>   | C                      | Guaranteed             |                          |                                                   |

| Zero input reading                   | Z <sub>ADI</sub>  | 000                    | 001                    | HEX                      | $V_{ADIN} = V_{REFL}$                             |

| Full-scale reading                   | F <sub>ADI</sub>  | 3FC                    | 3FF                    | HEX                      | V <sub>ADIN</sub> = V <sub>REFH</sub>             |

| Input capacitance                    | C <sub>ADI</sub>  | _                      | 20                     | pF                       | Not tested.                                       |

| Input impedance                      | R <sub>ADI</sub>  | 20M                    | _                      | Ω                        | Measured at 5V                                    |

| V <sub>REFH</sub> /V <sub>REFL</sub> | I <sub>VREF</sub> | _                      | 1.6                    | mA                       | Not tested.                                       |

Note: ADC performance increases with increase in operating voltage and temperature.

Figure 2. Typical ADC Accuracy (2.4V and 2.7V)

Figure 3. Typical ADC Accuracy (3V and 3.3V)

Memory Characteristics At an operating voltage of less than 2.7 V, the FLASH memory can only be read. Program and erase are achieved at an operating voltage of 2.7 to 3.3 V. The program and erase parameters in the MC68HC908LJ12 Technical Data are for  $V_{DD} = 2.7$  to 3.3 V only.

MC68HLC908LJ12 Order Numbers Table 7 shows the ordering numbers for the MC68HLC908LJ12.

Table 7. MC68HLC908LJ12 Order Numbers

| MC Order Number <sup>(1)</sup> | Package     | Operating<br>Temperature Range |

|--------------------------------|-------------|--------------------------------|

| MC68HLC98LJ12CFB               | 52-pin LQFP | −40 °C to +85 °C               |

| MC68HLC98LJ12CPB               | 64-pin LQFP | −40 °C to +85 °C               |

| MC68HLC98LJ12CFU               | 64-pin QFP  | −40 °C to +85 °C               |

<sup>1.</sup> The missing "0" in "908" is intentional.

## MC68HC08LJ12

The MC68HC08LJ12 is the ROM part equivalent to the MC68HC908LJ12.

Table 8. Summary of MC68HC08LJ12 and MC68HC908LJ12 Differences

|                                               | MC68HC08LJ12                             | MC68HC908LJ12                                               |

|-----------------------------------------------|------------------------------------------|-------------------------------------------------------------|

| Operating voltages                            | —<br>5.0 V ± 10%                         | 3.3V ± 10%<br>5.0V ± 10%                                    |

| Memory (\$C000-\$EFFF)                        | 12,288 bytes ROM                         | 12,288 bytes FLASH                                          |

| User vectors (\$FFD0-\$FFFF)                  | 48 bytes ROM                             | 48 bytes FLASH                                              |

| Registers at \$FE08 and \$FF09                | Not used; locations are reserved.        | FLASH related registers.<br>\$FE08 — FLCR<br>\$FF09 — FLBPR |

| Monitor ROM (\$FC00-\$FDFF and \$FE10-\$FFCF) | Used for testing purposes only.          | Used for testing and FLASH programming/erasing.             |

| Available packages                            | 52-pin LQFP<br>64-pin LQFP<br>64-pin QFP | 52-pin LQFP<br>64-pin LQFP<br>64-pin QFP                    |

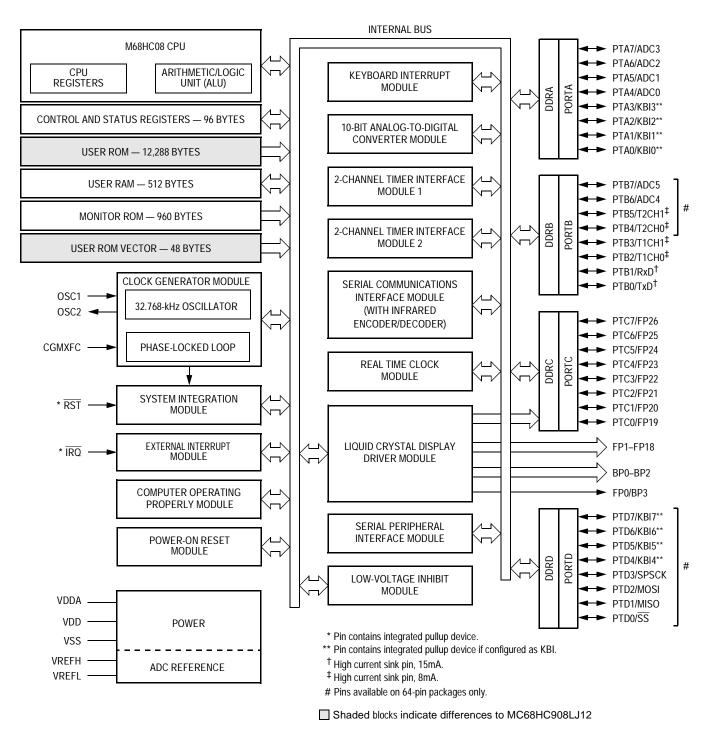

MCU Block Diagram Figure 4 shows the block diagram of the MC68HC08LJ12.

Memory Map The MC68HC08LJ128 has 12,288 bytes of user ROM from \$C000 to \$EFFF,

and 48 bytes of user ROM vectors from \$FFD0 to \$FFFF. On the MC68HC908LJ12 these memory locations are FLASH memory.

Figure 5 shows the memory map of the MC68HC08LJ12.

MC68HC08LJ12.

On the MC68HC908LJ12, these two locations are the FLASH control register

and the FLASH block protect register respectively.

Monitor ROM The monitor program (monitor ROM: \$FE10-\$FFCF and \$FC00-\$FDFF) on

the MC68HC08LJ12 is for device testing only.

Figure 4. MC68HC08LJ12 Block Diagram

| <b>#</b> 0000       |                                            |

|---------------------|--------------------------------------------|

| \$0000<br>↓         | I/O Registers                              |

| \$005F              | 96 Bytes                                   |

| \$0060              | RAM                                        |

| ↓<br>\$025F         | 512 Bytes                                  |

| \$0260              |                                            |

| ψ0 <u>2</u> 00<br>↓ | Unimplemented<br>48,544 Bytes              |

| \$BFFF              | 40,044 Bytes                               |

| \$C000              | ROM                                        |

| \$EFFF              | 12,288 Bytes                               |

| \$F000              | Unimplemented                              |

| ↓<br>\$FBFF         | 3,072 Bytes                                |

| \$FC00              | Monitor ROM 1                              |

| ↓<br>\$FDFF         | 512 Bytes                                  |

| \$FE00              | SIM Break Status Register (SBSR)           |

| \$FE01              | SIM Reset Status Register (SRSR)           |

| \$FE02              | Reserved                                   |

| \$FE03              | SIM Break Flag Control Register (SBFCR)    |

| \$FE04              | Interrupt Status Register 1 (INT1)         |

| \$FE05              | Interrupt Status Register 2 (INT2)         |

| \$FE06              | Interrupt Status Register 3 (INT3)         |

| \$FE07              | Reserved                                   |

| \$FE08              | Reserved                                   |

| \$FE09              | Reserved                                   |

| \$FE0A              | Reserved                                   |

| \$FE0B              | Reserved                                   |

| \$FE0C              | Break Address Register High (BRKH)         |

| \$FE0D              | Break Address Register Low (BRKL)          |

| \$FE0E              | Break Status and Control Register (BRKSCR) |

| \$FE0F              | LVI Status Register (LVISR)                |

| \$FE10              | Monitor ROM 2                              |

| ↓<br>\$FFCF         | 448 Bytes                                  |

| \$FFD0              | ROM Vectors                                |

| ↓<br>¢EEEE          | 48 Bytes                                   |

| \$FFFF              | ·                                          |

Figure 5. MC68HC08LJ12 Memory Map

**Electrical Specifications**  Electrical specifications for the MC68HC908LJ12 apply to the MC68HC08LJ12

except for the parameters indicated below.

Functional Operating Range

**Table 9. Operating Range**

| Characteristic              | Symbol         | Value      | Unit |

|-----------------------------|----------------|------------|------|

| Operating temperature range | T <sub>A</sub> | -40 to +85 | °C   |

| Operating voltage range     | $V_{DD}$       | 5.0V ± 10% | V    |

RAM Memory Characteristics

**Table 10. Memory Characteristics**

| Characteristic             | Symbol    | Min. | Max. | Unit |

|----------------------------|-----------|------|------|------|

| RAM data retention voltage | $V_{RDR}$ | 1.3  | _    | V    |

Notes:

Since MC68HC08LJ12 is a ROM device, FLASH memory electrical characteristics do not apply.

## MC68HC08LJ12 **Order Numbers**

These part numbers are generic numbers only. To place an order, ROM code must be submitted to the ROM Processing Center (RPC).

Table 11. MC68HC08LJ12 Order Numbers

| MC Order Number | Package     | Operating<br>Temperature Range |

|-----------------|-------------|--------------------------------|

| MC68HC08LJ12CFB | 52-pin LQFP | −40 °C to +85 °C               |

| MC68HC08LJ12CPB | 64-pin LQFP | −40 °C to +85 °C               |

| MC68HC08LJ12CFU | 64-pin QFP  | −40 °C to +85 °C               |

HC908LJ12AD/D AMENDMENTS TO MC68HC908LJ12/D, REV. 2

# AMENDMENTS TO MC68HC908LJ12/D, REV. 2

5.0V DC Electrical Characteristics

Pages 394 and 395, Table 23-4 5.0V DC Electrical Characteristics —

Delete LVI typical values and correct note 6.

## From:

| Characteristic                            | Symbol             | Min  | Тур  | Max  | Unit |

|-------------------------------------------|--------------------|------|------|------|------|

| Low-voltage inhibit, trip falling voltage | $V_{TRIPF}$        | 4.00 | 4.32 | 4.70 | V    |

| Low-voltage inhibit, trip rising voltage  | V <sub>TRIPR</sub> | 4.00 | 4.32 | 4.70 | V    |

#### Notes:

6. LCD driver configured for high current mode.

## To:

| Characteristic                            | Symbol             | Min  | Тур | Max  | Unit |

|-------------------------------------------|--------------------|------|-----|------|------|

| Low-voltage inhibit, trip falling voltage | V <sub>TRIPF</sub> | 4.00 | _   | 4.70 | V    |

| Low-voltage inhibit, trip rising voltage  | V <sub>TRIPR</sub> | 4.00 | _   | 4.70 | V    |

#### Notes:

6. LCD driver configured for low current mode.

# 3.3V DC Electrical Characteristics

Pages 396 and 397, Table 23-5 3.3V DC Electrical Characteristics —

Delete LVI typical values and correct note 6.

## From:

| Characteristic                            | Symbol             | Min  | Тур  | Max  | Unit |

|-------------------------------------------|--------------------|------|------|------|------|

| Low-voltage inhibit, trip falling voltage | $V_{TRIPF}$        | 2.40 | 2.57 | 2.88 | V    |

| Low-voltage inhibit, trip rising voltage  | V <sub>TRIPR</sub> | 2.46 | 2.63 | 2.97 | V    |

#### Notes

6. LCD driver configured for high current mode.

## To:

| Characteristic                            | Symbol             | Min  | Тур | Max  | Unit |

|-------------------------------------------|--------------------|------|-----|------|------|

| Low-voltage inhibit, trip falling voltage | $V_{TRIPF}$        | 2.40 | _   | 2.88 | V    |

| Low-voltage inhibit, trip rising voltage  | V <sub>TRIPR</sub> | 2.46 | _   | 2.97 | V    |

#### Notes:

6. LCD driver configured for low current mode.

## Oscillator Characteristics

Page 398, **Table 23-8 5.0V Oscillator Specifications** and **Table 23-9 3.3V Oscillator Specifications** — Replace Internal oscillator clock frequency values.

## From:

| Characteristic                      | Symbol            | Min | Тур | Max | Unit |

|-------------------------------------|-------------------|-----|-----|-----|------|

| Internal oscillator clock frequency | f <sub>ICLK</sub> | 46k | 47k | 48k | Hz   |

| Characteristic                      | Symbol            | Min   | Тур   | Max | Unit |

|-------------------------------------|-------------------|-------|-------|-----|------|

| Internal oscillator clock frequency | f <sub>ICLK</sub> | 42.8k | 43.4k | 44k | Hz   |

To: See Figure 1 . Typical Internal Oscillator Frequency on page 6 of this document.

- END -

# Freescale Semiconductor, Inc.

#### **HOW TO REACH US:**

#### **USA/EUROPE/LOCATIONS NOT LISTED:**

Motorola Literature Distribution P.O. Box 5405, Denver, Colorado 80217 1-800-521-6274 or 480-768-2130

#### JAPAN:

Motorola Japan Ltd.; SPS, Technical Information Center 3-20-1, Minami-Azabu Minato-ku, Tokyo 106-8573 Japan 81-3-3440-3569

#### ASIA/PACIFIC:

Motorola Semiconductors H.K. Ltd. Silicon Harbour Centre, 2 Dai King Street Tai Po Industrial Estate, Tai Po, N.T., Hong Kong 852-26668334

#### **HOME PAGE:**

http://motorola.com/semiconductors

Information in this document is provided solely to enable system and software implementers to use Motorola products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part.

Motorola and the Stylized M Logo are registered in the U.S. Patent and Trademark Office. digital dna is a trademark of Motorola, Inc. All other product or service names are the property of their respective owners. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

© Motorola, Inc. 2003