MC68HC11KW1

# MC68HC11KW1

TECHNICAL DATA

## MC68HC11KW1

## High-density complementary www.DataSheet4U.com metal oxide semiconductor (HCMOS) microcontroller unit

All Trade Marks recognized. This document contains information on new products. Specifications and information herein are subject to change without notice.

All products are sold on Motorola's Terms & Conditions of Supply. In ordering a product covered by this document the Customer agrees to be bound by those Terms & Conditions and nothing contained in this document constitutes or forms part of a contract (with the exception of the contents of this Notice). A copy of Motorola's Terms & Conditions of Supply is available on request.

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and the part claim and trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

The Customer should ensure that it has the most up to date version of the document by contacting its local Motorola office. This document supersedes any earlier documentation relating to the products referred to herein. The information contained in this document is current at the date of publication. It may subsequently be updated, revised or withdrawn.

www.DataSheet4U.com

## Conventions

Where abbreviations are used in the text, an explanation can be found in the glossary, at the back of this manual. Register and bit mnemonics are defined in the paragraphs describing them.

An overbar is used to designate an active-low signal, eg: RESET.

Because the bits in any one register are not necessarily linked by a common function, the description of a register may appear in several sections referring to different aspects of device operation. A full description of a bit is given only in a section in which it has relevance. Elsewhere, it appears shaded in the register diagram and is only briefly described.

When the state of a bit on reset is described as 'x', this means that its state depends on factors such as the operating mode selected. A 'u' indicates that the bit's state on reset is undefined.

## TABLE OF CONTENTS

www.DataSheet4U.com

| Paragraph |

|-----------|

| Number    |

#### TITLE

Page Number

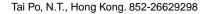

#### 1 INTRODUCTION

| 1.1 | Features    | 1- | 1 |

|-----|-------------|----|---|

| 1.2 | Mask option | 1- | 2 |

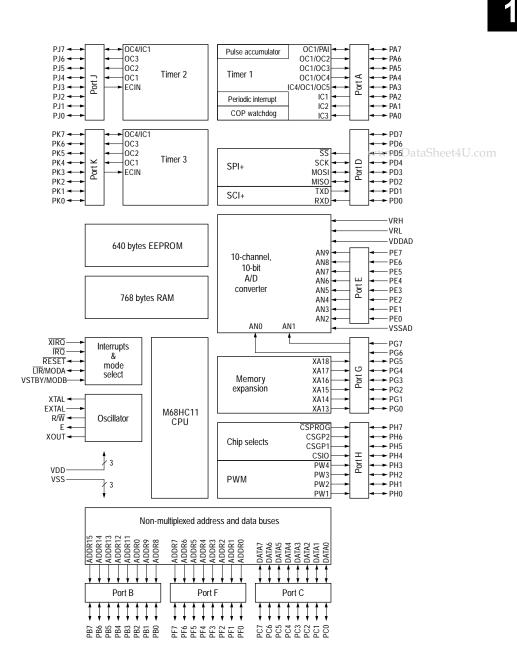

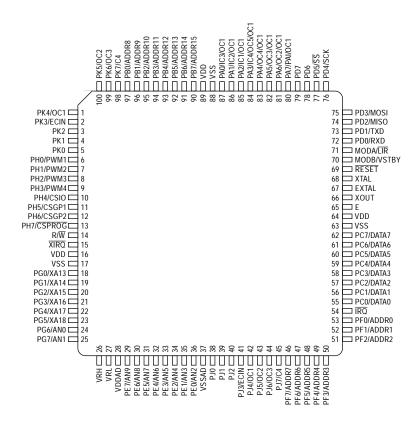

#### 2 PIN DESCRIPTIONS

| 2.1     | RESET                                                 | .2-2  |

|---------|-------------------------------------------------------|-------|

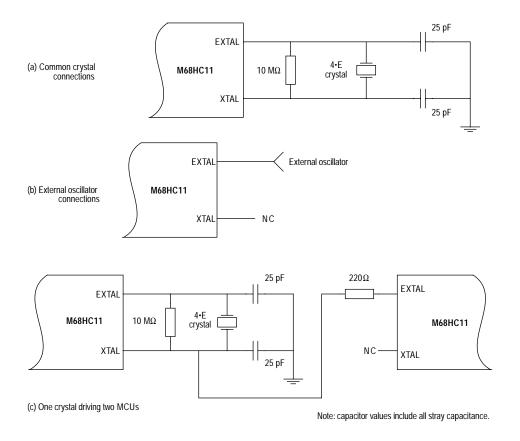

| 2.2     | Crystal driver and external clock input (XTAL, EXTAL) | .2-3  |

| 2.3     | VDD and VSS                                           | .2-4  |

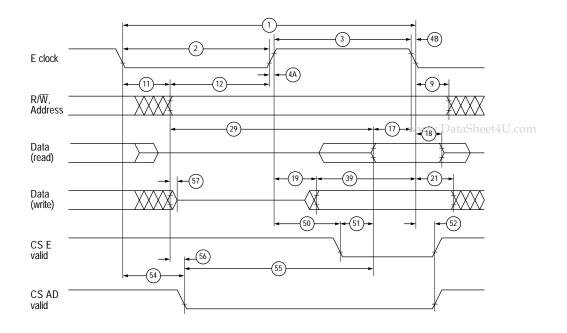

| 2.4     | E clock output (E)                                    | .2-4  |

| 2.5     | XOUT                                                  | .2-4  |

| 2.6     | Interrupt request (IRQ)                               | 2-4   |

| 2.7     | Nonmaskable interrupt (XIRQ)                          | .2-5  |

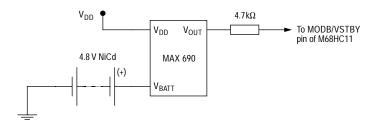

| 2.8     | MODA and MODB (MODA/LIR and MODB/VSTBY)               | .2-5  |

| 2.9     | VRH and VRL                                           | .2-6  |

| 2.10    | R/W                                                   | .2-6  |

| 2.11    | Port signals                                          | .2-6  |

| 2.11.1  | Port A                                                | .2-6  |

| 2.11.2  | Port B                                                | .2-8  |

| 2.11.3  | Port C                                                | .2-8  |

| 2.11.4  | Port D                                                |       |

| 2.11.5  | Port E                                                | .2-9  |

| 2.11.6  | Port F                                                | .2-9  |

| 2.11.7  | Port G                                                | .2-9  |

| 2.11.8  | Port H                                                | .2-10 |

| 2.11.9  | Port J                                                |       |

| 2.11.10 | 0 Port K                                              | .2-10 |

Paragraph Number

#### TITLE

Page Number

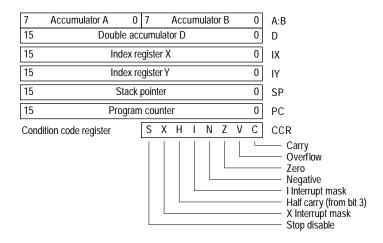

#### 3 **CENTRAL PROCESSING UNIT**

| 3.1     | Registers                                        |                 |

|---------|--------------------------------------------------|-----------------|

| 3.1.1   | Accumulators A, B and D<br>Index register X (IX) | 3-2             |

| 3.1.2   | Index register X (IX)                            | 3-2 heet 40.com |

| 3.1.3   | Index register Y (IY)                            | 3-2             |

| 3.1.4   | Stack pointer (SP)                               | 3-2             |

| 3.1.5   | Program counter (PC)                             | 3-4             |

| 3.1.6   | Condition code register (CCR)                    | 3-4             |

| 3.1.6.1 | Carry/borrow (C)                                 | 3-5             |

| 3.1.6.2 | 2 Overflow (V)                                   | 3-5             |

| 3.1.6.3 | B Zero (Z)                                       | 3-5             |

| 3.1.6.4 | Negative (N)                                     | 3-5             |

| 3.1.6.5 | ······································           |                 |

| 3.1.6.6 | 6 Half carry (H)                                 | 3-6             |

| 3.1.6.7 | · · · · · · · · · · · · · · · · · · ·            |                 |

| 3.1.6.8 |                                                  |                 |

| 3.2     | Data types                                       | 3-6             |

| 3.3     | Opcodes and operands                             | 3-7             |

| 3.4     | Addressing modes                                 |                 |

| 3.5     | Immediate (IMM)                                  | 3-7             |

| 3.5.1   | Direct (DIR)                                     | 3-7             |

| 3.5.2   | Extended (EXT)                                   | 3-8             |

| 3.5.3   | Indexed (IND, X; IND, Y)                         | 3-8             |

| 3.5.4   | Inherent (INH)                                   | 3-8             |

| 3.5.5   | Relative (REL)                                   |                 |

| 3.6     | Instruction set                                  | 3-8             |

|         |                                                  |                 |

#### 4

#### **OPERATING MODES AND ON-CHIP MEMORY**

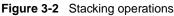

| 4.1     | Operating modes                                           | 4-1  |

|---------|-----------------------------------------------------------|------|

| 4.1.1   | Single chip operating mode                                | 4-1  |

| 4.1.2   | Expanded operating mode                                   | 4-1  |

| 4.1.3   | Special test mode                                         | 4-2  |

| 4.1.4   | Special bootstrap mode                                    | 4-2  |

| 4.2     | On-chip memory                                            | 4-3  |

| 4.2.1   | Mapping allocations                                       | 4-3  |

| 4.2.1.1 |                                                           |      |

| 4.2.1.2 | Bootloader ROM                                            | 4-4  |

| 4.2.2   | Registers                                                 | 4-4  |

| 4.3     | System initialization                                     | 4-10 |

| 4.3.1   | Mode selection                                            | 4-10 |

| 4.3.1.1 | HPRIO — Highest priority I-bit interrupt & misc. register | 4-11 |

Paragraph Number

| 4.3.2.1       Initialization       4-12         4.3.2.1       CONFIG — System configuration register       4-12         4.3.2.2       INIT — RAM and I/O mapping register       4-13         4.3.2.3       INIT2 — EEPROM mapping register       4-15         4.3.2.4       OPTION — System configuration options register 1       4-15         4.3.2.5       OPT2 — System configuration options register 1       4-16         4.3.2.6       BPROT — Block protect register       4-18         4.3.2.7       TMSK2 — Timer interrupt mask register 2       4-20         4.3.2.8       TCTL4 and TCTL6 — Timer 2 and 3 control registers       4-21         4.4       Memory expansion logic       4-22         4.4.1       Memory expansion logic       4-22         4.4.1       Memory expansion examples       4-24         4.4.4       MMSIZ — Memory mapping window size register       4-24         4.4.4       MMMICR, MM2CR - Memory mapping window 1 and 2 control registers       4-31         4.5.2       Chip select priorities       4-33         4.5.2       General-purpose chip select       4-33         4.5.3       I/O chip select       4-33         4.5.4       CSCTL — Chip select control register       4-34         4.5.5       Gener                                                           |         |                         |      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------------------------|------|

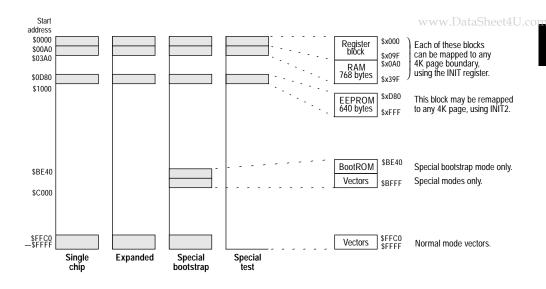

| 4.3.2.2       INIT — RAM and I/O mapping register       4-13         4.3.2.3       INIT2 — EEPROM mapping register       4-15         4.3.2.4       OPTION — System configuration options register 1       4-15         4.3.2.5       OPT2 — System configuration options register 1       4-16         4.3.2.6       BPROT — Block protect register       4-18         4.3.2.7       TMSK2 — Timer interrupt mask register 2       4-20         4.3.2.8       TCTL4 and TCTL6 — Timer 2 and 3 control registers       4-21         4.4       Memory expansion       4-22         4.4.1       Memory expansion logic       4-22         4.4.2       Extended addressing       4-23         4.4.3       Memory expansion examples       4-24         4.4.4       MMSIZ — Memory mapping window size register       4-29         4.4.5       MMWDR – Memory mapping window base register       4-30         4.4.6       MM1CR, MM2CR – Memory mapping window 1 and 2 control registers       4-31         4.5.7       Chip select priorities       4-33         4.5.8       Program chip select       4-33         4.5.9       Program chip select control register       4-33         4.5.1       Chip select priorities       4-33         4.5.2       GPCS1A                                                            | 4.3.2   |                         |      |

| 4.3.2.3       INIT2 — EEPROM mapping register       .4-15         4.3.2.4       OPTION — System configuration options register 1       .4-15         4.3.2.5       OPT2 — System configuration options register 2       .4-18         4.3.2.6       BPROT — Block protect register       .4-18         4.3.2.7       TMSK2 — Timer interrupt mask register 2       .4-20         4.3.2.8       TCTL4 and TCTL6 — Timer 2 and 3 control registers       .4-21         4.4       Memory expansion logic       .4-22         4.4.1       Memory expansion logic       .4-22         4.4.2       Extended addressing       .4-23         4.4.3       Memory expansion logic       .4-23         4.4.4       MMSIZ — Memory mapping window size register       .4-30         4.4.5       MMWBR - Memory mapping window base register       .4-30         4.4.6       MM1CR, MM2CR - Memory mapping window 1 and 2 control registers       .4-31         4.4.7       PGAR — Port G assignment register       .4-33         4.5.2       Program chip select       .4-33         4.5.3       I/O chip select control register       .4-33         4.5.4       CSCTL — Chip select control register       .4-35         4.5.5       General-purpose chip select 1 address register       .4-36 </td <td></td> <td></td> <td></td> |         |                         |      |

| 4.3.2.4       OPTION — System configuration options register 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |                         |      |

| 4.3.2.5       OPT2 — System configuration options register 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |                         |      |

| 4.3.2.6       BPROT — Block protect register       4-18         4.3.2.7       TMSK2 — Timer interrupt mask register 2       4-20         4.3.2.8       TCTL4 and TCTL6 — Timer 2 and 3 control registers       4-21         4.4       Memory expansion       4-22         4.4.1       Memory expansion logic       4-22         4.4.2       Extended addressing       4-23         4.4.3       Memory expansion examples       4-24         4.4.4       MMSIZ — Memory mapping window size register       4-29         4.4.5       MMWBR – Memory mapping window base register       4-30         4.4.6       MM1CR, MM2CR – Memory mapping window base register       4-31         4.4.7       PGAR — Port G assignment register       4-32         4.5.1       Chip select priorities       4-33         4.5.2       Program chip select       4-33         4.5.3       I/O chip select       4-33         4.5.4       CSCTL — Chip select control register       4-35         4.5.5.1       GPCS1A — General-purpose chip select 1 address register       4-35         4.5.5.3       GPCS1A — General-purpose chip select 2 address register       4-37         4.5.6       One chip select driving another       4-38         4.5.7.       Clock stretchin                                                           |         |                         |      |

| 4.3.2.7       TMSK2 — Timer interrupt mask register 2       .4-20         4.3.2.8       TCTL4 and TCTL6 — Timer 2 and 3 control registers       .4-21         4.4       Memory expansion       .4-22         4.4.1       Memory expansion logic       .4-22         4.4.1       Memory expansion examples       .4-23         4.4.2       Extended addressing       .4-23         4.4.3       Memory expansion examples       .4-24         4.4.4       MMSIZ — Memory mapping window size register       .4-29         4.4.5       MMWBR – Memory mapping window base register       .4-30         4.4.6       MM1CR, MM2CR – Memory mapping window 1 and 2 control registers       .4-31         4.4.7       PGAR — Port G assignment register       .4-33         4.5.1       Chip select priorities       .4-33         4.5.2       Program chip select control register       .4-33         4.5.3       I/O chip select       .4-33         4.5.4       CSCTL — Chip select control register       .4-35         4.5.5       General-purpose chip select 1 address register       .4-36         4.5.5.4       GPCS1A — General-purpose chip select 2 control register       .4-37         4.5.5       GPCS1C — General-purpose chip select 2 control register       .4-37                                           |         |                         |      |

| 4.3.2.8       TCTL4 and TCTL6 — Timer 2 and 3 control registers       4-21         4.4       Memory expansion       4-22         4.4.1       Memory expansion logic       4-22         4.4.2       Extended addressing       4-23         4.4.3       Memory expansion examples       4-24         4.4.4       MMSIZ — Memory mapping window size register       4-29         4.4.5       MMWBR – Memory mapping window base register       4-30         4.4.6       MMICR, MM2CR – Memory mapping window 1 and 2 control registers       4-31         4.4.7       PGAR — Port G assignment register       4-32         4.5.1       Chip select priorities       4-33         4.5.2       Program chip select       4-33         4.5.3       I/O chip select control register       4-33         4.5.4       CSCTL — Chip select control register       4-35         4.5.5       General-purpose chip select 1 address register       4-36         4.5.5.1       GPCS1A — General-purpose chip select 2 control register       4-37         4.5.5.3       GPCS2A — General-purpose chip select 2 address register       4-37         4.5.5.4       GPCS2C — General-purpose chip select 2 control register       4-37         4.5.6       One chip select driving another       4-38 <td></td> <td></td> <td></td>       |         |                         |      |

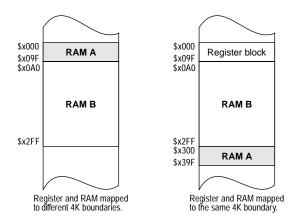

| 4.4       Memory expansion       4-22         4.4.1       Memory expansion logic       4-22         4.4.2       Extended addressing       4-23         4.4.3       Memory expansion examples       4-24         4.4.4       MMSIZ — Memory mapping window size register       4-29         4.4.5       MMWBR – Memory mapping window base register       4-30         4.4.6       MM1CR, MM2CR – Memory mapping window 1 and 2 control registers       4-31         4.4.7       PGAR — Port G assignment register       4-32         4.5       Chip select priorities       4-33         4.5.2       Program chip select       4-33         4.5.3       I/O chip select       4-33         4.5.4       CSCTL — Chip select control register       4-34         4.5.5       General-purpose chip select 1 address register       4-35         4.5.5.1       GPCS1A — General-purpose chip select 2 address register       4-36         4.5.5.2       GPCS1A — General-purpose chip select 2 control register       4-36         4.5.5.4       GPCS2C — General-purpose chip select 2 control register       4-37         4.5.5       General-purpose chip select 2 control register       4-38         4.5.7       Clock stretching       4-39         4.5.7                                                              |         |                         |      |

| 4.4.1       Memory expansion logic       4-22         4.4.2       Extended addressing       4-23         4.4.3       Memory expansion examples       4-24         4.4.4       MMSIZ — Memory mapping window size register       4-29         4.4.5       MMWBR – Memory mapping window base register       4-29         4.4.6       MMICR, MM2CR – Memory mapping window base register       4-30         4.4.6       MMICR, MM2CR – Memory mapping window 1 and 2 control registers       4-31         4.4.7       PGAR — Port G assignment register       4-32         4.5       Chip selects       4-33         4.5.2       Program chip select       4-33         4.5.4       CSCTL — Chip select control register       4-34         4.5.5       General-purpose chip select 1 address register       4-35         4.5.5       General-purpose chip select 2 address register       4-36         4.5.5.3       GPCS2A — General-purpose chip select 2 control register       4-37         4.5.6       One chip select driving another       4-38         4.5.7       Clock stretching       4-39         4.5.7.1       CSCSTR — Chip select clock stretch register       4-34         4.6.1       EEPROM and CONFIG register       4-41         4.6.1.2                                                             |         |                         |      |

| 4.4.2       Extended addressing       4-23         4.4.3       Memory expansion examples       4-24         4.4.4       MMSIZ — Memory mapping window size register       4-29         4.4.5       MMWBR – Memory mapping window base register       4-30         4.4.6       MM1CR, MM2CR – Memory mapping window 1 and 2 control registers       4-31         4.4.7       PGAR — Port G assignment register       4-32         4.5       Chip selects       4-33         4.5.2       Program chip select       4-33         4.5.3       I/O chip select control register       4-33         4.5.4       CSCTL — Chip select control register       4-34         4.5.5       General-purpose chip select 1 address register       4-35         4.5.5.1       GPCS1A — General-purpose chip select 1 control register       4-36         4.5.5.2       GPCS1C — General-purpose chip select 2 address register       4-37         4.5.6       One chip select driving another       4-38         4.5.7       Clock stretching       4-39         4.5.7       Clock stretching       4-39         4.5.7       Clock stretching       4-39         4.5.7       Clock stretching       4-41         4.6.1       EEPROM       4-41 <tr< td=""><td></td><td></td><td></td></tr<>                                              |         |                         |      |

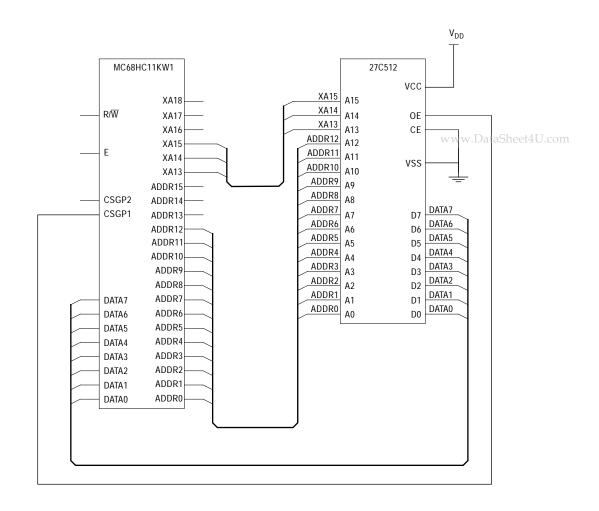

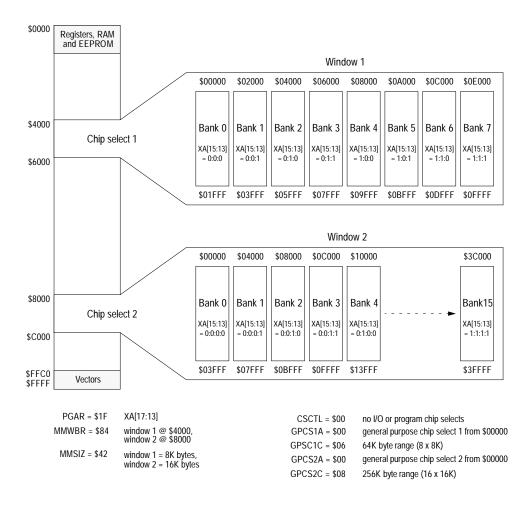

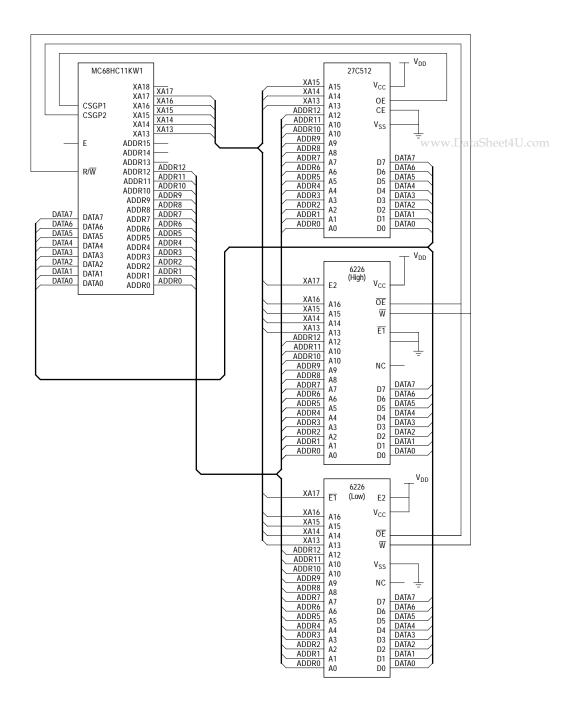

| 4.4.3       Memory expansion examples       4-24         4.4.4       MMSIZ — Memory mapping window size register       4-29         4.4.5       MMWBR – Memory mapping window base register       4-30         4.4.6       MM1CR, MM2CR – Memory mapping window 1 and 2 control registers       4-31         4.4.7       PGAR — Port G assignment register       4-32         4.5       Chip selects       4-32         4.5.1       Chip select priorities       4-33         4.5.2       Program chip select       4-33         4.5.3       I/O chip select       4-33         4.5.4       CSCTL — Chip select control register       4-34         4.5.5       General-purpose chip select 1 address register       4-35         4.5.5.1       GPCS1A — General-purpose chip select 1 control register       4-36         4.5.5.2       GPCS1C — General-purpose chip select 1 control register       4-36         4.5.5.3       GPCS2A — General-purpose chip select 2 address register       4-37         4.5.6       One chip select driving another       4-38         4.5.7       Clock stretching       4-39         4.6       EEPROM and CONFIG register       4-41         4.6.1       EEPROM       4-41         4.6.1.2       EEPROM pow erase                                                                 |         |                         |      |

| 4.4.4       MMSIZ — Memory mapping window size register       4-29         4.4.5       MMWBR – Memory mapping window base register       4-30         4.4.6       MM1CR, MM2CR – Memory mapping window 1 and 2 control registers       4-31         4.4.7       PGAR — Port G assignment register       4-32         4.5       Chip selects       4-32         4.5       Chip select priorities       4-33         4.5.1       Chip select priorities       4-33         4.5.2       Program chip select       4-33         4.5.3       I/O chip select control register       4-33         4.5.4       CSCTL — Chip select control register       4-34         4.5.5       General-purpose chip selects       4-35         4.5.5       GPCS1A — General-purpose chip select 1 address register       4-36         4.5.5.2       GPCS1C — General-purpose chip select 2 address register       4-37         4.5.5.4       GPCS2C — General-purpose chip select 2 control register       4-37         4.5.6       One chip select driving another       4-38         4.5.7       Clock stretching       4-39         4.5.7       Clock stretching       4-39         4.5.8       EEPROM and CONFIG register       4-41         4.6.1       EPROM <td< td=""><td></td><td></td><td></td></td<>                             |         |                         |      |

| 4.4.5       MMWBR – Memory mapping window base register       4-30         4.4.6       MM1CR, MM2CR – Memory mapping window 1 and 2 control registers       4-31         4.4.7       PGAR — Port G assignment register       4-32         4.5       Chip selects       4-32         4.5.1       Chip select priorities       4-33         4.5.2       Program chip select       4-33         4.5.3       I/O chip select       4-33         4.5.4       CSCTL — Chip select control register       4-34         4.5.5       General-purpose chip selects       4-35         4.5.5.1       GPCS1A — General-purpose chip select 1 address register       4-36         4.5.5.2       GPCS1C — General-purpose chip select 2 address register       4-37         4.5.5.3       GPCS2A — General-purpose chip select 2 control register       4-37         4.5.5.4       GPCS2C — General-purpose chip select 2 control register       4-37         4.5.6       One chip select driving another       4-38         4.5.7       Clock stretching       4-39         4.5.7       Clock stretching       4-39         4.5.7       Clock stretching register       4-41         4.6.1       EPROM       4-41         4.6.1       EPROM       4-41 </td <td></td> <td></td> <td></td>                                             |         |                         |      |

| 4.4.6MM1CR, MM2CR - Memory mapping window 1 and 2 control registers4-314.4.7PGAR — Port G assignment register4-324.5Chip selects4-324.5.1Chip select priorities4-334.5.2Program chip select4-334.5.3I/O chip select4-334.5.4CSCTL — Chip select control register4-344.5.5General-purpose chip selects4-354.5.6.1GPCS1A — General-purpose chip select 1 address register4-364.5.5.3GPCS2A — General-purpose chip select 2 address register4-374.5.6One chip select driving another4-384.5.7Clock stretching4-394.5.7Clock stretching4-394.5.7.1CSCSTR — Chip select clock stretch register4-394.6EEPROM and CONFIG register4-414.6.1.1PPROG — EEPROM programming control register4-434.6.1.3EEPROM bulk erase4-434.6.1.4EEPROM bulk erase4-434.6.1.4EEPROM bulk erase4-444.6.2CONFIG register programming4-44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |                         |      |

| 4.4.7       PGAR — Port G assignment register       4-32         4.5       Chip selects       4-32         4.5.1       Chip select priorities       4-33         4.5.2       Program chip select       4-33         4.5.3       I/O chip select       4-33         4.5.4       CSCTL — Chip select control register       4-34         4.5.5       General-purpose chip selects       4-35         4.5.5.1       GPCS1A — General-purpose chip select 1 address register       4-36         4.5.5.2       GPCS1C — General-purpose chip select 2 address register       4-37         4.5.5.3       GPCS2A — General-purpose chip select 2 control register       4-37         4.5.6       One chip select driving another       4-38         4.5.7       Clock stretching       4-39         4.5.7.1       CSCSTR — Chip select clock stretch register       4-39         4.6       EEPROM and CONFIG register       4-41         4.6.1       EEPROM conserver       4-43         4.6.1.1       PPROG — EEPROM programming control register       4-43         4.6.1.3       EEPROM bulk erase       4-43         4.6.1.4       EEPROM bulk erase       4-43         4.6.1.4       EEPROM bulk erase       4-43         4.6                                                                                              |         |                         |      |

| 4.5Chip selects4-324.5.1Chip select priorities4-334.5.2Program chip select4-334.5.3I/O chip select4-334.5.4CSCTL — Chip select control register4-344.5.5General-purpose chip selects4-354.5.5.1GPCS1A — General-purpose chip select 1 address register4-364.5.5.2GPCS1C — General-purpose chip select 2 address register4-374.5.5.3GPCS2A — General-purpose chip select 2 control register4-374.5.5.4GPCS2C — General-purpose chip select 2 control register4-394.5.7Clock stretching4-394.5.7Clock stretching4-394.6EEPROM and CONFIG register4-414.6.1EEPROM4-414.6.1.2EEPROM bulk erase4-434.6.1.3EEPROM bulk erase4-434.6.1.4EEPROM bulk erase4-444.6.2CONFIG register programming4-44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |                         |      |

| 4.5.1Chip select priorities.4-334.5.2Program chip select4-334.5.3I/O chip select4-334.5.4CSCTL — Chip select control register4-344.5.5General-purpose chip selects4-354.5.6GPCS1A — General-purpose chip select 1 address register4-364.5.5.2GPCS1C — General-purpose chip select 2 address register4-364.5.5.3GPCS2A — General-purpose chip select 2 control register4-374.5.6One chip select driving another4-384.5.7Clock stretching4-394.5.7Clock stretching4-394.6EEPROM and CONFIG register4-414.6.1EPROM4-414.6.1.1PPROG — EEPROM programming control register4-434.6.1.3EEPROM bulk erase4-434.6.1.4EEPROM byte erase4-444.6.2CONFIG register programming4-44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |                         |      |

| 4.5.2Program chip select4-334.5.3I/O chip select4-334.5.4CSCTL — Chip select control register4-344.5.5General-purpose chip selects4-354.5.5.1GPCS1A — General-purpose chip select 1 address register4-364.5.5.2GPCS1C — General-purpose chip select 1 control register4-364.5.5.3GPCS2A — General-purpose chip select 2 address register4-374.5.6One chip select driving another4-384.5.7Clock stretching4-394.5.7.1CSCSTR — Chip select clock stretch register4-394.6EEPROM and CONFIG register4-414.6.1EEPROM4-414.6.1.1PPROG — EEPROM programming control register4-434.6.1.3EEPROM for erase4-434.6.1.4EEPROM bulk erase4-444.6.2CONFIG register programming4-44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |                         |      |

| 4.5.3I/O chip select4-334.5.4CSCTL — Chip select control register4-344.5.5General-purpose chip selects4-354.5.5.1GPCS1A — General-purpose chip select 1 address register4-364.5.5.2GPCS1C — General-purpose chip select 1 control register4-364.5.5.3GPCS2A — General-purpose chip select 2 address register4-374.5.5.4GPCS2C — General-purpose chip select 2 control register4-374.5.5One chip select driving another4-384.5.7Clock stretching4-394.5.7.1CSCSTR — Chip select clock stretch register4-394.6EEPROM and CONFIG register4-414.6.1EEPROM4-414.6.1.1PPROG — EEPROM programming control register4-434.6.1.3EEPROM for erase4-434.6.1.4EEPROM bulk erase4-444.6.2CONFIG register programming4-44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         | • •                     |      |

| 4.5.4CSCTL — Chip select control register4-344.5.5General-purpose chip selects4-354.5.5.1GPCS1A — General-purpose chip select 1 address register4-354.5.5.2GPCS1C — General-purpose chip select 1 control register4-364.5.5.3GPCS2A — General-purpose chip select 2 address register4-374.5.6One chip select driving another4-384.5.7Clock stretching4-394.5.7.1CSCSTR — Chip select clock stretch register4-394.6EEPROM and CONFIG register4-414.6.1EEPROM4-414.6.1.1PPROG — EEPROM programming control register4-434.6.1.3EEPROM tow erase4-434.6.1.4EEPROM bulk erase4-444.6.2CONFIG register programming4-44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         | <b>o</b> 1              |      |

| 4.5.5General-purpose chip selects4-354.5.5.1GPCS1A — General-purpose chip select 1 address register4-354.5.5.2GPCS1C — General-purpose chip select 1 control register4-364.5.5.3GPCS2A — General-purpose chip select 2 address register4-374.5.5.4GPCS2C — General-purpose chip select 2 control register4-374.5.5One chip select driving another4-384.5.7Clock stretching4-394.5.7.1CSCSTR — Chip select clock stretch register4-394.6EEPROM and CONFIG register4-414.6.1EEPROM4-414.6.1.1PPROG — EEPROM programming control register4-434.6.1.3EEPROM tow erase4-434.6.1.4EEPROM bulk erase4-444.6.2CONFIG register programming4-44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         | •                       |      |

| 4.5.5.1GPCS1A — General-purpose chip select 1 address register4-354.5.5.2GPCS1C — General-purpose chip select 1 control register4-364.5.5.3GPCS2A — General-purpose chip select 2 address register4-374.5.5.4GPCS2C — General-purpose chip select 2 control register4-374.5.6One chip select driving another4-384.5.7Clock stretching4-394.5.7.1CSCSTR — Chip select clock stretch register4-394.6EEPROM and CONFIG register4-414.6.1EEPROM4-414.6.1.1PPROG — EEPROM programming control register4-434.6.1.3EEPROM tow erase4-434.6.1.4EEPROM bulk erase4-434.6.1.4EEPROM byte erase4-444.6.2CONFIG register programming4-44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |                         |      |

| 4.5.5.2GPCS1C — General-purpose chip select 1 control register4-364.5.5.3GPCS2A — General-purpose chip select 2 address register4-374.5.5.4GPCS2C — General-purpose chip select 2 control register4-374.5.6One chip select driving another4-384.5.7Clock stretching4-394.6EEPROM and CONFIG register4-414.6.1EEPROM4-414.6.1.1PPROG — EEPROM programming control register4-434.6.1.2EEPROM bulk erase4-434.6.1.3EEPROM row erase4-434.6.1.4EEPROM byte erase4-444.6.2CONFIG register programming4-44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |                         |      |

| 4.5.5.3GPCS2A — General-purpose chip select 2 address register4-374.5.5.4GPCS2C — General-purpose chip select 2 control register4-374.5.6One chip select driving another4-384.5.7Clock stretching4-394.5.7.1CSCSTR — Chip select clock stretch register4-394.6EEPROM and CONFIG register4-414.6.1EEPROM4-414.6.1.1PPROG — EEPROM programming control register4-414.6.1.2EEPROM bulk erase4-434.6.1.3EEPROM row erase4-434.6.1.4EEPROM byte erase4-444.6.2CONFIG register programming4-44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |                         |      |

| 4.5.5.4GPCS2C — General-purpose chip select 2 control register4-374.5.6One chip select driving another4-384.5.7Clock stretching4-394.5.7.1CSCSTR — Chip select clock stretch register4-394.6EEPROM and CONFIG register4-414.6.1EEPROM4-414.6.1.1PPROG — EEPROM programming control register4-414.6.1.2EEPROM bulk erase4-434.6.1.3EEPROM row erase4-434.6.1.4EEPROM byte erase4-444.6.2CONFIG register programming4-44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |                         |      |

| 4.5.6One chip select driving another4-384.5.7Clock stretching4-394.5.7.1CSCSTR — Chip select clock stretch register4-394.6EEPROM and CONFIG register4-414.6.1EEPROM4-414.6.1.1PPROG — EEPROM programming control register4-414.6.1.2EEPROM bulk erase4-434.6.1.3EEPROM row erase4-434.6.1.4EEPROM byte erase4-444.6.2CONFIG register programming4-44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |                         |      |

| 4.5.7Clock stretching4-394.5.7.1CSCSTR — Chip select clock stretch register4-394.6EEPROM and CONFIG register4-414.6.1EEPROM4-414.6.1.1PPROG — EEPROM programming control register4-414.6.1.2EEPROM bulk erase4-434.6.1.3EEPROM row erase4-434.6.1.4EEPROM byte erase4-444.6.2CONFIG register programming4-44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |                         |      |

| 4.5.7.1CSCSTR — Chip select clock stretch register4-394.6EEPROM and CONFIG register4-414.6.1EEPROM4-414.6.1.1PPROG — EEPROM programming control register4-414.6.1.2EEPROM bulk erase4-434.6.1.3EEPROM row erase4-434.6.1.4EEPROM byte erase4-444.6.2CONFIG register programming4-44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |                         |      |

| 4.6EEPROM and CONFIG register4-414.6.1EEPROM4-414.6.1.1PPROG — EEPROM programming control register4-414.6.1.2EEPROM bulk erase4-434.6.1.3EEPROM row erase4-434.6.1.4EEPROM byte erase4-444.6.2CONFIG register programming4-44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |                         |      |

| 4.6.1       EEPROM       4-41         4.6.1.1       PPROG — EEPROM programming control register       4-41         4.6.1.2       EEPROM bulk erase       4-43         4.6.1.3       EEPROM row erase       4-43         4.6.1.4       EEPROM byte erase       4-44         4.6.2       CONFIG register programming       4-44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |                         |      |

| 4.6.1.1PPROG — EEPROM programming control register.4-414.6.1.2EEPROM bulk erase.4-434.6.1.3EEPROM row erase.4-434.6.1.4EEPROM byte erase.4-444.6.2CONFIG register programming.4-44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4.6 El  | -                       |      |

| 4.6.1.2         EEPROM bulk erase         .4-43           4.6.1.3         EEPROM row erase         .4-43           4.6.1.4         EEPROM byte erase         .4-44           4.6.2         CONFIG register programming         .4-44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4.6.1   |                         |      |

| 4.6.1.3EEPROM row erase4-434.6.1.4EEPROM byte erase4-444.6.2CONFIG register programming4-44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4.6.1.1 |                         |      |

| 4.6.1.4EEPROM byte erase                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |                         |      |

| 4.6.2 CONFIG register programming                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         | EEPROM row erase        | 4-43 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4.6.1.4 | •                       |      |

| 4.6.3 RAM and EEPROM security4-45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |                         |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4.6.3   | RAM and EEPROM security | 4-45 |

#### 5

## **RESETS AND INTERRUPTS**

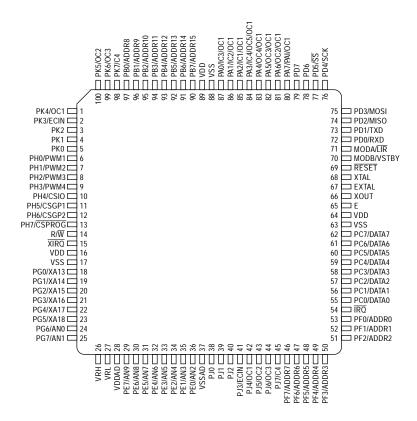

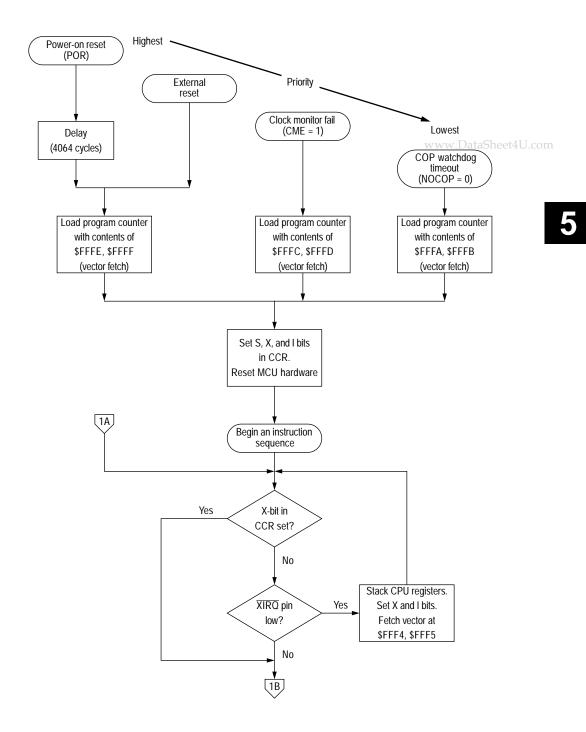

| 5.1   | Resets                 | 5-1 |

|-------|------------------------|-----|

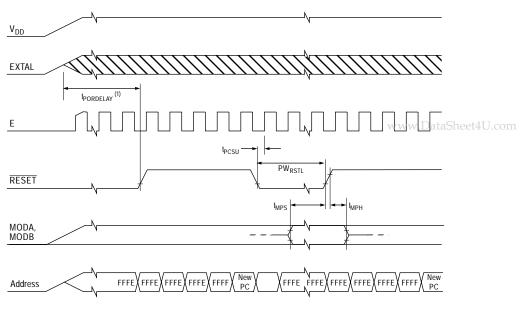

| 5.1.1 | Power-on reset         | 5-1 |

| 5.1.2 | External reset (RESET) | 5-2 |

| Paragraph | 1 |

|-----------|---|

| Number    |   |

| 5.1.3   | COP reset                                                   |      |

|---------|-------------------------------------------------------------|------|

| 5.1.3.1 | COPRST — Arm/reset COP timer circuitry register             |      |

| 5.1.4   | Clock monitor reset                                         |      |

| 5.1.5   | OPTION — System configuration options register 1            |      |

| 5.1.6   | CONFIG — Configuration control register                     |      |

|         | fects of reset                                              |      |

| 5.2.1   | Central processing unit                                     | 5-7  |

| 5.2.2   | Memory map                                                  |      |

| 5.2.3   | Parallel I/O                                                | 5-7  |

| 5.2.4   | Timer 1                                                     | 5-7  |

| 5.2.5   | Timers 2 and 3                                              | 5-8  |

| 5.2.6   | Real-time interrupt (RTI)                                   | 5-8  |

| 5.2.7   | Pulse accumulator                                           |      |

| 5.2.8   | Computer operating properly (COP)                           | 5-8  |

| 5.2.9   | Serial communications interface (SCI)                       | 5-8  |

| 5.2.10  | Serial peripheral interface (SPI)                           | 5-9  |

| 5.2.11  | Analog-to-digital converter                                 | 5-9  |

| 5.2.12  | System                                                      | 5-9  |

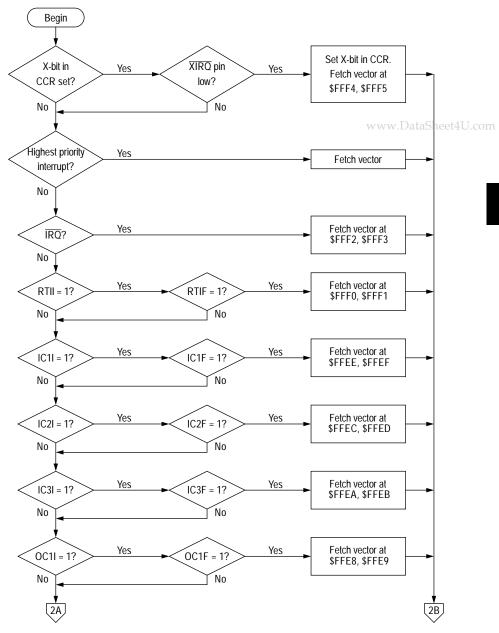

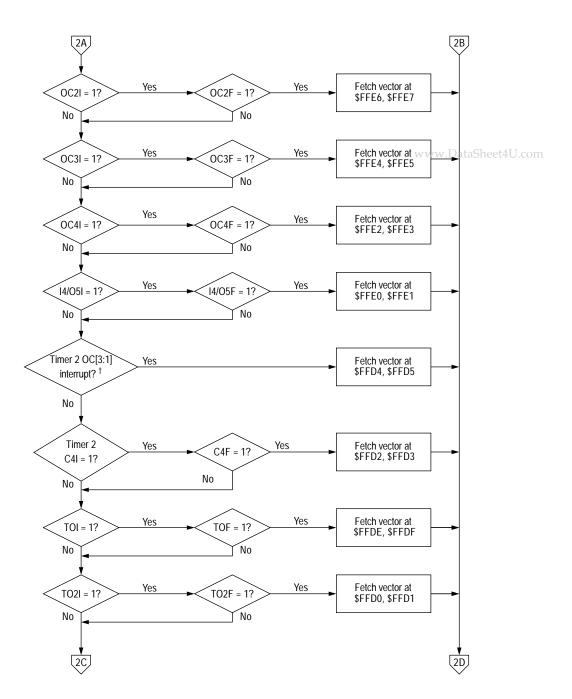

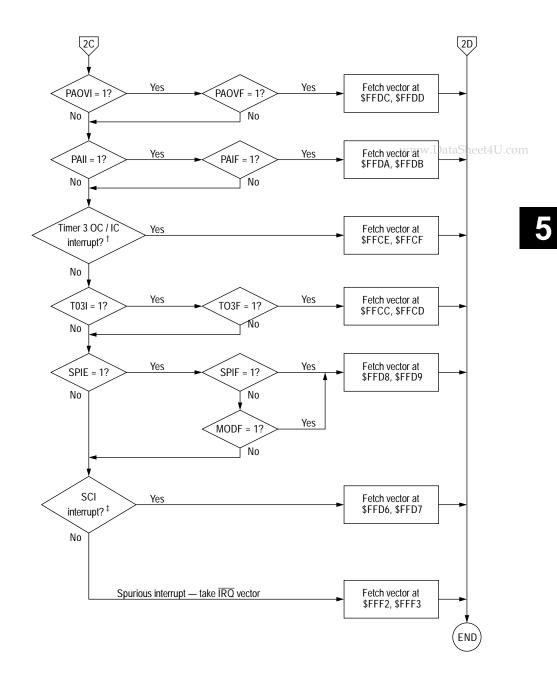

| 5.3 Re  | eset and interrupt priority                                 | 5-9  |

| 5.3.1   | HPRIO — Highest priority I-bit interrupt and misc. register | 5-10 |

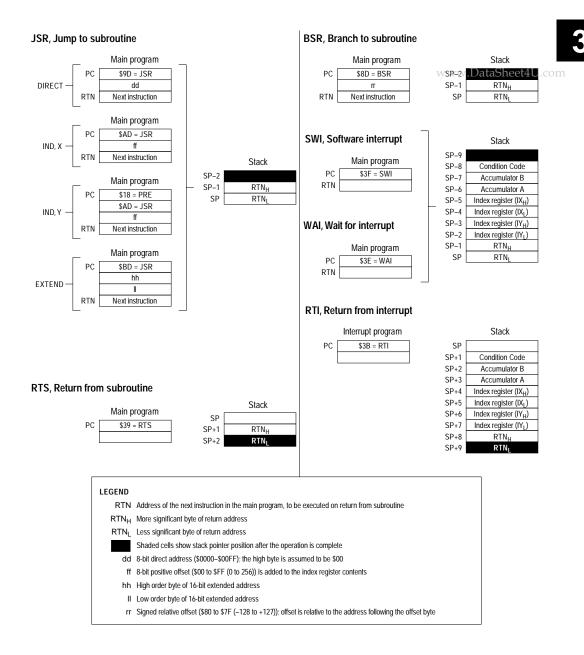

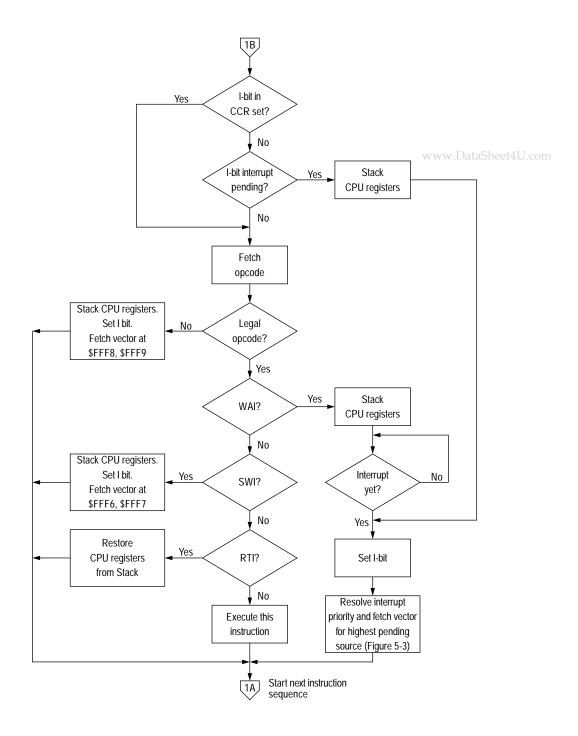

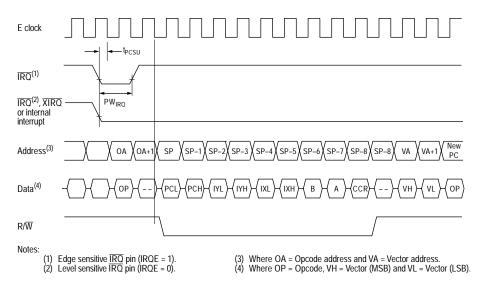

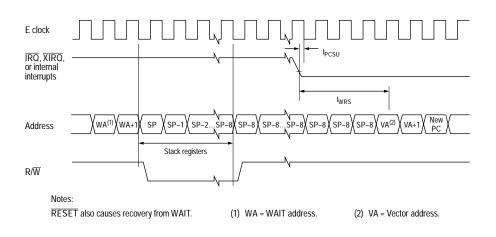

| 5.4 Int | terrupts                                                    | 5-13 |

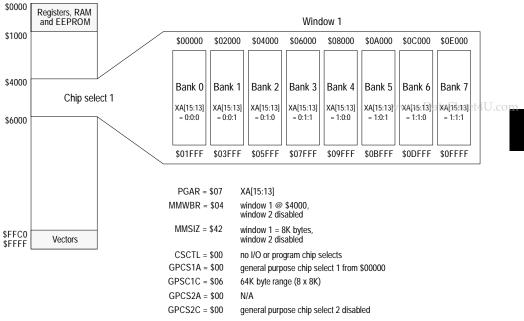

| 5.4.1   | Interrupt recognition and register stacking                 | 5-13 |

| 5.4.2   | Nonmaskable interrupt request (XIRQ)                        | 5-14 |

| 5.4.3   | Illegal opcode trap                                         | 5-14 |

| 5.4.4   | Software interrupt                                          | 5-14 |

| 5.4.5   | Maskable interrupts                                         | 5-15 |

| 5.4.6   | Reset and interrupt processing                              | 5-15 |

| 5.5 Lo  | w power operation                                           | 5-15 |

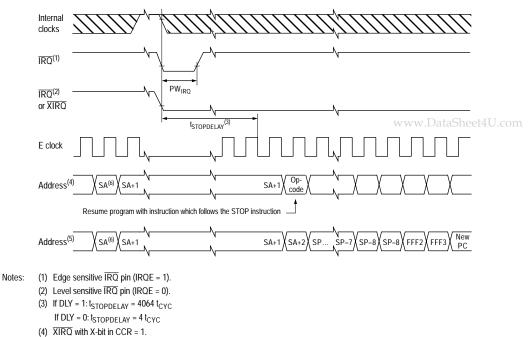

| 5.5.1   | WAIT                                                        |      |

| 5.5.2   | STOP                                                        | 5-16 |

|         |                                                             |      |

#### 6

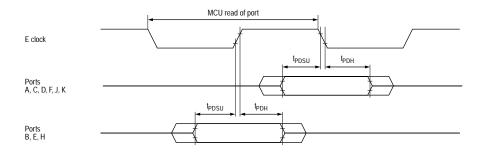

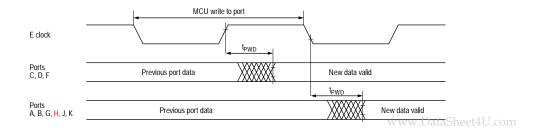

#### PARALLEL INPUT/OUTPUT

| 6.1   | Port A                                    | .6-2 |

|-------|-------------------------------------------|------|

| 6.1.1 | PORTA — Port A data register              | .6-2 |

| 6.1.2 | DDRA — Data direction register for port A | .6-2 |

| 6.2   | Port B                                    | .6-3 |

| 6.2.1 | PORTB — Port B data register              | .6-3 |

| 6.2.2 | DDRB — Data direction register for port B | .6-3 |

| 6.3   | Port C                                    | .6-4 |

| 6.3.1 | PORTC — Port C data register              | .6-4 |

| 6.3.2 | DDRC — Data direction register for port C | .6-4 |

| 6.4   | Port D                                    | .6-5 |

| 6.4.1 | PORTD — Port D data register              | .6-5 |

| 6.4.1 | PORTD — Port D data register              | .6-5 |

Paragraph Number

| 6.4.2 DDRD — Data direction register for port D       | 6-5                          |

|-------------------------------------------------------|------------------------------|

| 6.5 Port E                                            | 6-6                          |

| 6.5.1 PORTE — Port E data register                    | 6-6                          |

| 6.6 Port F                                            | 6-7                          |

| 6.6.1 PORTF — Port F data register                    | 6-7                          |

| 6.6.2 DDRF — Data direction register for port F       | www.DataSh <b>6=7</b> 4U.com |

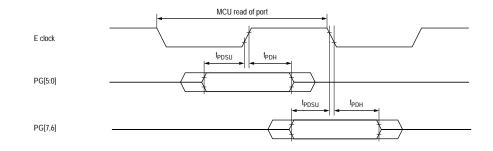

| 6.7 Port G                                            | 6-8                          |

| 6.7.1 PORTG — Port G data register                    | 6-8                          |

| 6.7.2 DDRG — Data direction register for port G       | 6-9                          |

| 6.7.3 PGAR — Port G assignment register               | 6-9                          |

| 6.8 Port H                                            | 6-10                         |

| 6.8.1 PORTH — Port H data register                    | 6-10                         |

| 6.8.2 DDRH — Data direction register for port H       | 6-10                         |

| 6.9 Port J                                            | 6-11                         |

| 6.9.1 PORTJ — Port J data register                    | 6-11                         |

| 6.9.2 DDRJ — Data direction register for port J       | 6-11                         |

| 6.10 Port K                                           | 6-12                         |

| 6.10.1 PORTK — Port K data register                   | 6-12                         |

| 6.10.2 DDRK — Data direction register for port K      | 6-12                         |

| 6.11 Internal pull-up resistors                       | 6-13                         |

| 6.11.1 PPAR — Port pull-up assignment register        | 6-13                         |

| 6.12 System configuration                             | 6-14                         |

| 6.12.1 OPT2 — System configuration options register 2 | 6-14                         |

| 6.12.2 CONFIG — System configuration register         |                              |

|                                                       |                              |

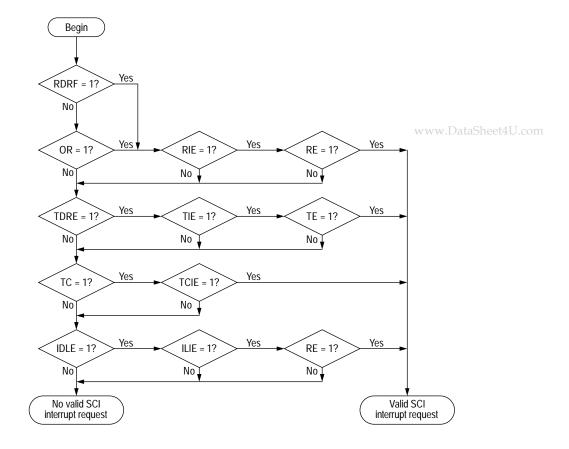

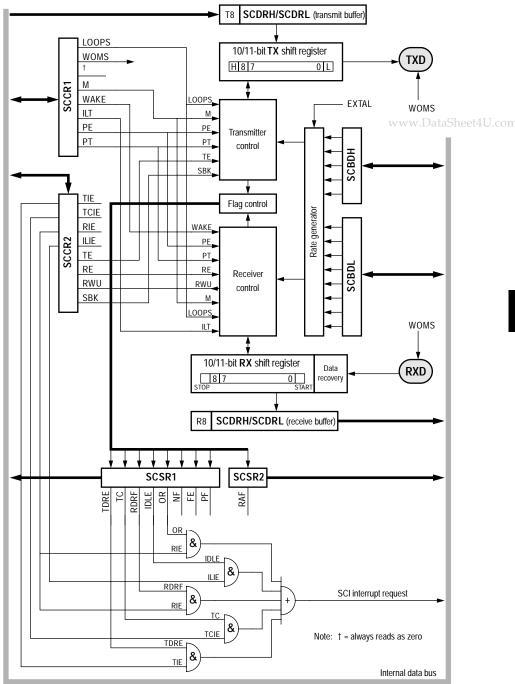

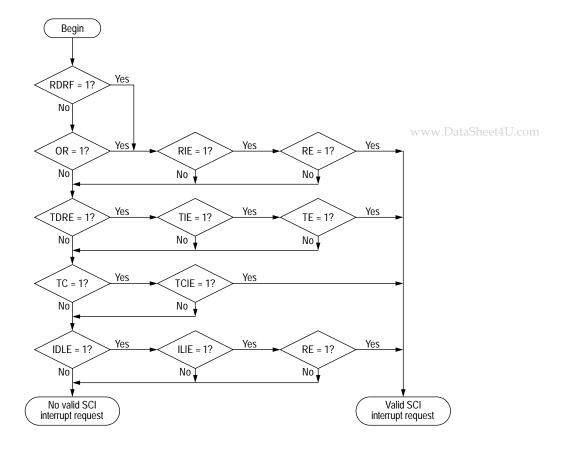

#### 7 SERIAL COMMUNICATIONS INTERFACE

| 7.1   | Data format                                    |      |

|-------|------------------------------------------------|------|

| 7.2   | Transmit operation                             | 7-2  |

| 7.3   | Receive operation                              | 7-2  |

| 7.4   | Wake-up feature                                |      |

| 7.4.1 | Idle-line wake-up                              | 7-4  |

| 7.4.2 | Address-mark wake-up                           |      |

| 7.5   | SCI error detection                            |      |

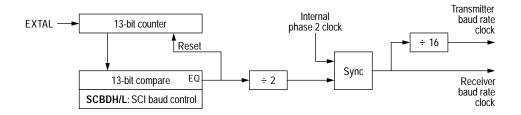

| 7.6   | SCI registers                                  | 7-5  |

| 7.6.1 | SCBDH, SCBDL — SCI baud rate control registers |      |

| 7.6.2 | SCCR1 — SCI control register 1                 | 7-7  |

| 7.6.3 | SCCR2 — SCI control register 2                 | 7-9  |

| 7.6.4 | SCSR1 — SCI status register 1                  | 7-10 |

| 7.6.5 | SCSR2 — SCI status register 2                  | 7-11 |

| 7.6.6 | SCDRH, SCDRL — SCI data high/low registers     | 7-12 |

| 7.7   | Status flags and interrupts                    |      |

| 7.7.1 | Receiver flags                                 | 7-13 |

|       |                                                |      |

#### TITLE

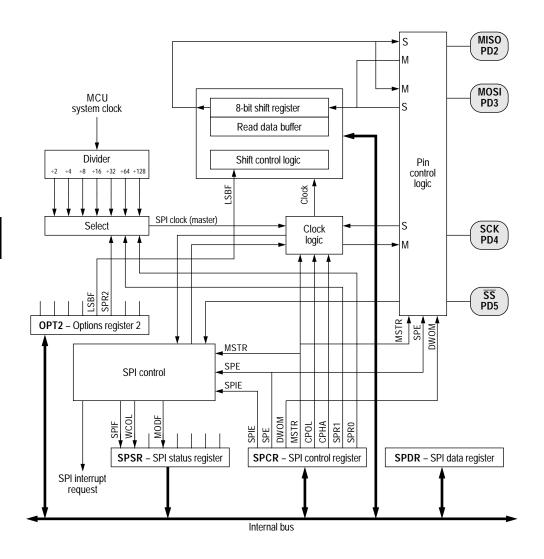

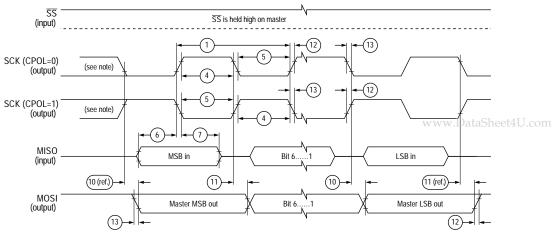

#### 8 SERIAL PERIPHERAL INTERFACE

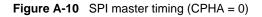

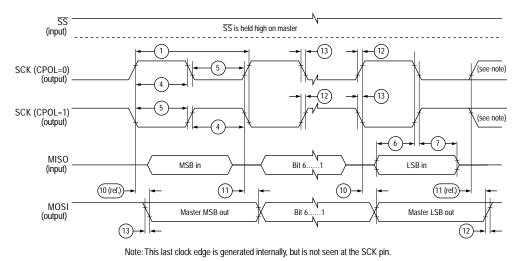

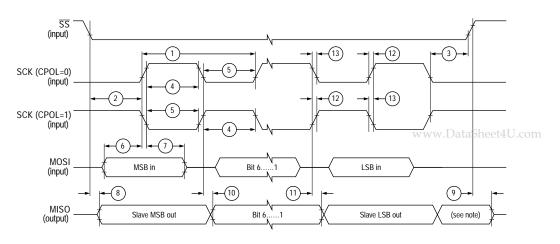

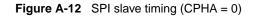

| 8.1   | Functional description                         |                     |

|-------|------------------------------------------------|---------------------|

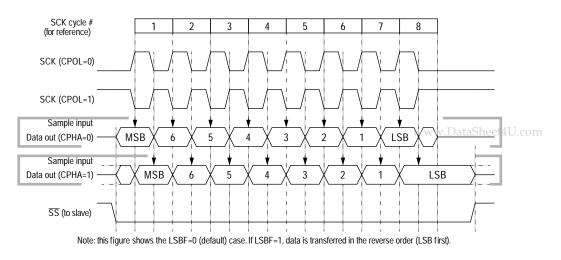

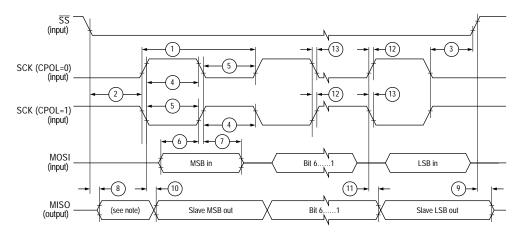

| 8.2   | SPI transfer formats                           | 8-2                 |

| 8.2.1 | Clock phase and polarity controls              | www.DataSheet4U.con |

| 8.3   | SPI signals                                    |                     |

| 8.3.1 | Master in slave out                            | 8-4                 |

| 8.3.2 | Master out slave in                            |                     |

| 8.3.3 | Serial clock                                   |                     |

| 8.3.4 | Slave select                                   |                     |

| 8.4   | SPI system errors                              | 8-5                 |

| 8.5   | SPI registers                                  | 8-5                 |

| 8.5.1 | SPCR — SPI control register                    |                     |

| 8.5.2 | SPSR — SPI status register                     | 8-8                 |

| 8.5.3 | SPDR — SPI data register                       | 8-9                 |

| 8.5.4 | OPT2 — System configuration options register 2 | 8-9                 |

|       |                                                |                     |

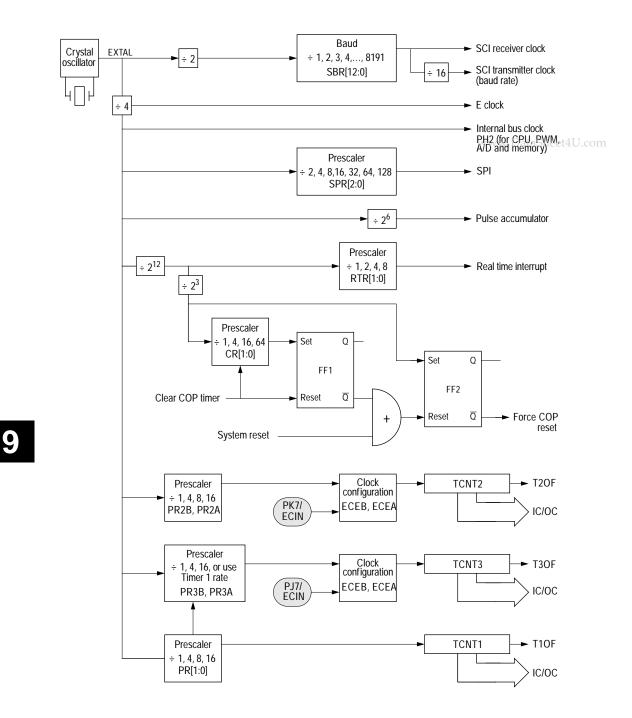

#### 9

#### TIMING SYSTEM

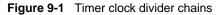

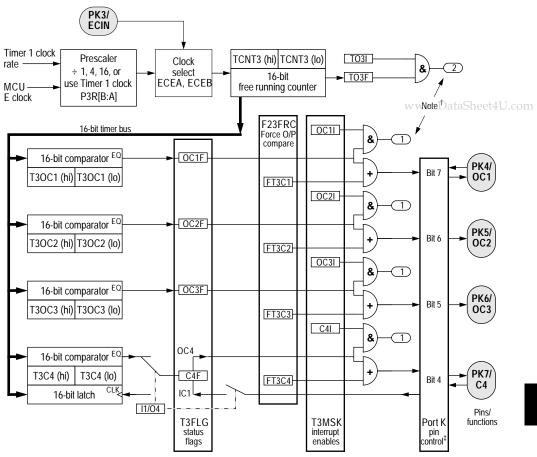

| 9.1 T    | ïmer 1                                                   | 9-1  |

|----------|----------------------------------------------------------|------|

| 9.1.1    | Timer 1 structure                                        | 9-3  |

| 9.1.2    | Input capture                                            | 9-4  |

| 9.1.2.1  | TCTL2 — Timer control register 2                         | 9-6  |

| 9.1.2.2  | TIC1–TIC3 — Timer input capture registers                | 9-7  |

| 9.1.2.3  | TI4/O5 — Timer input capture 4/output compare 5 register | 9-7  |

| 9.1.3    | Output compare                                           | 9-8  |

| 9.1.3.1  | TOC1–TOC4 — Timer output compare registers               | 9-9  |

| 9.1.3.2  | CFORC — Timer compare force register                     | 9-9  |

| 9.1.3.3  | OC1M — Output compare 1 mask register                    | 9-10 |

| 9.1.3.4  | OC1D — Output compare 1 data register                    | 9-10 |

| 9.1.3.5  | TCNT — Timer counter register                            | 9-11 |

| 9.1.3.6  | TCTL1 — Timer control register 1                         | 9-11 |

| 9.1.3.7  | TMSK1 — Timer interrupt mask register 1                  | 9-12 |

| 9.1.3.8  | TFLG1 — Timer interrupt flag register 1                  |      |

| 9.1.3.9  | TMSK2 — Timer interrupt mask register 2                  | 9-14 |

| 9.1.3.10 | TFLG2 — Timer interrupt flag register 2                  | 9-15 |

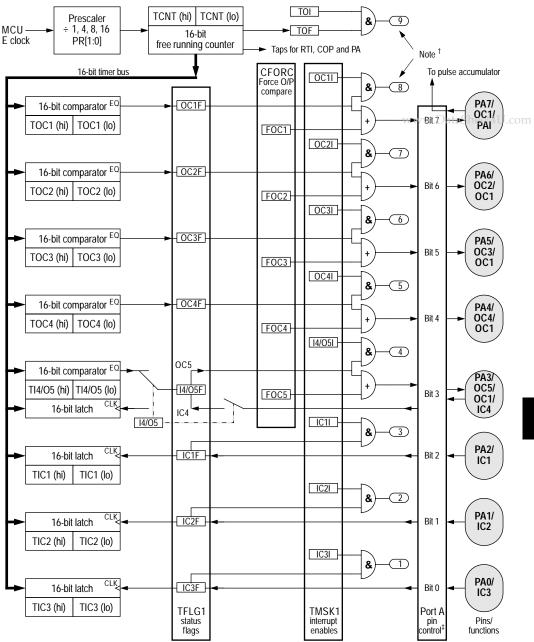

| 9.2 T    | ïmer 2                                                   | 9-15 |

| 9.2.1    | Output compare                                           | 9-18 |

| 9.2.2    | Input capture                                            | 9-18 |

| 9.2.3    | F23FRC — Compare force register for Timers 2 and 3       | 9-18 |

| 9.2.4    | T2C4 — Timer 2 channel 4 register                        | 9-19 |

| 9.2.5    | T2OC1–T2OC3 — Timer 2 output compare registers           | 9-19 |

| 9.2.6    | TCNT2 — Timer 2 counter register                         | 9-20 |

| Paragraph |

|-----------|

| Number    |

| 9.2.7 TCTL3 — Timer control register 3 (Timer 2)                |                                |

|-----------------------------------------------------------------|--------------------------------|

| 9.2.8 TCTL4 — Timer control register 4 (Timer 2)                |                                |

| 9.2.9 T2MSK — Timer 2 interrupt mask register                   | 9-22                           |

| 9.2.10 T2FLG — Timer 2 interrupt flag register                  | 9-23                           |

| 9.3 Timer 3                                                     |                                |

| 9.3.1 T3C4 — Timer 3 channel 4 register                         | <u>w.DataSh<b>9=24</b>U.co</u> |

| 9.3.2 T3OC1-T3OC3 — Timer 3 output compare registers            | 9-26                           |

| 9.3.3 TCNT3 — Timer 3 counter register                          |                                |

| 9.3.4 TCTL5 — Timer control register 5 (Timer 3)                |                                |

| 9.3.5 TCTL6 — Timer control register 6 (Timer 3)                | 9-27                           |

| 9.3.6 T3MSK — Timer 3 interrupt mask register                   | 9-29                           |

| 9.3.7 T3FLG — Timer 3 interrupt flag register                   | 9-30                           |

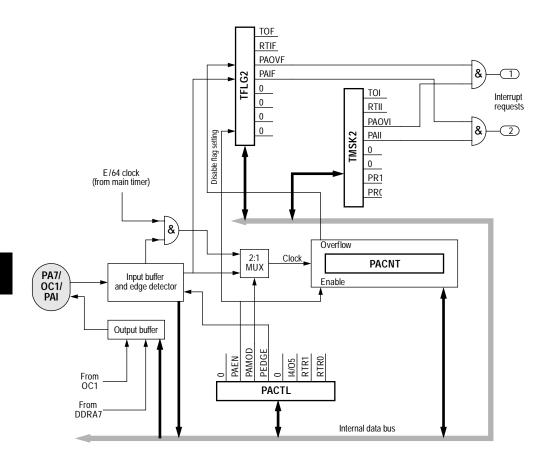

| 9.4 Real-time interrupt                                         | 9-31                           |

| 9.4.1 TMSK2 — Timer interrupt mask register 2                   |                                |

| 9.4.2 TFLG2 — Timer interrupt flag register 2                   | 9-32                           |

| 9.4.3 PACTL — Pulse accumulator control register                | 9-33                           |

| 9.5 Computer operating properly watchdog function               | 9-33                           |

| 9.6 Pulse accumulator                                           | 9-33                           |

| 9.6.1 PACTL — Pulse accumulator control register                | 9-35                           |

| 9.6.2 PACNT — Pulse accumulator count register                  | 9-36                           |

| 9.6.3 Pulse accumulator status and interrupt bits               | 9-36                           |

| 9.6.3.1 TMSK2 — Timer interrupt mask 2 register                 | 9-36                           |

| 9.6.3.2 TFLG2 — Timer interrupt flag 2 register                 | 9-36                           |

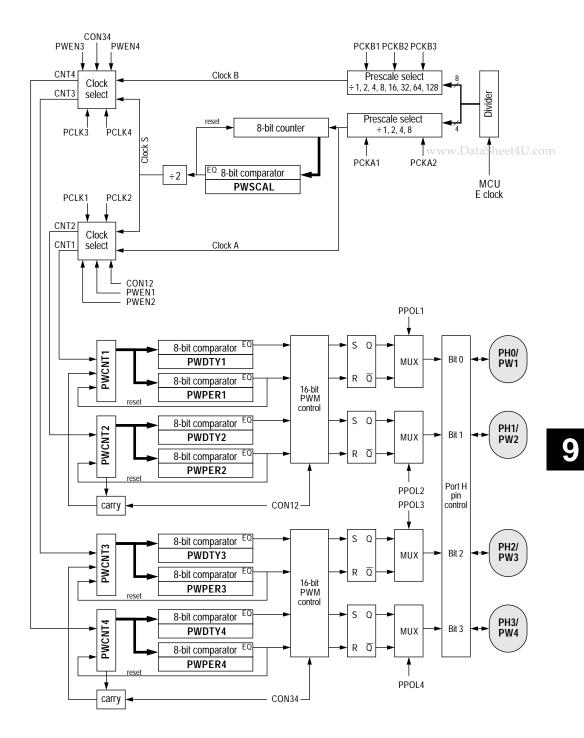

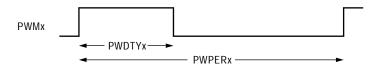

| 9.7 Pulse-width modulation (PWM) timer                          | 9-37                           |

| 9.7.1 PWM timer block diagram                                   | 9-38                           |

| 9.7.2 PWCLK — PWM clock prescaler and 16-bit select register    | 9-38                           |

| 9.7.2.1 16-bit PWM function                                     | 9-38                           |

| 9.7.2.2 Clock prescaler selection                               | 9-40                           |

| 9.7.3 PWPOL — PWM timer polarity & clock source select register |                                |

| 9.7.4 PWSCAL — PWM timer prescaler register                     | 9-41                           |

| 9.7.5 PWEN — PWM timer enable register                          | 9-42                           |

| 9.7.6 PWCNT1-4 — PWM timer counter registers 1 to 4             |                                |

| 9.7.7 PWPER1-4 — PWM timer period registers 1 to 4              |                                |

| 9.7.8 PWDTY1-4 — PWM timer duty cycle registers 1 to 4          |                                |

| 9.7.9 Boundary cases                                            |                                |

| -                                                               |                                |

#### 10 ANALOG-TO-DIGITAL CONVERTER

| 10.1   | Conversion process            |      |

|--------|-------------------------------|------|

| 10.2   | Channel assignments           |      |

| 10.3   | Single channel operation      |      |

| 10.3.1 | 4-conversion, single scan     |      |

| 10.3.2 | 4-conversion, continuous scan |      |

| 10.3.3 | 8-conversion, single scan     | 10-4 |

#### Paragraph Number

#### TITLE

Page Number

| 10.3.4 8-conversion, continuous scan                   | 10-4                                 |

|--------------------------------------------------------|--------------------------------------|

| 10.4 Multiple channel operation                        | 10-4                                 |

| 10.4.1 4-channel single scan                           | 10-5                                 |

| 10.4.2 4-channel continuous scan                       | 10-5                                 |

| 10.4.3 8-channel single scan                           | 10-5                                 |

| 10.4.4 8-channel continuous scan                       | <u>www.D</u> 4 <b>0-5</b> heet4U.com |

| 10.5 Power-up and clock select                         | 10-5                                 |

| 10.6 Operation in STOP and WAIT modes                  | 10-6                                 |

| 10.7 Registers                                         | 10-6                                 |

| 10.7.1 ADCTL — A/D control and status register         | 10-6                                 |

| 10.7.2 ADFRQ — A/D converter frequency select register | 10-7                                 |

| 10.7.3 ADR1 — ADR8 A/D result registers                | 10-8                                 |

|                                                        |                                      |

#### A ELECTRICAL SPECIFICATIONS