# MC68HC04P2 MC68HC04P3

# **Product Preview**

## 8-BIT HCMOS MICROCOMPUTER UNITS

The MC68HC04P2 and MC68HC04P3 HCMOS microcomputer units (MCUs) are members of the M68HC04 Family of very low-cost single-chip microcomputers. These 8-bit microcomputers contain a CPU, on-chip CLOCK, ROM, RAM, I/O, and TIMER. They are designed for the user who needs an economical microcomputer with the proven capabilities of the M6800-based instruction set. The following are some of the hardware and software highlights of the MC68HC04P2 and MC68HC04P3 microcomputers.

#### HARDWARE FEATURES

- Low Power HCMOS

- Power Saving Stop and Wait Modes

- 8-Bit Architecture

- MC68HC04P2 and MC68HC04P3 are Pin Compatible With the MC6804P2

- RAM: MC68HC04P2 32 Bytes MC68HC04P3 — 128 Bytes

- Memory Mapped I/O

- User ROM: MC68HC04P2 1024 Bytes MC68HC04P3 — 2048 Bytes

- 72 Bytes of ROM for Look-Up Tables

- 20 TTL/CMOS Compatible Bidirectional I/O Lines (Eight Lines are LED Compatible)

- On-Chip Clock Generator

- Self-Check Mode

- Master Reset

- Complete Development System Support on EXORciser

- Software Programmable Timer Prescaler

- 5 Volt Single Supply

#### SOFTWARE FEATURES

- Similar to M6800 Family

- Byte Efficient Instruction Set

- Easy to Program

- True Bit Manipulation

- Bit Test and Branch Instruction

- Versatile Interrupt Handling

- Versatile Indirect Registers

- Conditional Branches

- Single Instruction Memory Examine/Change

- Timer Pin is Software Programmable as Clock Input or Timer Input

- 10 Powerful Addressing Modes

## **USER SELECTABLE OPTIONS**

- 20 Bidirectional I/O Lines with TTL or TTL/CMOS Interface Option

- Crystal or Low-Cost Resistor Oscillator Option

- Vectored Interrupts: Timer, Software, and External

- Mask Selectable Edge- or Level-Sensitive Interrupt Pin

# **HCMOS**

(HIGH-DENSITY CMOS SILICON-GATE)

8-BIT HCMOS MICROCOMPUTERS

| PIN ASSIGNMENT           |     |        |    |              |

|--------------------------|-----|--------|----|--------------|

| vss d                    | 1 • | $\neg$ | 28 | RESET        |

| IRQ [                    | 2   |        | 27 | <b>1</b> PA7 |

| v <sub>cc</sub> <b>c</b> | 3   |        | 26 | <b>1</b> PA6 |

| EXTAL <b>C</b>           | 4   |        | 25 | PA5          |

| XTAL <b>[</b>            | 5   |        | 24 | PA4          |

| MDS <b>[</b>             | 6   |        | 23 | PA3          |

| TIMER [                  | 7   |        | 22 | PA2          |

| PC0 <b>[</b>             | 8   |        | 21 | PA1          |

| PC1 <b>[</b>             | 9   |        | 20 | PA0          |

| PC2                      | 10  |        | 19 | PB7          |

| РСЗ 🕻                    | 11  |        | 18 | <b>T</b> PB6 |

| <b>РВО </b>              | 12  |        | 17 | <b>]</b> PB5 |

| РВ1 🕻                    | 13  |        | 16 | PB4          |

| РВ2 🚺                    | 14  |        | 15 | РВЗ          |

| ·                        |     |        |    |              |

This document contains information on a product under development. Motorola reserves the right to change or discontinue this product without notice.

# MC68HC04P2, MC68HC04P3

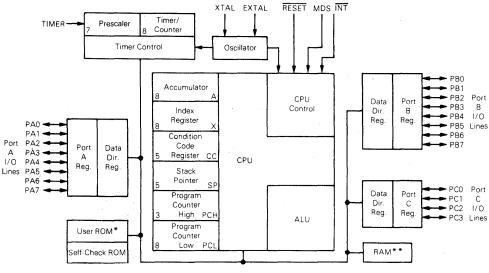

#### **BLOCK DIAGRAM**

- \*User ROM area: MC68HC04P2 = 1024 × 8 MC68HC04P3 = 2048 × 8

- \* \* RAM area: MC68HC04P2 =  $32 \times 8$  MC68HC04P3 =  $128 \times 8$

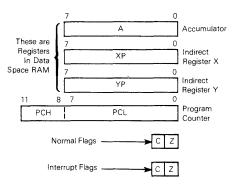

## PROGRAMMING MODEL