# MC68322

# Integrated Printer Processor User's Manual

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different applications. All opeating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent r ights nor the rights of others. Motorola products are not designed, intended, or author ized for use as components in systems intended for surgical implant into the body or other applications induces are not designed, intended, or author ized for use as components in Motorola product culd create a situation where personal injuy or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola we negligent regarding the design or madfacture of the pat. Motorola and its officers employees.

© 1997 Motorola, Inc. All Rights Reserved.

Windows Printing System<sup>™</sup> is a registered trademark of Microsoft Corporation. PostScript<sup>®</sup> is a registered trademark of Adobe Systems, Inc. Centronics<sup>®</sup> is a registered trademark of Centronics Inc. All other trademarks are the property of their respective owners.

## **ABOUT THIS MANUAL**

The *MC68322 Integrated Printer Processor User's Manual* contains information about the programming capabilities, registers, and overall operation of the MC68322 device.

### **CONVENTIONS**

The following conventions should help you navigate through this manual. Anything that is not on this list is in plain text.

- Signals, pins, lines, and bit names appear in uppercase text.

- Register acronyms appear in uppercase text, but their full names are in lowercase.

- Cross references appear in initial-cap bold text.

- Instructions appear in lowercase bold text.

All acronyms and mnemonics are defined the first time they appear in each section. The easiest way to start using this manual is to use the index to find the topic you're interested in.

### SUPPLEMENTAL DOCUMENTATION

There are two manuals available from Motorola that will enable you to have a more well-rounded reference source for the MC68322. To order them, see the back cover of this manual for the Motorola Literature Distribution Center contact information click here to go to the LDC website.

- The *M68000 Family Programmer's Reference Manual* (M68000PM/AD) provides instructions and detailed information on the EC000 core and other devices.

- The MC68322 Integrated Printer Processor Product Brief (MC68322P/D) provides a brief description of the MC68322's capabilities.

#### **GIVE US YOUR OPINION**

We are constantly trying to make our documentation easier to access and use, so please give us your feedback. You can either print out and send us the form on the following page or fill out the survey on the web at http://www.mot.com/SPS/ADC/site/docs\_survey.html. You can also visit the Motorola Imaging and Storage Division website at http://www.mot.com/isd for information about applications, errata, and other products. This manual is also available in PDF format at that site.

MOTOROLA

## MOTOROLA IMAGING AND STORAGE DIVISION CUSTOMER DOCUMENTATION SURVEY

Fill out this form and fax it to the ISD Information Development team at (512) 891-8593.

Title of Manual:

- 1. Did the information in this document appear to be organized in a logical manner?

- 2. Was the level of writing appropriate for you as a user of this Motorola product? \_\_\_\_\_

- 3. Were the illustrations and graphics clear and easy to understand? \_\_\_\_\_

- 4. Some information, such as signal summaries, may have been duplicated in other sections for the purpose of making it easier for you to use. Did you find it useful? \_\_\_\_\_

- 5. Did any of the technical information assume too much prerequisite knowledge? \_\_\_\_\_

- 6. If you answered yes to #5, do you need more task-oriented information? \_\_\_\_\_

- 7. Were there enough example applications in the manual? \_

- 8. The Information Development team is considering the placement of documentation on CD-ROM in the future. Does your computer have a CD player? \_\_\_\_\_

- 9. What information should we add to the next version of this document?

10. What information should we delete from the next version of this document?

11. Was there technical information in this document that you have a question about? Explain.

Thank you for your comments. They will be used to improve this and other Motorola customer documentation.

| lame:                   |

|-------------------------|

| itle:                   |

| Company:                |

| vddress:                |

| City/State/Zip/Country: |

| mail Address:           |

| Phone Number:           |

## TABLE OF CONTENTS

### Paragraph Number

### Title

Page Number

### Section 1 Introduction

| 1.1   | Features                  |  |

|-------|---------------------------|--|

| 1.2   | Processors and Modules    |  |

| 1.2.1 | The EC000 Core            |  |

| 1.2.2 | Graphics Unit             |  |

| 1.2.3 | Bus Interface Unit        |  |

| 1.2.4 | System Integration Module |  |

| 1.2.5 | DRAM Controller           |  |

| 1.2.6 | DMA Interface             |  |

| 1.2.7 | Parallel Port Interface   |  |

| 1.3   | Internal Memory Map       |  |

| 1.4   | Understanding the MC68322 |  |

| 1.4.1 | Printer Languages         |  |

| 1.4.2 | Bitmap                    |  |

| 1.4.3 | Banding                   |  |

| 1.4.4 | Halftoning                |  |

| 1.4.5 | Duplex Printing           |  |

|       |                           |  |

### Section 2 Signal Descriptions

| 2.1   | Address Bus                             | .2-3 |

|-------|-----------------------------------------|------|

| 2.2   | Data Bus                                | .2-3 |

| 2.3   | System Interface                        | .2-4 |

| 2.3.1 | Reset (RESET)                           | .2-4 |

| 2.3.2 | System Clock                            | .2-4 |

| 2.3.3 | High Impedance Mode                     |      |

| 2.4   | External Bus Master Interface           | .2-6 |

| 2.5   | DRAM Interface                          | .2-7 |

| 2.6   | DMA Interface                           | .2-8 |

| 2.7   | Printer Communication Interface         | .2-8 |

| 2.8   | Print Engine Video Controller Interface | .2-8 |

| 2.9   | Parallel Port Interface                 | .2-9 |

| Paragraph |

|-----------|

| Number    |

Title

Page Number

### Section 3 The Core

| 3.1 | Programming Model               | 3-1 |

|-----|---------------------------------|-----|

| 3.2 | Data Types and Addressing Modes | 3-3 |

| 3.3 | Instruction Set Summary         | 3-4 |

### Section 4 Bus Operation

| 4.1                            | EC000 Core Read Cycle                                                                                               | 4-1                       |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------|---------------------------|

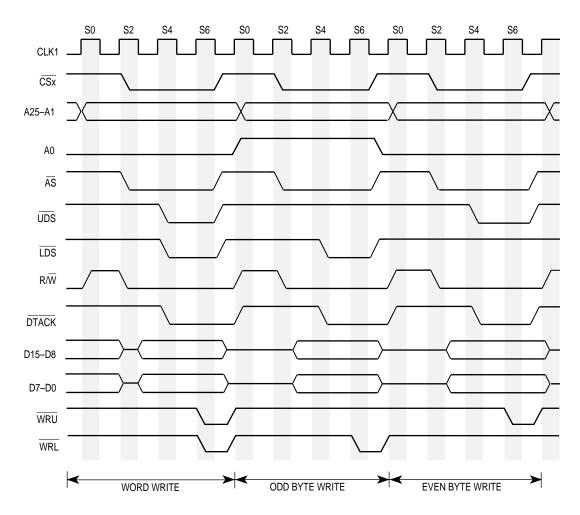

| 4.2                            | EC000 Core Write Cycle                                                                                              |                           |

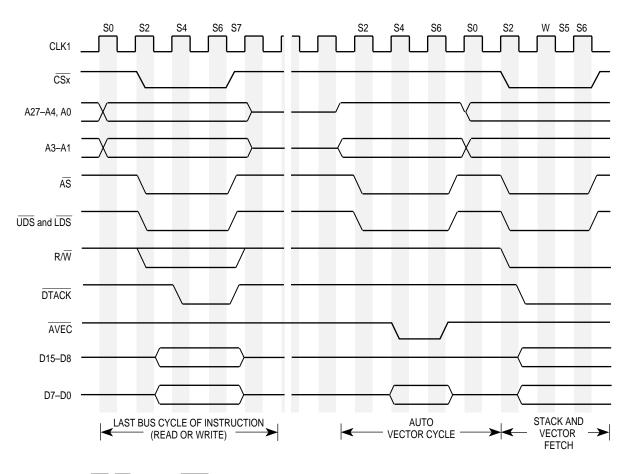

| 4.3                            | Interrupt Acknowledge Bus Cycle                                                                                     |                           |

| 4.4                            | Reset Operation                                                                                                     |                           |

| 4.5                            | External Bus Master                                                                                                 |                           |

| 4.5.1                          | MC68322 Bus Arbitration                                                                                             |                           |

| 4.5.2                          | External Bus Master Read Cycle                                                                                      |                           |

| 4.5.3                          | •                                                                                                                   |                           |

| 4.5.4                          | Illegal Address Interrupt                                                                                           |                           |

| 4.5<br>4.5.1<br>4.5.2<br>4.5.3 | External Bus Master<br>MC68322 Bus Arbitration<br>External Bus Master Read Cycle<br>External Bus Master Write Cycle | 4-5<br>4-5<br>4-10<br>4-1 |

### Section 5 Interrupt and Exception Handling

| 5.1   | Internal Interrupts            | 5-1  |

|-------|--------------------------------|------|

| 5.1.1 | Hardware Interrupts            | 5-2  |

| 5.1.2 | Software Interrupts            | 5-3  |

| 5.2   | External Interrupts            | 5-4  |

| 5.3   | Timer Module                   | 5-6  |

| 5.4   | Core Exception Handling        | 5-7  |

| 5.4.1 | Processing Specific Exceptions | 5-10 |

| 5.4.2 | Multiple Exceptions            | 5-13 |

| 5.4.3 | Exception Bus Cycles           | 5-14 |

| 5.5   | Module Soft-Reset Register     | 5-14 |

### Section 6 System Integration Module

| 6.1 | Chip-Select Registers And Banks                        | 6-1 |

|-----|--------------------------------------------------------|-----|

| 6.2 | Synchronous and AsynchronouS Chip-Select Access Timing | 6-4 |

| Paragraph |       |

|-----------|-------|

| Number    | Title |

Page Number

### Section 7 DRAM Controller

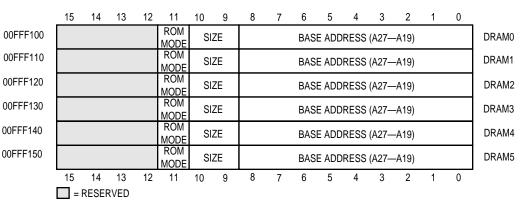

| 7.1     | DRAM Registers and Banks       | 7-1 |

|---------|--------------------------------|-----|

| 7.1.1   | Base Address and Size Fields   | 7-1 |

| 7.1.2   | ROM Mode                       | 7-2 |

| 7.1.2.1 | Functional Description         | 7-2 |

| 7.1.2.2 | Timing Example                 | 7-3 |

| 7.1.2.3 | Address Demultiplexing Circuit | 7-4 |

| 7.1.2.4 | Operational Example            | 7-4 |

| 7.2     | DRAM Control Register          |     |

| 7.3     | DRAM Timing Modes              |     |

| 7.4     | DRAM Accesses                  |     |

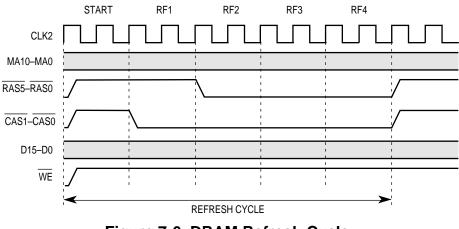

| 7.4.1   | DRAM Refresh Cycles            | 7-6 |

| 7.4.2   | DRAM Read Cycles               | 7-7 |

| 7.4.3   | DRAM Write Cycles              |     |

| 7.4.4   | DRAM Bus Arbitration           | 7-9 |

| 7.4.5   | DRAM Burst Accesses7           | -10 |

| 7.5     | Power-Up Sequence7             | -10 |

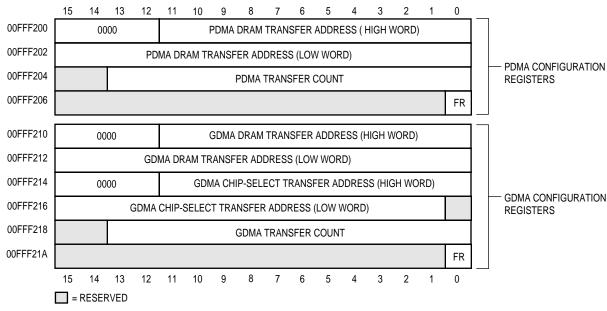

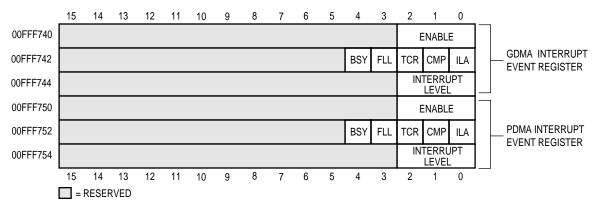

### Section 8 DMA Interface

| 8.1   | DMA Configuration Registers            | 8-2  |

|-------|----------------------------------------|------|

| 8.1.1 | Transfer Address Fields                | 8-2  |

| 8.1.2 | Transfer Count Fields                  | 8-3  |

| 8.1.3 | Flush Request Fields                   | 8-3  |

| 8.2   | GDMA Control Register                  | 8-3  |

| 8.3   | DMA Speed Register                     |      |

| 8.4   | DMA Interrupt Event Registers          | 8-5  |

| 8.5   | Initiating A DMA Operation             | 8-6  |

| 8.6   | DMA Transfers                          |      |

| 8.6.1 | PDMA Transfers                         | 8-7  |

| 8.6.2 | GDMA MC68322 Bus Read and Write Cycles | 8-7  |

| 8.6.3 | GDMA DRAM Bus Read and Write Cycles    | 8-8  |

| 8.7   | DMA Transfer Termination               | 8-9  |

| 8.7.1 | Normal Termination                     | 8-9  |

| 8.7.2 | Bad Address Termination                | 8-10 |

| 8.7.3 | Core-Forced Termination                | 8-10 |

### Paragraph Number

Title

Page Number

### Section 9 Parallel Port Interface

| 9.1     | PPI Registers                    |      |

|---------|----------------------------------|------|

| 9.1.1   | Parallel Port Interface Register |      |

| 9.1.2   | Parallel Port Control Register   | 9-4  |

| 9.1.3   | PPI Interrupt Event Register     | 9-6  |

| 9.2     | Hardware Handshaking             | 9-8  |

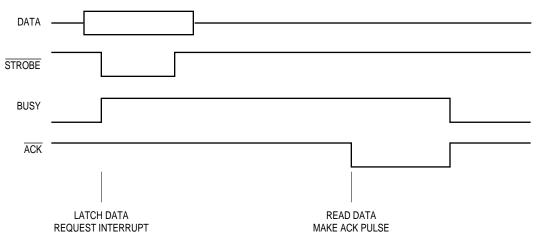

| 9.2.1   | Compatibility Handshaking        | 9-8  |

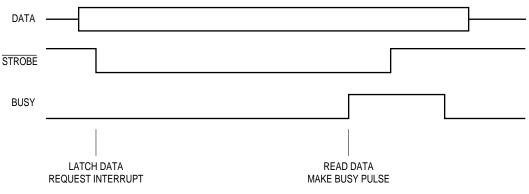

| 9.2.2   | ECP Handshaking                  |      |

| 9.2.2.1 | Command Byte Detection           | 9-9  |

| 9.2.2.2 | RLE Decompression                |      |

| 9.2.3   | Disabling Hardware Handshaking   | 9-10 |

| 9.3     | Software-Controlled Handshaking  | 9-11 |

| 9.4     | Digital Filtering                | 9-11 |

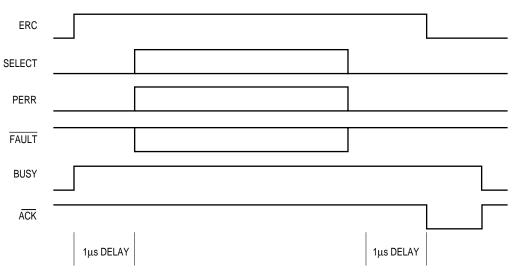

| 9.5     | Error Cycles                     |      |

| 9.6     | Parallel Port Data Bus Latching  | 9-13 |

| 9.7     | PPI on Reset                     | 9-14 |

| 9.8     | PPI Data Transfer Rate           | 9-14 |

|         |                                  |      |

### Section 10 Print Engine Interface

| 10.1     | Print Engine Interface Registers               |       |

|----------|------------------------------------------------|-------|

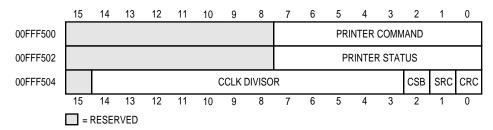

| 10.1.1   | Printer Communication Register                 |       |

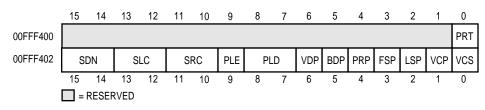

| 10.1.2   | PVC Control Register                           |       |

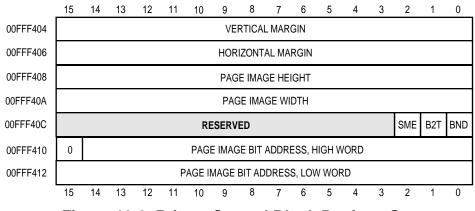

| 10.1.3   | Printer Control Block Register Set             |       |

| 10.1.4   | PVC Interrupt Event Register                   |       |

| 10.1.5   | Printer Communication Interrupt Event Register |       |

| 10.2     | Printer Communication Protocol                 |       |

| 10.3     | Print Engine Interface Operation               |       |

| 10.3.1   | Synchronous/Asynchronous PVC Operation         |       |

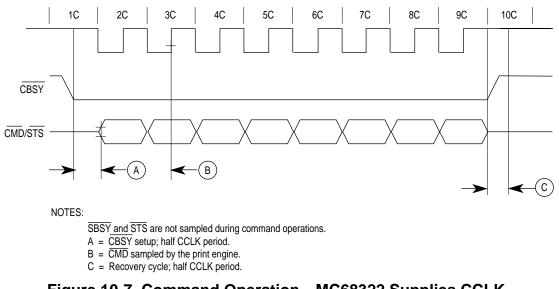

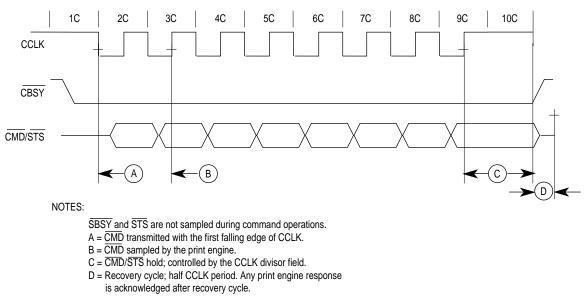

| 10.3.2   | Command Operation                              | 10-11 |

| 10.3.2.1 | CCLK Supplied By MC68322                       |       |

| 10.3.2.2 | CCLK Supplied By Print Engine                  | 10-12 |

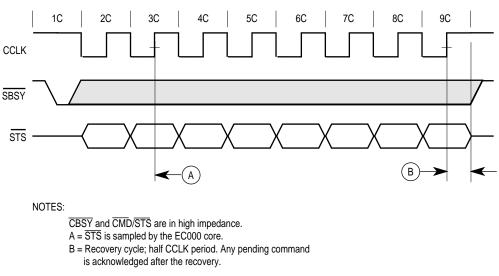

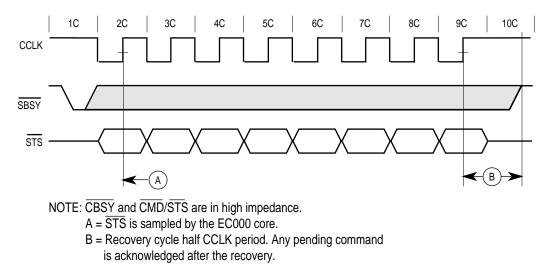

| 10.3.3   | Status Operation                               |       |

| 10.3.3.1 | CCLK Supplied By MC68322                       |       |

| 10.3.3.2 | CCLK Supplied By Print Engine                  |       |

| 10.3.4   | PLL Video Clock Divisor                        | 10-15 |

| 10.4     | PVC On Reset                                   | 10-16 |

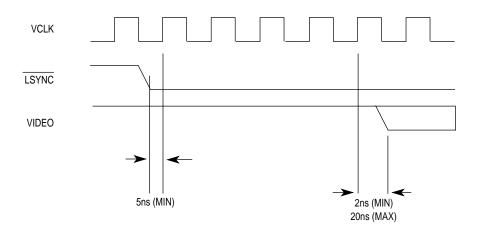

| 10.5     | PVC Video Data Timing                          | 10-16 |

| Paragraph<br>Number | Title                                  | Page<br>Number |

|---------------------|----------------------------------------|----------------|

| 10.5.1              | 1X Video Clock(PVCCR Bit 0 = 0)        | 10-17          |

| 10.5.2              | VCLK Rising Edge (PVCCR Bit 1 = 11)    | 10-17          |

| 10.5.3              | Border Polarity High (PVCCR Bit 5 = 0) | 10-17          |

### Section 11 RISC Graphics Processor

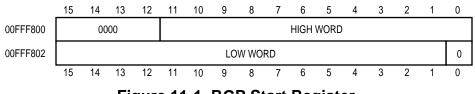

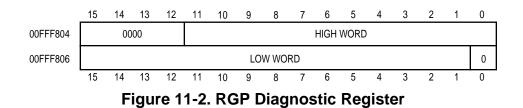

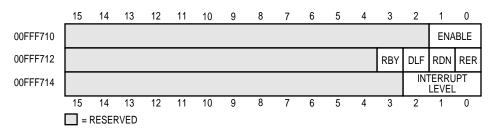

| 11.1   | RGP Registers                |      |

|--------|------------------------------|------|

| 11.1.1 | RGP Start Register           |      |

| 11.1.2 | RGP Diagnostic Register      |      |

| 11.1.3 | RGP Interrupt Event Register |      |

| 11.2   | RGP Basic Operation          | 11-3 |

### Section 12 Graphic Operations

| 12.1   | Types of Bitmaps                          |       |

|--------|-------------------------------------------|-------|

| 12.2   | Graphic Operands                          |       |

| 12.3   | Types of Graphic Operands                 |       |

| 12.4   | Boolean Codes                             |       |

| 12.5   | Bit Block Transfers                       |       |

| 12.6   | Scanline Transfers                        |       |

| 12.6.1 | Scanline Tables and Bit String Specifiers |       |

| 12.6.2 | Scanline Run Operation                    |       |

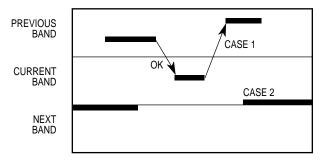

| 12.6.3 | Executing During Banded Applications      |       |

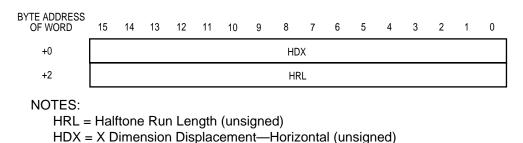

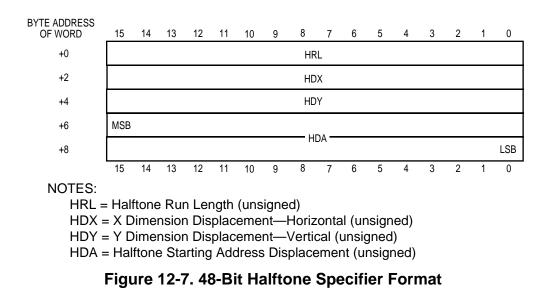

| 12.6.4 | Halftone Companion Tables                 |       |

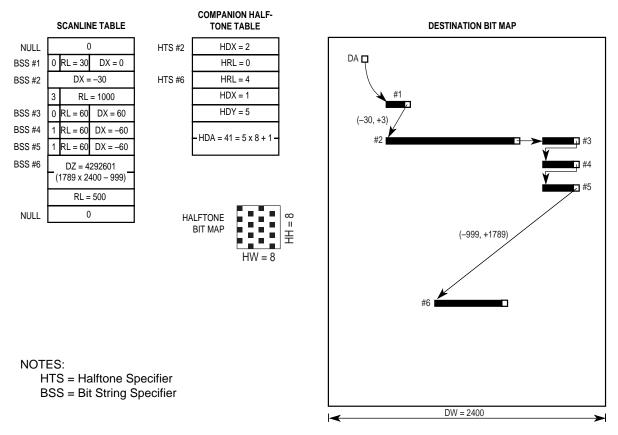

| 12.7   | Scanline and Halftone Table Example       |       |

| 12.8   | BitBLT and Scanline Order Execution       |       |

| 12.9   | Location and Address Constraints          | 12-15 |

### Section 13 Graphic Orders

| 13.1   | Types of Graphic Orders      |  |

|--------|------------------------------|--|

| 13.1.1 | Initialization               |  |

| 13.1.2 | Program Flow Control         |  |

| 13.1.3 | Bit Block Transfer           |  |

| 13.1.4 | Expanded Bit Block Transfer  |  |

| 13.1.5 | Scanline Transfer            |  |

| 13.2   | Sequence of the Display List |  |

| 13.3   | Graphic Order Addresses      |  |

| 13.3.1 | Physical vs Logical Address  |  |

| Paragraph<br>Number | Title                       | Page<br>Number |

|---------------------|-----------------------------|----------------|

| 13.3.2              | Duplex Addresses            | 13-6           |

| 13.4                | Band Number and Band Faults | 13-7           |

| 13.5                | Graphic Order Descriptions  | 13-8           |

### Section 14 Electrical and Thermal Characteristics

| 14.1   | Maximum Ratings                |  |

|--------|--------------------------------|--|

| 14.2   | Thermal Characteristics        |  |

| 14.3   | DC Electrical Specifications   |  |

| 14.4   | AC Electrical Specifications   |  |

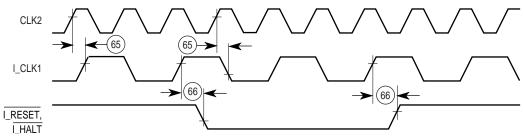

| 14.4.1 | Clock and Reset Timing         |  |

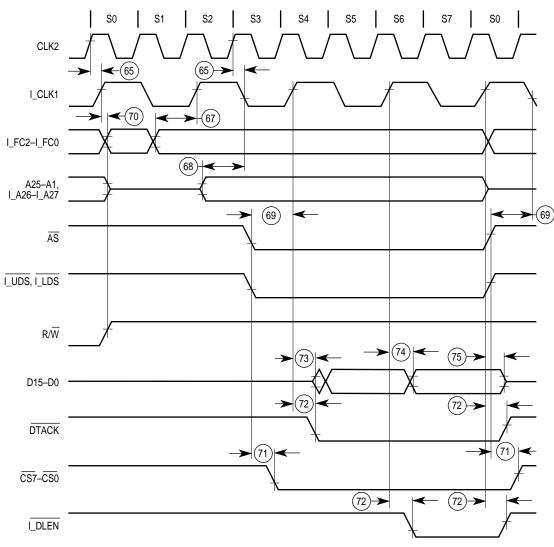

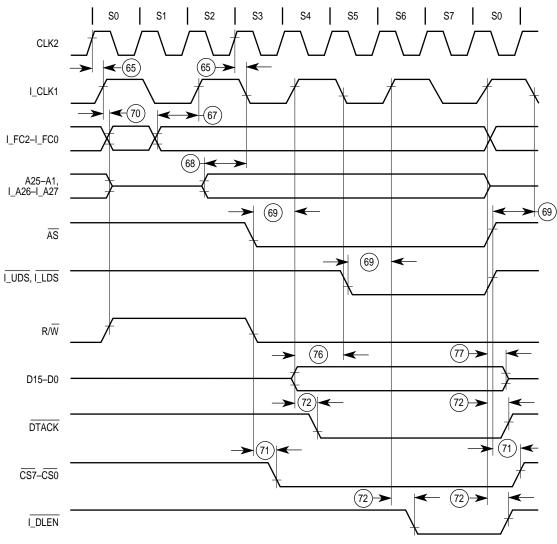

| 14.4.2 | MC68322 Bus Timing             |  |

| 14.4.3 | DRAM Timing                    |  |

| 14.4.4 | IDMA Timing                    |  |

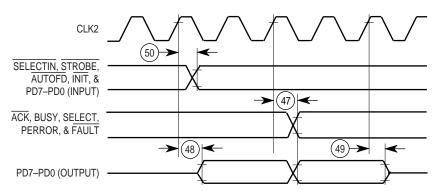

| 14.4.5 | Print Engine Interface Timing  |  |

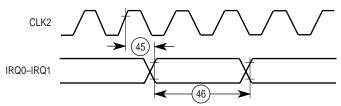

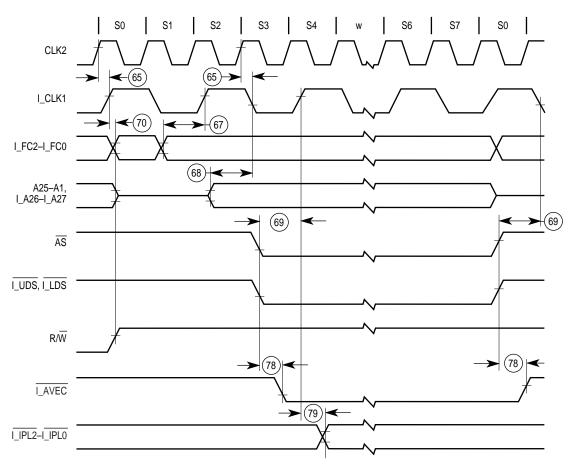

| 14.4.6 | Interrupt Timing               |  |

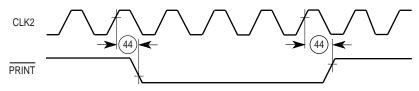

| 14.4.7 | Parallel Port Interface Timing |  |

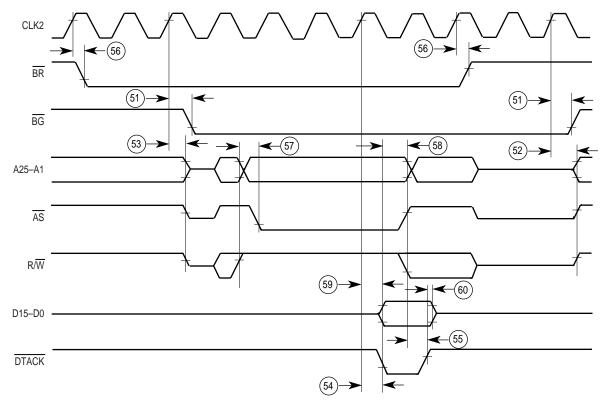

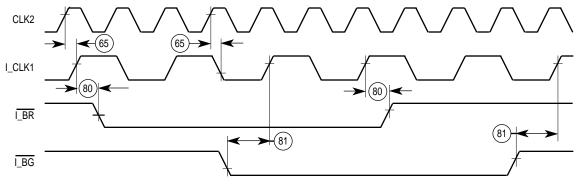

| 14.4.8 | External Bus Master Timing     |  |

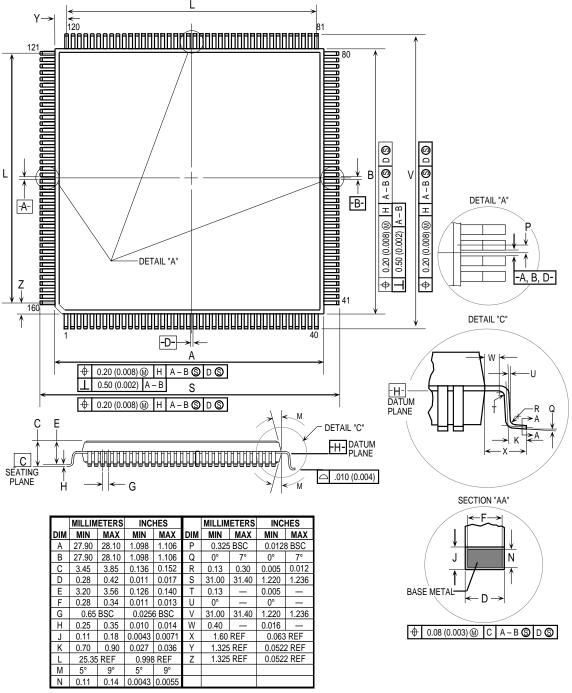

### Section 15 Ordering Information and Mechanical Data

| 15.1 | Ordering Information |  |

|------|----------------------|--|

| 15.2 | Pin Assignment       |  |

| 15.3 | Mechanical Data      |  |

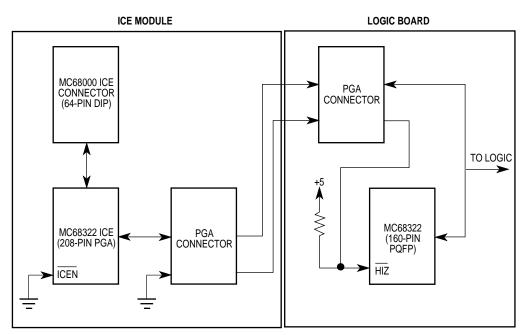

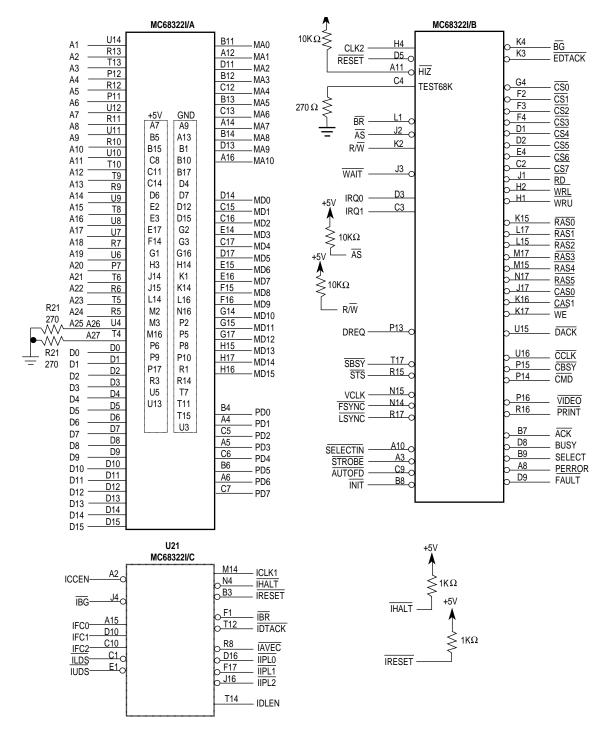

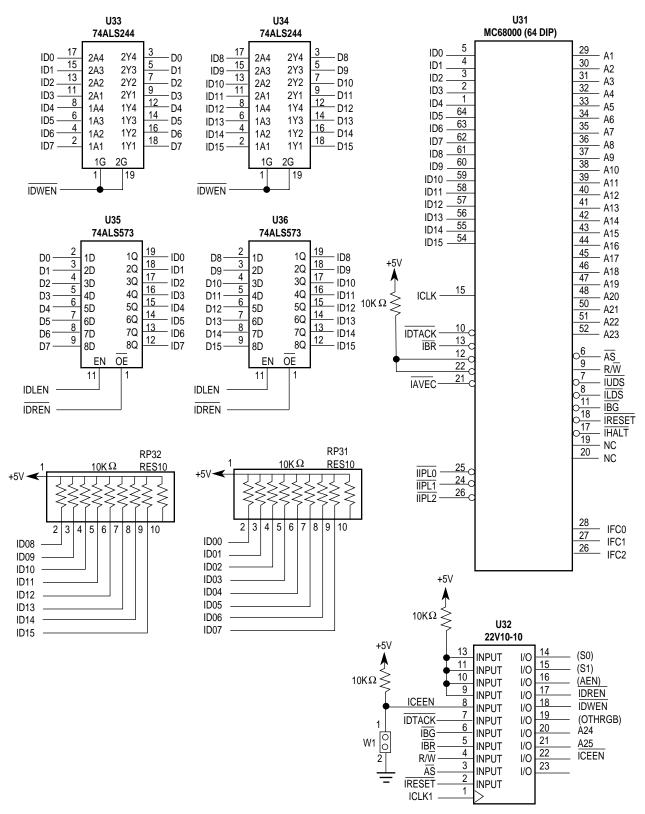

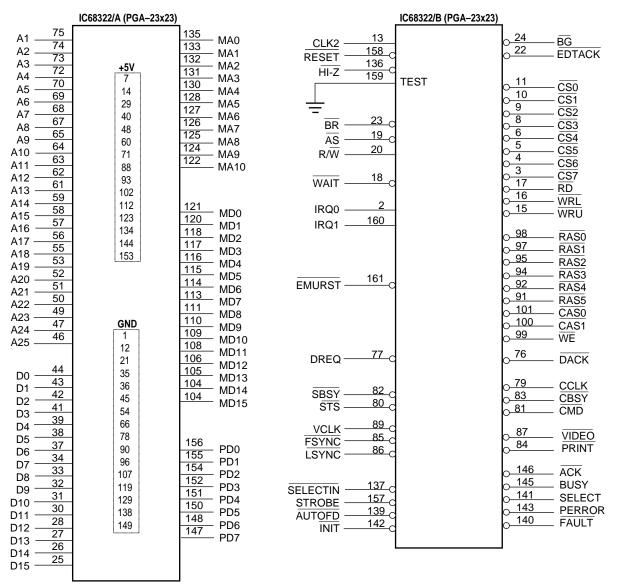

### Appendix A In-Circuit Emulation Interface

| A.1   | ICE Interface Signals          | A-1  |

|-------|--------------------------------|------|

| A.1.1 | ICE Signal Descriptions        |      |

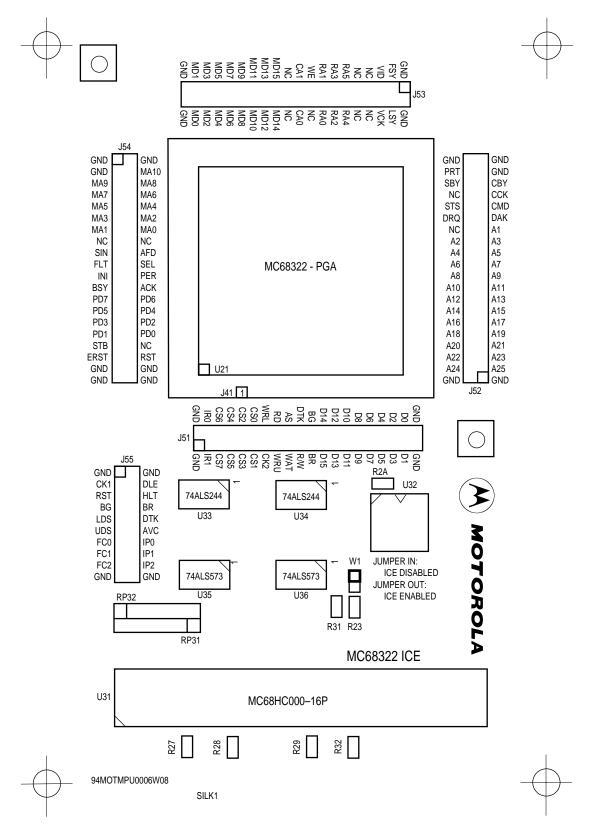

| A.2   | ICE Adaptor Board Design       |      |

| A.3   | ICE Adaptor Board Schematics   |      |

| A.3.1 | In-Circuit Emulation Interface |      |

| A.4   | ICE Pin Assignment             | A-16 |

### Paragraph Number

Title

### Page Number

### Appendix B Applications

| B.1  | Configuring The MC68322                        | B-1  |

|------|------------------------------------------------|------|

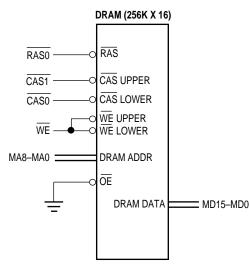

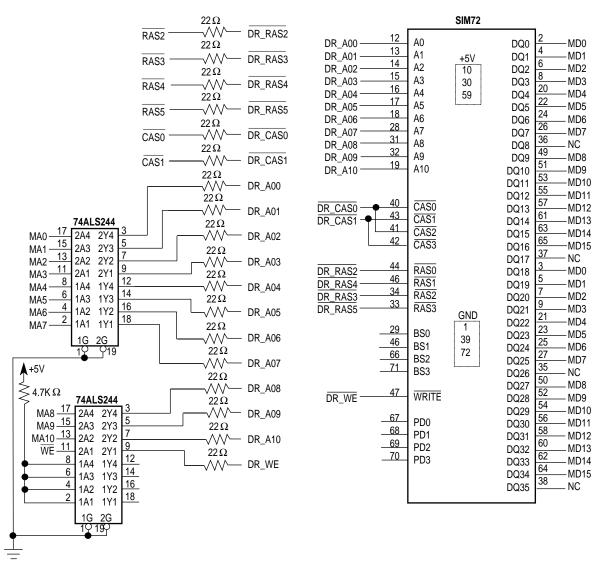

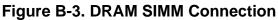

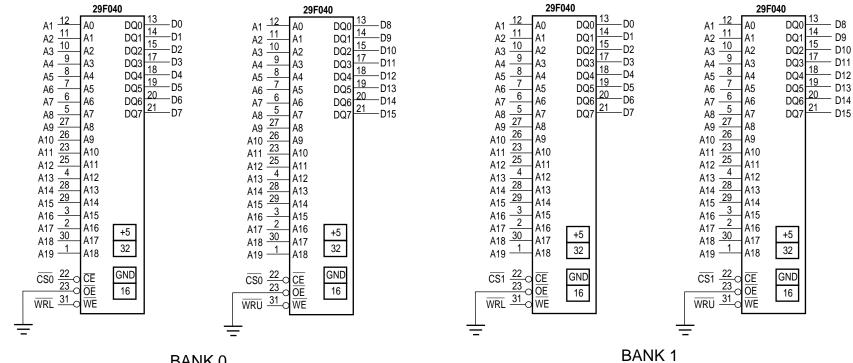

| B.2  | Configuring The DRAM and DRAM SIMM             | B-2  |

| B.3  | Configuring The Flash EPROM                    | B-4  |

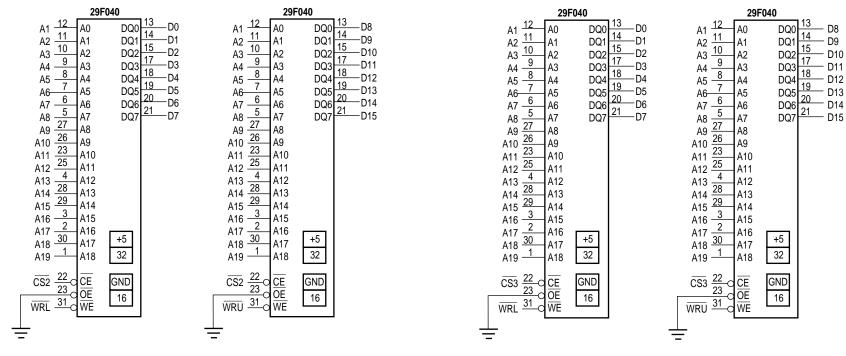

| B.4  | Configuring The Random Control Logic           | B-7  |

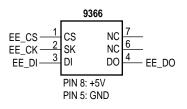

| B.5  | Configuring The Serial EEPROM                  | B-8  |

| B.6  | Configuring The In-Circuit Emulation           | B-9  |

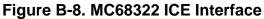

| B.7  | Configuring The Parallel Port                  | B-10 |

| B.8  | Configuring The Generic Print Engine Interface | B-11 |

| B.9  | MC68322 Memory Map Initialization Example      | B-12 |

| B.10 | MC68322 Internal Registers Sample Code         | B-13 |

### Appendix C Memory-Mapped Register Summary

| C.1 | MC68322 Mask Register | C-3 |

|-----|-----------------------|-----|

| C.2 | Test Register         | C-3 |

### Appendix D Alternate Pin Functions

| Pins                 | D-1                                                                                 |

|----------------------|-------------------------------------------------------------------------------------|

| State During Reset   | D-2                                                                                 |

| Registers            | D-2                                                                                 |

| Input Pin Mode       | D-3                                                                                 |

| Buzzer               | D-3                                                                                 |

| In-Circuit Emulation | D-3                                                                                 |

| Operation Example    | D-4                                                                                 |

|                      | State During Reset<br>Registers<br>Input Pin Mode<br>Buzzer<br>In-Circuit Emulation |

### Appendix E Glossary

### Index

## LIST OF ILLUSTRATIONS

| Figu<br>Numb |                                                          | Page<br>Number |

|--------------|----------------------------------------------------------|----------------|

| 1-1.         | MC68322 Block Diagram                                    | 1-3            |

| 1-2.         | Graphics Unit Data Flow Diagram                          |                |

| 1-3.         | 16M Memory Map                                           |                |

| 1-4.         | 256M Memory Map                                          |                |

| 1-5.         | Memory Map Address Register                              |                |

| 1-6.         | Bitmap Structure                                         |                |

| 1-7.         | Unpacked And Packed Bitmaps                              | 1-9            |

| 1-8.         | Duplex Laser Printer Paper Path                          | 1-11           |

| 1-9.         | Example of a Duplex Printing Operation                   |                |

| 2-1.         | Functional Signal Groups                                 | 2-1            |

| 2-2.         | CLK1 Phase Relationship                                  |                |

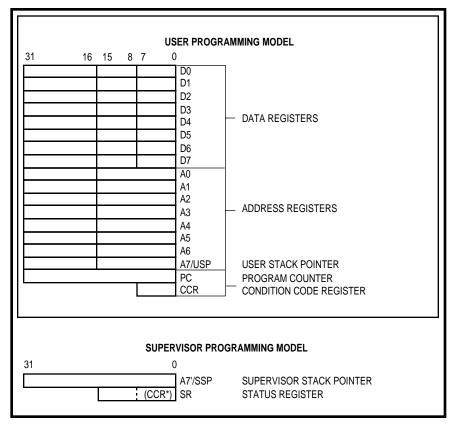

| 3-1.         | EC000 Core Programming Model                             | 3-2            |

| 4-1.         | Read Cycle Flowchart                                     | 4-2            |

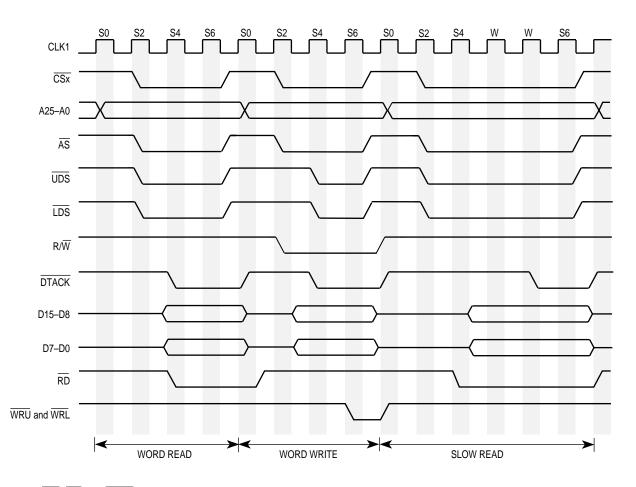

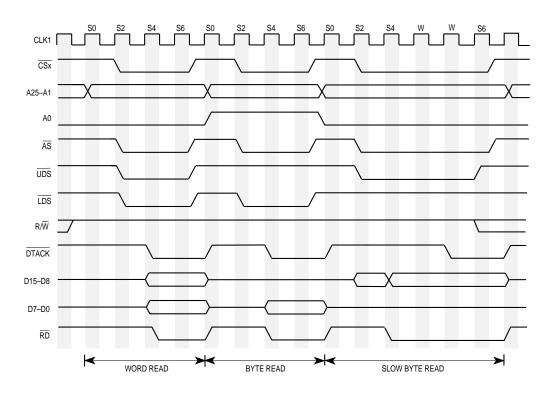

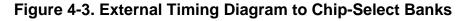

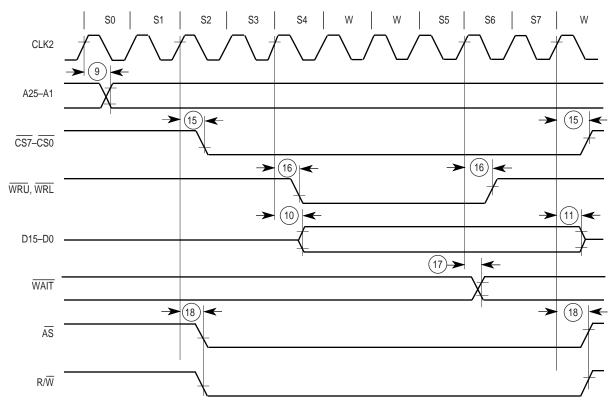

| 4-2.         | External Timing Diagram to Chip-Selects Banks            | 4-2            |

| 4-3.         | External Timing Diagram to Chip-Select Banks             | 4-3            |

| 4-4.         | Word and Byte Read Cycle Timing Diagram to DRAM          |                |

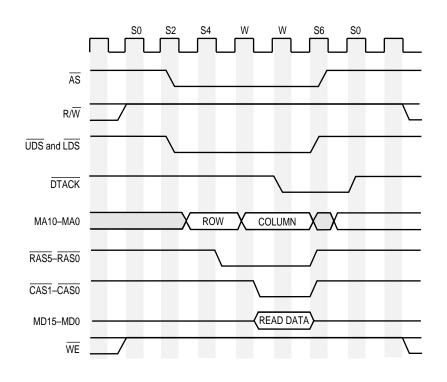

| 4-5.         | Write Cycle Flowchart                                    |                |

| 4-6.         | Word and Byte Write Cycle Timing Diagram to Chip-Selects |                |

| 4-7.         | Word Write Cycle Timing Diagram to DRAM                  |                |

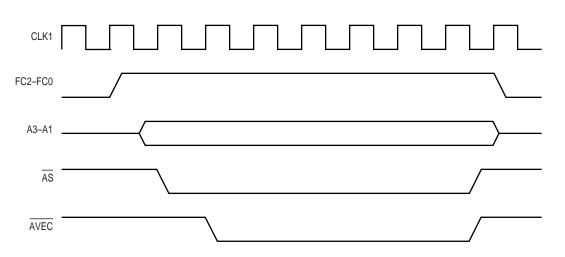

| 4-8.         | Internal Interrupt Acknowledge Cycle                     |                |

| 4-9.         | Interrupt Acknowledge Cycle Timing Diagram               |                |

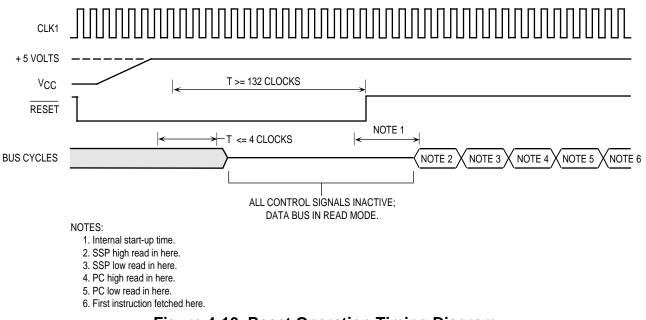

| 4-10.        | Reset Operation Timing Diagram                           |                |

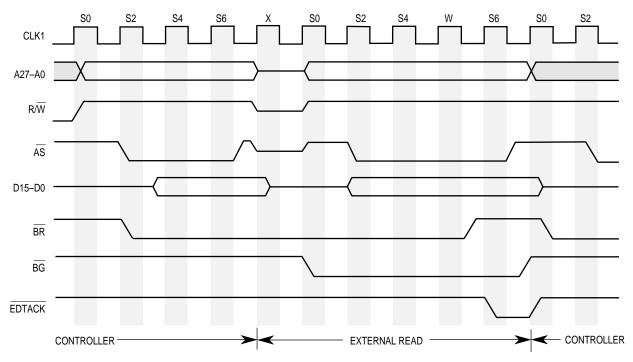

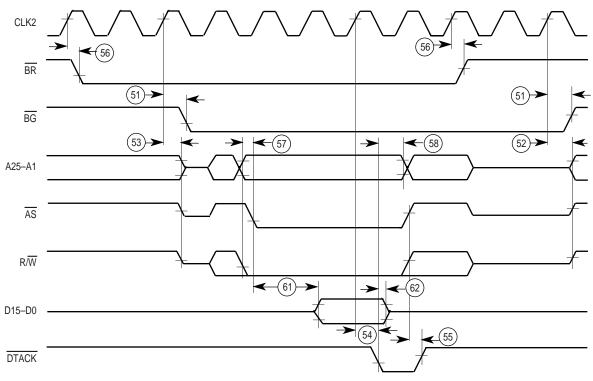

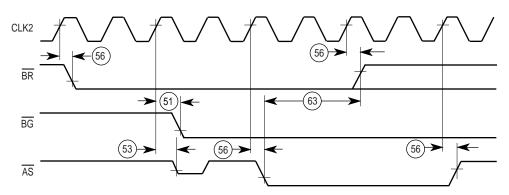

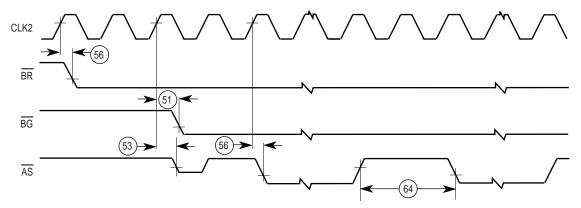

| 4-11.        | Bus Arbitration Timing Diagram                           |                |

| 4-12.        | External Bus Master Read Cycle                           |                |

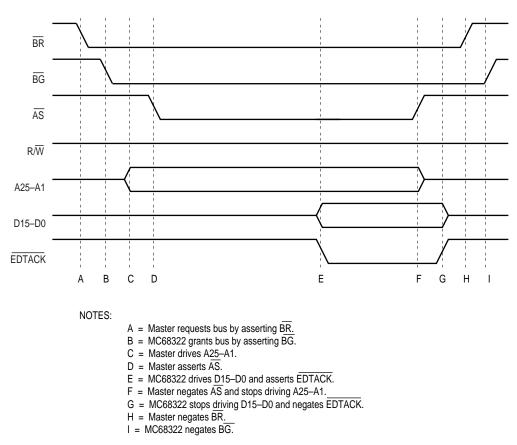

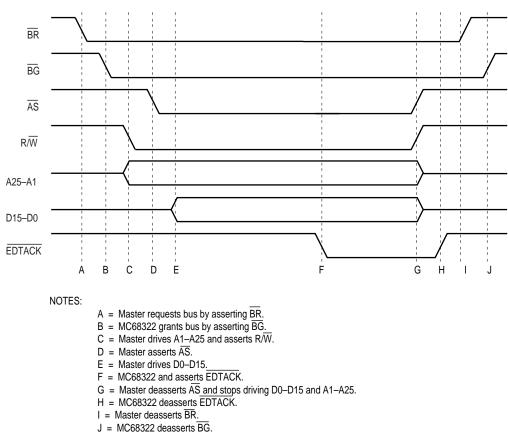

| 4-13.        | External Bus Master Write Cycle                          | 4-12           |

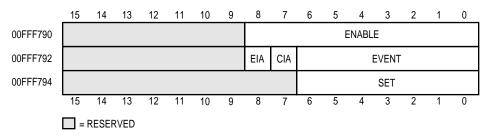

| 5-1.         | Software Interrupt Event Register                        |                |

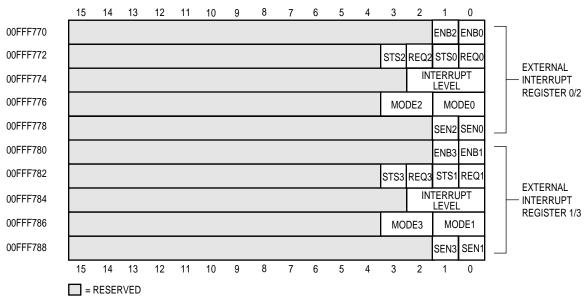

| 5-2.         | External Interrupt Registers (EXIR0/2–EXIR1/3)           |                |

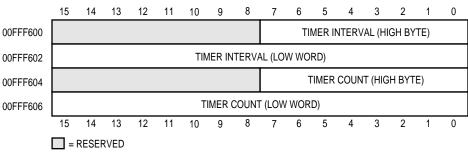

| 5-3.         | Timer Register                                           | 5-6            |

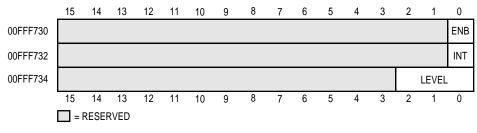

| 5-4.         | Timer Interrupt Event Register                           |                |

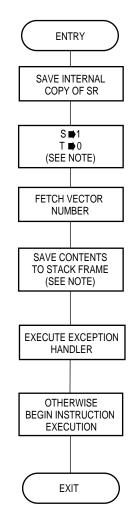

| 5-5.         | General Exception Processing Flowchart                   |                |

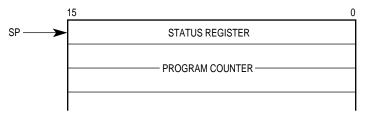

| 5-6.         | General Form of an Exception Stack Frame                 |                |

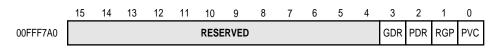

| 5-7.         | Module Soft-Reset Register                               | 5-14           |

| Figur<br>Numb             |                                                   | Page<br>Number |

|---------------------------|---------------------------------------------------|----------------|

| 6-1.                      | Chip-Select Register (CSR7–CSR0)                  | 6-1            |

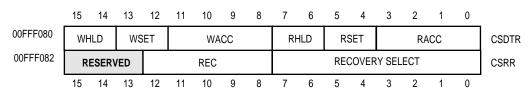

| 6-2.                      | Chip-Select DMA Timing and Recovery Registers     |                |

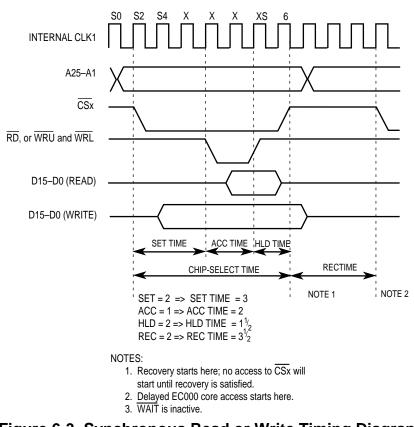

| 6-3.                      | Synchronous Read or Write Timing Diagram          |                |

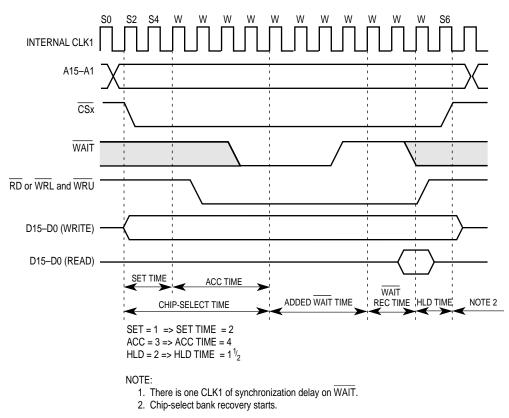

| 6-4.                      | Asynchronous Read or Write Timing Diagram         |                |

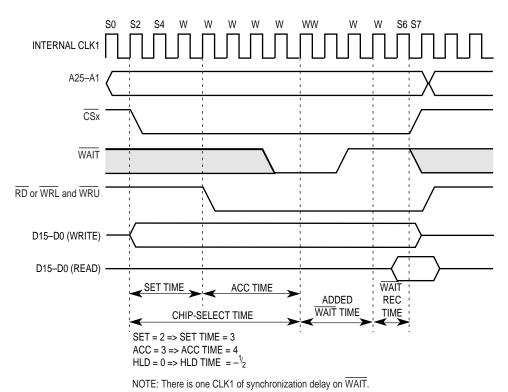

| 6-5.                      | Special Asynchronous Read or Write Timing Diagram | 6-6            |

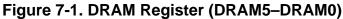

| 7-1.                      | DRAM Register (DRAM5–DRAM0)                       | 7_1            |

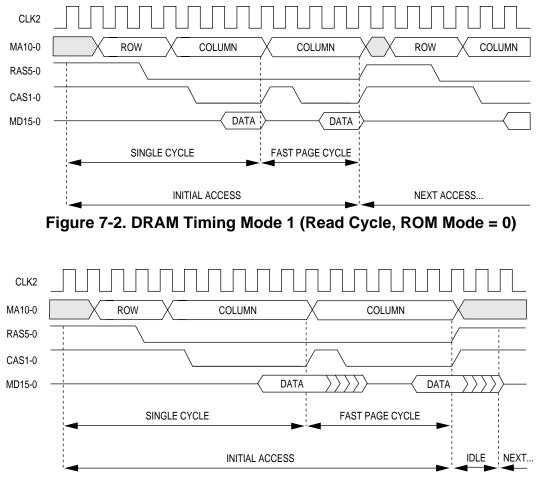

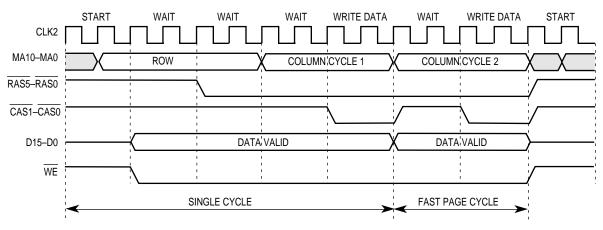

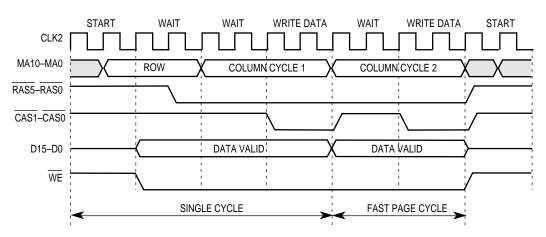

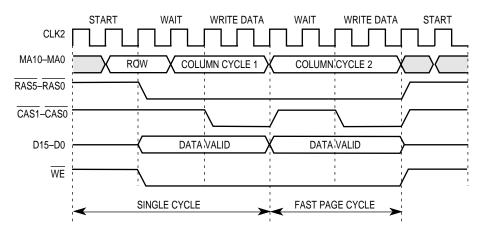

| 7-1.<br>7-2.              | DRAM Timing Mode 1 (Read Cycle, ROM Mode = 0)     | 7-1<br>7-3     |

| 7-2.<br>7-3.              | DRAM Timing Mode 1 (Read Cycle, ROM Mode = 0)     |                |

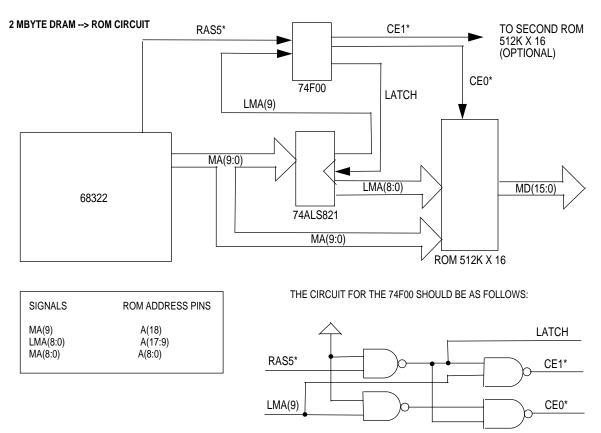

| 7-3.<br>7-4.              | Address Demultiplexing Example                    |                |

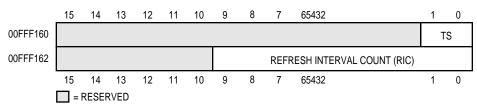

| 7- <del>4</del> .<br>7-5. | DRAM Control Register                             |                |

| 7-6.                      | DRAM Refresh Cycle                                |                |

| 7-7.                      | DRAM Timing Mode 0 (Read Cycle, ROM Mode = 0)     |                |

| 7-8.                      | DRAM Timing Mode 1 (Read Cycle, ROM Mode = 0)     | 7 7<br>7-7     |

| 7-9.                      | DRAM Timing Mode 2 (Read Cycle, ROM Mode = 0)     |                |

| 7-10.                     | DRAM Timing Mode 0 (Write Cycle)                  |                |

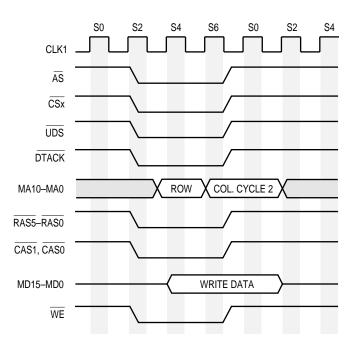

| 7-11.                     | DRAM Timing Mode 1 (Write Cycle)                  |                |

| 7-12.                     | DRAM Timing Mode 2 (Write Cycle)                  |                |

| 8-1.                      | PDMA and GDMA Configuration Registers             |                |

| 8-2.                      | GDMA Control Register                             |                |

| 8-3.                      | DMA Speed Register                                |                |

| 8-4.                      | DMA Interrupt Event Registers                     |                |

| 8-5.                      | GDMA MC68322 Bus Read Or Write Cycle              |                |

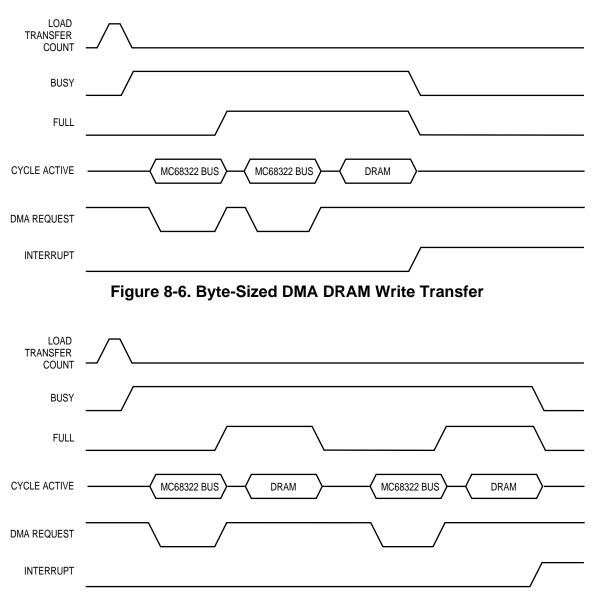

| 8-6.                      | Byte-Sized DMA DRAM Write Transfer                |                |

| 8-7.                      | Word-Sized DMA DRAM Write Transfer                | 8-9            |

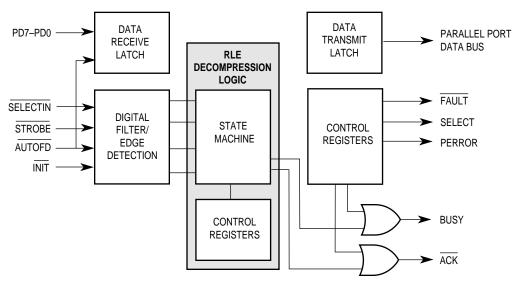

| 9-1.                      | Parallel Port Interface Controller Block Diagram  | 9-1            |

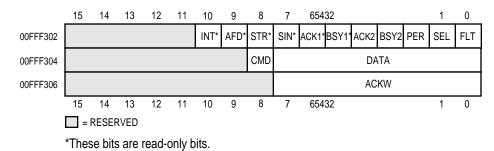

| 9-2.                      | Parallel Port Interface Register                  | 9-2            |

| 9-3.                      | Parallel Port Control Register                    | 9-4            |

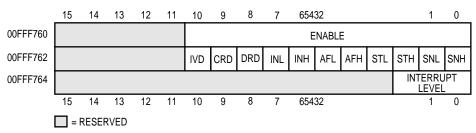

| 9-4.                      | PPI Interrupt Event Register                      | 9-6            |

| 9-5.                      | Compatibility Mode Timing Diagram                 | 9-8            |

| 9-6.                      | ECP Mode Timing Diagram                           | 9-9            |

| 9-7.                      | Error Cycle Timing Diagram                        | 9-13           |

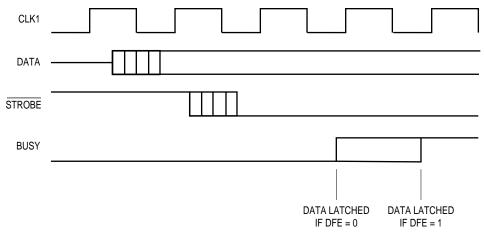

| 9-8.                      | Parallel Port Data Latch Timing Diagram           | 9-13           |

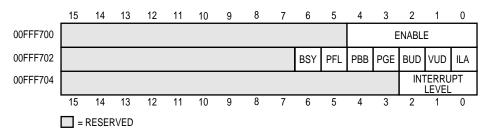

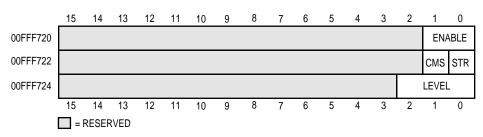

| 10-1.                     | Printer Communication Register                    | 10-2           |

| 10-2.                     | PVC Control Register                              |                |

| 10-3.                     | Printer Control Block Register Set                | 10-5           |

| 10-4.                     | PVC Interrupt Event Register                      |                |

| Figur<br>Numb                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Page<br>Number                                                                                                            |

|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

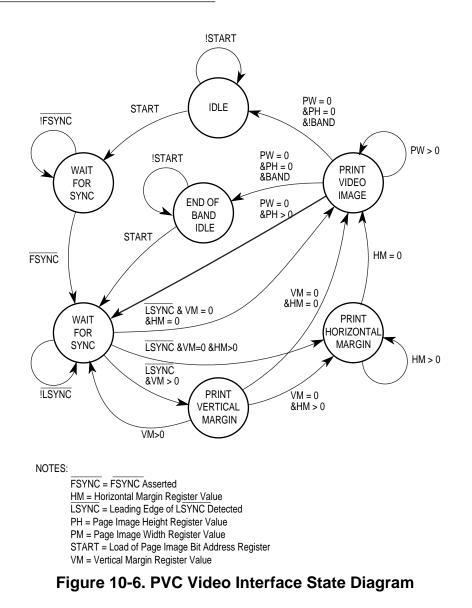

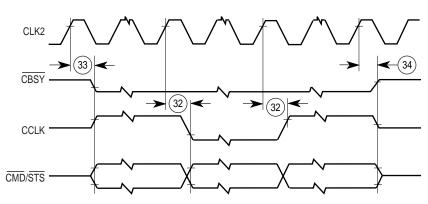

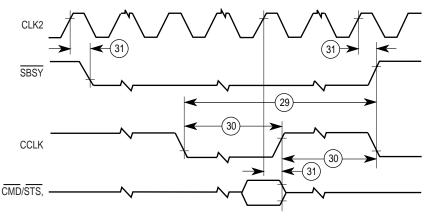

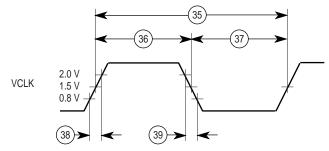

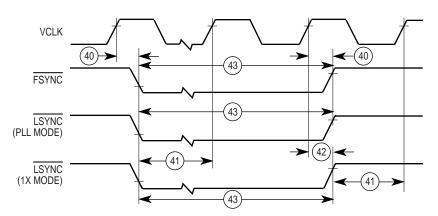

| 10-5.<br>10-6.<br>10-7.<br>10-8.<br>10-9.<br>10-10.                  | Printer Communication Interrupt Event Register<br>PVC Video Interface State Diagram<br>Command Operation—MC68322 Supplies CCLK<br>Command Operation—Print Engine Supplies CCLK<br>Status Operation—MC68322 Supplied CCLK<br>Status Operation—Print Engine Supplied CCLK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 10-10<br>10-12<br>10-13<br>10-14                                                                                          |

| 11-1.<br>11-2.<br>11-3.                                              | RGP Start Register<br>RGP Diagnostic Register<br>RGP Interrupt Event Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 11-2                                                                                                                      |

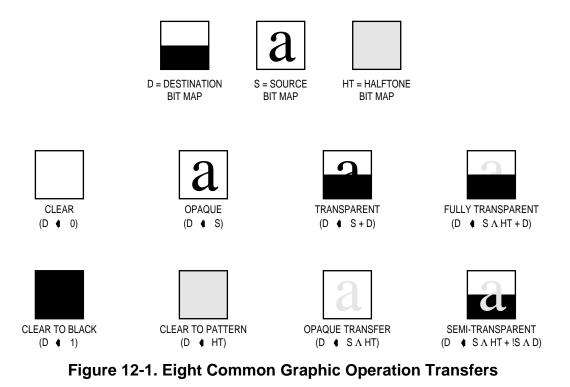

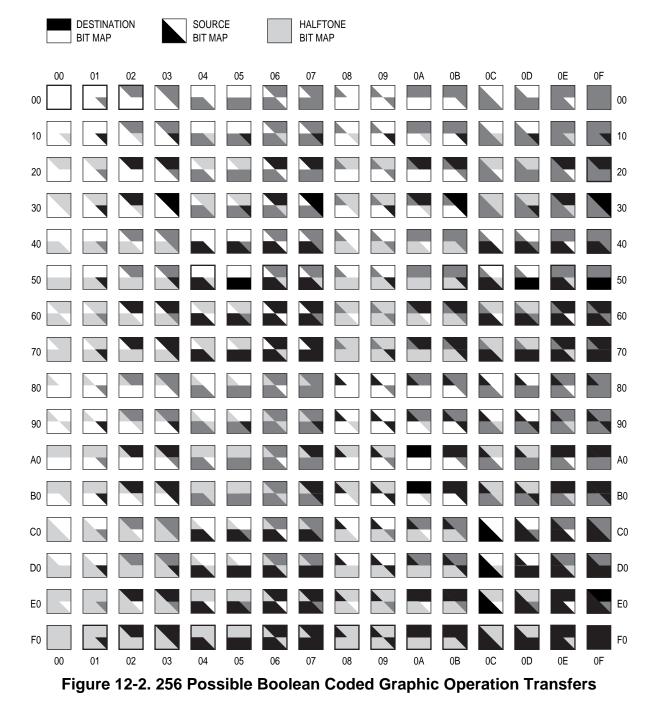

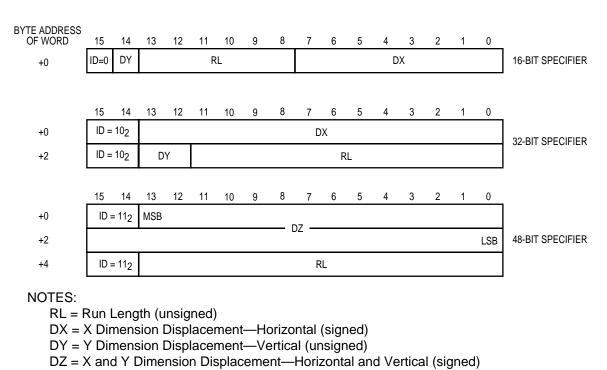

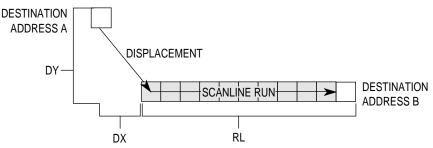

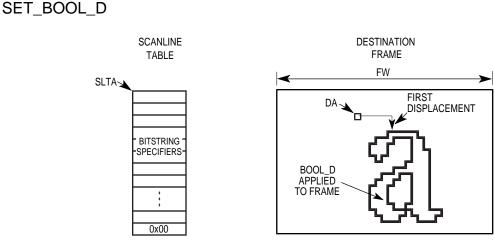

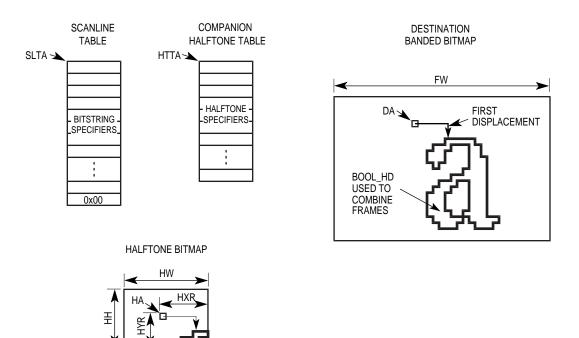

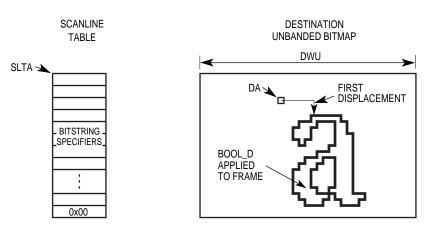

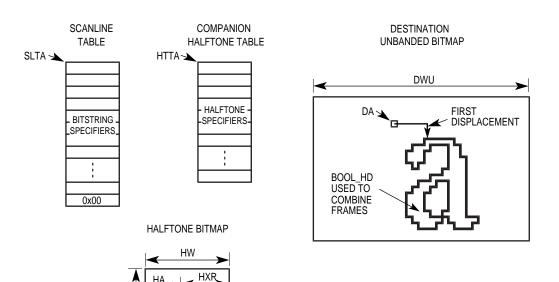

| 12-1.<br>12-2.<br>12-3.<br>12-4.<br>12-5.<br>12-6.<br>12-7.<br>12-8. | Eight Common Graphic Operation Transfers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 12-4<br>12-7<br>12-8<br>12-9<br>12-10<br>12-11                                                                            |

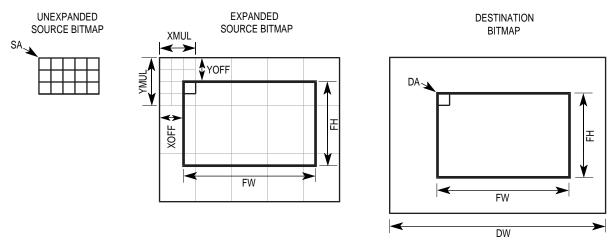

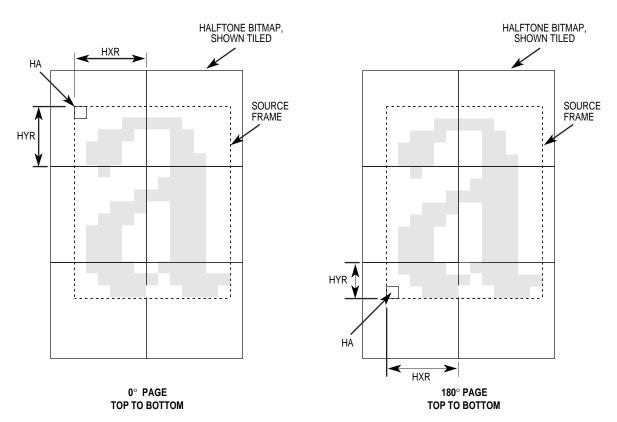

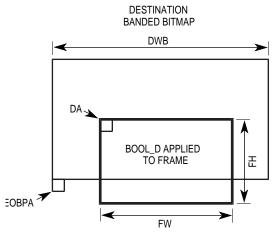

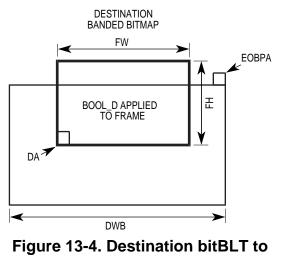

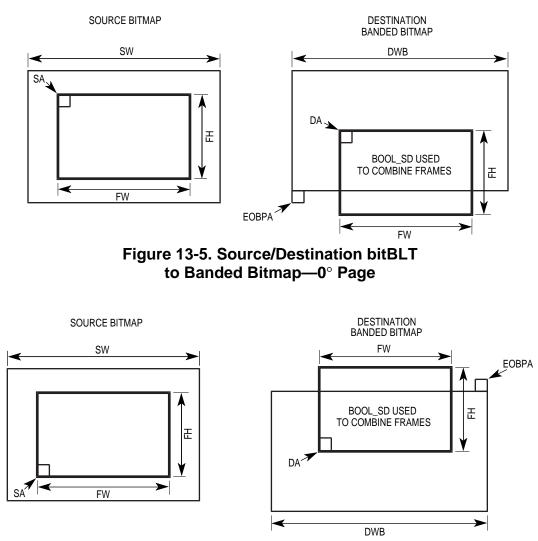

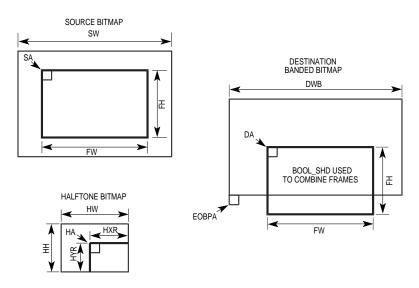

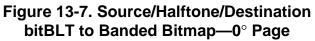

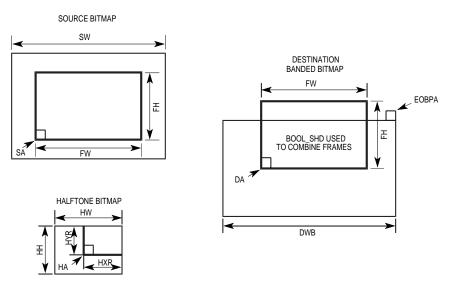

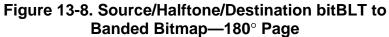

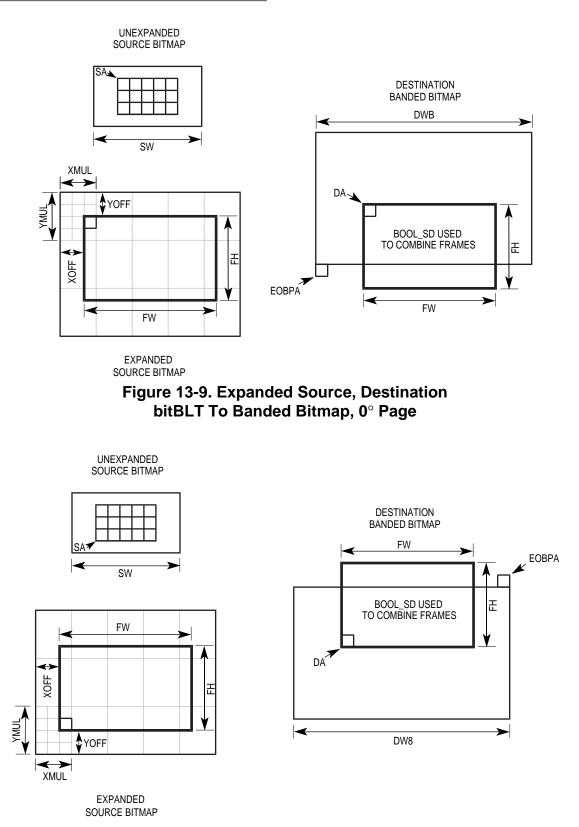

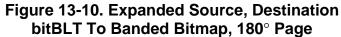

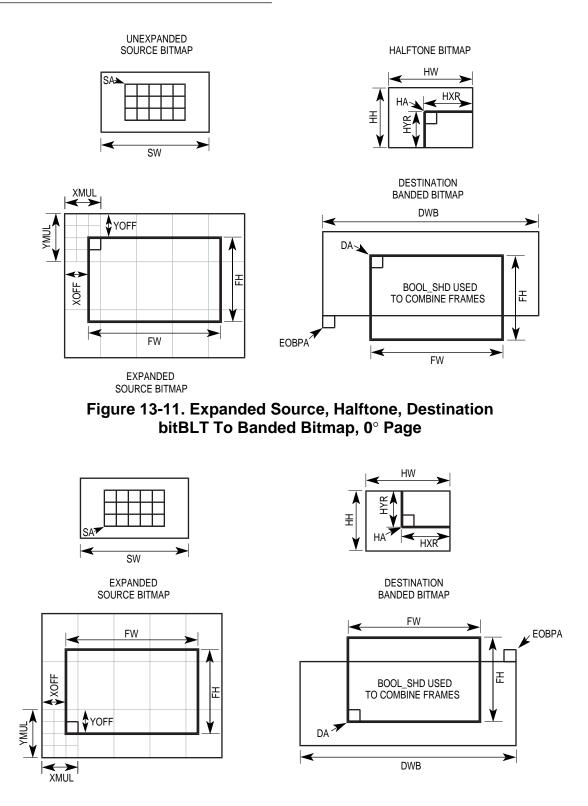

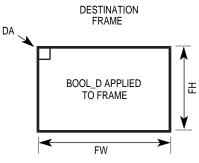

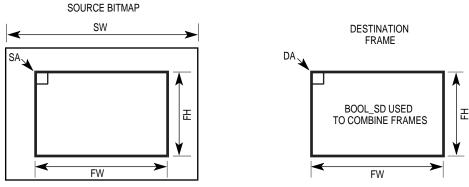

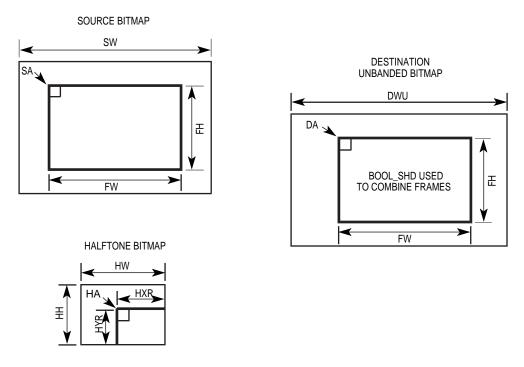

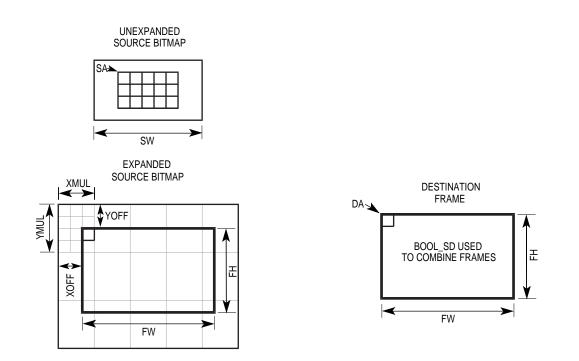

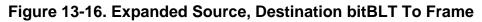

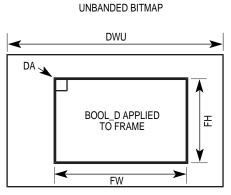

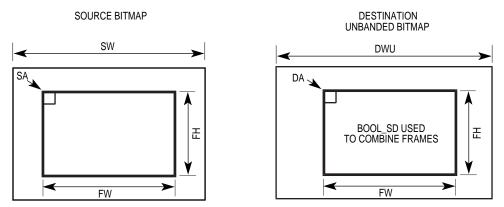

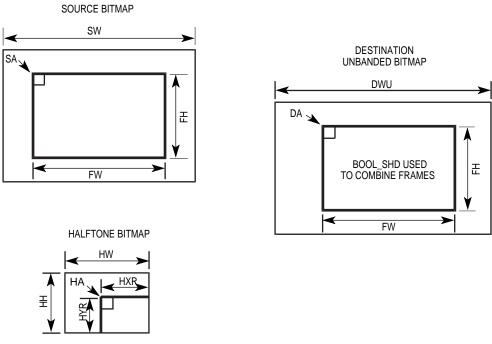

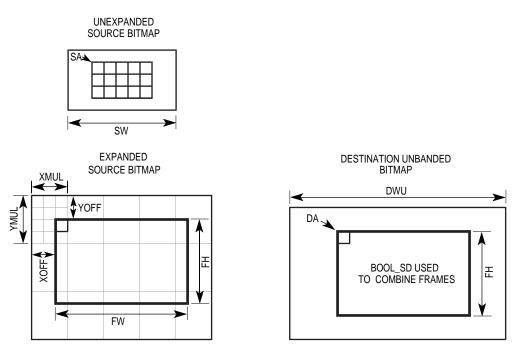

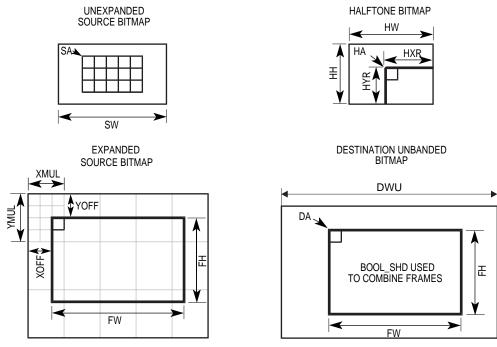

| 13-10.<br>13-11.<br>13-12.<br>13-13.<br>13-14.<br>13-15.             | Controlling Left and Right Clipping of Expanded Bit Maps<br>Halftone Specification for bitBLT Operations<br>Destination bitBLT to Banded Bitmap—0° Page<br>Destination bitBLT to Banded Bitmap—180° Page<br>Source/Destination bitBLT to Banded Bitmap—0° Page<br>Source/Halftone/Destination bitBLT to Banded Bitmap—0° Page<br>Source/Halftone/Destination bitBLT to Banded Bitmap—0° Page<br>Source/Halftone/Destination bitBLT to Banded Bitmap—0° Page<br>Expanded Source, Destination bitBLT To Banded Bitmap, 0° Page<br>Expanded Source, Destination bitBLT To Banded Bitmap, 180° Page<br>Expanded Source, Halftone, Destination bitBLT To Banded Bitmap, 180° Page<br>Expanded Source, Halftone, Destination bitBLT To Banded<br>Bitmap, 0° Page<br>Expanded Source, Halftone, Destination bitBLT To Banded<br>Bitmap, 180° Page<br>Destination bitBLT to Frame<br>Source/Destination bitBLT to Frame<br>Source/Halftone/ Destination bitBLT to Frame<br>Source/Halftone/ Destination bitBLT to Frame<br>Source/Halftone/ Destination bitBLT to Frame | 13-7<br>13-10<br>13-10<br>13-12<br>13-12<br>13-15<br>13-15<br>13-18<br>13-18<br>13-22<br>13-22<br>13-23<br>13-24<br>13-26 |

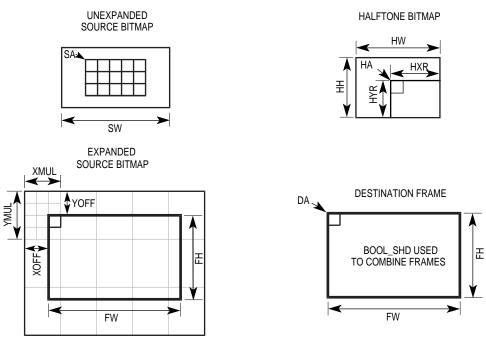

|                                                                      | Expanded Source, Halftone, Destination bitBLT To Frame<br>Destination bitBLT to Unbanded Bitmap                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                           |

| Figur<br>Numb   |                                                                                            | Page<br>Number |

|-----------------|--------------------------------------------------------------------------------------------|----------------|

| 13-19.          | Source/Destination bitBLT to Unbanded Bitmap                                               | 13-33          |

| 13-20.          | Source/Halftone/Destination bitBLT to Unbanded Bitmap                                      | 13-35          |

|                 | Expanded Source, Destination bitBLT To Unbanded Bitmap                                     |                |

|                 | Expanded Source, Halftone, Destination bitBLT to Unbanded Bitmap                           |                |

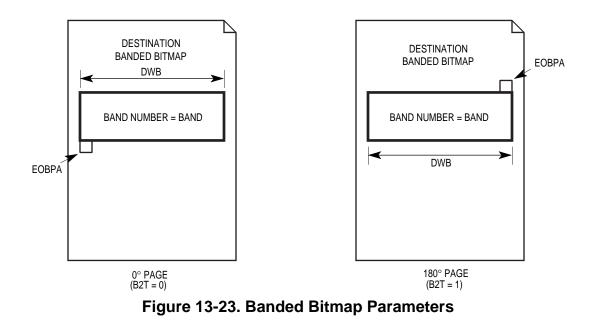

|                 | Banded Bitmap Parameters                                                                   |                |

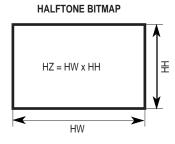

|                 | Halftone Bitmap Parameters                                                                 |                |

|                 | Unpacked Source Bitmap                                                                     |                |

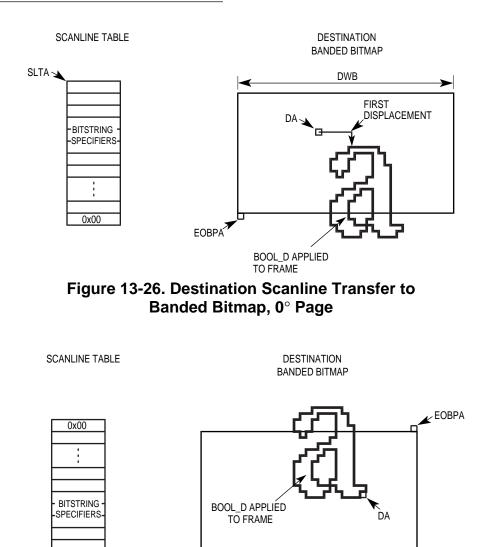

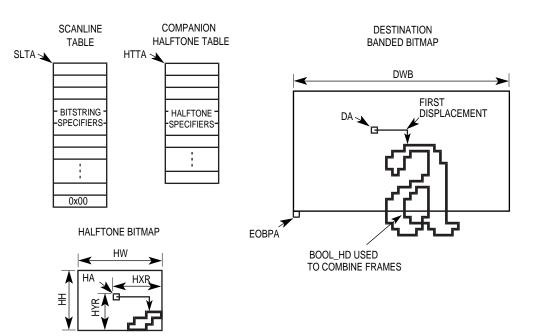

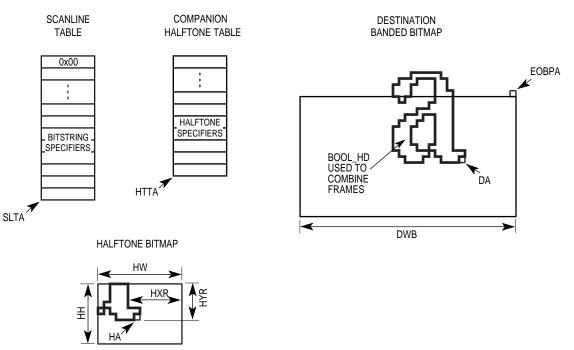

|                 | Destination Scanline Transfer to Banded Bitmap, 0° Page                                    |                |

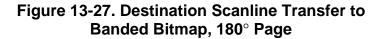

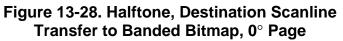

|                 | Destination Scanline Transfer to Banded Bitmap, 180° Page                                  |                |

|                 | Halftone, Destination Scanline Transfer to Banded Bitmap, 0° Page                          |                |

|                 | Halftone, Destination Scanline Transfer to Banded Bitmap, 180° Page                        |                |

|                 | Destination Scanline Transfer to Frame<br>Halftone, Destination Scanline Transfer to Frame |                |

|                 | Destination Scanline Transfer to Unbanded Bitmap                                           |                |

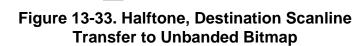

|                 | Halftone, Destination Scanline Transfer to Unbanded Bitmap                                 |                |

| 15-55.          |                                                                                            | 13-39          |

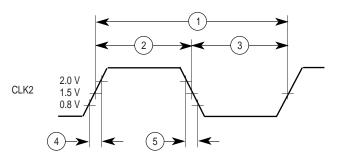

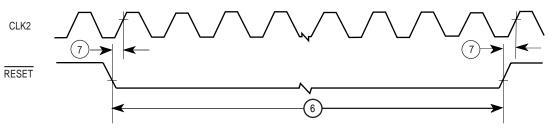

| 14-1.           | Clock AC Timing                                                                            | 14-3           |

| 14-2.           | Reset AC Timing                                                                            |                |

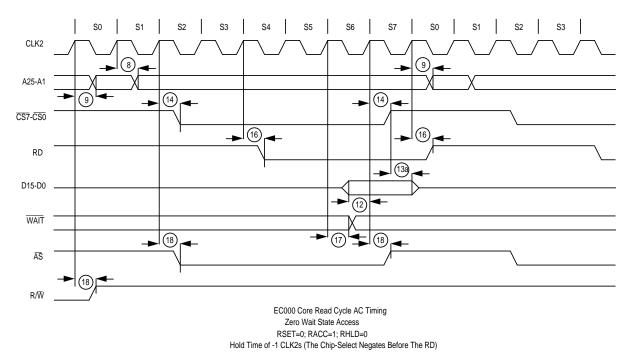

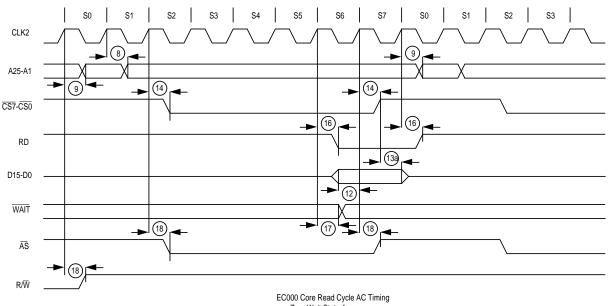

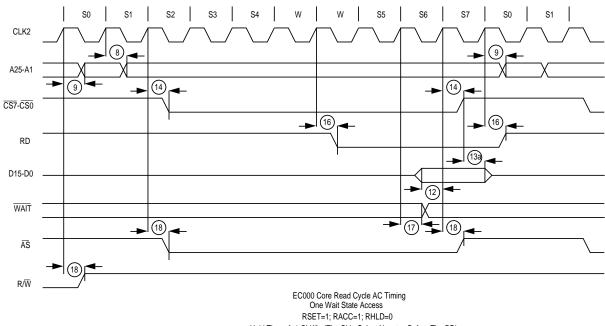

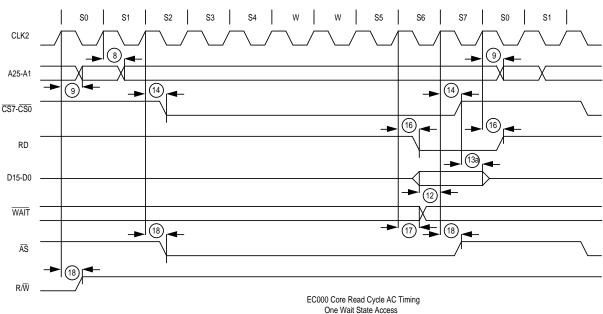

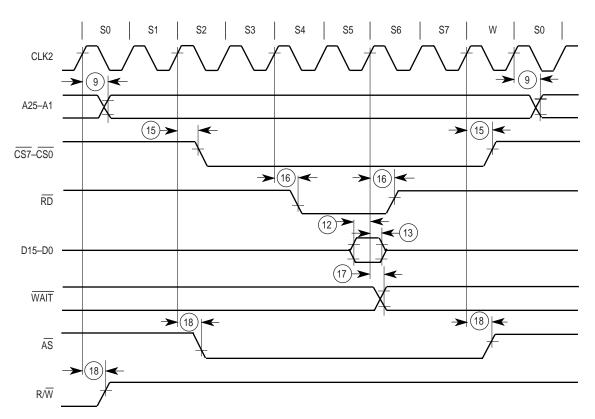

| 14-3.           | Read Access (2:2:1:3)                                                                      |                |

| 14-4.           | Read Access (2:4:-1:3)                                                                     |                |

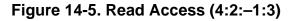

| 14-5.           | Read Access (4:2:-1:3)                                                                     |                |

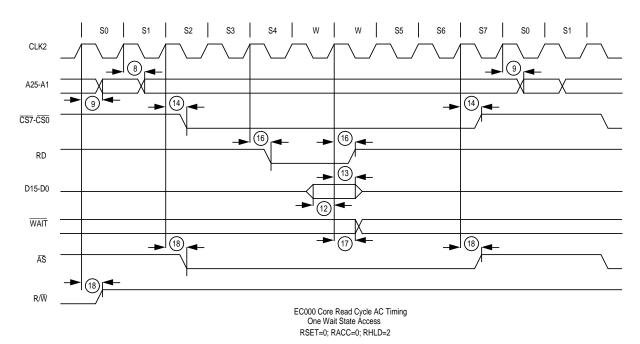

| 14-6.           | Read Access (2:2:3:3)                                                                      |                |

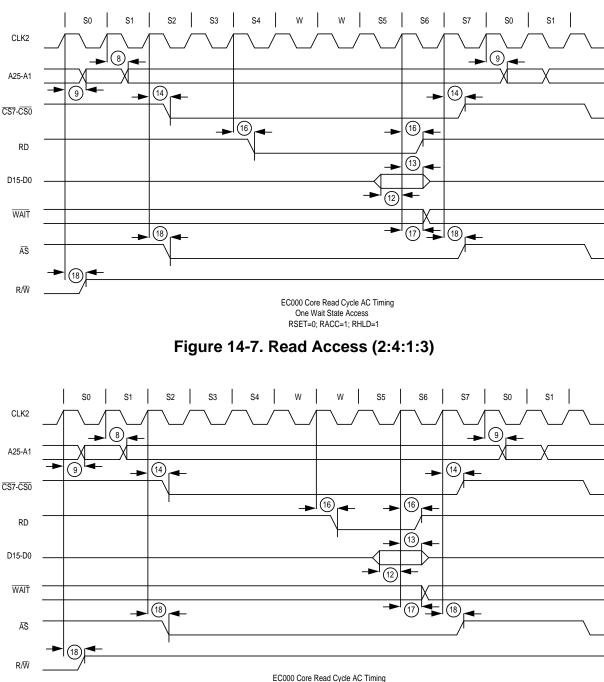

| 14-7.           | Read Access (2:4:1:3)                                                                      |                |

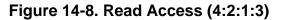

| 14-8.           | Read Access (4:2:1:3)                                                                      | 14-7           |

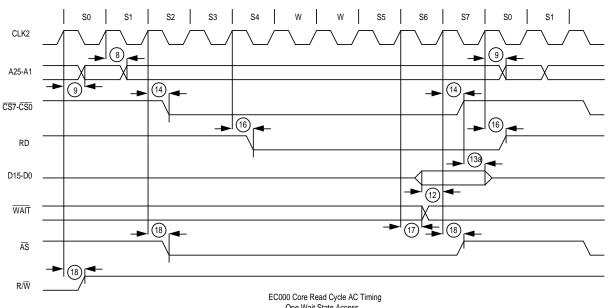

| 14-9.           | Read Access (2:6:-1:3)                                                                     | 14-8           |

|                 | Read Access (4:4:-1:3)                                                                     |                |

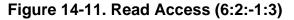

|                 | Read Access (6:2:-1:3)                                                                     |                |

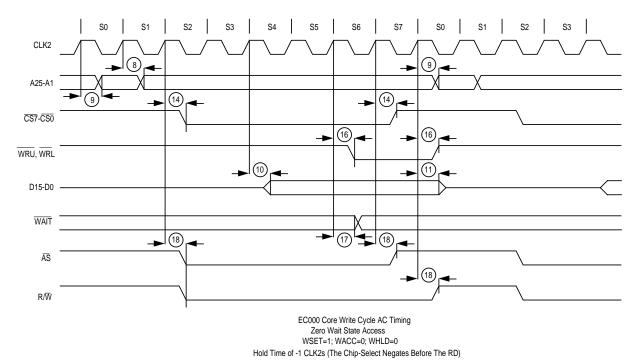

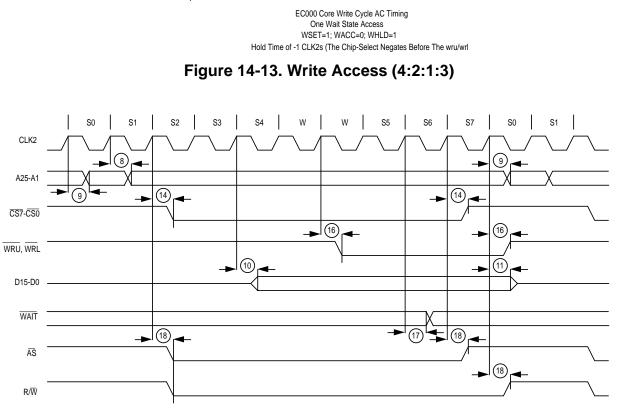

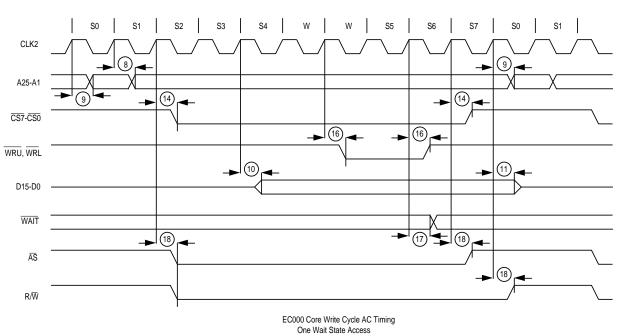

|                 | Write Access (4:2:-1:3)                                                                    |                |

|                 | Write Access (4:2:1:3)                                                                     |                |

|                 | Write Access (4:4:-1:3)                                                                    |                |

|                 | DMA Read Cycle AC Timing                                                                   |                |

|                 | DMA Write Cycle AC Timing                                                                  |                |

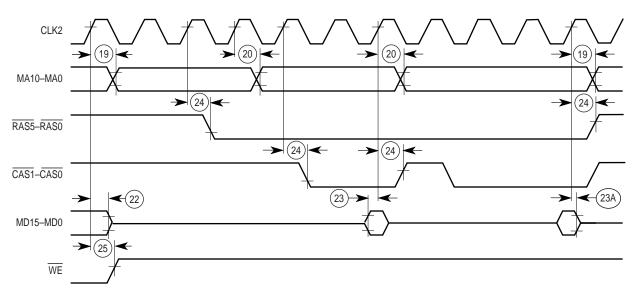

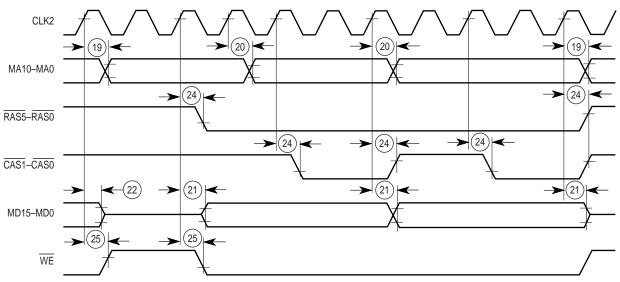

|                 | DRAM Read Cycle AC Timing                                                                  |                |

| 14-18.          | DRAM Write Cycle AC Timing                                                                 | 14-12          |

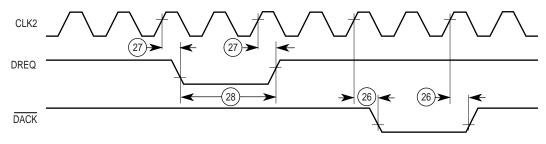

| 14-19.          | DMA Request/Acknowledge AC Timing                                                          | 14-13          |

|                 | Print Engine Interface Input AC Timing                                                     |                |

|                 | Print Engine Interface Output AC Timing<br>Video Clock AC Timing                           |                |

|                 | -                                                                                          |                |

| 14-23.          | PVC AC Timing<br>Print Engine Interface AC Timing                                          | 1/ 16          |

| 14-24.<br>17-25 | Interrupt Interface AC Timing                                                              | 1/1-16         |

|                 | Parallel Port Interface AC Timing                                                          |                |

| 14-20.          |                                                                                            |                |

| Figur<br>Numb                                                                                   |                                                                                                                                                                                                                                                                                                                                                                      | Page<br>Number                                                           |

|-------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

| 14-28.<br>14-29.                                                                                | External Bus Master Read Cycle AC Timing<br>External Bus Master Write Cycle AC Timing<br>External Bus Master Bus Arbitration AC Timing<br>External Bus Master Multiple Cycle AC Timing                                                                                                                                                                               | 14-19<br>14-19                                                           |

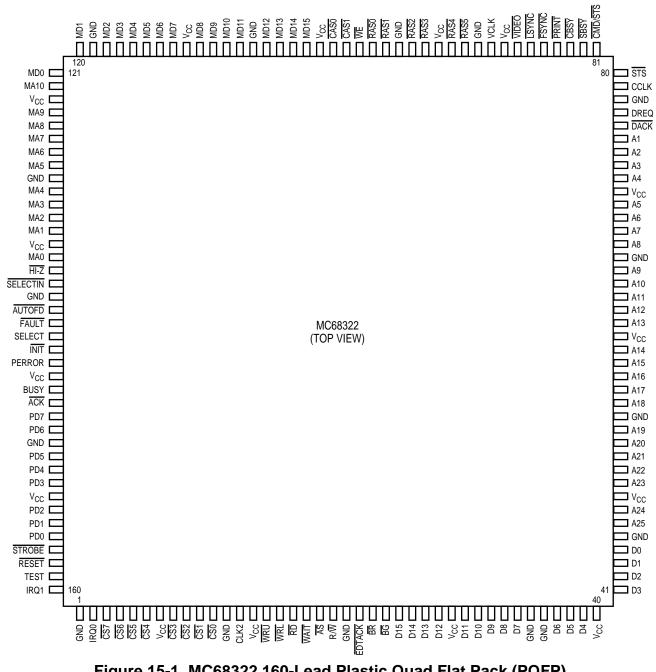

| 15-1.<br>15-2.                                                                                  | MC68322 160-Lead Plastic Quad Flat Pack (PQFP)<br>160 Pin QFP Package Dimensions                                                                                                                                                                                                                                                                                     |                                                                          |

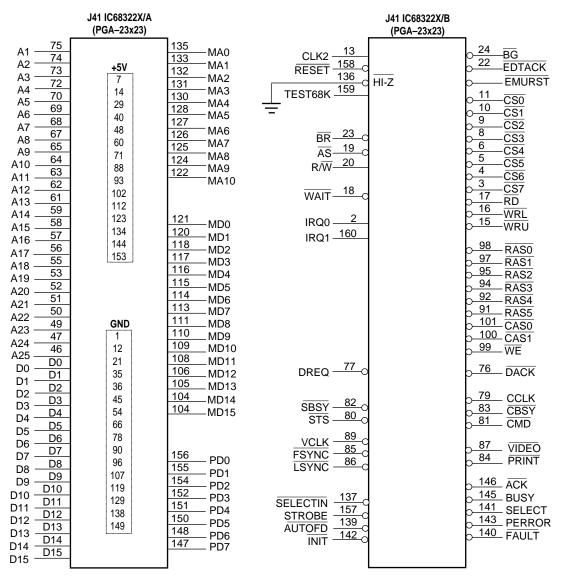

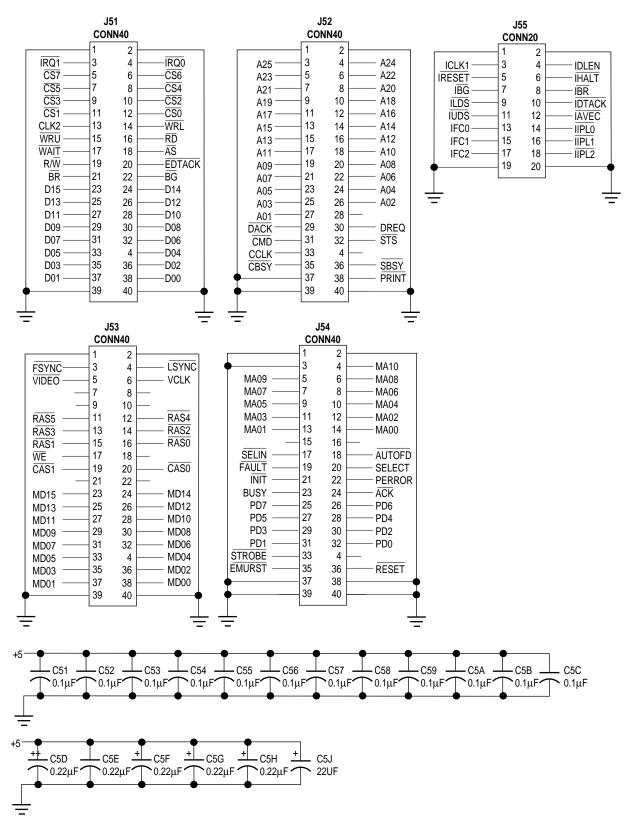

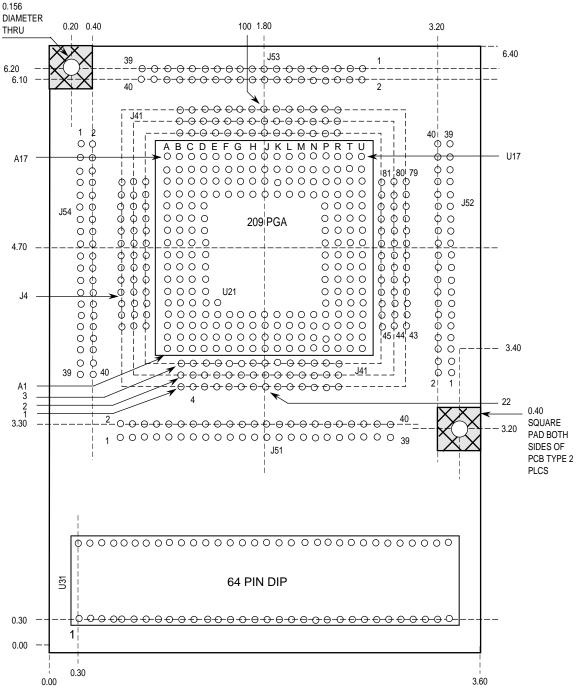

| A-1.<br>A-2.<br>A-3.<br>A-4.<br>A-5.<br>A-6.<br>A-7.<br>A-8.<br>A-9.<br>A-10.<br>A-11.<br>A-12. | ICE Interface Block Diagram<br>MC68322 PGA Pinout<br>MC68000 Emulator Connection<br>PGA Connector<br>Test Points<br>ICE Adaptor Board<br>ICE Adaptor Board<br>ICE Adaptor Board<br>ICE Reset AC Timing<br>ICE Reset AC Timing<br>ICE Read Cycle AC Timing<br>ICE Write Cycle AC Timing<br>ICE Interrupt Acknowledge Cycle AC Timing<br>ICE Bus Arbitration AC Timing | A-6<br>A-7<br>A-8<br>A-9<br>A-10<br>A-11<br>A-12<br>A-13<br>A-14<br>A-15 |

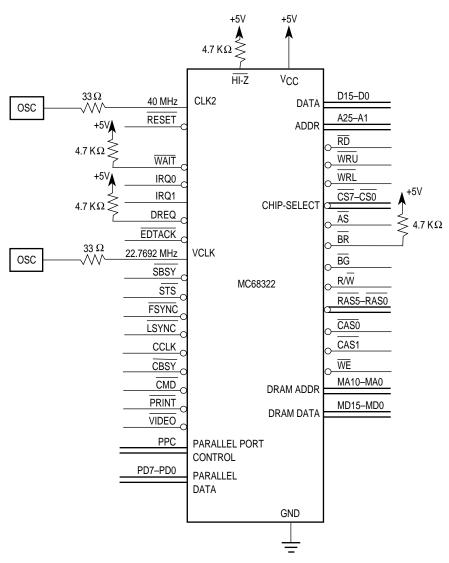

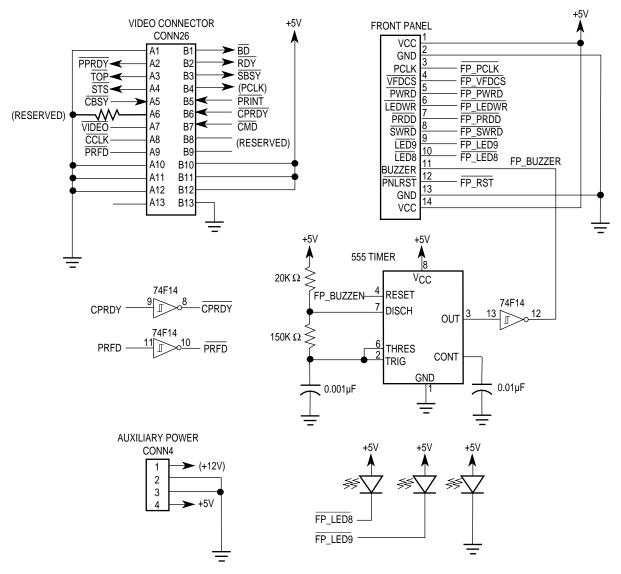

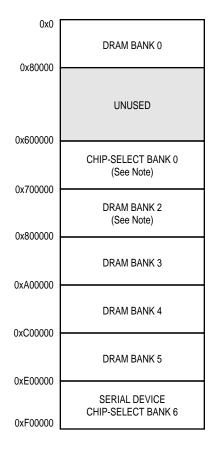

| B-1.<br>B-2.<br>B-3.<br>B-4.<br>B-5.<br>B-6.<br>B-7.<br>B-8.<br>B-9.<br>B-10.<br>B-11.          | MC68322 Connection<br>DRAM Connection<br>DRAM SIMM Connection<br>Flash EEPROM Connection (1 of 2)<br>Reset Circuit<br>Front Panel Buffers and Latches<br>4-Kbit Serial EEPROM Connection<br>MC68322 ICE Interface<br>Parallel Port Connector Interface<br>Print Engine Interface<br>Initialized Memory Map From Code Example                                         | B-3<br>B-4<br>B-5<br>B-7<br>B-7<br>B-8<br>B-8<br>B-9<br>B-10<br>B-11     |

# LIST OF TABLES

| Tabl<br>Numb                 | -                                                                                                                               | Page<br>Number |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------------|----------------|

| 2-1.<br>2-2.<br>2-3.         | Signal Summary<br>HI-Z and TEST Combinations<br>DRAM Address Multiplexer                                                        | 2-5            |

| 3-1.<br>3-2.<br>3-3.<br>3-4. | Processor Data Formats<br>Effective Addressing Modes<br>Notational Conventions<br>Instruction Set Summary                       | 3-3<br>3-4     |

| 5-1.<br>5-2.<br>5-3.<br>5-4. | Hardware Interrupt Events<br>External Interrupt Polarity<br>Exception Vector Assignments<br>Exception Grouping and Priority     | 5-5<br>5-9     |

| 6-1.<br>6-2.                 | Size Field Encoding<br>Synchronous Timing Values                                                                                |                |

| 7-1.<br>7-2.                 | DRAM Size Options<br>DRAM Timing Modes                                                                                          |                |

| 8-1.                         | DM Field Encoding                                                                                                               | 8-4            |

|                              | SLC and SRC Encodings<br>PLL Video Clock Divisor                                                                                |                |

| 12-1.<br>12-2.<br>12-3.      | Graphic Operation Data Operand Constant Values<br>Bit String Specifier Field Definitions<br>bitBLT and Scanline Execution Times | 12-8           |

| 13-1.<br>13-2.<br>13-3.      | Graphic Order Organization<br>Graphic Orders Sorted by Opcode<br>Supported Scaling Factors                                      | 13-8           |

# LIST OF TABLES (Continued)

| Tabl<br>Numb | -                                                                                        | Page<br>umber |

|--------------|------------------------------------------------------------------------------------------|---------------|

| A-2.         | ICE Interface Signal Summary<br>Data Strobe Control of Data Bus<br>Function Code Outputs | <br>.A-2      |

| C-1.         | Memory-Mapped Register Set                                                               | <br>C-1       |

| D-1.         | ALTPIN SEL Bit Descriptions                                                              | <br>D-1       |

### SECTION 1 INTRODUCTION

The MC68322 is a high-performance integrated printer processor that combines an MC68000 compatible EC000 core processor, a RISC graphics processor (RGP), a print engine video controller (PVC), and numerous system integration features on a single integrated circuit. It is the first of Motorola's M68000 Family designed specifically for nonimpact printers. The MC68322 provides a unique solution for new designs as well as an excellent migration path for existing M68000-powered printers. Additionally, the new chip finds ready application to the inkjet printer and multifunction-peripheral (fax/modem/printer) markets and other embedded control applications, which require very fast bit manipulations. The dual processor and dual bus architecture gives the MC68322 the ability to deliver excellent performance. Historically, printer applications have been solved using a single general-purpose processor with external application specific circuitry. The MC68322 employs a highly specialized, multiprocessor architecture that enables the user to take advantage of memory reduction techniques. This design implementation provides a technically superior and more cost effective system solution.

The specialized display list banding techniques (executed by the RGP) enable system memory requirements to be significantly reduced. The use of software memory reduction techniques alone (an approach taken by conventional controllers) lack the power needed to handle complex pages, causing the controller to fall back to lower resolution or reduced page throughput. The MC68322 optimizes overall system performance by integrating an EC000 core, RGP, and PVC using a unique dual bus architecture. This architecture eliminates bus contention between processing units and modules creating a true parallel processing environment. The additional bandwidth allows each processing unit to operate at peak performance. Working in conjunction with an on-chip, programmable, bursting DRAM controller, the processing units enable the MC68322 to produce 600 dpi images using substantially less memory than conventional controllers. The MC68322 extends these benefits to low-cost 4-8 ppm printers.

The MC68322 significantly reduces component count, board space, power consumption and their inherent costs while yielding higher reliability and shorter design time. It also provides support for toner conservation, thus enabling the print controller to conserve toner when printing in draft mode. The MC68322 also provides the perfect printing environment for users of complex page description languages (such as PCL and PostScript<sup>®</sup>) and less scaleable graphics imaging models such as Windows Printing System<sup>™</sup> and QuickDraw<sup>®</sup>). Complete code compatibility with the M68000 Family gives the designer access to a broad base of established real-time kernels, operating systems, languages, applications, and development tools, many of which are optimized for embedded processing and printing applications.

MOTOROLA

### **1.1 FEATURES**

The following list summarizes the main features of the MC68322:

- Static EC000 Core Processor

- □ Complete code compatibility with M68000 Family

- Glueless interface to peripherals

- 256M address range

- Graphics Unit

- Memory reduction techniques

- Run length encoded scan line tables

- □ RISC graphics processor

- Processes multi-operation graphics orders from display list

- Requires significantly less bitmap image memory due to hardware banding capability

- Dedicated graphics bus allows up to 8 ppm performance at 600 dpi resolution

- Print engine video controller

- Converts bitmap image to serial datastream and feeds print engine

- Generic, programmable, nonimpact printer communications interface

Toner conservation technique

- Dedicated high-performance DMA controller for graphics unit operations

- Bus Interface Unit

- Dual bus architecture allows separate buses to function independently

- Distributed processing optimizes system performance

- □ Write buffer for EC000 core enhances performance

- System Integration Module

- Eight Programmable Chip Selects

- □ 256K to 256M of address space

- □ Independently programmable timing parameters for each bank

- □ Integrated system timer

- DRAM System Integration Module

- □ Supports 512K, 2M, and 8M DRAM bank sizes

- Directly controls up to 6 banks of DRAM; supports up to 48M of DRAM

- Dependence of DRAM banks

- Bursting DRAM interface

- General-Purpose DMA Controller Module

- Provides high-speed downloads to and from DRAM

- IEEE 1284 Parallel Port Controller Module

- DMA controller supports 2M/sec bidirectional communication transfers

- 16-, 20-, or 25-MHz Operation

- 160-Pin Plastic Quad Flat Packaging

MC68322 USER'S MANUAL

MOTOROLA

### 1.2 PROCESSORS AND MODULES

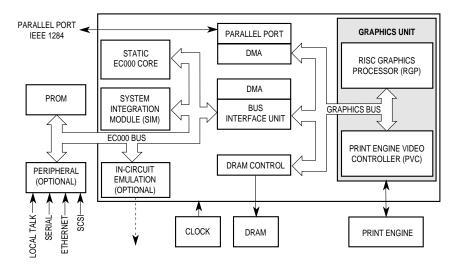

To improve total system throughput and reduce part count, board size, and cost of system implementation, the M68300 Family integrates intelligent peripheral modules with typical glue logic on-chip. The MC68322 consists of two processor units (the EC000 core and RGP) and six modules that assist them (the PVC, bus interface unit, system integration module, DRAM system integration module, DMA controller, and parallel port interface). Figure 1-1 illustrates the MC68322 block diagram.

Figure 1-1. MC68322 Block Diagram

#### 1.2.1 The EC000 Core

The MC68322 contains a static, low-power, 16-bit microprocessor (EC000 core), which performs general-purpose computing, I/O and exception handling, and display list rendering. The core has a 16-bit data path that is upward compatible with 32-bit machines. It also has a 32-bit internal architecture with internal 32-bit data and address registers, and an extended address range. The address range is 28 bits for internal register decoding of chip-selects and DRAM controller functions. This address range allows for full code compatibility with existing M68000 Family-based designs and future upward compatibility to higher performance designs. The core is register and memory-map compatible with the industry standard MC68000, MC68EC000, and MC68HC000 processors.

The MC68322 is designed to support in-circuit emulation with existing emulators so that new hardware and software designs being ported to the MC68322 can be tested rapidly. This is accomplished by providing signals in a 208-pin grid array (PGA) package that are not available in the 160-pin quad flat pack (QFP) package.

MOTOROLA

#### 1.2.2 Graphics Unit

The graphics unit performs all graphics functions required by complex PDLs, such as bit-block transfer (bitBLT). A bitBLT is a CPU-intensive function of logically bits from one memory location to another. The graphics unit acts as a dedicated hardware execution engine to perform the bitBLT function with virtually no intervention from the core. bitBLT operations are performed very fast by the graphics unit, supporting one, two, and three operand bitBLT operations to yield 256 logical bitBLT operation combinations.

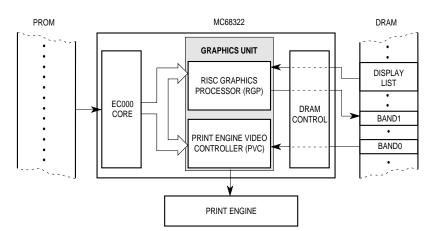

The graphics unit contains two independent processing units that can function in parallel with the core—a RISC graphics processor (RGP) and a print engine video controller (PVC). Both processing units perform burst read and write accesses to DRAM through the DRAM controller. The RGP is a high-performance bit-image processor optimized for the 16-bit DRAM controller on the MC68322. It achieves performance levels that enable the MC68322 to be used effectively in banding applications or in other high-speed, high-density bitmapped graphics products. The RGP is comprised of four major blocks:

- · Graphic order parser

- Graphic order execution unit

- Writeback logic

- Band control registers

The PVC contains a generic nonimpact printer communication interface, which can be used with most of the printers currently on the market. The communications interface is 8-bit synchronous full duplex and supports almost all laser and inkjet printers. Internal interrupt events (if enabled) indicate that a serial command has been sent or a serial status has been received. This interface accesses a memory-mapped register called the printer communication interface register, which contains 8-bit command and status fields. Using these fields, the printer communication interface controls the CBSY and SBSY signals to provide a handshake that communicates between the PVC and the print engine. In addition to this communication interface, the PVC also provides for serialization of the bitmap image data through the video data output at a clock rate specified by the video clock input. A digital phase-locked loop is also provided for those printers that do not supply a video clock source.

The RGP interprets a list of special instructions called graphic orders (a display list that the core or host application processor generates) to render a banded bitmap page image. After a page or band image is rendered by the RGP, the PVC converts the bitmap image into a serial datastream and transfers the rendered page image through the video port to the print engine. Both the RGP and PVC require only a minimal amount of initialization and intervention by the core to produce an image and transfer it to the print engine. Figure 1-2 illustrates the data flow of the graphics unit.

Figure 1-2. Graphics Unit Data Flow Diagram

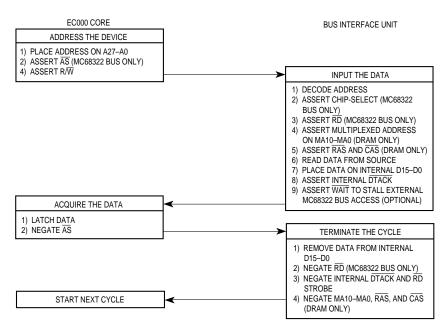

### 1.2.3 Bus Interface Unit

The dual bus architecture of the MC68322 allows the printing workload to be distributed among processing units and executed in parallel. The bus interface unit (BIU) allows the core and graphics unit, which reside on the MC68322 bus and graphics bus, to function independently. This is done through an arbitration unit which accommodates core accesses to DRAM residing on the graphics bus. However, to print pages correctly, the graphics unit gets higher priority than the core for DRAM accesses. The core performs instruction and PROM data fetches without any impact to graphics bus operations. The BIU contains a single-word, writeback buffer that reduces peak bus traffic generated by multiple active modules. The write back buffer provides a no-wait state write profile to the core and delays the write until the graphics unit stops using the graphics bus.

### 1.2.4 System Integration Module

The system integration module (SIM) provides the ROM, PROM, and peripheral chip-selects. It contains eight chip-select banks that can be programmed to decode addresses and supply internal DTACK termination. These eight chip-select banks are individually programmable for an address range of 256K to 64M. They can be located anywhere within the 256M memory map and can be either contiguous or disjointed, as required by the operating environment. Also, each chip-select bank can be independently size or disabled.

The chip-selects for each bank can be set up to provide a wide range of timing parameters, such as setup, access, hold, and recovery times for both read and write bus cycles. The MC68322's SIM provides internal bus cycle auto-acknowledge and the asynchronous WAIT signal allows external devices to insert additional wait states as needed. The SIM also allows SRAM to be added to the MC68322 bus for system stack space, temporary data storage, or as a buffer for peripheral data.

MOTOROLA

### 1.2.5 DRAM Controller

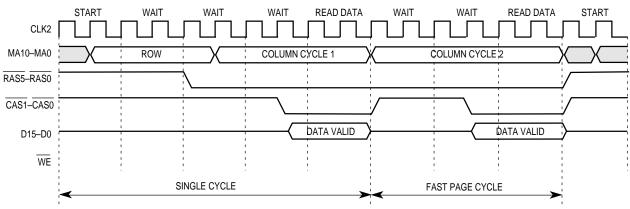

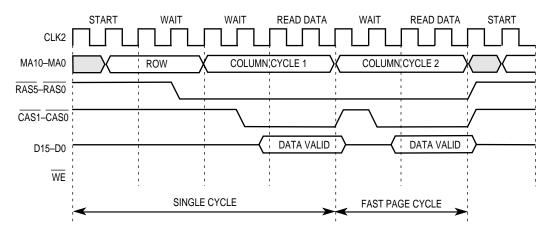

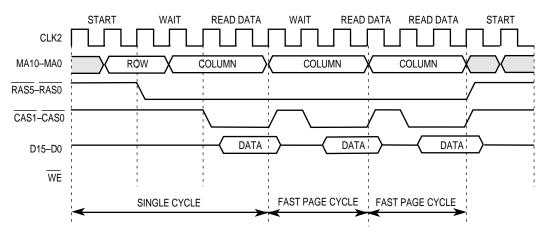

The MC68322 provides a fully integrated bursting DRAM controller containing six DRAM banks of varying programmable sizes and locations. They can be located contiguously or disjointedly, as required by the operating environment. The DRAM controller multiplexes addresses to provide up to 8M of DRAM address space per bank. The timing parameters for each DRAM bank are preprogrammed to provide a 3-, 4-, or 5-clock access from industry standard fast-page mode DRAMs. On reset, all DRAM banks are disabled. Additionally, the DRAM controller provides a separate 16-bit DRAM data path and a write enable signal for a glueless DRAM interface. DRAM refresh cycles are carried out with CAS before RAS refresh cycles. The DRAM refresh rate is fully programmable and the controller performs refreshes from system reset until it is initialized.

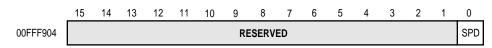

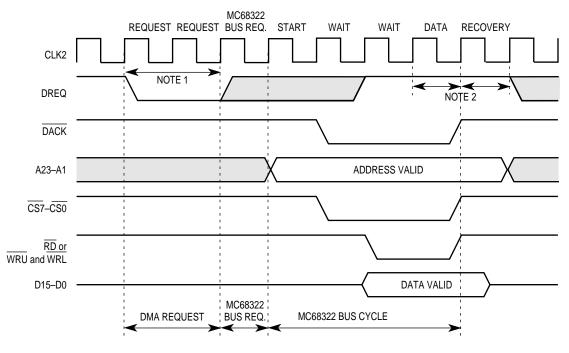

### 1.2.6 DMA Interface

The DMA interface contains two DMA controllers—a single-ended general-purpose DMA (GDMA) and a dedicated parallel port interface DMA (PDMA) controller. The DMA interface can be programmed to transfer data from a high-speed I/O peripheral to DRAM with minimal intervention from the core.

### 1.2.7 Parallel Port Interface

The MC68322 contains a direct, IEEE 1284 Level 2 compliant, bidirectional 8-bit PPI. The PPI supports four IEEE 1284 communications modes—compatibility (Centronics<sup>™</sup>), nibble, byte, and enhanced capabilities port (ECP). It also fully supports all variants of these modes, including device ID requests and run-length encoded data compression. The PPI contains specialized hardware to provide automatic handshaking during forward data transfers. When hardware handshaking is used in conjunction with the PDMA, transfer rates as high as 2M/sec and up can be achieved in the ECP forward mode. The hardware handshaking can also be completely disabled for the software to directly control the parallel port interface signals and support new protocols. Control and data signals provide a glueless interface to the parallel port.

### **1.3 INTERNAL MEMORY MAP**

The MC68322 uses memory-mapped registers that occupy 4K of memory space. With these registers the hardware configuration and timing can be set, the status information can be read, and the PVC, RGP, DMA, and PPI interfaces can be controlled. All registers can be written and read, except for a few read-only and write-only registers that are noted. For more information about each register, see its corresponding module's section. **Appendix C Memory-Mapped Register Summary** discusses all the registers and their location in memory during power-up.

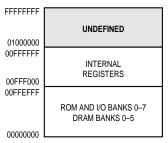

Register operations are implemented within one MC68322 bus cycle for both read and write operations and are completed without asserting any wait states. The registers should only be read and/or written as 16-bit words. All register addresses are on word boundaries. The MC68322 powers up with a 16M memory map with the registers occupying the upper 4K of the 16M of memory space. They are located at address range 0x00FFF000 through 0x00FFFFFF. The MC68322 memory map for a 16M memory space is illustrated in Figure 1-3.

Figure 1-3. 16M Memory Map

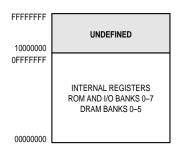

After power-up, the MC68322 can be configured for the full 256M address space and the registers can be moved to start at a higher address. The MC68322 memory map for a 256M memory space is illustrated in Figure 1-4.

Figure 1-4. 256M Memory Map

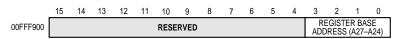

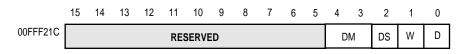

The memory map address register contains bits 27–24 of the register set's base address and is illustrated in Figure 1-5. This register is used to relocate the memory-mapped registers within the memory map.

Figure 1-5. Memory Map Address Register

DRAM, ROM, or I/O can be programmed individually to reside anywhere in the memory map. The address space for registers, ROM or I/O (chip-selects), and DRAM can overlap. In case of an address overlap, registers have the highest priority, then chip-selects, and finally the DRAM. Only the device with the highest priority responds to the access.

MOTOROLA

### 1.4 UNDERSTANDING THE MC68322

Familiarity with some of the basic printer operation concepts is key to understanding how the MC68322 works. These concepts include understanding printer languages, bitmaps, banding, halftoning, and duplex printing.

### 1.4.1 Printer Languages

There are three basic types of printer languages:

- Printer Control Language (PCL)—A term coined by Hewlett Packard when LaserJet printers were first introduced. It embodies a relatively simple set of escape sequences reminiscent of ANSI 3.64. Of the common printer languages, PCL is considered moderately complex.

- 2. Page Description Languages (PDL)—Actual programming languages. The major players are Adobe's PostScript and Microsoft's TrueImage and they resemble other languages like BASIC, FORTRAN, and C, except that PDLs are interpreted rather than compiled. The instructions for how the page is to be formed are described in lexical verbs such as FINDFONT and MOVETO. This means that the parsing and interpretation of these languages must be done in the printer engine itself. Generally, PDLs describe one page at a time and each page is a separate PDL program. Also, PDLs are considered highly complex.

- 3. Document Description Languages (DDL)—Similar to PDLs in that they are programming languages with lexical verbs. The difference between DDLs and PDLs is that DDLs generally describe an entire document consisting of multiple pages. This increases the storage requirements of a printer in that the entire document must be parsed and interpreted before any printing can begin. Like PDLs, DDLs are considered highly complex.

### 1.4.2 Bitmap

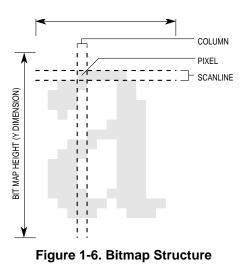

A bitmap is a two dimensional array of memory bits. A scanline is one row in the array. There is no special term for each column of the array. The junction point of a scanline and a column is a pixel. The bitmap width, called the X dimension, is the number of pixels in each scanline. The bitmap height, called the Y dimension, is the number of scanlines in the bitmap array. Figure 1-6 illustrates these terms.

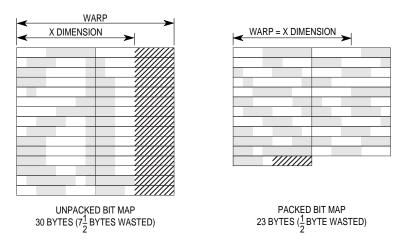

A bitmap can be stored in memory as either packed or unpacked, as illustrated in Figure7. Packed bitmaps occupy less memory than unpacked bitmaps. In an unpacked bitmap, each scanline begins on a byte or word boundary. In a packed bitmap, scanlines follow one another without regard to byte or word boundaries. The MC68322 supports both packed and unpacked bitmap structures.

MOTOROLA

In addition to width and height dimensions, an unpacked bitmap also possesses an attribute known as the bitmap warp, which is the distance between the beginning of each consecutive scanline. The bitmap warp is the value used to obtain Y dimension movement within the bitmap. For example, to move from one pixel to a pixel in the same column, but in the next lower scanline, simply add the bitmap warp to the current position in memory. A packed bitmap also has a bitmap warp that is equal to the width of the bitmap.

### 1.4.3 Banding

Banding is a process in which the page to be printed is constructed in a series of partial page images or bands. To better accommodate banding, the MC68322 allows the page image to be represented in an intermediate form. In this intermediate form, the page image is represented by a series of graphic orders, which are collectively called a display list and are maintained in memory.

The PDL or PCL emulator firmware running on the core generates the display list before the print engine begins the actual printing process. The RGP executes the graphic orders in the display list to build the bitmapped image in bands as the print engine is started. Generally, band n+1 is being constructed while band n is being output to the print engine.

### 1.4.4 Halftoning

Halftoning involves applying a pattern or halftone screen to a data transfer to modify its appearance. Halftone screens are used to produce shades of gray in a monochrome printing environment such as printing presses, dot matrix printers, or laser printers. Halftone screens are commonly seen in newspapers because that is where photographs with levels of gray are represented with a medium that only allows black and white. Halftone screens are repetitive in both the X and Y dimensions of a bitmap array. For example, to perform shading, a 10101010 pattern might be applied to the even scanlines and a 01010101 pattern to the odd scanlines.

### 1.4.5 Duplex Printing

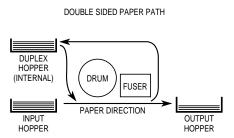

The MC68322 supports duplex printing applications. Duplex printing is the operation of placing an image on both sides of a page before it leaves the printer. In a duplex laser printer, paper travels out of the input hopper and under a drum to receive a toner image. The paper then travels through a fuser to set the toner onto the first side of the paper and into an internal duplex hopper. Next, the paper moves out of the duplex hopper and under the drum again to receive the second toner image, this time on the reverse side of the paper. Finally, once the second image has been fused, the paper is placed in the output hopper.

Figure 1-8. Duplex Laser Printer Paper Path

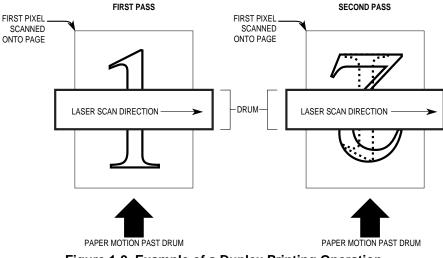

Since the image is placed on both sides of the page in duplex printing, image orientation is important. When the page is turned to read either side, both images must appear right-side up. To achieve the correct image orientation, the physical characteristics of the print engine and the format of the printed page must be taken into consideration. For example, it is important to know how the page is turned over to expose both sides to the drum inside the print engine as well as how the page is going to be bound in the completed document.

Images printed on the opposite side of a page may have to be rotated 180Understandably, these types of pages are called 180° pages. They require pixel data to be transmitted from the page image bitmap starting at the bottom-right corner and then continuing from right to left, bottom to top. Pages that do not require this type of rotation are called 0° pages and they are transmitted starting at the top-left corner and then continuing from left to right, top to bottom.

In banding applications, 180° pages require special attention. Since the page image is transmitted to the print engine in bottom to top order, bands must be generated in this order too. The MC68322 directly supports 180° page rendering and printing as required by duplex banding applications. The RGP and graphic order instruction set are specifically designed to render images either top to bottom or bottom to top, thus enabling banding of both 0° and 180° pages on duplex printers.

MOTOROLA

There are two elements to keep in mind when determining image orientation—the feed edge and the binding edge. The feed edge of a page is the edge that is first fed into the print engine. The binding edge of a page is the edge that will be used in the binding process. For example, if a document is to be stored in a three-ring binder, the binding edge would be the edge of the paper where the holes are punched. To determine whether the second side of a page needs to be rotated, the feed edge must be compared to the binding edge. If the feed edge is the same as the binding edge, then the second side does not need to be rotated. However, if the feed edge is different from the binding edge, then the second side must be rotated 180° to have the proper orientation between both sides of the page.

Figure 1-9 illustrates a duplex printing operation. The paper is fed by its short edge when the binding edge is defined as the long edge. This means the second pass image should be rotated 180°. During the first pass, paper travels from the input hopper and under the drum and an image is placed on the page. After fusing, the page is placed face down in the duplex hopper. During the second pass, paper travels from the duplex hopper and under the drum and another image is placed on the page. After fusing, the page is placed in the output hopper with the second pass image facing up. To properly orient the two images on the page the second pass data must be sent to the printer in right to left and bottom to top order so that a 180° image rotation will occur.

Figure 1-9. Example of a Duplex Printing Operation

## SECTION 2 SIGNAL DESCRIPTIONS

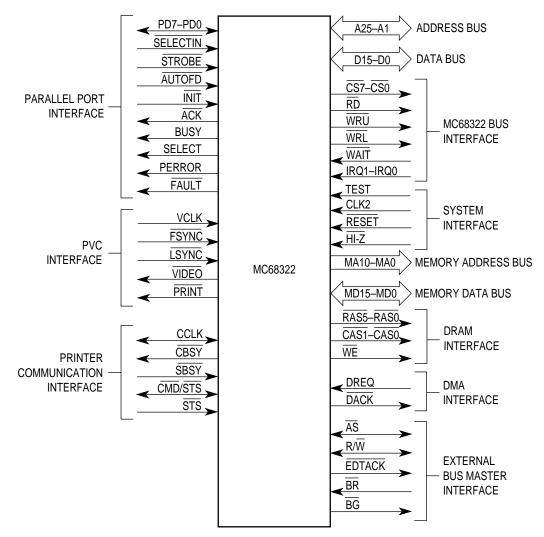

This section contains brief descriptions of the MC68322 input and output signals as illustrated in the figure below.

Figure 2-1. Functional Signal Groups

|                                    |           | INPUT/OUTPUT |                        | THREE-STATED |         |

|------------------------------------|-----------|--------------|------------------------|--------------|---------|

| SIGNAL NAME                        | MNEMONIC  |              | ACTIVE STATE           | ON BG        | ON HI-Z |

| Address Bus                        | A25–A1    | Input/Output | —                      | Yes          | Yes     |

| Parallel Port Acknowledge          | ACK       | Output       | Low                    | No           | Yes     |

| Address Strobe                     | ĀS        | Input/Output | Low                    | Yes          | Yes     |

| Parallel Port Autofeed             | AUTOFD    | Input        | Low                    | _            | _       |

| Bus Grant                          | BG        | Output       | Low                    | No           | Yes     |

| Bus Request                        | BR        | Input        | Low                    | —            | —       |

| Parallel Port Busy                 | BUSY      | Output       | High                   | No           | Yes     |

| Column Address Strobe              | CAS1-CAS0 | Output       | Low                    | No           | Yes     |

| Command Busy                       | CBSY      | Output       | Low                    | No           | Yes     |

| Command Clock                      | CCLK      | Input/Output | _                      | No           | Yes     |

| 2X System Clock                    | CLK2      | Input        | _                      |              | _       |

| Command/Status Data                | CMD/STS   | Input/Output | Low                    | No           | Yes     |

| Chip Select                        | CS7-CS0   | Output       | Low                    | No           | Yes     |

| Data Bus                           | D0-D15    | Input/Output | _                      | No           | Yes     |

| DMA Data Acknowledge               | DACK      | Output       | Low                    | —            | Yes     |

| DMA Data Request                   | DREQ      | Input        | Programmable           | _            | _       |

| External Master DTACK              | EDTACK    | Output       | Low                    | No           | Yes     |

| Parallel Port Fault                | FAULT     | Output       | Low                    | No           | Yes     |

| Frame Synchronization              | FSYNC     | Input        | Programmable           | _            | _       |

| Parallel Port Initialization Input | ĪNIT      | Input        | Low                    | _            | _       |

| Interrupt Request                  | IRQ1-IRQ0 | Input        | Programmable           | —            | —       |

| Line Synchronization               | LSYNC     | Input        | Programmable           | _            | _       |

| DRAM Multiplexed Address Bus       | MA10-MA0  | Output       | —                      | No           | Yes     |

| DRAM Memory Data Bus               | MD15-MD0  | Input/Output | —                      | No           | Yes     |

| Parallel Port Data Bus             | PD7–PD0   | Input/Output | —                      | No           | Yes     |

| Parallel Port Paper Error          | PERROR    | Output       | Low                    | No           | Yes     |

| Print Request                      | PRINT     | Output       | Programmable           | No           | Yes     |

| Read/Write                         | R/W       | Input/Output | Read-High<br>Write-Low | Yes*         | Yes     |

| DRAM Row Address Strobe            | RAS5-RAS0 | Output       | Low                    | No           | Yes     |

| Read Strobe                        | RD        | Output       | Low                    | No           | Yes     |

| Reset                              | RESET     | Input        | Low                    | —            |         |

| Status Busy                        | SBSY      | Input        | Low                    | —            | —       |

| Parallel Port Selected             | SELECT    | Output       | High                   | No           | Yes     |

| Parallel Port Select In            | SELECTIN  | Input        | Low                    | _            | —       |

| Parallel Port Data Strobe          | STROBE    | Input        | Low                    | _            | _       |

### Table 2-1. Signal Summary

|                      |                       |        |              | THREE-STATED |         |

|----------------------|-----------------------|--------|--------------|--------------|---------|

| SIGNAL NAME          | MNEMONIC INPUT/OUTPUT |        | ACTIVE STATE | ON BG        | ON HI-Z |

| Status Data          | STS                   | Input  | Low          | _            | _       |

| High Impedance       | HI-Z                  | Input  | Low          | _            | _       |

| Power Input          | V <sub>CC</sub>       | Input  | —            | _            | _       |

| Video Clock          | VCLK                  | Input  | Programmable | _            | _       |

| Video                | VIDEO                 | Output | Programmable | No           | Yes     |

| Processor Wait       | WAIT                  | Input  | Low          | _            | _       |

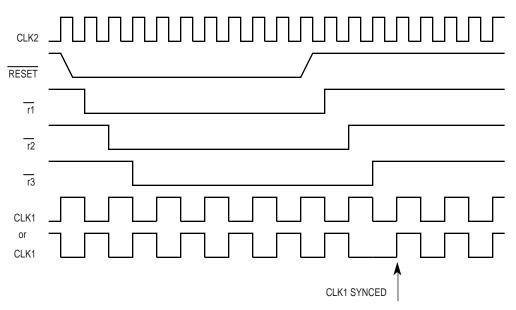

| DRAM Write Enable    | WE                    | Output | Low          | No           | Yes     |