## **MOTOROLA**

SEMICONDUCTOR TECHNICAL DATA

# Advance Information

# **2.8** $\Omega$ (Typ) Quad H-Bridge Motor Driver

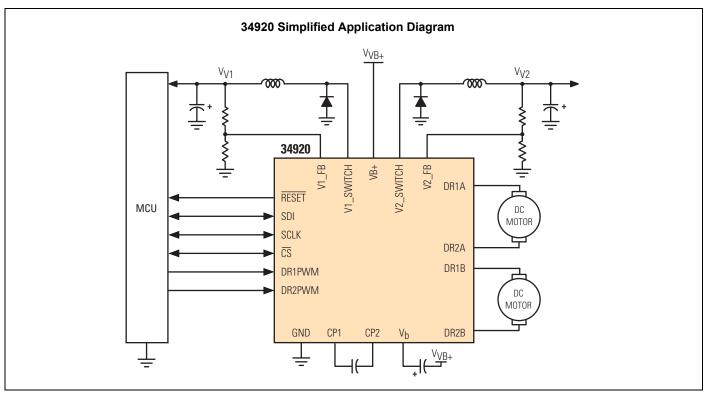

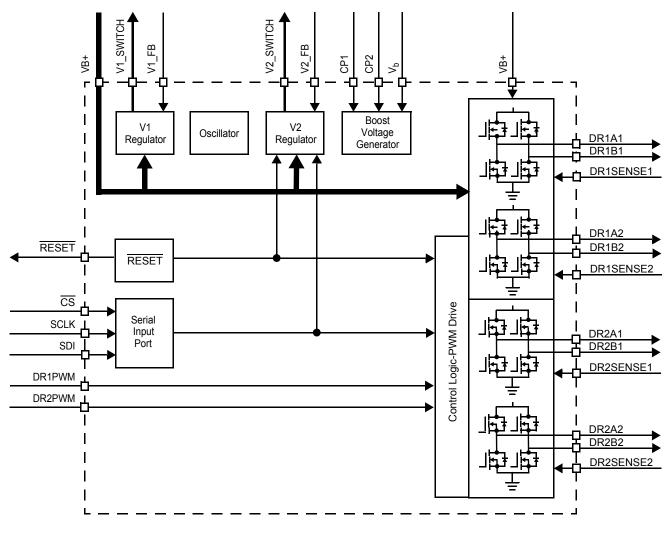

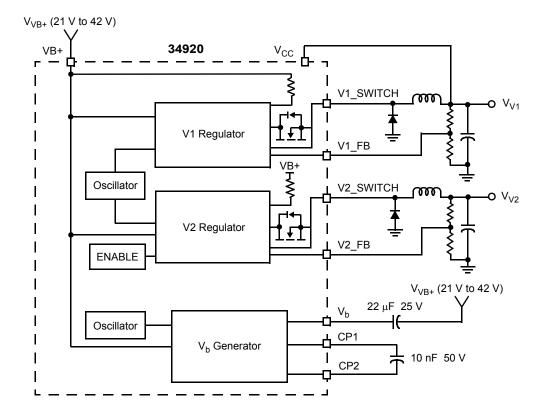

The 34920 is a multifunctional analog ASIC. The 34920 integrates two circuits, four H-bridge drivers, a reset circuit in a single IC, and two DC/DC switching voltage regulators. Input voltage is 21 V to 42 V DC.

Each motor of the two driver blocks can be configured as either a DC motor driver with pulse width modulation (PWM)-control or a single bipolar step motor driver. In step motor mode, both drivers are capable of being operated in the quarter step mode.

In DC motor mode, both bridges in a driver are in parallel, providing 2.4 A of drive current. In step motor mode, each bridge in a driver drives one phase. Each phase is driven with a bipolar current mode drive.

### Features

- Individual Thermal Limit Protection

- User-Selectable Motors: 2 DC Motors (2.4 A/Motor), 2 Step Motors (W1-2 Phase Control), 1 DC Motor and 1 Step Motor

- 2 Buck Regulators (Switching @ 200 kHz)

- V<sub>V2</sub> Output Voltage Is Programmable to 10 V to 15 V DC (Externally Set)

- Low-Voltage Detection Reset (V<sub>V1</sub> and V<sub>VB+</sub>)

- Pb-Free Packaging Designated by Suffix Code EI

34920

## **ORDERING INFORMATION**

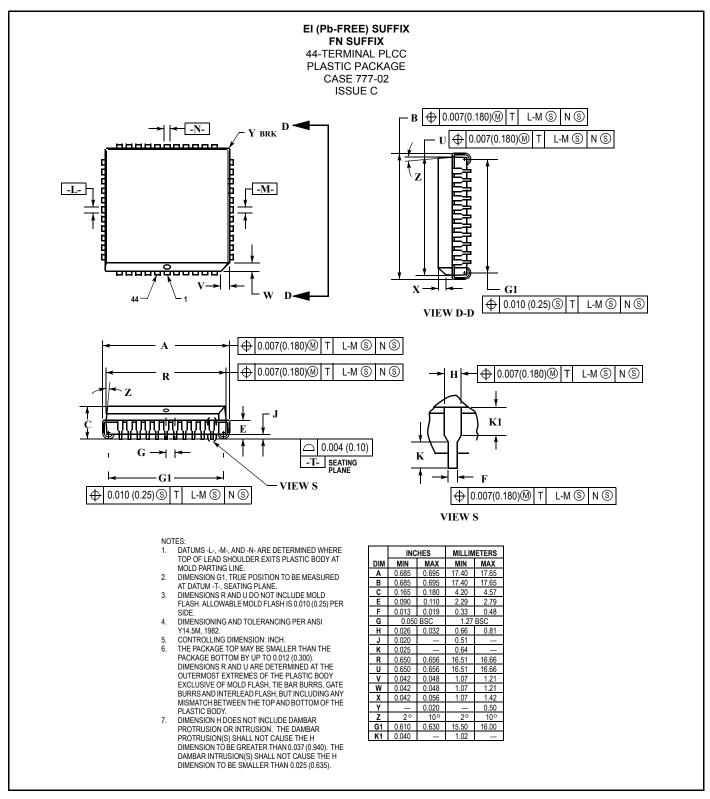

| Device          | Temperature<br>Range (T <sub>A</sub> ) | Package |

|-----------------|----------------------------------------|---------|

| MC34920EI/FN/R2 | 0°C to 70°C                            | 44 PLCC |

digitaldna

intelligence everywhere

This document contains certain information on a new product. Specifications and information herein are subject to change without notice

**IOTOROLA** For More Information On This Pro Go to: www.freescale.com

Figure 1. 34920 Simplified Internal Block Diagram

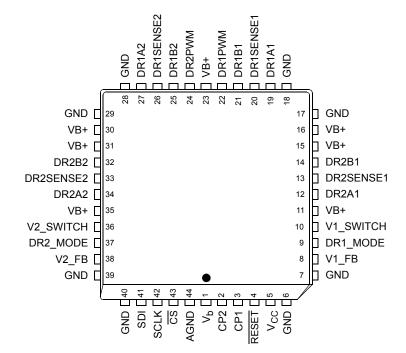

## TERMINAL FUNCTION DESCRIPTION

| Terminal                        | Terminal Name   | Formal Name                             | Definition                                                                                                     |

|---------------------------------|-----------------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------|

| 1                               | Vb              | Output terminal to V <sub>Vb</sub>      | Terminal to connect to V <sub>Vb</sub> capacitor.                                                              |

| 2 CP2                           |                 | Capacitor to CP1                        | Terminal for boost generator switch capacitor.                                                                 |

| 3                               | CP1             | Capacitor to CP2                        | Terminal for boost generator switch capacitor.                                                                 |

| 4                               | RESET           | Reset Output                            | Active low Reset output.                                                                                       |

| 5                               | V <sub>CC</sub> | V <sub>CC</sub> Supply Voltage          | $V_{CC}$ power input for internal use. The 34920 accepts either 3.3 V ±10% or 5.0 V ±5% for its logic voltage. |

| 6, 7, 17, 18, 28,<br>29, 39, 40 | GND             | Substrate Ground                        | Ground connections for digital IC circuitry.                                                                   |

| 8                               | V1_FB           | V1 Regulator Feedback Input             | Voltage feedback for the V1 regulator.                                                                         |

| 9                               | DR1_MODE        | Mode Select for Driver 1                | Selects operational mode of Driver 1; Step = 1/DC = 0.                                                         |

| 10                              | V1_SWITCH       | Internal MOSFET Source for V1 Regulator | Switching output for V1 regulator.                                                                             |

| 11, 15, 16, 23,<br>30, 31, 35   | VB+             | VB+ (Bulk) Supply Voltage               | High-voltage supply for motors and regulators.                                                                 |

| 12                              | DR2A1           | Driver 2, Bridge 1, Output A            | Motor driver output.                                                                                           |

| 13                              | DR2SENSE1       | Driver 2, Bridge 1, I Sense             | Current sense for current mode.                                                                                |

| 14                              | DR2B1           | Driver 2, Bridge 1, Output B            | Motor driver output.                                                                                           |

| 19                              | DR1A1           | Driver 1, Bridge 1, Output A            | Motor driver output.                                                                                           |

| 20                              | DR1SENSE1       | Driver 1, Bridge 1, I Sense             | Current sense for current mode.                                                                                |

| 21                              | DR1B1           | Driver 1, Bridge 1, Output B            | Motor driver output.                                                                                           |

| 22                              | DR1PWM          | Driver 1 PWM Input                      | PWM input for Driver 1. Used only when DR1_MODE terminal = 0.                                                  |

| 24                              | DR2PWM          | Driver 2 PWM Input                      | PWM input for Driver 2. Used only when DR2_MODE terminal = 0.                                                  |

| 25                              | DR1B2           | Driver 1, Bridge 2, Output B            | Motor driver output.                                                                                           |

### **TERMINAL FUNCTION DESCRIPTION (continued)**

| Terminal Terminal Name |           | Formal Name                             | Definition                                             |

|------------------------|-----------|-----------------------------------------|--------------------------------------------------------|

| 26                     | DR1SENSE2 | Driver 1, Bridge 2, I Sense             | Current sense for current mode.                        |

| 27                     | DR1A2     | Driver 1, Bridge 2, Output A            | Motor driver output.                                   |

| 32                     | DR2B2     | Driver 2, Bridge 2, Output B            | Motor driver output.                                   |

| 33                     | DR2SENSE2 | Driver 2, Bridge 2, I Sense             | Current sense for current mode.                        |

| 34                     | DR2A2     | Driver 2, Bridge 2, Output A            | Motor driver output.                                   |

| 36                     | V2_SWITCH | Internal MOSFET Source for V2 Regulator | Switching output for V2 regulator.                     |

| 37                     | DR2_MODE  | Mode Select for Driver 2                | Selects operational mode of Driver 2. Step = 1/DC = 0. |

| 38                     | V2_FB     | V2 Regulator Feedback Input             | Switch output for V2 regulator.                        |

| 41                     | SDI       | Serial Port Data Input                  | Serial input register serial data input.               |

| 42                     | SCLK      | Serial Data Port Clock                  | Serial input register clock.                           |

| 43                     | CS        | Serial Data Port Chip Select            | Serial input register chip select input. Active low.   |

| 44                     | AGND      | Analog Ground                           | Ground connection for analog circuitry.                |

#### **MAXIMUM RATINGS**

All voltages are with respect to ground unless otherwise noted.

| Rating                                                             | Symbol                                 | Value                 | Unit |

|--------------------------------------------------------------------|----------------------------------------|-----------------------|------|

| VB+ Supply Voltage                                                 | V <sub>VB+</sub>                       | 45                    | V    |

| V <sub>CC</sub> Voltage                                            | V <sub>CC(MAX)</sub>                   | 7.0                   | V    |

| Bridge Output Current                                              | I <sub>OUT</sub>                       | 1.5                   | A    |

| Maximum Voltage on RESET (Note 1)                                  | V <sub>MAXRST</sub>                    | V <sub>CC</sub> - 0.5 | V    |

| ESD Voltage<br>Human Body Model (Note 2)<br>Machine Model (Note 3) | V <sub>ESD1</sub><br>V <sub>ESD2</sub> | ±1000<br>±100         | V    |

| Storage Temperature                                                | T <sub>STG</sub>                       | -40 to 175            | °C   |

| Operating Ambient Temperature                                      | T <sub>A</sub>                         | 0 to 70               | °C   |

| Operating Junction Temperature                                     | TJ                                     | 135                   | °C   |

| Power Dissipation ( $T_A = 25^{\circ} C$ ) (Note 4)                | PD                                     | 2.0                   | W    |

| Terminal Soldering Temperature (Note 5)                            | T <sub>SOLDER</sub>                    | 220                   | °C   |

| Thermal Resistance, Junction to Ambient (Note 6)                   | $R_{	extsf{	heta}JA}$                  | 37                    | °C/W |

Notes

1. RESET is an open drain (open collector) output with an internal pull-up resistor.

2. ESD1 testing is performed in accordance with the Human Body Model ( $C_{ZAP}$ =100 pF,  $R_{ZAP}$ =1500  $\Omega$ ).

3. ESD2 testing is performed in accordance with the Machine Model ( $C_{ZAP}$ =200 pF,  $R_{ZAP}$ =0  $\Omega$ ).

4. Maximum power dissipation at indicated ambient temperature in free air with no heatsink used.

5. Terminal soldering temperature limit is for 10 seconds maximum duration. Not designed for immersion soldering. Exceeding these limits may cause malfunction or permanent damage to the device.

6.  $R_{\theta JA}$  is dependent on customer application and PCB layout.

### STATIC ELECTRICAL CHARACTERISTICS

Characteristics noted under conditions 21 V  $\leq$  V<sub>VB+</sub>  $\leq$  42 V, T<sub>A</sub> = 10°C to 55°C, T<sub>J</sub> max = 135°C, V<sub>CC</sub> = 5.25 V max unless otherwise noted. Typical values noted reflect the approximate parameter mean at T<sub>A</sub> = 25°C under typical conditions unless otherwise noted.

| Characteristic                                                                                   | Symbol                                           | Min        | Тур  | Max        | Unit |

|--------------------------------------------------------------------------------------------------|--------------------------------------------------|------------|------|------------|------|

| POWER INPUT                                                                                      | ιΙ.                                              |            |      | •          |      |

| V <sub>VB+</sub> Supply Voltage                                                                  | V <sub>VB+</sub>                                 | 21         | _    | 42         | V    |

| V <sub>VB+</sub> Standby Current                                                                 | I <sub>VB+</sub>                                 |            |      |            | mA   |

| $V_{VB+}$ = 42 V, $I_{CC}$ Load = 5.0 mA, No Serial Clock, No Motor Driver, No Load on $V_{V2}$  |                                                  | 1.0        | 14   | 55         |      |

| CMOS LOGIC LEVEL (Note 7)                                                                        |                                                  |            |      |            | •    |

| Input Current, High-Voltage State                                                                | I <sub>IH</sub>                                  | -          | 0.1  | 170        | μA   |

| Input Current, Low-Voltage State                                                                 | Ι <sub>ΙL</sub>                                  | -170       | -0.1 | -          | μA   |

| Input Low Input Voltage State<br>$V_{CC}$ + 3.3 V ±10%<br>$V_{CC}$ + 5.0 V ±5%                   | V <sub>IL</sub>                                  |            |      | 0.8<br>1.5 | V    |

| Input High-Voltage State<br>$V_{CC}$ + 3.3 V ±10%<br>$V_{CC}$ + 5.0 V ±5%                        | V <sub>IH</sub>                                  | 2.1<br>3.3 | -    |            | V    |

| V1 AND V2 VOLTAGE REGULATORS                                                                     |                                                  |            |      |            |      |

| Regulator Output Voltage                                                                         | V <sub>OUT</sub>                                 | -4.0%      | Nom  | +4.0%      | V    |

| Regulator Thermal Shutdown Junction Temperature                                                  | T <sub>J(SHUTDOWN)</sub>                         | 155        | -    | 175        | °C   |

| Regulator Thermal Junction Temperature                                                           | T <sub>J(ENABLE)</sub>                           | 135        | -    | 155        | °C   |

| Overcurrent Detect Level (Peak) for IV1_SWITCH                                                   | I <sub>OC_V1</sub>                               | 1.5        | 2.0  | 2.5        | А    |

| Overcurrent Detect Level (Peak) for I <sub>V2_SWITCH</sub>                                       | I <sub>OC_V2</sub>                               | 2.5        | 3.25 | 4.0        | А    |

| Short Circuit Detect Level (Peak) for I <sub>V1_SWITCH</sub><br>In Soft Start and Foldback Modes | I <sub>SC_V1</sub>                               | 0.75       | 1.25 | 1.75       | A    |

| Short Circuit Detect Level (Peak) for I <sub>V2_SWITCH</sub><br>In Soft Start and Foldback Modes | I <sub>SC_V2</sub>                               | 1.75       | 2.25 | 2.75       | A    |

| V1 Switching MOSFET on Resistance<br>Full On, Typical Value @ T <sub>J</sub> = 25°C              | R <sub>DS(ON)V1</sub>                            | _          | 2.0  | _          | Ω    |

| V2 Switching MOSFET on Resistance<br>Full On, Typical Value @ T <sub>J</sub> = 25°C              | R <sub>DS(ON)V2</sub>                            | _          | 0.75 | _          | Ω    |

| Regulator Feedback Input<br>Internal Reference Value of 2.50 V ±2%                               | V <sub>V1_FB</sub> ,<br>V <sub>V2_FB</sub>       | _          | 2.5  | -          | V    |

| Turn-Off Regulator<br>V <sub>V1</sub> Output/V <sub>V2</sub> Output = 0 V                        | Voff <sub>V1_FB</sub> ,<br>Voff <sub>V2_FB</sub> | 3.0        | _    | _          | V    |

Notes

7. Applicable to all logic level input signals. Inputs are to be designed to accept 3.3 V logic levels and be +5.0 V tolerant.

## STATIC ELECTRICAL CHARACTERISTICS (continued)

Characteristics noted under conditions 21 V  $\leq$  V<sub>VB+</sub>  $\leq$  42 V, T<sub>A</sub> = 10°C to 55°C, T<sub>J</sub> max = 135°C, V<sub>CC</sub> = 5.25 V max unless otherwise noted. Typical values noted reflect the approximate parameter mean at T<sub>A</sub> = 25°C under typical conditions unless otherwise noted.

| Characteristic                                                                                                                                               | Symbol                            | Min  | Тур  | Max | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|------|------|-----|------|

| V1 AND V2 VOLTAGE REGULATORS (continued)                                                                                                                     |                                   |      |      |     |      |

| Voltage Overshoot<br>External V <sub>CC</sub> Load Current from 0.01 to 0.500 A, t <sub>RISE</sub> > 100 ns                                                  | V <sub>OVRSHT</sub>               | _    | 5.0% | _   | -    |

| Load Ripple<br>0.5 A maximum                                                                                                                                 | V <sub>OUTRIPPLE</sub>            | _    | 100  | _   | mV   |

| VBOOST GENERATOR                                                                                                                                             |                                   |      |      |     |      |

| Charge Pump Output Voltage<br>I <sub>LOAD</sub> = 1.0 mA                                                                                                     | V <sub>Vb-</sub> V <sub>VB+</sub> | 10   | _    | 14  | V    |

| BIPOLAR CURRENT REGULATED STEP MOTOR DRIVE SYSTEM                                                                                                            |                                   |      |      |     |      |

| Peak Step Motor Current, Phase A or B<br>Motor Not Stalled                                                                                                   | I <sub>STEPMOTOR</sub><br>Peak    | _    | _    | 0.6 | A    |

| Maximum Allowable Voltage Drop Across Any H-Bridge Switch<br>$I_{LOAD}$ = 0.6 A (from Output to GND) or $I_{LOAD}$ = 0.6 A (from V <sub>VB+</sub> to Output) | V <sub>DROP</sub>                 | _    | _    | 1.6 | V    |

| Comparator High Threshold Voltage<br>CURR_I0_PHASEX=0, CURR_I1_PHASEX=0                                                                                      | V <sub>TH</sub>                   | 450  | 550  | 650 | mV   |

| Comparator Medium Threshold Voltage<br>CURR_I0_PHASEX=1, CURR_I1_PHASEX=0                                                                                    | V <sub>TM</sub>                   | 300  | _    | 440 | mV   |

| Comparator Low Threshold Voltage<br>CURR_I0_PHASEX=0, CURR_I1_PHASEX=1                                                                                       | V <sub>TL</sub>                   | 105  | _    | 255 | mV   |

| $V_OOFF$ Output Leakage Current for Step Motor Driver Outputs<br>$V_OOFF = 5.0 V$                                                                            | I <sub>O</sub> OFF                | -1.0 | 0.1  | 1.0 | mA   |

| Step Motor Driver Thermal Shutdown Junction Temperature                                                                                                      | T <sub>J(SHUTDOWN)</sub>          | 155  | -    | 175 | °C   |

| Step Motor Driver Thermal Enable Junction Temperature                                                                                                        | T <sub>J(ENABLE)</sub>            | 135  | -    | 155 | °C   |

| Single MOSFET<br>Typical Value @ T <sub>J</sub> = 25°C                                                                                                       | R <sub>DS(ON)</sub>               | _    | 1.43 | _   | Ω    |

## STATIC ELECTRICAL CHARACTERISTICS (continued)

Characteristics noted under conditions 21 V  $\leq$  V<sub>VB+</sub>  $\leq$  42 V, T<sub>A</sub> = 10°C to 55°C, T<sub>J</sub> max = 135°C, V<sub>CC</sub> = 5.25 V max unless otherwise noted. Typical values noted reflect the approximate parameter mean at T<sub>A</sub> = 25°C under typical conditions unless otherwise noted.

| Characteristic                                                                                                                                                                      | Symbol                               | Min                      | Тур  | Max | Unit |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|--------------------------|------|-----|------|

| DC MOTOR DRIVE SYSTEM                                                                                                                                                               |                                      |                          |      |     |      |

| Maximum Allowable Voltage Drop Across Any H-Bridge Switch                                                                                                                           | V <sub>DROP</sub>                    |                          |      |     | V    |

| $I_{LOAD}$ = 0.75 A (from Output to GND) or $I_{LOAD}$ = 0.75 A (from V <sub>VB+</sub> to Output) (Using 2 H-Bridges in Parallel)                                                   |                                      | -                        | -    | 1.3 |      |

| Peak DC Motor Driver Current<br>Motor Not Stalled (Using 2 H-Bridges in Parallel)                                                                                                   | I <sub>DCMOTOR</sub><br>Peak Current | _                        | _    | 1.2 | A    |

| DC Motor Overcurrent Threshold (Note 8)                                                                                                                                             | I <sub>DCMOTOR</sub> OCT             |                          |      |     | А    |

| Motor Stalled (Paralleled H-Bridges Used for DC Motor Drive)                                                                                                                        | DCMOTOR                              | 1.6                      | 2.0  | 2.5 |      |

| DC Motor Driver Sustaining Current Value                                                                                                                                            | IDC_SUSTAIN                          |                          |      |     | А    |

| Current Allowed to Sustain for a Minimum of 100 ms (OCT delay),<br>Current Ripple 100 mA (Peak-to-Peak or Less)                                                                     |                                      | 1.6                      | 2.0  | 2.4 |      |

| Differential DC Motor Driver Output Voltage                                                                                                                                         | V <sub>DCMD</sub>                    |                          |      |     | V    |

| $V_{VB+}$ + Rising Monotonically from 0 V to 42 V (1.0 $\mu$ s < t <sub>R</sub> < 10 ms) OR $V_{VB+}$ Falling Monotonically from 42 V to 0 V (1.0 $\mu$ s < t <sub>F</sub> < 10 ms) |                                      | -                        | -    | 4.0 |      |

| DC Motor Driver Thermal Shutdown Output Voltage                                                                                                                                     | V <sub>OH_DCM</sub>                  |                          |      |     | V    |

| I <sub>OH</sub> = 0.1 V                                                                                                                                                             |                                      | V <sub>VB+</sub> - 0.5 V | -    | -   |      |

| DC Motor Driver Thermal Shutdown Junction Temperature                                                                                                                               | T <sub>J(SHUTDOWN)</sub>             | 155                      | -    | 175 | °C   |

| DC Motor Driver Thermal Enable Junction Temperature                                                                                                                                 | T <sub>J(ENABLE)</sub>               | 135                      | _    | 155 | °C   |

| Equivalent Resistance                                                                                                                                                               | R <sub>DS(ON)</sub>                  |                          |      |     | Ω    |

| Using 2 H-Bridges in Parallel, Nom Value @ $T_J$ = 25°C                                                                                                                             |                                      | -                        | 0.73 | -   |      |

### Notes

8. Because the current clamp is applied to the top H-bridge transistors only, overcurrent protection applies to motor currents. But note that no short circuit protection exists against shorts from the DC motor outputs (DR1A1, DR1A2, DR1B1, or DR1B2 to substrate ground or to VB+.

## STATIC ELECTRICAL CHARACTERISTICS (continued)

Characteristics noted under conditions 21 V  $\leq$  V<sub>VB+</sub>  $\leq$  42 V, T<sub>A</sub> = 10°C to 55°C, T<sub>J</sub> max = 135°C, V<sub>CC</sub> = 5.25 V max unless otherwise noted. Typical values noted reflect the approximate parameter mean at T<sub>A</sub> = 25°C under typical conditions unless otherwise noted.

| Characteristic                          | Symbol             | Min                     | Тур  | Max  | Unit |

|-----------------------------------------|--------------------|-------------------------|------|------|------|

| RESET                                   |                    |                         |      |      |      |

| RESET High-State Output Voltage         | V <sub>OH</sub>    |                         |      |      | V    |

| I <sub>OH</sub> = -0.1 mA               |                    | V <sub>CC</sub> - 0.5 V | -    | -    |      |

| RESET Low-State Output Voltage          | V <sub>OL</sub>    |                         |      |      | V    |

| $V_{V1}_{FB} < V_{V1T+}$                |                    | -                       | -    | 0.2  |      |

| Input Low Voltage State                 | V <sub>IL</sub>    |                         |      |      | V    |

| V <sub>CC</sub> + 3.3 V ±10%            |                    | -                       | -    | 0.8  |      |

| V <sub>CC</sub> + 5.0 V ±5%             |                    | -                       | -    | 1.5  |      |

| Input High-Voltage State                | V <sub>IH</sub>    |                         |      |      | V    |

| V <sub>CC</sub> + 3.3 V ±10%            |                    | 2.1                     | -    | -    |      |

| V <sub>CC</sub> + 5.0 V ±5%             |                    | 3.3                     | -    | -    |      |

| RESET $V_{V1\_FB}$ Low Threshold        | V <sub>V1T-</sub>  |                         |      |      | V    |

| Voltage at V1_FB ↓                      |                    | 1.9                     | 2.08 | 2.2  |      |

| RESET V <sub>V1_FB</sub> High Threshold | V <sub>V1T+</sub>  |                         |      |      | V    |

| Voltage at V1_FB <b>†</b>               |                    | 2.05                    | 2.23 | 2.35 |      |

| RESET V <sub>VB+</sub> Low Threshold    | V <sub>VB+T-</sub> |                         |      |      | V    |

| VB+ 🖡                                   |                    | 13.5                    | 15.4 | 16.5 |      |

| RESET V <sub>VB+</sub> High Threshold   | V <sub>VB+T+</sub> |                         |      |      | V    |

| VB+ 1                                   |                    | 13.5                    | 16.6 | 20   |      |

## DYNAMIC ELECTRICAL CHARACTERISTICS

Characteristics noted under conditions 21 V  $\leq$  V<sub>VB+</sub>  $\leq$  42 V, T<sub>A</sub> = 10°C to 55°C, T<sub>J</sub> max = 135°C, V<sub>CC</sub> = 5.25 V max unless otherwise noted. Typical values noted reflect the approximate parameter mean at T<sub>A</sub> = 25°C under typical conditions unless otherwise noted.

| Characteristic                                     | Symbol               | Min    | Тур  | Max | Unit |

|----------------------------------------------------|----------------------|--------|------|-----|------|

| SERIAL INPUT PORT TIMING                           | ·                    |        |      |     |      |

| Serial Clock Frequency                             | f <sub>CLK</sub>     | -      | 4.0  | 12  | MHz  |

| SCLK High Width                                    | t <sub>CLH</sub>     | 41.667 | 125  | -   | ns   |

| SCLK Low Width                                     | t <sub>CLL</sub>     | 41.667 | 125  | -   | ns   |

| Delay CS Falling to First SCLK Rising              | t <u>cs</u> -sclk    | 83.333 | 250  | -   | ns   |

| Delay Last SCLK Rising Edge to CS Rising           | tsclk-CS             | 83.333 | 250  | -   | ns   |

| Data Valid to SCLK Set-Up Time                     | t <sub>DSU</sub>     | 41.667 | 125  | -   | ns   |

| Data Hold Time                                     | t <sub>DHD</sub>     | 41.667 | 125  | -   | ns   |

| SDI Rise Time                                      | t <sub>RD</sub>      | 5.0    | -    | 10  | ns   |

| SDI Fall Time                                      | t <sub>FD</sub>      | 5.0    | -    | 10  | ns   |

| SCLK Rise/Fall Time                                | t <sub>RFC</sub>     | 5.0    | -    | 10  | ns   |

| CS Off-Time (t <sub>DHD</sub> + t <sub>DSU</sub> ) | t <sub>NCS-OFF</sub> | 83.333 | 250  | -   | ns   |

| V1 AND V2 VOLTAGE REGULATORS                       |                      |        |      |     |      |

| Clock Frequency Overtemperature                    | f <sub>OP</sub>      | 175    | 200  | 225 | kHz  |

| V1 Duty Cycle                                      | V1_DC                | 35     | 37.5 | 40  | %    |

| V2 Duty Cycle                                      | V2_DC                | 80     | 82.5 | 85  | %    |

| BIPOLAR CURRENT REGULATED STEP MOTOR DRIVE         | SYSTEM               |        |      |     |      |

| Shoot-Through Delay                                | t <sub>DEAD</sub>    | 15     | 200  | 350 | ns   |

| Off-Time                                           | t <sub>OFF</sub>     | 20     | 29   | 38  | μS   |

| Current Blanking Time                              | t <sub>BLANK</sub>   | 300    | -    | 750 | ns   |

| DC MOTOR DRIVE SYSTEM                              |                      |        |      |     |      |

| PWM Frequency                                      | f <sub>PWM</sub>     |        |      |     | kHz  |

| T <sub>A</sub> = 25°C                              |                      | -      | 20   | 21  |      |

| Shoot-Through Delay                                | t <sub>DEAD</sub>    | 15     | 180  | 350 | ns   |

| Overcurrent Off-Time                               | t <sub>OC_OFF</sub>  | 10     | 40   | 70  | μS   |

## DYNAMIC ELECTRICAL CHARACTERISTICS (continued)

Characteristics noted under conditions 21 V  $\leq$  V<sub>VB+</sub>  $\leq$  42 V, T<sub>A</sub> = 10°C to 55°C, T<sub>J</sub> max = 135°C, V<sub>CC</sub> = 5.25 V max unless otherwise noted. Typical values noted reflect the approximate parameter mean at T<sub>A</sub> = 25°C under typical conditions unless otherwise noted.

| Characteristic                                                                               | Symbol               | Min | Тур | Мах | Unit |

|----------------------------------------------------------------------------------------------|----------------------|-----|-----|-----|------|

| RESET                                                                                        |                      |     |     |     |      |

| $\begin{tabular}{lllllllllllllllllllllllllllllllllll$                                        | t <sub>DELAY</sub>   | 15  | 33  | 50  | ms   |

| $V_{CC}$ Out-of-Tolerance Persistence Time<br>RESET De-Asserted, $V_{V1_{FB}} < V_{V1T_{-}}$ | t <sub>PERSIST</sub> | 10  | 20  | 30  | μS   |

| RESET Rise Time<br>10% to 90% (Note 9)                                                       | t <sub>R</sub>       | -   | 630 | 750 | ns   |

| RESET Fall Time<br>90% to 10% (Note 9)                                                       | t <sub>F</sub>       | _   | 11  | 50  | ns   |

Notes

9. Test circuit is 50 pF capacitor from RESET to GND.

| DIR_PH_A | CURR_I0_<br>PHASEA | CURR_I1_<br>PHASEA | IPH_A (mA) | DIR_PH_B | CURR_10_<br>PHASEB | CURR_I1_<br>PHASEB | IPH_B (mA) |

|----------|--------------------|--------------------|------------|----------|--------------------|--------------------|------------|

| 0        | 0                  | 0                  | 550        | 0        | 0                  | 0                  | 550        |

| 0        | 1                  | 0                  | 367        | 0        | 1                  | 0                  | 367        |

| 0        | 0                  | 1                  | 183        | 0        | 0                  | 1                  | 183        |

| Х        | 1                  | 1                  | Off        | х        | 1                  | 1                  | Off        |

| 1        | 0                  | 0                  | -550       | 1        | 0                  | 0                  | -550       |

| 1        | 1                  | 0                  | -367       | 1        | 1                  | 0                  | -367       |

| 1        | 0                  | 1                  | -183       | 1        | 0                  | 1                  | -183       |

### Table 1. Step Motor Truth Table

## Table 2. DC Motor Drive System Truth Table

| DRx_DIR_DCM | DRxPWM | High-Side A | Low-Side A | High-Side B | Low-Side B |

|-------------|--------|-------------|------------|-------------|------------|

| 0           | 0      | On          | Off        | On          | Off        |

| 0           | 1      | Off         | On         | On          | Off        |

| 1           | 0      | On          | Off        | On          | Off        |

| 1           | 1      | On          | Off        | Off         | On         |

Figure 3. RESET Generation Timing Diagram (Assumes V<sub>VB+</sub> > V<sub>VB+T+</sub> During Entire Period)

## SYSTEM/APPLICATION INFORMATION

## INTRODUCTION

### Introduction

The 34920 is a multifunctional analog IC that can be used in printer and scanner applications. It integrates two switching voltage regulator circuits, four H-bridge drivers, and a reset circuit in a single IC. All 34920 control lines are compatible with CMOS type 3.3 V and 5.0 V logic.

## **Switching Voltage Regulator Circuits**

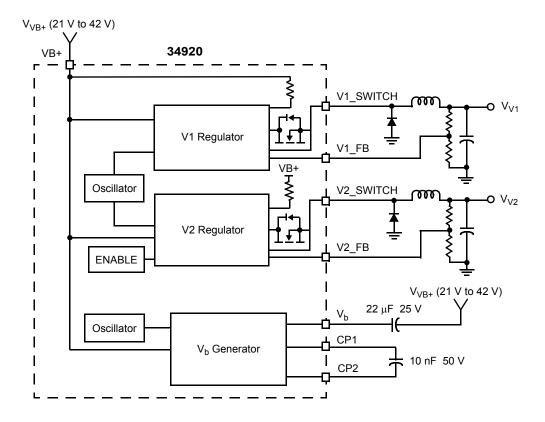

Two switching voltage regulators provide the following voltages from an unregulated input of 21 V to 42 V DC. Both are buck-type switching regulators using a MOSFET (internal to the 34920), current sense resistor (internal to the 34920), Schottky diode (external to the 34920), external inductor, and filter capacitor.

- V1 Voltage Regulator This regulator is programmable, has a duty cycle of 37%, and provides either 3.3 V (+5%/ -4%) or 5.0 V (+5%/-4%) at a current of 10 mA (minimum) to 500 mA (maximum).

- V2 Voltage Regulator This regulator has a programmable output voltage (by means of an external resistor divider network) in the range of 10 V to 15 V ±2% with a VB+ supply voltage range of 21 V to 42 V.

The V2 voltage regulator is controlled by an Enable bit in the serial register that allows software to turn this regulator on and off. However, the Enable bit does not effect the V1 voltage regulator. The Enable bit will disable the V2 voltage regulator and disable all motor driver circuits.

#### **Motor Drivers**

The two motor drivers can be selectable as either a bidirectional DC motor driver, with PWM control and peak currents of 2.4 A, or a bipolar step motor driver, with average current levels of 183 mA and 550 mA per phase, and quarter step mode capability. In step mode, both drivers are capable of being operated in the quarter step mode.

### **RESET** Generation

The 34920 provides an output, RESET, that drives an external reset signal to the system microprocessor and/or the system digital logic IC. This signal is an active low logic level signal that is derived by monitoring the level of the VB+ and V1\_FB terminals.

When RESET is asserted, either internally or from an external source, all 34920 motor driver outputs will be in their inactive states, and the serial input port will be loaded with the reset value.

## FUNCTIONAL DESCRIPTION

## Input Power Supply (V<sub>VB+</sub>)

The input voltage for the switching regulators and motor drivers.  $V_{VB^+}$  is a voltage range of 21 V to 42 V.

### **CMOS Logic Level**

CMOS logic level specifications are described on <u>page 6</u> of the Static Electrical Characteristics table.

### 34920 Input

Table 3, page 15, describes the 34920 input specifications.

### **Serial Input Port**

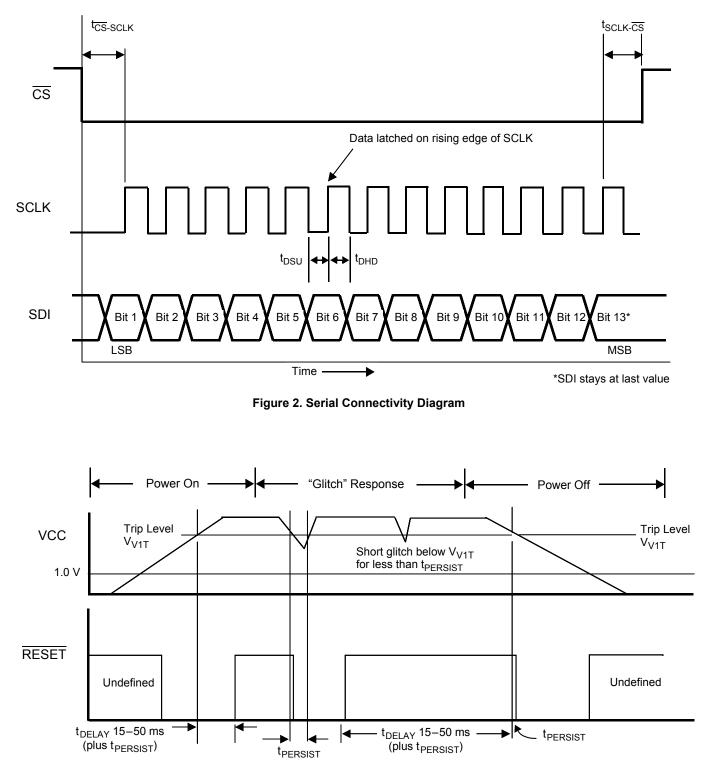

The 34920 provides a serial input port for bit depth of 13 bits of input. This port provides an interface between the 34920 and the digital controller IC. This port is write-only. The interface consists of three signal lines: chip select ( $\overline{CS}$ , active low), serial clock (SCLK), and serial data input (SDI).

The digital controller initiates a serial transfer by pulling low the chip select line ( $\overline{CS}$ ). It then generates 13 clock pulses on the SCLK terminal while presenting the serial data on the serial data input (SDI). The 34920 presents the data on SDI one setup time ( $t_{DSU}$ ) before the rising edge of SCLK. The data is held constant for the data hold time ( $t_{DHD}$ ) beyond the SCLK rising edge. The data is shifted into the 34920 on the rising edge of SCLK. The least significant bit (LSB) is the first to be shifted out of the 34920 on the rising edge of SCLK, followed by the remaining bits to the last of the 13 bits, which is the most significant bit (MSB). The  $\overline{CS}$  line is then returned to a high state. The low-to-high transition of  $\overline{CS}$  will load the data into the internal 34920 input register, where all the inputs are presented to their appropriate functions in a parallel fashion.

**Note** The minimum off-time ( $\overline{CS}$  signal equal to logic [1]) for the  $\overline{CS}$  signal needs to be at least 1.0 t<sub>DSU</sub> delay + 1.0 t<sub>DHD</sub> delay. This will provide the time for the 34920 to clear the serial input data register (transfer the serial data in parallel to internal latches that use the data) and thereby avoid a data overrun condition and loss of data. See the serial input port timing data in the Dynamic Electrical Characteristics table, <u>page 10</u>.

### Table 3. 34920 Input Specifications

| Name                         | Description                                                                                                                                                                                                                                           |

|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V1_FB                        | Voltage feedback for the V1 regulator.                                                                                                                                                                                                                |

| VCC                          | VCC power input for internal use. The 34920 accepts either 3.3 V ±10% or 5.0 V ±5% for its logic voltage.                                                                                                                                             |

| V2_FB                        | Voltage feedback for the V2 regulator.                                                                                                                                                                                                                |

| CS                           | Serial input register chip select input. Active low.                                                                                                                                                                                                  |

| SCLK                         | Serial input register clock.                                                                                                                                                                                                                          |

| SDI                          | Serial input register serial data input.                                                                                                                                                                                                              |

| DRxPWM                       | PWM input for the DC motor driver for either Driver 1 or Driver 2.                                                                                                                                                                                    |

| DRx_MODE                     | Selects mode of each motor driver. Step = 1/DC = 0.                                                                                                                                                                                                   |

| The following inputs are the | rough the Serial Input Register                                                                                                                                                                                                                       |

| V2_Enable                    | Enable bit to turn on and off the V2 regulator and the motor drivers. When low (= logic [0]), the V2 regulator and the motor drivers are turned off and the 34920 is placed in its lowest possible power state. V1 is not affected by the Enable bit. |

| DR1_CURR_I1_PHASEA           | Second of two inputs that control the current level in the step motor Phase A winding (Driver 1/Step Mode).                                                                                                                                           |

| DR1_CURR-I0_PHASEA           | First of two inputs that control the current level in the step motor Phase A winding (Driver 1/Step Mode).                                                                                                                                            |

| DR1_DIR_PH_A                 | Controls the direction of the current flow through Phase A of the step motor; i.e., logic [1] level causes conventional current flow from DR1A1 to DR1B1 (Driver 1/Step Mode).                                                                        |

| DR1_CURR_I1_PHASEB           | Second of two inputs that control the current level in the step motor Phase B winding (Driver 1/Step Mode).                                                                                                                                           |

| DR1_CURR_I0_PHASEB           | First of two inputs that control the current level in the step motor Phase B winding (Driver 1/Step Mode).                                                                                                                                            |

| DR1_DIR_PH_B                 | Controls the direction of the current flow through Phase B of the step motor. A logic [1] level causes conventional current flow from DR1A2 to DR1B2 (Driver 1/Step Mode).                                                                            |

| DR2_CURR_I1_PHASEA           | Second of two inputs that control the current level in the step motor Phase A winding (Driver 2/Step Mode).                                                                                                                                           |

| DR2_CURR_I0_PHASEA           | One of two inputs that control the current level in the step motor Phase A winding (Driver 2/Step Mode).                                                                                                                                              |

| DR2_DIR_PH_A                 | Controls the direction of the current flow through Phase A of the step motor. A logic [1] level causes conventional current flow from DR2A1 to DR2B1 (Driver 2/Step Mode).                                                                            |

| DR2_CURR_I1_PHASEB           | Second of two inputs that control the current level in the step motor Phase B winding (Driver 2/Step Mode).                                                                                                                                           |

| DR2_CURR_I0_PHASEB           | One of two inputs that control the current level in the step motor Phase B winding (Driver 2/Step Mode).                                                                                                                                              |

| DR2_DIR_PH_B                 | Controls the direction of the current flow through Phase B of the step motor. A logic [1] level causes conventional                                                                                                                                   |

current flow from DR2A2 to DR2B2 (Driver 2/Step Mode).

## Serial Input Port Bit Definitions

<u>Tables 4</u> through  $\underline{7}$  define the bit definitions as they apply to the 13 bits of input that are brought into the 34920 through the

serial input port. These signals are listed in bit order from LSB (first bit to be shifted in) to MSB (last bit to be shifted in).

### Table 4. Serial Input Port Definition for Step/Step Mode

| Name                | Bit | Reset<br>Value | Description                                                                                                                                                                |

|---------------------|-----|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V2_Enable           | 1   | 1              | Enable bit to turn on and off the V2 regulator and the motor drivers and place the 34920 in the minimum power consumption state.                                           |

| SDR2_CURR_I1_PHASEB | 2   | 1              | Second of two inputs that control the current level in the SDR2 step motor Phase B winding.                                                                                |

| SDR2_CURR_I0_PHASEB | 3   | 1              | One of two inputs that control the current level in the SDR2 step motor Phase B winding.                                                                                   |

| SDR2_DIR_PH_B       | 4   | 0              | Controls the direction of the current flow through Phase B of the SDR2 step motor. A logic [1] level causes conventional current flow from PH_B+ (source) to PH_B- (sink). |

| SDR2_CURR_I1_PHASEA | 5   | 1              | Second of two inputs that control the current level in the SDR2 step motor Phase A winding.                                                                                |

| SDR2_CURR_I0_PHASEA | 6   | 1              | One of two inputs that control the current level in the SDR2 step motor Phase A winding.                                                                                   |

| SDR2_DIR_PH_A       | 7   | 0              | Controls the direction of the current flow through Phase A of the SDR2 step motor. A logic [1] level causes conventional current flow from PH_A+ (source) to PH_A- (sink). |

| SDR1_CURR_I1_PHASEB | 8   | 1              | Second of two inputs that control the current level in the SDR1 step motor Phase B winding.                                                                                |

| SDR1_CURR_I0_PHASEB | 9   | 1              | One of two inputs that control the current level in the SDR1 step motor Phase B winding.                                                                                   |

| SDR1_DIR_PH_B       | 10  | 0              | Controls the direction of the current flow through Phase B of the SDR1 step motor. A logic [1] level causes conventional current flow from PH_B+ (source) to PH_B- (sink). |

| SDR1_CURR_I1_PHASEA | 11  | 1              | Second of two inputs that control the current level in the SDR1 step motor Phase A winding.                                                                                |

| SDR1_CURR_I0_PHASEA | 12  | 1              | One of two inputs that control the current level in the SDR1 step motor Phase A winding.                                                                                   |

| SDR1_DIR_PH_A       | 13  | 0              | Controls the direction of the current flow through Phase A of the SDR1 step motor. A logic [1] level causes conventional current flow from PH_A+ (source) to PH_A- (sink). |

| Name        | Bit | Reset<br>Value | Description                                                                                                                                                                           |  |

|-------------|-----|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| V2_Enable   | 1   | 1              | Enable bit to turn on and off the V2 regulator and the motor drivers and place the 34920 in the minimum power consumption state.                                                      |  |

| Not Used    | 2   | х              | Not used in this mode.                                                                                                                                                                |  |

| Not Used    | 3   | Х              | Not used in this mode.                                                                                                                                                                |  |

| Not Used    | 4   | Х              | Not used in this mode.                                                                                                                                                                |  |

| Not Used    | 5   | Х              | Not used in this mode.                                                                                                                                                                |  |

| Not Used    | 6   | Х              | Not used in this mode.                                                                                                                                                                |  |

| DR2_DIR_DCM | 7   | 0              | Controls the direction of the current flow through the DC motor. A logic [1] level causes conventional current flow from DR2A1 (source)/DR2A2 (source) to DR2B1 (sink)/ DR2B2 (sink). |  |

| Not Used    | 8   | Х              | Not used in this mode.                                                                                                                                                                |  |

| Not Used    | 9   | Х              | Not used in this mode.                                                                                                                                                                |  |

| Not Used    | 10  | Х              | Not used in this mode.                                                                                                                                                                |  |

| Not Used    | 11  | Х              | Not used in this mode.                                                                                                                                                                |  |

| Not Used    | 12  | Х              | Not used in this mode.                                                                                                                                                                |  |

| DR1_DIR_DCM | 13  | 0              | Controls the direction of the current flow through the DC motor. A logic [1] level causes conventional current flow from DR1A1 (source)/DR1A2 (source) to DR1B1 (sink)/DR1B2 (sink).  |  |

### Table 5. Serial Input Port Definition for DC Motor/DC Motor Mode (Note 10)

Notes

10. DR1\_MODE and DR2\_MODE terminals = logic [0] for DC motor drive for both drivers.

### Table 6. Serial Input Port Definition for DR1=Step/DR2=DC Motor Mode

| Name                | Bit | Reset<br>Value | Description                                                                                                                                                                           |  |

|---------------------|-----|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| V2_Enable           | 1   | 1              | Enable bit to turn on and off the V2 regulator and the motor drivers and place the 3492 in the minimum power consumption state.                                                       |  |

| Not Used            | 2   | Х              | Not used in this mode.                                                                                                                                                                |  |

| Not Used            | 3   | Х              | Not used in this mode.                                                                                                                                                                |  |

| Not Used            | 4   | Х              | Not used in this mode.                                                                                                                                                                |  |

| Not Used            | 5   | Х              | Not used in this mode.                                                                                                                                                                |  |

| Not Used            | 6   | Х              | Not used in this mode.                                                                                                                                                                |  |

| DR2_DIR_DCM         | 7   | 0              | Controls the direction of the current flow through the DC motor. A logic [1] level causes conventional current flow from DR2A1 (source)/DR2A2 (source) to DR2B1 (sink)/ DR2B2 (sink). |  |

| SDR1_CURR_I1_PHASEB | 8   | 1              | Second of two inputs that control the current level in the SDR1DR1 step motor Phase B winding.                                                                                        |  |

| SDR1_CURR_I0_PHASEB | 9   | 1              | One of two inputs that control the current level in the SDR1 step motor Phase B winding.                                                                                              |  |

| SDR1_DIR_PH_B       | 10  | 1              | Controls the direction of the current flow through Phase B of the SDR1 step motor. A logic [1] level causes conventional current flow from PH_B+ (source) to PH_B- (sink).            |  |

| SDR1_CURR_I1_PHASEA | 11  | 0              | Second of two inputs that control the current level in the SDR1 step motor Phase A winding.                                                                                           |  |

| SDR1_CURR_I0_PHASE  | 12  | 1              | One of two inputs that control the current level in the SDR1 step motor Phase A winding.                                                                                              |  |

| SDR1_DIR_PH_A       | 13  | 1              | Controls the direction of the current flow through Phase A of the SDR1 step motor. A logic [1] level causes conventional current flow from PH_A+ (source) to PH_A- (sink).            |  |

## Table 7. Serial Input Port Definition for DR1=DC Motor/DR2=Step Mode

| Name                | Bit | Reset<br>Value | Description                                                                                                                                                                           |  |

|---------------------|-----|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| V2_Enable           | 1   | 1              | Enable bit to turn on and off the V2 regulator and the motor drivers and place the 34920 in the minimum power consumption state.                                                      |  |

| SDR2_CURR_I1_PHASEB | 2   | 1              | Second of two inputs that control the current level in the SDR2 step motor Phase B winding.                                                                                           |  |

| SDR2_CURR_I0_PHASEB | 3   | 1              | One of two inputs that control the current level in the SDR2 step motor Phase B winding.                                                                                              |  |

| SDR2_DIR_PH_B       | 4   | 0              | Controls the direction of the current flow through Phase B of the SDR2 step motor. A logic [1] level causes conventional current flow from PH_B+ (source) to PH_B+ (sink).            |  |

| SDR2_CURR_I1_PHASEA | 5   | 1              | Second of two inputs that control the current level in the SDR2 step motor Phase A winding.                                                                                           |  |

| SDR2_CURR_I0_PHASEA | 6   | 1              | One of two inputs that control the current level in the SDR2 step motor Phase A winding.                                                                                              |  |

| SDR2_DIR_PH_A       | 7   | 0              | Controls the direction of the current flow through Phase A of the SDR2 step motor. A logic [1] level causes conventional current flow from PH_A+ (source) to PH_A- (sink).            |  |

| Not Used            | 8   | х              | Not used in this mode.                                                                                                                                                                |  |

| Not Used            | 9   | х              | Not used in this mode.                                                                                                                                                                |  |

| Not Used            | 10  | х              | Not used in this mode.                                                                                                                                                                |  |

| Not Used            | 11  | х              | Not used in this mode.                                                                                                                                                                |  |

| Not Used            | 12  | х              | Not used in this mode.                                                                                                                                                                |  |

| DR1_DIR_DCM         | 13  | 0              | Controls the direction of the current flow through the DC motor. A logic [1] level causes conventional current flow from DR1A1 (source)/DR1A2 (source) to DR1B1 (sink)/ DR1B2 (sink). |  |

### **Voltage Regulators**

The 34920 contains two switching voltage regulators (see Figure 4). Both are buck-type voltage regulators using an internal switching MOSFET. The V1 regulator provides either 3.3 V or 5.0 V at +5%/-4% tolerance. The V2 regulator's output voltage,  $V_{V2}$ , is programmable through the use of an external resistor divider network. The voltage tolerance on the  $V_{V2}$  output is ±2% of the nominal voltage set point. The switching frequency of the V1 and V2 regulators is approximately 200 kHz.

The V1 and V2 regulators are designed with a dual-mode current limit circuit. The current limit threshold is lowered during the power-on period to allow for a softer start-up, thereby reducing electrical stress in the external components.

$V_{VB+}$ , the input voltage for the switching voltage regulators, ranges from 21 V to 42 V. To minimize the ripple current on  $V_{VB+}$ , the V1 regulator and the V2 regulator switch out of phase.

A boost voltage generator ( $V_b$  generator), which acts as a single-stage charge pump, provides gate drive voltage for the switching regulators. It uses an external capacitor to store the charge.

Output voltages  $V_{V1}$  and  $V_{V2}$  are set externally with a resistor (1% tolerance) divider network. Input voltages at V1\_FB and V2\_FB should be chosen to provide a feedback voltage, for the required output regulated voltage, to equal the internal regulator reference voltages of 2.5 V ±2%.

Figure 4. Voltage Regulator Functions

#### **Voltage Regulator Output Requirements**

<u>Table 8</u> provides a listing of the output voltages and currents. Both switchmode converters operate at approximately 200 kHz  $\pm$ 25 kHz.

| Voltage Name              | Minimum Voltage  | Maximum Voltage  | Load Range                           |

|---------------------------|------------------|------------------|--------------------------------------|

| V <sub>V1</sub>           | -4.0% of Nominal | +4.0% of Nominal | 10 mA Min, 500 mA Max DC             |

| V <sub>V2</sub> (Note 11) | -2.0% of Nominal | +2.0% of Nominal | 10 mA Min, 1.3 A Max DC<br>(Note 12) |

#### **Table 8. Voltage Regulator Output Requirements**

Notes

- 11. This voltage is programmable within a range of 10 V to 15 V via external resistors. The voltage tolerance around any set point is ±2% of the nominal.

- 12. Maximum peak duration is 400 ms.

The V1 and V2 regulators provide individual internal overtemperature sensing for protection. During an overtemperature event, when the device  $T_J$  is at or above  $T_{J(SHUTDOWN)}$ , the internal thermal protection circuit disables the drive outputs by driving all outputs to the zero current state until the device temperatures have dropped below the lower thermal threshold temperature  $T_{J(ENABLE)}$ , at which time the driver is re-enabled.

The V1 and V2 voltage regulators may be shut down by applying a voltage in the range of 3.0 V to 6.0 V to the respective V1\_FB and V2\_FB terminals. This will result in the regulator output voltages to be equal to 0 V.

### **Overcurrent Protection**

Output voltages V<sub>V1</sub> and V<sub>V2</sub> are short circuit protected. The outputs respond to an overcurrent situation by limiting the internal switching duty cycle. This can be reset by removing the main supply to the chip or when the short circuit condition is removed. Refer to the respective I<sub>OC</sub> and I<sub>SC</sub> values for V1 and V2 voltage regulators on page 6 of the Static Electrical Characteristics table.

### **Power-Saving Mode of Operation**

The V2 voltage regulator can be disabled via the serial interface by setting the V2\_Enable bit (bit 1–LSB) to a value of 0. This provides a reduction in the bias current provided by the V1 supply.

### V1 Voltage Regulator

Implementation of the V1 switching voltage regulator is accomplished through the use of an internal switch MOSFET, internal MOSFET current sense resistor, external Schottky diode, external inductor, and filter capacitor. The frequency of operation of this regulator is controlled by the internal clock, which is 200 kHz ±25 kHz. The duty cycle (on-time) for this internal regulator clock is a fixed 37.5%. This regulator switches out of phase from the V2 regulator to minimize ripple current on VB+. The line regulation range is 21 V <  $V_{VB+}$  < 42 V. The load

side regulation is specified on <u>page 6</u> of the Static Electrical Characteristics table.

This converter is designed so that the current limit threshold is lowered during the power-on period to allow for a "softer" start-up, thereby reducing electrical stress in the external components. This limiting is required for their safe operation.

The voltage is set externally with a resistor (1% tolerance) divider network. The V1\_FB input voltage should be chosen, using external voltage divider resistors, so as to provide a regulator feedback voltage, for the required output regulated voltage, to equal the internal regulator reference voltage of 2.50 V  $\pm 2\%$ . The V1 regulator is ideal for providing either 3.3 V or 5.0 V with a precision of  $\pm 5\%/-4\%$ .

Output current sensing is implemented by sensing the voltage across an internal sense resistor connected between VB+ and the drain of the internal MOSFET. Current is measured on a cycle-by-cycle basis. The purpose of this current sense is to prevent damage to the 34920 and its associated external components.

### V2 Voltage Regulator

The V2 switching voltage regulator is implemented as a buck regulator with an internal switch MOSFET, internal MOSFET current sense resistor, external Schottky diode, external inductor, and filter capacitor. The frequency of operation of this regulator is controlled by the internal clock, which is 200 kHz ±25 kHz. This regulator switches out of phase from the V1 regulator to minimize ripple current on VB+.

This converter is designed so that the current limit threshold is lowered during the power-on period to allow for a "softer" start-up, thereby reducing electrical stress in the external components. This limiting is required for their safe operation.

The output voltage is variable with  $\pm 2\%$  precision, with a V<sub>VB+</sub> supply voltage range of 21 V to 42 V. The exact voltage will be set externally with a resistor (1% tolerance) divider network. The V2\_FB input voltage should be chosen, using external voltage divider resistors, so as to provide a regulator

feedback voltage, for the required output regulated voltage, to equal the internal regulator reference voltages of  $2.50 \text{ V} \pm 2\%$ .

Output current sensing is implemented by sensing the voltage across an internal sense resistor connected between VB+ and the drain of the internal MOSFET. Current is measured on a cycle-by-cycle basis. The purpose of this current sense is to prevent any damage to the 34920 and its associated external components.

**Note** There is a V2\_Enable bit in the Serial Communication Input register (bit 1). When this bit is set to logic [1], the V2 voltage regulator is enabled. When this bit = logic [0], the V2 voltage regulator is disabled. Refer to <u>Tables 3</u> through <u>7</u>, pp. 15–19, for a description of this bit. The V2\_Enable bit will also disable the motor drivers.

#### V<sub>b</sub> Generator

The boost voltage generator circuit is a charge pump circuit using two external capacitors to provide the necessary voltage to drive internal 34920 loads. This circuit is driven at a frequency of 200 kHz ±25 kHz.

The V<sub>b</sub> generator is utilized exclusively by the 34920. There is no provision for external loading. Also, there is no disable feature for the V<sub>b</sub> generator.

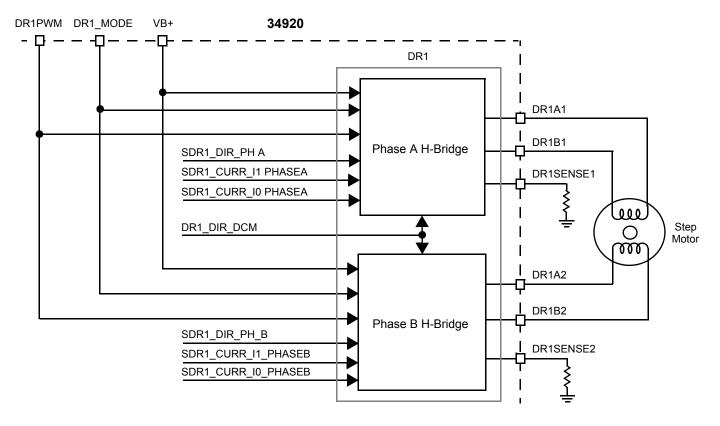

### **Motor Drive Systems**

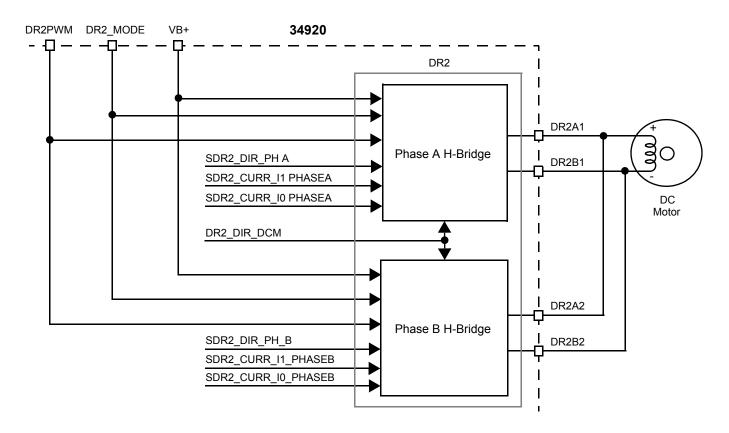

The 34920 provides two motor drivers. Both drivers are mode selectable to be either a multi-current level bi-directional driver for bipolar step motors or a bi-directional DC motor driver with PWM control. The DR1\_MODE (Mode1) and DR2\_MODE (Mode2) terminals select whether the appropriate motor driver will drive a step motor (terminal = 1) or DC motor (terminal = 0). Figures 5 and 6 depict the two motor configurations.

Figure 5. Simplified Step Application Diagram Showing 1 of 2 Step Drive Circuits

Figure 6. Simplified DC Application Diagram Showing 1 of 2 Motor Drive Circuits

#### **Bipolar Current Regulated Step Motor Drive System**

The drive circuitry is powered by the V<sub>VB+</sub> supply voltage. For example, with external current sense resistors of 0.910  $\Omega$  ±1%, the drive circuitry provides drive for a bipolar step motor at current levels of approximately 183 mA, 367 mA, and 550 mA. Current mode operation supports quarter stepping.

This drive enters the fast current decay mode when both the CURR\_I0\_PHASEX and CURR\_I1\_PHASEX inputs are set to the logic [1] level. In fast current decay mode, any residual motor winding current is forced into the  $V_{VB+}$  supply rail when going to a zero current state from a non-zero current level. This forces the motor winding current toward zero as quickly as possible.

For each of the two H-bridge drivers, controlled crossover delay, a blanking period, and internal overtemperature sensing are provided. The crossover delay is controlled to provide sufficient time for cross-conduction suppression. At no time will both the upper and lower output device on the same side of the H-bridge be allowed to conduct simultaneously. Also, following a turn-on event a blanking period is included to prevent false turn-offs owing to the initial turn-on current spike, which results from motor circuit capacitance.

This drive has internal overtemperature sensing for protection. During an overtemperature event, when the device  $T_J$  is at or above  $T_{J(SHUTDOWN)}$ , the internal thermal protection

circuit disables the drive outputs by driving all outputs to the zero current state until the device temperatures have dropped below the lower thermal threshold temperature  $T_{J(\text{ENABLE})}$ , at which time the driver is re-enabled.

**Note** During power-on the step motor driver circuit inhibits its outputs when V<sub>VB+</sub> is at 4.0 V or greater until RESET is released. Likewise, during power-down the step motor driver circuit inhibits its outputs from the point when RESET goes low until V<sub>VB+</sub> has dropped below 4.0 V.

### **DC Motor Drive System**

This drive circuitry provides bi-directional drive to a DC motor via two inputs, DCM\_PWM (an external terminal, CMOS-compatible input) and DRx\_DIR\_DCM (a bit in the serial input port; refer to <u>Tables 5</u> through <u>7</u>, pp. 17–19). This drive is powered from VB+. The DC motor control circuitry uses voltage mode control.

To drive a DC motor the 34920 outputs DR2A1 and DR2A2 must be connected together externally, then connected to the DC motor "+" lead. Likewise, the 34920 outputs DR2B1 and DR2B2 must be connected together externally, then connected to the DC motor "-" lead (see Figure 6).

This drive provides internal overtemperature sensing for protection. During an overtemperature event, when the device  $T_{\rm J}$  is at or above  $T_{\rm J(SHUTDOWN)}$ , the internal thermal protection

circuit disables the drive outputs by driving both outputs to the high state until the device temperatures have dropped below the lower thermal threshold temperature  $T_{J(ENABLE)}$ , at which time the drive is re-enabled.

The crossover delay must be controlled to provide sufficient time for cross-condition suppression. At no time can both the upper and lower output devices on the same side of the H-bridge be allowed to conduct simultaneously. Also, following a turn-on event a blanking period is included to prevent false turn-offs owing to the initial turn-on current spike, which results from motor circuit capacitance.

**Note** During power-on the DC Motor Driver circuit inhibits its outputs when V<sub>VB+</sub> is at 4.0 V or greater until RESET is released. Likewise, during power-down of the machine the DC Motor Driver circuit inhibits its outputs from the point when RESET goes low until V<sub>VB+</sub> has dropped below 4.0 V.

### **RESET** Functionality

The 34920 provides an output, RESET, that drives an external reset signal to the system microprocessor and/or the system digital logic IC. This signal is an active low logic level signal that is derived by monitoring the level of the V<sub>CC</sub> terminal. This output is the equivalent of an open drain- (or open collector-) type output, with an internal 2.5 k $\Omega$  pull-up to V<sub>CC</sub>. This output terminal can be driven by other external sources and therefore the state of RESET must be monitored by the 34920.

**Note** When RESET is asserted either internally or from an external source, all 34920 motor drive outputs will be in their inactive states, and the serial input port will be loaded with the "Reset Value" (refer to <u>Tables 4</u> through <u>7</u>). The V2 voltage regulator will be enabled.

During power-up this output asserts a logic low level, and it monitors the V1 regulator output voltage and detects the point that it reaches  $V_{V1T+}$ . The output will then remain low for a delay of 15 ms to 50 ms before releasing to a high state. A second case is if  $V_{V1\_FB}$  is at or above  $V_{V1T+}$  for a period longer than the delay period of  $t_{DELAY}$  and  $V_{VB+}$  is still less than  $V_{VB+T-}$ . In this situation RESET will remain low until  $V_{VB+}$  is greater than  $V_{VB+T-}$ , at which point RESET will be released immediately and there will be no delay period. If  $V_{VB+}$  passes through  $V_{VB+T+}$  during the  $t_{DELAY}$  period, RESET will remain low until the end of the  $t_{DELAY}$  period, which started at the time  $V_{V1\_FB}$  passed through the  $V_{V1T+}$  level.

During power-down this output immediately asserts a logic low at the point when V<sub>V1\_FB</sub> drops down to the trip point of V<sub>V1T-</sub>. Also, if V<sub>VB+</sub> drops below V<sub>VB+T-</sub> and V<sub>V1\_FB</sub> is still at or above V<sub>V1T-</sub>, RESET will be pulled low.

#### **RESET** Behavior

The following conditions describe the behavior of the RESET circuit.

**A Note on Terminology** Assertion of RESET is defined as the RESET terminal outputting a logic low voltage, and deassertion is when the terminal is pulled up to the  $V_{CC}$  voltage.

On the power-up condition, RESET behaves as follows:

If 1.0 V < V<sub>V1\_FB</sub> < V<sub>V1T+</sub> or V<sub>VB+</sub> < V<sub>VB+T+</sub>, RESET will be asserted.

Important If  $V_{V1\_FB} < 1.0 \text{ V}$ , RESET is undefined.

- If  $\overline{\text{RESET}}$  is asserted owing to  $V_{V1\_FB} < V_{V1T\_}$ , then when  $V_{V1\_FB}$  rises monotonically from below  $V_{V1T\_}$  to above  $V_{V1T+}$ ,  $\overline{\text{RESET}}$  will de-assert after a duration of  $t_{DELAY}$ .

- If  $\overline{\text{RESET}}$  is asserted owing to  $V_{VB+} < V_{VB+T+}$  and  $V_{V1\_FB} \geq V_{V1T+}$ , then when  $V_{VB+}$  rises to the  $V_{VB+T+}$  level  $\overline{\text{RESET}}$  will de-assert with no delay. The only case where a delay would be seen is if the time period from where  $V_{V1\_FB}$  rises to the  $V_{V1T+}$  level to the point where  $V_{VB+}$  rises to the  $V_{VB+T+}$  level is less than the  $t_{DELAY}$  period. Then the delay in de-asserting  $\overline{\text{RESET}}$  would be the remaining  $t_{DELAY}$  time, thereby maintaining the full  $t_{DELAY}$  period, between the time when  $V_{V1\_FB}$  reaches  $V_{V1T+}$  and the de-assertion of  $\overline{\text{RESET}}$ , that is required for a reliable system reset.

On the power-down condition, RESET behaves as follows:

- If  $\overline{\text{RESET}}$  is not asserted, and the V<sub>V1\_FB</sub> voltage monotonically decreases to a value below the negativegoing threshold of V<sub>V1T</sub> and remains below V<sub>V1T</sub> for longer than t<sub>PERSIST</sub> (10 µs to 30 µs),  $\overline{\text{RESET}}$  will be asserted.  $\overline{\text{RESET}}$  will remain asserted while 1.0 V < V<sub>V1\_FB</sub> < V<sub>V1T+</sub>. If V<sub>V1\_FB</sub> falls below 1.0 V, the  $\overline{\text{RESET}}$ signal is undefined.

- RESET will also be asserted when V<sub>VB+</sub> decreases below the V<sub>VB+T+</sub> level. This will occur even if the V<sub>V1\_FB</sub> level is still above V<sub>V1T-</sub>.

On the V<sub>V1 FB</sub> glitch condition, RESET behaves as follows:

• If the V<sub>V1\_FB</sub> supply falls below V<sub>V1T</sub> and remains there for less than t<sub>PERSIST</sub> (10  $\mu$ s to 30  $\mu$ s), RESET will not be asserted. However, if the condition lasts longer than t<sub>PERSIST</sub>, RESET will be asserted for a duration of t<sub>DELAY</sub>.

### **Environmental Specifications**

#### **Ambient Temperature and Relative Humidity**

<u>Table 9</u> lists the temperature and relative humidity for operating and storage conditions for the 34920.

| Table 9. Ambient Temperature and Humidity | Table 9 | 9. Ambient | Temperature | and Humidity |

|-------------------------------------------|---------|------------|-------------|--------------|