Product data sheet

## MC33771C Battery cell controller IC

Rev. 7.0 — 16 July 2024

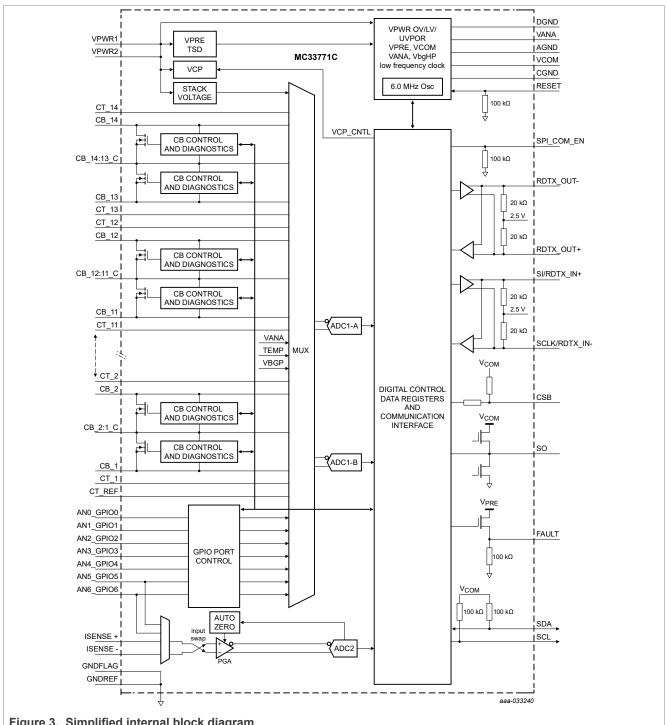

## 1 General description

The MC33771C is a SMARTMOS lithium-ion battery cell controller IC designed for automotive applications, such as hybrid electric (HEV) and electric vehicles (EV) along with industrial applications, such as energy storage systems (ESS) and uninterruptible power supply (UPS) systems.

The device performs ADC conversions of the differential cell voltages and current, as well as battery coulomb counting and battery temperature measurements. The information is transmitted to MCU using one of the microcontroller interfaces (Serial Peripheral Interface (SPI) or Transformer physical layer (TPL)) of the IC.

### 2 Features

- 9.6 V  $\leq$  V<sub>PWR</sub>  $\leq$  63 V operation, 75 V transient

- 7 to 14 cells management

- Isolated 2.0 Mbps differential communication or 4.0 Mbps SPI

- · Addressable on initialization

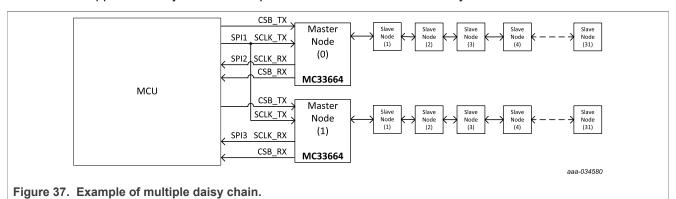

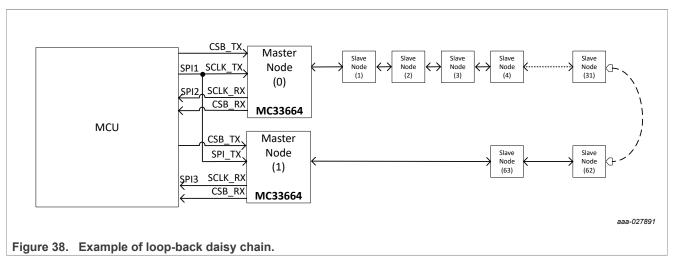

- · Bi-directional transceiver to support up to 63 nodes in daisy chain

- 0.8 mV maximum total voltage measurement error

- · Synchronized cell voltage/current measurement with coulomb count

- · Averaging of cell voltage measurements

- Total stack voltage measurement

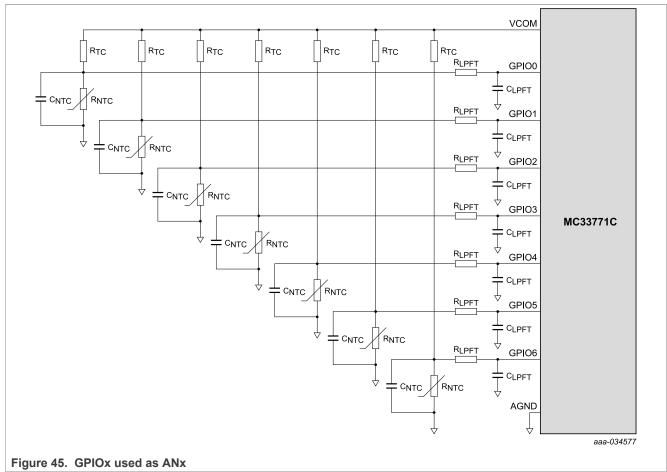

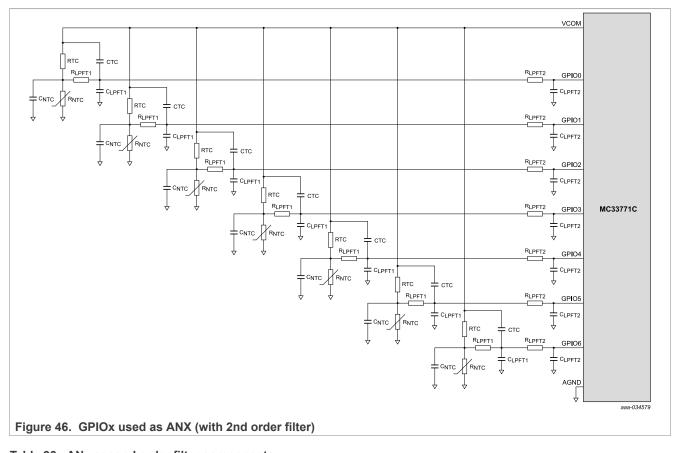

- Seven GPIO/temperature sensor inputs

- 5.0 V at 5.0 mA reference supply output

- · Automatic over/undervoltage and temperature detection routable to fault pin

- · Integrated sleep mode over/undervoltage and temperature monitoring

- · Onboard 300 mA passive cell balancing with diagnostics

- · Hot plug capable

- · Detection of internal and external faults, as open lines, shorts, and leakages

- Designed to support ISO 26262, up to ASIL D safety system.

- Qualified in compliance with AECQ-100

Battery cell controller IC

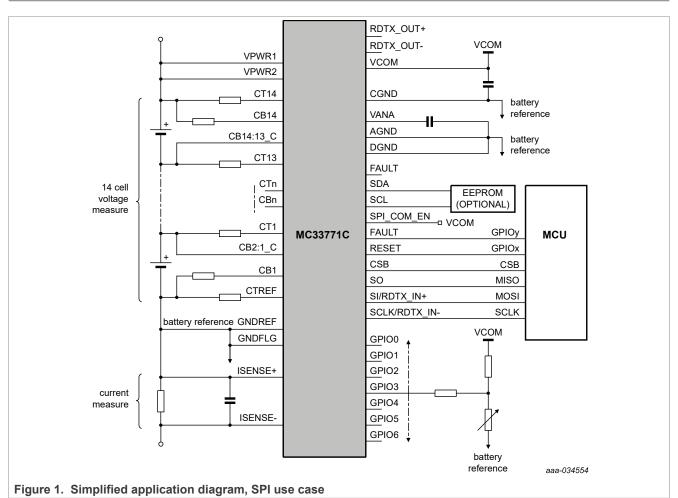

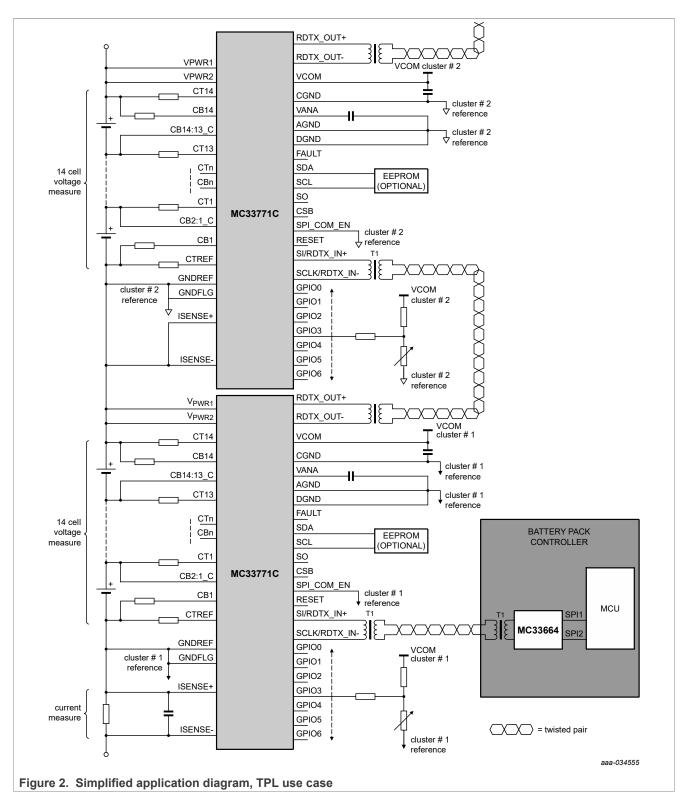

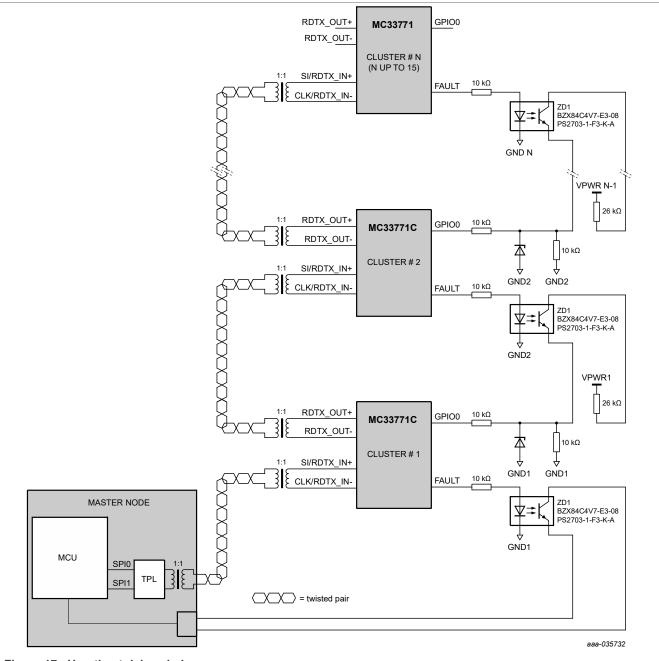

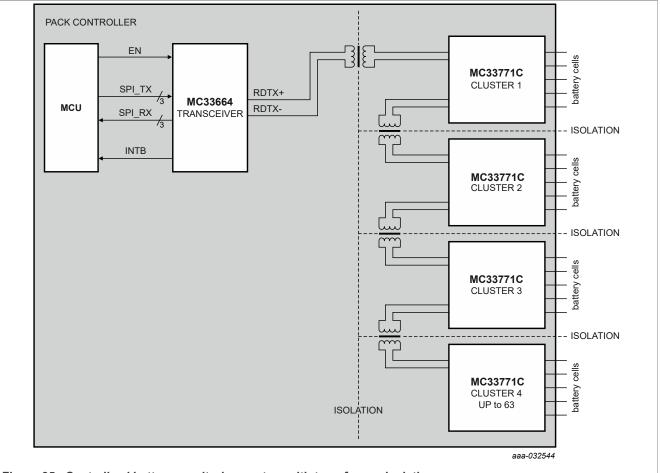

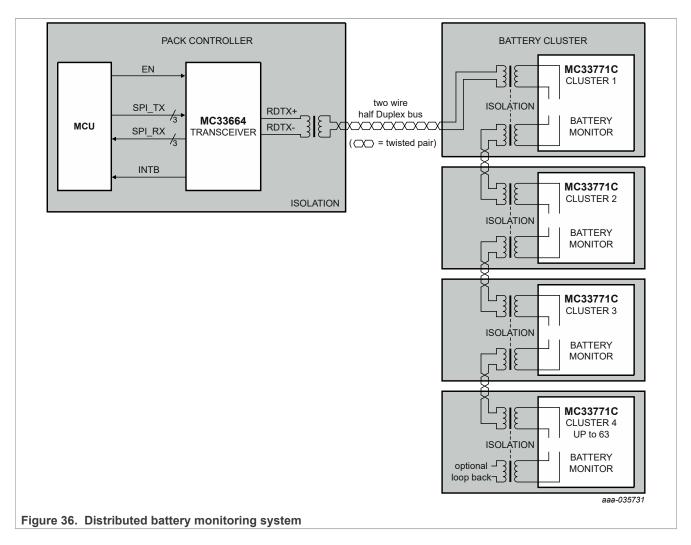

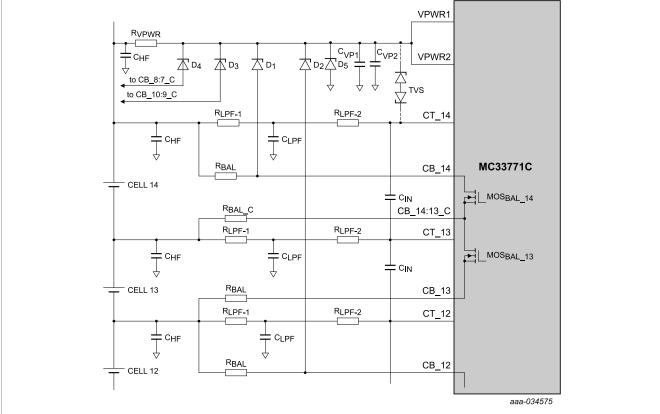

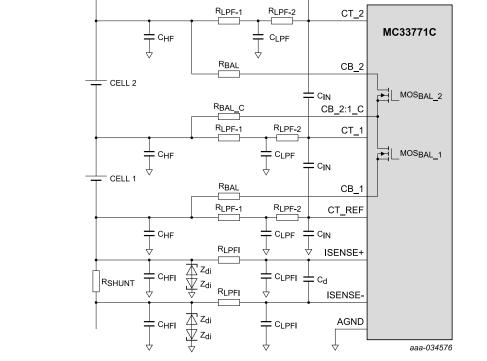

## 3 Simplified application diagram

Battery cell controller IC

## 4 Applications

• Automotive: 48 V and high-voltage battery packs

MC33771C Product data sheet

- E-bikes, e-scooters

- Energy storage systems

- Uninterruptible power supply (UPS)

## **5** Ordering information

### 5.1 Part numbers definition

## MC33771C T/y z AE/R2

#### Table 1. Part number breakdown

| Code | Option | Description                                     |

|------|--------|-------------------------------------------------|

|      | Т      | TPL communication type                          |

| N N  | Р      | y = P (Premium with current measurement option) |

| У    | А      | y = A (Advanced)                                |

| 7    | 1      | z = 1 (7 to 14 channels)                        |

| Ζ.   | 2      | z = 2 (7 to 8 channels)                         |

|      | AE     | Package suffix                                  |

|      | R2     | Tape and reel indicator                         |

### 5.2 Part numbers list

This section describes the part numbers available to be purchased along with their differences. Valid orderable part numbers are provided on the web. To determine the orderable part numbers for this device, go to <u>http://www.nxp.com</u>.

Table 2. Advanced orderable part tableTemperature range is -40 to 105 °CPackage type is 64-pin LQFP-EP

| Orderable part       | Number of channels | OV/UV |     | Current channel or<br>coulomb count |

|----------------------|--------------------|-------|-----|-------------------------------------|

| TPL differential com | nmunication protoc | ol    |     |                                     |

| MC33771CTA1AE        | 7 to 14            | Yes   | Yes | No                                  |

| MC33771CTA2AE        | 7 to 8             | Yes   | Yes | No                                  |

Table 3. Premium orderable part tableTemperature range is -40 to 105 °CPackage type is 64-pin LQFP-EP

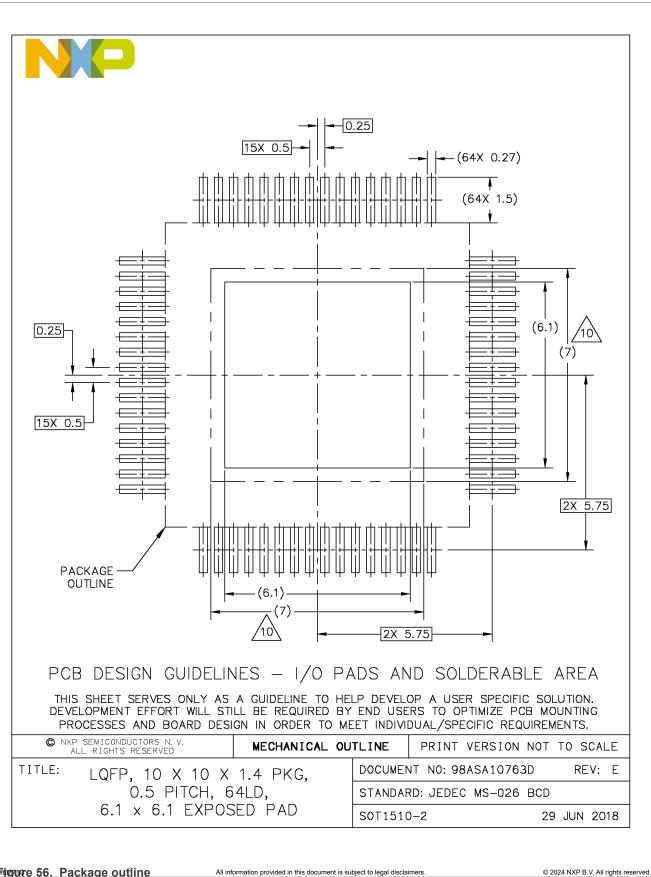

| Orderable part                                                    | Number of<br>channels                                                   | OV/UV | Precision GPIO as temperature channels and OT/UT | Current channel or<br>coulomb count |  |  |

|-------------------------------------------------------------------|-------------------------------------------------------------------------|-------|--------------------------------------------------|-------------------------------------|--|--|

| TPL differential com                                              | IPL differential communication protocol with current measurement option |       |                                                  |                                     |  |  |

| MC33771CTP1AE         7 to 14         Yes         Yes         Yes |                                                                         |       |                                                  |                                     |  |  |

| MC33771CTP2AE                                                     | 7 to 8                                                                  | Yes   | Yes                                              | Yes                                 |  |  |

Battery cell controller IC

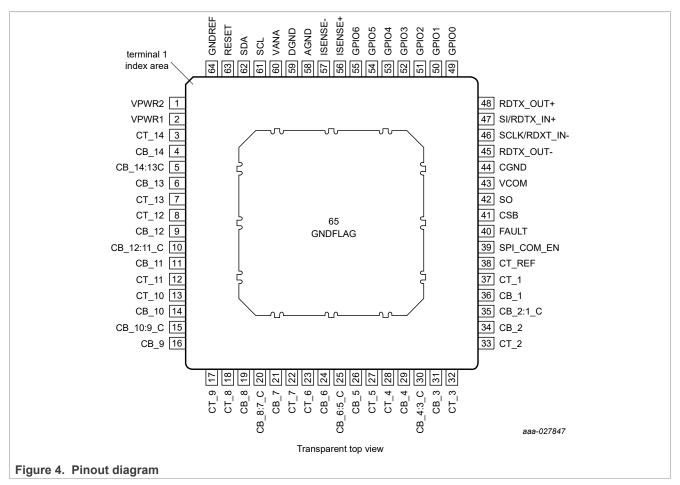

## 7 Pinning information

### 7.1 Pinout diagram

### 7.2 Pin definitions

| Table 4. Pin d | definitions |          |                                                                           |

|----------------|-------------|----------|---------------------------------------------------------------------------|

| Number         | Name        | Function | Definition                                                                |

| 1              | VPWR2       | Input    | Power input to the MC33771C                                               |

| 2              | VPWR1       | Input    | Power input to the MC33771C                                               |

| 3              | CT_14       | Input    | Cell pin 14 input. Terminate to LPF resistor.                             |

| 4              | CB_14       | Output   | Cell balance driver. Terminate to cell 14 cell balance load resistor.     |

| 5              | CB_14:13_C  | Output   | Cell balance 14:13 common. Terminate to CB_14:13_C balance load resistor. |

| 6              | CB_13       | Output   | Cell balance driver. Terminate to cell 13 cell balance load resistor.     |

| 7              | CT_13       | Input    | Cell pin 13 input. Terminate to LPF resistor.                             |

| 8              | CT_12       | Input    | Cell pin 12 input. Terminate to LPF resistor.                             |

MC33771C Product data sheet

Battery cell controller IC

| Number | Name       | Function | Definition                                                                |

|--------|------------|----------|---------------------------------------------------------------------------|

| 9      | CB_12      | Output   | Cell balance driver. Terminate to cell 12 cell balance load resistor.     |

| 10     | CB_12:11_C | Output   | Cell balance 12:11 common. Terminate to CB_12:11_C balance load resistor. |

| 11     | CB_11      | Output   | Cell balance driver. Terminate to cell 11 cell balance load resistor.     |

| 12     | CT_11      | Input    | Cell pin 11 input. Terminate to LPF resistor.                             |

| 13     | CT_10      | Input    | Cell pin 10 input. Terminate to LPF resistor.                             |

| 14     | CB_10      | Output   | Cell balance driver. Terminate to cell 10 cell balance load resistor.     |

| 15     | CB_10:9_C  | Output   | Cell balance 10:9 common. Terminate to CB_10:9_C balance load resistor.   |

| 16     | CB_9       | Output   | Cell balance driver. Terminate to cell 9 cell balance load resistor.      |

| 17     | CT_9       | Input    | Cell pin 9 input. Terminate to LPF resistor.                              |

| 18     | CT_8       | Input    | Cell pin 8 input. Terminate to LPF resistor.                              |

| 19     | CB_8       | Output   | Cell balance driver. Terminate to cell 8 cell balance load resistor.      |

| 20     | CB_8:7_C   | Output   | Cell balance 8:7 common. Terminate to CB_8:7_C balance load resistor.     |

| 21     | CB_7       | Output   | Cell balance driver. Terminate to cell 7 cell balance load resistor.      |

| 22     | CT_7       | Input    | Cell pin 7 input. Terminate to LPF resistor.                              |

| 23     | CT_6       | Input    | Cell pin 6 input. Terminate to LPF resistor.                              |

| 24     | CB_6       | Output   | Cell balance driver. Terminate to cell 6 cell balance load resistor.      |

| 25     | CB_6:5_C   | Output   | Cell balance 6:5 common. Terminate to CB_6:5_C balance load resistor.     |

| 26     | CB_5       | Output   | Cell balance driver. Terminate to cell 5 cell balance load resistor.      |

| 27     | CT_5       | Input    | Cell pin 5 input. Terminate to LPF resistor.                              |

| 28     | CT_4       | Input    | Cell pin 4 input. Terminate to LPF resistor.                              |

| 29     | CB_4       | Output   | Cell balance driver. Terminate to cell 4 cell balance load resistor.      |

| 30     | CB_4:3_C   | Output   | Cell balance 4:3 common. Terminate to CB_4:3_C balance load resistor.     |

| 31     | CB_3       | Output   | Cell balance driver. Terminate to cell 3 cell balance load resistor.      |

| 32     | CT_3       | Input    | Cell pin 3 input. Terminate to LPF resistor.                              |

| 33     | CT_2       | Input    | Cell pin 2 input. Terminate to LPF resistor.                              |

| 34     | CB_2       | Output   | Cell balance driver. Terminate to cell 2 cell balance load resistor.      |

Table 4. Pin definitions...continued

Battery cell controller IC

| Number | Name          | Function | Definition                                                                                             |  |

|--------|---------------|----------|--------------------------------------------------------------------------------------------------------|--|

| 35     | CB_2:1_C      | Output   | Cell Balance 2:1 common. Terminate to CB_2:1_C balance load resistor.                                  |  |

| 36     | CB_1          | Output   | Cell balance driver. Terminate to cell 1 cell balance load resistor.                                   |  |

| 37     | CT_1          | Input    | Cell pin 1 input. Terminate to LPF resistor.                                                           |  |

| 38     | CT_REF        | Input    | Cell pin REF input. Terminate to LPF resistor.                                                         |  |

| 39     | SPI_COM_EN    | Input    | SPI communication enable. Pin must be high for the SPI to be active.                                   |  |

| 40     | FAULT         | Output   | Fault output dependent on user defined internal or external faults. If not used, it must be left open. |  |

| 41     | CSB           | Input    | SPI chip select                                                                                        |  |

| 42     | SO            | Output   | SPI serial output                                                                                      |  |

| 43     | VCOM          | Output   | Communication regulator output                                                                         |  |

| 44     | CGND          | Ground   | Communication decoupling ground. Terminate to GNDREF.                                                  |  |

| 45     | RDTX_OUT-     | I/O      | Receive/transmit output negative                                                                       |  |

| 46     | SCLK/RDTX_IN- | I/O      | SPI clock or receive/transmit input negative                                                           |  |

| 47     | SI/RDTX_IN+   | I/O      | SPI serial input or receive/transmit input positive                                                    |  |

| 48     | RDTX_OUT+     | I/O      | Receive/transmit output positive                                                                       |  |

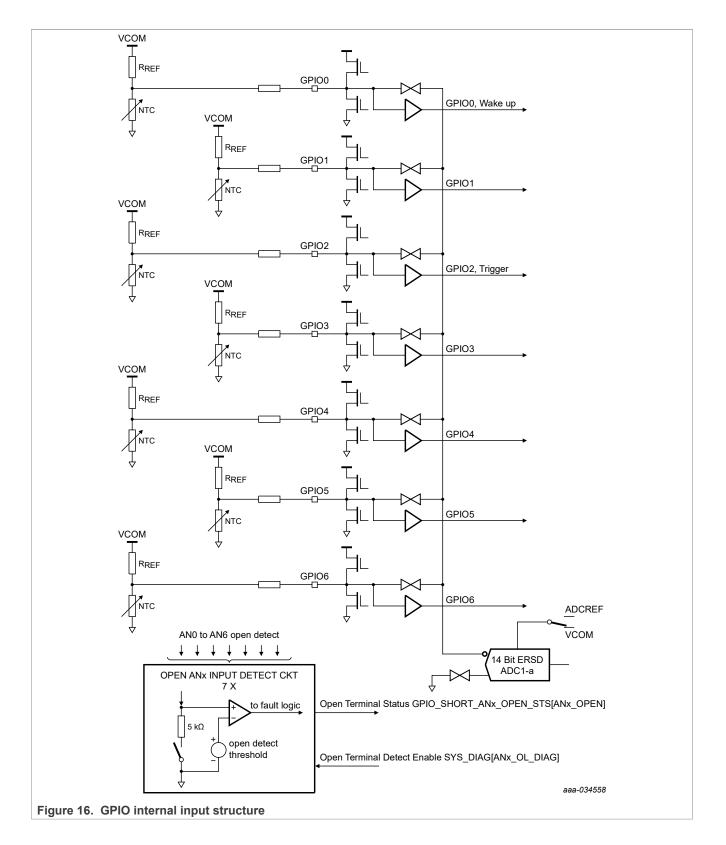

| 49     | GPIO0         | I/O      | General purpose analog input or GPIO or wake-up or fault daisy chain                                   |  |

| 50     | GPIO1         | I/O      | General purpose analog input or GPIO                                                                   |  |

| 51     | GPIO2         | I/O      | General purpose analog input or GPIO or conversion trigger                                             |  |

| 52     | GPIO3         | I/O      | General purpose analog input or GPIO                                                                   |  |

| 53     | GPIO4         | I/O      | General purpose analog input or GPIO                                                                   |  |

| 54     | GPIO5         | I/O      | General purpose analog input or GPIO                                                                   |  |

| 55     | GPIO6         | I/O      | General purpose analog input or GPIO                                                                   |  |

| 56     | ISENSE+       | Input    | Current measurement input+                                                                             |  |

| 57     | ISENSE-       | Input    | Current measurement input-                                                                             |  |

| 58     | AGND          | Ground   | Analog ground, terminate to GNDREF                                                                     |  |

| 59     | DGND          | Ground   | Digital ground, terminate to GNDREF                                                                    |  |

| 60     | VANA          | Output   | Precision ADC analog supply                                                                            |  |

| 61     | SCL           | I/O      | l <sup>2</sup> C clock                                                                                 |  |

| 62     | SDA           | I/O      | l <sup>2</sup> C data                                                                                  |  |

| 63     | RESET         | Input    | RESET is an active high input. RESET has an internal pull down. If not used, it can be tied to GND.    |  |

| 64     | GNDREF        | Ground   | Ground reference for device. Terminate to reference of battery cluster.                                |  |

Table 4. Pin definitions...continued

| Number | Name    | Function | Definition                                                     |

|--------|---------|----------|----------------------------------------------------------------|

| 65     | GNDFLAG |          | Device flag. Terminate to lowest potential of battery cluster. |

#### Table 4. Pin definitions...continued

## 8 General product characteristics

### 8.1 Ratings and operating requirements relationship

The operating voltage range pertains to the VPWR pins referenced to the AGND pins.

Table 5. Ratings vs. operating requirements

| Fatal range                         | На                                                                                                    | ndling range – no permanent fail                            | ure                                                                                                                                                                    | Fatal range                                               |

|-------------------------------------|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|

| Permanent<br>failure might<br>occur | Lower limited operating range<br>• No permanent failure,<br>but IC functionality is not<br>guaranteed | Normal operating range <ul> <li>100 % functional</li> </ul> | <ul> <li>Upper limited operating range</li> <li>IC parameters might be out of specification</li> <li>Detection of V<sub>PWR</sub> overvoltage is functional</li> </ul> | <ul> <li>Permanent<br/>failure might<br/>occur</li> </ul> |

| V <sub>PWR</sub> < -0.3 V           | 7.6 V ≤ $V_{PWR}$ < 9.6 V<br><b>Reset range:</b><br>-0.3 V ≤ $V_{PWR}$ < 7.6 V                        | 9.6 V ≤ V <sub>PWR</sub> ≤ 63 V                             | 63 V < V <sub>PWR</sub> ≤ 75 V                                                                                                                                         | 75 V < V <sub>PWR</sub>                                   |

In both upper and lower limited operating range, no information can be provided about IC performance. Only the detection of  $V_{PWR}$  overvoltage is guaranteed in the upper limited operating range.

Performance in normal operating range is guaranteed only if there is a minimum of seven battery cells in the stack.

### 8.2 Maximum ratings

Table 6. Maximum ratings

All voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Symbol                                                   | Description (rating)                                    | Min  | Max        | Unit |

|----------------------------------------------------------|---------------------------------------------------------|------|------------|------|

| Electrical ratings                                       |                                                         |      |            |      |

| VPWR1, VPWR2                                             | Supply input voltage                                    | -0.3 | 75         | V    |

| CT14                                                     | Cell terminal voltage                                   | -0.3 | 75         | V    |

| VPWR to CT14                                             | Voltage across VPWR1,2 pins pair and CT14 pin           | -10  | 10.5       | V    |

| CT <sub>N</sub> to CT <sub>N-1</sub>                     | Cell terminal differential voltage [1]                  | -0.3 | 6.0        | V    |

| CT <sub>REF</sub> to GND                                 | Cell terminal reference to ground                       | _    | 5          | V    |

| CT <sub>N</sub> to GND                                   | Cell terminal voltage to ground (N=1 to 4 or N=6 to 14) | _    | (N+1) * 5  | V    |

|                                                          | Cell terminal voltage to ground (N=5)                   | —    | 27.5       | V    |

| CT <sub>N(CURRENT)</sub>                                 | Cell terminal input current                             | —    | ±500       | μA   |

| $CB_N$ to $CB_{N:N-1_C}$<br>$CB_{N:N-1_C}$ to $CB_{N-1}$ | Cell balance differential voltage                       | -    | 10         | V    |

| CB <sub>2n</sub> to GND                                  | Cell balance voltage to GND (n=1 to 7)                  | -    | (2n+1) . 5 | V    |

| CB <sub>2n+1</sub> to GND                                | Cell balance voltage to GND (n=0 to 6)                  | _    | (2n+1) . 5 | V    |

Battery cell controller IC

Table 6. Maximum ratings...continued

All voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Symbol                         | Description (rating)                                                                                                                                                                                                                                                                                                                                                                                    | Min   | Max                                  | Unit |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------------------------------------|------|

| CB <sub>2n:2n-1_C</sub> to GND | Cell balance voltage to GND (n=1 to 6)                                                                                                                                                                                                                                                                                                                                                                  | —     | 2n . 5                               | V    |

| CB <sub>N:N-1_C</sub> to CTn-1 | Cell balance input to cell terminal input                                                                                                                                                                                                                                                                                                                                                               | -10   | 10                                   | V    |

| VISENSE                        | ISENSE+ and ISENSE– pin voltage                                                                                                                                                                                                                                                                                                                                                                         | -0.3  | 2.5                                  | V    |

| VCOM                           | Maximum voltage may be applied to VCOM pin from external source                                                                                                                                                                                                                                                                                                                                         | -     | 5.8                                  | V    |

| VANA                           | Maximum voltage may be applied to VANA pin                                                                                                                                                                                                                                                                                                                                                              | —     | 3.1                                  | V    |

| V <sub>GPIO0</sub>             | GPIO0 pin voltage                                                                                                                                                                                                                                                                                                                                                                                       | -0.3  | 6.5                                  | V    |

| V <sub>GPIOx</sub>             | GPIOx pins (x = 1 to 6) voltage                                                                                                                                                                                                                                                                                                                                                                         | -0.3  | VCOM +<br>0.5                        | V    |

| V <sub>DIG</sub>               | Voltage I <sup>2</sup> C pins (SDA, SCL)                                                                                                                                                                                                                                                                                                                                                                | -0.3  | VCOM +<br>0.5                        | V    |

| V <sub>RESET</sub>             | RESET pin                                                                                                                                                                                                                                                                                                                                                                                               | -0.3  | 6.5                                  | V    |

| V <sub>CSB</sub>               | CSB pin                                                                                                                                                                                                                                                                                                                                                                                                 | -0.3  | 6.5                                  | V    |

| V <sub>SPI_COMM_EN</sub>       | SPI_COMM_EN                                                                                                                                                                                                                                                                                                                                                                                             | -0.3  | 6.5                                  | V    |

| V <sub>SO</sub>                | SO pin                                                                                                                                                                                                                                                                                                                                                                                                  | -0.3  | VCOM +<br>0.5                        | V    |

| V <sub>GPIO5,6</sub>           | Maximum voltage for GPIO5 and GPIO6 pins used as current input                                                                                                                                                                                                                                                                                                                                          | -0.3  | 2.5                                  | V    |

| FAULT                          | Maximum applied voltage to pin                                                                                                                                                                                                                                                                                                                                                                          | -0.3  | 7.0                                  | V    |

| I <sub>pin_unpowered</sub>     | Input current in a pin when the device is unpowered                                                                                                                                                                                                                                                                                                                                                     | -2    | 2                                    | mA   |

| V <sub>COMM</sub>              | Maximum voltage to pins RDTX_OUT+, RDTX_OUT–,<br>SI/RDTX_IN+, SCLK/RDTX_IN-                                                                                                                                                                                                                                                                                                                             | -10.0 | 10.0                                 | V    |

| V <sub>ESD1</sub>              | ESD voltage<br>Human body model (HBM)<br>Charge device model (CDM)<br>Charge device model corner pins (CDM)                                                                                                                                                                                                                                                                                             |       | ±2000<br>±500 <sup>[2]</sup><br>±750 | V    |

| V <sub>ESD2</sub>              | ESD voltage (VPWR1, VPWR2, CTx, CBx, GPIOx, ISENSE+,<br>ISENSE-, RDTX_OUT+, RDTX_OUT-, SI/RDTX_IN+, SCLK/<br>RDTX_IN-) versus all ground pins<br>Human body model (HBM)                                                                                                                                                                                                                                 | _     | ±4000                                | V    |

| V <sub>ESD3</sub>              | <ul> <li>ESD voltage (CTREF, CTx, CBx, GPIOx, ISENSE+, ISENSE-,<br/>RDTX_OUT+, RDTX_OUT-, SI/RDTX_IN+, SCLK/ RDTX_IN-)</li> <li>IEC 61000-4-2, Unpowered (Gun configuration: 330Ω / 150pF)</li> <li>HMM, Unpowered (Gun configuration: 330Ω / 150pF)</li> <li>ISO 10605:2009, Unpowered (Gun configuration: 2 kΩ / 150pF)</li> <li>ISO 10605:2009, Powered (Gun configuration: 2 kΩ / 150pF)</li> </ul> |       | ±8000<br>±8000<br>±8000<br>±8000     | V    |

[1] Adjacent CT pins may experience an overvoltage that exceeds their maximum rating during OV/UV functional verification test or during open line diagnostic test. Nevertheless, the IC is completely tolerant to this special situation. For CT\_REF pin applicable limit is ±450 V.

[2]

ESD testing is performed in accordance with the human body model (HBM) (C<sub>ZAP</sub> = 100 pF, R<sub>ZAP</sub> = 1500 Ω), and the charge device model (CDM) (C<sub>ZAP</sub> = [3] 4.0 pF).

These voltage values can be sustained only if ESD caps are used as described in Section 13.2 [4]

### 8.3 Thermal characteristics

#### Table 7. Thermal ratings

All voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Symbol                 | Description (rating)                                                           |            | Min | Max  | Unit |

|------------------------|--------------------------------------------------------------------------------|------------|-----|------|------|

| Thermal rati           | ngs                                                                            |            |     |      |      |

|                        | Operating temperature                                                          |            |     |      | °C   |

| T <sub>A</sub>         | Ambient                                                                        |            | -40 | +105 |      |

| TJ                     | Junction <sup>[1]</sup>                                                        |            | -40 | +150 |      |

| T <sub>STG</sub>       | Storage temperature                                                            |            | -55 | +150 | °C   |

| T <sub>PPRT</sub>      | Peak package reflow temperature                                                | [2]<br>[3] | _   | 260  | °C   |

| Thermal resi           | istance and package dissipation ratings                                        |            |     |      |      |

| R <sub>OJB</sub>       | Junction-to-board (bottom exposed pad soldered to board) 64<br>LQFP EP         | [4]        |     | 10   | °C/W |

| R <sub>ØJA</sub>       | Junction-to-ambient, natural convection, single-layer board (1s) 64<br>LQFP EP | [5]<br>[6] |     | 59   | °C/W |

| R <sub>OJA</sub>       | Junction-to-ambient, natural convection, four-layer board (2s2p) 64<br>LQFP EP | [5]<br>[6] |     | 27   | °C/W |

| R <sub>ØJCTOP</sub>    | Junction-to-case top (exposed pad) 64 LQFP EP                                  | [7]        |     | 14   | °C/W |

| R <sub>ØJCBOTTOM</sub> | Junction-to-case bottom (exposed pad) 64 LQFP EP                               | [8]        |     | 0.97 | °C/W |

| Ψ <sub>JT</sub>        | Junction to package top, natural convection                                    | [9]        | _   | 3    | °C/W |

The user must ensure that the average maximum operating junction temperature (TJ) is not exceeded. [1]

[2] Pin soldering temperature limit is for 10 seconds maximum duration. Not designed for immersion soldering. Exceeding these limits may cause a malfunction or permanent damage to the device.

NXP's Package Reflow capability meets Pb-free requirements for JEDEC standard J-STD-020C. For Peak Package Reflow Temperature and Moisture [3] Sensitivity Levels (MSL), go to www.nxp.com, search by part number (remove prefixes/suffixes) and enter the core ID to view all orderable parts and review parametrics.

[4] Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient [5] temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

[6] Per JEDEC JESD51-6 with the board (JESD51-7) horizontal.

Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1), with the cold plate [7] temperature used for the case temperature.

Thermal resistance between the die and the solder pad on the bottom of the package based on simulation without any interface resistance [8]

[9] Thermal characterization parameter indicating the temperature difference between the package top and the junction temperature per JEDEC JESD51-2.

### 8.4 Electrical characteristics

#### Table 8. Static and dynamic electrical characteristics

Characteristics noted under conditions 9.6 V  $\leq$  V<sub>PWR</sub>  $\leq$  63 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  105 °C, GND = 0 V, unless otherwise stated. Typical values refer to  $V_{PWR}$  = 56 V,  $T_A$  = 25 °C, unless otherwise noted.

| Symbol               | Parameter                                                                                                               | Min | Тур | Max      | Unit |  |  |

|----------------------|-------------------------------------------------------------------------------------------------------------------------|-----|-----|----------|------|--|--|

| Power management     |                                                                                                                         |     |     |          |      |  |  |

| V <sub>PWR(FO)</sub> | Supply voltage<br>Full parameter specification                                                                          | 9.6 | _   | 63       | V    |  |  |

| I <sub>VPWR</sub>    | Supply current (base value)<br>Normal mode, cell balance OFF, ADC inactive, SPI<br>communication inactive, IVCOM = 0 mA | _   | 5.4 | 8.5<br>— | mA   |  |  |

MC33771C **Product data sheet**

Battery cell controller IC

Table 8. Static and dynamic electrical characteristics...continued

Characteristics noted under conditions 9.6 V  $\leq V_{PWR} \leq 63$  V, -40 °C  $\leq T_A \leq 105$  °C, GND = 0 V, unless otherwise stated. Typical values refer to  $V_{PWR} = 56$  V,  $T_A = 25$  °C, unless otherwise noted.

| Ivpwr(tpl_tx)<br>Ivpwr(cbon)<br>Ivpwr(adc) | Normal mode, cell balance OFF, ADC inactive, TPL<br>communication inactive, IVCOM = 0 mA<br>Supply current adder when TPL communication active                                                                                                                                                                        |                      | 8.0        | 10.0                        |    |

|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|------------|-----------------------------|----|

| VPWR(CBON)                                 | Supply current adder when TPL communication active                                                                                                                                                                                                                                                                    |                      | 1          | <u> </u>                    |    |

| . ,                                        | 113                                                                                                                                                                                                                                                                                                                   |                      | <u> </u>   | 16                          | mA |

| VPWR(ADC)                                  | Supply current adder to set all 14 cell balance switches ON                                                                                                                                                                                                                                                           | _                    | 0.97       | _                           | mA |

|                                            | Delta supply current to perform ADC conversions (addend) <sup>[1]</sup><br>ADC1-A,B continuously converting<br>ADC2 continuously converting                                                                                                                                                                           | _                    | 3.0<br>1.4 | 5.0<br><br>2.0<br>          | mA |

| Ivpwr(ss)                                  | Supply current in sleep mode and in idle mode, communication<br>inactive, cell balance off, cyclic measurement off, oscillator monitor<br>on<br>SPI mode (25 °C)<br>SPI mode (-40 °C to 60 °C)<br>SPI mode (105 °C)<br>TPL mode ( $T_A = 25$ °C)<br>TPL mode ( $T_A = -40$ °C to 60 °C)<br>TPL mode ( $T_A = 105$ °C) | <br><br>64<br>54     | 40<br>     | <br>75<br>100<br>108<br>115 | μΑ |

| Ivpwr(ckmon)                               | Clock monitor current consumption                                                                                                                                                                                                                                                                                     | 76<br>—              | 5          | 138<br>8                    | μA |

| Vvpwr_ct                                   | $\begin{tabular}{ l l l l l l l l l l l l l l l l l l l$                                                                                                                                                                                                                                                              | -3.0<br>-2.0<br>-1.5 |            | 3.0<br>2.0<br>1.5           | V  |

| V <sub>PWR(OV_FLAG)</sub>                  | V <sub>PWR</sub> overvoltage fault threshold (flag)                                                                                                                                                                                                                                                                   | 63<br>—              | 65         | 68<br>—                     | V  |

| V <sub>PWR(LV_FLAG)</sub>                  | V <sub>PWR</sub> low-voltage warning threshold (flag)                                                                                                                                                                                                                                                                 | 11.7<br>—            | 12         | 12.3                        | V  |

| V <sub>PWR(UV_POR)</sub>                   | V <sub>PWR</sub> undervoltage shutdown threshold (POR)                                                                                                                                                                                                                                                                | 7.6                  | 8.5        | 9.6                         | V  |

| V <sub>PWR(HYS)</sub>                      | V <sub>PWR</sub> UV hysteresis voltage                                                                                                                                                                                                                                                                                | 100<br>—             | 200        | _                           | mV |

| t <sub>VPWR(FILTER)</sub>                  | V <sub>PWR</sub> OV, LV filter                                                                                                                                                                                                                                                                                        | _                    | 50         |                             | μs |

| VCOM power supp                            | bly                                                                                                                                                                                                                                                                                                                   |                      |            |                             |    |

| V <sub>COM</sub>                           | VCOM output voltage                                                                                                                                                                                                                                                                                                   | 4.9<br>—             | 5.0        | 5.2<br>—                    | V  |

| I <sub>VCOM</sub>                          | VCOM output current allocated for external use                                                                                                                                                                                                                                                                        | _                    | 1_         | 5.0                         | mA |

| V <sub>COM(UV)</sub>                       | VCOM undervoltage fault threshold                                                                                                                                                                                                                                                                                     | 4.2                  | 4.4        | 4.6                         | V  |

| V <sub>COM_HYS</sub>                       | VCOM undervoltage hysteresis                                                                                                                                                                                                                                                                                          | _                    | 100        | _                           | mV |

|                                            | VCOM undervoltage fault timer                                                                                                                                                                                                                                                                                         | _                    | 10         |                             | μs |

| t <sub>VCOM(FLT_TIMER)</sub>               |                                                                                                                                                                                                                                                                                                                       |                      |            |                             | 1  |

| t <sub>VCOM(FLT_TIMER)</sub>               | VCOM fault retry timer                                                                                                                                                                                                                                                                                                | _                    | 10         |                             | ms |

MC33771C Product data sheet

Battery cell controller IC

Characteristics noted under conditions 9.6 V  $\leq V_{PWR} \leq 63$  V, -40 °C  $\leq T_A \leq 105$  °C, GND = 0 V, unless otherwise stated. Typical values refer to  $V_{PWR} = 56$  V,  $T_A = 25$  °C, unless otherwise noted.

| Symbol                      | Parameter                                                                                                                                                                                                                                | Min                | Тур                 | Max       | Unit   |

|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|---------------------|-----------|--------|

| ILIM_VCOM(OC)               | VCOM current limit                                                                                                                                                                                                                       | 65                 | —                   | 140       | mA     |

| R <sub>VCOM(SS)</sub>       | VCOM sleep mode pull-down resistor                                                                                                                                                                                                       | 1.0                | 2.0                 | 5.0<br>—  | kΩ     |

| t <sub>VCOM</sub>           | VCOM rise time (for $V_{PWR}$ > 10V and CL = 2.2 µF (ceramic X7R only) in parallel with 220 pF)                                                                                                                                          | <sup>1]</sup>      | _                   | 440       | μs     |

| VANA power supp             | bly                                                                                                                                                                                                                                      |                    |                     | 1         |        |

| V <sub>ANA</sub>            | VANA output voltage (not used by external circuits)<br>Decouple with 47 nF X7R 0603 or 0402                                                                                                                                              | 2.6                | 2.65                | 2.7       | V      |

| V <sub>ANA(UV)</sub>        | VANA undervoltage fault threshold                                                                                                                                                                                                        | 2.28               | 2.4                 | 2.5       | V      |

| V <sub>ANA_HYS</sub>        | VANA undervoltage hysteresis                                                                                                                                                                                                             |                    | 50                  | _         | mV     |

| V <sub>ANA(FLT_TIMER)</sub> | VANA undervoltage fault timer                                                                                                                                                                                                            | —                  | 11                  | _         | μs     |

| V <sub>ANA(OV)</sub>        | VANA overvoltage fault threshold                                                                                                                                                                                                         | 2.77               | 2.8                 | 2.85<br>— | V      |

| t <sub>VANA(RETRY)</sub>    | VANA fault retry timer                                                                                                                                                                                                                   | —                  | 10                  | —         | ms     |

| ILIM_VANA(OC)               | VANA current limit                                                                                                                                                                                                                       | 5.0                | —                   | 10        | mA     |

| R <sub>VANA_RPD</sub>       | VANA sleep mode pull-down resistor                                                                                                                                                                                                       | —                  | 1.0                 | —         | kΩ     |

| t <sub>VANA</sub>           | VANA rise time (CL = 47 nF ceramic X7R only) [4]                                                                                                                                                                                         | <sup>1]</sup>      | —                   | 400       | μs     |

| ADC1-A, ADC1-B              |                                                                                                                                                                                                                                          |                    |                     |           |        |

| CTn <sub>(LEAKAGE)</sub>    | Cell terminal input leakage current (except in SLEEP mode when cell balancing is ON)                                                                                                                                                     | -                  | 10                  | 100       | nA     |

| CTn <sub>(FV)</sub>         | Cell terminal input current - functional verification                                                                                                                                                                                    | -                  | 0.365               | 0.5<br>—  | mA     |

| CT <sub>N</sub>             | Cell terminal input current during conversion                                                                                                                                                                                            | _                  | 50                  | _         | nA     |

| R <sub>PD</sub>             | Cell terminal open load detection pull-down resistor                                                                                                                                                                                     | 850<br>—           | 950                 | 1250<br>— | Ω      |

| V <sub>VPWR_RES</sub>       | VPWR terminal measurement resolution                                                                                                                                                                                                     | _                  | 2.44141             | -         | mV/LSB |

| V <sub>VPWR_RNG</sub>       | VPWR terminal measurement range                                                                                                                                                                                                          | 9.6                | _                   | 75        | V      |

| VPWR <sub>TERM_ERR</sub>    | VPWR terminal measurement accuracy                                                                                                                                                                                                       | -0.5               | _                   | 0.5       | %      |

| V <sub>CT_RNG</sub>         | ADC differential input voltage range for CTn to CTn-1                                                                                                                                                                                    | <sup>5]</sup> 0.0  | _                   | 4.85      | V      |

| V <sub>CT_ANx_RES</sub>     | Cell voltage and ANx resolution in 15-bit MEAS_xxxx registers                                                                                                                                                                            | —                  | 152.58789           | —         | µV/LSB |

| V <sub>ANX_RATIO_RES</sub>  | ANx resolution in 15-bit MEAS_xxxx registers in ratiometric mode                                                                                                                                                                         | -                  | VCOM.<br>(30.51758) | -         | µV/LSB |

| V <sub>ERR33RT</sub>        | Cell voltage measurement error V <sub>CELL</sub> = 3.3 V, T <sub>A</sub> = 25 °C $\begin{bmatrix} 1 \\ 1 \end{bmatrix}$                                                                                                                  |                    | ±0.4                | 0.8       | mV     |

| V <sub>ERR</sub>            | Cell voltage measurement error         [6] $0.1 \text{ V} \le \text{V}_{\text{CELL}} \le 4.8 \text{ V}, -40 \text{ °C} \le \text{T}_{\text{A}} \le 105 \text{ °C}$ (or -40 °C $\le \text{T}_{\text{J}} \le 125 \text{ °C}$ )         [7] | <sup>7]</sup> -5 5 | ±0.7                | 5.5<br>—  | mV     |

| V <sub>ERR_1</sub>          | Cell voltage measurement errorIf $0 \ V \le V_{CELL} \le 1.5 \ V, -40 \ ^{\circ}C \le T_A \le 60 \ ^{\circ}C \ (or -40 \ ^{\circ}C \le T_J \le 85 \ ^{\circ}C)$ If                                                                       | 3] -1 5            | ±0.4                | 1.5       | mV     |

Battery cell controller IC

Characteristics noted under conditions 9.6 V  $\leq V_{PWR} \leq 63$  V, -40 °C  $\leq T_A \leq 105$  °C, GND = 0 V, unless otherwise stated. Typical values refer to  $V_{PWR} = 56$  V,  $T_A = 25$  °C, unless otherwise noted.

| Symbol                | Parameter                                                                                                                                                                                                                                                              |                   | Min         | Тур                   | Max       | Unit |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------------|-----------------------|-----------|------|

| V <sub>ERR_2</sub>    | Cell voltage measurement error<br>1.5 V $\leq$ V <sub>CELL</sub> $\leq$ 2.7 V, -40 °C $\leq$ T <sub>A</sub> $\leq$ 60 °C (or -40 °C $\leq$ T <sub>J</sub> $\leq$ 85 °C)                                                                                                | [6]<br>[7]        | -2.0        | ±0.4                  | 2.0       | mV   |

| V <sub>ERR_3</sub>    | Cell voltage measurement error<br>2.7 V $\leq$ V <sub>CELL</sub> $\leq$ 3.7 V, -40 °C $\leq$ T <sub>A</sub> $\leq$ 60 °C (or -40 °C $\leq$ T <sub>J</sub> $\leq$ 85 °C)                                                                                                | [6]<br>[7]        | -2.0        | ±0.5                  | 2.0       | mV   |

| V <sub>ERR_4</sub>    | Cell voltage measurement error<br>3.7 V $\leq$ V <sub>CELL</sub> $\leq$ 4.3 V, -40 °C $\leq$ T <sub>A</sub> $\leq$ 60 °C (or -40 °C $\leq$ T <sub>J</sub> $\leq$ 85 °C)                                                                                                | [6]<br>[7]        | -2.8        | ±0.7                  | 2.8       | mV   |

| V <sub>ERR_5</sub>    | Cell voltage measurement error<br>1.5 V ≤ V <sub>CELL</sub> ≤ 4.5 V, −40 °C ≤ T <sub>A</sub> ≤ 105 °C (or −40 °C ≤ T <sub>J</sub> ≤<br>125 °C)                                                                                                                         | [6]<br>[7]        | -4.5        | ±0.7                  | 4.5       | mV   |

| V <sub>err33rta</sub> | Cell voltage measurement error after aging, V <sub>CELL</sub> = 3.3 V, T <sub>A</sub> = 25 $^\circ\text{C}$                                                                                                                                                            | [6]<br>[9]        | -1.5        | ±0.5                  | 1.5       | mV   |

| V <sub>ERR_A</sub>    | Cell voltage measurement error<br>after aging, 0.1 V $\leq$ V <sub>CELL</sub> $\leq$ 4.8 V, -40 °C $\leq$ T <sub>A</sub> $\leq$ 105 °C (or<br>-40 °C $\leq$ T <sub>J</sub> $\leq$ 125 °C)                                                                              | [6]<br>[8]<br>[9] | -8.0<br>    | ±0.8                  | 8.0       | mV   |

| V <sub>ERR_1A</sub>   | Cell voltage measurement error<br>after aging, 0 V $\leq$ V <sub>CELL</sub> $\leq$ 1.5 V, -40 °C $\leq$ T <sub>A</sub> $\leq$ 60 °C (or -40 °C $\leq$ T <sub>J</sub> $\leq$ 85 °C)                                                                                     | [6]<br>[8]<br>[9] | -2.0        | ±0.5                  | 2.0       | mV   |

| V <sub>ERR_2A</sub>   | Cell voltage measurement error<br>after aging, 1.5 V $\leq$ V <sub>CELL</sub> $\leq$ 2.7 V, -40 °C $\leq$ T <sub>A</sub> $\leq$ 60 °C (or<br>-40 °C $\leq$ T <sub>J</sub> $\leq$ 85 °C)                                                                                | [6]<br>[9]        | -2.5        | ±0.5                  | 2.5       | mV   |

| V <sub>ERR_3A</sub>   | Cell voltage measurement error<br>after aging, 2.7 V $\leq$ V <sub>CELL</sub> $\leq$ 3.7 V, -40 °C $\leq$ T <sub>A</sub> $\leq$ 60 °C (or<br>-40 °C $\leq$ T <sub>J</sub> $\leq$ 85 °C)                                                                                | [6]<br>[9]        | -3.2        | ±0.4                  | 3.2       | mV   |

| V <sub>ERR_4A</sub>   | Cell voltage measurement error<br>after aging, 3.7 V $\leq$ V <sub>CELL</sub> $\leq$ 4.3 V, -40 °C $\leq$ T <sub>A</sub> $\leq$ 60 °C (or<br>-40 °C $\leq$ T <sub>J</sub> $\leq$ 85 °C)                                                                                | [6]<br>[9]        | -3.9        | ±0.7                  | 3.9       | mV   |

| V <sub>ERR_5A</sub>   | Cell voltage measurement error<br>after aging, $1.5 \text{ V} \le \text{V}_{\text{CELL}} \le 4.5 \text{ V}$ , $-40 ^{\circ}\text{C} \le \text{T}_{\text{A}} \le 105 ^{\circ}\text{C}$ (or<br>$-40 ^{\circ}\text{C} \le \text{T}_{\text{J}} \le 125 ^{\circ}\text{C}$ ) | [6]<br>[9]        | -6.0        | ±0.7                  | 6.0       | mV   |

| V <sub>ANX_ERR</sub>  | Magnitude of ANx error in the entire measurement range:<br>Ratiometric measurement<br>Absolute measurement after soldering and aging, input in the<br>range [1.0, 4.5] V                                                                                               | [6]<br>[9]        |             |                       | 16<br>10  | mV   |

|                       | Absolute measurement after soldering and aging, input in the range [0, 4.85] V, for $-40 \degree C < T_A < 60 \degree C$ )<br>Absolute measurement after soldering and aging, input in the                                                                             |                   | -8.0<br>-11 | _                     | 8.0<br>11 |      |

| t <sub>vconv</sub>    | range [0, 4.85] V, for −40 °C < T <sub>A</sub> < 105 °C)<br>Single channel net conversion time<br>13-bit resolution<br>14-bit resolution<br>15-bit resolution                                                                                                          |                   |             | 6.77<br>9.43<br>14.75 |           | μs   |

| V <sub>V_NOISE</sub>  | 16-bit resolution Conversion noise                                                                                                                                                                                                                                     |                   |             | 25.36                 |           | µVrm |

| _                     | 13-bit resolution<br>14-bit resolution                                                                                                                                                                                                                                 |                   | _           | 1800<br>1000          | _         |      |

Battery cell controller IC

| Symbol                  | Parameter                                                              | Min                  | Тур    | Мах      | Unit   |

|-------------------------|------------------------------------------------------------------------|----------------------|--------|----------|--------|

|                         | 15-bit resolution                                                      | -                    | 600    | —        |        |

|                         | 16-bit resolution                                                      | -                    | 400    | —        |        |

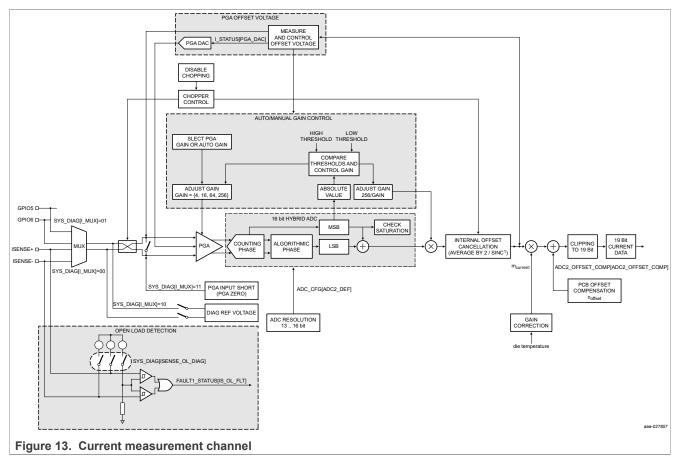

| ADC2/current sen        | se module                                                              | I                    |        | <b>I</b> | I      |

| V <sub>INC</sub>        | ISENSE+/ISENSE- input voltage (reference to AGND)                      | -300                 | _      | 300      | mV     |

| V <sub>IND</sub>        | ISENSE+/ISENSE- differential input voltage range                       | -150                 | -      | 150      | mV     |

| VISENSEX(OFFSET)        | ISENSE+/ISENSE- input voltage offset error                             | [10]                 | _      | 0.5      | μV     |

| ISENSEX(BIAS)           | ISENSE+/ISENSE- input bias current                                     | -100                 | _      | 100      | nA     |

| I <sub>SENSE(DIF)</sub> | ISENSE+/ISENSE- differential input bias current                        | -5.0                 | _      | 5.0      | nA     |

| IGAINERR                | ISENSE error including nonlinearities                                  | <sup>[11]</sup> -0.5 | _      | 0.5      | %      |

| IISENSE OL              | ISENSE open load injected current                                      | <sup>[12]</sup> 109  | 130    | 151      | μA     |

|                         |                                                                        | _                    |        | —        |        |

| VISENSE_OL              | ISENSE open load detection threshold                                   | 340                  | 460    | 600      | mV     |

| -                       |                                                                        | —                    |        | —        |        |

| V <sub>2RES</sub>       | Current sense user register resolution                                 | —                    | 0.6    | —        | µV/LSB |

| V <sub>PGA_SAT</sub>    | PGA saturation half-range                                              |                      |        |          | mV     |

|                         | Gain = 256                                                             | —                    | 4.9    | <u> </u> |        |

|                         | Gain = 64                                                              | -                    | 19.5   | -        |        |

|                         | Gain = 16                                                              | -                    | 78.1   | —        |        |

|                         | Gain = 4                                                               |                      | 150.0  |          |        |

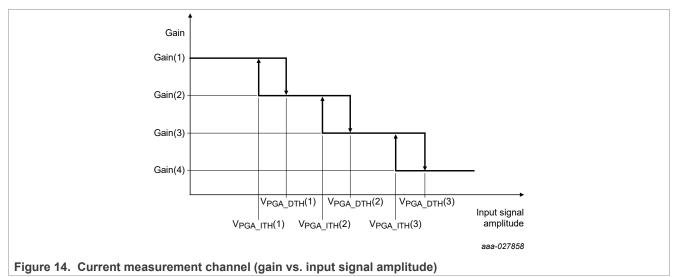

| V <sub>PGA_ITH</sub>    | Voltage threshold for PGA gain increase                                |                      |        |          | mV     |

|                         | Gain = 256                                                             | —                    | —      | —        |        |

|                         | Gain = 64                                                              | —                    | 2.344  | —        |        |

|                         | Gain = 16                                                              | —                    | 9.375  | -        |        |

|                         | Gain = 4                                                               |                      | 37.50  |          |        |

| V <sub>PGA_DTH</sub>    | Voltage threshold for PGA gain decrease                                |                      |        |          | mV     |

|                         | Gain = 256                                                             | —                    | 4.298  | —        |        |

|                         | Gain = 64                                                              | —                    | 17.188 | —        |        |

|                         | Gain = 16                                                              | <u> </u>             | 68.750 | —        |        |

|                         | Gain = 4                                                               | —                    | —      | —        |        |

| t <sub>AZC_SETTLE</sub> | Time to perform auto-zero procedure after enabling the current channel |                      | 200    | —        | μs     |

| t <sub>ICONV</sub>      | ADC conversion time including PGA settling time                        |                      |        |          | μs     |

|                         | 13 bit resolution                                                      | _                    | 19.00  | <u> </u> |        |

|                         | 14 bit resolution                                                      | _                    | 21.67  | <u> </u> |        |

|                         | 15 bit resolution                                                      | <u> </u>             | 27.00  | —        |        |

|                         | 16 bit resolution                                                      | —                    | 37.67  | —        |        |

| VI_NOISE                | Noise error at 16-bit conversion                                       | [10]                 | 3.01   | —        | μVrms  |

| V <sub>I_NOISE</sub>    | Noise error at 13-bit conversion                                       | _                    | 8.33   | —        | μVrms  |

| ADC <sub>CLK</sub>      | ADC2 and ADC1-A,B clocking frequency                                   | 5.7                  | 6.0    | 6.3      | MHz    |

|                         |                                                                        | —                    |        |          |        |

| Diagnostic thresh       | olds                                                                   |                      |        |          |        |

| V <sub>OL_DETECT</sub>  | Cell terminal open load V detection threshold                          | [13]                 |        |          | mV     |

|                         | $1.5 \text{ V} \le \text{V}_{\text{CELL}} \le 2.7 \text{ V}$           | -                    | 50     | _        |        |

|                         | $2.5 \text{ V} \le \text{V}_{\text{CELL}} \le 3.7 \text{ V}$           | -                    | 100    | _        |        |

|                         | $2.5 \text{ V} \le \text{V}_{\text{CELL}} \le 4.3 \text{ V}$           | _                    | 150    | <u> </u> |        |

Table 8. Static and dynamic electrical characteristics...continued

Characteristics noted under conditions 9.6 V  $\leq V_{PWR} \leq 63$  V, -40 °C  $\leq T_A \leq 105$  °C, GND = 0 V, unless otherwise stated. Typical values refer to  $V_{PWR} = 56$  V,  $T_A = 25$  °C, unless otherwise noted.

Battery cell controller IC

Table 8. Static and dynamic electrical characteristics...continued

Characteristics noted under conditions 9.6 V  $\leq V_{PWR} \leq 63$  V, -40 °C  $\leq T_A \leq 105$  °C, GND = 0 V, unless otherwise stated. Typical values refer to  $V_{PWR} = 56$  V,  $T_A = 25$  °C, unless otherwise noted.

| Symbol                                    | Parameter                                                                                                                                                                                | Min                | Тур            | Max                  | Unit |

|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------------|----------------------|------|

| V <sub>LEAK</sub>                         | Cell terminal leakage detection level [6] [14]                                                                                                                                           | -27                | -              | 27                   | mV   |

| V <sub>REF_DIAG</sub>                     | ISENSE diagnostic reference with PGA having gain 4                                                                                                                                       | 124                | 127            | 130                  | mV   |

| V <sub>OFF_DIAG</sub>                     | ISENSE diagnostic common mode offset voltage [15]                                                                                                                                        | _                  | _              | 37.2                 | μV   |

| V <sub>REF_ZD</sub>                       | Precision diagnostic Zener reference for cell voltage channel <sup>[6]</sup><br>functional verification                                                                                  | 4.45<br>—          | 4.6            | 4.85<br>—            | V    |

| V <sub>CVFV</sub>                         | Cell voltage channel functional verification allowable error in CT [6]<br>verification measurement [14]                                                                                  | -22                | -              | 6.0                  | mV   |

| V <sub>BGP</sub>                          | Voltage reference used in ADC1-A,B functional verification                                                                                                                               | _                  | 1.18           | _                    | V    |

| ADC1a <sub>FV</sub> , ADC1b <sub>FV</sub> | ADC1-A and ADC1-B functional verification [14]<br>Maximum tolerance between ADC1-A, B and diagnostic reference $(1.5 V \le V_{CELL} \le 4.3 V)$                                          | -5.25              | _              | 5.25                 | mV   |

| CTx_UV_TH                                 |                                                                                                                                                                                          | 390<br>650<br>1200 |                |                      | mV   |

| CTx_OV_TH                                 |                                                                                                                                                                                          |                    |                | 1800<br>4000<br>4000 | mV   |

| Cell balance drivers                      |                                                                                                                                                                                          |                    | -              | 1                    |      |

| V <sub>DS(CLAMP)</sub>                    | Cell balance driver VDS active clamp voltage                                                                                                                                             | 10                 | 11             | 12                   | V    |

| V <sub>OUT(FLT_TH)</sub>                  | Output fault detection voltage threshold<br>Balance off (open load)<br>Balance on (shorted load)                                                                                         | 0.3                | 0.55           | 0.75                 | V    |

| R <sub>PD_CB</sub>                        | Output OFF open load detection pull-down resistor<br>Balance off, open load detect disabled                                                                                              | 1.7                | 2.0            | 2.9                  | kΩ   |

| I <sub>OUT(LKG)</sub>                     | Output leakage current<br>Balance off, open load detect disabled at V <sub>DS</sub> = 4.0 V                                                                                              | _                  | _              | 1.0                  | μA   |

| R <sub>DS(on)</sub>                       | Drain-to-source on resistance<br>$I_{OUT} = 300 \text{ mA}, T_J = 105 \text{ °C}$<br>$I_{OUT} = 300 \text{ mA}, T_J = 25 \text{ °C}$<br>$I_{OUT} = 300 \text{ mA}, T_J = -40 \text{ °C}$ |                    | <br>0.5<br>0.4 | 0.80                 | Ω    |

| I <sub>LIM_CB</sub>                       | Driver current limitation                                                                                                                                                                | 310                | _              | 950                  | mA   |

| t <sub>ON</sub>                           | Cell balance driver turn on $R_L = 15 \Omega$                                                                                                                                            | _                  | 350            | 450                  | μs   |

| t <sub>OFF</sub>                          | Cell balance driver turn off $R_L = 15 \Omega$                                                                                                                                           |                    | 200            | _                    | μs   |

|                                           | Short/open detect filter time                                                                                                                                                            | l                  | 20             |                      | μs   |

Battery cell controller IC

#### Table 8. Static and dynamic electrical characteristics...continued

Characteristics noted under conditions 9.6 V  $\leq V_{PWR} \leq 63$  V, -40 °C  $\leq T_A \leq 105$  °C, GND = 0 V, unless otherwise stated. Typical values refer to  $V_{PWR} = 56$  V,  $T_A = 25$  °C, unless otherwise noted.

| Symbol                    | Parameter                                                                                                    | Min                       | Тур       | Мах              | Unit   |

|---------------------------|--------------------------------------------------------------------------------------------------------------|---------------------------|-----------|------------------|--------|

| IC_TEMP1_ERR              | IC temperature measurement error                                                                             | -3.0                      | -         | 3.0              | к      |

| IC_TEMP1_RES              | IC temperature resolution                                                                                    | —                         | 0.032     | -                | K/LSB  |

| TSD_TH                    | Thermal shutdown                                                                                             | 155<br>—                  | 170       | 185<br>—         | °C     |

| TSD_HYS                   | Thermal shutdown hysteresis                                                                                  | 5.0<br>—                  | 10        | 12.2<br>—        | °C     |

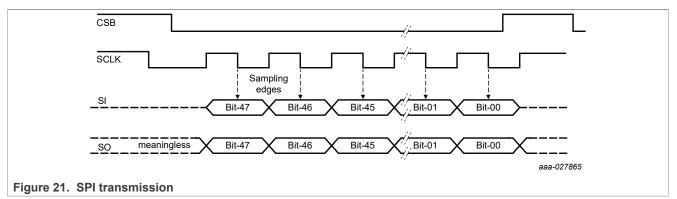

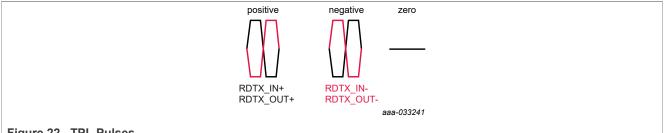

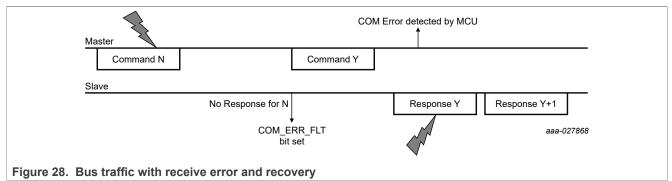

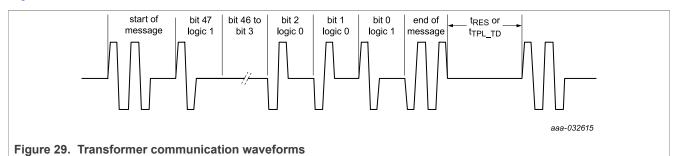

| Default operational       | parameters                                                                                                   | 1                         |           |                  |        |