CM44-10116-2E

www.DatasheetAU.com

# FUJITSU SEMICONDUCTOR CONTROLLER MANUAL

# F<sup>2</sup>MC-16LX 16-BIT MICROCONTROLLER MB90M405 Series HARDWARE MANUAL

# F<sup>2</sup>MC-16LX 16-BIT MICROCONTROLLER MB90M405 Series HARDWARE MANUAL

**FUJITSU LIMITED**

#### Objectives and Intended Reader

Thank you for purchasing a Fujitsu semiconductor product.

The MB90M405 series is a series of general-purpose 16-bit microcontrollers with 60 built-in high-tension-resistant output pins required for fluorescent display control. The MB90M405 series was developed for applications that require the control of a vacuum fluorescent tube panel.

This manual, intended for engineers who design products using the MB90M405 series, describes the functions and operations of MB90M405 series products.

#### Trademark

F<sup>2</sup>MC is the abbreviation of FUJITSU Flexible Microcontroller.

Embedded Algorithm is a trademark of Advanced Micro Devices Corporation.

Other system and product names used in this manual are trademarks of their respective companies or organizations.

The symbols <sup>TM</sup> and <sup>®</sup> are sometimes omitted in the text.

#### License

Purchase of FUJITSU Ltd,  $I^2C$  components conveys a license under the Philips  $I^2C$  Patent Right to use.

These components in an I<sup>2</sup>C system, provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips.

#### Organization of This Manual

This manual consists of the following 24 chapters and an appendix:

#### **CHAPTER 1 "OVERVIEW"**

This chapter summarizes the features and basic specifications of the MB90M405 series of microcontrollers.

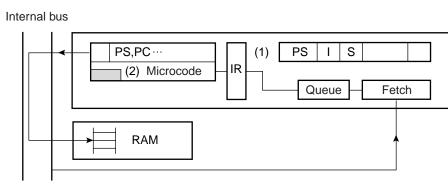

#### CHAPTER 2 "CPU"

This chapter describes the CPU and the memory space provided by the MB90M405 series

#### CHAPTER 3 "RESETS"

This chapter describes resets for the MB90M405 series.

#### **CHAPTER 4 "CLOCKS"**

This chapter describes the clocks used by MB90M405 series.

#### CHAPTER 5 "LOW POWER CONSUMPTION MODE"

This chapter describes the low power consumption mode of MB90M405 series.

#### **CHAPTER 6 "INTERRUPTS"**

This chapter explains the interrupts and extended intelligent I/O service (EI<sup>2</sup>OS) in the MB90M405 series.

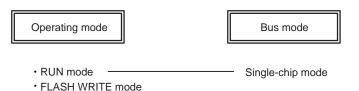

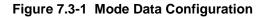

#### CHAPTER 7 "SETTING A MODE"

This chapter describes the operating modes and the memory access modes of the MB90M405 series.

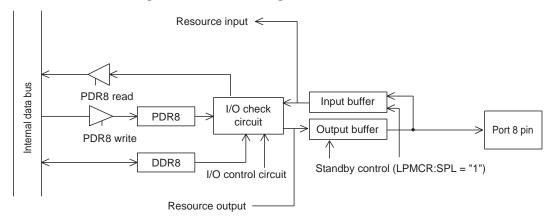

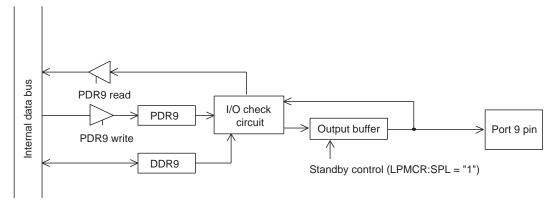

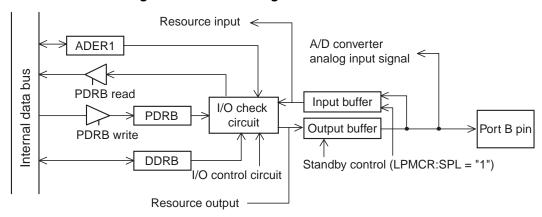

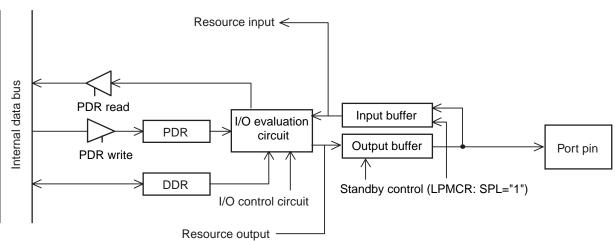

#### CHAPTER 8 "I/O PORTS"

This chapter describes the functions and operations of the MB90M405 series I/O ports.

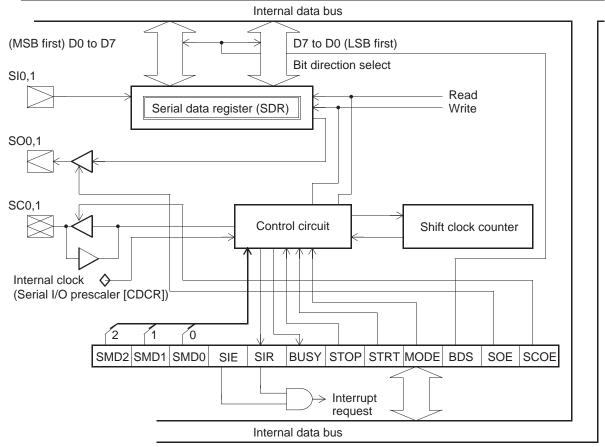

#### CHAPTER 9 "SERIAL I/O"

This chapter describes the functions and operations of the serial I/O unit of the MB90M405 series.

#### CHAPTER 10 "TIMEBASE TIMER"

This chapter describes the functions and operation of the timebase timer of the MB90M405 series.

#### CHAPTER 11 "WATCHDOG TIMER"

This chapter describes the functions and operations of the watchdog timer of the MB90M405 series.

#### CHAPTER 12 "16-BIT RELOAD TIMER"

This chapter describes the functions and operations of the 16-bit reload timer of the MB90M405 series.

#### CHAPTER 13 "16-BIT I/O TIMER"

This chapter describes the functions and operations of the 16-bit I/O timer of the MB90M405 series.

#### CHAPTER 14 "UART"

This chapter describes the functions and operations of the MB90M405 series UART.

#### CHAPTER 15 "DTP/EXTERNAL INTERRUPT CIRCUIT"

This chapter describes the functions and operations of the DTP/external interrupt circuit of the MB90M405 series.

#### CHAPTER 16 "I<sup>2</sup>C INTERFACE"

This chapter describes the functions and operations of the I<sup>2</sup>C interface of the MB90M405 series.

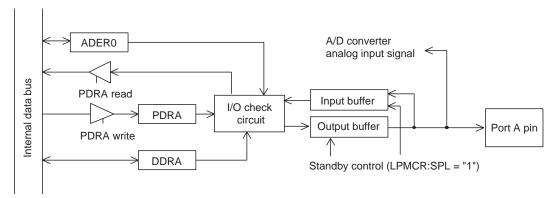

#### CHAPTER 17 "8/10-BIT A/D CONVERTER"

This chapter describes the functions and operations of the MB90M405 series 8/10-bit A/D converter.

#### CHAPTER 18 "FL CONTROL CIRCUIT"

This chapter explains the functions and operation of the MB90M405 series FL control circuit.

#### CHAPTER 19 "WATCH CLOCK OUTPUT"

This chapter describes the functions and operations of MB90M405 series watch clock output.

#### CHAPTER 20 "DELAYED INTERRUPT GENERATOR MODULE"

This chapter describes the functions and operation of the MB90M405 series delayed interrupt generator module.

#### CHAPTER 21 "ADDRESS MATCH DETECTION FUNCTION"

This chapter describes the address match detection function of the MB90M405 series and its operations.

#### CHAPTER 22 "ROM MIRRORING FUNCTION SELECTION MODULE"

This chapter describes the function and operation of the MB90M405 series ROM mirroring function selection module.

#### CHAPTER 23 "1M-BIT FLASH MEMORY"

This chapter describes the functions and operations of the MB90M405 series 1M-bit flash memory.

#### CHAPTER 24 "EXAMPLE OF MB90MF408 SERIAL PROGRAMMING CONNECTION"

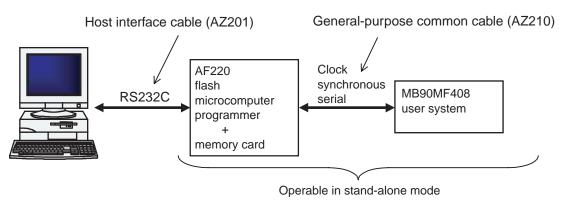

This chapter provides examples of connection for serial programming using the AF220 flash microcomputer programmer manufactured by YDC Corporation.

#### APPENDIX

This appendix includes I/O maps, instruction lists, and other information.

- The contents of this document are subject to change without notice. Customers are advised to consult with FUJITSU sales representatives before ordering.

- The information and circuit diagrams in this document are presented as examples of semiconductor device applications, and are not intended to be incorporated in devices for actual use. Also, FUJITSU is unable to assume responsibility for infringement of any patent rights or other rights of third parties arising from the use of this information or circuit diagrams.

- The products described in this document are designed, developed and manufactured as contemplated for general use, including without limitation, ordinary industrial use, general office use, personal use, and household use, but are not designed, developed and manufactured as contemplated (1) for use accompanying fatal risks or dangers that, unless extremely high safety is secured, could have a serious effect to the public, and could lead directly to death, personal injury, severe physical damage or other loss (i.e., nuclear reaction control in nuclear facility, aircraft flight control, air traffic control, mass transport control, medical life support system, missile launch control in weapon system), or (2) for use requiring extremely high reliability (i.e., submersible repeater and artificial satellite).

Please note that Fujitsu will not be liable against you and/or any third party for any claims or damages arising in connection with above-mentioned uses of the products.

- Any semiconductor devices have an inherent chance of failure. You must protect against injury, damage or loss from such failures by incorporating safety design measures into your facility and equipment such as redundancy, fire protection, and prevention of over-current levels and other abnormal operating conditions.

- If any products described in this document represent goods or technologies subject to certain restrictions on export under the Foreign Exchange and Foreign Trade Law of Japan, the prior authorization by Japanese government will be required for export of those products from Japan.

# CONTENTS

| CHAP | TER 1 OVERVIEW                               | 1  |

|------|----------------------------------------------|----|

| 1.1  | Features                                     | 2  |

| 1.2  | Product Lineup                               | 5  |

| 1.3  | Block Diagram                                | 7  |

| 1.4  | Package Dimensions                           | 8  |

| 1.5  | Pin Assignments                              |    |

| 1.6  | Pin Functions                                | 10 |

| 1.7  | I/O Circuit Types                            |    |

| 1.8  | Notes on Handling Devices                    |    |

| 1.9  | Clock Supply Map                             | 19 |

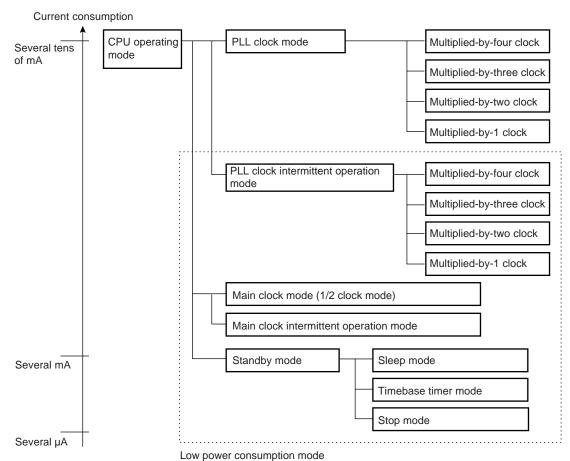

| 1.10 | Low Power Consumption Mode                   | 20 |

| СНАР | TER 2 CPU                                    | 21 |

| 2.1  | CPU                                          | 22 |

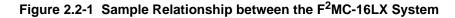

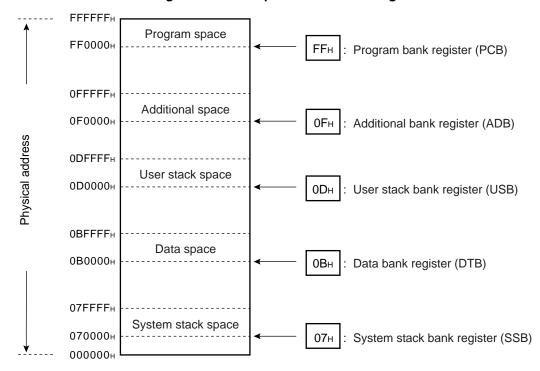

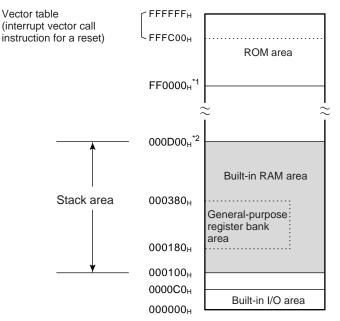

| 2.2  | Memory Space                                 | 23 |

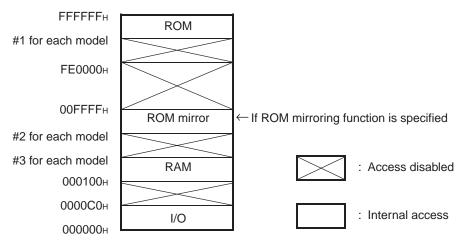

| 2.3  | Memory Maps                                  |    |

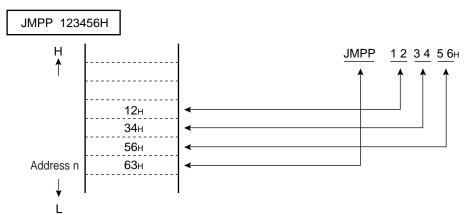

| 2.4  | Addressing                                   | 28 |

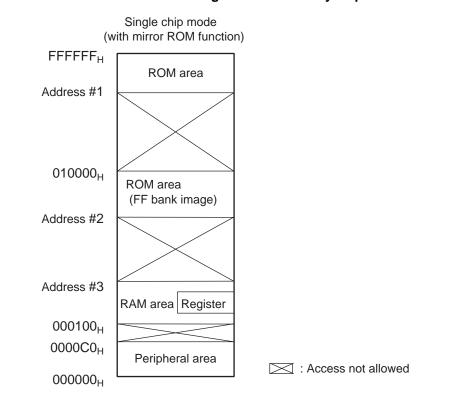

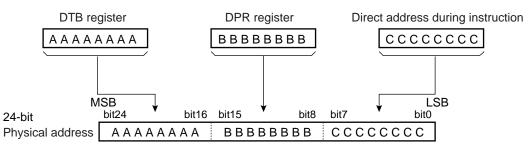

| 2.4  | Address Specification by Linear Addressing   | 29 |

| 2.4  | Address Specification by Bank Addressing     | 30 |

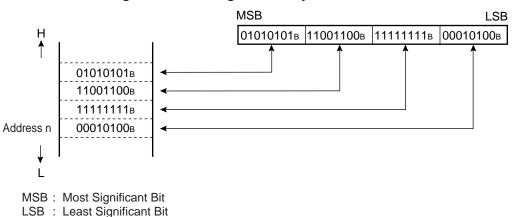

| 2.5  | Memory Location of Multibyte Data            | 32 |

| 2.6  | Registers                                    | 34 |

| 2.7  | Dedicated Registers                          | 35 |

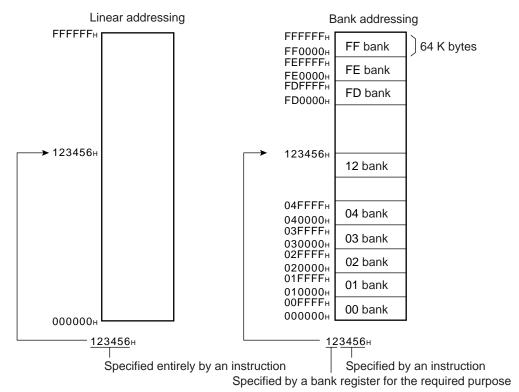

| 2.7  | 7.1 Accumulator (A)                          | 37 |

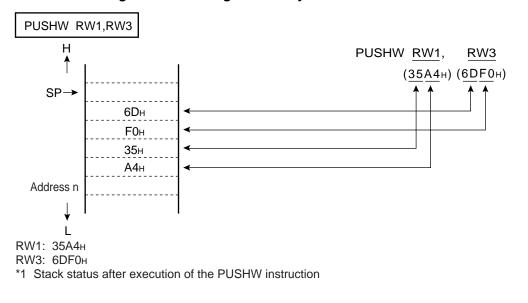

| 2.7  | 7.2 Stack Pointers (USP, SSP)                | 40 |

| 2.7  | 7.3 Processor Status (PS)                    | 42 |

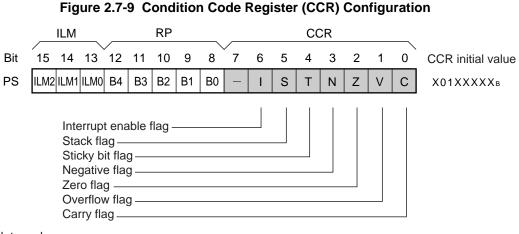

| 2.7  | 7.4 Condition Code Register (PS: CCR)        | 43 |

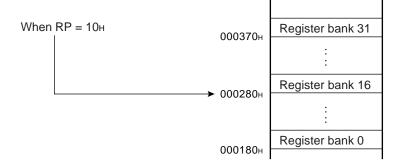

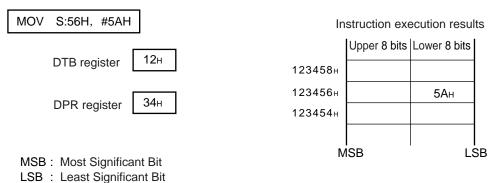

| 2.7  | 7.5 Register Bank Pointer (PS: RP)           | 45 |

| 2.7  | 7.6 Interrupt Level Mask Register (PS: ILM)  | 46 |

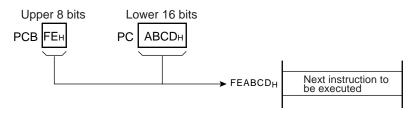

| 2.7  | 7.7 Program Counter (PC)                     | 47 |

| 2.7  | 7.8 Direct Page Register (DPR)               | 48 |

| 2.7  | 7.9 Bank Registers (PCB, DTB, USB, SSB, ADB) | 49 |

| 2.8  | General-Purpose Registers                    | 50 |

| 2.9  | Prefix Codes                                 | 52 |

| 2.9  | 0.1 Bank Select Prefix (PCB, DTB, ADB, SPB)  | 53 |

| 2.9  | 0.2 Common Register Bank Prefix (CMR)        | 55 |

| 2.9  | 9.3 Flag Change Suppression Prefix (NCC)     | 56 |

| 2.9  | 0.4 Restrictions on Prefix Codes             | 57 |

| СНАР       | TER 3 RESETS                                                                    | 59  |

|------------|---------------------------------------------------------------------------------|-----|

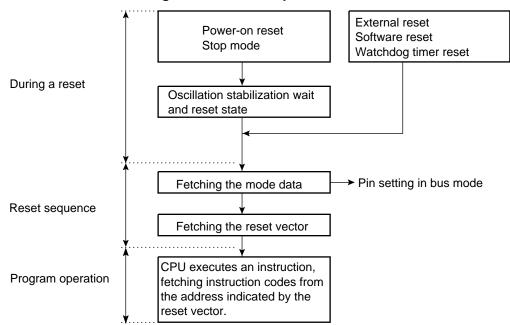

| 3.1        | Resets                                                                          | 60  |

| 3.2        | Reset Causes and Oscillation Stabilization Wait Time                            | 62  |

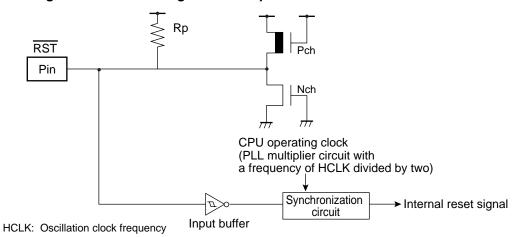

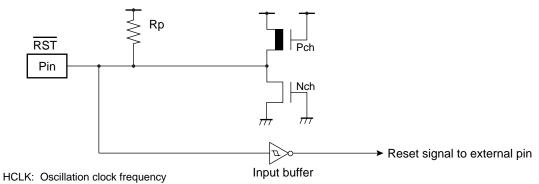

| 3.3        | External Reset Pin                                                              | 63  |

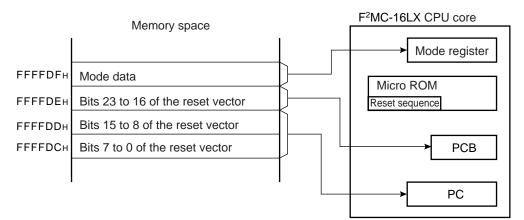

| 3.4        | Reset Operation                                                                 |     |

| 3.5        | Reset Cause Bits                                                                |     |

| 3.6        | Status of Pins in a Reset                                                       |     |

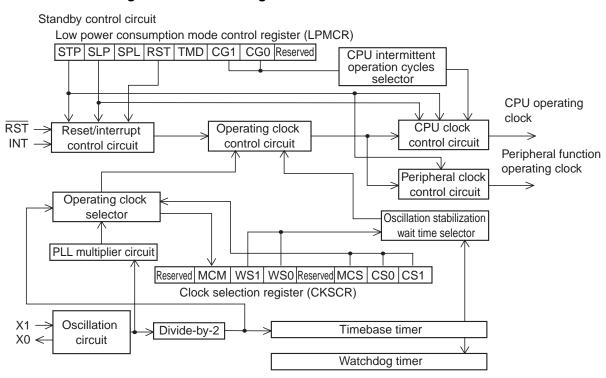

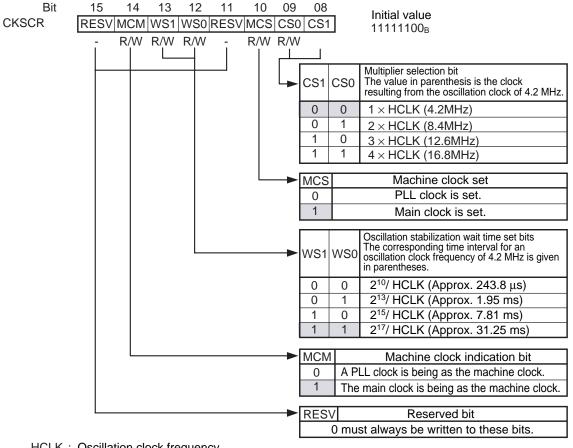

| СНАР       | TER 4 CLOCKS                                                                    |     |

| 4.1        | Clocks                                                                          |     |

| 4.2        | Block Diagram of the Clock Generation Block                                     |     |

| 4.3        | Clock Selection Register (CKSCR)                                                |     |

| 4.4        | Clock Mode                                                                      |     |

| 4.5        | Oscillation Stabilization Wait Time                                             |     |

| 4.6        | Connection of an Oscillator or an External Clock to the Microcontroller         |     |

| СНАР       | TER 5 LOW POWER CONSUMPTION MODE                                                | 81  |

| 5.1        | Low Power Consumption Mode                                                      |     |

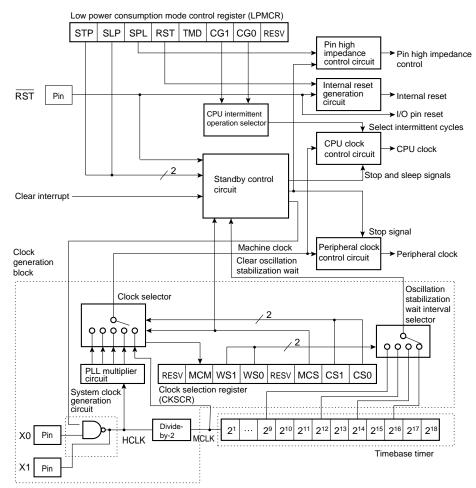

| 5.2        | Block Diagram of the Low Power Consumption Control Circuit                      |     |

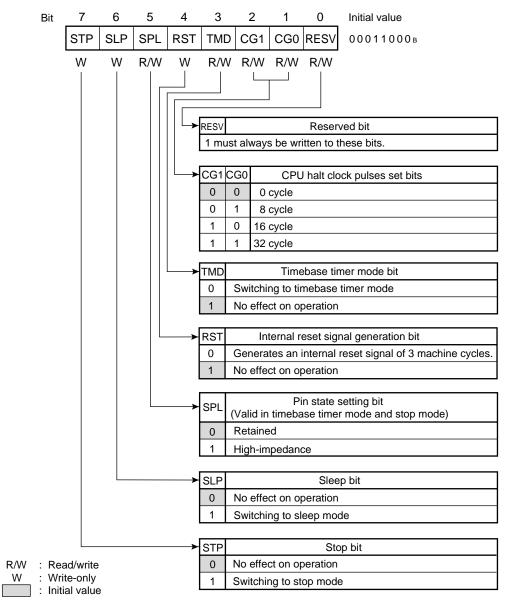

| 5.3        | Low Power Consumption Mode Control Register (LPMCR)                             |     |

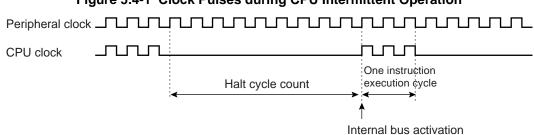

| 5.4        | CPU Intermittent Operation Mode                                                 |     |

| 5.4        | Standby Mode                                                                    |     |

| 5.5<br>5.5 | -                                                                               |     |

| 5.5        | •                                                                               |     |

| 5.5<br>5.5 |                                                                                 |     |

| 5.6        | •                                                                               |     |

| 5.0<br>5.7 | Status Change Diagram                                                           |     |

|            | Pin Status in Standby Mode and during Reset                                     |     |

| 5.8        | Usage Notes on Low Power Consumption Mode                                       |     |

| СНАР       | TER 6 INTERRUPTS                                                                | 101 |

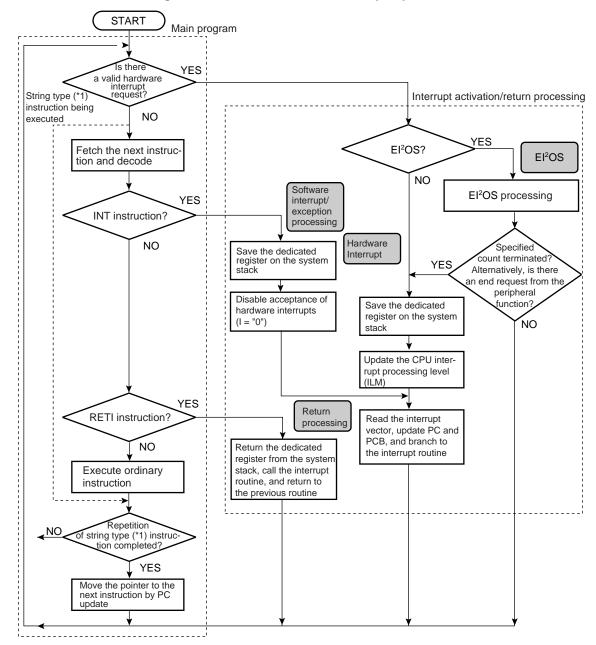

| 6.1        | Interrupts                                                                      | 102 |

| 6.2        | Interrupt Causes and Interrupt Vectors                                          | 104 |

| 6.3        | Interrupt Control Registers and Peripheral Functions                            | 106 |

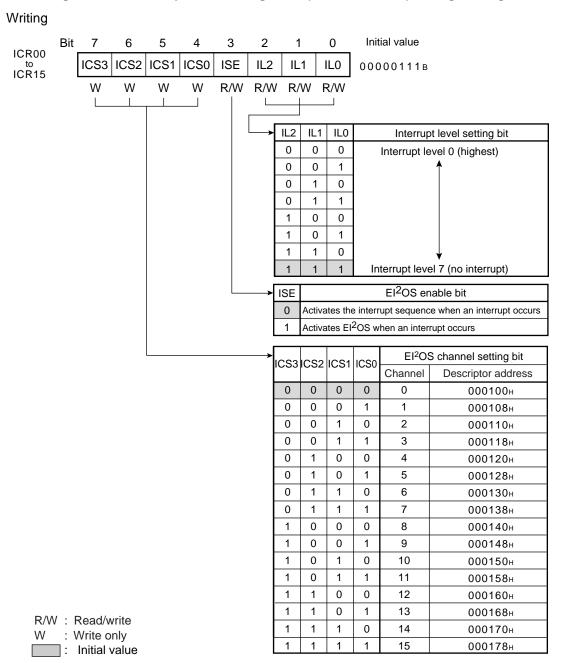

| 6.3        | .1 Interrupt Control Registers (ICR00 to ICR15)                                 | 108 |

| 6.3        | .2 Interrupt Control Register Functions                                         | 110 |

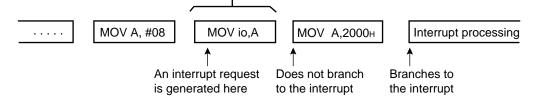

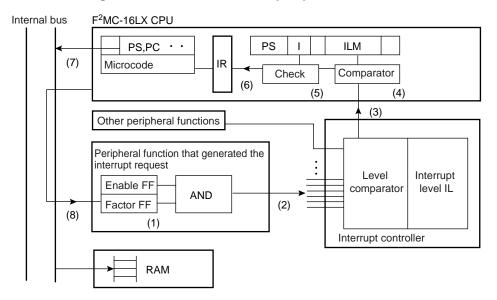

| 6.4        | Hardware Interrupts                                                             | 113 |

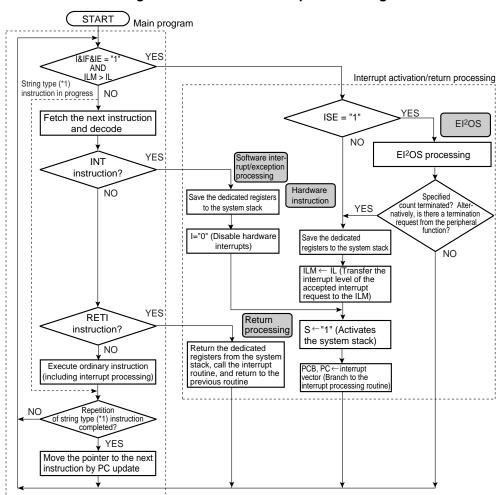

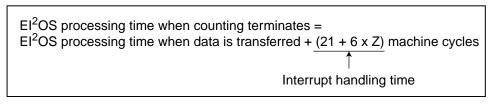

| 6.4        | .1 Operation of Hardware Interrupts                                             | 116 |

| 6.4        | .2 Processing for Interrupt Operation                                           | 118 |

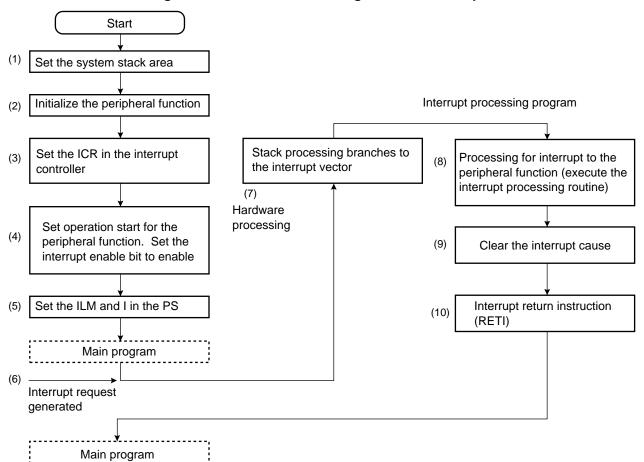

| 6.4        | .3 Procedure for Using Hardware Interrupts                                      | 119 |

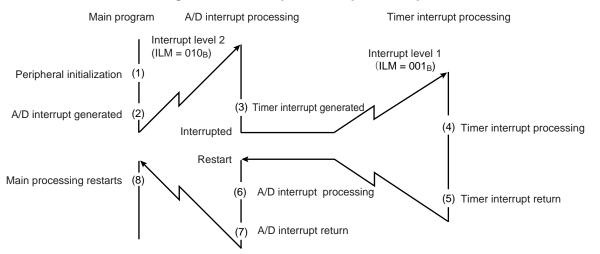

| 6.4        | .4 Multiple Interrupts                                                          | 121 |

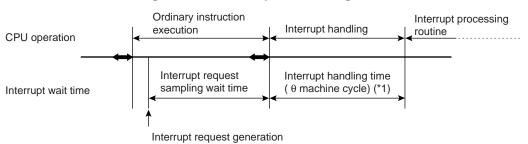

| 6.4        | .5 Hardware Interrupt Processing Time                                           | 123 |

| 6.5        | Software Interrupts                                                             | 125 |

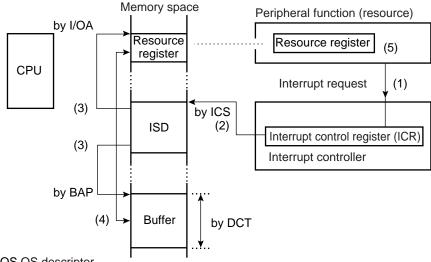

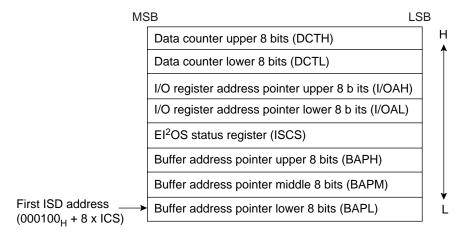

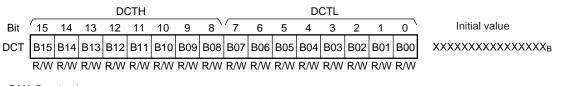

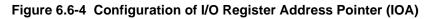

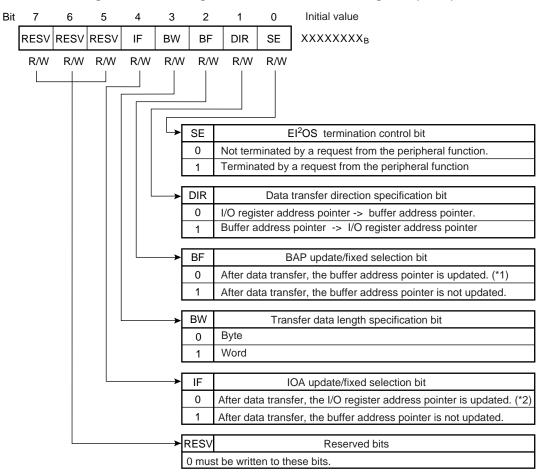

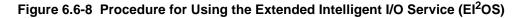

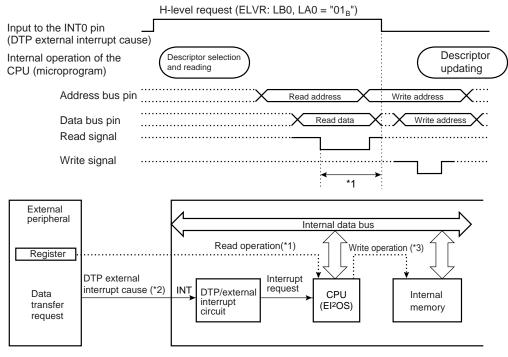

| 6.6        | Interrupt of Extended Intelligent I/O Service (EI <sup>2</sup> OS)              |     |

| 6.6        |                                                                                 |     |

| 6.6        |                                                                                 |     |

| 6.6        |                                                                                 |     |

| 6.6        |                                                                                 |     |

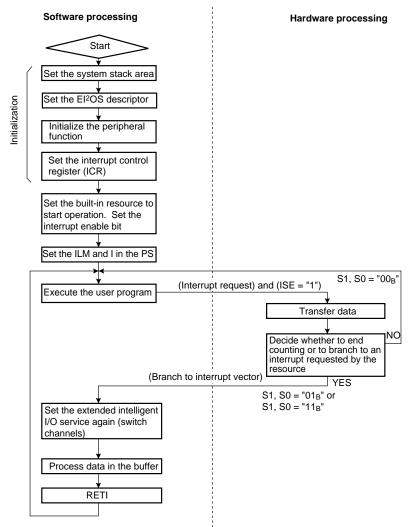

| 6.6        | .5 Processing Time of the Extended Intelligent I/O Service (EI <sup>2</sup> OS) | 136 |

| 149 |

|-----|

|     |

|     |

|     |

| 153 |

|     |

| 156 |

| 158 |

| 160 |

|     |

|     |

|     |

|     |

|     |

|     |

|     |

|     |

|     |

|     |

|     |

|     |

|     |

|     |

|     |

|     |

|     |

|     |

|     |

|     |

|     |

| 195 |

| 197 |

| 199 |

| 200 |

| 202 |

|     |

|     |

| 207 |

| 210 |

|     |

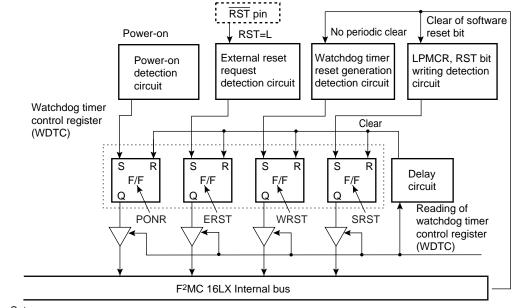

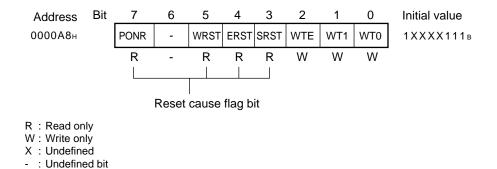

| CHAPTER 11 WATCHDOG TIMER                                                       | 211 |

|---------------------------------------------------------------------------------|-----|

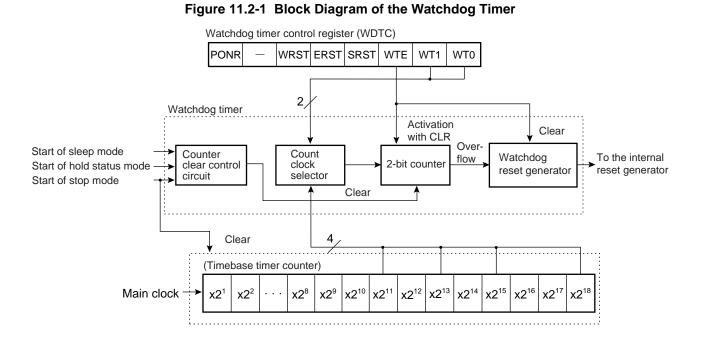

| 11.1 Overview of the Watchdog Timer                                             | 212 |

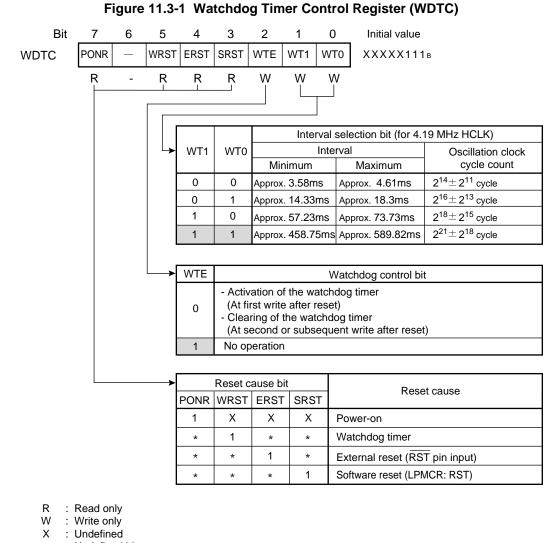

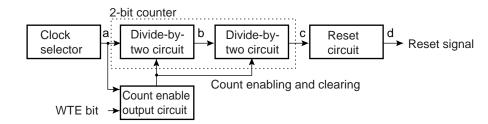

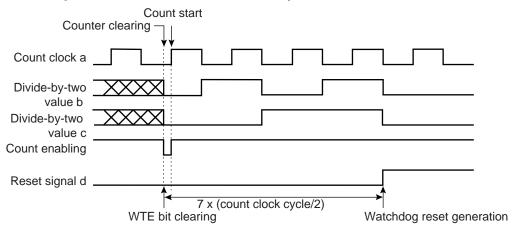

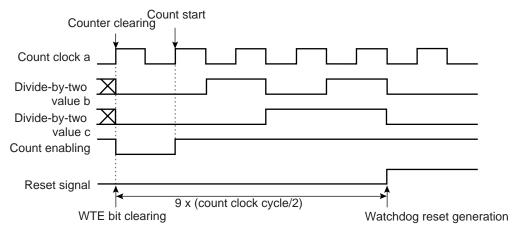

| 11.2 Configuration of the Watchdog Timer                                        | 213 |

| 11.3 Watchdog Timer Control Register (WDTC)                                     | 215 |

| 11.4 Operation of the Watchdog Timer                                            | 217 |

| 11.5 Usage Notes on the Watchdog Timer                                          | 219 |

| CHAPTER 12 16-BIT RELOAD TIMER                                                  | 221 |

| 12.1 Overview of the 16-Bit Reload Timer                                        | 222 |

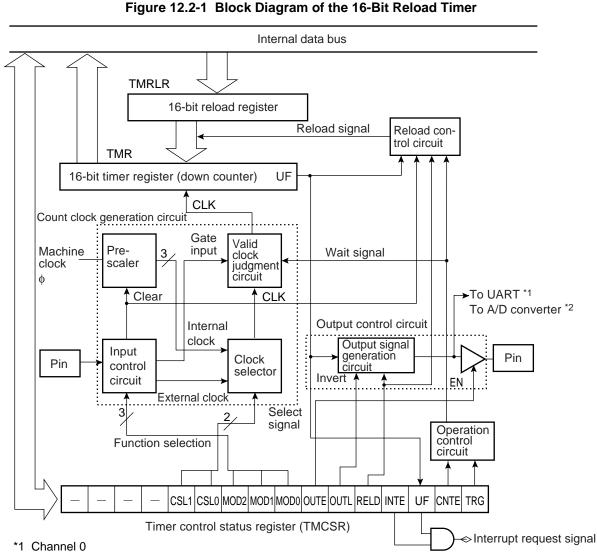

| 12.2 Configuration of the 16-Bit Reload Timer                                   |     |

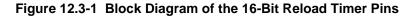

| 12.3 16-Bit Reload Timer Pins                                                   |     |

| 12.4 16-Bit Reload Timer Registers                                              | 228 |

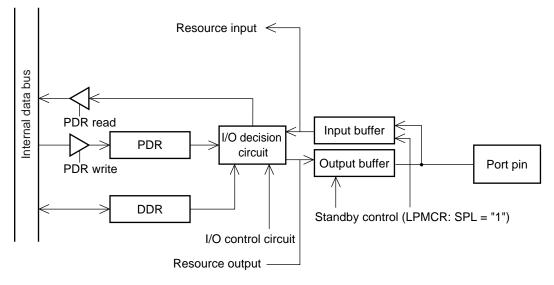

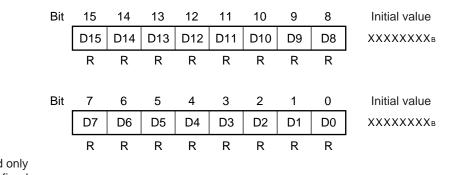

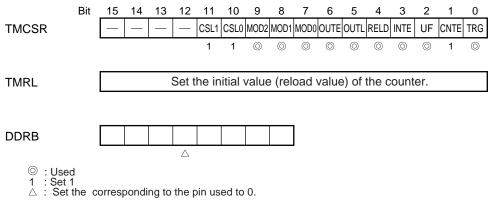

| 12.4.1 Timer Control Status Register, Higher (TMCSR)                            | 229 |

| 12.4.2 Timer Control Status Register, Lower (TMCSR)                             | 231 |

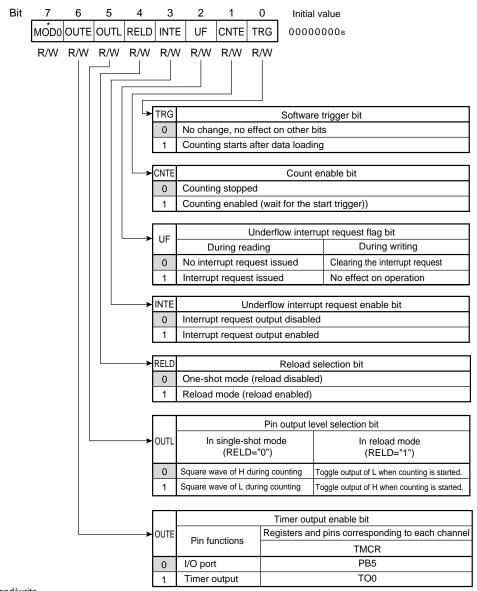

| 12.4.3 16-bit Timer Register (TMR)                                              | 233 |

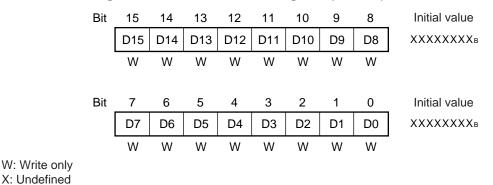

| 12.4.4 16-bit Reload Register (TMRLR)                                           | 234 |

| 12.5 16-Bit Reload Timer Interrupts                                             | 235 |

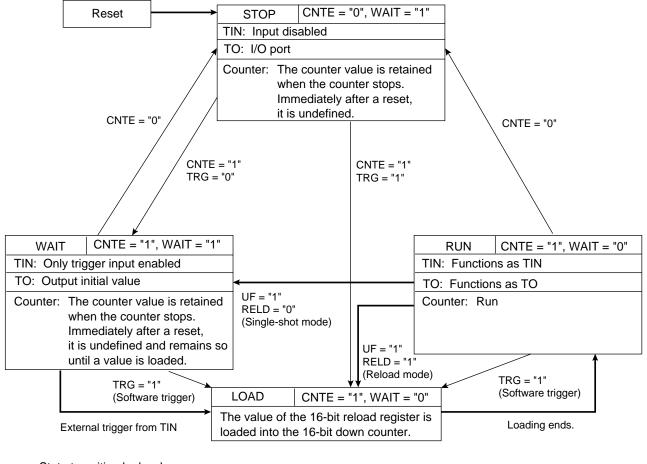

| 12.6 Operation of the 16-Bit Reload Timer                                       | 236 |

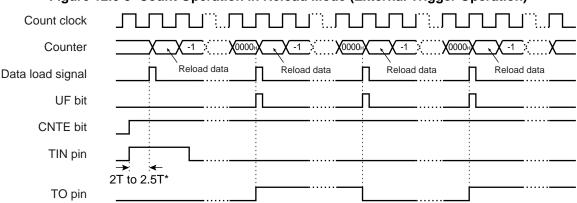

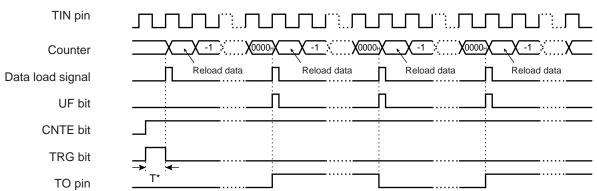

| 12.6.1 Internal Clock Mode (Reload Mode)                                        | 238 |

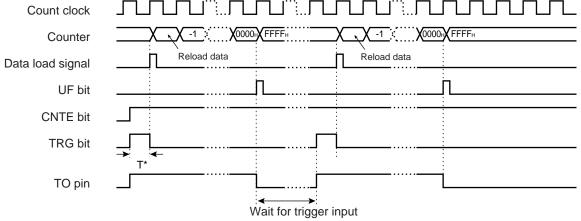

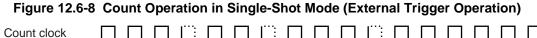

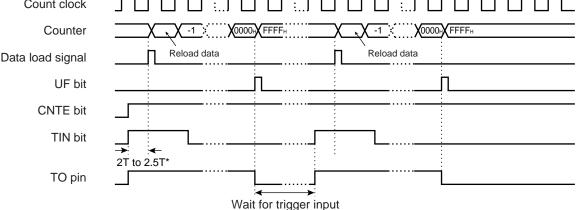

| 12.6.2 Internal Clock Mode (Single-shot Mode)                                   | 240 |

| 12.6.3 Event Count Mode                                                         | 242 |

| 12.7 Usage Notes on the 16-Bit Reload Timer                                     | 244 |

| CHAPTER 13 16-BIT I/O TIMER                                                     | 245 |

| 13.1 Overview of the 16-Bit I/O Timer                                           | 246 |

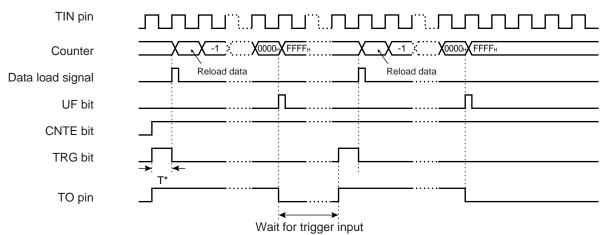

| 13.2 16-Bit I/O Timer Block Diagram                                             | 247 |

| 13.3 16-Bit I/O Timer Registers                                                 | 248 |

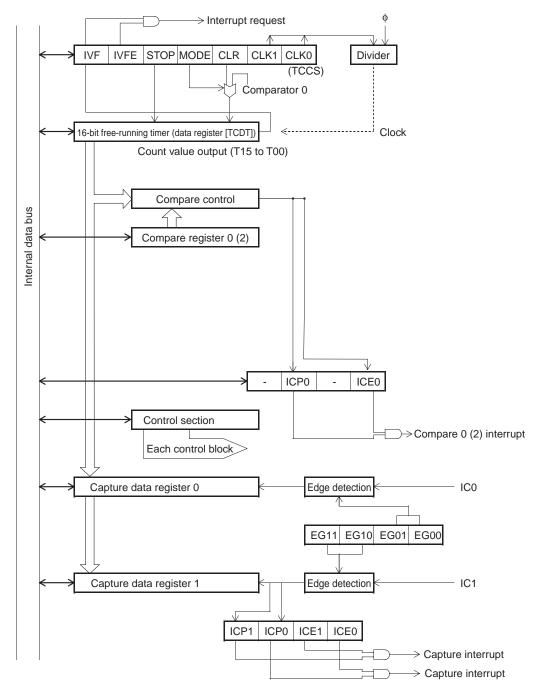

| 13.3.1 16-Bit Free-Running Timer Registers (TCDT and TCCS)                      | 249 |

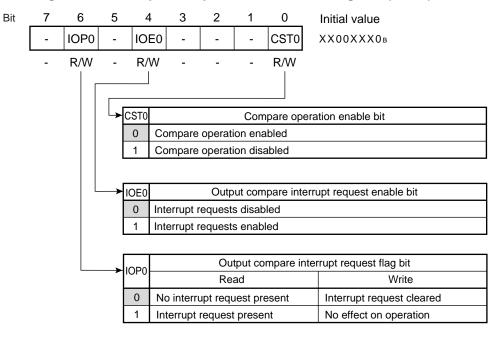

| 13.3.2 Output Compare Registers (OCCP0 and OCS0)                                | 252 |

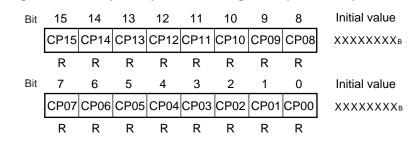

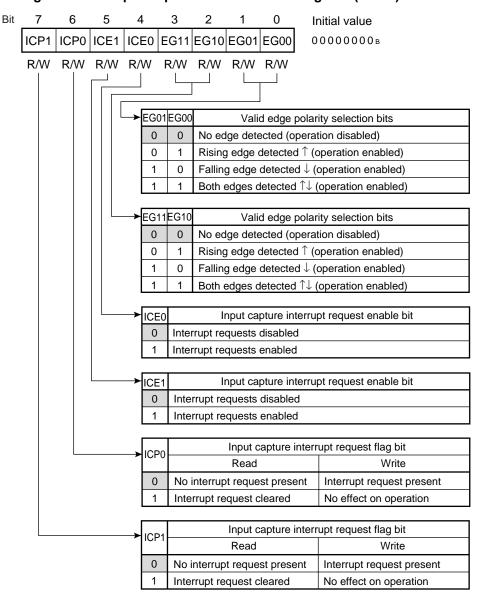

| 13.3.3 Input Capture Registers (IPC0/IPC1 and ICSSS0)                           | 255 |

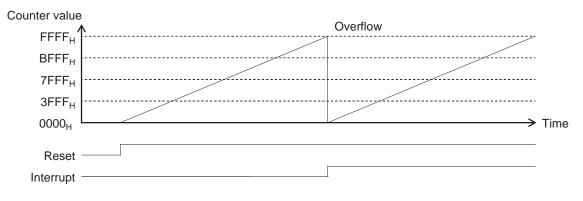

| 13.4 16-Bit Free-Running Timer Operations                                       | 258 |

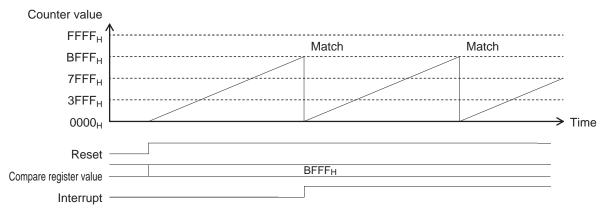

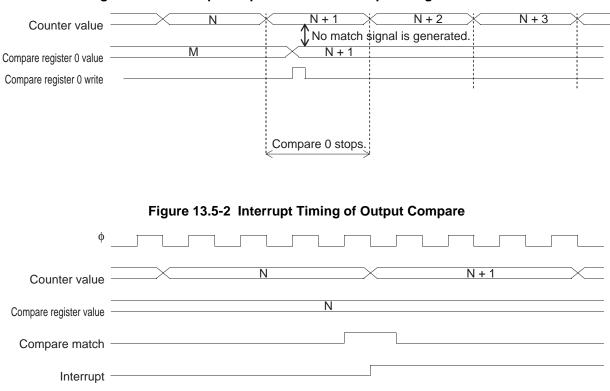

| 13.5 16-Bit Output Compare Operations                                           | 260 |

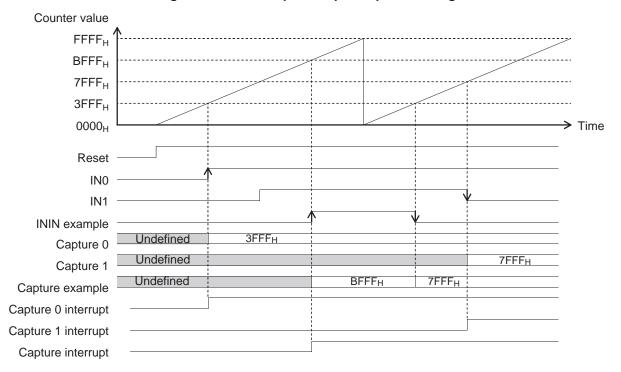

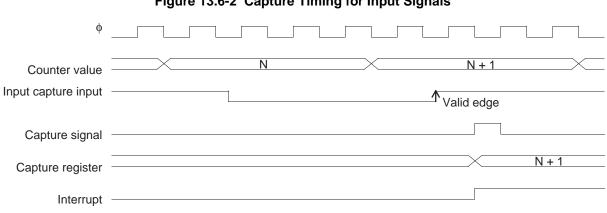

| 13.6 16-Bit Input Capture Operations                                            | 261 |

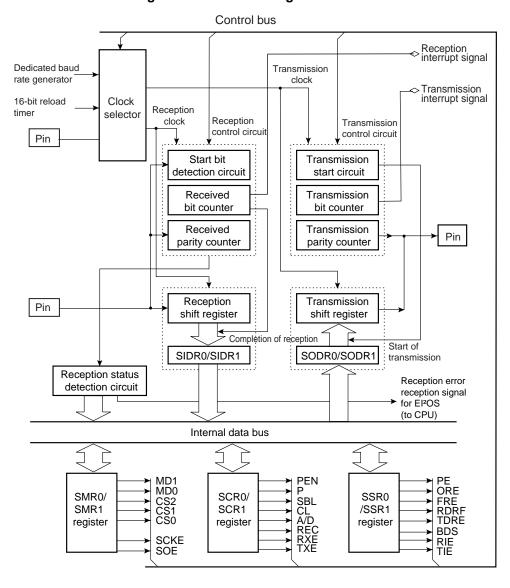

| CHAPTER 14 UART                                                                 | 263 |

| 14.1 Overview of UART                                                           |     |

| 14.2 Configuration of UART                                                      | 266 |

| 14.3 UART Pins                                                                  |     |

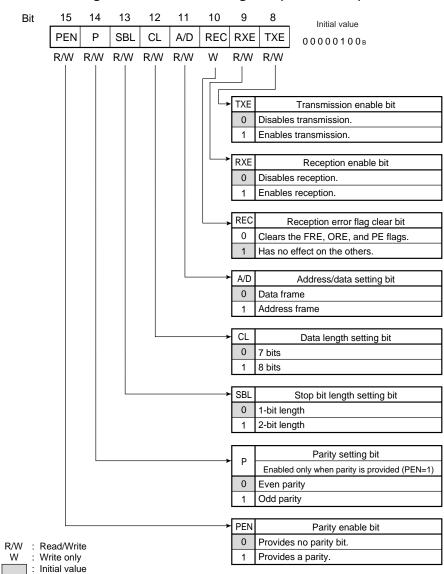

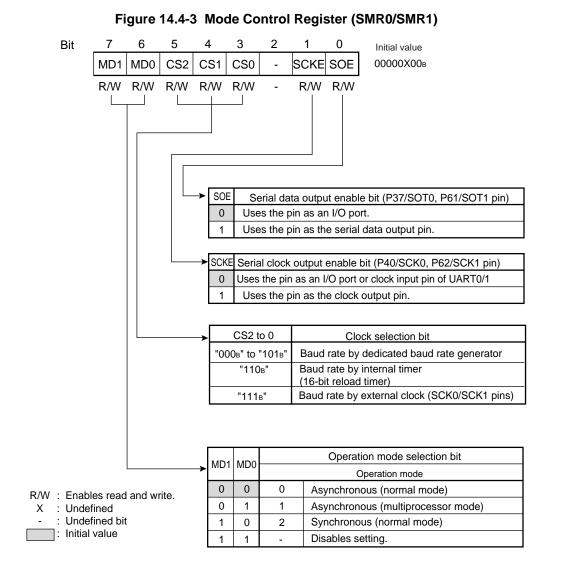

| 14.4 UART Registers                                                             | 271 |

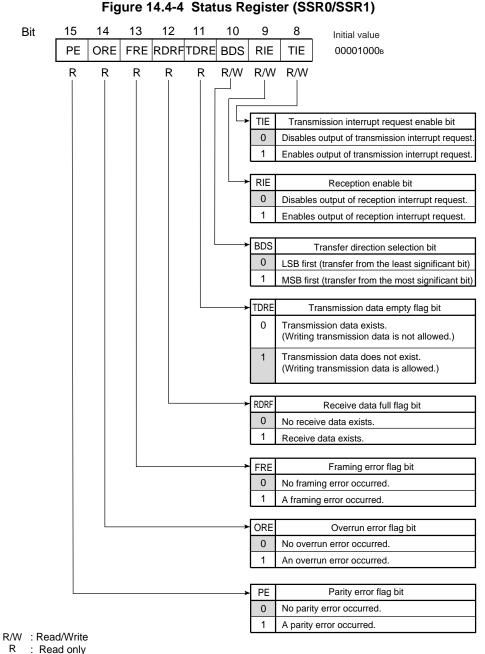

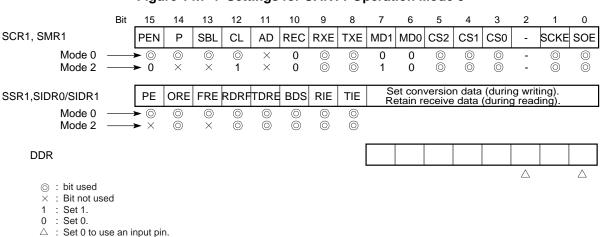

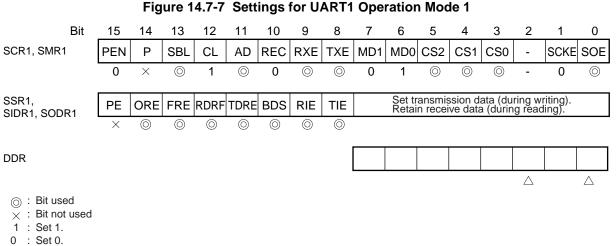

| 14.4.1 Control Register (SCR0/SCR1)                                             | 272 |

| 14.4.2 Mode Register (SMR0/SMR1)                                                | 275 |

| 14.4.3 Status Register (SSR0/SSR1)                                              |     |

| 14.4.4 Input Data Register (SIDR0/SIDR1) and Output Data Register (SODR0/SODR1) | 280 |

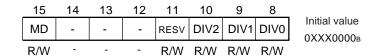

| 14.4.5 Communication Prescaler Control Register (CDCR0/CDCR1)                   | 282 |

| 14.5 UART Interrupts                                                            | 284 |

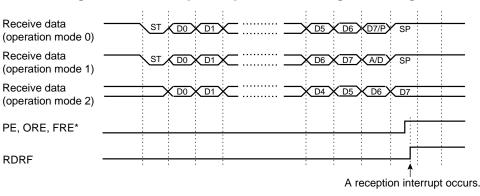

| 14.5.1 Reception Interrupt Generation and Flag Set Timing                       | 286 |

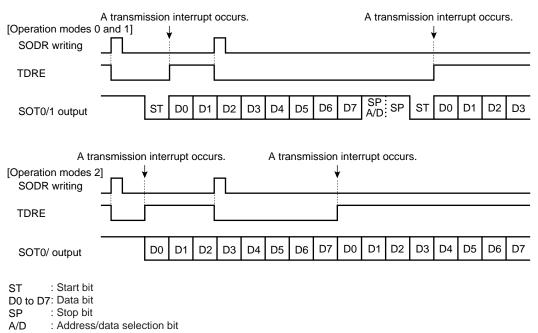

| 14.5.2 Transmission Interrupt Generation and Flag Set Timing                    | 288 |

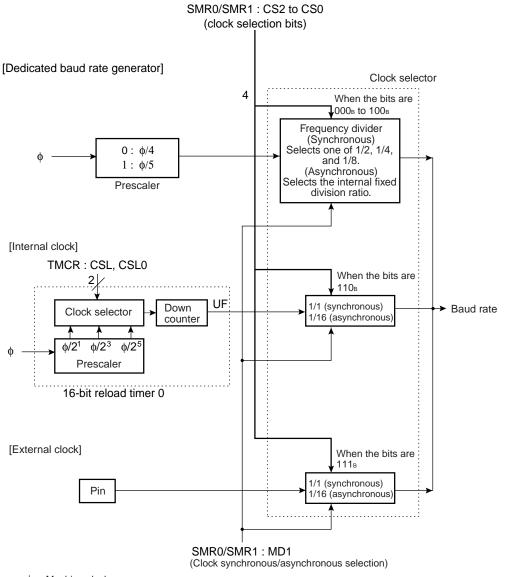

| 14.6 UART Baud Rates                                                            | 289 |

| 14.6.1 Baud Rates Determined Using the Dedicated Baud Rate Generator                                                                                                | 291                                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

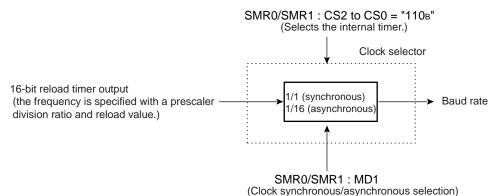

| 14.6.2 Baud Rates Determined Using the Internal Timer                                                                                                               | 293                                                  |

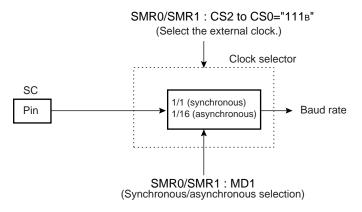

| 14.6.3 Baud Rates Determined Using the External Clock                                                                                                               | 295                                                  |

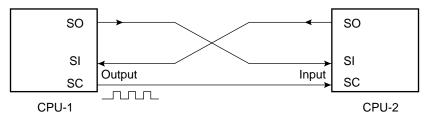

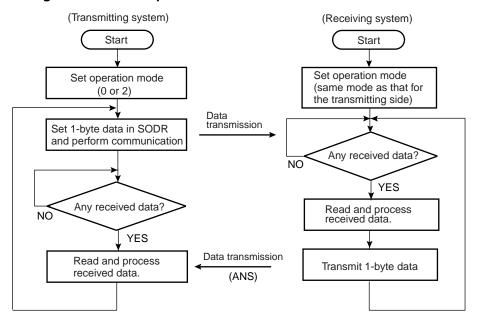

| 14.7 Operation of UART                                                                                                                                              |                                                      |

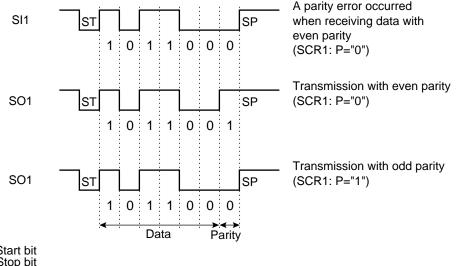

| 14.7.1 Operation in Asynchronous Mode (Operation Modes 0 and 1)                                                                                                     |                                                      |

| 14.7.2 Operation in Synchronous Mode (Operation Mode 2)                                                                                                             |                                                      |

| 14.7.3 Bidirectional Communication Function (Normal Mode)                                                                                                           |                                                      |

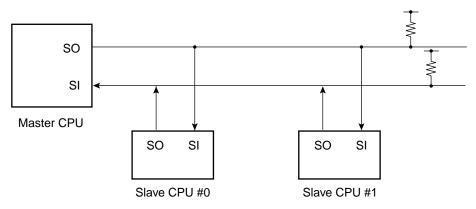

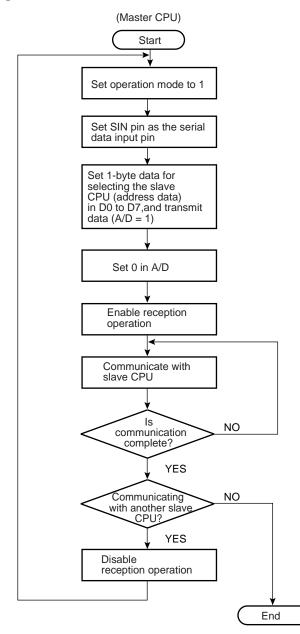

| 14.7.4 Master-slave Communication Function (Multiprocessor Mode)                                                                                                    |                                                      |

| 14.8 Notes on Using UART                                                                                                                                            | 307                                                  |

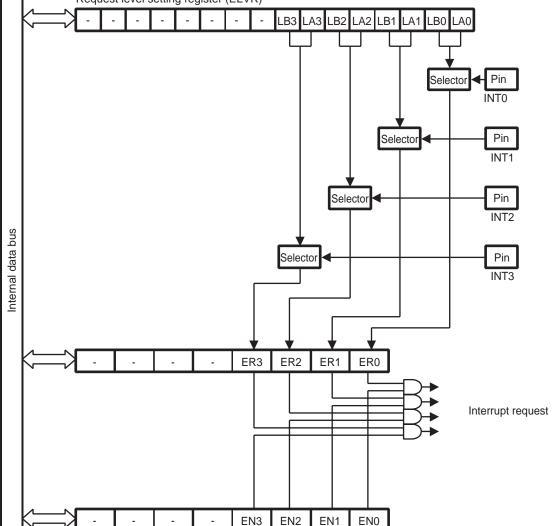

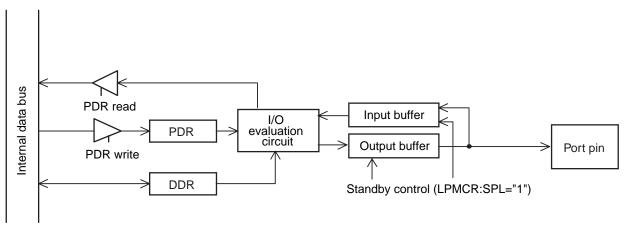

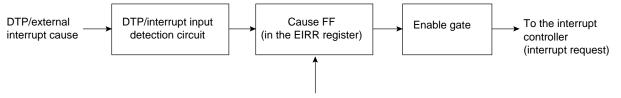

| CHAPTER 15 DTP/EXTERNAL INTERRUPT CIRCUIT                                                                                                                           | 200                                                  |

| 15.1 Overview of the DTP/External Interrupt Circuit                                                                                                                 |                                                      |

| 15.2 Configuration of the DTP/External Interrupt Circuit                                                                                                            |                                                      |

| 15.3 DTP/External Interrupt Circuit Pins                                                                                                                            |                                                      |

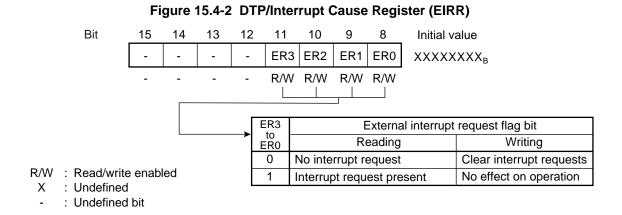

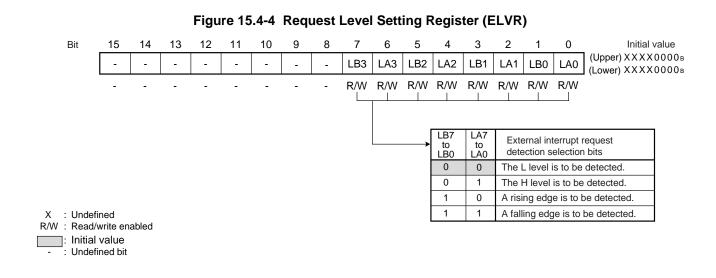

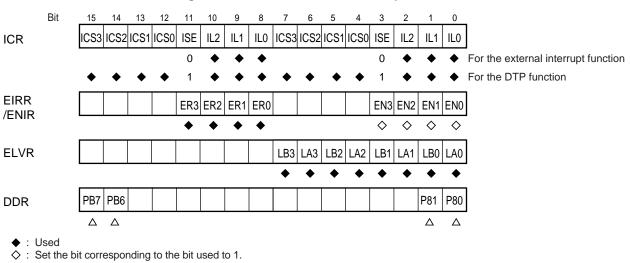

| 15.4 DTP/External Interrupt Circuit Registers                                                                                                                       |                                                      |

| 15.4 DTP/External Interrupt Circuit Registers                                                                                                                       |                                                      |

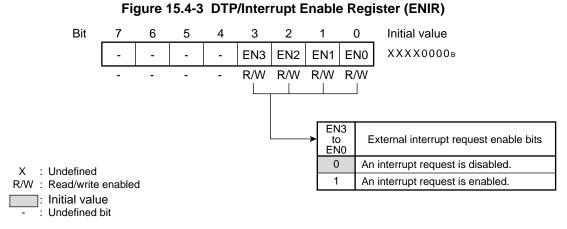

| 15.4.2 DTP/Interrupt Enable Register (ENIR)                                                                                                                         |                                                      |

| 15.4.2 DTP/Interrupt Enable Register (ENIR)                                                                                                                         |                                                      |

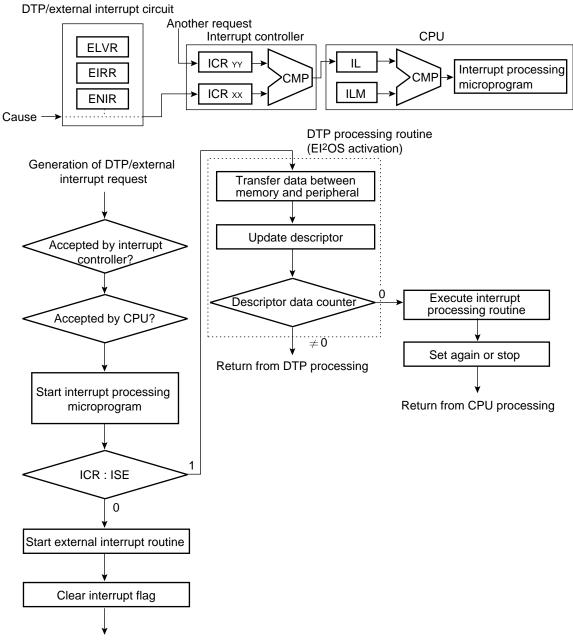

| 15.5 Operation of the DTP/External Interrupt Circuit                                                                                                                |                                                      |

| 15.5 Operation of the DTP/External Interrupt Circuit                                                                                                                |                                                      |

| 15.5.2 DTP Function                                                                                                                                                 |                                                      |

| 15.6 Usage Notes on the DTP/External Interrupt Circuit                                                                                                              | -                                                    |

|                                                                                                                                                                     |                                                      |

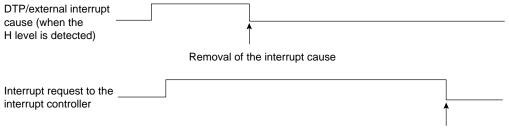

| CHAPTER 16 I <sup>2</sup> C INTERFACE                                                                                                                               | 331                                                  |

| 16.1 Overview of the I <sup>2</sup> C Interface                                                                                                                     |                                                      |

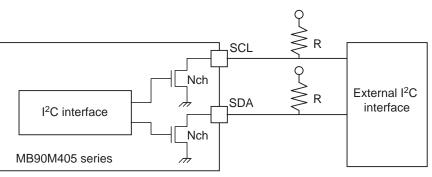

| 16.2 Block Diagram and Configuration of the I <sup>2</sup> C Interface                                                                                              |                                                      |

| 16.3 I <sup>2</sup> C Interface Registers                                                                                                                           | 335                                                  |

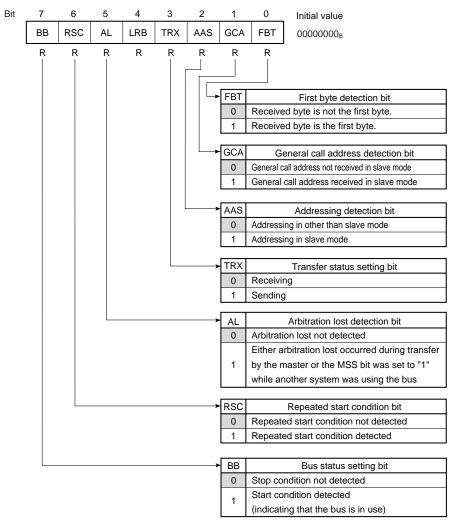

| 16.3.1 I <sup>2</sup> C Status Register (IBSR)                                                                                                                      | 336                                                  |

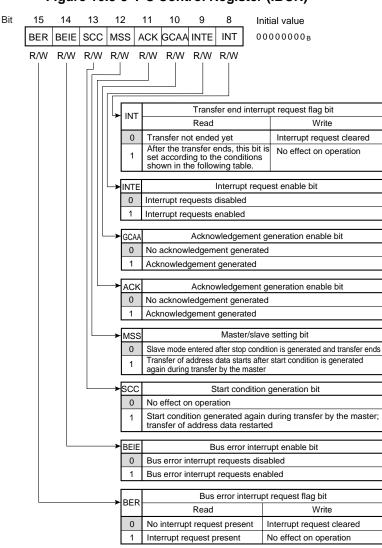

| 16.3.2 I <sup>2</sup> C Control Register (IBCR)                                                                                                                     | 338                                                  |

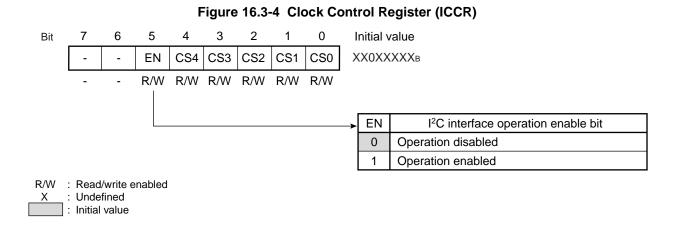

| 16.3.3 I <sup>2</sup> C Clock Control Register (ICCR)                                                                                                               | 341                                                  |

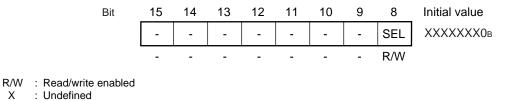

| 16.3.4 I <sup>2</sup> C Address Register (IADR)                                                                                                                     |                                                      |

| 16.3.5 I <sup>2</sup> C Data Register (IDAR)                                                                                                                        |                                                      |

| 16.3.6 I <sup>2</sup> C Port Select Register (ISEL)                                                                                                                 |                                                      |

| 16.4 Operation of the I <sup>2</sup> C Interface                                                                                                                    |                                                      |

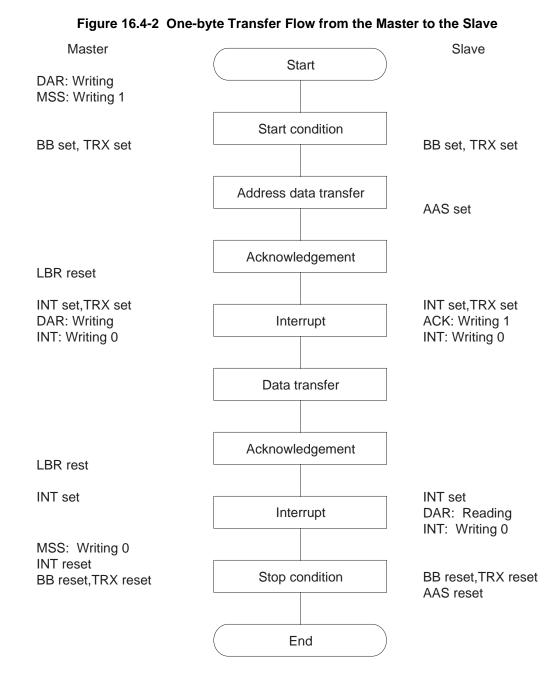

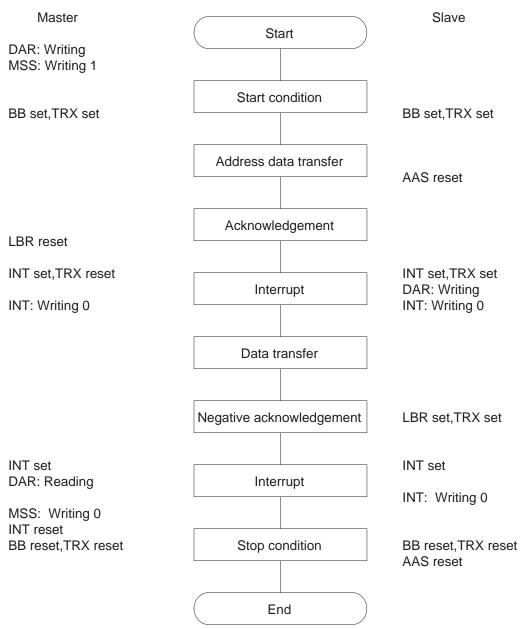

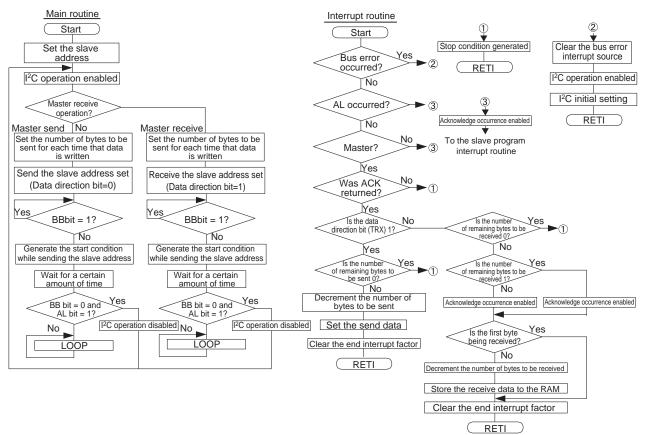

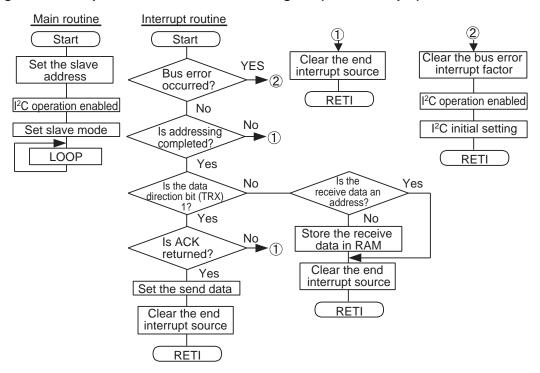

| 16.4.1 Transfer Flow of the I <sup>2</sup> C Interface                                                                                                              | 349                                                  |

| 16.4.2 Mode Flow of the I <sup>2</sup> C Interface                                                                                                                  | 351                                                  |

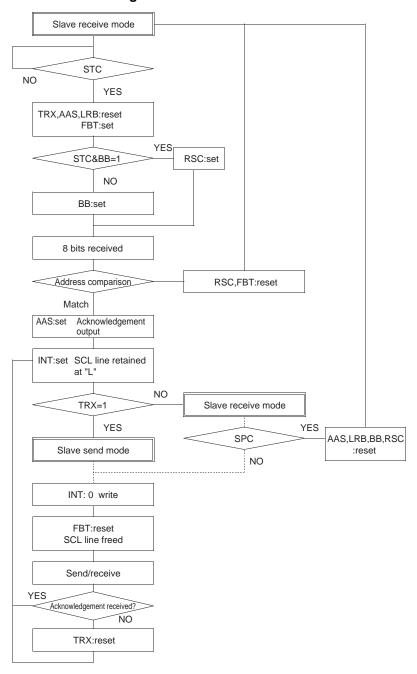

| 16.4.3 Operation Flow of the I <sup>2</sup> C Interface                                                                                                             | 352                                                  |

| •                                                                                                                                                                   |                                                      |

| ·                                                                                                                                                                   |                                                      |

|                                                                                                                                                                     |                                                      |

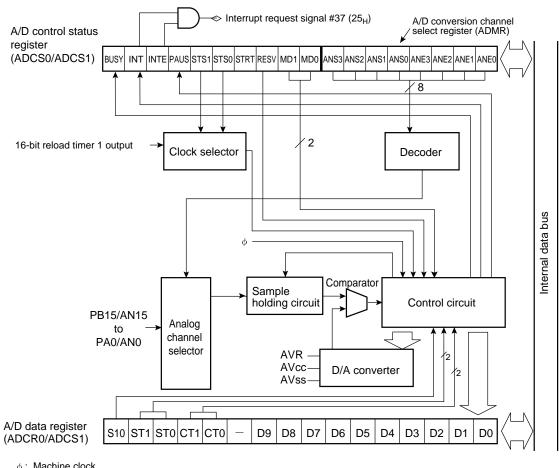

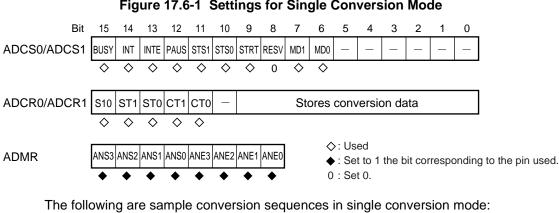

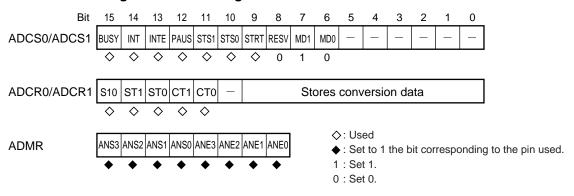

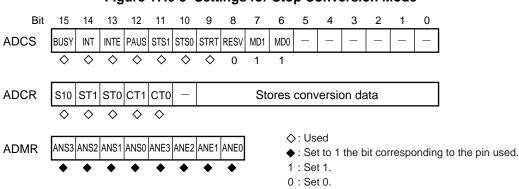

| 17.1 Overview of the 8/10-Bit A/D Converter                                                                                                                         | 356                                                  |

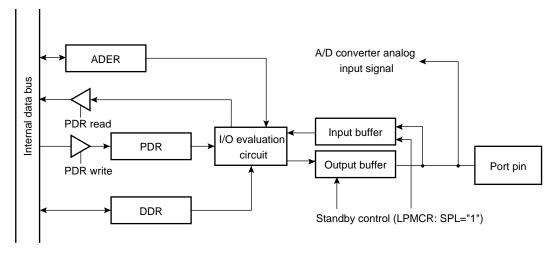

| <ul><li>17.1 Overview of the 8/10-Bit A/D Converter</li><li>17.2 Configuration of the 8/10-Bit A/D Converter</li></ul>                                              | 356<br>358                                           |

| <ul> <li>17.1 Overview of the 8/10-Bit A/D Converter</li> <li>17.2 Configuration of the 8/10-Bit A/D Converter</li> <li>17.3 8/10-Bit A/D Converter Pins</li> </ul> |                                                      |

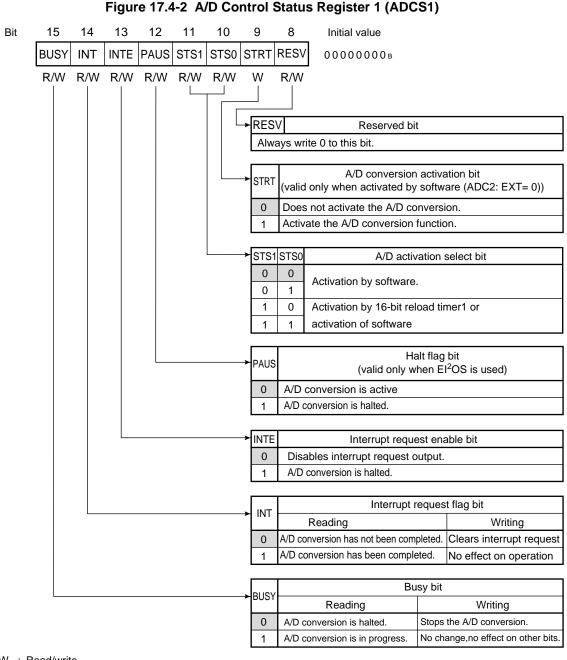

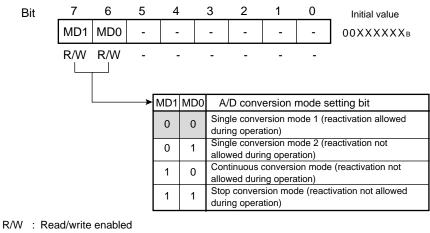

| <ul> <li>17.1 Overview of the 8/10-Bit A/D Converter</li></ul>                                                                                                      |                                                      |

| <ul> <li>17.1 Overview of the 8/10-Bit A/D Converter</li></ul>                                                                                                      |                                                      |

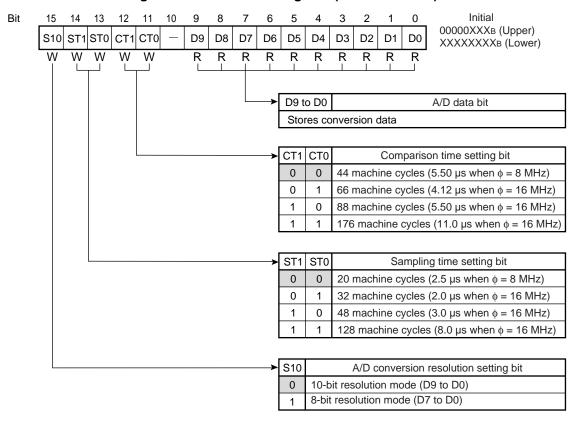

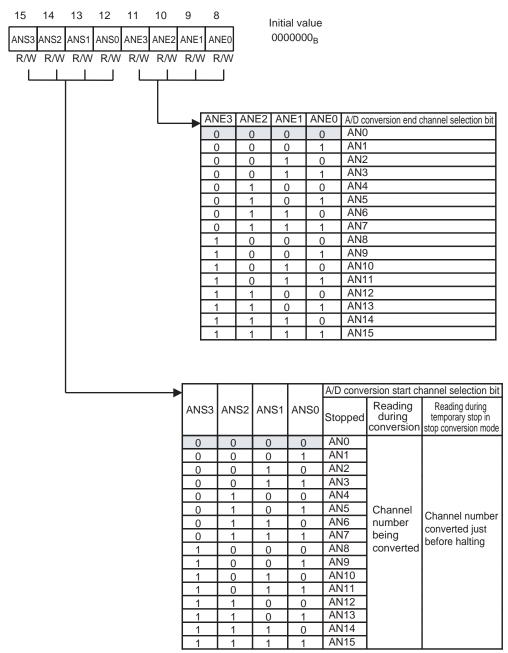

| <ul> <li>17.1 Overview of the 8/10-Bit A/D Converter</li></ul>                                                                                                      |                                                      |

| <ul> <li>17.1 Overview of the 8/10-Bit A/D Converter</li></ul>                                                                                                      | 356<br>358<br>360<br>362<br>363<br>365<br>365<br>367 |

| <ul> <li>17.2 Configuration of the 8/10-Bit A/D Converter</li> <li>17.3 8/10-Bit A/D Converter Pins</li> <li>17.4 8/10-Bit A/D Converter Registers</li></ul>        |                                                      |

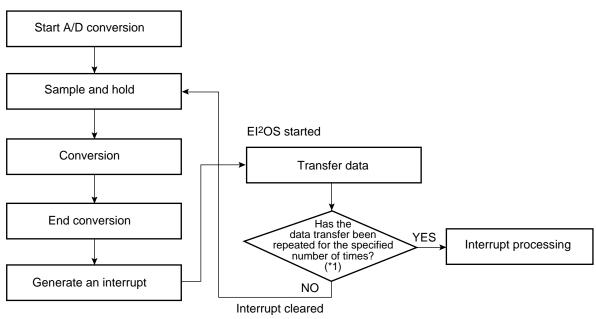

| 17.6  | Operation of the 8/10-Bit A/D Converter                                                               | 372 |

|-------|-------------------------------------------------------------------------------------------------------|-----|

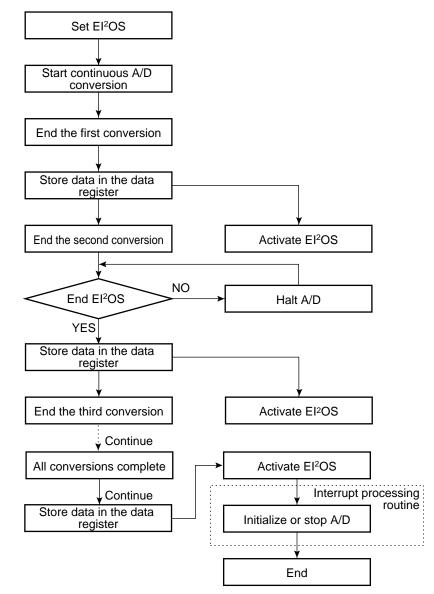

|       | 6.1 Conversion Using El <sup>2</sup> OS                                                               |     |

| 17.6  | 6.2 A/D Conversion Data Protection Function                                                           | 376 |

| 17.7  | Usage Notes on the 8/10-Bit A/D Converter                                                             | 378 |

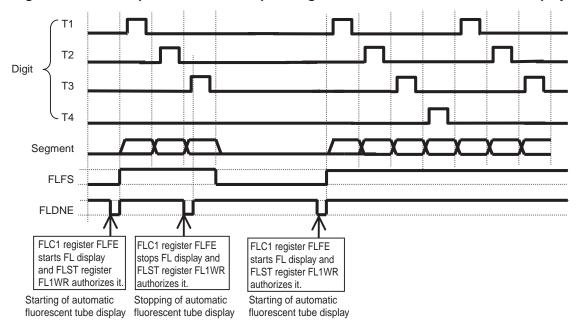

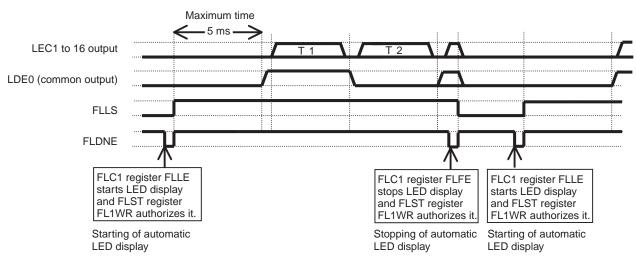

| CHAP  | TER 18 FL CONTROL CIRCUIT                                                                             | 379 |

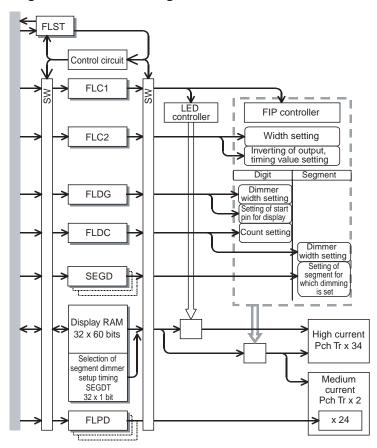

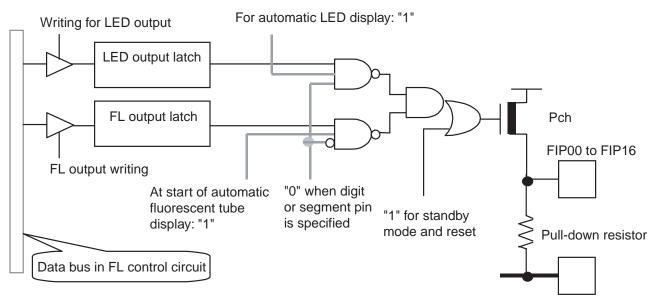

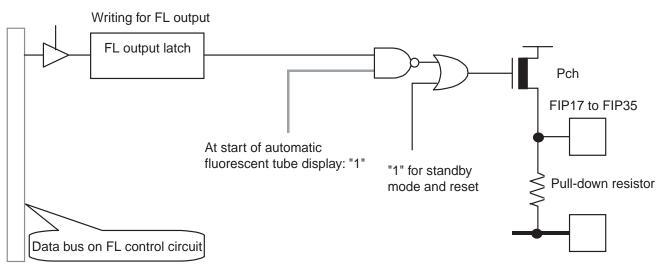

| 18.1  | Overview of FL Control Circuit                                                                        | 380 |

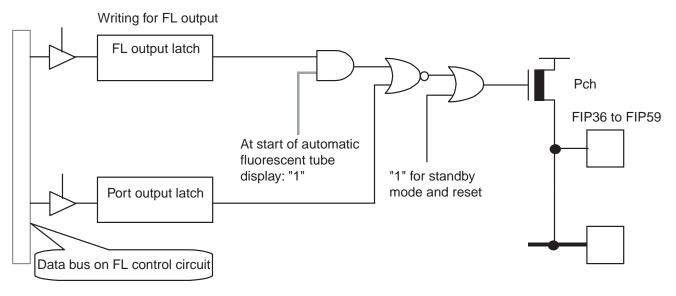

| 18.2  | Configuration of FL Control Circuit                                                                   | 382 |

| 18.3  | FL Control Circuit Pins                                                                               | 383 |

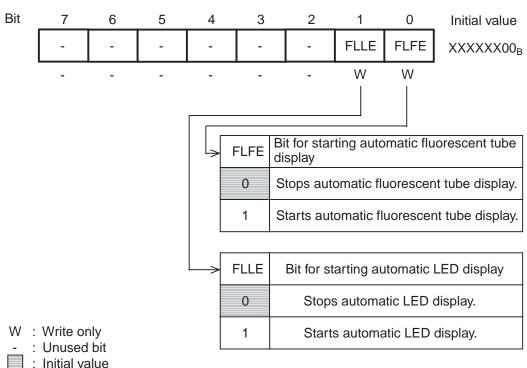

| 18.3  | 3.1 Display Control Register 1 (FLC1)                                                                 | 385 |

| 18.3  | 3.2 Display Control Register 2 (FLC2)                                                                 | 387 |

| 18.3  | 3.3 Digit Setting Register (FLDG)                                                                     | 389 |

|       | 3.4 Digit Count Register (FLDC)                                                                       |     |

| 18.3  | 3.5 Port Register (FLPD)                                                                              | 393 |

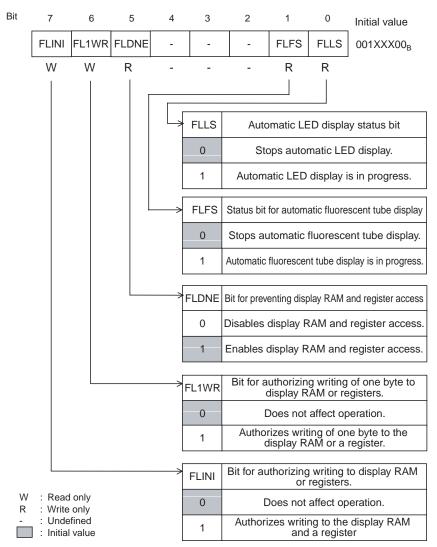

|       | 3.6 Status/Authorization Register (FLST)                                                              |     |

| 18.3  | 3.7 Display RAM                                                                                       | 396 |

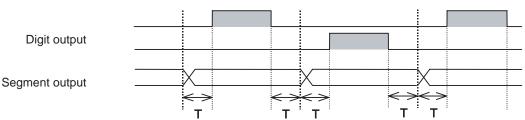

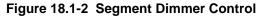

| 18.3  | 3.8 Segment Dimmer Setting Register (SEGD)                                                            | 397 |

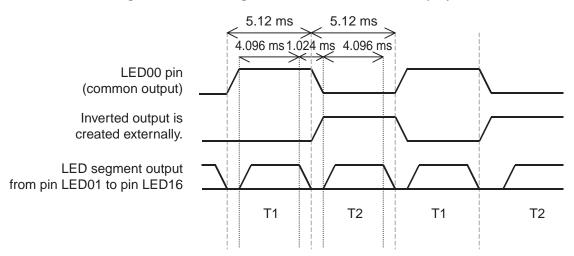

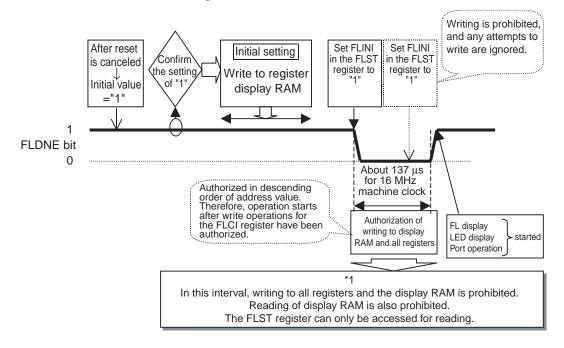

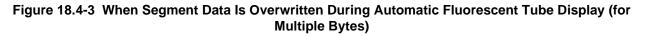

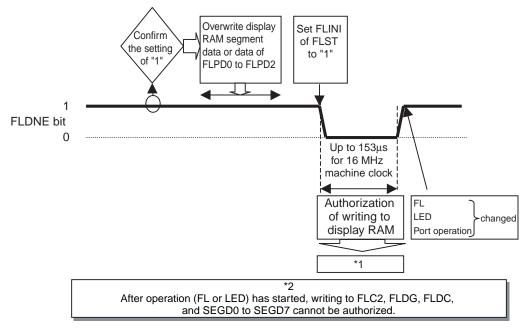

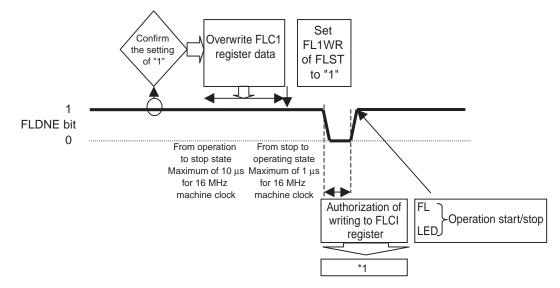

| 18.4  | FL Control Circuit Operation                                                                          | 398 |

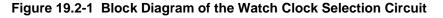

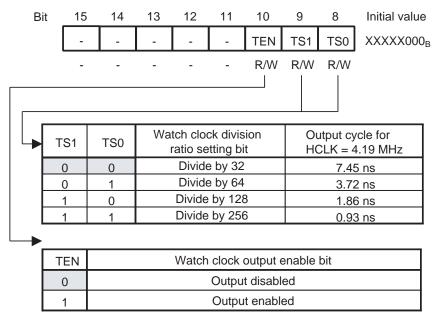

| СНАРТ | TER 19 WATCH CLOCK OUTPUT                                                                             | 403 |

|       | Overview of the Watch Clock Output Circuit                                                            |     |

|       | Configuration of the Watch Clock Output Circuit                                                       |     |

|       | Watch Clock Output Control Register (TMCS)                                                            |     |

| 10.0  |                                                                                                       | 400 |

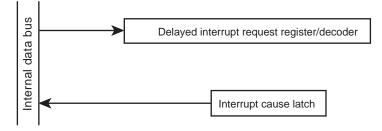

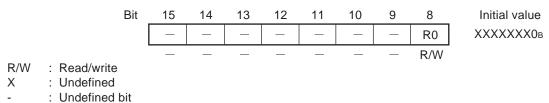

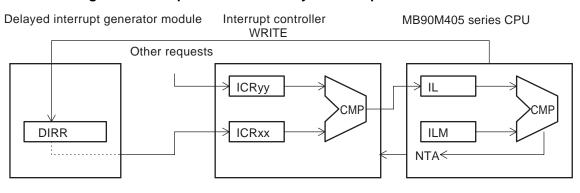

| CHAP  | TER 20         DELAYED INTERRUPT GENERATOR MODULE                                                     |     |

| 20.1  |                                                                                                       |     |

| 20.2  | Delayed Interrupt Cause/Cancel Register (DIRR)                                                        |     |

|       | Operation of the Delayed Interrupt Generator Module                                                   |     |

| 20.4  | Precautions to Follow when Using the Delayed Interrupt Generator Module                               | 411 |

| CHAPT | FER 21 ADDRESS MATCH DETECTION FUNCTION                                                               | 413 |

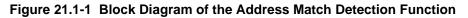

| 21.1  | Overview of the Address Match Detection Function                                                      | 414 |

| 21.2  | Registers of the Address Match Detection Function                                                     | 415 |

| 21.2  | 2.1 Program Address Detection Register for Upper, Middle, and Lower Parts of Address<br>(PADR0/PADR1) | 416 |

| 21 2  | 2.2 Program Address Detection Control Status Register (PACSR)                                         |     |

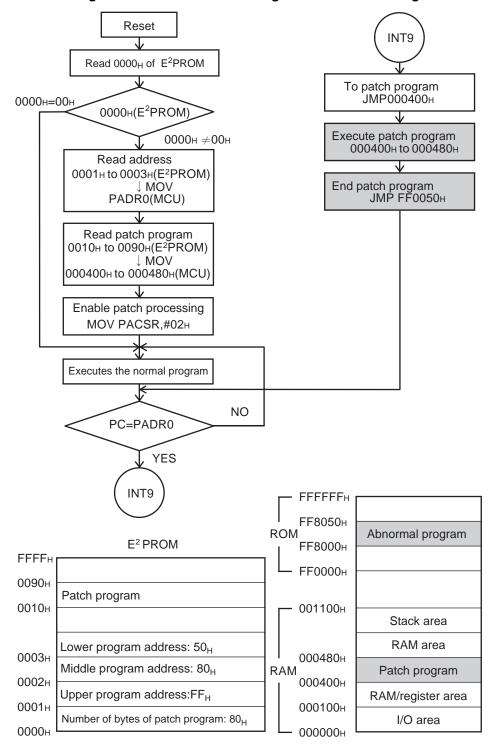

|       | Operation of the Address Match Detection Function                                                     |     |

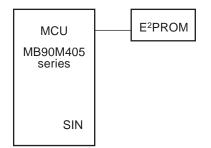

|       | Example of Using the Address Match Detection Function                                                 |     |

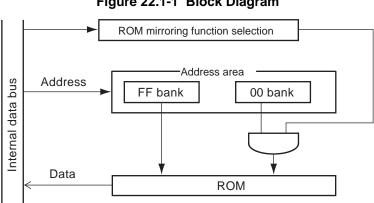

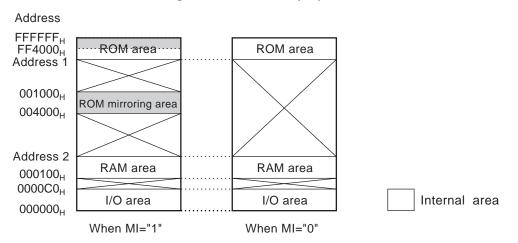

| СНАРТ | TER 22 ROM MIRRORING FUNCTION SELECTION MODULE                                                        | 123 |

| 22.1  | Overview of the ROM Mirroring Function Selection Module                                               |     |

|       | •                                                                                                     |     |

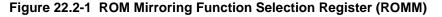

| 22.2  | ROM Mirroring Function Selection Register (ROMM)                                                      | 425 |

| CHAP  | TER 23 1M-BIT FLASH MEMORY                                                                            |     |

| 23.1  | Overview of the 1M-Bit Flash Memory                                                                   |     |

| 23.2  | Registers and Sector Configuration of the Flash Memory                                                |     |

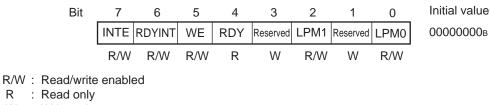

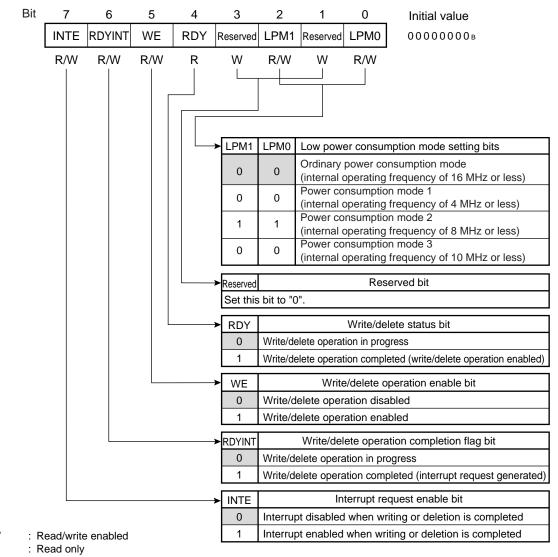

| 23.3  | Flash Memory Control Status Register (FMCS)                                                           |     |

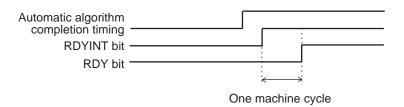

| 23.4  | Starting the Automatic Algorithm of the Flash Memory                                                  | 433 |

| 23.5 De | etailed Description of Flash Memory Writing and Deletion       | . 434 |

|---------|----------------------------------------------------------------|-------|

| 23.5.1  | Placing the Flash Memory in Read/Reset Status                  | . 435 |

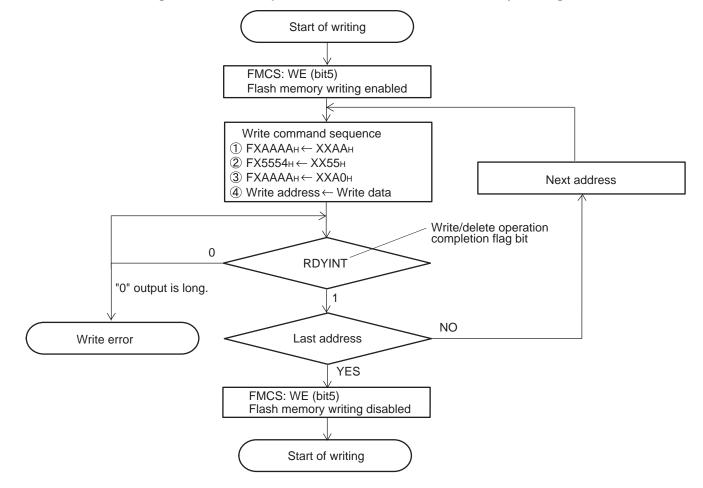

| 23.5.2  | Writing Data to the Flash Memory                               | . 436 |

| 23.5.3  | Deleting All Data Items from the Flash Memory (Chip Deletion)  | . 438 |

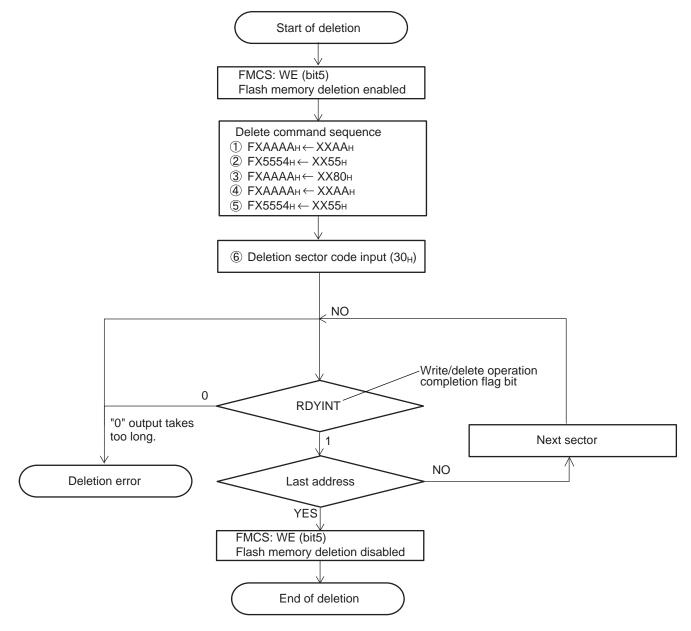

| 23.5.4  | Deleting a Data Item from the Flash Memory (Sector Deletion)   | . 439 |

| 23.5.5  | Temporarily Stopping Deletion of Sectors from the Flash Memory | . 441 |

| 23.5.6  | Resuming Flash Memory Sector Deletion                          | . 442 |

|         |                                                                |       |

# CHAPTER 24 EXAMPLE OF MB90MF408/MF408A SERIAL PROGRAMMING

|       |                                                                                                            | 443 |

|-------|------------------------------------------------------------------------------------------------------------|-----|

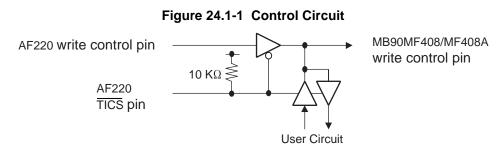

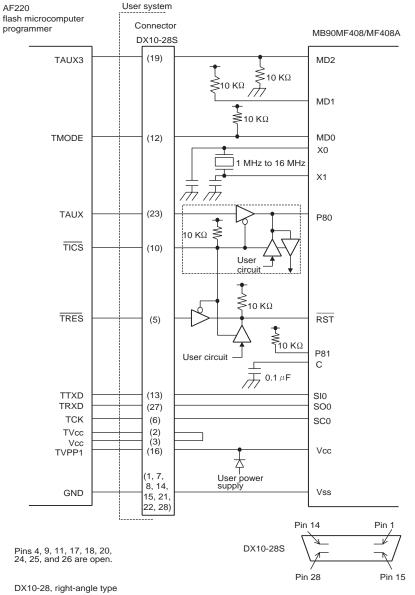

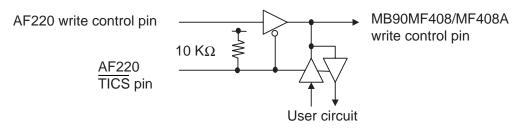

| 24.1  | Standard Configuration for Serial Programming Connection to MB90MF408/MF408A                               | 444 |

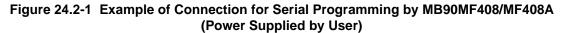

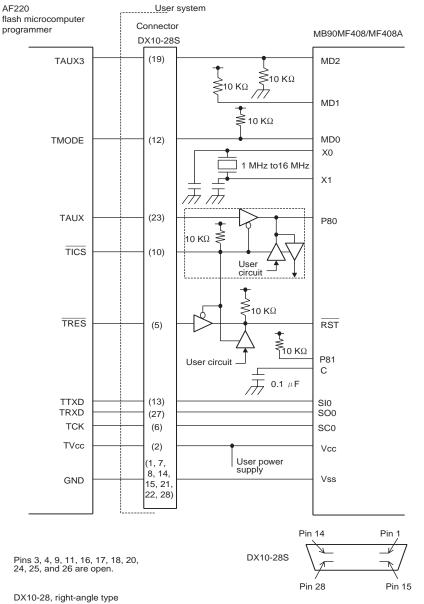

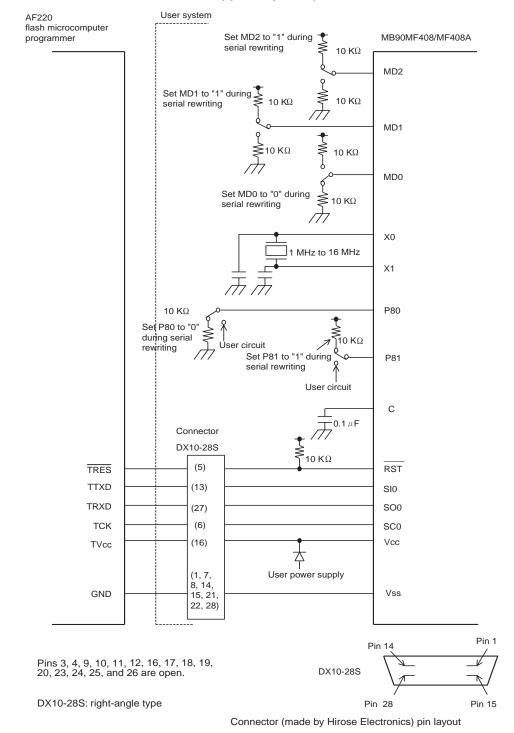

| 24.2  | Example of Connection for Serial Programming (Power Supplied by User)                                      | 446 |

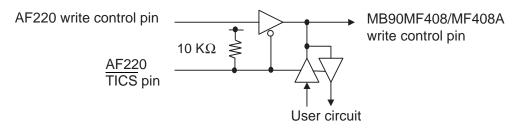

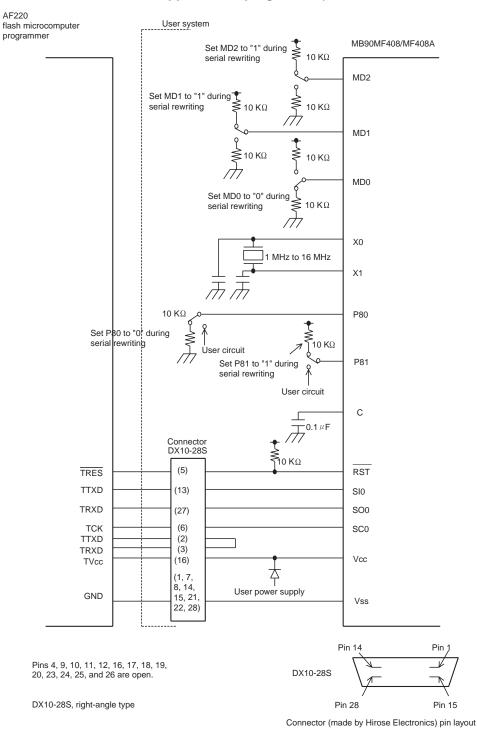

| 24.3  | Example of Connection for Serial Programming (When Power Supplied from Programmer)                         | 448 |

| 24.4  | Example of Minimum Connection with Flash Microcomputer Programmer<br>(When Power Supplied from User)       | 450 |

| 24.5  | Example of Minimum Connection with Flash Microcomputer Programmer<br>(When Power Supplied from Programmer) | 452 |

| APPEN |                                                                                                            | 455 |

| APPE  | NDIX A I/O Map                                                                                             | 456 |

| APPE  | NDIX B Instructions                                                                                        | 463 |

| B.1   | Instruction Types                                                                                          | 464 |

| B.2   | Addressing                                                                                                 | 465 |

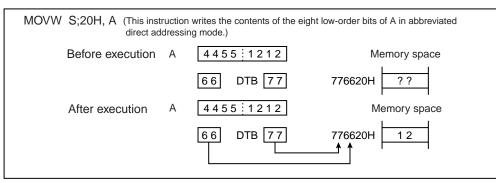

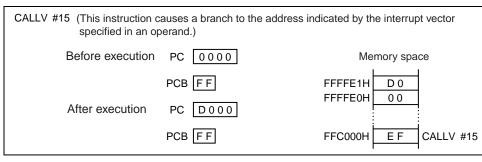

| B.3   | Direct Addressing                                                                                          | 467 |

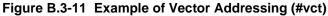

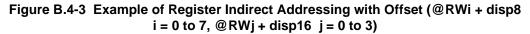

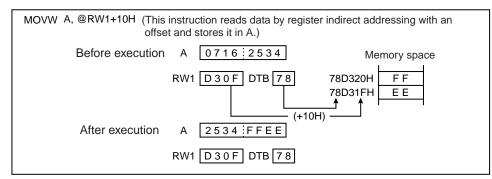

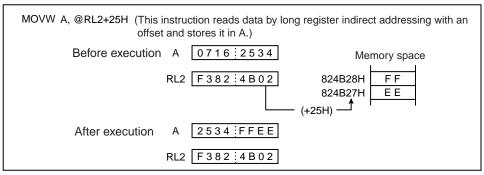

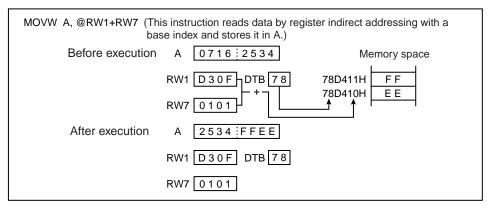

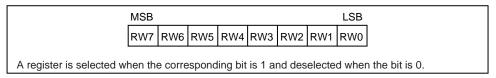

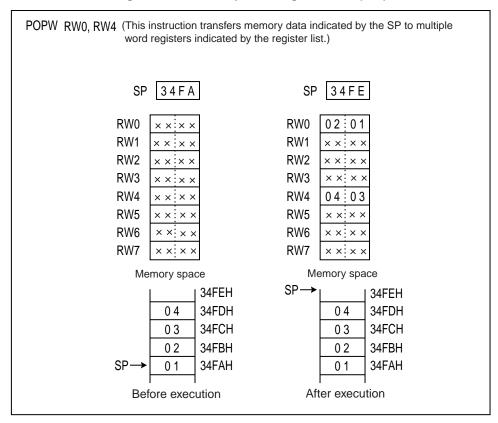

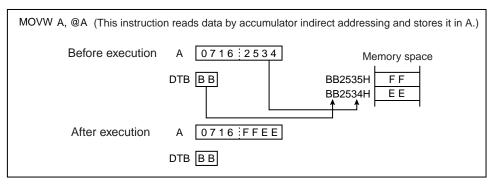

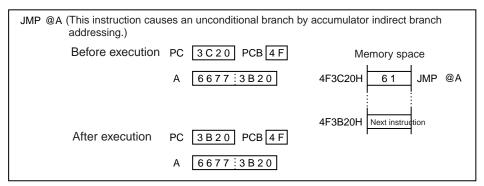

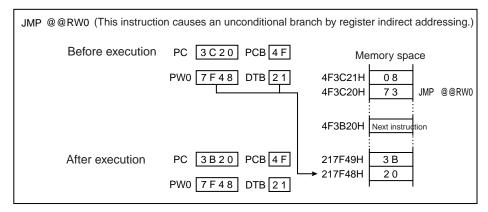

| B.4   | Indirect Addressing                                                                                        | 472 |

| B.5   | Execution Cycle Count                                                                                      | 478 |

| B.6   | Effective Address Field                                                                                    | 481 |

| B.7   | How to Read the Instruction List                                                                           | 482 |

| B.8   | F <sup>2</sup> MC-16LX Instruction List                                                                    | 485 |

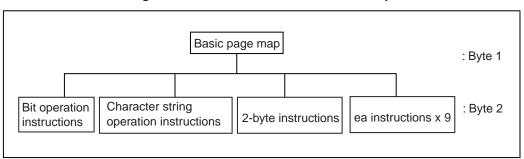

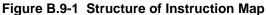

| B.9   | Instruction Map                                                                                            | 499 |

| APPE  | NDIX C Index of Registers                                                                                  | 521 |

| APPE  | NDIX D Index of Pin Functions                                                                              | 525 |

| INDEX | 529 |

|-------|-----|

|-------|-----|

# CHAPTER 1 OVERVIEW

# This chapter summarizes the features and basic specifications of the MB90M405 series of microcontrollers.

- 1.1 "Features"

- 1.2 "Product Lineup"

- 1.3 "Block Diagram"

- 1.4 "Package Dimensions"

- 1.5 "Pin Assignments"

- 1.6 "Pin Functions"

- 1.7 "I/O Circuit Types"

- 1.8 "Notes on Handling Devices"

- 1.9 "Clock Supply Map"

- 1.10 "Low Power Consumption Mode"

### 1.1 Features

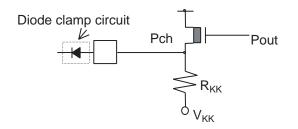

The MB90M405 series of general-purpose 16-bit microcontrollers was developed for applications that require control of fluorescent display tube panels. The microcontrollers in this series have 60 high dielectric output pins for fluorescent display control.

The instruction set inherits the AT architecture of the  $F^2MC-8L$  and  $F^2MC-16L$ , and has additional instructions that support the C language. In addition, the instruction set supports extended addressing mode, enhanced signed multiply/divide instructions, and more powerful bit manipulation instructions. The microcontrollers also have a 32bit accumulator that enables processing of long-word data.

#### ■ MB90M405 Series Features

- O Clocks

- Built-in PLL clock multiplier circuit

- Source oscillation

Main clock that divides the source oscillation by two

PLL clock that multiplies the source oscillation by 1 to 4 (2.1 to 16.8 MHz when the source oscillation is 4.2 MHz), which can be configured from the machine clock

- Minimum instruction execution time: 59.5 ns (when the source oscillation is 4.2 MHz, the PLL clock is multiplied by 4, and  $V_{CC}$  is 3 V)

- The source oscillation can be divided by 16, 32, 64, or 128 for external clock output.

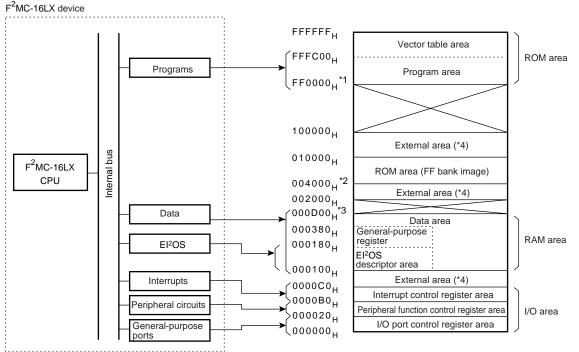

#### O Maximum memory address space: 16 M bytes

24-bit addressing can also be used.

#### O Optimum instruction set for controller applications

- Many data types (bit, byte, and long word) can be handled.

- As many as 23 addressing modes are available.

- Efficient code (compiler)

- Enhanced high-precision arithmetic operations with a 32-bit accumulator

- Enhanced signed multiply/divide instructions and RETI instruction function

#### O Instruction set supporting the C language and multitasking

- System stack pointer

- · Instruction set symmetry and barrel shift instructions

- Program patch function (two-address pointer)

#### **O** Improved execution speed

The built-in 4-byte instruction queue prereads instructions to improve execution speed.

#### O Interrupt function

- Eight programmable priority levels can be set.

- An enhanced interrupt function with 32 interrupt causes is supported.

#### **O** Data transfer function

O Extended intelligent I/O service function: Up to 16 channels can be set.

#### O Low-power mode

- Sleep mode (in which the CPU operating clock stops)

- Timebase timer mode (in which only the source oscillation clock and Timebase timer are active)

- Stop mode (in which the source oscillation stops)

- CPU intermittent operation mode (in which the CPU operates at every specified cycle)

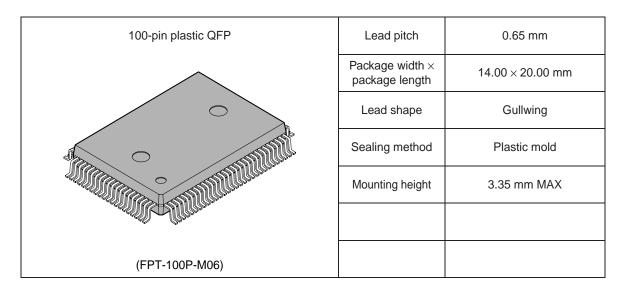

#### O Package

• QFP-100 (FPT-100P-M06: 0.65 mm pin pitch)

#### **O** Process

CMOS technology

#### Internal Peripheral Functions (resources)

- O I/O ports: Up to 26 ports (used also for internal resources)

- **O** Timebase timer: 1 channel

- O Watchdog timer: 1 channel

- O 16-bit reload timer: 3 channels

- O 16-bit free-running timer: 1 channel

#### O Output compare: 1 channel

• When the counter value of the 16-bit free-running timer matches the value set in the compare register, an interrupt request can be output.

#### **O** Input capture: 2 channels

• When the effective edge of a signal that is output from an external input pin is detected, the counter value of the 16-bit free-running timer can be read into the input capture data register and an interrupt request can be output.

#### ○ Serial I/O: 2 channels

#### O UART: 2 channels

- With full-duplex double buffer (8-bit length)

- Capable of asynchronous or clock synchronous serial transfer (I/O extended serial)

#### **O DTP/external interrupt (4 channels)**

- The input of an external interrupt can be used to activate the extended intelligent I/O service.

- The input of an external interrupt can be used to cause an internal hardware interrupt.

#### O Delayed interrupt generator module

Generates an interrupt request for task switching.

#### O 8/10-bit A/D converter (16 channels)

Selectable resolution of 8 or 10 bits

#### **O FL-control circuit**

- Enables FL driver control (automatic display control of up to 32 digit lines and up to 59 segment lines)

- Up to 32 digit lines (can be set line by line)

- Dimmer setting

- Permits LED driver control (automatic display control of up to 16 lines)

- Automatic display control of up to 16 lines with a 1/2 duty factor

#### • Clock output circuit

• Enables the source oscillation to be divided by 32, 64, 128, or 256 for clock output.

# 1.2 Product Lineup

# Table 1.2-1 "MB90M405 Series Product Lineup" shows the MB90M405 series product lineup.

#### Product Lineup

#### Table 1.2-1 MB90M405 Series Product Lineup

| Model                          | MB90MV405                                                                                                                                                                                                                                                             | MB90MF408 (*1)<br>MB90MF408A (*2) | MB90M408 (*1)<br>MB90M408A (*2) | MB90M407 (*1)<br>MB90M407A (*2) |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|---------------------------------|---------------------------------|

| Туре                           | Evaluation device                                                                                                                                                                                                                                                     | Built-in flash<br>memory          | Built-in r                      | mask ROM                        |

| ROM size                       | Not installed                                                                                                                                                                                                                                                         | 128K                              | bytes                           | 96K bytes                       |

| RAM size                       | 4K bytes                                                                                                                                                                                                                                                              | 4K I                              | oytes                           | 4K bytes                        |

| CPU function                   | Number of basic instructions: 351<br>Minimum instruction execution time: 59.5 ns/4.2 MHz (when PLL clock is multiplied by 4)<br>Number of addressing modes: 23<br>Program patch function: 2-address pointer<br>Maximum memory address space: 16M bytes                |                                   |                                 |                                 |

| Port                           | I/O ports (CMOS):                                                                                                                                                                                                                                                     | 26 (also used for resou           | irces)                          |                                 |

| FL control circuit             | 60 FL output lines (43 FL output lines and 17 LED control lines in LED control mode)<br>Capable of FL driver control and LED driver control<br>Enables dimmer setting for both digit and segment lines in FL driver control mode                                      |                                   |                                 |                                 |

| Serial I/O (UART)              | With a full-duplex double buffer<br>Capable of synchronous or asynchronous clock transfer<br>Also can be used for clock synchronous extended serial I/O<br>Dedicated built-in baud rate generator<br>Four built-in channels (two channels are also used for the UART) |                                   |                                 |                                 |

| 16-bit reload<br>timer         | 16-bit reload timer operation (can be set for toggle or one-shot output)<br>Supports an event count function<br>Three built-in channels                                                                                                                               |                                   |                                 |                                 |

| 16-bit free-<br>running timer  | 16-bit output compare x 1 channel (for clearing the free-running timer)<br>16-bit input capture x 2 channels                                                                                                                                                          |                                   |                                 |                                 |

| 8/10-bit A/D<br>converter      | 16 channels (input multiplexing)<br>Capable of 8-bit or 10-bit resolution<br>Conversion time: 5.9 μs (for an the operating machine clock of 16.8 MHz)                                                                                                                 |                                   |                                 |                                 |

| Timing clock<br>output circuit | An external input clock frequency can be divided and output externally.<br>Specifiable division ratio: Programmable to 1/16, 1/32, 1/64, or 1/128                                                                                                                     |                                   |                                 |                                 |

| I <sup>2</sup> C bus           | One built-in I <sup>2</sup> C interface channel                                                                                                                                                                                                                       |                                   |                                 |                                 |

| DTP/external<br>interrupt      | Four independent channels (can also be used for A/D input)<br>Interrupt source: "L"> "H" edge, "H"> "L" edge, "L" level, or "H" level can be set.                                                                                                                     |                                   |                                 |                                 |

#### **CHAPTER 1 OVERVIEW**

#### Table 1.2-1 MB90M405 Series Product Lineup (Continued)

| Model                | MB90MV405                                                             | MB90MF408 (*1)<br>MB90MF408A (*2) | MB90M408 (*1)<br>MB90M408A (*2) | MB90M407 (*1)<br>MB90M407A (*2) |

|----------------------|-----------------------------------------------------------------------|-----------------------------------|---------------------------------|---------------------------------|

| Low-power mode       | Sleep mode, Timebase timer mode, stop mode, and CPU intermittent mode |                                   |                                 |                                 |

| Process              | CMOS                                                                  |                                   |                                 |                                 |

| Package              | PGA256 QFP-100 (0.65 mm pitch)                                        |                                   |                                 | ch)                             |

| Operating<br>voltage | $3.3V\pm0.3V$ (16.8 MHz: 4.2 MHz multiplied by 4)                     |                                   |                                 | y 4)                            |

\*1: The FL output pins (FIP00 to FIP59) are output with a pull-down resistor.

\*2: The FL output pins (FIP00 to FIP16) are output without a pull-down resistor. The FL output pins (FIP17 to FIP59) are output with a pull-down resistor.

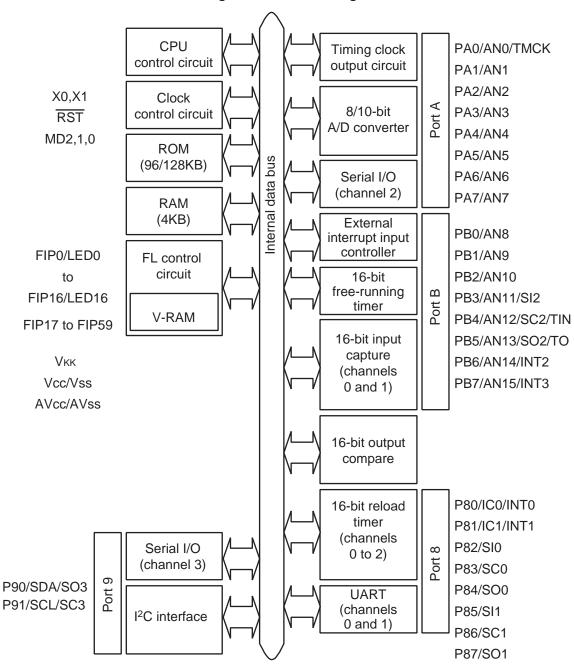

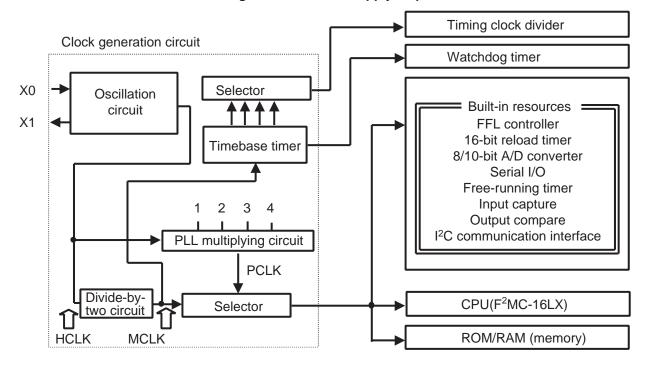

## 1.3 Block Diagram

Figure 1.3-1 "Block Diagram" shows a block diagram of the MB90M405 series of microcontrollers.

#### Block Diagram

Figure 1.3-1 Block Diagram

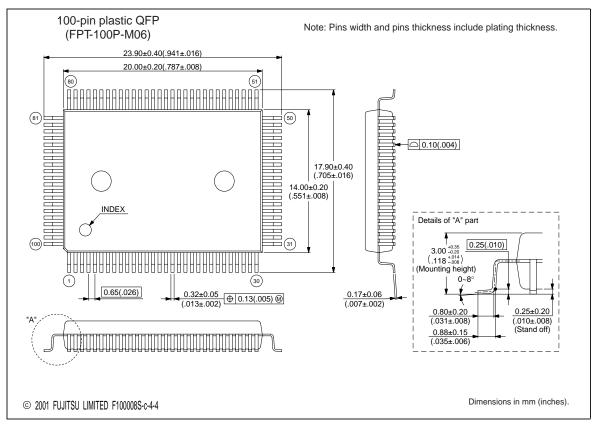

# 1.4 Package Dimensions

This section provides the dimensions of the MB90M405 series package.

#### ■ FPT-100P-M06 Dimensions

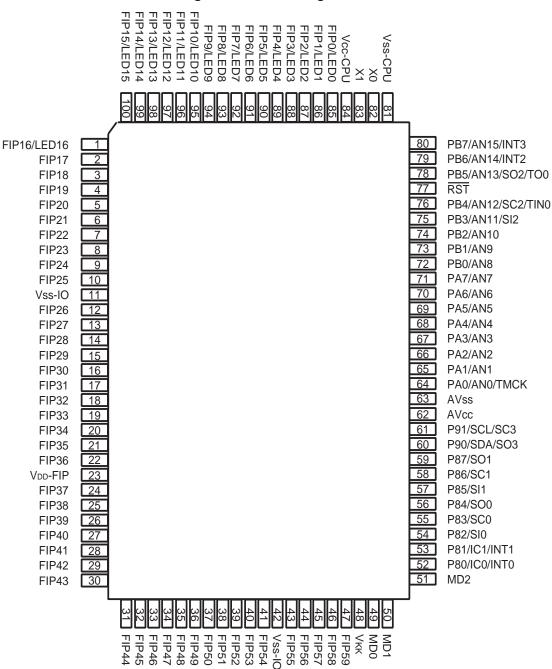

## 1.5 Pin Assignments

#### Pin Assignments

# 1.6 **Pin Functions**

Table 1.6-1 "Pin Functions" summarizes the pin names and functions, as well as the related circuit types and states at reset.

#### Pin Functions

Table 1.6-1 Pin Functions

| Pin number                       | Pin name       | Circuit | State/function                | Function                                                                                                                     |                     |                                                                                                                              |

|----------------------------------|----------------|---------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------|

| QFP-100M06                       | Fill Hallie    | type    | at reset                      | Function                                                                                                                     |                     |                                                                                                                              |

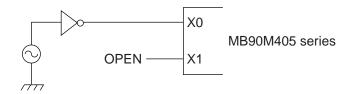

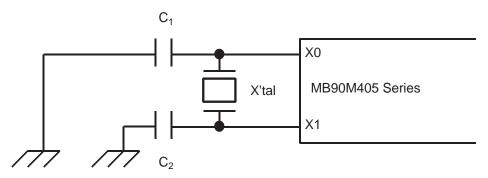

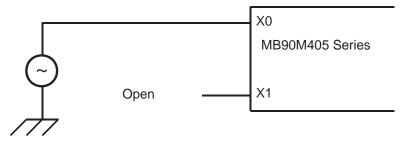

| 82, 23                           | X0, X1         | A       | Oscillating                   | Oscillation input pin<br>When an external clock is connected, leave the<br>X1 pin open.                                      |                     |                                                                                                                              |

| 77                               | RST            | В       | Reset input                   | External reset input pin                                                                                                     |                     |                                                                                                                              |

| 85 to 100                        | FIP0 to FIP15  |         |                               | Set when the FL driver is enabled                                                                                            |                     |                                                                                                                              |

| 85 10 100                        | LED0 to LED15  |         |                               | Set when the LED driver is enabled                                                                                           |                     |                                                                                                                              |

| 1                                | FIP16          | С       | V <sub>KK</sub> pull-down     | Set when the FL driver is enabled                                                                                            |                     |                                                                                                                              |

| I                                | LED16          |         | output (when a                | Set when the LED driver is enabled                                                                                           |                     |                                                                                                                              |

| 2 to 10<br>12 to 19              | FIP17 to FIP33 |         | pull-down<br>resistor is set) |                                                                                                                              |                     |                                                                                                                              |

| 20 to 22<br>24 to 41<br>43 to 47 | FIP34 to FIP59 | D       |                               | Pin dedicated to FL driver output                                                                                            |                     |                                                                                                                              |

|                                  | P80            |         |                               | I/O port                                                                                                                     |                     |                                                                                                                              |

| 50                               | IC0            |         |                               | External trigger input pin for input capture channel 0                                                                       |                     |                                                                                                                              |

| 52                               | INTO           | Е       | _                             | E Dert in such /                                                                                                             | Dest is such (UK e) | External cause input pin for external interrupt<br>input channel 0<br>Input is enabled when the EN0 bit enables this<br>pin. |

|                                  | P81            |         | Port input (Hi-z)             | I/O port                                                                                                                     |                     |                                                                                                                              |

|                                  | IC1            |         |                               | External trigger input pin for input capture channel 1                                                                       |                     |                                                                                                                              |

| 53                               | INT1           |         |                               | External cause input pin for external interrupt<br>input channel 1<br>Input is enabled when the EN1 bit enables this<br>pin. |                     |                                                                                                                              |

| Table 1.6-1 | Pin | Functions | (Continued) |

|-------------|-----|-----------|-------------|

|-------------|-----|-----------|-------------|

| Pin number | Pin name | Circuit | State/function | Function                                                                                                                                                                                                                                           |               |                                                                                                                                            |                   |                                                                                                                                                                                                                                                   |

|------------|----------|---------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| QFP-100M06 | Finnanie | type    | at reset       | i unction                                                                                                                                                                                                                                          |               |                                                                                                                                            |                   |                                                                                                                                                                                                                                                   |

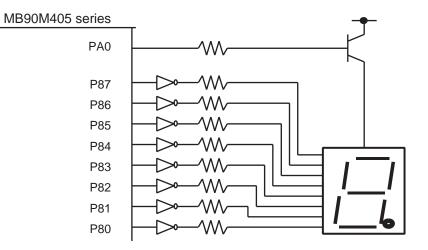

|            | P82      |         |                | I/O port                                                                                                                                                                                                                                           |               |                                                                                                                                            |                   |                                                                                                                                                                                                                                                   |

| 54         | SIO      |         |                | Serial data input pin for serial I/O channel 0<br>This pin is used occasionally while serial I/O<br>channel 0 is performing an input operation. Do<br>not use this pin for any other purpose during an<br>input operation on serial I/O channel 0. |               |                                                                                                                                            |                   |                                                                                                                                                                                                                                                   |

|            | P83      |         |                | I/O port                                                                                                                                                                                                                                           |               |                                                                                                                                            |                   |                                                                                                                                                                                                                                                   |

| 55         | SC0      |         |                | Serial clock I/O pin for serial I/O channel 0<br>This function is enabled when serial I/O channel 0<br>is enabled for serial clock output.                                                                                                         |               |                                                                                                                                            |                   |                                                                                                                                                                                                                                                   |

|            | P84      |         |                | I/O port                                                                                                                                                                                                                                           |               |                                                                                                                                            |                   |                                                                                                                                                                                                                                                   |

| 56         | SO0      | E       |                | Serial data output pin for serial I/O channel 0<br>This function is enabled when serial I/O channel 0<br>is enabled for serial data output.                                                                                                        |               |                                                                                                                                            |                   |                                                                                                                                                                                                                                                   |

|            | P85      | E       |                | I/O port                                                                                                                                                                                                                                           |               |                                                                                                                                            |                   |                                                                                                                                                                                                                                                   |

| 57         | SI1      |         |                | -                                                                                                                                                                                                                                                  | Port input (F | Port input (Hi-z                                                                                                                           | Port input (Hi-z) | Serial data input pin for serial I/O channel1<br>This pin is used occasionally while serial I/O<br>channel 1 is performing an input operation. Do<br>not use this pin for any other purpose during an<br>input operation on serial I/O channel 1. |

|            | P86      |         |                | I/O port                                                                                                                                                                                                                                           |               |                                                                                                                                            |                   |                                                                                                                                                                                                                                                   |

| 58         | SC1      |         |                |                                                                                                                                                                                                                                                    |               | Serial clock I/O pin for serial I/O channel 1<br>This function is enabled when serial I/O channel 1<br>is enabled for serial clock output. |                   |                                                                                                                                                                                                                                                   |

|            | P87      |         |                | I/O port                                                                                                                                                                                                                                           |               |                                                                                                                                            |                   |                                                                                                                                                                                                                                                   |

| 59         | SO1      |         |                | Serial data output pin for serial I/O channel 1<br>This function is enabled when serial I/O channel 1<br>is enabled for serial data output.                                                                                                        |               |                                                                                                                                            |                   |                                                                                                                                                                                                                                                   |

|            | P90      |         |                | I/O port (N-channel open drain)                                                                                                                                                                                                                    |               |                                                                                                                                            |                   |                                                                                                                                                                                                                                                   |

| 60         | SDA      | G       |                | $I^2C$ interface data I/O pin. This function is<br>enabled when $I^2C$ interface operation is enabled.<br>Set the port to the input setting (DDR9 bit 8 = 0)<br>while the $I^2C$ interface is active.                                              |               |                                                                                                                                            |                   |                                                                                                                                                                                                                                                   |

|            | SO3      |         |                | Serial data output pin for serial I/O channel 3<br>This function is enabled when serial I/O channel 3<br>is enabled for serial data output.                                                                                                        |               |                                                                                                                                            |                   |                                                                                                                                                                                                                                                   |

#### **CHAPTER 1 OVERVIEW**

Table 1.6-1 Pin Functions (Continued)

| Pin number<br>QFP-100M06 | Pin name    | Circuit<br>type | State/function<br>at reset | Function                                                                                                                                                                                                 |  |                                                                                                                                                                                                                                                    |

|--------------------------|-------------|-----------------|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                          | P91         |                 |                            | I/O port (N-channel open drain)                                                                                                                                                                          |  |                                                                                                                                                                                                                                                    |

| 61                       | SCL         | G               | Port input (Hi-z)          | $I^2C$ interface clock I/O pin. This function is<br>effective when $I^2C$ interface operation is enabled.<br>Set the port to the input setting (DDR9 bit 9 = 0)<br>while the $I^2C$ interface is active. |  |                                                                                                                                                                                                                                                    |

|                          | SC3         |                 |                            | Serial clock I/O pin for serial I/O channel 3<br>This function is enabled when serial I/O channel 3<br>is enabled for serial clock output.                                                               |  |                                                                                                                                                                                                                                                    |

|                          | PA0         |                 |                            | I/O port                                                                                                                                                                                                 |  |                                                                                                                                                                                                                                                    |

| 64                       | AN0         |                 |                            | Analog input pin channel 0 for the A/D converter<br>This function is enabled when analog input is<br>enabled (set by the ADER).                                                                          |  |                                                                                                                                                                                                                                                    |

|                          | ТМСК        |                 |                            | Timing clock output pin. This function is enabled<br>when output is enabled.<br>The function is disabled when the ADER enables<br>analog input.                                                          |  |                                                                                                                                                                                                                                                    |

|                          | PA1 to PB2  |                 |                            | I/O port                                                                                                                                                                                                 |  |                                                                                                                                                                                                                                                    |

| 65 to 74                 | AN1 to AN10 |                 |                            | Analog input pin channels 1 to 10 for the A/D<br>converter<br>This function is enabled when analog input is<br>enabled (set by the ADER).                                                                |  |                                                                                                                                                                                                                                                    |

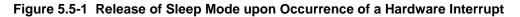

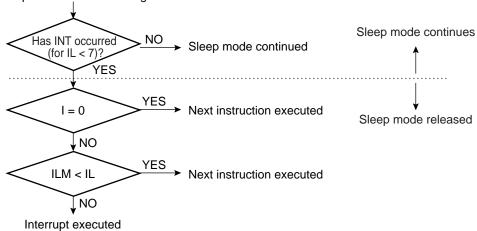

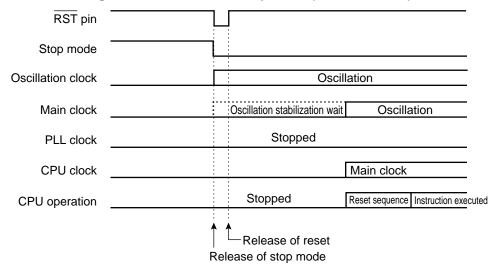

|                          | PB3         |                 |                            | I/O port                                                                                                                                                                                                 |  |                                                                                                                                                                                                                                                    |