# **Advanced Products**

# FUJITSU

# MB8868A

MOS Universal Asynchronous Receiver/Transmitter (UART)

#### Description

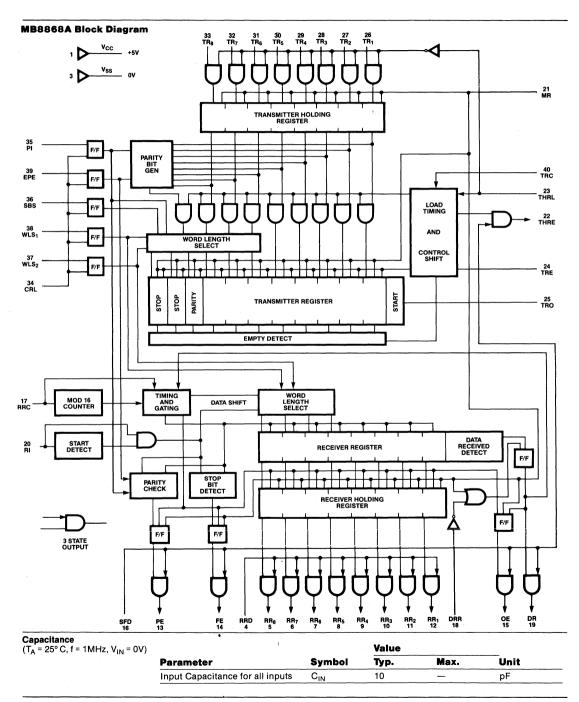

The Fujitsu MB8868/A is a programmable Universal Asynchronous Receiver/Transmitter (UART), fabricated with an N-channel silicon gate MOS technology. All control pins, input pins and output pins are TTL compatible. The UART interfaces asynchronous serial data channels from terminals or other peripherals to the parallel data of a microprocessor, computer, or other terminal. Parallel data is converted by the transmitter section of the UART into a serial word consisting of the data as well as start, parity, and stop bit(s). Serial data is converted by the receiver section of the UART into parallel data. The receiver section verifies correct code transmission by parity checking and active reception of a valid stop bit. The UART can be programmed to accept word lengths of 5, 6, 7, or 8 bits. Even or odd parity can be set. Parity generation and checking can be inhibited.

One, one and one-half, or two stop bits can be set when transmitting a 5-bit code.

#### Features

- Full or Half Duplex Operation

- Completely Programmable

Start Bit Generated

- Automatically Data and Clock Synchronization Performed

- Automatically Data Received/Transmitted Status Automatically Generated

- Complete Static Circuity

- TTL Compatible I/O

- Three-State Output

- Capability

- Single Power Supply: +5V

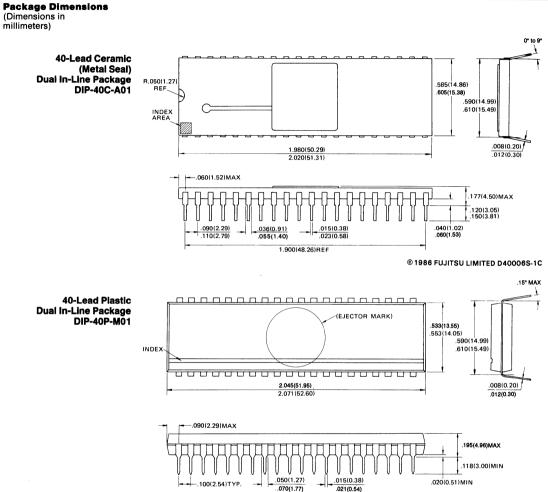

Standard 40-Pin Dual In-Line Package

- Functionally Compatible with Western Digital TR1863 and AMI S1602

4

MB8868A

#### FUJITSU

7

**Pin Assignment**

| Vcc 🗆           |       | $\sim$ | 40   | TRC             |

|-----------------|-------|--------|------|-----------------|

| *N.C.           | 2     |        | 39   |                 |

|                 |       |        |      |                 |

| Vss 🗖           | 3     |        | 38   |                 |

| RRD 🗖           | 4     |        | 37   |                 |

| RR8             | 5     |        | 36   | SBS             |

| RR7             | 6     |        | 35   | ПЫ              |

|                 | 7     |        | 34   |                 |

|                 | 8     |        | 33   | ПТВа            |

|                 | 9     |        | 32   |                 |

|                 | 10    |        | 31   |                 |

| RR <sub>2</sub> | 11    |        | 30   |                 |

|                 | 12    |        | 29   | TR4             |

| PE 🗔            | 13    |        | 28   | TR <sub>3</sub> |

| FE 🗖            | 14    |        | 27   | TR2             |

| OE 🗖            | 15    |        | 26   |                 |

| SFD             | 16    |        | 25   | TRO             |

| RRC 🗔           | 17    |        | 24   | TRE             |

| DRR 🖂           | 18    |        | 23   |                 |

| DR 🗖            | 19    |        | 22   | THRE            |

| BIC             | 20    |        | 21   | Бмв             |

|                 |       |        | 21   |                 |

| *N.C. (         | (no c | onnect | tion | )               |

\* 5

÷ C

## **Absolute Maximum**

Ratings (See Note)

| Rating                                               | Symbol           | Value        | Unit            |

|------------------------------------------------------|------------------|--------------|-----------------|

| V <sub>CC</sub> Pin Potential to V <sub>SS</sub> Pin | V <sub>cc</sub>  | -0.3 to +7.0 | V <sub>DC</sub> |

| Input Voltage                                        | V <sub>IN</sub>  | -0.3 to +7.0 | V <sub>DC</sub> |

| Output Voltage                                       | Vo               | -0.3 to +7.0 | V <sub>DC</sub> |

| Operating Temperature                                | T <sub>OP</sub>  | 0 to +70     | °C              |

| Storate Temperature                                  | T <sub>stg</sub> | -55 to +150  | °C              |

Note: Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. Functional operation should be restricted to the conditions as detailed in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields. It is advised that normal precattions be taken to avoid applications of any voltages higher than maximum rated voltages to this high impedance circuit.

#### **Recommended Operating** Conditions (Referenced to V<sub>SS</sub>)

Value Operating Temperature Parameter Symbol Min. Typ. Max. Unit 4.75 5.0 5.25 ٧ Vcc Supply Voltage V<sub>SS</sub> 0.0 0.0 0.0 v O°C to +70°C 2.2 ٧ Logic Input High Voltage  $V_{\rm H}$ \_\_\_\_ Vcc ٧ Logic Input Low Voltage VIL -0.3 +0.8 \_\_\_\_

DC Characteristics (Recommended operating conditions unless otherwise noted)

|                                                                                                                 |       |                 | Value |           |      |       |  |

|-----------------------------------------------------------------------------------------------------------------|-------|-----------------|-------|-----------|------|-------|--|

| Parameter                                                                                                       | Symbo | Symbol          | Min.  | Тур.      | Max. | Units |  |

| Input Leakage Current<br>(V <sub>IN</sub> = 0 to 5.25V, V <sub>CC</sub> = 5.25V)                                |       | lu              |       | - <u></u> | 350  | μA    |  |

| Output Leakage Current for 3-State<br>(V <sub>OUT</sub> = 0V to V <sub>CC</sub> , SFD = RRD = V <sub>IH</sub> ) |       | I <sub>LZ</sub> | -20   | <u> </u>  | +20  | μA    |  |

| Output Low Voltage (I <sub>OL</sub> = 1.8mA)                                                                    | 1     | VOL             |       |           | 0.4  | V     |  |

| Output High Voltage (I <sub>OL</sub> = -200µA)                                                                  | a 1.  | V <sub>OH</sub> | 2.4   |           |      | V     |  |

| V <sub>CC</sub> Supply Current                                                                                  |       | Icc             |       | 70        |      | mA    |  |

AC Characteristics (Recommended operating ranges unless otherwise noted)

|                  | Value                |                         |                                                             |                                                                       |

|------------------|----------------------|-------------------------|-------------------------------------------------------------|-----------------------------------------------------------------------|

| Symbol           | Min.                 | Typ.                    | Max.                                                        | Units                                                                 |

| f <sub>C</sub>   | DC                   |                         | 800                                                         | kHz                                                                   |

| t <sub>PWC</sub> | 200                  | <u> </u>                | ·. ····                                                     | ns                                                                    |

| t <sub>PWT</sub> | 180                  | <u> </u>                | _                                                           | ns                                                                    |

| t <sub>PWR</sub> | 180                  |                         |                                                             | ns                                                                    |

| t <sub>PWM</sub> | 150                  |                         | <u> </u>                                                    | ns                                                                    |

| t <sub>C</sub>   | 180                  |                         |                                                             | ns                                                                    |

| t <sub>H</sub>   | 20                   |                         |                                                             | ns                                                                    |

| t <sub>SET</sub> | 0                    | -                       | _                                                           | ns                                                                    |

| t <sub>pd0</sub> |                      |                         | 350                                                         | ns                                                                    |

| t <sub>pd1</sub> | _                    |                         | 350                                                         | ns                                                                    |

| 1                | C<br>H<br>SET<br>pd0 | с 180<br>н 20<br>свет 0 | C      180         H      20         SET      0         pd0 | C      180         H      20         SET      0         pd0       350 |

### **Pin Descriptions**

| Pin Name             | Pin Number         | Description                                                                                                                                                                                                                                                                                                                   |

|----------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RRD                  | 4                  | Receiver Register Disconnect                                                                                                                                                                                                                                                                                                  |

|                      |                    | A high logic level, $V_{IH}$ , on this pin disconnects the Receiver Holding Register outputs from the data outputs $RR_8$ -RR <sub>1</sub> on pins 5–12.                                                                                                                                                                      |

| RR <sub>8</sub> thru | 5, 6, 7, 8, 9, 10, | Receiver Holding Register Data                                                                                                                                                                                                                                                                                                |

| RR <sub>1</sub>      | 11, 12             | These are the parallel outputs from the Receiver Holding<br>Register if the RRD input is an input low level, $V_{IL}$ . Data is right<br>justified for character formats of less than eight bits, with RR <sub>1</sub><br>being the least significant bit. Unused MSB's are forced to a<br>low logic output level, $V_{OL}$ . |

| PE                   | 13                 | Parity Error                                                                                                                                                                                                                                                                                                                  |

|                      |                    | This output pin goes to a high level, V <sub>OH</sub> , if the received parity does not agree with that programmed by the Even Parity Enable input (pin 39).                                                                                                                                                                  |

|                      |                    | With each character transferred to the Receiver Holding<br>Register, this output is updated. The status Flag Disconnect<br>input (pin 16) allows additional PE lines to be tied together by<br>providing an output disconnect capability.                                                                                     |

Pin Descriptions (Continued)

| Pin Name | Pin Number | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FE       | 14         | Framing Error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|          |            | This output pin goes to a high level, $V_{OH}$ , if the received character has no valid Stop bit. With each character transferred to the Receiver Holding Register, this output is updated. The Status Flag Disconnect input (pin 16) allows additional FE lines to be tied together by providing an output disconnect capability.                                                                                                                                                                                                                                                                                     |

| OE       | 15         | Overrun Error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|          |            | This output pin goes to a high level, $V_{OH}$ , if the Data Received<br>Flag (pin 19) is not reset before the next character is transferred<br>to the Receiver Holding Register. The Status Flag Disconnect<br>input (pin 16) allows additional OE lines to be tied together by<br>providing an output disconnect capability.                                                                                                                                                                                                                                                                                         |

| SFD      | 16         | Status Flag Disconnect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|          |            | When this input goes to a high level, V <sub>IH</sub> , PEE, FE, OE, DR, and THRE outputs are disconnected allowing bus sharing capability.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| RRC      | 17         | Receiver Register Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|          |            | This clock input is sixteen times the desired receiver shift rate.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

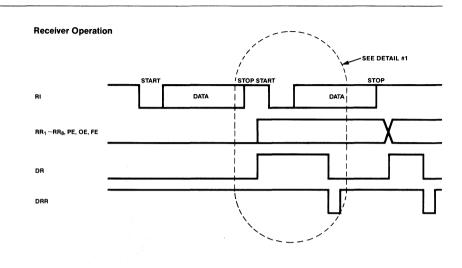

| DRR      | 18         | Data Received Reset (DRR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|          |            | A low level input, V <sub>IL</sub> , resets the data Received (DR) line.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| DR       | 19         | Data Received                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|          |            | This output goes to a high level, V <sub>OH</sub> , when an entire character<br>has been received and transferred to the Receiver Holding<br>Register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| RI       | 20         | Receiver Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|          |            | Serial input data enters on this line. It is transferred to the Receiver Register as determined by the character length, parity, and number of Stop bits. When data is not being received, this input must be at high level, $V_{\rm H}$                                                                                                                                                                                                                                                                                                                                                                               |

| MR       | 21         | Master Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|          |            | A high level pulse, $V_{IH}$ , on this input will clear the internal logic. The Transmitter and Receiver Registers, the Receiver Holding Register, FE, OE, PE, and DRR are reset. In addition, the serial output line is set to a high level, $V_{OH}$ .                                                                                                                                                                                                                                                                                                                                                               |

| THRE     | 22         | Transmitter Holding Register Empty                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|          |            | This output goes to a high level, V <sub>OH</sub> , when the Transmitter<br>Holding Register has completed transfer of its contents to the<br>Transmitter Register. The high level indicates that a new<br>character may be loaded into the transmitter Holding Register.                                                                                                                                                                                                                                                                                                                                              |

| THRL     | 23         | Transmitter Holding Register Load                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|          |            | When a low level, $V_{iL}$ , is applied to this input, a character is<br>loaded into the Transmitter Holding Register. This character is<br>transferred to the Transmitter Register on a low to high level<br>transition, as long as the Transmitter Register is not<br>currently in the process of transmitting a character. If a<br>character is being transmitted, the transfer from the Transmitter<br>Holding Register is delayed until character transmission has<br>been completed. Then, the new character is transferred<br>simultaneously with the start of the serial transmission of the<br>new character. |

| TRE      | 24         | Transmitter Register Empty                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|          |            | This output is at a high level , $V_{OH}$ , when the Transmitter Register has completed the serial transmission of a full character including the required number of Stop bits. A high level will be maintained until the start of transmission of                                                                                                                                                                                                                                                                                                                                                                     |

Pin Descriptions (Continued)

| Pin Name                                        | Pin Number      | Description                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------------------------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TRO                                             | 25              | Transmitter Register Output                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                 |                 | This output line transmits the Transmitter Register contents [Start bit, Data bits, Parity bit, and Stop bit(s)] serially. This output remains at a high level, $V_{OH}$ , when no data is being transmitted. Therefore, the start of transmission is determined by the transition of the Start bit from a high level to a low level voltage, $V_{OL}$ .                                                           |

| TR₁ thru                                        | 26, 27, 28, 29, | Transmitter Register Data Inputs                                                                                                                                                                                                                                                                                                                                                                                   |

| TR <sub>8</sub>                                 | 30, 31, 32, 33  | The THRL strobe loads each character on these lines into the Transmitter Holding Register. If WLS <sub>1</sub> and WLS <sub>2</sub> have selected a character of less than 8 bits, the character is then right-justified to the least significant bit, TR <sub>1</sub> , with the excess bits not used. A high input level, V <sub>IH</sub> , will cause a high output level, V <sub>OH</sub> , to be transmitted. |

| CRL                                             | 34              | Control Register Load                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                 | ø               | When this input is at a high level, $V_{1H}$ , the control bits (WLS <sub>1</sub> , WLS <sub>2</sub> , EPE, PI, SBS), are loaded into the Control Register. This input may be either strobed or hard wired to a high level.                                                                                                                                                                                        |

| PI                                              | 35              | Parity Inhibit                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                 |                 | When this input is at a high level, $V_{IH}$ , parity generation and<br>verification circuitry are inhibited and the PE output will be held<br>to a low level, $V_{OL}$ . In the inhibit condition, the Stop bit(s) will<br>follow the last data bit on transmission.                                                                                                                                              |

| SBS                                             | 36              | Stop Bit(s) Select                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                 |                 | A high level, $V_{IH}$ , on this input will select two Stop bits, and a low level, $V_{IL}$ , will select one Stop bit. If 5-bit long words are selected, a high level, $V_{IH}$ , will generate one and one-half Stop bits.                                                                                                                                                                                       |

| WLS <sub>1</sub> , WLS <sub>2</sub><br>EPE, TRC |                 | Word Length Select (WLS <sub>1</sub> , WLS <sub>2</sub> )<br>The state of these two inputs determines the character length<br>(exclusive of parity) as follows:                                                                                                                                                                                                                                                    |

|                                                 |                 | WLS2      WLS1      Word Length        VIH      VIH      8 bits        VIH      VIL      7 bits        VIL      VIH      6 bits        VIL      VIH      5 bits                                                                                                                                                                                                                                                    |

|                                                 |                 | Even Parity Enable (EPE)<br>A high level, $V_{IH}$ , on this input will select even Parity, while a low<br>level, $V_{IL}$ , selects odd Parity.                                                                                                                                                                                                                                                                   |

|                                                 |                 | Transmitter Register Clock (TRC)<br>The frequency of this clock is 16 times the desired transmitter<br>shift rate.                                                                                                                                                                                                                                                                                                 |

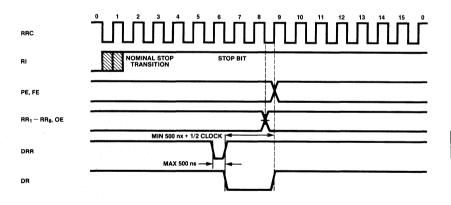

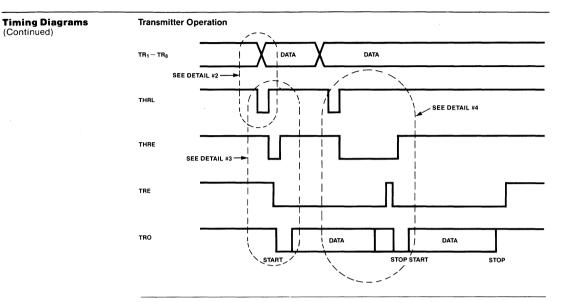

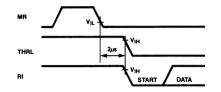

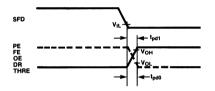

**Timing Diagrams**

Timing for Status Flag, RR<sub>1</sub>, thru RR<sub>8</sub> and DR (Detail #1)

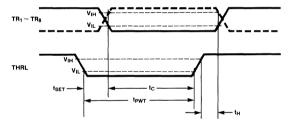

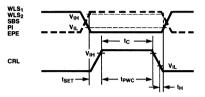

Data Input Load Cycle (Detail #2)

#### **Timing Diagrams** (Continued)

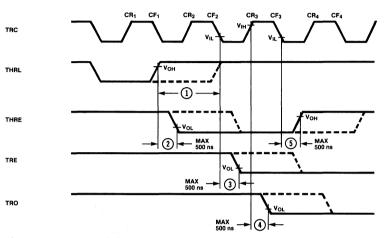

Transmitter Output Timing (1) (Detail #3)

#### Notes:

0 When the positive transition of THRL is  $\geq$  500 ns before the falling edge of TRC (CF2 in the figure), then TRE is enabled at CF2. But when 500 ns >0 > 0 ns, then TRE is invalid between CF2 and CF3

① THRE goes low during 500 ns Max. from the postive transition of THRL.

① TRE goes low during 500 ns Max. from the first falling edge of TRC after THRE goes low with TRE high.

() TRO goes low (START BIT) during 500 ns Max. from the first rising edge of TRC after TRE goes low. ③ THRE goes high during 500 ns Max. from the falling edge of TRC after Start bit is enabled.

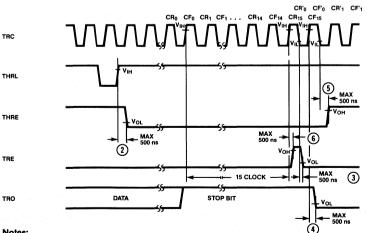

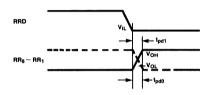

### Transmitter Output Timing (2) (Detail #4)

Λ

Notes:

2~ (5) Refer to Notes in Detail #3

(i) TRE goes high during 500 ns Max. from the 15th rising edge of TRC after Stop bit is enabled.

**Timing Diagrams** (Continued)

**Other Timing Diagrams**

Input After Master Reset

**Control Register Load Cycle**

Data Output

© 1985 FUJITSU LIMITED D40005S-1C