# **FUJITSU**

October 1986

# ■ MB88306 MB88307 MB88308 MB88309

**CMOS Output Expander**

#### DESCRIPTION

Each of the four expanders provides a serial I/O port and an 8-bit parallel output port. Data is serially loaded via the input port, converted to an 8-bit parallel format, and latched. The latched data is then transferred to the parallel output port for distribution. The 8-bit output port can directly drive a Light Emitting Diode (LED) display; the LED display can be expanded in byte-size increments to make any desired configuration. In terms of output drive and shift clock triggers, each expander is unique—see description that follows.

| Expander | Output          | Shift Clock Trigge |

|----------|-----------------|--------------------|

| MB88306  | CMOS 3-Štate    | Rising Edge        |

| MB88307  | NMOS Open Drain | Rising Edge        |

| MB88308  | CMOS 3-State    | Falling Edge       |

| MB88309  | NMOS Open Drain | Falling Edge       |

|          |                 |                    |

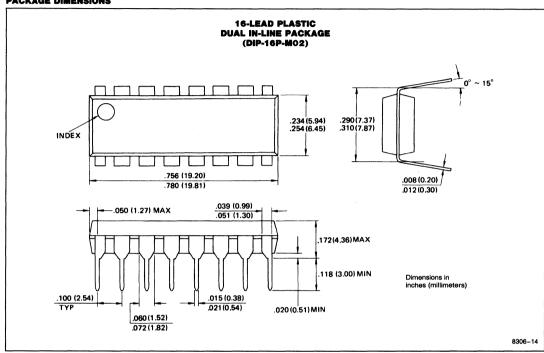

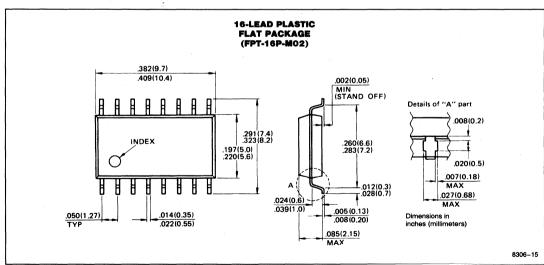

MB88306/7/8/9 are fabricated by a silicon-gate CMOS process and are packaged in a standard 16-pin plastic DIP or SOP. All four expanders operate with a single +5V power source and a 2 MHz shift clock over an ambient temperature range of  $-40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$ .

# **FEATURES**

- 8-bit parallel output

- Serial input/output

- Expandable in 8-bit increments

- LED direct drive capability: 15 mA max at 1.2V

- Two output port types:

- -CMOS 3-state output (MB88306/8)

- -NMOS open-drain output (MB88307/9)

- Two shift clock polarities:

- -Rising-edge-triggering (MB88306/7)

- -Falling-edge-triggering (MB88308/9)

- Simple interface to Fujitsu 4-bit microcomputers

- TTL compatible outputs

- Single +5V power supply

- Silicon-gate CMOS process

- Two package options:

- -16-pin plastic DIP (Suffix -P)

- -16-pin plastic SOP (Suffix -PF)

Copyright @ 1986 by Fujitsu Limited and Fujitsu Subsidiaries worldwide.

This document contains information considered proprietary by Fujitsu Limited, Tokyo, Japan and its subsidiaries. No part of this document may be copied or reproduced in any form or by any means, or transferred to any third party without the prior written consent of Fujitsu Limited.

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields. However, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high impedance circuit.

B38306

MB88306

# PIN DESCRIPTION

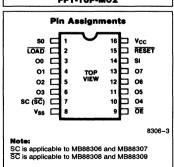

Figures 1 and 2 show the pin assignment and logic symbol of the MB88306/7/8/9. Table 1 shows the pin description. The MB88306/7/8/9 have two interfaces: one is the processor interface; SI, SC (SC), RESET, LOAD, and OE inputs; the other is the expansion output port; O7-O0, and SO outputs.

**Table 1: Pin Description**

| Symbol          | Number        | Туре | Name & Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----------------|---------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ower Supply     | ,             |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Vcc             | 16            | _    | + 5V dc power supply pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| V <sub>SS</sub> | 8             |      | Power supply ground pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Processor In    | terface       |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| SI              | 14            | I    | Serial data input to the internal shift register: A data bit on the SI pin is shifted into the MSB of the shift register at the rising edge (MB88306/7) of the shift clock SC or the falling edge (MB88308/9) of the shift clock for SC. The data bits are transferred from the processor or from the SO pin of the cascaded devices.                                                                                                                                                                           |

| SC<br>(SC)      | 4             | l    | Shift clock input for the internal shift register: The rising edge of SC (MB88306/7) or falling edge of SC (MB88308/9) shifts a data bit on the SI pin into the MSB of the shift register, each bit of the shift register is shifted right, and the LSB of the shift register appears directly on the SO pin. A high level and low level and the falling edge (MB88306/7) or the rising edge (MB88308/9) keep contents of the shift register. This is a hysteresis input.                                       |

| RESET           | 15            |      | Preset input for the internal data latch: A low level on the RESET pin initializes the data latch in high state, and also inhibits the LOAD input. This is a hysteresis input. The RESET input does not affect the shift register and the output drain.                                                                                                                                                                                                                                                         |

| LOAD            | 2             | 1 .  | Load enable input for the internal data latch: A low level on the LOAD pin transfers 8-bit parallel data of the shift register into the data latch. A high level inhibits data transmission from the shift register to the data latch, to hold contents of the data latch. This input is automatically inhibited when the RESET input is activated (low). This is a hysteresis input.                                                                                                                           |

| ŌĒ              | 9             | I    | Output enable input of the output driver: A low level on the $\overline{\text{OE}}$ pin outputs 8-bit data of the data latch on the data output pins O7-O0. A high level places the O7-O0 pins in high impedance state. The $\overline{\text{OE}}$ pin does not control the SO output.                                                                                                                                                                                                                          |

| Expansion Po    | ort           |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 07-00           | 13–10,<br>6–3 | О    | Parallel data output: This is an 8-bit 3-state data output port. This port outputs 8-bit data in the data latch when the $\overline{OE}$ pin is activated (low), and is placed in high impedance state when the $\overline{OE}$ pin is inactive (high). This port is CMOS 3-state output (MB88306/8) or NMOS open-drain output (MB88307/9). Both output drivers can directly drive LEDs. The MSB and LSB of the shift register are output onto the O7 and O0 pins, respectively. These pins are TTL compatible. |

| SO              | 1             | 0    | Serial data output of the internal shift register: The LSB of the shift register appears directly onto the SO pin with some delay time because the SO output has no output latch. This pin is used to cascade devices to expand the data output port in 8-bit units. This pin is TTL compatible but is not 3-state output controlled by the OE pin.                                                                                                                                                             |

#### **FUNCTIONAL DESCRIPTION**

#### **BLOCK FUNCTIONS**

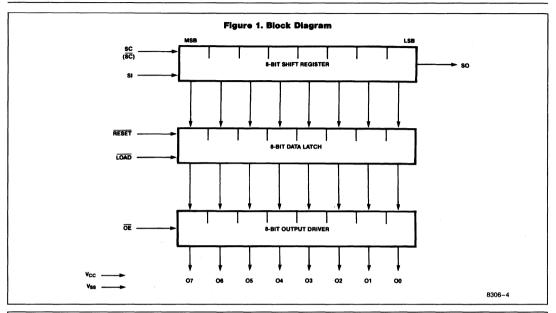

The MB88306/7/8/9 consist of a shift register, a data latch, and an output driver. Figure 1.

#### **Shift Register**

This is an 8-bit serial-in/parallel-out static shift register, that converts serial data loaded by the processor into 8-bit parallel data. The rising edge (MB88308/9) of the shift clock (SC or SC) shifts a data bit on the SI pin into the MSB of the shift register. Each bit of the shift register is shifted right (MSB → LSB), and the LSB of the shift register is shifted out onto the SO pin. Eight parallel output lines of the shift register are internally connected to the data latch inputs. The Shift register has no clear input and, after power-up, the register contents are undefined. The RESET input does not affect the shift register.

#### **Data Latch**

This is an 8-bit D-type transparent latch that holds 8-bit parallel data transferred from the shift register. The latch has two control inputs, <u>LOAD</u> and <u>RESET</u>: The <u>LOAD</u> pin is a data enable input and a low level on this pin transfers contents of the shift register into the data latch. The <u>RESET</u> pin is a preset input and a low level on this pin initializes the data latch in the high state. When

the  $\overline{\text{RESET}}$  input is active, the  $\overline{\text{LOAD}}$  input is automatically inhibited.

#### **Output Driver**

This is an 8-bit 3-state output driver that is driven by 8 bits of data from the data latch. The MB88306/8 have a CMOS 3-state output driver and the MB88307/9 have an NMOS open-drain output driver. Both drivers are controlled by the  $\overline{OE}$  input and can directly drive LEDs (V<sub>OL</sub> = 1.2V max at l<sub>OL</sub> = 20 mA). A low level on the  $\overline{OE}$  pin enables 8-bit data in the data latch onto output pins O7–O0. A high level forces the output pins to a high impedance state. The  $\overline{RESET}$  input does not affect the output driver.

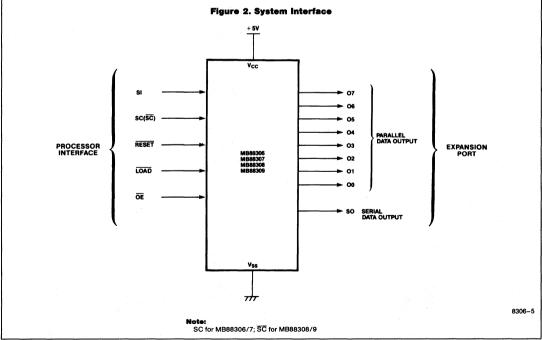

#### SYSTEM INTERFACE

The processor and expansion-port interface for the four expanders is shown in Figure 2. As previously indicated, internal operations of the MB88306 and MB88307 are initiated on the rising edge of Shift Clock (SC) whereas, the same operations in the MB88308 and MB88309 occur on the falling edge of \$\overline{SC}\$. The Serial Output (SO) pin can be used to cascade two or more expanders; an example is shown later in this data sheet.

**Table 2. Expander Functions**

|        |                      | Control Inputs |       |    |                   | Internal State |        |  |

|--------|----------------------|----------------|-------|----|-------------------|----------------|--------|--|

| Mode   | SC ( <del>SC</del> ) | LOAD           | RESET | ŌĒ | Shift<br>Register | Data<br>Latch  | Output |  |

| Shift  | ↑(↓)                 | Н              | х     | ×  | х                 | х              | Х      |  |

| Hold   | H/L,                 | ×              | ×     | Н  | ×                 | х              | Z      |  |

| 11010  | ↓ (↑)                | ^              | ^     | L  | ^                 | ^              | Х      |  |

| Load   | X (X)                |                | Н     | н  | X                 | ×              | Z      |  |

|        | 1                    | _              |       | L  | H/L               | H/L            | H/L    |  |

| Reset  | X (X)                | х              |       | Н  | X                 | Н              | Z      |  |

| 110001 | ^(^)                 | ^              | _     | L  | ^                 | ''             | ×      |  |

#### Legend:

H = High level L = Low level

Z = High impedance X = Don't care 1 = Rising edge

↓ = Falling edge

#### FUNCTIONAL DESCRIPTION (Continued)

#### **OPERATING MODES**

### Initialization (Reset Mode)

After power on, contents of the shift register and data latch are undefined. The shift register can not be initialized by hardware because it has no preset input. The data latch can be preset to a high state by a low level on the RESET pin.

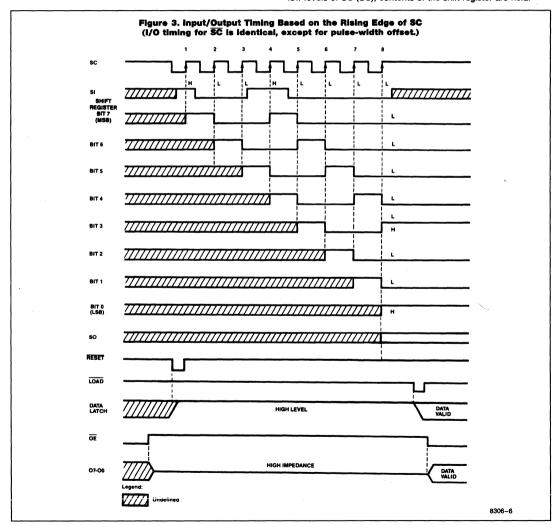

#### Data Input (Shift & Hold Modes)

Data serially loaded by the processor through the SI pin synchronously with the shift clock, SC (MB88306/7) or SC (MB88308/9). At the rising edge of SC or the falling edge of SC, serial data on the SI pin is shifted into the MSB of the shift register. Each bit of the shift register is shifted right, and the LSB of the shift register underflows onto the SO pin. During high and low levels of SC (SC), contents of the shift register are held.

#### FUNCTIONAL DESCRIPTION (Continued)

#### Data Output (Load Mode)

A low level on the  $\overline{\text{LOAD}}$  pin transfers 8 bits of data from the shift register in parallel into the data latch. A low level on the  $\overline{\text{OE}}$  pin enables the 8-bit data in the data latch onto the output port pins O7–O0. When the  $\overline{\text{LOAD}}$  pin is high, the shift register and the data latch are isolated to hold contents of the data latch. (When the  $\overline{\text{RESET}}$  pin is activated, the load input is automatically inhibited.) Also, when the  $\overline{\text{OE}}$  pin is inactive, the O7–O0 pins are forced to a high impedance state. (The data output pins of

the MB88307/9 float when 1s are output because they have NMOS open-drain drivers.)

#### APPLICATION

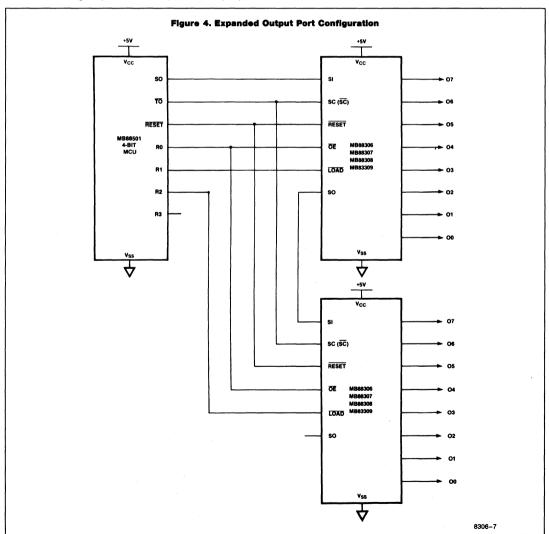

Figure 4 shows an example of an expanded output port configuration

# **ABSOLUTE MAXIMUM RATINGS**

|                                  |                  | Rating               |                       | ,    |                                         |  |

|----------------------------------|------------------|----------------------|-----------------------|------|-----------------------------------------|--|

| Parameter                        | Symbol           | Min                  | Max                   | Unit | Remarks                                 |  |

| Supply Voltage                   | V <sub>CC</sub>  | V <sub>SS</sub> -0.3 | V <sub>SS</sub> +7.0  | ٧    |                                         |  |

| Input Voltage                    | V <sub>IN</sub>  | V <sub>SS</sub> -0.3 | V <sub>SS</sub> +7.0  | V    | Should not exceed V <sub>CC</sub> +0.3V |  |

| Output Voltage                   | V <sub>OUT</sub> | V <sub>SS</sub> -0.3 | V <sub>SS</sub> + 7.0 | V    | Should not exceed V <sub>CC</sub> +0.3V |  |

| Output Low Current               | l <sub>OL</sub>  |                      | 20                    | mA   |                                         |  |

| Total Output<br>Low Current      | ΣI <sub>OL</sub> |                      | 60                    | mA   |                                         |  |

| Power Dissipation                | P <sub>D</sub>   | -                    | 200                   | mW   |                                         |  |

| Operating Ambient<br>Temperature | T <sub>A</sub>   | -40                  | +85                   | °C   |                                         |  |

| Storage Temperature              | T <sub>STG</sub> | -55                  | + 150                 | •c   |                                         |  |

#### Note:

Permanent device damage may occur if the above ABSOLUTE MAXIMUM RATINGS are exceeded. Functional operation should be restricted to the conditions as detailed in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# RECOMMENDED OPERATING CONDITIONS

|                                  |                  | Va                   | lue                  |      |                                         |  |  |

|----------------------------------|------------------|----------------------|----------------------|------|-----------------------------------------|--|--|

| Parameter                        | Symbol           | Min                  | Max                  | Unit | Remarks                                 |  |  |

| Supply Voltage                   | Vcc              | 4.5                  | 5.5                  | ٧    | Guaranteed range                        |  |  |

| oupply voltage                   | V <sub>SS</sub>  | 0                    | 0                    | ٧    |                                         |  |  |

| Input High Voltage               | V <sub>IH</sub>  | 0.7V <sub>CC</sub>   | V <sub>CC</sub> +0.3 | ٧    | Non-hysteresis inputs: SI, OE           |  |  |

| input riigii voitago             | V <sub>IHS</sub> | 0.8V <sub>CC</sub>   | V <sub>CC</sub> +0.3 | ٧    | Hysteresis inputs: RESET, LOAD, SC (SC) |  |  |

| Input Low Voltage                | V <sub>IL</sub>  | V <sub>SS</sub> -0.3 | 0.3V <sub>CC</sub>   | V    | Non-hysteresis inputs: SI, OE           |  |  |

| mput 2011 Voltago                | V <sub>ILS</sub> | V <sub>SS</sub> -0.3 | 0.2V <sub>CC</sub>   | ٧    | Hysteresis inputs: RESET, LOAD, SC (SC) |  |  |

| Operating Ambient<br>Temperature | TA               | -40                  | + 85                 | °C   |                                         |  |  |

# DC CHARACTERISTICS

(Recommended operating conditions unless otherwise noted)

|                                             |                 |                                 |                                                                                                                                                                  | Value |      |     |      |

|---------------------------------------------|-----------------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-----|------|

| Parameter                                   | Symbol          | Pin                             | Condition                                                                                                                                                        | Min   | Тур  | Max | Unit |

| Output High Voltage                         | V <sub>OH</sub> | 07-00 <sup>1</sup> , SO         | $V_{CC} = 4.5V, I_{OH} = -200 \mu A$                                                                                                                             | 2.4   |      |     | ٧    |

|                                             | •оп             | 0. 00,00                        | $V_{CC} = 4.5V, I_{OH} = -10 \mu A$                                                                                                                              | 4.0   |      |     | V    |

|                                             |                 |                                 | $V_{CC} = 4.5V, I_{OL} = 1.8 \text{ mA}$                                                                                                                         |       |      | 0.4 | ٧    |

| Output Low Voltage                          | V <sub>OL</sub> | 07-00, SO                       | V <sub>CC</sub> = 4.5V, I <sub>OL</sub> = 5.0 mA                                                                                                                 |       |      | 0.6 | ٧    |

|                                             |                 |                                 | $V_{CC} = 4.5V, I_{OL} = 15 \text{ mA}$                                                                                                                          | _     |      | 1.2 | ٧    |

| Input Leakage<br>Current                    | I <sub>IL</sub> | SI, SC, (SC)<br>RESET, LOAD, OE | V <sub>CC</sub> = 5.5V, V <sub>IN</sub> = 0.4V                                                                                                                   |       |      | -10 | μΑ   |

| High-Impedance<br>Output Leakage<br>Current | loz             | O7-O0 <sup>1</sup>              | V <sub>CC</sub> = 5.5V,<br>V <sub>IN</sub> = 0V to 5.5V,<br>Off State                                                                                            |       |      | ±10 | μΑ   |

| Open-Drain<br>Output Leakage<br>Current     | lleak           | 07-00², SO                      | $V_{CC} = 5.5V$ ,<br>$V_{IN} = 5.5V$ ,<br>Off State                                                                                                              |       |      | 10  | μΑ   |

| Supply Current                              | lcc             | V <sub>CC</sub>                 | V <sub>CC</sub> = 5.0V (Typ),<br>5.5V (Max), f <sub>C</sub> = 2 MHz,<br>All Outputs Open and<br>All Inputs Pulled<br>Up/Down to V <sub>CC</sub> /V <sub>SS</sub> |       | '100 | 200 | μΑ   |

#### Notes:

- 1. This parameter is specified for MB88307/MB88309 (CMOS 3-state output).

- 2. This parameter is specified for MB88306/MB88308 (NMOS open-drain output).

### **AC CHARACTERISTICS**

(Recommended operating conditions unless otherwise noted)

# **Input Timing Requirements**

|                               |                 | Pin                                                  | Condition           |     |     |      |      |

|-------------------------------|-----------------|------------------------------------------------------|---------------------|-----|-----|------|------|

| Parameter                     | Symbol          |                                                      |                     | Min | Тур | Max  | Unit |

| Shift Clock Frequency         | fc              | SC (SC)                                              |                     |     |     | 2    | MHz  |

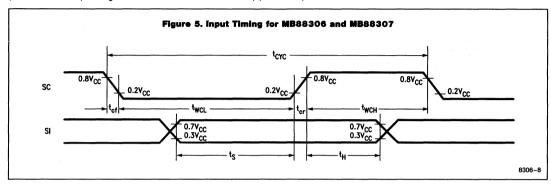

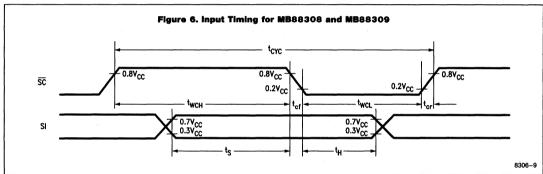

| Shift Clock Cycle Time        | tcyc            | SC (SC)                                              | Fig. 5 (Fig. 6)     | 0.5 |     |      | μs   |

| Shift Clock Pulse Width       | twch            | SC (SC)                                              | Fig. 5 (Fig. 6)     | 200 |     |      | ns   |

| Offic Glook Fallo Wilder      | twcL            | 00 (00)                                              | - i.g. 5 (i.i.g. 5) |     |     |      |      |

| Shift Clock Rise/Fall Times   | t <sub>cr</sub> | t <sub>cf</sub> SC ( <del>SC</del> ) Fig. 5 (Fig. 6) | 10                  |     | 100 | ns   |      |

| Office Glock (1800) Can Timod | t <sub>cf</sub> |                                                      | . ig. 5 (i ig. 5)   |     |     | 1.00 |      |

| Input Data Setup Time         | ts              | SI                                                   | Fig. 5 (Fig. 6)     | 100 |     |      | ns   |

| Input Data Hold Time          | ۲н              | SI                                                   | Fig. 5 (Fig. 6)     | 50  |     |      | ns   |

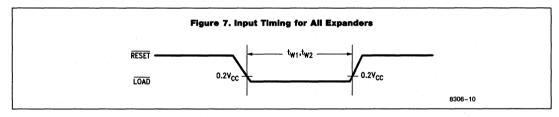

| Reset Pulse Width             | t <sub>W1</sub> | RESET                                                | Fig. 7              | 100 |     |      | ns   |

| Load Pulse Width              | t <sub>W2</sub> | LOAD                                                 | Fig. 7              | 200 |     |      | ns   |

# **AC CHARACTERISTICS**

(Recommended operating conditions unless otherwise noted) (Continued)

#### **AC CHARACTERISTICS**

(Recommended operating conditions unless otherwise noted) (Continued)

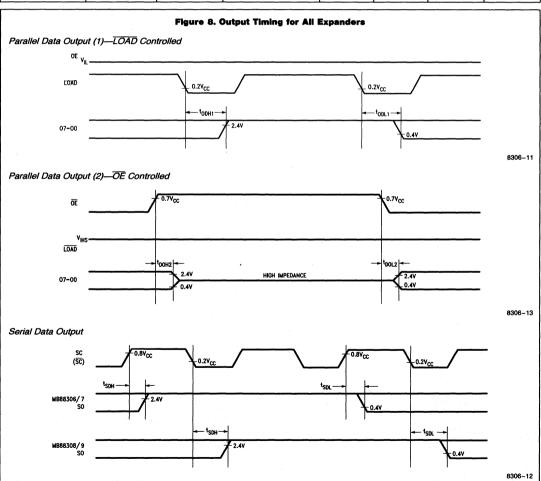

# **Output Timing Responses**

| Parameter                            | Symbol            | Pin   | Condition                                     |     |     |     |      |

|--------------------------------------|-------------------|-------|-----------------------------------------------|-----|-----|-----|------|

|                                      |                   |       |                                               | Min | Тур | Max | Unit |

| Parallel Data Output Delay Time  too | t <sub>ODH1</sub> |       | O7-O0  Output Load: 50 pF + 1.2 kΩ See Fig. 8 |     |     | 500 | ns   |

|                                      | t <sub>ODL1</sub> | 07-00 |                                               |     |     | 200 | ns   |

|                                      | t <sub>DOH2</sub> |       |                                               |     |     | 500 | ns   |

|                                      | t <sub>DOL2</sub> |       |                                               |     |     | 200 | ns   |

| Serial Data<br>Output Delay          | <sup>t</sup> SDH  | so    |                                               |     |     | 500 | ns   |

| Time                                 | t <sub>SDL</sub>  |       |                                               |     |     | 200 | ns   |