# **SPANSION™ MCP**

#### **Data Sheet**

September 2003

This document specifies SPANSION<sup>™</sup> memory products that are now offered by both Advanced Micro Devices and Fujitsu. Although the document is marked with the name of the company that originally developed the specification, these products will be offered to customers of both AMD and Fujitsu.

#### **Continuity of Specifications**

There is no change to this datasheet as a result of offering the device as a SPANSION<sup>™</sup> product. Future routine revisions will occur when appropriate, and changes will be noted in a revision summary.

#### **Continuity of Ordering Part Numbers**

AMD and Fujitsu continue to support existing part numbers beginning with "Am" and "MBM". To order these products, please use only the Ordering Part Numbers listed in this document.

#### For More Information

Please contact your local AMD or Fujitsu sales office for additional information about SPANSION<sup>™</sup> memory solutions.

Stacked MCP (Multi-Chip Package) FLASH MEMORY & SRAM cmos

# 64M (×16) FLASH MEMORY & 8M (×16) SRAM

# MB84SD23280FA/MB84SD23280FE-70

#### **■ FEATURES**

- Power supply voltage of 1.65 V to 1.95 V

- High performance

70 ns maximum access time (Flash)

70 ns maximum access time (SRAM)

- Operating Temperature -30 °C to +85 °C

- Package 73-ball FBGA

(Continued)

#### **■ PRODUCT LINEUP**

|                              | Flash Memory                         | SRAM                                 |

|------------------------------|--------------------------------------|--------------------------------------|

| Supply Voltage (V)           | $Vccf^* = 1.8 V_{-0.15 V}^{+0.15 V}$ | $Vccs^* = 1.8 V_{-0.15 V}^{+0.15 V}$ |

| Max Address Access Time (ns) | 70                                   | 70                                   |

| Max CE Access Time (ns)      | 70                                   | 70                                   |

| Max OE Access Time (ns)      | 20                                   | 35                                   |

<sup>\*:</sup> Both Vccf and Vccs must be in recommended operation range when either part is being accessed.

#### ■ PACKAGE

(Continued)

#### • FLASH MEMORY

- 0.17 μm process technology

- Simultaneous Read/Write operation (Dual Bank)

- FlexBank™\*¹

Bank A: 16M bit (16KB  $\times$  4 and 64KB  $\times$  31)

Bank B: 16M bit  $(64KB \times 32)$ Bank C: 16M bit  $(64KB \times 32)$

Bank D: 16M bit (16KB  $\times$  4 and 64KB  $\times$  31)

- Minimum 100,000 program/erase cycles

- Sector Erase Architecture

Four 8K words, a hundred twenty-eight 32K words sectors.

Any combination of sectors can be concurrently erased. Also supports full chip erase.

WP Input Pin

At  $V_{IL}$ , allows protection of all sectors, regardless of sector protection/unprotection status At  $V_{IH}$ , allows removal of sector protection

Embedded Erase<sup>™ \*2</sup> Algorithms

Automatically preprograms and erases the chip or any sector

• Embedded Program™ \*2 Algorithms

Automatically writes and verifies data at specified address

- Data Polling and Toggle Bit feature for detection of program or erase cycle completion

- Automatic sleep mode

When address remain stable, the device automatically switches itself to low power mode

- Low Vcc write inhibit

- Erase Suspend/Resume

Suspends the erase operation to allow a read data and/or program in another sector within the same device resumes the erase operation

Sector Protection

Software command sector locking

Please Refer to "MBM29BS64LF" Datasheet in Detailed Function

#### SRAM

#### • Power Dissipation

Operating: 50 mA Max Standby :15 µA Max

- Power Down Features using CE1s and CE2s

- Data Retention Supply Voltage: 1.0 V to 1.95 V

- CE1s and CE2s Chip Select

- Byte Data Control: LB (DQ7 to DQ0), UB (DQ15 to DQ8)

<sup>\*1:</sup> FlexBank™ is a trademark of Fujitsu Limited, Japan.

<sup>\*2:</sup> Embedded Erase™ and Embedded Program™ are trademarks of Advanced Micro Devices, Inc.

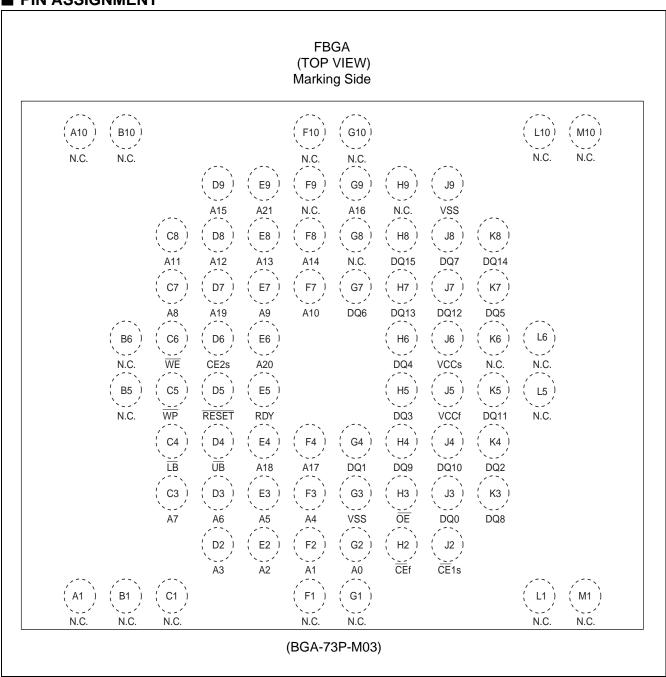

#### **■ PIN ASSIGNMENT**

#### **■ PIN DESCRIPTION**

### **Pin Configuration**

| Pin Name                            | Function                                | Input/Output |

|-------------------------------------|-----------------------------------------|--------------|

| A <sub>18</sub> to A <sub>0</sub>   | Address Inputs (Common)                 | I            |

| A21, A20, A19                       | Address Inputs (Flash)                  | I            |

| DQ <sub>15</sub> to DQ <sub>0</sub> | Data Inputs/Outputs (Common)            | I/O          |

| CEf                                 | Chip Enable (Flash)                     | I            |

| CE1s                                | Chip Enable (SRAM)                      | I            |

| CE2s                                | Chip Enable (SRAM)                      | I            |

| ŌĒ                                  | Output Enable (Common)                  | I            |

| WE                                  | Write Enable (Common)                   | I            |

| RDY                                 | Ready Outputs (Flash) Open Drain Output | 0            |

| ŪB                                  | Upper Byte Control (SRAM)               | I            |

| LB                                  | Lower Byte Control (SRAM)               | I            |

| RESET                               | Hardware Reset Pin (Flash)              | I            |

| WP                                  | Write Protect (Flash)                   | I            |

| N.C.                                | No Internal Connection                  | _            |

| Vss                                 | Device Ground (Common)                  | Power        |

| Vccf                                | Device Power Supply (Flash)             | Power        |

| Vccs                                | Device Power Supply (SRAM)              | Power        |

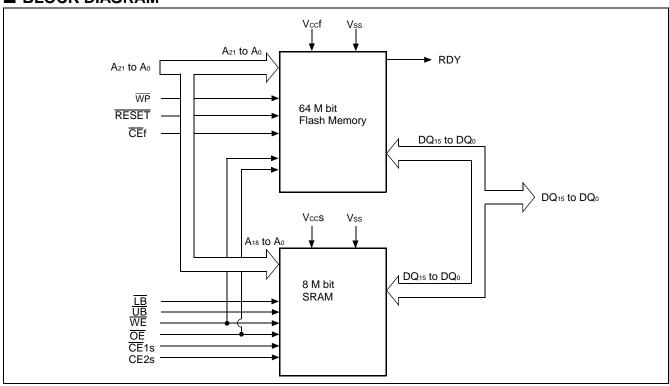

### **■ BLOCK DIAGRAM**

#### **■ DEVICE BUS OPERATIONS**

#### **User Bus Operations**

| Operation*1, *3                        | CEf                                                                                            | CE1s   | CE2s   | ΟE | WE   | LB             | UB           | DQ7 to<br>DQ₀ | DQ <sub>15</sub> to<br>DQ <sub>8</sub> | RESET | WP*4 |   |  |  |   |   |   |              |              |  |  |  |

|----------------------------------------|------------------------------------------------------------------------------------------------|--------|--------|----|------|----------------|--------------|---------------|----------------------------------------|-------|------|---|--|--|---|---|---|--------------|--------------|--|--|--|

| Full Standby                           | Н                                                                                              | H<br>X | X<br>L | Х  | Х    | Х              | Х            | High-Z        | High-Z                                 | Н     | Х    |   |  |  |   |   |   |              |              |  |  |  |

|                                        | Н                                                                                              | L      | Н      | Н  | Н    | Χ              | Х            | High-Z        | High-Z                                 |       |      |   |  |  |   |   |   |              |              |  |  |  |

| Output Disable                         | П                                                                                              | L      | П      | Χ  | Х    | Н              | Н            | High-Z        | High-Z                                 | H     | Х    |   |  |  |   |   |   |              |              |  |  |  |

| Output Disable                         | L                                                                                              | Н      | Х      | Н  | Н    | Х              | Х            | High-Z        | High-Z                                 |       | ^    |   |  |  |   |   |   |              |              |  |  |  |

|                                        | _                                                                                              | X      | L      | 11 | 11   |                | ^            | r iigii-Z     | r iigii-z                              |       |      |   |  |  |   |   |   |              |              |  |  |  |

| Read from Flash*2                      | ead from Flash*2 $\qquad \qquad L \qquad \frac{H \qquad X}{X \qquad \qquad L} \qquad \qquad L$ | 1      | LH     | Х  | x x  | D <sub>о</sub> | <b>D</b> оит | Н             | Χ                                      |       |      |   |  |  |   |   |   |              |              |  |  |  |

| Read Holli Flash                       |                                                                                                | Х      | L      |    | - '' |                |              | 2001          | 2001                                   |       |      |   |  |  |   |   |   |              |              |  |  |  |

| Write to Flash                         | L                                                                                              | H X    | Х      | H  | LX   | X              | Х            | Din           | Din                                    | н     | Н    |   |  |  |   |   |   |              |              |  |  |  |

| Willo to Flacin                        |                                                                                                | _      | _      |    | _    | _              | _            | _             |                                        | _     |      | _ |  |  | _ | Х | L | ^            | Dii(         |  |  |  |

|                                        |                                                                                                |        |        |    |      |                |              |               |                                        |       |      |   |  |  |   | L | L | <b>D</b> оит | <b>D</b> оит |  |  |  |

| Read from SRAM                         | Н                                                                                              | L      | Н      | L  | Н    | Н              | L            | High-Z        | <b>D</b> оит                           | Н     | X    |   |  |  |   |   |   |              |              |  |  |  |

|                                        |                                                                                                |        |        |    |      | L              | Н            | <b>D</b> оит  | High-Z                                 |       |      |   |  |  |   |   |   |              |              |  |  |  |

|                                        |                                                                                                |        |        |    |      | L              | L            | Din           | Din                                    |       |      |   |  |  |   |   |   |              |              |  |  |  |

| Write to SRAM                          | Н                                                                                              | L      | Н      | Χ  | L    | Н              | L            | High-Z        | Din                                    | Н     | X    |   |  |  |   |   |   |              |              |  |  |  |

|                                        |                                                                                                |        |        |    |      | L              | Н            | Din           | High-Z                                 |       |      |   |  |  |   |   |   |              |              |  |  |  |

| Flash All Sector Write<br>Protection*4 | Х                                                                                              | Х      | Х      | Х  | Х    | Х              | Х            | Х             | Х                                      | Н     | L    |   |  |  |   |   |   |              |              |  |  |  |

| Flash Hardware Reset                   | Х                                                                                              | Н      | Х      | Х  | Х    | Х              | Х            | High-Z        | High-Z                                 | L     | Х    |   |  |  |   |   |   |              |              |  |  |  |

| Tidon Flandware Neset                  | ^                                                                                              | X      | L      | ^  | ^    | ^              | ^            | A Filgri-Z    | riigii-Z                               | L     | ^    |   |  |  |   |   |   |              |              |  |  |  |

Legend :  $L = V_{IL}$ ,  $H = V_{IH}$ ,  $X = V_{IL}$  or  $V_{IH}$ . See " $\blacksquare$ DC CHARACTERISTICS" for voltage levels.

<sup>\*1:</sup> Other operations except for this indicated table are prohibited.

<sup>\*2:</sup> Do not apply  $\overline{CE}f = V_{IL}$ ,  $\overline{CE}1s = V_{IL}$  and  $CE2s = V_{IH}$  all at once.

<sup>\*3:</sup>  $\overline{WE}$  can be  $V_{IL}$  if  $\overline{OE}$  is  $V_{IL}$ ,  $\overline{OE}$  at  $V_{IH}$  initiates the write operations.

<sup>\*4:</sup> At  $\overline{WP}$ =V<sub>IL</sub>, all sectors are protected.

#### ■ ABSOLUTE MAXIMUM RATINGS

| Parameter                                 | Symbol | Rat  | Unit       |       |

|-------------------------------------------|--------|------|------------|-------|

| raiametei                                 | Symbol | Min  | Max        | Offic |

| Storage Temperature                       | Tstg   | -40  | +125       | °C    |

| Ambient Temperature with Power Applied    | TA     | -30  | +85        | °C    |

| Voltage with Respect to Ground All pins * | Vin    | -0.3 | Vccf + 0.1 | V     |

| Voltage with Respect to Ground All pins   | Vouт   | -0.3 | Vccs + 0.1 | V     |

| Vccf Supply *                             | Vccf   | -0.2 | +2.5       | V     |

| Vccs Supply *                             | Vccs   | -0.5 | +2.5       | V     |

<sup>\*:</sup> Minimum DC voltage on input or I/O pins are -0.5 V. During voltage transitions, inputs may negative overshoot Vss to -2.0 V for periods of up to 20 ns. Maximum DC voltage on input and I/O pins are Vcc +0.5 V. During voltage transitions, outputs may positive overshoot to Vcc +2.0 V for periods of up to 20 ns.

WARNING: Semiconductor devices can be permanently damaged by application of stress (voltage, current, temperature, etc.) in excess of absolute maximum ratings. Do not exceed these ratings.

#### ■ RECOMMENDED OPERATING CONDITIONS

| Parameter            | Symbol | Va    | Unit  |       |

|----------------------|--------|-------|-------|-------|

| Farameter            | Symbol | Min   | Max   | Oilit |

| Ambient Temperature  | TA     | -30   | +85   | °C    |

| Vccf Supply Voltages | Vccf   | +1.65 | +1.95 | V     |

| Vccs Supply Voltages | Vccs   | +1.65 | +1.95 | V     |

WARNING: The recommended operating conditions are required in order to ensure the normal operation of the semiconductor device. All of the device's electrical characteristics are warranted when the device is operated within these ranges.

> Always use semiconductor devices within their recommended operating condition ranges. Operation outside these ranges may adversely affect reliability and could result in device failure.

> No warranty is made with respect to uses, operating conditions, or combinations not represented on the data sheet. Users considering application outside the listed conditions are advised to contact their FUJITSU representatives beforehand.

#### **■ DC CHARACTERISTICS\*1,\*2**

| Davamatar                                            | Cumbal             |                                                                                                                            | Took Cond                                                                                                                                  | :4:                 |            |          | Value |          | l lm!4 |

|------------------------------------------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------------|----------|-------|----------|--------|

| Parameter                                            | Symbol             | Test Conditions                                                                                                            |                                                                                                                                            | Min                 | Тур        | Max      | Unit  |          |        |

| Input Leakage Current                                | Li                 | VIN = Vss                                                                                                                  | to Vccf, Vccs                                                                                                                              |                     |            | -1.0     |       | +1.0     | μΑ     |

| Output Leakage Current                               | ILO                | Vout = Vs                                                                                                                  | ss to Vccf, Vccs                                                                                                                           |                     |            | -1.0     | _     | +1.0     | μΑ     |

| Flash Vcc Active Read                                | Icc1f              | <u>CE</u> f _ \/                                                                                                           | ., <del>OE</del> = V <sub>IH</sub> , <del>W</del> E                                                                                        | =f _ \/             | 5 MHz      |          | 12    | 16       | mA     |

| Current *3                                           | ICC1I              | CEI = VII                                                                                                                  | _, OE = VIH, VVI                                                                                                                           | _1 = VIH            | 1 MHz      |          | 3.3   | 5        | ША     |

| Flash Vcc Active Write<br>Current *4                 | Icc2f              | <del>CE</del> f = Vιι                                                                                                      | , $\overline{OE} = V_IH,V_P_I$                                                                                                             | > = V <sub>IH</sub> |            | _        | 15    | 40       | mA     |

| Flash Vcc Active Current (Read-While-Program)*5      | Іссзf              | CEf = VII                                                                                                                  | ., <del>ОЕ</del> = Vін                                                                                                                     |                     |            | _        | 25    | 60       | mA     |

| Flash Vcc Active Current (Read-While-Erase)*5        | Icc4f              | <del>CE</del> f = Vιι                                                                                                      | ., <del>OE</del> = V <sub>IH</sub>                                                                                                         |                     |            |          | 25    | 60       | mA     |

| SRAM Vcc Active Current                              | Icc1S              |                                                                                                                            | $\frac{V_{\text{CCS}} = V_{\text{CCS}} \text{ Max},}{\overline{\text{CE}} 1s = V_{\text{IL}}, \text{CE2s} = V_{\text{IH}}}$ toycle =10 MHz |                     |            | _        | _     | 50       | mA     |

| SRAM Vcc Active Current                              | Icc2S              | <u>CE</u> 1s = 0                                                                                                           | ).2 V,                                                                                                                                     | tcycle =            | 10 MHz     | _        | _     | 50       | mA     |

| SKAWI VCC ACTIVE CUITETT                             | 10025              | CE2s = \                                                                                                                   | √ccs – 0.2 V                                                                                                                               | tcycle =            | 1 MHz      | _        | _     | 10       | mA     |

| Flash Vcc Standby Current                            | I <sub>SB1</sub> f | $V_{ccf} = V_{ccf} Max, \overline{CEf} = \overline{RESET}$<br>= $V_{cc} \pm 0.2 \text{ V},$<br>$V_{IN} \leq 0.2 \text{ V}$ |                                                                                                                                            |                     |            | 0.2      | 10    | μA       |        |

| Flash Vcc <u>Standby</u> Current (Standby, RESET) *6 | Is <sub>B2</sub> f | Vccf = Vc                                                                                                                  | ccf Max, RESE                                                                                                                              | T = VIL             |            | _        | 0.2   | 10       | μA     |

| SRAM Vcc Standby Current                             | I <sub>SB1</sub> S | <u>CE</u> 1s ≥ \                                                                                                           | /ccs – 0.2 V, CI                                                                                                                           | <b>E2s ≥ V</b> c    | cs – 0.2 V | _        | _     | 14       | μΑ     |

| SRAM Vcc Standby Current                             | I <sub>SB2</sub> S | CE2s <u>&lt;</u> (                                                                                                         | ).2 V                                                                                                                                      |                     |            | _        | _     | 14       | μΑ     |

| Input Low Level                                      | Vıl                |                                                                                                                            | _                                                                                                                                          |                     |            | -0.2     | _     | 0.2      | V      |

| Input High Level                                     | VIH                |                                                                                                                            |                                                                                                                                            |                     | Flash      | Vccf-0.2 | _     | Vccf+0.2 | ٧      |

| Imput riigii Levei                                   | VIH                | SRAM                                                                                                                       |                                                                                                                                            | 1.6                 | _          | Vccs+0.2 | V     |          |        |

| Flash Output Low Level                               | Vol                | Flash Vccf = Vccf Min, IoL = 1.0 mA                                                                                        |                                                                                                                                            | _                   | _          | 0.1      | V     |          |        |

| SRAM Output Low Level                                | VOL                | SRAM Vccs = Vccs Min, loL = 2.1 mA                                                                                         |                                                                                                                                            | _                   | _          | 0.4      | V     |          |        |

| Flash Output High Level                              | Vон                | Flash Vccf = Vccf Min, IoH = -0.1 mA                                                                                       |                                                                                                                                            | Vccf-0.1            | _          | _        | V     |          |        |

| SRAM Output High Level                               | VOH                | SRAM                                                                                                                       | Vccs = Vccs N                                                                                                                              | /lin, Іон =         | -0.5 mA    | Vccs-0.5 |       | _        | V      |

| Flash Low Vcc Lock-Out<br>Voltage                    | VLKO               |                                                                                                                            | _                                                                                                                                          |                     |            | 1.0      | _     | 1.4      | ٧      |

<sup>\*1 :</sup> All voltage are referenced to Vss.

<sup>\*2 :</sup> lout depends on the output load conditions.

<sup>\*3 :</sup> The lcc current listed includes both the DC operating current and the frequency dependent component.

<sup>\*4:</sup> Icc active while Embedded Algorithm (program or erase) is in progress.

<sup>\*5 :</sup> Embedded Algorithm (program or erase) is in progress. (@5 MHz)

<sup>\*6 :</sup> Automatic sleep mode enables the low power mode when address remain stable for tacc + 60 ns.

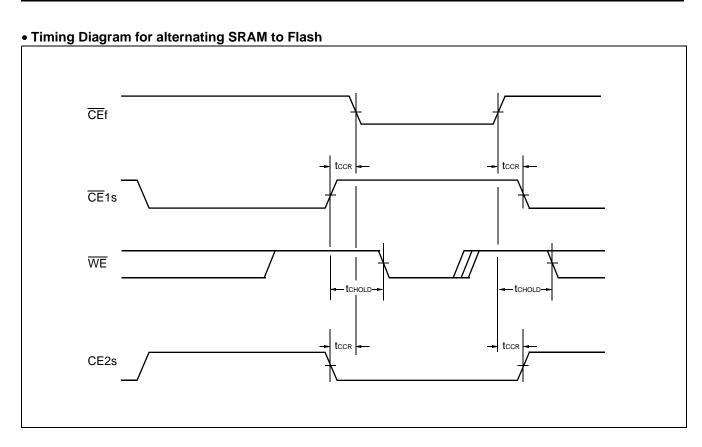

### **■** AC CHARACTERISTICS

### • CE Timing

| Parameter       | Syn   | nbol           | Condition | Value | Unit  |

|-----------------|-------|----------------|-----------|-------|-------|

| raiailletei     | JEDEC | Standard       | Condition | Min   | Offic |

| CE Recover Time | _     | tccr           | _         | 0     | _     |

| CE Hold Time    | _     | <b>t</b> chold | _         | 3     | _     |

#### ■ SECTOR LOCK/UNLOCK COMMAND

The sector lock/unlock command sequence allows the system to determine which sectors are protected from accidental writes. When the device is first powered up, all sectors are locked. To unlock a sector, the system must write the sector lock/unlock command sequence. Two cycles are first written: addresses are don't care and data is 60h. During the third cycle, the sector address (SLA) and unlock command (60h) is written, while specifying with address  $A_6$  whether that sector should be locked ( $A_6 = V_{IL}$ ) or unlocked ( $A_6 = V_{IH}$ ). After the third cycle, the system can continue to lock or unlock additional cycles, or exit the sequence by writing F0h (reset command).

#### • Flash Characteristics

Please refer to "■ 64M FLASH MEMORY for MCP 1.8 V".

#### • SRAM Characteristics

Please refer to "■ 8M SRAM for MCP 1.8 V".

#### ■ 64M FLASH MEMORY for MCP 1.8 V

- 1. Flexible Sector-erase Architecture on FLASH MEMORY

- Sixteen 4K words, and one hundred twenty-six 32K words.

- Individual-sector, multiple-sector, or bulk-erase capability.

| ▲          | SA0 :16KB                  | 000000h<br>002000h | <b>A</b>         | SA67:64KB                  | 200000h<br>208000h |

|------------|----------------------------|--------------------|------------------|----------------------------|--------------------|

|            | SA1 :16KB                  | 002000h<br>004000h |                  | SA68 : 64KB                | 210000h            |

|            | SA2 : 16KB                 | 006000h            |                  | SA69 : 64KB                | 218000h            |

|            | SA3 : 16KB                 | 008000h            |                  | SA70 : 64KB                | 220000h            |

|            | SA4 : 64KB                 | 010000h            |                  | SA71 : 64KB                | 228000h            |

|            | SA5 : 64KB<br>SA6 : 64KB   | 018000h            |                  | SA72 : 64KB<br>SA73 : 64KB | 230000h            |

|            | SA7 : 64KB                 | 020000h            |                  | SA74 : 64KB                | 238000h            |

|            | SA8 : 64KB                 | 028000h            |                  | SA75 : 64KB                | 240000h            |

|            | SA9 : 64KB                 | 030000h            |                  | SA76 : 64KB                | 248000h            |

|            | SA10 : 64KB                | 038000h            |                  | SA77 : 64KB                | 250000h            |

|            | SA11:64KB                  | 040000h            |                  | SA78 : 64KB                | 258000h<br>260000h |

| _ [        | SA12:64KB                  | 048000h            |                  | SA79 : 64KB                | 268000h            |

|            | SA13:64KB                  | 050000h<br>058000h | ω                | SA80 : 64KB                | 270000h            |

| BANK       | SA14:64KB                  | 060000h            | BANK             | SA81 : 64KB                | 278000h            |

| <b>Z</b> L | SA15 : 64KB                | 068000h            | Z                | SA82 : 64KB                | 280000h            |

| -          | SA16 : 64KB                | 070000h            | <u></u>          | SA83 : 64KB                | 288000h            |

| ш          | SA17 : 64KB                | 078000h            | <b>"</b>         | SA84 : 64KB                | 290000h            |

| , <u> </u> | SA18 : 64KB                | 080000h            | ı                | SA85 : 64KB                | 298000h            |

|            | SA19 : 64KB                | 088000h            |                  | SA86 : 64KB                | 2A0000h            |

|            | SA20 : 64KB<br>SA21 : 64KB | 090000h            |                  | SA87 : 64KB<br>SA88 : 64KB | 2A8000h            |

|            | SA21 : 64KB<br>SA22 : 64KB | 098000h            | <del>     </del> | SA88 : 64KB<br>SA89 : 64KB | 2B0000h            |

|            | SA22 : 64KB                | 0A0000h            | <del>     </del> | SA90 : 64KB                | 2B8000h            |

|            | SA23 : 64KB                | 0A8000h            | <del>     </del> | SA90 : 64KB                | 2C0000h            |

|            | SA25 : 64KB                | 0B0000h            |                  | SA92 : 64KB                | 2C8000h            |

|            | SA26 : 64KB                | 0B8000h            |                  | SA93 : 64KB                | 2D0000h            |

|            | SA27 : 64KB                | 0C0000h            |                  | SA94 : 64KB                | 2D8000h            |

|            | SA28 : 64KB                | 0C8000h            |                  | SA95 : 64KB                | 2E0000h            |

|            | SA29 : 64KB                | 0D0000h            |                  | SA96 : 64KB                | 2E8000h            |

|            | SA30 : 64KB                | 0D8000h            |                  | SA97:64KB                  | 2F0000h<br>2F8000h |

|            | SA31 : 64KB                | 0E0000h            |                  | SA98 : 64KB                | 300000h            |

|            | SA32 : 64KB                | 0E8000h<br>0F0000h |                  | SA99 : 64KB                | 308000h            |

| L          | SA33 : 64KB                | 0F8000h            |                  | SA100: 64KB                | 310000h            |

|            | SA34 : 64KB                | 100000h            |                  | SA101: 64KB                | 318000h            |

| <b>↑</b> ⊢ | SA35 : 64KB                | 108000h            |                  | SA102: 64KB                | 320000h            |

| - 1 ⊢      | SA36 : 64KB                | 110000h            |                  | SA103: 64KB                | 328000h            |

| - 1 ⊢      | SA37 : 64KB                | 118000h            |                  | SA104: 64KB                | 330000h            |

| - 1 ⊢      | SA38 : 64KB<br>SA39 : 64KB | 120000h            |                  | SA105: 64KB<br>SA106: 64KB | 338000h            |

|            | SA40 : 64KB                | 128000h            |                  | SA106. 64KB<br>SA107: 64KB | 340000h            |

| - 1 ⊢      | SA40 : 64KB                | 130000h            |                  | SA107: 64KB                | 348000h            |

|            | SA41 : 64KB                | 138000h            |                  | SA108: 64KB                | 350000h            |

|            | SA43 : 64KB                | 140000h            |                  | SA110: 64KB                | 358000h            |

|            | SA44 : 64KB                | 148000h            |                  | SA111: 64KB                | 360000h            |

|            | SA45 : 64KB                | 150000h            |                  | SA112: 64KB                | 368000h            |

|            | SA46 : 64KB                | 158000h            |                  | SA113: 64KB                | 370000h            |

|            | SA47:64KB                  | 160000h            |                  | SA114: 64KB                | 378000h            |

| . [        | SA48 : 64KB                | 168000h<br>170000h | '. <u> </u>      | SA115: 64KB                | 380000h<br>388000h |

| $\cup$     | SA49 : 64KB                | 170000h<br>178000h | ⋖ 🗀              | SA116: 64KB                | 390000h            |

| $\prec$    | SA50:64KB                  | 180000h            | <b>Y</b>         | SA117: 64KB                | 398000h            |

| BANK       | SA51 : 64KB                | 188000h            | ANK              | SA118: 64KB                | 3A0000h            |

| , , , , ,  | SA52 : 64KB                | 190000h            | ≴ ⊢              | SA119: 64KB                | 3A8000h            |

| മ          | SA53 : 64KB                | 198000h            | ω                | SA120: 64KB                | 3B0000h            |

| ı  -       | SA54 : 64KB                | 1A0000h            |                  | SA121: 64KB                | 3B8000h            |

|            | SA55 : 64KB                | 1A8000h            |                  | SA122: 64KB                | 3C0000h            |

|            | SA56 : 64KB                | 1B0000h            |                  | SA123: 64KB                | 3C8000h            |

|            | SA57 : 64KB<br>SA58 : 64KB | 1B8000h            |                  | SA124: 64KB<br>SA125: 64KB | 3D0000h            |

| ⊢          | SA50 : 64KB                | 1C0000h            | <del>     </del> | SA125: 64KB                | 3D8000h            |

|            | SA60 : 64KB                | 1C8000h            |                  | SA120: 04RB<br>SA127: 64KB | 3E0000h            |

| -          | SA61 : 64KB                | 1D0000h            |                  | SA128: 64KB                | 3E8000h            |

| -          | SA62 : 64KB                | 1D8000h            |                  | SA129: 64KB                | 3F0000h            |

|            | SA63 : 64KB                | 1E0000h            |                  | SA130: 16KB                | 3F8000h            |

|            | SA64:64KB                  | 1E8000h            |                  | SA131: 16KB                | 3FA000h            |

|            | SA65 : 64KB                | 1F0000h            |                  | SA132: 16KB                | 3FC000h<br>3FE000h |

|            | SA66 : 64KB                | 1F8000h<br>1FFFFFh |                  | SA133: 16KB                | 3FFFFFh            |

|            |                            | HILEFEII           |                  | ·                          | 0                  |

|            |                            |                    |                  |                            |                    |

#### FlexBank™ Architecture

| Bank | Quantity | Size      |

|------|----------|-----------|

| ^    | 4        | 8K words  |

| A    | 31       | 32K words |

| В    | 32       | 32K words |

| С    | 32       | 32K words |

| D    | 31       | 32K words |

| Б    | 4        | 8K words  |

#### • Simultaneous Operation

| Case | Bank 1 Status   | Bank 2 Status   |

|------|-----------------|-----------------|

| 1    | Read mode       | Read mode       |

| 2    | Read mode       | Autoselect mode |

| 3    | Read mode       | Program mode    |

| 4    | Read mode       | Erase mode *    |

| 5    | Autoselect mode | Read mode       |

| 6    | Program mode    | Read mode       |

| 7    | Erase mode *    | Read mode       |

<sup>\*:</sup> By writing erase suspend command on the bank address of sector being erased, the erase operation gets suspended so that it enables reading from or programming the remaining sectors.

Note: Bank 1 and Bank 2 are divided for the sake of convenience at Simultaneous Operation. Actually, the Bank consists of 4 banks, Bank A, Bank B, Bank C and Bank D. Bank Address (BA) meant to specify each of the Banks.

#### • Sector Address Table

| Bank   | Sector | Sector Size | (×16) Address Range |

|--------|--------|-------------|---------------------|

|        | SA0    | 8 Kwords    | 000000h to 001FFFh  |

|        | SA1    | 8 Kwords    | 002000h to 003FFFh  |

|        | SA2    | 8 Kwords    | 004000h to 005FFFh  |

|        | SA3    | 8 Kwords    | 006000h to 007FFFh  |

|        | SA4    | 32 Kwords   | 008000h to 00FFFFh  |

|        | SA5    | 32 Kwords   | 010000h to 017FFFh  |

|        | SA6    | 32 Kwords   | 018000h to 01FFFFh  |

|        | SA7    | 32 Kwords   | 020000h to 027FFFh  |

|        | SA8    | 32 Kwords   | 028000h to 02FFFFh  |

|        | SA9    | 32 Kwords   | 030000h to 037FFFh  |

|        | SA10   | 32 Kwords   | 038000h to 03FFFFh  |

|        | SA11   | 32 Kwords   | 040000h to 047FFFh  |

|        | SA12   | 32 Kwords   | 048000h to 04FFFFh  |

|        | SA13   | 32 Kwords   | 050000h to 057FFFh  |

|        | SA14   | 32 Kwords   | 058000h to 05FFFFh  |

|        | SA15   | 32 Kwords   | 060000h to 067FFFh  |

|        | SA16   | 32 Kwords   | 068000h to 06FFFFh  |

| Bank D | SA17   | 32 Kwords   | 070000h to 077FFFh  |

|        | SA18   | 32 Kwords   | 078000h to 07FFFFh  |

|        | SA19   | 32 Kwords   | 080000h to 087FFFh  |

|        | SA20   | 32 Kwords   | 088000h to 08FFFFh  |

|        | SA21   | 32 Kwords   | 090000h to 097FFFh  |

|        | SA22   | 32 Kwords   | 098000h to 09FFFFh  |

|        | SA23   | 32 Kwords   | 0A0000h to 0A7FFFh  |

|        | SA24   | 32 Kwords   | 0A8000h to 0AFFFFh  |

|        | SA25   | 32 Kwords   | 0B0000h to 0B7FFFh  |

|        | SA26   | 32 Kwords   | 0B8000h to 0BFFFFh  |

|        | SA27   | 32 Kwords   | 0C0000h to 0C7FFFh  |

|        | SA28   | 32 Kwords   | 0C8000h to 0CFFFFh  |

|        | SA29   | 32 Kwords   | 0D0000h to 0D7FFFh  |

|        | SA30   | 32 Kwords   | 0D8000h to 0DFFFFh  |

|        | SA31   | 32 Kwords   | 0E0000h to 0E7FFFh  |

|        | SA32   | 32 Kwords   | 0E8000h to 0EFFFFh  |

|        | SA33   | 32 Kwords   | 0F0000h to 0F7FFFh  |

|        | SA34   | 32 Kwords   | 0F8000h to 0FFFFFh  |

| Bank     | Sector               | Sector Size | (×16) Address Range |

|----------|----------------------|-------------|---------------------|

|          | SA35                 | 32 Kwords   | 100000h to 107FFFh  |

|          | SA36                 | 32 Kwords   | 108000h to 10FFFFh  |

|          | SA37<br>SA38<br>SA39 | 32 Kwords   | 110000h to 117FFFh  |

|          |                      | 32 Kwords   | 118000h to 11FFFFh  |

|          |                      | 32 Kwords   | 120000h to 127FFFh  |

|          | SA40                 | 32 Kwords   | 128000h to 12FFFFh  |

|          | SA41                 | 32 Kwords   | 130000h to 137FFFh  |

|          | SA42                 | 32 Kwords   | 138000h to 13FFFFh  |

|          | SA43                 | 32 Kwords   | 140000h to 147FFFh  |

|          | SA44                 | 32 Kwords   | 148000h to 14FFFFh  |

|          | SA45                 | 32 Kwords   | 150000h to 157FFFh  |

|          | SA46                 | 32 Kwords   | 158000h to 15FFFFh  |

|          | SA47                 | 32 Kwords   | 160000h to 167FFFh  |

|          | SA48                 | 32 Kwords   | 168000h to 16FFFFh  |

|          | SA49                 | 32 Kwords   | 170000h to 177FFFh  |

| Davids C | SA50                 | 32 Kwords   | 178000h to 17FFFFh  |

| Bank C   | SA51                 | 32 Kwords   | 180000h to 187FFFh  |

|          | SA52                 | 32 Kwords   | 188000h to 18FFFFh  |

|          | SA53                 | 32 Kwords   | 190000h to 197FFFh  |

|          | SA54                 | 32 Kwords   | 198000h to 19FFFFh  |

|          | SA55                 | 32 Kwords   | 1A0000h to 1A7FFFh  |

|          | SA56                 | 32 Kwords   | 1A8000h to 1AFFFFh  |

|          | SA57                 | 32 Kwords   | 1B0000h to 1B7FFFh  |

|          | SA58                 | 32 Kwords   | 1B8000h to 1BFFFFh  |

|          | SA59                 | 32 Kwords   | 1C0000h to 1C7FFFh  |

|          | SA60                 | 32 Kwords   | 1C8000h to 1CFFFFh  |

|          | SA61                 | 32 Kwords   | 1D0000h to 1D7FFFh  |

|          | SA62                 | 32 Kwords   | 1D8000h to 1DFFFFh  |

|          | SA63                 | 32 Kwords   | 1E0000h to 1E7FFFh  |

|          | SA64                 | 32 Kwords   | 1E8000h to 1EFFFFh  |

|          | SA65                 | 32 Kwords   | 1F0000h to 1F7FFFh  |

|          | SA66                 | 32 Kwords   | 1F8000h to 1FFFFFh  |

| Bank    | Sector | Sector Size | (×16) Address Range |

|---------|--------|-------------|---------------------|

|         | SA67   | 32 Kwords   | 200000h to 207FFFh  |

|         | SA68   | 32 Kwords   | 208000h to 20FFFFh  |

|         | SA69   | 32 Kwords   | 210000h to 217FFFh  |

|         | SA70   | 32 Kwords   | 218000h to 21FFFFh  |

|         | SA71   | 32 Kwords   | 220000h to 227FFFh  |

|         | SA72   | 32 Kwords   | 228000h to 22FFFFh  |

|         | SA73   | 32 Kwords   | 230000h to 237FFFh  |

|         | SA74   | 32 Kwords   | 238000h to 23FFFFh  |

|         | SA75   | 32 Kwords   | 240000h to 247FFFh  |

|         | SA76   | 32 Kwords   | 248000h to 24FFFFh  |

|         | SA77   | 32 Kwords   | 250000h to 257FFFh  |

|         | SA78   | 32 Kwords   | 258000h to 25FFFFh  |

|         | SA79   | 32 Kwords   | 260000h to 267FFFh  |

|         | SA80   | 32 Kwords   | 268000h to 26FFFFh  |

|         | SA81   | 32 Kwords   | 270000h to 277FFFh  |

| David D | SA82   | 32 Kwords   | 278000h to 27FFFFh  |

| Bank B  | SA83   | 32 Kwords   | 280000h to 287FFFh  |

|         | SA84   | 32 Kwords   | 288000h to 28FFFFh  |

|         | SA85   | 32 Kwords   | 290000h to 297FFFh  |

|         | SA86   | 32 Kwords   | 298000h to 29FFFFh  |

|         | SA87   | 32 Kwords   | 2A0000h to 2A7FFFh  |

|         | SA88   | 32 Kwords   | 2A8000h to 2AFFFFh  |

|         | SA89   | 32 Kwords   | 2B0000h to 2B7FFFh  |

|         | SA90   | 32 Kwords   | 2B8000h to 2BFFFFh  |

|         | SA91   | 32 Kwords   | 2C0000h to 2C7FFFh  |

|         | SA92   | 32 Kwords   | 2C8000h to 2CFFFFh  |

|         | SA93   | 32 Kwords   | 2D0000h to 2D7FFFh  |

|         | SA94   | 32 Kwords   | 2D8000h to 2DFFFFh  |

|         | SA95   | 32 Kwords   | 2E0000h to 2E7FFFh  |

|         | SA96   | 32 Kwords   | 2E8000h to 2EFFFFh  |

|         | SA97   | 32 Kwords   | 2F0000h to 2F7FFFh  |

|         | SA98   | 32 Kwords   | 2F8000h to 2FFFFFh  |

| Bank   | Sector | Sector Size | (×16) Address Range |

|--------|--------|-------------|---------------------|

|        | SA99   | 32 Kwords   | 300000h to 307FFFh  |

|        | SA100  | 32 Kwords   | 308000h to 30FFFFh  |

|        | SA101  | 32 Kwords   | 310000h to 317FFFh  |

|        | SA102  | 32 Kwords   | 318000h to 31FFFFh  |

|        | SA103  | 32 Kwords   | 320000h to 327FFFh  |

|        | SA104  | 32 Kwords   | 328000h to 32FFFFh  |

|        | SA105  | 32 Kwords   | 330000h to 337FFFh  |

|        | SA106  | 32 Kwords   | 338000h to 33FFFFh  |

|        | SA107  | 32 Kwords   | 340000h to 347FFFh  |

|        | SA108  | 32 Kwords   | 348000h to 34FFFFh  |

|        | SA109  | 32 Kwords   | 350000h to 357FFFh  |

|        | SA110  | 32 Kwords   | 358000h to 35FFFFh  |

|        | SA111  | 32 Kwords   | 360000h to 367FFFh  |

|        | SA112  | 32 Kwords   | 368000h to 36FFFFh  |

|        | SA113  | 32 Kwords   | 370000h to 377FFFh  |

|        | SA114  | 32 Kwords   | 378000h to 37FFFFh  |

|        | SA115  | 32 Kwords   | 380000h to 387FFFh  |

| Bank A | SA116  | 32 Kwords   | 388000h to 38FFFFh  |

|        | SA117  | 32 Kwords   | 390000h to 397FFFh  |

|        | SA118  | 32 Kwords   | 398000h to 39FFFFh  |

|        | SA119  | 32 Kwords   | 3A0000h to 3A7FFFh  |

|        | SA120  | 32 Kwords   | 3A8000h to 3AFFFFh  |

|        | SA121  | 32 Kwords   | 3B0000h to 3B7FFFh  |

|        | SA122  | 32 Kwords   | 3B8000h to 3BFFFFh  |

|        | SA123  | 32 Kwords   | 3C0000h to 3C7FFFh  |

|        | SA124  | 32 Kwords   | 3C8000h to 3CFFFFh  |

|        | SA125  | 32 Kwords   | 3D0000h to 3D7FFFh  |

|        | SA126  | 32 Kwords   | 3D8000h to 3DFFFFh  |

|        | SA127  | 32 Kwords   | 3E0000h to 3E7FFFh  |

|        | SA128  | 32 Kwords   | 3E8000h to 3EFFFFh  |

|        | SA129  | 32 Kwords   | 3F0000h to 3F7FFFh  |

|        | SA130  | 8 Kwords    | 3F8000h to 3F9FFFh  |

|        | SA131  | 8 Kwords    | 3FA000h to 3FBFFFh  |

|        | SA132  | 8 Kwords    | 3FC000h to 3FDFFFh  |

|        | SA133  | 8 Kwords    | 3FE000h to 3FFFFFh  |

#### • Sector Protection Verify Autoselect Codes Table

| Туре                   | A21 to A13          | <b>A</b> 7 | <b>A</b> 6 | <b>A</b> 5 | <b>A</b> 4 | <b>A</b> 3 | <b>A</b> 2 | <b>A</b> 1 | Ao | Code (HEX) |

|------------------------|---------------------|------------|------------|------------|------------|------------|------------|------------|----|------------|

| Manufacture's Code     | BA*2                | L          | L          | L          | L          | L          | L          | L          | L  | 04h        |

| Device Code            | BA*2                | L          | L          | L          | L          | L          | L          | L          | Н  | 227Eh      |

| Extended Device Code*1 | BA                  | L          | L          | L          | L          | Н          | Н          | Н          | L  | 2224h      |

| Exterided Device Code  | BA                  | L          | L          | L          | L          | Н          | Н          | Н          | Н  | 2201h      |

| Sector lock/ unlock    | Sector<br>Addresses | L          | L          | L          | L          | L          | L          | Н          | L  | 01h*²      |

Legend: L = V<sub>IL</sub>, H = V<sub>IH</sub>. See "■DC CHARACTERISTICS" for voltage levels.

<sup>\*1:</sup> A read cycle at address (BA) 01h outputs device code. When 227Eh is output, it indicates that two additional codes, called Extended Device Codes, will be required. Therefore the system may continue reading out these Extended Device Codes at the address of (BA) 0Eh, as well as at (BA) 0Fh

<sup>\*2:</sup> Outputs 01h at protected sector group addresses and outputs 00h at unprotected sector group addresses.

#### • Flash Memory Command Definitions

| Command                    | Bus Write<br>Cycles Req'd | First<br>Write |      |       | ond<br>Cycle |              | Write<br>cle | Fourth<br>Cy |      | Fifth<br>Cy |      | Sixth<br>Cy | Write<br>cle |

|----------------------------|---------------------------|----------------|------|-------|--------------|--------------|--------------|--------------|------|-------------|------|-------------|--------------|

| Sequence                   | Cycles Req u              | Addr.          | Data | Addr. | Data         | Addr.        | Data         | Addr.        | Data | Addr.       | Data | Addr.       | Data         |

| Read / Reset               | 1                         | XXXh           | F0h  | RA    | RD           | _            | _            | _            | _    | _           | _    | _           | _            |

| Read / Reset               | 3                         | 555h           | AAh  | 2AAh  | 55h          | 555h         | F0h          | RA           | RD   | _           | _    | _           | _            |

| Autoselect                 | 3                         | 555h           | AAh  | 2AAh  | 55h          | (BA)<br>555h | 90h          | _            | _    | _           | _    | _           | _            |

| Program                    | 4                         | 555h           | AAh  | 2AAh  | 55h          | 555h         | A0h          | PA           | PD   | _           | _    | _           | _            |

| Chip Erase                 | 6                         | 555h           | AAh  | 2AAh  | 55h          | 555h         | 80h          | 555h         | AAh  | 2AAh        | 55h  | 555h        | 10h          |

| Sector Erase               | 6                         | 555h           | AAh  | 2AAh  | 55h          | 555h         | 80h          | 555h         | AAh  | 2AAh        | 55h  | SA          | 30h          |

| Erase Suspend              | 1                         | ВА             | B0h  | _     | _            | _            | _            | _            | _    | _           | _    | _           | _            |

| Erase Resume               | 1                         | ВА             | 30h  | _     | _            | _            | _            | _            | _    | _           | _    | _           | _            |

| Fast Program               | 2                         | XXXh           | A0   | PA    | PD           |              |              |              |      |             |      |             |              |

| Set to Fast Mode           | 3                         | 555h           | AAh  | 2AAh  | 55h          | 555h         | 20h          | _            | _    | _           | _    | _           | _            |

| Reset from Fast<br>Mode *1 | 2                         | ВА             | 90h  | XXXh  | F0h*2        | _            | _            | _            | _    | _           | _    | _           | _            |

| Sector Lock/Unlock         | 3                         | XXXh           | 60h  | XXXh  | 60h          | SLA          | 60h          | _            | _    | _           | _    | _           | _            |

| Query                      | 1                         | (BA)<br>55h    | 98h  | _     | _            | _            | _            | _            | _    | _           | _    | _           | _            |

#### Legend:

- RA = Address of the memory location to be read.

- PA = Address of the memory location to be programmed Addresses are latched on the falling edge of the write pulse.

- SA = Address of the sector to be erased. The combination of A<sub>21</sub>, A<sub>20</sub>, A<sub>19</sub>, A<sub>18</sub>, A<sub>17</sub>, A<sub>16</sub>, A<sub>15</sub>, and A<sub>14</sub> will uniquely select any sector.

- BA = Bank Address. Address setted by A22, A21 will select Bank A, Bank B, Bank C and Bank D.

- SLA = Address of the sector to be locked. Set sector address (SA) and either  $A_6 = 1$  for unlocked or  $A_6 = 0$  for locked.

- RD = Data read from location RA during read operation.

- PD = Data to be programmed at location PA. Data latches on the rising edge of write pulse.

- CR = Configuration Register address bits A<sub>19</sub> to A<sub>12</sub>.

- \*1: This command is valid during Fast Mode.

- \*2: The data "00h" is also acceptable.

- Notes: Address bits A21 to A11 = X = "H" or "L" for all address commands except for PA, SA, BA.

- Bus operations are defined in "■ DEVICE BUS OPERATION".

- Both Read/Reset commands are functionally equivalent, resetting the device to the read mode.

#### 2. AC Characteristics

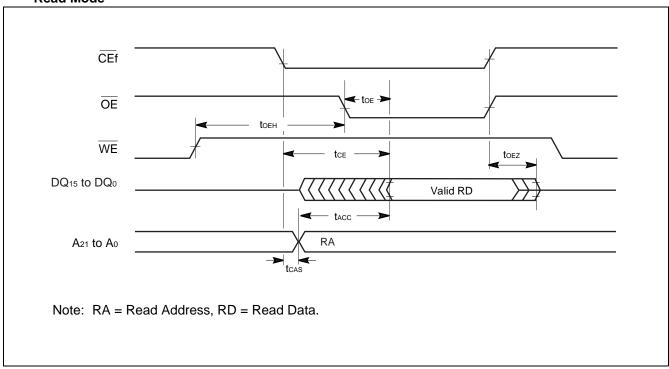

### • Read Operations

| Poro                    | meter                   | Syn   | nbol        | Va       | Unit           |      |

|-------------------------|-------------------------|-------|-------------|----------|----------------|------|

| Fala                    | meter                   | JEDEC | Standard    | Min      | Max            | Onit |

| Access Time from CEf    | Low                     | _     | <b>t</b> ce | _        | <del> 70</del> |      |

| Access Time *1          | ccess Time *1           |       | tacc        | _        | 70             | ns   |

| Output Enable to Output | ut Valid                | _     | <b>t</b> oe | <u> </u> |                | ns   |

| Output Enable Hold      | Read                    |       |             | 0        | _              | ns   |

| Time                    | Toggle and Data Polling | _     | tоен        | 10       | _              | ns   |

| Output Enable to High-  | Z *2                    | _     | toez        | _        | 10             | ns   |

<sup>\*1 :</sup> Access Time is from the last of either stable addresses.

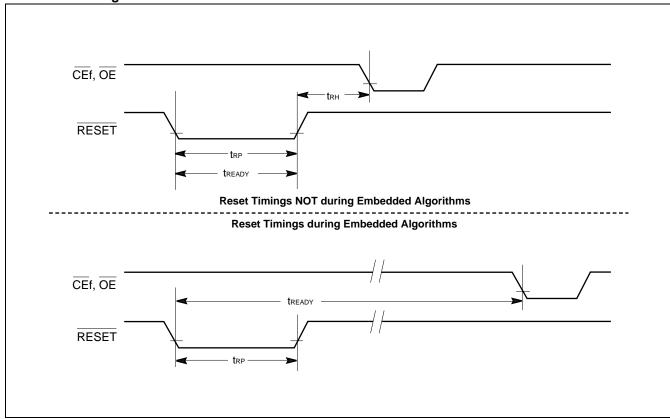

### • Hardware Reset (RESET)

| Parameter                                                    | Syn   | nbol           | Va  | Unit |       |  |

|--------------------------------------------------------------|-------|----------------|-----|------|-------|--|

| Farameter                                                    | JEDEC | Standard       | Min | Max  | O.iit |  |

| RESET Pin Low (During Embedded Algorithms) to Read Mode*     | _     | <b>t</b> READY | _   | 20   | μs    |  |

| RESET Pin Low (NOT During Embedded Algorithms) to Read Mode* | _     | <b>t</b> READY | _   | 500  | ns    |  |

| RESET Pulse Width                                            | _     | <b>t</b> RP    | 500 |      | ns    |  |

| Reset High Time Before Read*                                 | _     | <b>t</b> RH    | 200 |      | ns    |  |

| RESET Low to Standby Mode                                    | _     | <b>t</b> RPD   | 20  | _    | μs    |  |

<sup>\*:</sup> Not 100% tested.

<sup>\*2 :</sup> Not 100% tested.

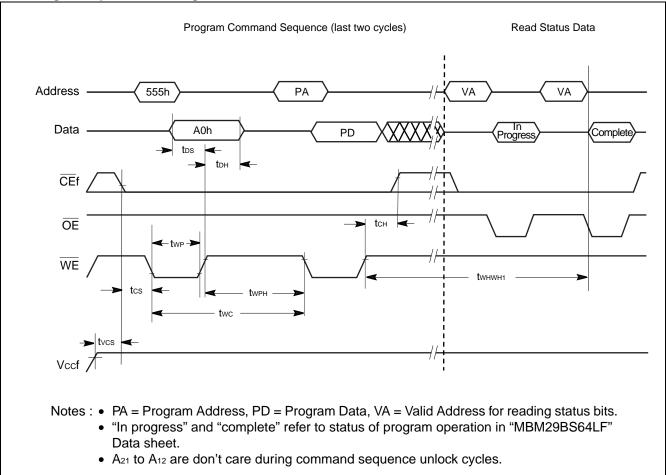

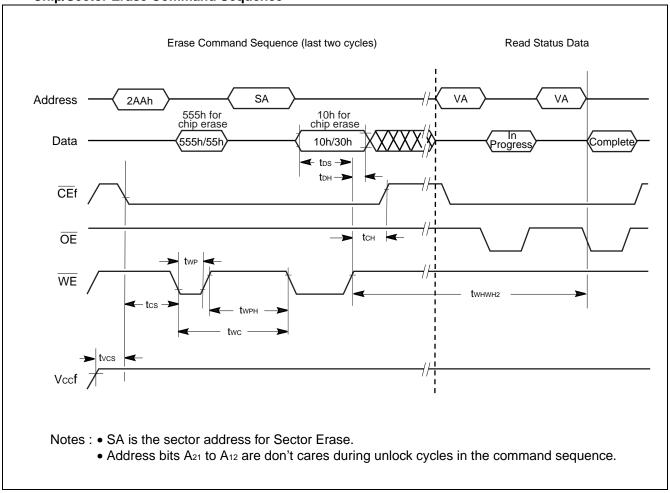

### • Erase/Program Operations

| Daman atau                                | Syr           | nbol           |     | Value |     | l lm!t |

|-------------------------------------------|---------------|----------------|-----|-------|-----|--------|

| Parameter                                 | JEDEC         | Standard       | Min | Тур   | Max | Unit   |

| Write Cycle Time*1                        | tavav         | twc            | 80  | _     | _   | ns     |

| Address Setup Time*2                      | <b>t</b> avwl | <b>t</b> AS    | 0   |       |     | ns     |

| Address Hold Time*2                       | twlax         | <b>t</b> AH    | 45  |       |     | ns     |

| Data Setup Time                           | <b>t</b> DVWH | tos            | 45  |       |     | ns     |

| Data Hold Time                            | twhox         | <b>t</b> DH    | 0   |       |     | ns     |

| Read Recovery Time Before Write           | <b>t</b> GHWL | <b>t</b> GHWL  | 0   |       |     | ns     |

| CE Hold Time                              | twheh         | tсн            | 0   | _     | _   | ns     |

| Write Pulse Width                         | <b>t</b> EHWH | twp            | 50  | _     | _   | ns     |

| Write Pulse Width High                    | twhwL         | <b>t</b> wph   | 30  | _     | _   | ns     |

| Latency Between Read and Write Operations | _             | tsr/w          | 0   | _     | _   | ns     |

| Programming Operation*3                   | twnwh1        | twnwh1         |     | 8     |     | μs     |

| Sector Erase Operation*3, *4              |               | 4              |     | 0.5   |     |        |

| Chip Erase Operation*3, *4                | twhwh2        | <b>t</b> whwh2 | _   | 67.0  |     | S      |

| Vcc Setup Time                            | _             | tvcs           | 50  |       |     | μs     |

| CE Setup Time to WE                       | <b>t</b> ELWL | <b>t</b> cs    | 0   | _     | _   | ns     |

<sup>\*1 :</sup> Not 100% tested.

<sup>\*2 :</sup> Addresses are latched on the falling edge of  $\overline{\text{WE}}$ .

<sup>\*3 :</sup> See the "Erase and Programming Performance" section in "BDS64xF" datasheet for more information.

<sup>\*4 :</sup> Does not include the preprogramming time.

### 3. Erase and Programming Performance

| Parameter             |         | Value |     | Unit  | Comments                              |

|-----------------------|---------|-------|-----|-------|---------------------------------------|

| Parameter             | Min     | Тур   | Max | Ullit | Comments                              |

| Sector Erase Time     | _       | 0.5   | 2.0 | S     | Excludes programming prior to erasure |

| Word Programming Time | _       | 6     | 100 | μs    | Excludes system level overhead        |

| Chip Programming Time | _       | 25.2  | 95  | S     | Excludes system level overhead        |

| Erase/Program Cycle   | 100,000 | _     | _   | cycle | _                                     |

Note: Typical Erase Conditions:  $T_A = +25^{\circ}C$ ,  $V_{CC}f = 1.8 \text{ V}$ Typical Program Conditions:  $T_A = +25^{\circ}C$ ,  $V_{CC}f = 1.8 \text{ V}$ , Data = checker

#### • Read Mode

#### Reset Timings

### • Program Operation Timings

### • Chip/Sector Erase Command Sequence

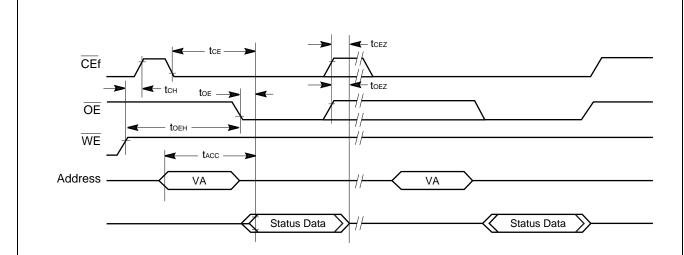

### • Data Polling Timings (During Embedded Algorithm)

Note: VA = Valid Address. Two read cycles are required to determine status. When the Embedded Algorithm operation is complete, and Data Polling will output true data.

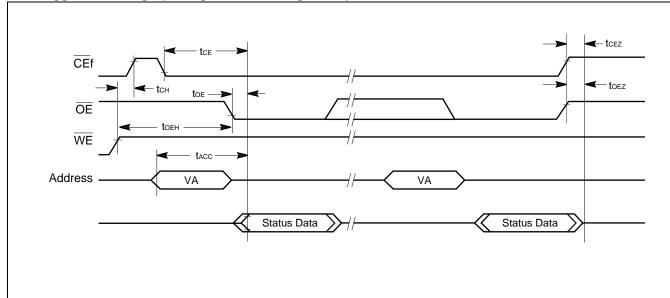

### • Toggle Bit Timings (During Embedded Algorithm)

Note: VA = Valid Address. Two read cycles are required to determine status. When the Embedded Algorithm operation is complete, the toggle bits will stop toggling.

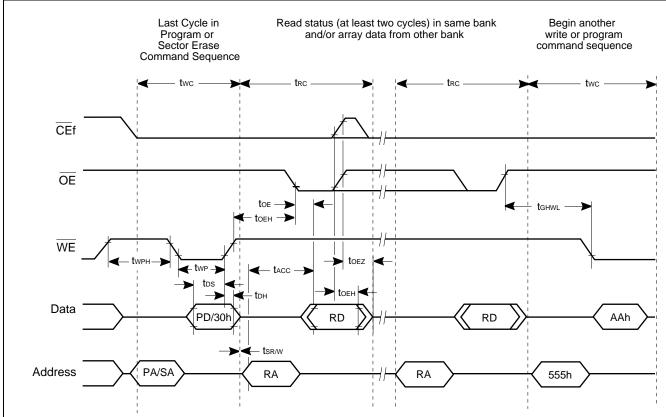

### • Bank-to-Bank Read/Write Cycle Timings

Note: Break points in waveforms indicate that system may alternately read array data from the "non-busy bank" while checking the status of the program or erase operation in the "busy" bank. The system should read status twice to ensure valid information.

#### ■ 8M SRAM for MCP 1.8 V

### 1. AC Characteristics

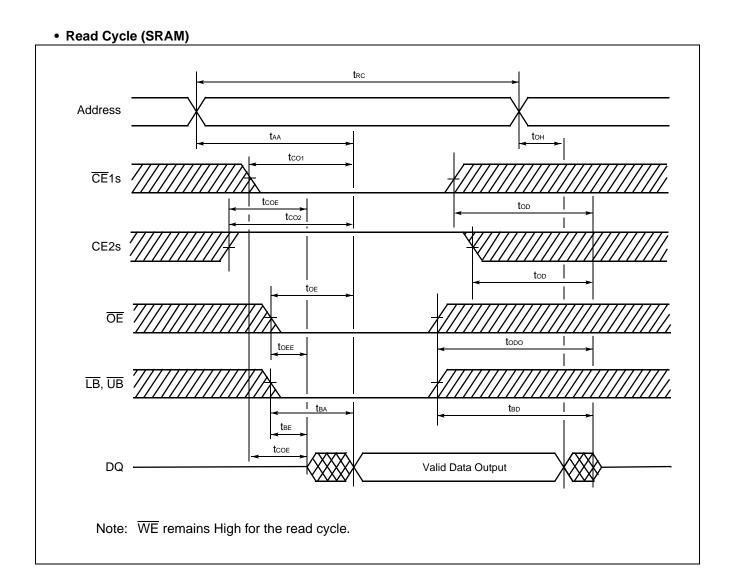

• Read Cycle (SRAM)

| Parameter                                             | Symbol      | Va  | lue | Unit |

|-------------------------------------------------------|-------------|-----|-----|------|

| Farameter                                             | Symbol      | Min | Max | Onit |

| Read Cycle Time                                       | <b>t</b> RC | 70  | _   | ns   |

| Address Access Time                                   | <b>t</b> AA | _   | 70  | ns   |

| Chip Enable (CE1s) Access Time                        | tco1        | _   | 70  | ns   |

| Chip Enable (CE2s) Access Time                        | tco2        | _   | 70  | ns   |

| Output Enable Access Time                             | <b>t</b> oe | _   | 35  | ns   |

| LB, UB to Output Valid                                | <b>t</b> BA | _   | 70  | ns   |

| Chip Enable (CE1s Low and CE2s High) to Output Active | tcoe        | 5   | _   | ns   |

| Output Enable Low to Output Active                    | toee        | 0   | _   | ns   |

| LB, UB Enable Low to Output Active                    | <b>t</b> BE | 5   | _   | ns   |

| Chip Enable (CE1s High or CE2s Low) to Output High-Z  | top         | _   | 25  | ns   |

| Output Enable High to Output High-Z                   | todo        | _   | 25  | ns   |

| LB, UB Output Enable to Output High-Z                 | <b>t</b> BD | _   | 25  | ns   |

| Output Data Hold Time                                 | <b>t</b> он | 5   |     | ns   |

Note: Test Conditions-Output Load:1 TTL gate and 30 pF

Input rise and fall times: 5 ns Input pulse levels: 0.0 V to 1.8 V Timing measurement reference level

Input:  $0.5 \times V_{CCS}$ Output:  $0.5 \times V_{CCS}$

### • Write Cycle (SRAM)

| Parameter                     | Symbol       | Va  | lue | Unit  |

|-------------------------------|--------------|-----|-----|-------|

| Farameter                     | Symbol       | Min | Max | Offic |

| Write Cycle Time              | <b>t</b> wc  | 70  | _   | ns    |

| Write Pulse Width             | twp          | 55  | _   | ns    |

| CE1s to End of Write          | tcw1         | 55  | _   | ns    |

| CE2s to End of Write          | tcw2         | 55  | _   | ns    |

| Address valid to End of Write | taw          | 55  | _   | ns    |

| LB, UB to End of Write        | <b>t</b> BW  | 55  | _   | ns    |

| Address Setup Time            | <b>t</b> as  | 0   | _   | ns    |

| Write Recovery Time           | <b>t</b> wr  | 0   | _   | ns    |

| WE Low to Output High-Z       | todw         | _   | 25  | ns    |

| WE High to Output Active      | <b>t</b> oew | 0   | _   | ns    |

| Data Setup Time               | tos          | 30  | _   | ns    |

| Data Hold Time                | <b>t</b> DH  | 0   | _   | ns    |

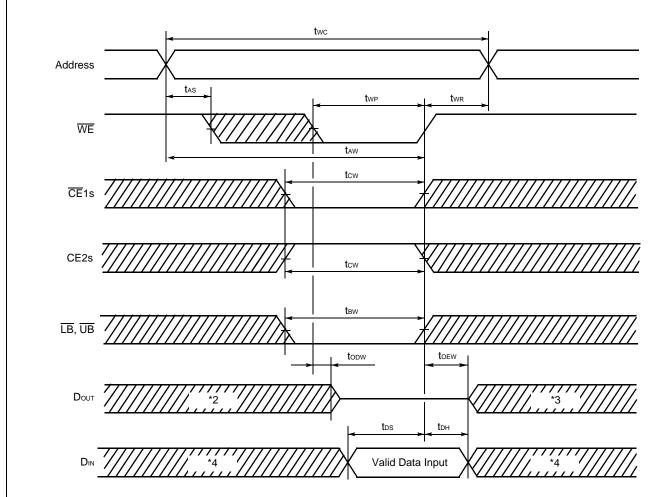

## • Write Cycle\*1 (WE control) (SRAM)

- \*1: If  $\overline{OE}$  is High during the write cycle, the outputs will remain at high impedance.

- \*2: If CE1s goes Low (or CE2s goes High) coincident with or after WE goes Low, the output will remain at high impedance.

- \*3: If CE1s goes High (or CE2s goes Low) coincident with or before WE goes High, the output will remain at high impedance.

- \*4: Because I/O signals may be in the output state at this Time, input signals of reverse polarity must not be applied.

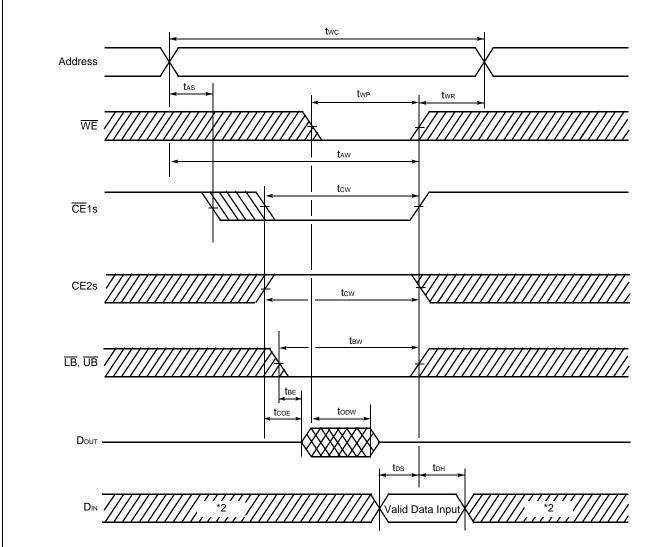

### • Write Cycle\*1 (CE1s control) (SRAM)

- \*1: If  $\overline{\text{OE}}$  is High during the write cycle, the outputs will remain at high impedance.

- \*2: Because I/O signals may be in the output state at this Time, input signals of reverse polarity must not be applied.

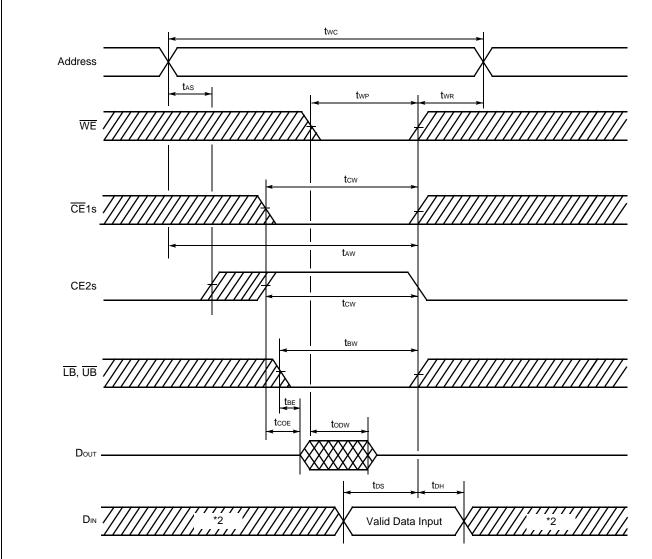

### • Write Cycle\*1 (CE2s Control) (SRAM)

- \*1: If  $\overline{OE}$  is High during the write cycle, the outputs will remain at high impedance.

- \*2: Because I/O signals may be in the output state at this Time, input signals of reverse polarity must not be applied.

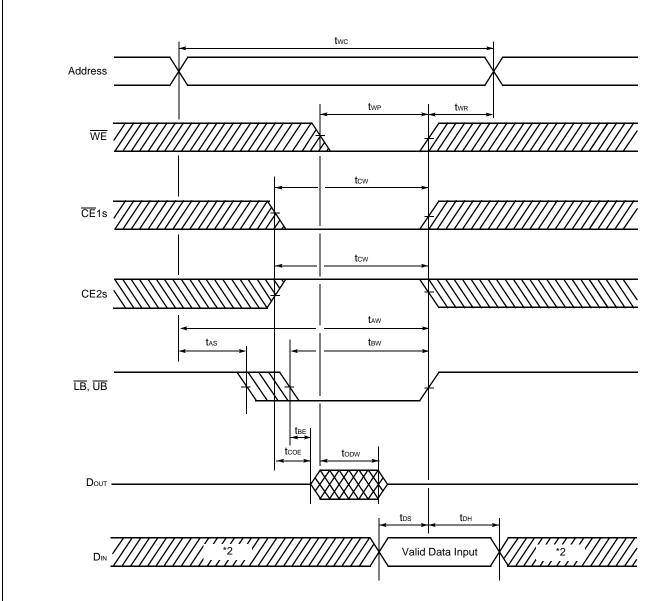

### • Write Cycle\*1 (LB, UB Control) (SRAM)

- \*1: If  $\overline{OE}$  is High during the write cycle, the outputs will remain at high impedance.

- \*2: Because I/O signals may be in the output state at this Time, input signals of reverse polarity must not be applied.

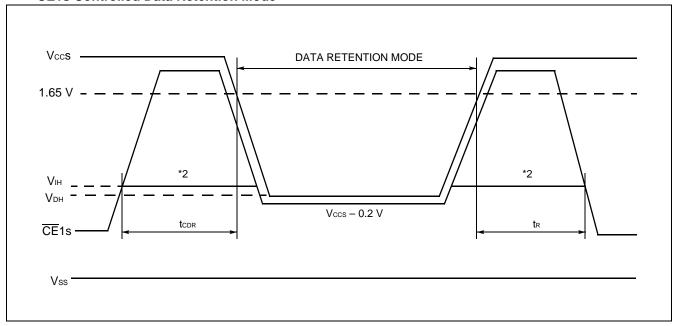

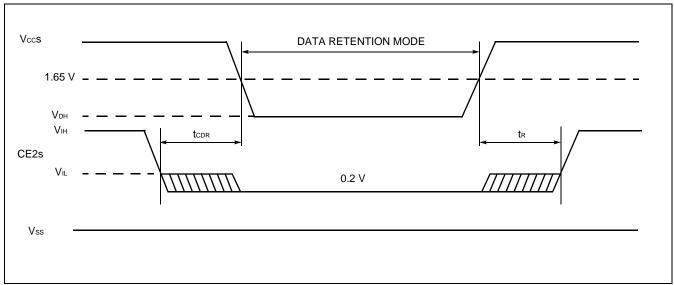

### 2. Data Retention Characteristics (SRAM)

| Parameter                                 | Symbol                  |                   | Unit        |     |       |    |

|-------------------------------------------|-------------------------|-------------------|-------------|-----|-------|----|

| Farameter                                 | Зуппоп                  | Min               | Тур         | Max | Oille |    |

| Data Retention Supply Voltage             |                         | V <sub>DH</sub>   | 1.0         | _   | 1.95  | V  |

| Standby Current                           | V <sub>DH</sub> = 1.8 V | I <sub>DDS2</sub> | _           | 0.3 | 14    | μΑ |

| Chip Deselect to Data Retention Mode Time |                         | <b>t</b> cdr      | 0           | _   | _     | ns |

| Recovery Time                             |                         | <b>t</b> R        | <b>t</b> RC | _   | _     | ns |

Note: tRC: Read cycle time

#### • CE1s Controlled Data Retention Mode \*1

- \*1: In  $\overline{\text{CE}}$ 1s controlled data retention mode, input level of CE2s should be fixed Vccs to Vccs-0.2 V or Vss to 0.2 V during data retention mode. Other input and input/output pins can be used between -0.3 V to Vccs+0.3 V.

- \*2: When  $\overline{\text{CE}}$ 1s is operating at the V<sub>IH</sub> Min level, the standby current is given by I<sub>SB1</sub>s during the transition of V<sub>CCS</sub> from V<sub>CCS</sub> Max to V<sub>IH</sub> Min level.

#### • CE2s Controlled Data Retention Mode\*

<sup>\*:</sup> In CE2s controlled data retention mode, input and input/output pins can be used between -0.3 V to Vccs+0.3 V.

#### **■ PIN CAPACITANCE**

| Parameter               | Symbol           | Test Setup          |     | Unit |      |       |

|-------------------------|------------------|---------------------|-----|------|------|-------|

| raiametei               | Syllibol         | rest Setup          | Min | Тур  | Max  | Oilit |

| Input Capacitance       | Cin              | V <sub>IN</sub> = 0 | _   | _    | 16.0 | pF    |

| Output Capacitance      | Соит             | Vout = 0            | _   | _    | 22.0 | pF    |

| Control Pin Capacitance | C <sub>IN2</sub> | V <sub>IN</sub> = 0 | _   | _    | 18.0 | pF    |

Note : Test conditions  $T_A = +25$  °C, f = 1.0 MHz

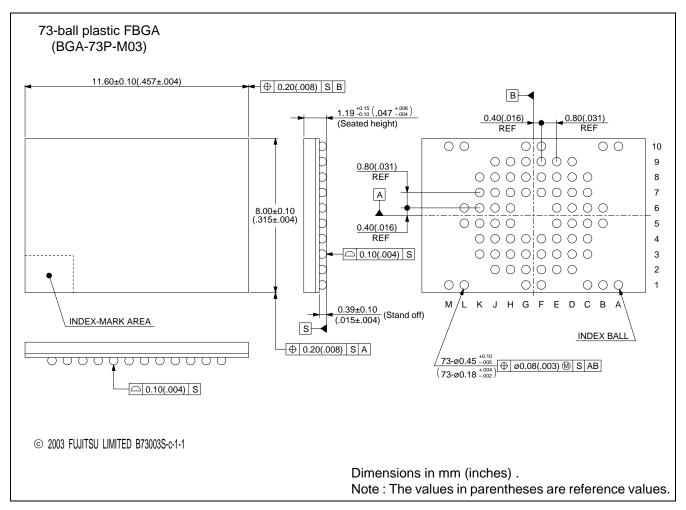

### **■ HANDLING OF PACKAGE**

Please handle this package carefully since the sides of package create acute angles.

### **■** CAUTION

• The high voltage (V<sub>ID</sub>) cannot apply to address pins and control pins.

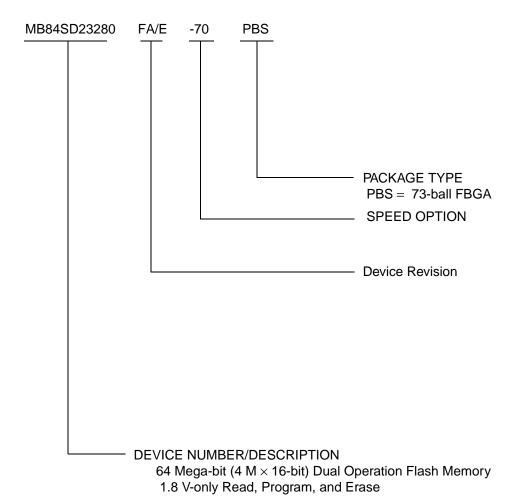

### **■ ORDERING INFORMATION**

8 Mega-bit (512K  $\times$  16-bit) SRAM

37

#### **■ PACKAGE DIMENSION**

# **FUJITSU LIMITED**

All Rights Reserved.

The contents of this document are subject to change without notice. Customers are advised to consult with FUJITSU sales representatives before ordering.

The information, such as descriptions of function and application circuit examples, in this document are presented solely for the purpose of reference to show examples of operations and uses of Fujitsu semiconductor device; Fujitsu does not warrant proper operation of the device with respect to use based on such information. When you develop equipment incorporating the device based on such information, you must assume any responsibility arising out of such use of the information. Fujitsu assumes no liability for any damages whatsoever arising out of the use of the information.

Any information in this document, including descriptions of function and schematic diagrams, shall not be construed as license of the use or exercise of any intellectual property right, such as patent right or copyright, or any other right of Fujitsu or any third party or does Fujitsu warrant non-infringement of any third-party's intellectual property right or other right by using such information. Fujitsu assumes no liability for any infringement of the intellectual property rights or other rights of third parties which would result from the use of information contained herein.

The products described in this document are designed, developed and manufactured as contemplated for general use, including without limitation, ordinary industrial use, general office use, personal use, and household use, but are not designed, developed and manufactured as contemplated (1) for use accompanying fatal risks or dangers that, unless extremely high safety is secured, could have a serious effect to the public, and could lead directly to death, personal injury, severe physical damage or other loss (i.e., nuclear reaction control in nuclear facility, aircraft flight control, air traffic control, mass transport control, medical life support system, missile launch control in weapon system), or (2) for use requiring extremely high reliability (i.e., submersible repeater and artificial satellite).

Please note that Fujitsu will not be liable against you and/or any third party for any claims or damages arising in connection with above-mentioned uses of the products.

Any semiconductor devices have an inherent chance of failure. You must protect against injury, damage or loss from such failures by incorporating safety design measures into your facility and equipment such as redundancy, fire protection, and prevention of over-current levels and other abnormal operating conditions.

If any products described in this document represent goods or technologies subject to certain restrictions on export under the Foreign Exchange and Foreign Trade Law of Japan, the prior authorization by Japanese government will be required for export of those products from Japan.

F0311 © FUJITSU LIMITED Printed in Japan