# 1 ch DC/DC Converter IC with PFM/PWM Synchronous Rectification

## Description

The MB39C014 is a current mode type 1-channel DC/DC converter IC built-in switching FET, synchronous rectification, and down conversion support. The device is integrated with a switching FET, oscillator, error amplifier, PWM control circuit, reference voltage source, and POWERGOOD circuit.

External inductor and decoupling capacitor are needed only for the external component.

As combining with external parts enables a DC/DC converter with a compact and high load response characteristic, this is suitable as the built-in power supply for such as mobile phone/PDA, DVDs, and HDDs.

#### **Features**

■ High efficiency : 96% (Max)

■ Output current (DC/DC) : 800 mA (Max)

■ Input voltage range : 2.5 V to 5.5 V

■ Operating frequency : 2.0/3.2 MHz (Typ)

■ No flyback diode needed

■ Low dropout operation : For 100% on duty

■ Built-in high-precision reference voltage generator : 1.20 V ± 2% ■ Consumption current in shutdown mode : 1 µA or less

■ Built-in switching FET : P-ch MOS  $0.3 \Omega$  (Typ) N-ch MOS  $0.2 \Omega$  (Typ)

■ High speed for input and load transient response in the current mode

■ Over temperature protection

■ Packaged in a compact package : SON10

## **Applications**

- Flash ROMs

- MP3 players

- Electronic dictionary devices

- Surveillance cameras

- Portable GPS navigators

- Mobile phones etc.

## **Contents**

| De | escription                                   | 1  |

|----|----------------------------------------------|----|

| Fe | eatures                                      | 1  |

| Αŗ | oplications                                  | 1  |

| Cc | ontents                                      | 2  |

| 1. | Pin Assignment                               | 3  |

| 2. | Pin Descriptions                             | 3  |

| 3. | I/O Pin Equivalent Circuit Diagram           | 4  |

|    | Block Diagram                                |    |

|    | 4.1 Current Mode                             | 6  |

| 5. | Function Of Each Block                       | 7  |

|    | 5.1 PWM Logic Control Circuit                | 7  |

|    | 5.2 IOUT Comparator Circuit                  | 7  |

|    | 5.3 Error Amp Phase Compensation Circuit     | 7  |

|    | 5.4 VREF Circuit                             |    |

|    | 5.5 POWERGOOD Circuit                        | 7  |

|    | 5.6 Protection Circuit                       | 8  |

| 6. | Absolute Maximum Ratings                     | 9  |

| 7. | Recommended Operating Conditions             | 10 |

| 8. | Electrical Characteristics                   | 11 |

| 9. | Test Circuit For Measuring Typical Operating |    |

|    | Characteristics                              | 13 |

| 10.                      | Application Notes                                                                                                                                                                         | . 14                                                              |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|

|                          | 10.1 Selection of Components                                                                                                                                                              | . 14                                                              |

|                          | 10.2 Output Voltage Setting                                                                                                                                                               |                                                                   |

|                          | 10.3 About Conversion Efficiency                                                                                                                                                          | . 15                                                              |

|                          | 10.4 Power Dissipation and Heat Considerations                                                                                                                                            | . 16                                                              |

|                          | 10.5 Transient Response                                                                                                                                                                   |                                                                   |

|                          | 10.6 Board Layout, Design Example                                                                                                                                                         |                                                                   |

|                          | 10.7 Layout Example of IC SW Components                                                                                                                                                   | . 17                                                              |

|                          | 10.8 Notes for Circuit Design                                                                                                                                                             |                                                                   |

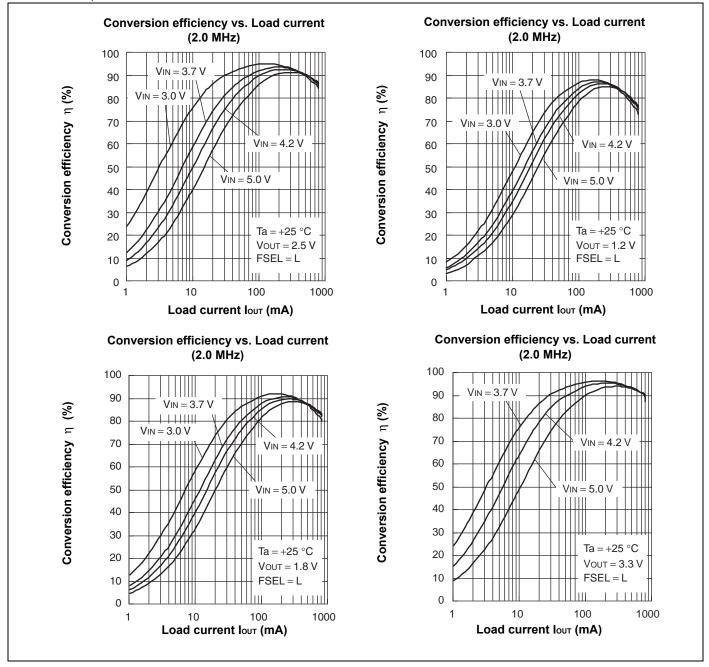

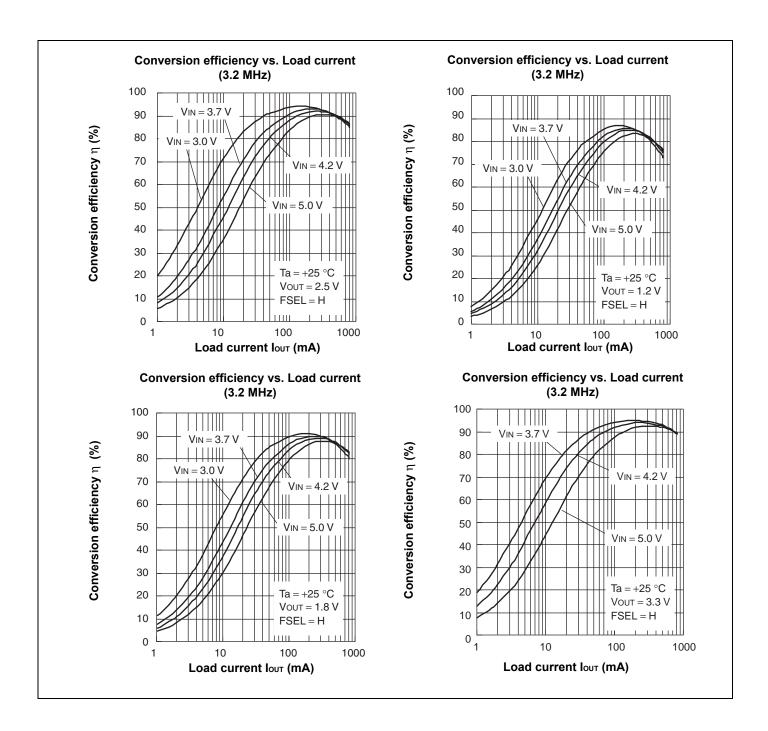

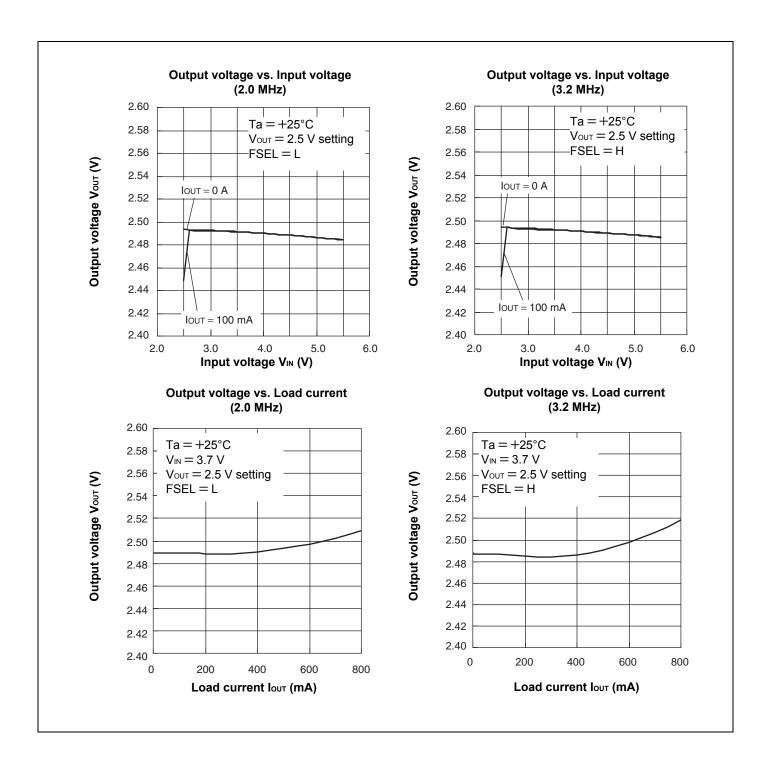

| 11.                      | <b>Example Of Standard Operation Characteristics</b>                                                                                                                                      | . 18                                                              |

|                          |                                                                                                                                                                                           |                                                                   |

| 12.                      | Application Circuit Examples                                                                                                                                                              | . 27                                                              |

| 12.                      | Application Circuit Examples                                                                                                                                                              |                                                                   |

| 12.                      |                                                                                                                                                                                           | . 27                                                              |

| 12.                      | 12.1 Application Circuit Example 1                                                                                                                                                        | . 27<br>. 27                                                      |

| 13.                      | 12.1 Application Circuit Example 1                                                                                                                                                        | . 27<br>. 27<br>. 28<br><b>. 29</b>                               |

| 13.                      | <ul><li>12.1 Application Circuit Example 1</li><li>12.2 Application Circuit Example 2</li><li>12.3 Application Circuit Example Components List</li></ul>                                  | . 27<br>. 27<br>. 28<br><b>. 29</b>                               |

| 13.<br>14.               | 12.1 Application Circuit Example 1                                                                                                                                                        | . 27<br>. 27<br>. 28<br>. <b>29</b>                               |

| 13.<br>14.<br>15.        | 12.1 Application Circuit Example 1  12.2 Application Circuit Example 2  12.3 Application Circuit Example Components List  Usage Precautions  Ordering Information                         | . 27<br>. 27<br>. 28<br>. <b>29</b><br>. <b>29</b>                |

| 13.<br>14.<br>15.<br>16. | 12.1 Application Circuit Example 1 12.2 Application Circuit Example 2 12.3 Application Circuit Example Components List Usage Precautions Ordering Information RoHS Compliance Information | . 27<br>. 27<br>. 28<br>. <b>29</b><br>. <b>29</b><br>. <b>30</b> |

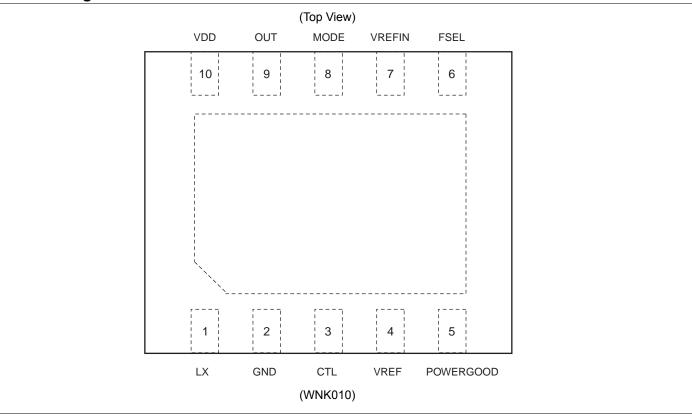

# 1. Pin Assignment

# 2. Pin Descriptions

| Pin No | Pin Name  | I/O | Description                                                                           |

|--------|-----------|-----|---------------------------------------------------------------------------------------|

| 1      | LX        | 0   | Inductor connection output pin. High impedance during shut down.                      |

| 2      | GND       | _   | Ground pin.                                                                           |

| 3      | CTL       | I   | Control input pin. (L : Shut down / H : Normal operation)                             |

| 4      | VREF      | 0   | Reference voltage output pin.                                                         |

| 5      | POWERGOOD | 0   | POWERGOOD circuit output pin. Internally connected to an N-ch MOS open drain circuit. |

| 6      | FSEL      | I   | Frequency switch pin.<br>(L (open) : 2.0 MHz, H : 3.2 MHz)                            |

| 7      | VREFIN    | I   | Error amplifier (Error Amp) non-inverted input pin.                                   |

| 8      | MODE      | I   | Use pin at L level or leave open.                                                     |

| 9      | OUT       | I   | Output voltage feedback pin.                                                          |

| 10     | VDD       | _   | Power supply pin.                                                                     |

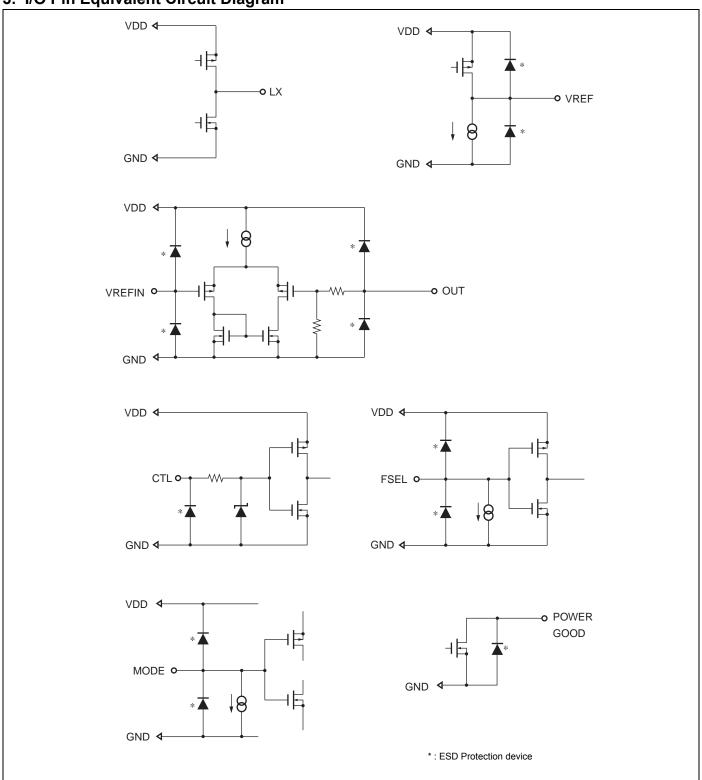

# 3. I/O Pin Equivalent Circuit Diagram

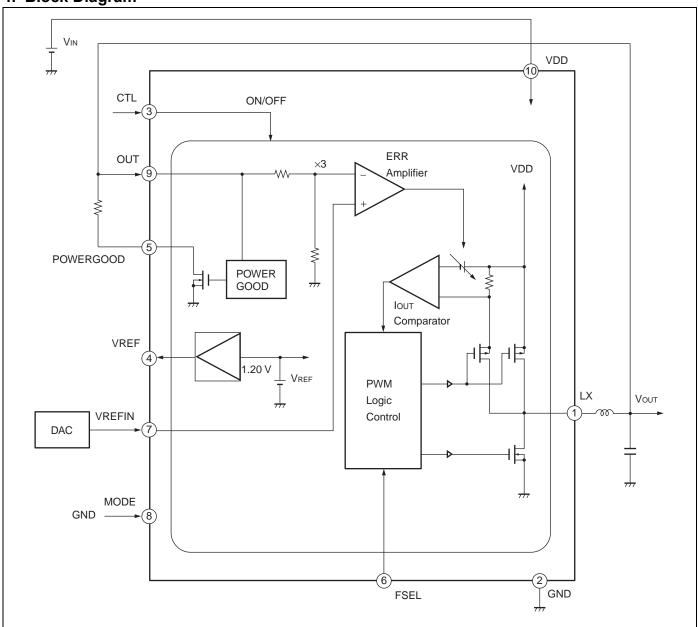

# 4. Block Diagram

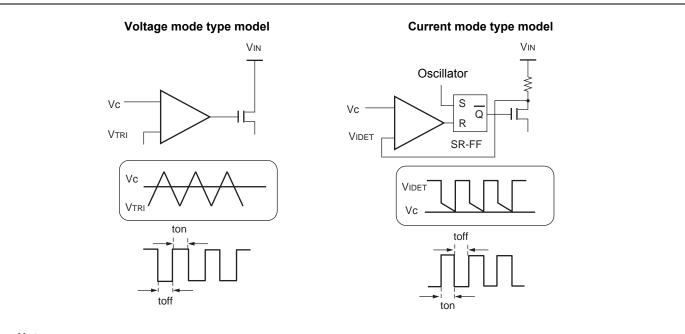

## 4.1 Current Mode

- Original Voltage Mode Type:

- Stabilize the output voltage by comparing two items below and on-duty control.

- □ Voltage (VC) obtained through negative feedback of the output voltage by Error Amp

- ☐ Reference triangular wave (VTRI)

- Current Mode Type:

- Instead of the triangular wave ( $V_{TRI}$ ), the voltage ( $V_{IDET}$ ) obtained through I-V conversion of the sum of currents that flow in the oscillator (rectangular wave generation circuit) and SW FET is used.

- Stabilize the output voltage by comparing two items below and on-duty control.

- □ Voltage (Vc) obtained through negative feedback of the output voltage by Error Amp

- □ Voltage (V<sub>IDET</sub>) obtained through I-V conversion of the sum of current that flow in the oscillator (rectangular wave generation circuit) and SW FET

#### Note:

The above models illustrate the general operation and an actual operation will be preferred in the IC.

## 5. Function of Each Block

## 5.1 PWM Logic Control Circuit

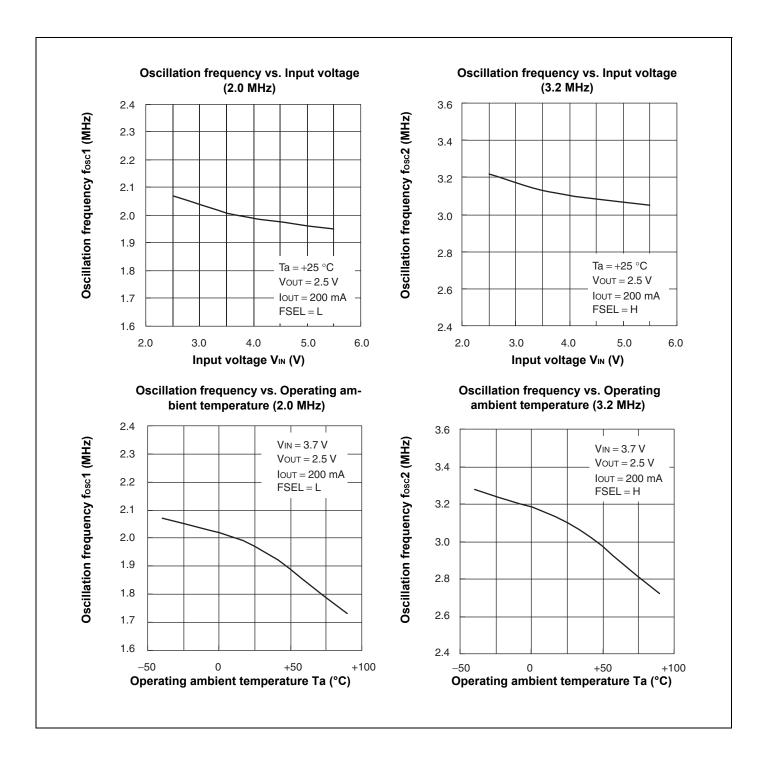

The built-in P-ch and N-ch MOS FETs are controlled for synchronization rectification according to the frequency (2.0 MHz/3.2 MHz) oscillated from the built-in oscillator (square wave oscillation circuit).

## 5.2 IOUT Comparator Circuit

This circuit detects the current (ILx) which flows to the external inductor from the built-in P-ch MOS FET.

By comparing VIDET obtained through I-V conversion of peak current IPK of ILX with the Error Amp output, the built-in P-ch MOS FET is turned off via the PWM Logic Control circuit.

## 5.3 Error Amp Phase Compensation Circuit

This circuit compares the output voltage to reference voltages such as VREF. This IC has a built-in phase compensation circuit that is designed to optimize the operation of this IC. This needs neither to be considered nor addition of a phase compensation circuit and an external phase compensation device.

#### 5.4 VREF Circuit

A high accuracy reference voltage is generated with BGR (bandgap reference) circuit. The output voltage is 1.20 V (Typ).

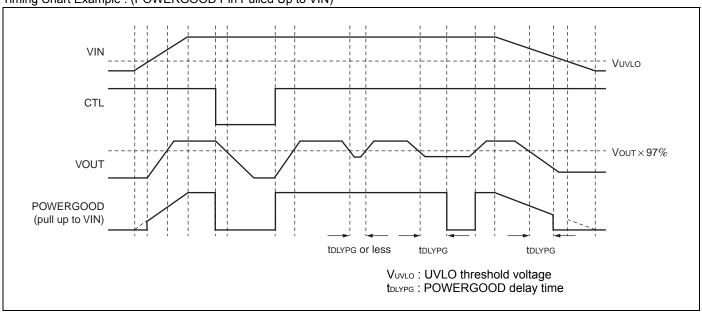

#### 5.5 POWERGOOD Circuit

The POWERGOOD circuit monitors the voltage at the OUT pin. The POWERGOOD pin is open drain output.

Use the pin with pull-up using the external resistor in the normal operation.

When the CTL is at the H level, the POWERGOOD pin becomes the H level. However, if the output voltage drops because of over current and etc, the POWERGOOD pin becomes the L level.

## 5.6 Protection Circuit

This IC has a built-in over-temperature protection circuit.

The over-temperature protection circuit turns off both N-ch and P-ch switching FETs when the junction

temperature reaches +135°C. When the junction temperature comes down to + 110°C, the switching FET is returned to the normal operation.

Since the PWM control circuit of this IC is in the control method in current mode, the current peak value is also monitored and controlled as required.

#### ■ Function Table

|                |                        | Inp | out  | Output                |             |               |

|----------------|------------------------|-----|------|-----------------------|-------------|---------------|

| MODE           | Switching<br>Frequency | CTL | FSEL | OUTPUT Pin<br>Voltage | VREF        | POWERGOOD     |

| Shutdown mode  | _                      | L   | *    | Output stop           | Output stop | Function stop |

| Operation mode | 2.0 MHz                | Н   | L    | VOUT voltage output   | 1.2 V       | Operation     |

| Operation mode | 3.2 MHz                | Н   | Н    | v OOT voltage output  | 1.2 V       | Operation     |

<sup>\* :</sup> Don't care

## 6. Absolute Maximum Ratings

| Parameter                     | Symbol           | Condition            | Rat         | ting                  | Unit  |  |

|-------------------------------|------------------|----------------------|-------------|-----------------------|-------|--|

| Farameter                     | Symbol           | Condition            | Min         | Max                   | Ollit |  |

| Power supply voltage          | V <sub>DD</sub>  | VDD pin              | - 0.3       | + 6.0                 | V     |  |

|                               |                  | OUT pin              | - 0.3       | V <sub>DD</sub> + 0.3 |       |  |

| Signal input voltage          | Visig            | CTL, MODE, FSEL pins | - 0.3       | V <sub>DD</sub> + 0.3 | V     |  |

|                               |                  | VREFIN pin           | - 0.3       | V <sub>DD</sub> + 0.3 |       |  |

| POWERGOOD pull-up voltage     | V <sub>IPG</sub> | POWERGOOD pin        | - 0.3       | + 6.0                 | V     |  |

| LX voltage                    | V <sub>L</sub> X | LX pin               | - 0.3       | V <sub>DD</sub> + 0.3 | V     |  |

| LX peak current               | Iрк              | ILX                  | _           | 1.8                   | Α     |  |

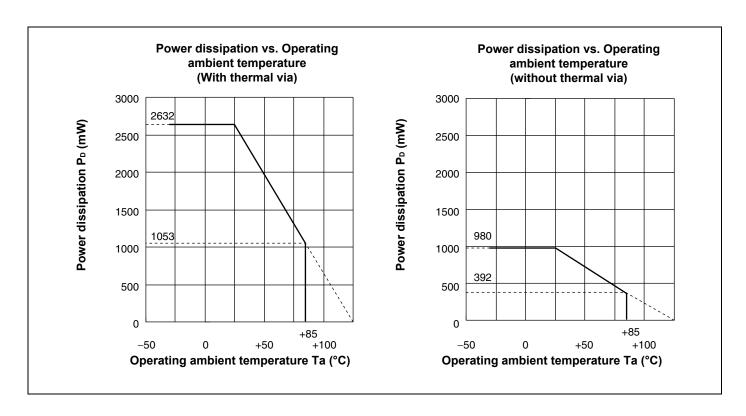

|                               |                  | Ta ≤ + 25°C          | _           | 2632*1, *2, *3        | mW    |  |

| Power dissination             | Pp               | 1a ≤ + 25 C          | _           | 980*1, *2, *4         | IIIVV |  |

| Power dissipation             | FD               | Ta = + 85 °C         | _           | 1053*1, *2, *3        | mW    |  |

|                               |                  | 1a — + 65 C          | _           | 392*1, *2, *4         | 11100 |  |

| Operating ambient temperature | Та               | _                    | <b>- 40</b> | + 85                  | °C    |  |

| Storage temperature           | Тѕтс             | _                    | <b>–</b> 55 | + 125                 | °C    |  |

<sup>\*1:</sup> Power dissipation value between  $\pm$  25°C and  $\pm$  85°C is obtained by connecting these two points with a straight line

#### Notes:

- The use of negative voltages below -0.3 V to the GND pin may create parasitic transistors on LSI lines, which can cause abnormal operation.

- This device can be damaged if the LX pin is short-circuited to VDD or GND.

- Take measures not to keep the FSEL pin falling below the GND potential of this IC as much as possible. In addition to erroneous operation, the IC may latch up and destroy itself if 110 mA or more current flows from this pin.

WARNING: Semiconductor devices can be permanently damaged by application of stress (voltage, current, temperature, etc.) in excess of absolute maximum ratings. Do not exceed these ratings.

$<sup>^{*}2</sup>$ : When mounted on a four-layer epoxy board of 11.7 cm  $\times$  8.4 cm

<sup>\*3 :</sup> Connection at exposure pad with thermal via. (Thermal via 4 holes)

<sup>\*4 :</sup> Connection at exposure pad, without a thermal via.

## 7. Recommended Operating Conditions

| Parameter            | Symbol          | Condition                                           |             | Value |       | Unit  |       |                                                     |   |   |   |    |

|----------------------|-----------------|-----------------------------------------------------|-------------|-------|-------|-------|-------|-----------------------------------------------------|---|---|---|----|

| raiailletei          | Syllibol        | Condition                                           | Min Typ Max |       | Max   | Oill  |       |                                                     |   |   |   |    |

| Power supply voltage | V <sub>DD</sub> | _                                                   | 2.5         | 3.7   | 5.5   | V     |       |                                                     |   |   |   |    |

| VREFIN voltage       | VREFIN          | _                                                   | 0.15        | _     | 1.20  | V     |       |                                                     |   |   |   |    |

| CTL voltage          | Vctl            | _                                                   | 0           | _     | 5.0   | V     |       |                                                     |   |   |   |    |

| LX current           | ILX             | _                                                   | _           | _     | 800   | mA    |       |                                                     |   |   |   |    |

| POWERGOOD current    | Ipg             | _                                                   | _           | _     | 1     | mA    |       |                                                     |   |   |   |    |

| VPEE output current  | Inour           | $2.5 \text{ V} \le \text{V}_{DD} \le 3.0 \text{ V}$ | _           | _     | 0.5   | mA    |       |                                                     |   |   |   |    |

| VREF output current  | Irout           | IKUUI                                               | IROUI       | IROUT | IROUT | IROUT | IROUT | $3.0 \text{ V} \le \text{V}_{DD} \le 5.5 \text{ V}$ | _ | _ | 1 | ША |

| Inductor value       |                 | 2.0 MHz (FSEL = L)                                  | _           | 2.2   | _     | μН    |       |                                                     |   |   |   |    |

| inductor value       | L               | 3.2 MHz (FSEL = H)                                  | _           | 1.5   | _     | μΠ    |       |                                                     |   |   |   |    |

#### Note:

The output current from this device has a situation to decrease if the power supply voltage  $(V_{IN})$  and the DC/DC converter output voltage  $(V_{OUT})$  differ only by a small amount. This is a result of slope compensation and will not damage this device.

#### WARNING:

The recommended operating conditions are required in order to ensure the normal operation of the semiconductor device. All of the device's electrical characteristics are warranted when the device is operated within these ranges.

Always use semiconductor devices within their recommended operating condition ranges. Operation outside these ranges may adversely affect reliability and could result in device failure.

No warranty is made with respect to uses, operating conditions, or combinations not represented on the data sheet. Users considering application outside the listed conditions are advised to contact their representatives beforehand.

Document Number: 002-08361 Rev. \*C

## 8. Electrical Characteristics

(Ta =  $\pm 25$ °C, VDD = 3.7 V, VOUT setting value = 2.5 V, MODE = 0 V)

| Parameter                |                                | Cumbal           | Pin No.   | Condition                                          | Value        |        |        |      |

|--------------------------|--------------------------------|------------------|-----------|----------------------------------------------------|--------------|--------|--------|------|

|                          |                                | Symbol           | Collation |                                                    | Min          | Тур    | Max    | Unit |

|                          |                                | IREFINM          |           | V <sub>REFIN</sub> = 0.833 V                       | -100         | 0      | + 100  | nA   |

|                          | Input current                  | IREFINL          | 7         | V <sub>REFIN</sub> = 0.15 V                        | -100         | 0      | + 100  | nA   |

|                          |                                | IREFINH          |           | V <sub>REFIN</sub> = 1.20 V                        | -100         | 0      | + 100  | nA   |

|                          | Output voltage                 | Vоит             |           | V <sub>REFIN</sub> = 0.833 V,<br>OUT = -100 mA     | 2.45         | 2.50   | 2.55   | V    |

|                          | Input stability                | LINE             | 9         | 2.5 V ≤ V <sub>DD</sub> ≤ 5.5 V *1                 | _            | 10     | _      | mV   |

|                          | Load stability                 | LOAD             | 9         | - 100 mA ≥ OUT ≥ - 800 mA                          | _            | 10     | _      | mV   |

|                          | Out pin input impedance        | Rоит             |           | OUT = 2.0 V                                        | 0.6          | 1.0    | 1.5    | МΩ   |

| DC/DC                    | LX peak current                | <b>I</b> PK      |           | Output shorted to GND                              | 0.9          | 1.2    | 1.7    | Α    |

| converter                | Oscillation frequency          | fosc1            | 1         | FSEL = 0 V                                         | 1.6          | 2.0    | 2.4    | MHz  |

| block                    |                                | fosc2            |           | FSEL = 3.7 V                                       | 2.56         | 3.20   | 3.84   | MHz  |

|                          | Rise delay time                | <b>t</b> PG      | 3, 9      | C1 = 4.7 $\mu$ F, OUT = 0 A, VOUT = 90%            | _            | 45     | 80     | μs   |

|                          | SW NMOS FET OFF voltage        | Vnoff            |           | _                                                  | <b>-40</b> * | -20*   | 0*     | mV   |

|                          | SW PMOS FET ON resistance      | RONP             |           | LX = -100 mA                                       | _            | 0.30   | 0.47   | Ω    |

|                          | SW NMOS FET ON resistance      | RONN             | 1         | LX = -100 mA                                       | _            | 0.20   | 0.36   | Ω    |

|                          | LX leak current                | ILEAKM           |           | $0 \le LX \le V_{DD}^{*2}$                         | -1.0         | _      | + 8.0  | μΑ   |

|                          | LA leak culterit               | ILEAKH           |           | $V_{DD} = 5.5 \text{ V}, 0 \le LX \le V_{DD}^{*2}$ | -2.0         |        | + 16.0 | μΑ   |

|                          | Over temperature               | Тотрн            |           |                                                    | + 120*       | + 135* | + 155* | °C   |

|                          | protection<br>(Junction Temp.) | Тотрь            | _         | _                                                  | + 95*        | + 110* | + 130* | °C   |

| Protection circuit block | UVLO threshold                 | $V_{THH}$        |           |                                                    | 2.07         | 2.20   | 2.33   | V    |

| Circuit Diook            | voltage                        | $V_{THL}$        | 10        |                                                    | 1.92         | 2.05   | 2.18   | V    |

|                          | UVLO hysteresis width          | V <sub>HYS</sub> | -         | _                                                  | 0.08         | 0.15   | 0.25   | ٧    |

<sup>\*:</sup> Standard design value

(Ta = +25°C, VDD = 3.7 V, VOUT setting value = 2.5 V, MODE = 0 V)

| Parameter           |                                      | Cumbal          | Pin No. | Condition                                                                                             | Value                            |                                  |                                  | Unit |

|---------------------|--------------------------------------|-----------------|---------|-------------------------------------------------------------------------------------------------------|----------------------------------|----------------------------------|----------------------------------|------|

| Pa                  | rameter                              | Symbol          | Pin No. | Condition                                                                                             | Min                              | Тур                              | Max                              | Unit |

|                     | POWERGOOD<br>threshold<br>voltage    | VTHPG           |         | *3                                                                                                    | V <sub>REFIN</sub> × 3<br>× 0.93 | V <sub>REFIN</sub> × 3<br>× 0.97 | V <sub>REFIN</sub> × 3<br>× 0.99 | V    |

| DOWED               | POWERGOOD                            | <b>t</b> DLYPG1 |         | FSEL = 0 V                                                                                            | _                                | 250                              | _                                | μs   |

| POWER<br>GOOD block | delay time                           | tDLYPG2         | 5       | FSEL = 3.7 V                                                                                          | _                                | 170                              | _                                | μs   |

| COOD BIOOK          | POWERGOOD output voltage             | Vol             |         | POWERGOOD = 250 μA                                                                                    | _                                | _                                | 0.1                              | V    |

|                     | POWERGOOD output current             | Іон             |         | POWERGOOD = 5.5 V                                                                                     | _                                | _                                | 1.0                              | μА   |

|                     | CTL threshold                        | Vтннст          | 3       | _                                                                                                     | 0.55                             | 0.95                             | 1.45                             | V    |

|                     | voltage                              | VTHLCT          |         | _                                                                                                     | 0.40                             | 0.80                             | 1.30                             | ]    |

| Control block       | CTL pin input current                | IICTL           |         | CTL = 3.7 V                                                                                           | _                                | _                                | 1.0                              | μА   |

|                     | FSEL threshold voltage               | VTHHFS          | - 6     | _                                                                                                     | 2.96                             | _                                | _                                | V    |

|                     |                                      | VTHLFS          | 0       | _                                                                                                     | _                                | _                                | 0.74                             | V    |

| Reference           | VREF voltage                         | VREF            | 4       | $ \begin{array}{l} \text{VREF} = -2.7 \; \mu\text{A}, \\ \text{OUT} = -100 \; \text{mA} \end{array} $ | 1.176                            | 1.200                            | 1.224                            | V    |

| voltage block       | VREF load stability                  | Loadref         | 1 4     | VREF = −1.0 mA                                                                                        | _                                | _                                | 20                               | mV   |

|                     | Shut down power supply               | IVDD1           |         | CTL = 0 V,<br>All circuits in OFF state                                                               | _                                | _                                | 1.0                              | μА   |

|                     | current                              | Ivdd1H          |         | CTL = 0 V, VDD = 5.5 V                                                                                | _                                | _                                | 1.0                              | μΑ   |

| General             | Standby power supply current (DC/DC) | IVDD2           | 10      | CTL = 3.7 V, OUT = 0 A,<br>FSEL = 0 V                                                                 | _                                | 4.0                              | 8.0                              | mA   |

|                     | Power-on invalid current             | IVDD            |         | CTL = 3.7 V,<br>VOUT = 90%*4                                                                          | _                                | 800                              | 1500                             | μА   |

<sup>\*1 :</sup> The minimum value of  $V_{\text{DD}}$  is the 2.5 V or  $V_{\text{OUT}}$  setting value  $\mbox{$\pm$}$  0.6 V, whichever is higher.

$<sup>^{\</sup>star}2~$  : The  $\pm$  leak at the LX pin includes the current of the internal circuit.

$<sup>^{\</sup>star}3$ : Detected with respect to the output voltage setting value of  $V_{\text{REFIN}}$

<sup>\*4 :</sup> Current consumption based on 100% ON-duty (High side FET in full ON state). The SW FET gate drive current is not included because the device is in full ON state (no switching operation). Also the load current is not included.

# 9. Test Circuit for Measuring Typical Operating Characteristics

| Component    | Specification    | Vendor     | Part Number                  | Remark                        |

|--------------|------------------|------------|------------------------------|-------------------------------|

| R1           | 1 ΜΩ             | KOA        | RK73G1JTTD D 1 MΩ            |                               |

| R3-1<br>R3-2 | 7.5 kΩ<br>120 kΩ | SSM<br>SSM | RR0816-752-D<br>RR0816-124-D | At VOUT = 2.5 V setting       |

| R4           | 300 kΩ           | SSM        | RR0816-304-D                 |                               |

| R5           | 1 ΜΩ             | KOA        | RK73G1JTTD D 1 MΩ            |                               |

| C1           | 4.7 μF           | TDK        | C2012JB1A475K                |                               |

| C2           | 4.7 μF           | TDK        | C2012JB1A475K                |                               |

| C6           | 0.1 μF           | TDK        | C1608JB1H104K                | For adjusting slow start time |

| L1           | 2.2 µH           | TDK        | VLF4012AT-2R2M               | 2.0 MHz operation             |

| L1           | 1.5 µH           | TDK        | VLF4012AT-1R5M               | 3.2 MHz operation             |

#### Note:

These components are recommended based on the operating tests authorized.

TDK : TDK Corporation SSM : SUSUMU Co., Ltd KOA : KOA Corporation

## 10. Application Notes

## 10.1 Selection of Components

#### 10.1.1 Selection of an External Inductor

Basically it dose not need to design inductor. This IC is designed to operate efficiently with a 2.2  $\mu$ H (2.0 MHz operation) or 1.5  $\mu$ H (3.2 MHz operation) inductor.

The inductor should be rated for a saturation current higher than the LX peak current value during normal operating conditions, and should have a minimal DC resistance. (100 m $\Omega$  or less is recommended.)

LX peak current value IPK is obtained by the following formula.

$$I_{PK} = I_{OUT} + \frac{V_{IN} - V_{OUT}}{L} \times \frac{D}{fosc} \times \frac{1}{2} = I_{OUT} + \frac{(V_{IN} - V_{OUT}) \times V_{OUT}}{2 \times L \times fosc \times V_{IN}}$$

L : External inductor value

lout : Load current

V<sub>IN</sub> : Power supply voltageV<sub>OUT</sub> : Output setting voltage

The maximum peak current value IPK;

D : ON- duty to be switched( = Vout/Vin) fosc : Switching frequency (2.0 MHz or 3.2 MHz)

ex) At  $V_{IN} = 3.7 \text{ V}$ ,  $V_{OUT} = 2.5 \text{ V}$ ,  $I_{OUT} = 0.8 \text{ A}$ ,  $L = 2.2 \mu\text{H}$ ,  $I_{OUT} = 2.0 \text{ MHz}$

$I_{PK} = I_{OUT} + \frac{(V_{IN} - V_{OUT}) \times V_{OUT}}{2 \times L \times fosc \times V_{IN}} = 0.8 \text{ A} + \frac{(3.7 \text{ V} - 2.5 \text{ V}) \times 2.5 \text{ V}}{2 \times 2.2 \text{ µH} \times 2 \text{ MHz} \times 3.7 \text{ V}} = 0.89 \text{ A}$

#### 10.1.2 I/O Capacitor Selection

- Select a low equivalent series resistance (ESR) for the VDD input capacitor to suppress dissipation from ripple currents.

- Also select a low equivalent series resistance (ESR) for the output capacitor. The variation in the inductor current causes ripple currents on the output capacitor which, in turn, causes ripple voltages an output equal to the amount of variation multiplied by the ESR value. The output capacitor value has a significant impact on the operating stability of the device when used as a DC/DC converter. Therefore, Cypress generally recommends a 4.7 μF capacitor, or a larger capacitor value can be used if ripple voltages are not suitable. If the V<sub>IN</sub>/V<sub>OUT</sub> voltage difference is within 0.6 V, the use of a 10 μF output capacitor value is recommended.

- Types of capacitors

Ceramic capacitors are effective for reducing the ESR and afford smaller DC/DC converter circuit. However, power supply functions as a heat generator, therefore avoid to use capacitor with the F-temperature rating (-80% to +20%). Cypress recommends capacitors with the B-temperature rating ( $\pm$  10% to  $\pm$  20%).

Normal electrolytic capacitors are not recommended due to their high ESR.

Tantalum capacitor will reduce ESR, however, it is dangerous to use because it turns into short mode when damaged. If you insist on using a tantalum capacitor, Cypress recommends the type with an internal fuse.

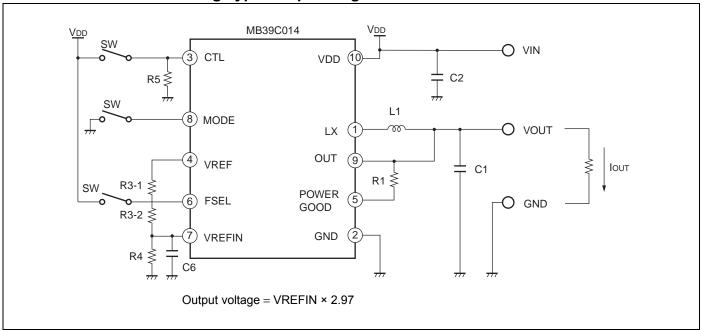

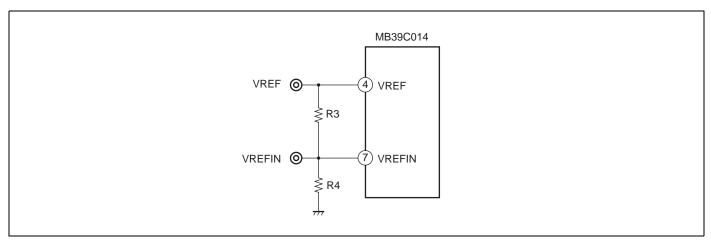

## 10.2 Output Voltage Setting

The output voltage Vout of this IC is defined by the voltage input to VREFIN. Supply the voltage for inputting to VREFIN from an external power supply, or set the VREF output by dividing it with resistors.

The output voltage when the VREFIN voltage is set by dividing the VREF voltage with resistors is shown in the following formula.

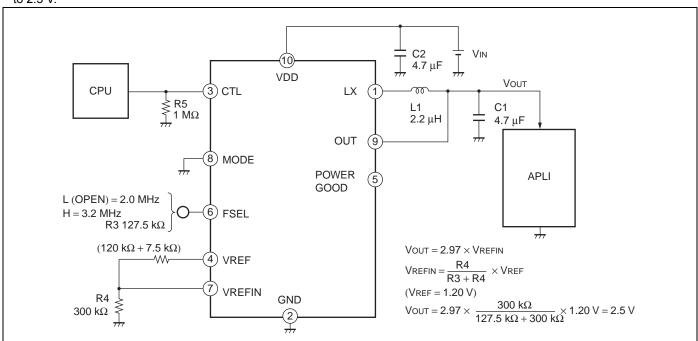

$$V_{OUT} = 2.97 \times V_{REFIN}, \qquad V_{REFIN} = \frac{R4}{R3 + R4} \times V_{REF}$$

$$(V_{REF} = 1.20 \text{ V})$$

#### Note:

Refer to "Application Circuit Examples" for an example of this circuit.

Although the output voltage is defined according to the dividing ratio of resistance, select the resistance value so that the current flowing through the resistance does not exceed the VREF current rating (1 mA).

## 10.3 About Conversion Efficiency

The conversion efficiency can be improved by reducing the loss of the DC/DC converter circuit.

The total loss (PLOSS) of the DC/DC converter is roughly divided as follows:

$P_{LOSS} = P_{CONT} + P_{SW} + P_{C}$

PCONT : Control system circuit loss (The power used for this IC to operate, including the gate driving power for internal SW

FETs)

Psw : Switching loss (The loss caused during switching of the IC's internal SW FETs)

Pc : Continuity loss (The loss caused when currents flow through the IC's internal SW FETs and external circuits)

The IC's control circuit loss (PCONT) is extremely small, less than 100 mW with no load.

As the IC contains FETs which can switch faster with less power, the continuity loss (Pc) is more predominant as the loss during heavy-load operation than the control circuit loss (Pcont) and switching loss (Psw).

Furthermore, the continuity loss (Pc) is divided roughly into the loss by internal SW FET ON-resistance and by external inductor series resistance.

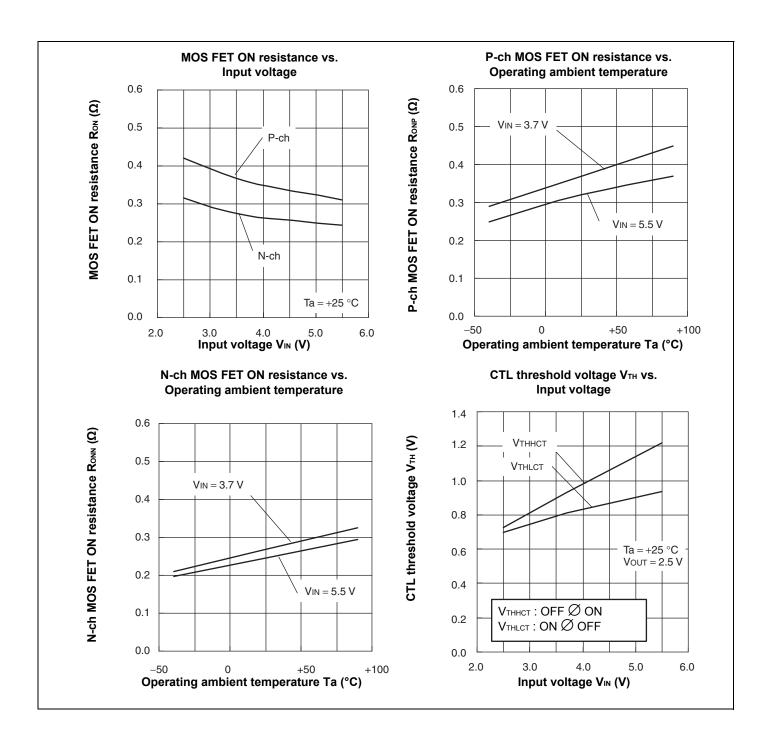

$$P_C = I_{OUT^2} \times (RDC + D \times R_{ONP} + (1 - D) \times R_{ONN})$$

D : Switching ON-duty cycle (= Vout / VIN)

RONP : Internal P-ch SW FET ON resistance

RONN : Internal N-ch SW FET ON resistance

RDC : External inductor series resistance

louт : Load current

The above formula indicates that it is important to reduce RDC as much as possible to improve efficiency by selecting components.

## 10.4 Power Dissipation and Heat Considerations

The IC is so efficient that no consideration is required in most of the cases. However, if the IC is used at a low power supply voltage, heavy load, high output voltage, or high temperature, it requires further consideration for higher efficiency.

The internal loss (P) is roughly obtained from the following formula:

$$P = I_{OUT}^2 \times (D \times R_{ONP} + (1 - D) \times R_{ONN})$$

D : Switching ON-duty cycle ( = Vout / VIN)

Ronp : Internal P-ch SW FET ON resistance

Ronn : Internal N-ch SW FET ON resistance

IOUT : Output current

The loss expressed by the above formula is mainly continuity loss. The internal loss includes the switching loss and the control circuit loss as well but they are so small compared to the continuity loss they can be ignored.

In this IC with Ronp greater than Ronn, the larger the on-duty cycle, the greater the loss.

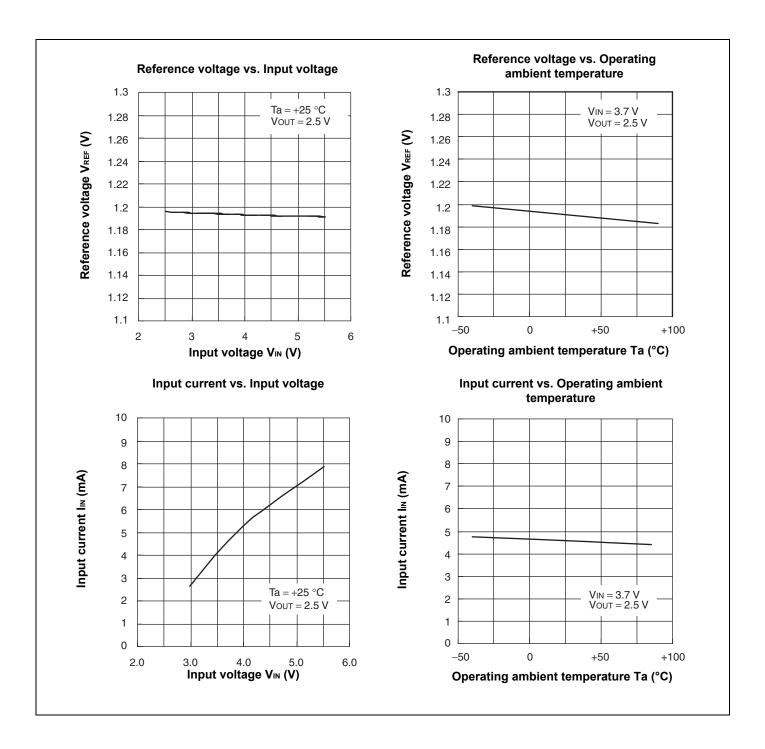

When assuming  $V_{IN} = 3.7 \text{ V}$ ,  $Ta = +70^{\circ}\text{C}$  for example,  $R_{ONP} = 0.42 \Omega$  and  $R_{ONN} = 0.36 \Omega$  according to the graph "MOS FET ON resistance vs. Operating ambient temperature". The IC's internal loss P is 144 mW at  $V_{OUT} = 2.5 \text{ V}$  and  $I_{OUT} = 0.6 \text{ A}$ . According to the graph "Power dissipation vs. Operating ambient temperature", the power dissipation at an operating ambient temperature Ta of  $+70^{\circ}\text{C}$  is 539 mW and the internal loss is smaller than the power dissipation.

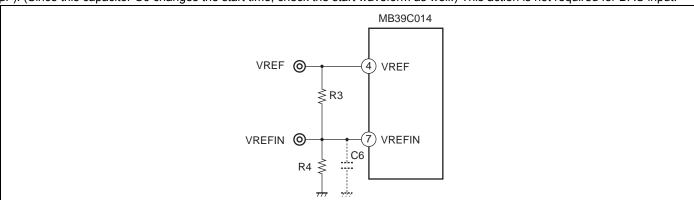

## 10.5 Transient Response

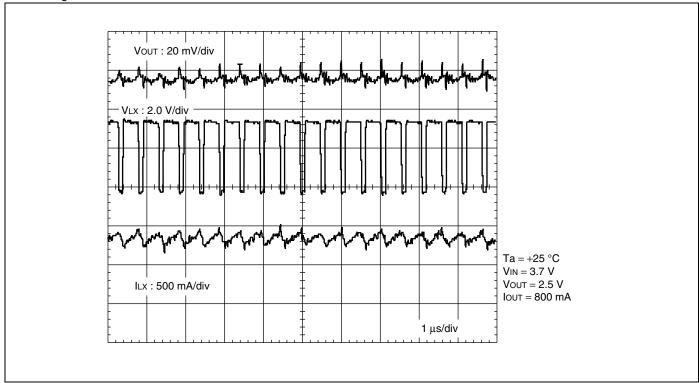

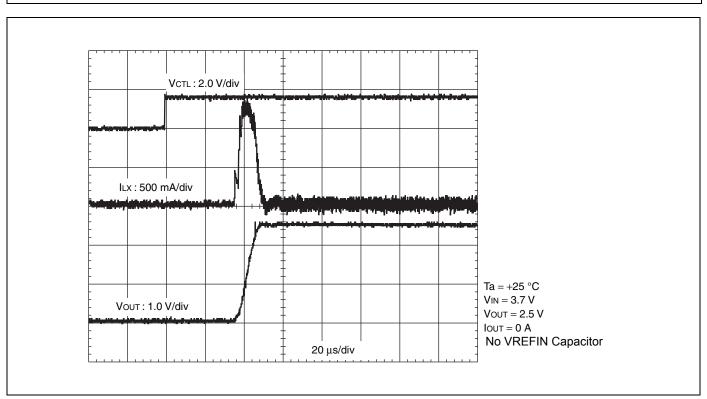

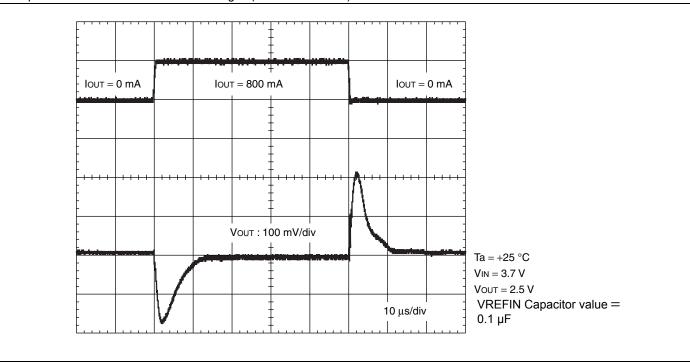

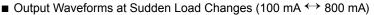

Normally,  $I_{OUT}$  is suddenly changed while  $V_{IN}$  and  $V_{OUT}$  are maintained constant, responsiveness including the response time and overshoot/undershoot voltage is checked. As this IC has built-in Error Amp with an optimized design, it shows good transient response characteristics. However, if ringing upon sudden change of the load is high due to the operating conditions, add capacitor C6 (e.g. 0.1  $\mu$ F). (Since this capacitor C6 changes the start time, check the start waveform as well.) This action is not required for DAC input.

Document Number: 002-08361 Rev. \*C

#### 10.6 Board Layout, Design Example

The board layout needs to be designed to ensure the stable operation of this IC. Follow the procedure below for designing the layout.

- Arrange the input capacitor (Cin) as close as possible to both the VDD and GND pins. Make a thru-hole (TH) near the pins of this capacitor if the board has planes for power and GND.

- Large AC currents flow between this IC and the input capacitor (Cin), output capacitor (Co), and external inductor (L). Group these components as close as possible to this IC to reduce the overall loop area occupied by this group. Also try to mount these components on the same surface and arrange wiring without thru-hole wiring. Use thick, short, and straight routes to wire the net (The layout by planes is recommended.).

- The feedback wiring to the OUT should be wired from the voltage output pin closest to the output capacitor (Co). The OUT pin is extremely sensitive and should thus be kept wired away from the LX pin of this IC as far as possible.

- If applying voltage to the VREFIN pin through dividing resistors, arrange the resistors so that the wiring can be kept as short as possible. Also arrange them so that the GND pin of the VREFIN resistor is close to the IC's GND pin. Further, provide a GND exclusively for the control line so that the resistor can be connected via a path that does not carry current. If installing a bypass capacitor for the VREFIN, put it close to the VREFIN pin.

- Try to make a GND plane on the surface to which this IC will be mounted. For efficient heat dissipation when using the SON-10 package, Cypress recommends providing a thermal via in the footprint of the thermal pad.

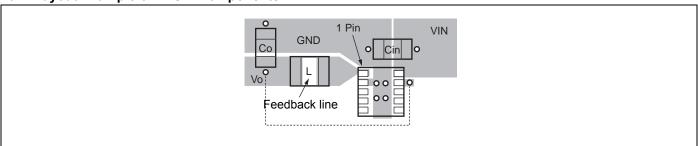

#### 10.7 Layout Example of IC SW Components

## 10.8 Notes for Circuit Design

- The switching operation of this IC works by monitoring and controlling the peak current which, incidentally, serves as form of short-circuit protection. However, do not leave the output short-circuited for long periods of time. If the output is short-circuited where VIN < 2.9 V, the current limit value (peak current to the inductor) tends to rise. Leaving in the short-circuit state, the temperature of this IC will continue rising and activate the thermal protection.

- Once the thermal protection stops the output, the temperature of the IC will go down and operation will resume, after which the output will repeat the starting and stopping.

- Although this effect will not destroy the IC, the thermal exposure to the IC over prolonged hours may affect the peripherals surrounding it.

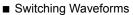

## 11. Example of Standard Operation Characteristics

(Shown below is an example of characteristics for connection according to "Test Circuit for Measuring Typical Operating Characteristics").

■ Output Waveforms at Sudden Load Changes (0 mA ↔ 800 mA)

## 12. Application Circuit Examples

## 12.1 Application Circuit Example 1

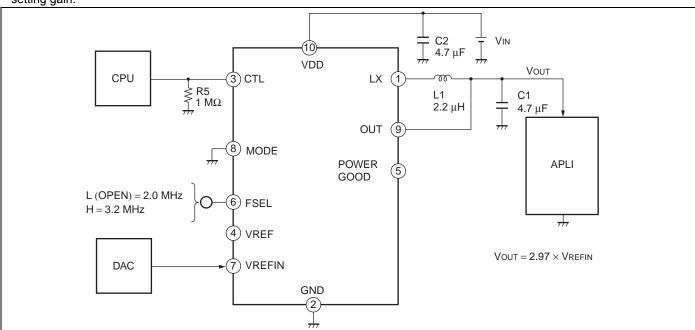

■ An external voltage is input to the reference voltage external input (VREFIN), and the Vouт voltage is set to 2.97 times the Vouт setting gain.

## 12.2 Application Circuit Example 2

■ The voltage of VREF pin is input to the reference voltage external input (VREFIN) by the dividing resistors. The Vour voltage is set to 2.5 V.

## 12.3 Application Circuit Example Components List

| Component | Item                     | Part Number                                | Specification                | Package      | Vendor |

|-----------|--------------------------|--------------------------------------------|------------------------------|--------------|--------|

| L1        | Inductor                 | VLF4012AT-2R2M                             | 2.2 μH, RDC = 76 mΩ          | SMD          | TDK    |

|           | inductor                 | MIPW3226D2R2M                              | 2.2 μH, RDC = 100 mΩ         | SMD          | FDK    |

| C1        | C1 Ceramic C2012JB1A475K |                                            | 4.7 µF (10 V)                | 2012         | TDK    |

| C2        | Ceramic capacitor        | C2012JB1A475K                              | 4.7 μF (10 V)                | 2012         | TDK    |

| R3        | Resistor                 | RK73G1JTTD D 7.5 kΩ<br>RK73G1JTTD D 120 kΩ | 7.5 kΩ<br>120 kΩ             | 1608<br>1608 | KOA    |

| R4        | Resistor                 | RK73G1JTTD D 300 kΩ                        | 300 kΩ                       | 1608         | KOA    |

| R5        | Resistor                 | RK73G1JTTD D                               | $1~\mathrm{M}\Omega\pm0.5\%$ | 1608         | KOA    |

TDK : TDK Corporation FDK : FDK Corporation KOA : KOA Corporation

## 13. Usage Precautions

#### 1. Do not Configure the IC Over the Maximum Ratings

If the IC is used over the maximum ratings, the LSI may be permanently damaged.

It is preferable for the device to normally operate within the recommended usage conditions. Usage outside of these conditions can adversely affect reliability of the LSI.

## 2. Use the Devices Within Recommended Operating Conditions

The recommended operating conditions are the conditions under which the LSI is guaranteed to operate.

The electrical ratings are guaranteed when the device is used within the recommended operating conditions and under the conditions stated for each item.

#### 3. Printed Circuit Board Ground Lines Should be Set up With Consideration for Common Impedance

#### 4. Take Appropriate Static Electricity Measures.

- Containers for semiconductor materials should have anti-static protection or be made of conductive material.

- After mounting, printed circuit boards should be stored and shipped in conductive bags or containers.

- Work platforms, tools, and instruments should be properly grounded.

- Working personnel should be grounded with resistance of 250 k $\Omega$  to 1 M $\Omega$  between body and ground.

#### 5. Do not Apply Negative Voltages.

The use of negative voltages below -0.3 V may create parasitic transistors on LSI lines, which can cause abnormal operation.

## 14. Ordering Information

| Part Number         | Package                        | Remarks |

|---------------------|--------------------------------|---------|

| MB39C014PN-🗆 🗆 🗀 E1 | 10-pin plastic SON<br>(WNK010) | -       |

## 15. RoHS Compliance Information

The LSI products of Cypress with "E1" are compliant with RoHS Directive, and has observed the standard of lead, cadmium, mercury, hexavalent chromium, polybrominated biphenyls (PBB), and polybrominated diphenylethers (PBDE).

A product whose part number has trailing characters "E1" is RoHS compliant.

Document Number: 002-08361 Rev. \*C Page 29 of 32

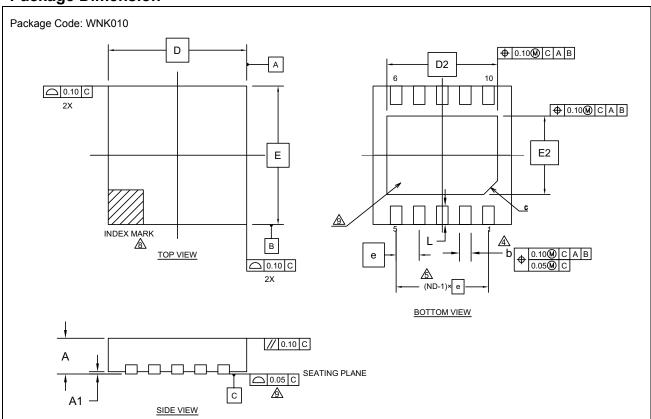

## 16. Package Dimension

| SYMBOL         | MILLIMETER     |          |      |  |  |

|----------------|----------------|----------|------|--|--|

| STIVIBUL       | MIN.           | NOM.     | MAX. |  |  |

| Α              |                |          | 0.75 |  |  |

| A1             | 0.00           | 0.05     |      |  |  |

| D              | •              | 3.00 BSC | ;    |  |  |

| E              | ;              | 3.00 BSC | ,    |  |  |

| b              | 0.22           | 0.25     | 0.28 |  |  |

| D <sub>2</sub> | 2              | 2.40 BSC |      |  |  |

| E <sub>2</sub> |                | 1.70 BSC |      |  |  |

| е              | 0.50 BSC       |          |      |  |  |

| С              | 0.30 REF       |          |      |  |  |

| L              | 0.30 0.40 0.50 |          |      |  |  |

#### NOTE

- 1. ALL DIMENSIONS ARE IN MILLIMETERS.

- 2. DIMENSIONING AND TOLERANCINC CONFORMS TO ASME Y14.5-1994.

- 3. N IS THE TOTAL NUMBER OF TERMINALS.

- ⚠ DIMENSION "b" APPLIES TO METALLIZED TERMINAL AND IS MEASURED BETWEEN 0.15 AND 0.30mm FROM TERMINAL TIP.IF THE TERMINAL HAS THE OPTIONAL RADIUS ON THE OTHER END OF THE TERMINAL. THE DIMENSION "b"SHOULD NOT BE MEASURED IN THAT RADIUS AREA.

- ⚠ ND REFER TO THE NUMBER OF TERMINALS ON D OR E SIDE.

- 6. MAX. PACKAGE WARPAGE IS 0.05mm.

- 7. MAXIMUM ALLOWABLE BURRS IS 0.076mm IN ALL DIRECTIONS.

- PIN #1 ID ON TOP WILL BE LOCATED WITHIN INDICATED ZONE.

- BILATERAL COPLANARITY ZONE APPLIES TO THE EXPOSED HEAT SINK SLUG AS WELL AS THE TERMINALS.

- 10. JEDEC SPECIFICATION NO. REF: N/A

002-15676 Rev. \*\*

# **Document History**

| Revision | ECN     | Orig. of<br>Change | Submission<br>Date | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|----------|---------|--------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| **       | _       | TAOA               | 11/21/2008         | Migrated to Cypress and assigned document number 002-08361. No change to document contents or format.                                                                                                                                                                                                                                                                                                                                                |  |

| *A       | 5490964 | TAOA               | 10/24/2016         | Updated to Cypress template.                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| *B       | 5633455 | НІХТ               | 02/17/2017         | Updated Pin Assignment: Change the package name from LCC-10P-M04 to WNK010 Updated Ordering Information: Change the package name from LCC-10P-M04 to WNK010 Deleted the words, "Lead Free version", in the Remarks. Deleted "Marking Format (Lead Free Version)" Deleted "Labeling Sample (Lead Free Version)" Deleted "Evaluation Board Specification" Deleted "EV Board Ordering Information" Updated Package Dimension: Updated to Cypress format |  |

| *C       | 5761100 | MASG               | 06/05/2017         | Adapted Cypress new logo.                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

## Sales, Solutions, and Legal Information

## **Worldwide Sales and Design Support**

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

cypress.com/wireless

#### **Products**

Wireless/RF

ARM® Cortex® Microcontrollers cypress.com/arm Automotive cypress.com/automotive Clocks & Buffers cypress.com/clocks Interface cypress.com/interface Internet of Things cypress.com/iot Memory cypress.com/memory Microcontrollers cypress.com/mcu **PSoC** cypress.com/psoc Power Management ICs cypress.com/pmic Touch Sensing cypress.com/touch **USB Controllers** cypress.com/usb

#### **PSoC® Solutions**

PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP | PSoC 6

#### **Cypress Developer Community**

Forums | WICED IOT Forums | Projects | Video | Blogs | Training | Components

#### **Technical Support**

cypress.com/support

© Cypress Semiconductor Corporation, 2008-2017. This document is the property of Cypress Semiconductor Corporation and its subsidiaries, including Spansion LLC ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United States and other countries worldwide. Cypress reserves all rights under such laws and treaties and does not, except as specifically stated in this paragraph, grant any license under its patents, copyrights, trademarks, or other intellectual property rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software, then Cypress parally a personal, non-exclusive, nontransferable license (without the right to sublicense) (1) under its copyright rights in the Software (a) for Software provided in source code form, to modify and reproduce the Software solely for use with Cypress hardware products, only internally within your organization, and (b) to distribute the Software in binary code form externally to end users (either directly or indirectly through resellers and distributors), solely for use on Cypress hardware product units, and (2) under those claims of Cypress's patents that are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely for use with Cypress hardware products. Any other use, reproduction, modification, translation, or compilation of the Software is prohibited.

TO THE EXTENT PERMITTED BY APPLICABLE LAW, CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE OR ACCOMPANYING HARDWARE, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. To the extent permitted by applicable law, Cypress reserves the right to make changes to this document without further notice. Cypress does not assume any liability arising out of the application or use of any product or circuit described in this document. Any information provided in this document, including any sample design information or programming code, is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Cypress products are not designed, intended, or authorized for use as critical components in systems designed or intended for the operation of weapons, weapons systems, nuclear installations, life-support devices or systems, other medical devices or systems (including resuscitation equipment and surgical implants), pollution control or hazardous substances management, or other uses where the failure of the device or system could cause personal injury, death, or property damage ("Unintended Uses"). A critical component is any component of a device or system whose failure to perform can be reasonably expected to cause the failure of the device or system, or to affect its safety or effectiveness. Cypress is not liable, in whole or in part, and you shall and hereby do release Cypress from any claim, damage, or other liability arising from or related to all Unintended Uses of Cypress products. You shall indemnify and hold Cypress harmless from and against all claims, costs, damages, and other liabilities, including claims for personal injury or death, arising from or related to any Unintended Uses of Cypress products.

Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, WICED, PSoC, CapSense, EZ-USB, F-RAM, and Traveo are trademarks or registered trademarks of Cypress in the United States and other countries. For a more complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respective owners.