### **General Description**

The MAX5936/MAX5937 are hot-swap controllers for -10V to -80V rails. The MAX5936/MAX5937 allow circuit line cards to be safely hot-plugged into a live back-plane without causing a glitch on the power supply. These devices integrate a circuit-breaker function requiring no RSENSE.

The MAX5936/MAX5937 provide a controlled turn-on for circuit cards, limiting inrush, preventing glitches on the power-supply rail, and preventing damage to board connectors and components. Before startup, the devices perform a Load Probe™ test to detect the presence of a short-circuit condition. If a short-circuit condition does not exist, the device limits the inrush current drawn by the load by gradually turning on the external MOSFET. Once the external MOSFET is fully enhanced, the MAX5936/MAX5937 provides overcurrent and short-circuit protection by monitoring the voltage drop across the RDS(ON) of the external power MOSFET. The MAX5936/MAX5937 integrate a 400mA fast GATE pulldown to guarantee that the power MOSFET is rapidly turned off in the event of an overcurrent or short-circuit condition.

The MAX5936/MAX5937 protect the system against input voltage (V<sub>IN</sub>) steps by providing V<sub>IN</sub> step immunity. The MAX5936/MAX5937 provide an accurate UVLO voltage. The MAX5936 has an open-drain, active-low PGOOD output and the MAX5937 has an open-drain, active-high PGOOD output.

The MAX5936/MAX5937 are offered with 100mV, 200mV, and 400mV circuit-breaker thresholds, in addition to a non-circuit-breaker option. These devices are offered in latched and autoretry fault management, are available in 8-pin SO packages, and specified for the extended (-40°C to +85°C) temperature range (see the *Selector Guide*).

### **Applications**

### \_Features

- -10V to -80V Operation

- No RSENSE Required

- Drives Large Power MOSFETS

- Programmable Inrush Current Limit During Hot Plug

- 100mV, 200mV, 400mV, and No-Circuit-Breaker Threshold Options

- Circuit-Breaker Fault with Transient Rejection

- Shorted Load Detection (Load Probe) Before Power MOSFET Turn-On

- ±2.4% Accurate Undervoltage Lockout (UVLO)

- Autoretry and Latched Fault Management Available

- Low Quiescent Current

### Ordering Information

| PART       | TEMP RANGE     | PIN-PACKAGE |

|------------|----------------|-------------|

| MAX5936ESA | -40°C to +85°C | 8 SO        |

| MAX5937ESA | -40°C to +85°C | 8 SO        |

**Note:** The first "\_" represents A for the autoretry and L for the latched fault management option. The second "\_" represents the circuit-breaker threshold. See the Selector Guide for additional information.

# Selector Guide and Typical Operating Circuit appear at end of data sheet.

#### TOP VIEW GND 1 UVLO 2 STEP\_MON 3 VEE 4 () FOR THE MAX5937. PGOOD (PGOOD) (PG

Load Probe is a trademark of Maxim Integrated Products, Inc.

###

Servers

Telecom Line Cards Network Switches

Network Routers

Solid-State Circuit Breaker

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at www.baash62944642, or visit Maxim's website at www.maxim-ic.com.

M/XI/M

# -48V Hot-Swap Controllers with VIN Step Immunity and No RSENSE

### **ABSOLUTE MAXIMUM RATINGS**

VEE, VOUT, PGOOD (PGOOD), LP,

| STEP_MON to GND                     | +0.3V to -85V |

|-------------------------------------|---------------|

| PGOOD (PGOOD) to Vout               | 0.3V to +85V  |

| PGOOD (PGOOD), LP, STEP_MON to VEE  | 0.3V to +85V  |

| GATE to VEE                         | 0.3V to +20V  |

| UVLO to V <sub>EE</sub>             | 0.3V to +6V   |

| Input Current                       |               |

| LP (internally, duty-cycle limited) | 1A            |

| PGOOD (PGOOD) (continuous)          |               |

| GATE (during 15V clamp, continuous)                   | 30mA           |

|-------------------------------------------------------|----------------|

| GATE (during 2V clamp, continuous)                    | 50mA           |

| GATE (during gate pulldown, continuous)               | 50mA           |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |                |

| 8-Pin SO (derate 5.9mW/°C above +70°C).               | 471mW          |

| Operating Temperature Range                           | 40°C to +85°C  |

| Junction Temperature                                  | +150°C         |

| Storage Temperature Range                             | 65°C to +150°C |

| Lead Temperature (soldering, 10s)                     | +300°C         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

$(V_{EE} = -10V \text{ to } -80V, V_{IN} = GND - V_{EE}, V_{STEP\_MON} = V_{EE}, R_{LP} = 200\Omega, UVLO \text{ open}, T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise noted}.$ Typical values are at V<sub>EE</sub> = -48V, T<sub>A</sub> = +25^{\circ}C.) (Notes 1, 2)

| PARAMETER                                             | SYMBOL      | CONDITIONS                                                   |                           | MIN   | ТҮР   | MAX   | UNITS |

|-------------------------------------------------------|-------------|--------------------------------------------------------------|---------------------------|-------|-------|-------|-------|

| Operating Voltage Range                               | VEE         | Referenced to GN                                             | D                         | -80   |       | -10   | V     |

| Operating Supply Current                              | ICC         |                                                              |                           |       | 0.95  | 1.4   | mA    |

|                                                       | VUVLO,R     | IV <sub>EE</sub> I increasing                                |                           | -33.5 | -31.0 | -29.5 | V     |

| Default V <sub>EE</sub> Undervoltage Lockout          | Vuvlo,f     | IV <sub>EE</sub> I decreasing                                |                           |       | -28   |       | V     |

| UVLO Reference Threshold,<br>V <sub>EE</sub> Rising   | VUVLO_REF,R | V <sub>UVLO</sub> increasing                                 |                           | 1.219 | 1.25  | 1.281 | V     |

| UVLO Reference Threshold,<br>V <sub>EE</sub> Falling  | VUVLO_REF,F | V <sub>UVLO</sub> decreasing                                 | l                         | 1.069 | 1.125 | 1.181 | V     |

| UVLO Input Resistance                                 |             |                                                              |                           | 20    |       | 50    | kΩ    |

| UVLO Transient Rejection                              | tovrej      |                                                              |                           | 0.8   | 1.5   | 2.25  | ms    |

| Power-Up Delay (Note 3)                               | tondly      |                                                              |                           | 80    | 220   | 380   | ms    |

| V <sub>EE</sub> and UVLO Glitch Rejection<br>(Note 4) | tREJ        |                                                              |                           | 0.8   | 1.5   | 2.25  | ms    |

| VOUT to VEE Leakage Current                           |             | V <sub>EE</sub> = -80V, V <sub>OUT</sub> = GND               |                           |       | 0.01  | 1     | μA    |

| LP to VEE Leakage Current                             |             | $V_{EE} = -80V, V_{LP} =$                                    | GND                       |       | 0.01  | 1     | μA    |

| External Gate-Drive Voltage                           | VGS         | Vgate - Vee                                                  | $V_{IN} = 10V$            | 6.5   | 6.8   | 7.2   | V     |

| External Gale-Drive voltage                           | VGS         | VGATE - VEE                                                  | $14 \leq V_{IN} \leq 80V$ | 8.1   | 10    | 12.8  | v     |

|                                                       |             | MOSFET fully                                                 | I <sub>CLAMP</sub> = 9mA  | 13.5  | 16    |       |       |

|                                                       |             | enhanced                                                     | $I_{CLAMP} = 20mA$        |       | 17    | 19.5  | V     |

| GATE to V <sub>EE</sub> Clamp Voltage                 |             | Power-off,                                                   | $I_{CLAMP} = 1mA$         |       | 2.1   | 2.55  | v     |

|                                                       |             | $V_{EE} = GND$                                               | $I_{CLAMP} = 10mA$        |       | 2.5   | 2.9   |       |

| Open-Loop Gate-Charge Current                         |             | V <sub>GATE</sub> = V <sub>EE</sub> , V <sub>OUT</sub> = GND |                           | -66   | -52   | -35   | μA    |

| GATE Pulldown Switch                                  | POATE       |                                                              | V <sub>IN</sub> > 10V     |       | 9     | 14.1  | Ω     |

| On-Resistance                                         | Rgate       |                                                              | $V_{IN} > 14V$            |       | 7.5   | 12.5  | 52    |

| Output-Voltage Slew Rate                              | SR          | l dV <sub>OUT</sub> /dt l                                    |                           | 2.4   | 9     | 14.8  | V/ms  |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{EE} = -10V \text{ to } -80V, V_{IN} = GND - V_{EE}, V_{STEP\_MON} = V_{EE}, R_{LP} = 200\Omega$ , UVLO open,  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted. Typical values are at  $V_{EE} = -48V$ ,  $T_A = +25^{\circ}C$ .) (Notes 1, 2)

| PARAMETER                                      | SYMBOL              | <b>CONDITIONS</b><br>-40°C < T <sub>A</sub> <+85°C    |                        | MIN      | ТҮР                     | МАХ   | UNITS  |

|------------------------------------------------|---------------------|-------------------------------------------------------|------------------------|----------|-------------------------|-------|--------|

| Circuit-Breaker Tempco                         |                     |                                                       |                        |          | 6000                    |       | ppm/°C |

| Circuit-Breaker Glitch Rejection               | tCB_DLY             |                                                       |                        | 1.0      | 1.2                     | 1.6   | ms     |

|                                                |                     | MAX5936LA/                                            | T <sub>A</sub> = +85°C | 118      | 140                     | 162   |        |

|                                                |                     | MAX5936AA/                                            | $T_A = +25^{\circ}C$   | 85       | 100                     | 115   |        |

|                                                |                     | MAX5937LA/                                            | T <sub>A</sub> = -10°C | 64       | 79                      | 94    |        |

|                                                |                     | MAX5937AA                                             | $T_A = -40^{\circ}C$   |          | 62                      |       |        |

|                                                |                     | MAX5936LB/                                            | $T_A = +85^{\circ}C$   | 244      | 284                     | 324   |        |

| Circuit-Breaker Threshold                      | V <sub>CB</sub>     | MAX5936AB/                                            | $T_A = +25^{\circ}C$   | 180      | 200                     | 220   | mV     |

| Circuit-Dreaker Threshold                      | VCB                 | MAX5937LB/                                            | T <sub>A</sub> = -10°C | 135      | 158                     | 181   | 1110   |

|                                                |                     | MAX5937AB                                             | $T_A = -40^{\circ}C$   |          | 124                     |       |        |

|                                                |                     | MAX5936LC/                                            | $T_A = +85^{\circ}C$   | 485      | 568                     | 651   |        |

|                                                |                     | MAX5936AC/                                            | $T_A = +25^{\circ}C$   | 355      | 400                     | 445   |        |

|                                                |                     | MAX5937LC/                                            | T <sub>A</sub> = -10°C | 270      | 316                     | 362   |        |

|                                                |                     | MAX5937AC                                             | T <sub>A</sub> = -40°C |          | 248                     |       |        |

|                                                |                     | MAX5936LA/                                            | T <sub>A</sub> = +85°C | 220      | 280                     | 340   |        |

|                                                | V <sub>SC</sub>     | MAX5936AA/<br>MAX5937LA/<br>MAX5937AA                 | $T_A = +25^{\circ}C$   | 160      | 200                     | 240   | mV     |

|                                                |                     |                                                       | T <sub>A</sub> = -10°C | 111      | 158                     | 205   |        |

|                                                |                     |                                                       | T <sub>A</sub> = -40°C |          | 124                     |       |        |

|                                                |                     | MAX5936LB/<br>MAX5936AB/<br>MAX5937LB/<br>MAX5937AB   | T <sub>A</sub> = +85°C | 470      | 568                     | 667   |        |

| Short-Circuit Threshold                        |                     |                                                       | $T_A = +25^{\circ}C$   | 350      | 400                     | 450   |        |

| Short-Circuit Threshold                        |                     |                                                       | T <sub>A</sub> = -10°C | 255      | 316                     | 377   |        |

|                                                |                     |                                                       | T <sub>A</sub> = -40°C |          | 248                     |       |        |

|                                                |                     | MAX5936LC/<br>MAX5936AC/<br>MAX5937LC/<br>MAX5937AC   | T <sub>A</sub> = +85°C | 962      | 1136                    | 1310  |        |

|                                                |                     |                                                       | $T_A = +25^{\circ}C$   | 700      | 800                     | 900   |        |

|                                                |                     |                                                       | T <sub>A</sub> = -10°C | 510      | 632                     | 754   |        |

|                                                |                     |                                                       | $T_A = -40^{\circ}C$   |          | 496                     |       |        |

| Short-Circuit Response Time<br>(Note 5)        |                     | 150mV overdrive, $C_{LOAD} = 0$ ,<br>to GATE below 1V |                        |          | 330                     | 500   | ns     |

| INPUT-VOLTAGE-STEP PROTECT                     | ION                 | 1                                                     |                        |          |                         |       |        |

| Input-Voltage-Step Detection<br>Threshold      | STEPTH              |                                                       |                        | 1.219    | 1.250                   | 1.281 | V      |

| Input-Voltage-Step Threshold<br>Offset Current | ISTEP_OS            |                                                       |                        | -10.8    | -10.0                   | -9.2  | μA     |

| LOAD-PROBE CIRCUIT                             |                     | 1                                                     |                        | <b>I</b> |                         |       | •      |

| Load-Probe Switch On-Resistance                |                     | $V_{LP} - V_{EE} = 1V$                                |                        |          | 7.5                     | 11    | Ω      |

| Load-Probe Timeout                             | tLP                 |                                                       |                        | 80       | 220                     | 380   | ms     |

| Load-Probe Retry Time                          | t <sub>LP_OFF</sub> |                                                       |                        |          | 16 x<br>t <sub>LP</sub> |       | s      |

| Load-Probe Voltage Threshold                   | VTHSC-DET           | Referenced to GN                                      | 1D                     | -220     | -200                    | -180  | mV     |

M/XI/M

### ELECTRICAL CHARACTERISTICS (continued)

$(V_{EE} = -10V \text{ to } -80V, V_{IN} = \text{GND} - V_{EE}, V_{\text{STEP}MON} = V_{EE}, R_{LP} = 200\Omega$ , UVLO open,  $T_A = -40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$ , unless otherwise noted. Typical values are at  $V_{EE} = -48V$ ,  $T_A = +25^{\circ}\text{C}$ .) (Notes 1, 2)

| PARAMETER                                      | SYMBOL             | CONDITIONS                                                                                          | MIN  | ТҮР                       | MAX  | UNITS |  |  |

|------------------------------------------------|--------------------|-----------------------------------------------------------------------------------------------------|------|---------------------------|------|-------|--|--|

| LOGIC AND FAULT MANAGEMENT                     |                    |                                                                                                     |      |                           |      |       |  |  |

| Autoretry Delay                                | <sup>t</sup> RETRY |                                                                                                     |      | 16 x<br>t <sub>LP</sub>   |      | S     |  |  |

| PGOOD (PGOOD) Assertion                        |                    | IV <sub>OUT</sub> - V <sub>EE</sub> I falling                                                       |      | 0.74 x<br>V <sub>CB</sub> |      |       |  |  |

| Threshold                                      |                    | Hysteresis                                                                                          |      | 0.26 x<br>V <sub>CB</sub> |      | mV    |  |  |

| PGOOD (PGOOD) Assertion Delay<br>Time (Note 6) |                    |                                                                                                     | 0.67 | 1.26                      | 1.85 | ms    |  |  |

| PGOOD (PGOOD) Low Voltage                      | Vol                | $I_{SINK}$ = 1mA, referenced to V <sub>OUT</sub> ,<br>V <sub>OUT</sub> < GND - 5V for PGOOD (PGOOD) |      | 0.05                      | 0.4  | V     |  |  |

| PGOOD (PGOOD) Open-Drain<br>Leakage            | ١L                 | $V_{EE} = -80V$ , $V_{PGOOD}(\overline{PGOOD})$ ,<br>$V_{PGOOD}(\overline{PGOOD}) = GND$            |      | 0.01                      | 1    | μA    |  |  |

Note 1: All currents into pins are positive and all currents out of pins are negative. All voltages referenced to V<sub>EE</sub>, unless otherwise specified.

Note 2: All limits are 100% tested at +25°C and +85°C. Limits at -40°C and -10°C are guaranteed by characterization.

Note 3: Delay time from a valid on-condition until the load probe test begins.

Note 4: VEE or UVLO voltages below VUVLO,F or VUVLO\_REF,F, respectively, are ignored during this time.

Note 5: The time ( $V_{OUT} - V_{EE}$ ) > V<sub>SC</sub> + overdrive until ( $V_{GATE} - V_{EE}$ ) drops to approximately 90% of its initial high value.

Note 6: The time when the PGOOD (PGOOD) condition is met until the PGOOD (PGOOD) signal is asserted.

www.DataSheet4U.com

# -48V Hot-Swap Controllers with VIN Step Immunity and No RSENSE

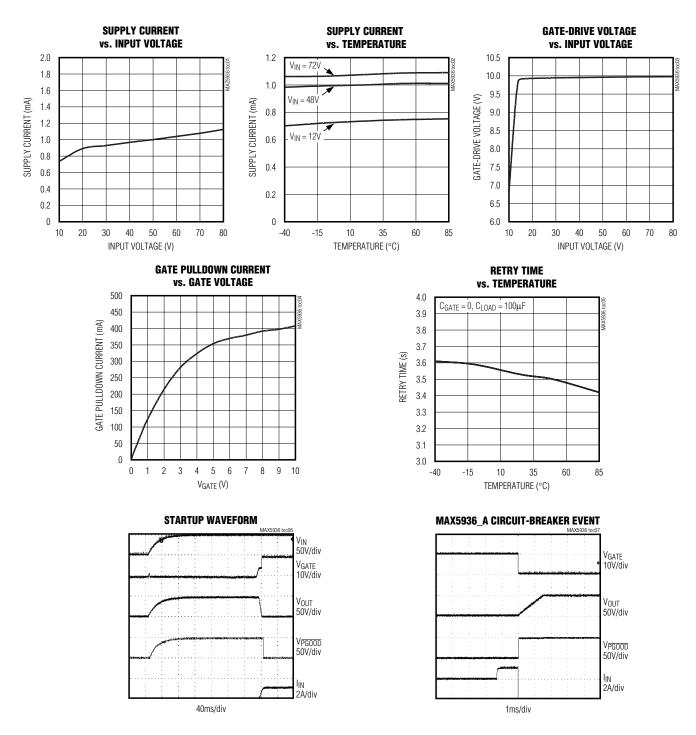

### **Typical Operating Characteristics**

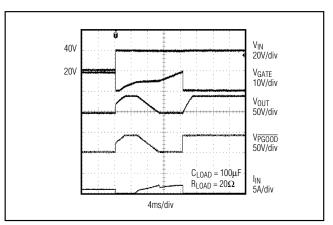

(V<sub>EE</sub> = -48V, GND = 0V, V<sub>IN</sub> = GND - V<sub>EE</sub>, all voltages are referenced to V<sub>EE</sub>,  $T_A$  = +25°C, unless otherwise noted.)

///XI//

www.DataSheet4U.com

### **Typical Operating Characteristics (continued)**

(VEE = -48V, GND = 0V, VIN = GND - VEE, all voltages are referenced to VEE, TA = +25°C, unless otherwise noted.)

www.DataSheet4U.com

### **Pin Description**

| PIN NAME |   |                 | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|----------|---|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|          |   | NAME            | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| 1        | 1 | GND             | Ground. The high-supply connection for a negative-rail hot-swap controller.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| 2        | 2 | UVLO            | Undervoltage Lockout Input, On/Off Control. Referenced to V <sub>EE</sub> . Drive UVLO above the 1.25V rising threshold to turn on the device. To turn off the device, drive UVLO below the 1.125V falling threshold for the 1.5ms glitch rejection period. Leave UVLO disconnected for the default 31V undervoltage lockout threshold. Cycle UVLO to unlatch the MAX5936L/MAX5937L after a fault. Cycling UVLO low deasserts PGOOD.                                                                                                                  |  |  |  |

| 3        | 3 | STEP_MON        | Input Voltage Step Monitor. 1.25V voltage threshold referenced to V <sub>EE</sub> . Connect a resistor between STEP_MON and V <sub>EE</sub> to set the step sensitivity. Connect a capacitor from GND to STEP_MON to adjust the step response relative to a step increase at V <sub>EE</sub> to eliminate false circuit-breaker and short-circuit faults. Connect to V <sub>EE</sub> to disable the step immunity function (see the <i>Selecting Resistor and Capacitor Values for Step Monitor</i> section in the <i>Applications Information</i> ). |  |  |  |

| 4        | 4 | V <sub>EE</sub> | Negative Input Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| 5        | 5 | LP              | Load-Probe Detect. Connect a resistor from LP to V <sub>OUT</sub> to set the load-probe test current.<br>Limit load-probe test current to 1A. Connect to V <sub>EE</sub> to disable the load-probe function.                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| 6        | 6 | GATE            | Gate-Drive Output. Connect to the gate of the external n-channel MOSFET.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| 7        | 7 | Vout            | Output Voltage Sense. VOUT is the negative rail of the load. Connect to the drain of the external n-channel MOSFET.                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 8        | _ | PGOOD           | Power-Good, Active-Low, Open-Drain Output. Referenced to $V_{OUT}$ . PGOOD asserts low when $V_{OUT}$ is within the limits and there is no fault.                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| _        | 8 | PGOOD           | Power-Good, Active-High, Open-Drain Output. Referenced to $V_{OUT}$ . PGOOD asserts high when $V_{OUT}$ is within limits and there is no fault.                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

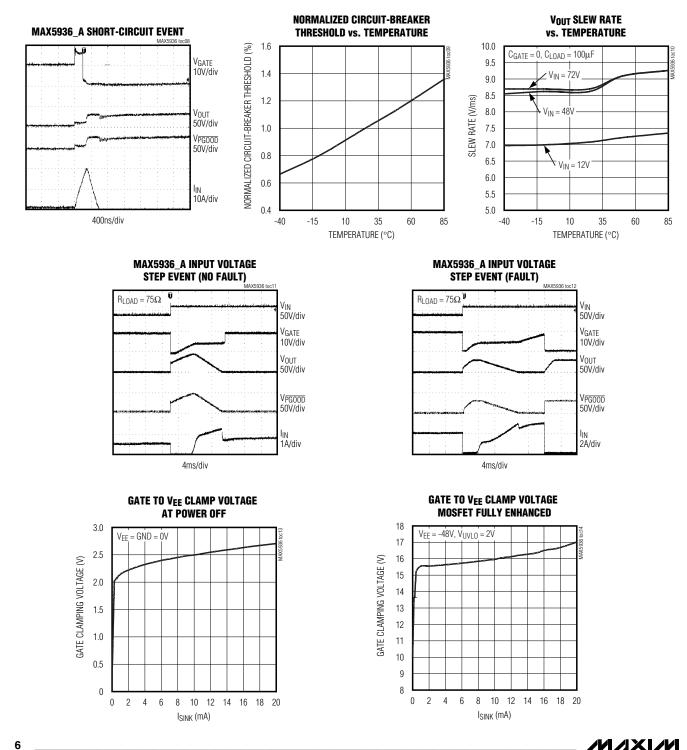

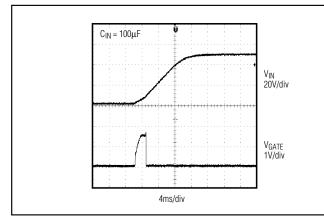

### **Detailed Description**

The MAX5936/MAX5937 hot-swap controllers incorporate overcurrent fault management and are intended for negative-supply-rail applications. The MAX5936/MAX5937 eliminate the need for an external RSENSE and include VIN input-step protection and load probe, which prevents powering up into a shorted load. They are intended for negative 48V telecom power systems where low cost, flexibility, multifault management, and compact size are required. The MAX5936/MAX5937 are ideal for the widest range of systems from those requiring low current with small MOSFETs to high-current systems requiring large power MOSFETs and low on-resistance.

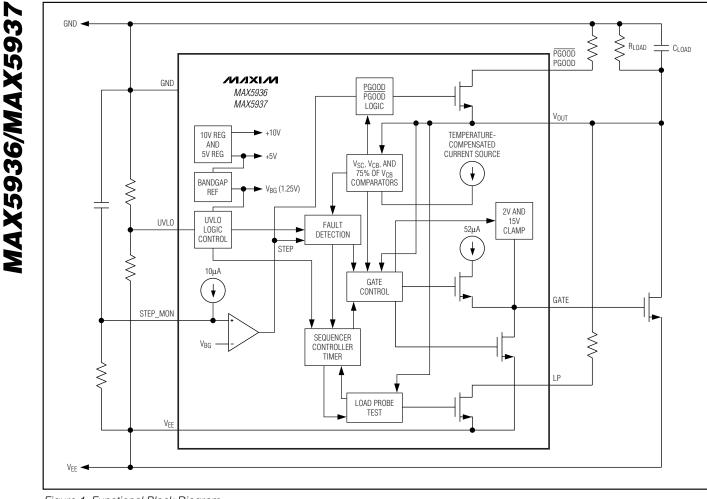

The MAX5936/MAX5937 control an external n-channel power MOSFET placed in the negative supply path of an external load. When no power is applied, the GATE output of the MAX5936/MAX5937 clamps the VGS of the MOSFET to 2V, keeping the MOSFET turned off. When power is applied to the MAX5936/MAX5937, the 2V

M/XI/M

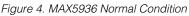

clamp at the GATE output is replaced by a strong pulldown device pulling GATE to VEE and the VGS of the MOSFET to 0V. As shown in Figure 2, this transition enables the MAX5936/MAX5937 to keep the power MOSFET continually off during the board insertion phase when the circuit board first makes contact with the backplane. Without this clamp, the GATE output of a powered-down controller would be floating and the MOSFET reverse transfer capacitance (gate-to-drain) would pull up and turn on the MOSFET gate when the MOSFET drain is rapidly pulled up by the VIN step during backplane contact. The MAX5936/MAX5937 GATE clamp can overcome the gate-to-drain capacitance of large power MOSFETs with added slew-rate control (CSLEW) capacitors while eliminating the need for additional gate-to-source capacitance. The MAX5936/ MAX5937 will keep the MOSFET off indefinitely if the supply voltage is below the user-set UVLO threshold or if a short circuit is detected in the load connected to the drain of the power MOSFET.

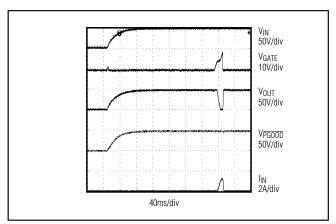

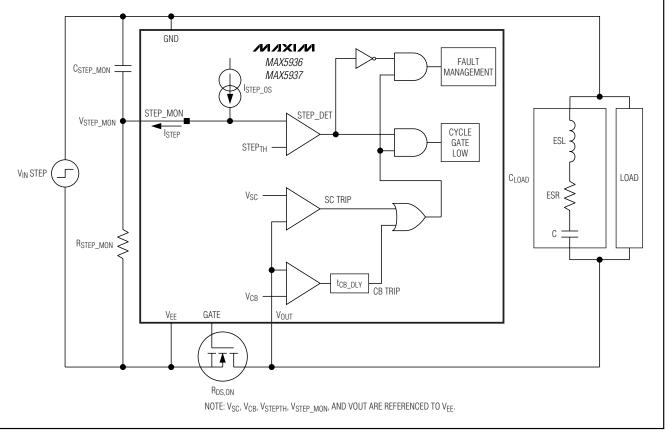

Figure 1. Functional Block Diagram

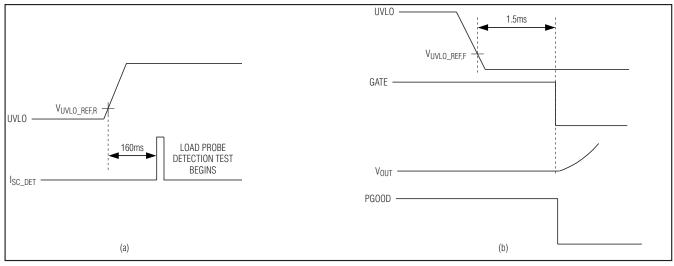

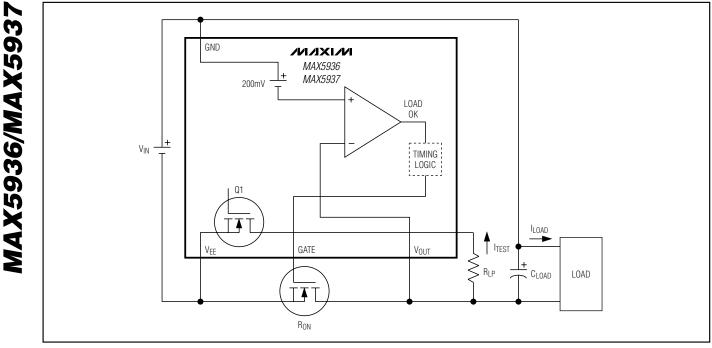

The MAX5936/MAX5937 conduct a load-probe test after contact transients from the hot plug-in have settled. This follows the MAX5936/MAX5937 power-up (when the UVLO condition has been met for 220ms (tLP)) and prior to the turn-on of the power MOSFET. This test pulls a user-programmable current through the load (1A, max) for up to 220ms and tests for a voltage of 200mV across the load at VOUT. This current is set by an external resistor, RLP, between VOUT and LP (Figure 14). When the voltage across the load exceeds 200mV, the test is truncated and the GATE turn-on sequence is started. If at the end of the 220ms test period the voltage across the load has not reached 200mV, the load is assumed to be shorted and the current to the load from the LP pin is shut off. The MAX5936A\_/MAX5937A\_ will timeout for 16 x tLP then retry the load-probe test. The MAX5936L\_/ MAX5937L\_ will latch the fault condition indefinitely until

\_\_\_\_\_

8

the UVLO is brought below 1.125V for 1.5ms or the power is recycled. See the *Applications Information* section for recommendations on selecting  $R_{LP}$  to set the current level.

Upon successful completion of the load-probe test, the MAX5936/MAX5937 enter the power-up GATE cycle and begin ramping the GATE voltage with a 52µA current source. This current source is restricted if V<sub>OUT</sub> begins to ramp down faster than the default 9V/ms slew rate. Charging up GATE enhances the power MOSFET in a controlled manner and ramping V<sub>OUT</sub> at a user-settable rate controls the inrush current from the backplane. The MAX5936/MAX5937 continue to charge up the GATE until one of two events occurs: a normal power-up GATE cycle is completed or a power-up to fault management is detected (see the *GATE Cycles* section in *Appendix A*).

Figure 2. GATE Voltage Clamp During Power-Up

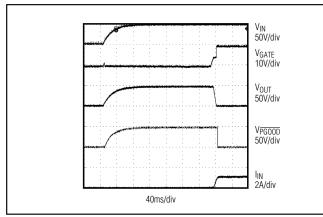

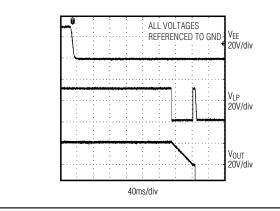

In a normal power-up GATE cycle, the voltage at V<sub>OUT</sub> (referenced to V<sub>EE</sub>) ramps to below 74% of the circuitbreaker threshold voltage, V<sub>CB</sub>. At this time, the remaining GATE voltage is rapidly pulled up to full enhancement. PGOOD is asserted 1.26ms after GATE is fully enhanced (see Figure 4). If the voltage at V<sub>OUT</sub> remains above 74% of the V<sub>CB</sub> (when GATE reaches 90% of full enhancement), then a power-up to fault management fault has occurred (see Figure 5). GATE is rapidly pulled to V<sub>EE</sub>, turning off the power MOSFET and disconnecting the load. PGOOD remains deasserted and the MAX5936/MAX5937 enter the fault management mode.

When the power MOSFET is fully enhanced, the MAX5936/MAX5937 monitor the drain voltage (V<sub>OUT</sub>) for circuit-breaker and short-circuit faults. The MAX5936/MAX5937 make use of the power MOSFET's  $R_{DS(ON)}$  as the current-sense resistance to detect excessive current

Figure 3. Load Probe Test During Initial Power-Up

through the load. The short-circuit threshold voltage, VSC, is twice VCB (VSC =  $2 \times VCB$ ) and is available in 100mV, 200mV, and 400mV thresholds. VCB and VSC are temperature-compensated (increasing with temperature) to track the normalized temperature coefficient of RDS(ON) for typical power MOSFETs.

When the load current is increased during full enhancement, this causes V<sub>OUT</sub> to exceed V<sub>CB</sub> but remains less than V<sub>SC</sub>, and starts the 1.2ms circuit-breaker glitch rejection timer. At the end of the glitch rejection period, if V<sub>OUT</sub> still exceeds V<sub>CB</sub>, the GATE is immediately pulled to V<sub>EE</sub> (330ns), PGOOD (PGOOD) is deasserted, and the part enters fault management. Alternatively, during full enhancement when V<sub>OUT</sub> exceeds V<sub>SC</sub>, there is no glitch rejection timer. GATE is immediately pulled to V<sub>EE</sub>, PGOOD is deasserted, and the part enters fault management.

Figure 5. MAX5936 Startup in Fault Condition

MAX5936/MAX5937

The VIN step immunity provides a means for transitioning through a large step increase in VIN with minimal backplane inrush current and without shutting down the load. Without VIN step immunity (when the power MOSFET is fully enhanced), a step increase in VIN will result in a high inrush current and a large step in VOUT, which can trip the circuit breaker. With VIN step immunity, the STEP\_MON input detects the step before a short circuit is detected at VOUT and alters the MAX5936/MAX5937 response to VOUT exceeding VSC due to the step. The 1.25V voltage threshold at STEP\_MON and a 10µA current source at STEP\_MON allow the user to set the sensitivity of the step detection with an external resistor to VEE. A capacitor is placed between GND and the STEP\_MON input, which, in conjunction with the resistor, sets the STEP\_MON time constant. When a step is detected by the STEP MON input to rise above its threshold (STEPTH), the overcurrent fault management is blocked and remains blocked as long as STEPTH is exceeded. When STEPTH is exceeded, the MAX5936/MAX5937 take no action until VOUT rises above VSC or above VCB for the 1.2ms circuitbreaker glitch rejection period. When either of these conditions occurs, a step GATE cycle begins and the GATE is immediately brought to VEE, which turns off the power MOSFET to minimize the resulting inrush current surge from the backplane and PGOOD remains asserted. GATE is held at VEE for 350µs, and after about 1ms, begins to ramp up thereby enhancing the power MOSFET in a controlled manner as in the power-up GATE cycle. This provides a controlled inrush current to charge the load capacitance to the new supply voltage (see the GATE Cycles section in Appendix A).

As in the case of the power-up GATE cycle, if  $V_{OUT}$  drops to less than 74% of the programmed  $V_{CB}$ , independent of the state of STEP\_MON, the GATE voltage

40V VIN 5V/div VGATE 10V/div VOUT 20V/div VOUT 20V/div VPGOOD 20V/div VPGOOD 20V/div IN 1A/div NA/Div VOUT 20V/div NOV 20V/div 20V/div NOV 20V/div 20V/div

<sup>2ms/div</sup> Figure 6. MAX5936 Response to a Step Input (V<sub>OUT</sub> < 0.74V<sub>CB</sub>)

is rapidly pulled to full enhancement. PGOOD remains asserted throughout the step. Otherwise, if the STEP\_MON input has decayed below its threshold but V<sub>OUT</sub> remains above 74% of the programmed V<sub>CB</sub> (when GATE reaches 90% of full enhancement), (a step-to-fault management fault has occurred). GATE is rapidly pulled to V<sub>EE</sub>, turning off the power MOSFET and disconnecting the load, PGOOD (PGOOD) is deasserted, and the MAX5936/MAX5937 enter the fault management mode.

#### **Fault Management**

Fault management can be triggered by the following conditions:

- VOUT exceeds 74% of VCB during GATE ramp at 90% of full enhancement,

- VOUT exceeds the VCB for longer than 1.2ms during full enhancement,

- VOUT exceeds the VSC during full enhancement, and

- Load-probe test fails.

Once in the fault management mode, GATE will always be pulled to  $V_{EE}$  to turn off the external MOSFET and PGOOD (PGOOD) will always be deasserted. The MAX5936A\_/MAX5937A\_ have automatic retry following a fault while the MAX5936L\_/MAX5937L remain latched in the fault condition.

#### Autoretry Fault Management (MAX5936A\_/MAX5937A\_)

If the MAX5936A\_/MAX5937A\_entered fault management due to circuit-breaker and short-circuit faults, the autoretry timer starts immediately. The timer times out in 3.5s (typ) and at the end of the timeout, the sequencer initiates a load-probe test. If this is successful, it starts a normal power-up GATE cycle.

Figure 7. MAX5936 Response to a Step Input (V<sub>OUT</sub> > 0.74V<sub>CB</sub>)

MAX5936/MAX5937

## -48V Hot-Swap Controllers with VIN Step Immunity and No RSENSE

#### Latched Fault Management (MAX5936L\_/MAX5937L\_)

When the MAX5936L\_/MAX5937L\_ enter fault management, they remain in this condition indefinitely until the power is recycled or until UVLO is brought below 1.125V for 1.5ms (typ) (when the short-circuit or circuitbreaker fault has cleared, the sequencer initiates a loadprobe test). If this is successful, it starts a normal power-up GATE cycle. A manual reset circuit (Figure 8) can be used to clear the latch.

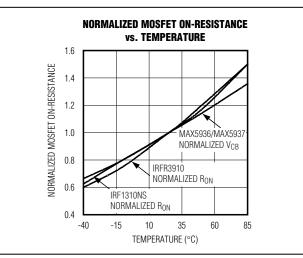

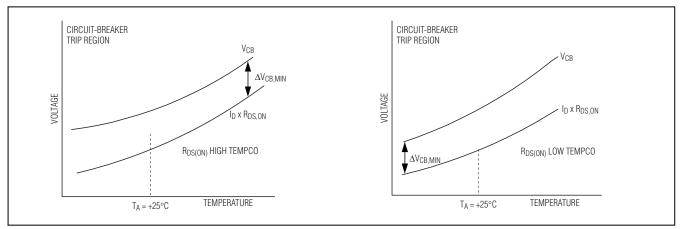

#### **Circuit-Breaker Thresholds**

The MAX5936/MAX5937 are available with 100mV, 200mV, and 400mV circuit-breaker thresholds. The short-circuit voltage threshold (V<sub>SC</sub>) is twice the circuit-breaker threshold voltage (V<sub>CB</sub>). In the MAX5936/MAX5937, V<sub>CB</sub> and V<sub>SC</sub> are temperature-compensated (increasing with temperature) to track the normalized temperature gradient of typical power MOSFETs.

The proper circuit-breaker threshold for an application depends on the R<sub>DS(ON)</sub> of the external power MOSFET and the maximum current the load is expected to draw. To avoid false fault indication and dropping of the load, the designer must take into account the load response to voltage ripples and noise from the backplane power supply, as well as switching currents in the downstream DC-DC converter that is loading the circuit. While the circuit-breaker threshold has glitch rejection that ignores ripples and noise lasting less than 1.2ms, the short-circuit detection is designed to respond very quickly (less than 330ns) to a short circuit. V<sub>SC</sub> and V<sub>CB</sub> must be selected from the three available ranges with an adequate margin to cover all possible ripples, noise, and system current transients.

Figure 8. Resetting MAX5936L/MAX5937L after a Fault Condition Using a Push-Button Switch

The short-circuit and circuit-breaker voltages are sensed at V<sub>OUT</sub>, which is the drain of the power MOSFET. The R<sub>DS(ON)</sub> of the MOSFET is the current-sense resistance, so the total current through the load and load capacitance is the drain current of the power MOSFET. Accordingly, the voltage at V<sub>OUT</sub> as a function of MOSFET drain current is:

#### VOUT = ID, MOSFET X RDS(ON)

The temperature compensation of the MAX5936/ MAX5937 is designed to track the RDS(ON) of the typical power MOSFET. Figure 9 shows the typical normalized tempco of the circuit-breaker threshold along with the normalized tempco of RDS(ON) for two typical power MOSFETS. When determining the circuit-breaker threshold in an application, go to the data sheet of the power MOSFET and locate the manufacturer's maximum RDS(ON) at +25°C with a VGS of 10V. Next, find the figure presenting the tempco of normalized RDS(ON) or on-resistance vs. temperature. Because this curve is in normalized units typically with a value of 1 at  $+25^{\circ}$ C, it is possible to multiply the curve by the drain voltage at +25°C and convert the curve to drain voltage. Now compare this curve to that of the MAX5936/MAX5937 normalized tempco of the circuit-breaker threshold to make a determination of the tracking error in mV between the power MOSFET [ID, MOSFET X RDS(ON)] and the MAX5936/MAX5937 over the application's operating temperature range. If the tempco of the power MOSFET is greater than that of the MAX5936/ MAX5937, then additional margin will be required in selecting the circuit-breaker and short-circuit voltages at higher temperatures as compared to +25°C. When dissipation in the power MOSFET is expected to lead to local temperature elevation relative to ambient conditions, then it becomes imperative that the MAX5936/ MAX5937 be located as close as possible to the power MOSFET. The marginal effect of temperature differences on circuit-breaker and short-circuit voltages can be estimated from a comparative plot such as Figure 9.

#### MAX5936LN and MAX5937LN

The MAX5936LN and MAX5937LN do not have circuitbreaker and short-circuit thresholds and these faults are ignored. For these devices PGOOD (PGOOD) asserts 1.26ms after GATE has ramped to 90% of full enhancement. The step detection function of the MAX5936LN and MAX5937LN responds to V<sub>IN</sub> and V<sub>OUT</sub> steps with the same voltage thresholds as the MAX5936\_C and MAX5937\_C.

Figure 9. MAX5936/MAX5937 Normalized Circuit-Breaker Threshold (V<sub>CB</sub>)

#### **PGOOD (PGOOD) Open-Drain Output** The power-good outputs, PGOOD (PGOOD), are open drain and are referenced to V<sub>OUT</sub>. They assert and latch if V<sub>OUT</sub> ramps below 72% of V<sub>CB</sub>, and with the built-in delay this occurs 1.26ms after the external MOSFET

becomes fully enhanced. PGOOD ( $\overrightarrow{PGOOD}$ ) deasserts any time the part enters fault management. PGOOD ( $\overrightarrow{PGOOD}$ ) has a delayed response to UVLO. The GATE goes to V<sub>EE</sub> when UVLO is brought below 1.125V for 1.5ms. This turns off the power MOSFET and allows VOUT to rise depending on the RC time constant of the load. PGOOD ( $\overrightarrow{PGOOD}$ ), in this situation, deasserts when V<sub>OUT</sub> rises above V<sub>CB</sub> for more than 1.4ms or above V<sub>SC</sub>, whichever occurs first (see Figure 12b). Due to the open-drain driver, PGOOD ( $\overline{PGOOD}$ ) requires an external pullup resistor to GND. Due to this external pullup, PGOOD will not follow positive V<sub>IN</sub> steps as well as if it were driven by an active pullup. As a result, when PGOOD ( $\overline{PGOOD}$ ) is asserted high, an apparent negative glitch appears at PGOOD ( $\overline{PGOOD}$ ) during a positive V<sub>IN</sub> step. This negative glitch is a result of the RC time constant of the external resistor and the PGOOD pin capacitance lagging the V<sub>IN</sub> step. It is not due to switching of the internal logic. To minimize this negative transient, it may be necessary to increase the pullup current and/or to add a small amount of capacitance from PGOOD ( $\overline{PGOOD}$ ) to GND to compensate for the pin capacitance.

**WARNING:** For the MAX5936\_N/MAX5937\_N, PGOOD (PGOOD) asserts 1.26ms after the power MOSFET is fully enhanced, independent of V<sub>OUT</sub>. Once the MOSFET is fully enhanced and UVLO is pulled below its respective threshold, GATE pulls to V<sub>EE</sub> to turn off the power MOSFET and disconnect the load. When UVLO is cycled low, PGOOD (PGOOD) is deasserted. In summary, once the MOSFET is fully enhanced, the MAX5936\_N/ MAX5937\_N ignore V<sub>OUT</sub> and deassert PGOOD (PGOOD) when UVLO goes low or when the power to the MAX5936\_N/ MAX5937\_N is fully recycled.

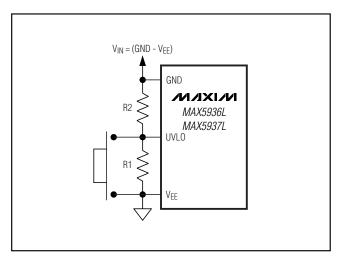

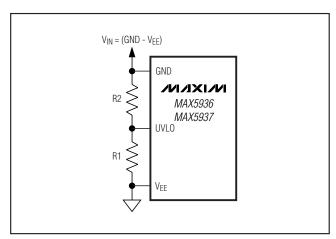

#### **Undervoltage Lockout (UVLO)**

UVLO provides an accurate means to set the turn-on voltage level for the MAX5936/MAX5937. Use a resistordivider network from GND to VEE to set the desired turn-on voltage (Figure 11). UVLO has hysteresis with a rising threshold of 1.25V and a falling threshold of 1.125V. A startup delay of 220ms allows contacts and voltages to settle prior to initiating the startup sequence (Figure 12a).

Figure 10. Circuit-Breaker Voltage Margin for High and Low Tempco Power MOSFETS

MAX5936/MAX5937

MAX5936/MAX5937

# -48V Hot-Swap Controllers with VIN Step Immunity and No RSENSE

This startup delay is from a valid UVLO condition until the start of the load-probe test. There is glitch rejection on UVLO going low, which requires that  $V_{UVLO}$  remains below its falling threshold for 1.5ms to turn off the part (Figure 12b). Use the following formula to calculate the MAX5936/MAX59337 turn-on voltage:

$$R2 = \left(\frac{V_{ON}}{V_{UVLO\_REF,R}} - 1\right) \times R1$$

Where V<sub>ON</sub> is the desired turn-on voltage of the MAX5936/MAX5937 and V<sub>UVLO\_REF,R</sub> is the 1.25V UVLO rising threshold.

Figure 11. Setting the MAX5936/MAX5937 Turn-On Voltage

#### Output Voltage (VOUT) Slew-Rate Control

The V<sub>OUT</sub> slew rate controls the inrush current required to charge the load capacitor. The MAX5936/MAX5937 have a default internal slew rate set for 9V/ms. The internal circuit establishing this slew rate accommodates up to about 1000pF of reverse transfer capacitance (miller capacitance) in the external power MOSFET without effecting the default slew rate. Using the default slew rate, the inrush current required to charge the load capacitance is given by:

$I_{INRUSH}$  (mA) =  $C_{LOAD}$  ( $\mu$ F) x SR (V/ms) where SR = 9V/ms (default, typ).

## Applications Information

#### Selecting Resistor and Capacitor for Step Monitor

When a positive  $V_{IN}$  step or ramp occurs, the  $V_{IN}$  increase results in a voltage rise at both STEP\_MON and VOUT relative to  $V_{EE}$ . When the voltage at STEP\_MON is above STEP<sub>TH</sub> the MAX5936/MAX5937 block short-circuit and circuit-breaker faults. During this STEP\_MON high condition, if VOUT rises above VSC, the MAX5936/MAX5937 immediately and very rapidly pull GATE to VEE. This turns off the power MOSFET to avoid inrush current spiking. GATE is held low for 350µs. About 1ms after the start of GATE pulldown, the MAX5936/MAX5937 begin to ramp GATE up to turn on the MOSFET in a controlled manner, which results in ramping VOUT down to the new supply level (see the *GATE Cycles* section in *Appendix A*).

Figure 12. UVLO Timing Diagram

This occurs with the least possible disturbance to V<sub>OUT</sub>, although during the brief period that the MOSFET is off, the voltage across the load droops slightly depending on the load current and load storage capacitance. PGOOD remains asserted throughout the V<sub>IN</sub> step event.

The objective in selecting the resistor and capacitor for the step monitor function is to ensure that the V<sub>IN</sub> steps of all anticipated slopes and magnitudes will be properly detected and blocked, which otherwise would result in a circuit-breaker or short-circuit fault. The following is a brief analysis for finding the resistor and capacitor. For a more complete analysis, see *Appendix B*.

Figure 13 is a functional diagram exhibiting the elements of the MAX5936/MAX5937 involved in the step immunity function. This block diagram shows the parallel relationship between V<sub>OUT</sub> and V<sub>STEP-MON</sub>. Each has an I\*R component establishing the DC level prior to a step. While it is referred to as a V<sub>IN</sub> step, it is the dynamic response to a finite voltage ramp that is of interest.

Given a positive  $V_{IN}$  ramp with a ramp rate of dV/dt, the approximate response of  $V_{OUT}$  to  $V_{IN}$  is:

$$V_{OUT}(t) = (dV/dt) \times \tau_C \times (1 - e^{(-t / \tau_L, eqv)})$$

where  $\tau_C = C_{LOAD} \times R_{DS(ON)}$  and  $\tau_{L,eqv}$  is the equivalent time constant of the load that must be found empirically (see *Appendix B*).

Similarly, the response of STEP\_MON to a VIN ramp is:

$V_{STEP\_MON}(t) = (dV/dt) \times \tau_{STEP} \times (1 - e^{(-t \ / \ \tau STEP)}) + 10 \mu A \\ \times R_{STEP}$

where  $\tau_{\text{STEP}} = \text{RSTEP}_{\text{MON}} \times \text{CSTEP}_{\text{MON}}$ .

For proper step detection, VSTEP\_MON must exceed STEPTH prior to VOUT reaching VSC or within 1.4ms of VOUT reaching VCB (overall VIN ramp rates anticipated in the application). VSTEP\_MON must be set below STEPTH with adequate margin,  $\Delta$ VSTEP\_MON, to accommodate the tolerance of both ISTEP\_OS (±8%) and RSTEP\_MON. RSTEP\_MON is typically set to 100k $\Omega$  which gives a  $\Delta$ VSTEP\_MON for a worst-case high of 0.36V.

Figure 13. MAX5936/MAX5937 Step Immunity Functional Diagram

## -48V Hot-Swap Controllers with VIN Step Immunity and No RSENSE

The margin of V<sub>OUT</sub> with respect to V<sub>SC</sub> and V<sub>CB</sub> was set when V<sub>SC</sub> and V<sub>CB</sub> were selected from the three available ranges. This margin may be lower at one of the temperature extremes and if so, that value should be used in the following discussion. These margins will be called  $\Delta$ V<sub>CB</sub> and  $\Delta$ V<sub>SC</sub> and they represent the minimum V<sub>OUT</sub> excursion required to trip the respective fault.

To set  $\tau_{STEP}$  to block all V<sub>CB</sub> and V<sub>SC</sub> faults for any ramp rate, find the ratio of  $\Delta V_{STEP}$ \_MON to  $\Delta V_{CB}$  and choose  $\tau_{STEP}$  so:

$\tau_{\text{STEP}} = 1.2 \times \tau_{\text{C}} \times \Delta V_{\text{STEP}}$  Mon /  $\Delta V_{\text{CB}}$

And since RSTEP\_MON = 100k  $\Omega.$  This results in CSTEP\_MON =  $\tau_{STEP}$  / 100k  $\Omega.$

After the first-pass component selection, if sufficient timing margin exists (see *Appendix B*), it is possible but not necessary to lower  $R_{STEP\_MON}$  below  $100k\Omega$  to reduce the sensitivity of STEP\_MON to V<sub>IN</sub> noise.

Appendix B gives a more complete analysis and discussion of the step monitor function. It provides methods for the characterization of the load response to a  $V_{\rm IN}$  ramp and graphical verification of the step monitor timing margins for a set of design parameters.

#### Selecting the PGOOD (PGOOD) Pullup Resistor

Due to the open-drain driver, PGOOD ( $\overrightarrow{PGOOD}$ ) requires an external pullup resistor to GND. This resistor should be selected to minimize the current load while PGOOD ( $\overrightarrow{PGOOD}$ ) is low. The PGOOD output specification for V<sub>OL</sub> is 0.4V at 1mA. As described in the *Detailed Description*, the external pullup interferes with the ability of PGOOD ( $\overrightarrow{PGOOD}$ ) to follow positive V<sub>IN</sub> steps as well as if it were driven by an active pullup. When PGOOD ( $\overrightarrow{PGOOD}$ ) is asserted high, an apparent negative glitch appears at PGOOD during a positive V<sub>IN</sub> step. To minimize this negative transient it may be necessary to increase the pullup current and/or to add a small amount of capacitance from PGOOD ( $\overrightarrow{PGOOD}$ ) to GND to compensate for the pin capacitance.

#### Setting the Test Current Level for Load-Probe Test

The load-probe test is a current test of the load that avoids turning on the power MOSFET. The MAX5936/ MAX5937 have an internal switch (Q1 in Figure 14) that pulls current through the load and through an external current-limiting resistor, R<sub>L</sub>P. During the test, this switch is pulsed on for up to 220ms (typ). Current is pulled through the load, which should charge up the load capacitance unless there is a short. If the voltage across the load exceeds 200mV, the test is truncated and normal powerup is allowed to proceed. If the voltage across the load does not reach 200mV in the 220ms period that the current is on, the load is assumed to be shorted and the current to the load from the LP pin is shut off. The MAX5936A\_/MAX5937A\_ time out for 16 x t\_P then retry the load-probe test. The MAX5936L\_/MAX5937L\_ latch the fault condition indefinitely until the UVLO is brought below 1.125V for 1.5ms or the power is recycled.

In the application, the current-limiting resistor should be selected to minimize the current pulled through the load while guaranteeing that it charges the maximum expected load capacitance to 220mV in 80ms. These parameters are the maximum load-probe test voltage and the minimum load-probe current pulse period, respectively. The maximum current possible is 1A, which is adequate to test a load capacitance as large as 170,000µF over the typical telecom operating voltage range.

#### ITEST (A) = $C_{LOAD,MAX}$ (F) x 220mV / 80ms

Since the minimum intended V<sub>IN</sub> for the application results in the lowest I<sub>TEST</sub>, during the load-probe test, this V<sub>IN,MIN</sub> should be used to set the R<sub>LP</sub>. This voltage will likely be near V<sub>ON,FALLING</sub> or V<sub>OFF</sub> for the application.

$\begin{array}{l} \mathsf{RTEST}(\Omega) = \mathsf{VIN}, \mathsf{MIN} \ / \ \mathsf{ITEST} = \mathsf{VIN}, \mathsf{MIN} \ \times \ \mathsf{80ms} \ / \\ (\mathsf{CLOAD}(\mathsf{MAX}) \ \times \ \mathsf{220mV}) \end{array}$

Example:  $V_{IN}$  operating range = 36V to 72V,  $C_{LOAD}$  = 10,000µF. First, find the RTEST, which will guarantee a successful test of the load.

$\label{eq:RLP} \begin{array}{l} \mathsf{R}_{\mathsf{LP}} = 36\mathsf{V}\times80\mathsf{ms}\,/\,(10,000\mu\mathsf{F}\times220\mathsf{mV}) = 1,309\Omega \Rightarrow \\ 1.30\mathsf{k}\Omega\,\pm1\% \end{array}$

Next, evaluate the RLP at the maximum operating voltage to verify that it will not exceed the 1A current limit for the load-probe test:

ITEST, MAX = VIN, MAX /  $R_{LP} = 72V / 1.30k\Omega = 55.4mA$

If the C<sub>LOAD</sub>(MAX) is increased to 170,000µF, the test current will approach the limit. In this case, R<sub>TEST</sub> will be a much lower value and must include the internal switch resistance. To find the external series resistor value that will guarantee a successful test at the lowest supply voltage, the maximum value for the load-probe switch on-resistance of 11 $\Omega$  should be used:

$$R_{LP,TOT} = 36V \times 80ms / (170,000\mu F \times 220mV) = 77\Omega = 11\Omega + R_{LP}$$

$$\mathsf{R}_{\mathsf{LP}} = 77\Omega - 11\Omega = 66\Omega \Longrightarrow 66.5\Omega \pm 1\%$$

Again R<sub>LP</sub> must be evaluated at the maximum operating voltage to verify that it will not exceed the 1A current limit for the load-probe test. In this case, the minimum value for the load-probe switch on-resistance of  $6\Omega$  should be used:

$\begin{array}{l} \text{ITEST,MAX} = \text{V}_{\text{IN,MAX}} / \text{R}_{\text{LP,TOT}} = 72 \text{V} / (66.5 \Omega + 6 \Omega) \\ = 993 \text{mA} \end{array}$

Figure 14. Load Probe Functional Diagram

#### Adjusting the VOUT Slew Rate

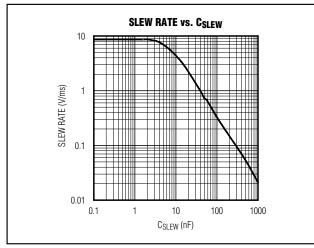

The default slew rate is set internally for 9V/ms. The slew rate can be reduced by placing an external capacitor from the drain of the power MOSFET to the GATE output of the MAX5936/MAX5937. Figure 15 shows a graph of Slew Rate vs.  $C_{SLEW}$ . This graph shows that for  $C_{SLEW} < 4700$  pF there is very little effect to the addition of external slew-rate control capacitance. This is intended so the GATE output can drive large MOSFETs with significant gate capacitance and still achieve the default slew rate. To select a slew-rate control capacitor, go into the graph with the desired slew rate and find the value of the miller capacitance. When  $C_{SLEW} > 4700$  pF, SR and  $C_{SLEW}$  are inversely related. Given the desired slew rate, the required  $C_{SLEW}$  is found as follows:

#### $C_{SLEW}(nF) = 23 / SR (V/ms)$

From the data sheet of the power MOSFET find the reverse transfer capacitance (gate-to-drain capacitance) above 10V. If the reverse transfer capacitance of the external power MOSFET is 5% or more of C<sub>SLEW</sub>, then it should be subtracted from C<sub>SLEW</sub> in the equation above.

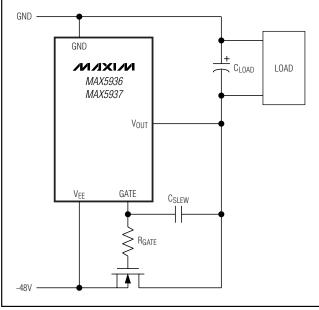

Figure 16 gives an example of the external circuit for controlling slew rate. Depending on the parasitics asso-

ciated with the selected power MOSFET, the addition of C<sub>SLEW</sub> may lead to oscillation while the MOSFET and GATE control are in the linear range. If this is an issue, an external resistor, R<sub>GATE</sub>, in series with the gate of the MOSFET is recommended to prevent possible oscillation. It should be as small as possible, e.g.,  $5\Omega$  to  $10\Omega$ , to avoid impacting the MOSFET turn-off performance of the MAX5936/MAX5937.

#### **Layout Guidelines**

To benefit from the temperature compensation designed into the MAX5936/MAX5937, the part should be placed as close as possible to the power MOSFET that it is controlling. The VEE pin of the MAX5936/ MAX5937 should be placed close to the source pin of the power MOSFET and they should share a wide trace. A common top layer plane would service both the thermal and electrical requirements. The load-probe current must be taken into account. If this current is high, the layout traces and current-limiting resistor must be sized appropriately. Stray inductance must be minimized in the traces of the overall layout of the hot-swap controller, the power MOSFET, and the load capacitor. Starting from the board contacts, all high-current traces should be short, wide, and direct. The potentially high pulse current pins of the MAX5936/MAX5937 are GATE (when pulling GATE low),

Figure 15. MAX5936/MAX5937 Slew Rate vs. C<sub>SLEW</sub>

Figure 16. Adjusting the MAX5936/MAX5937 Slew Rate

load-probe, and VEE. Because of the nature of the hotswap requirement, no decoupling capacitor is recommended for the MAX5936/MAX5937. Because there is no decoupling capacitor, stray inductance can result in excessive ringing at the GND pin during power-up or during very rapid V<sub>IN</sub> steps. This should be examined in every application design since ringing at the GND pin may exceed the absolute maximum supply rating for the part.

MIXXIM

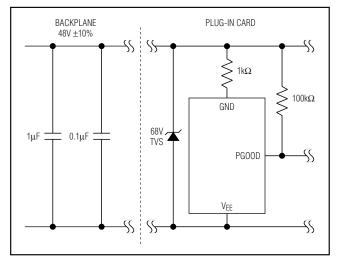

### **Input Transient Protection**

During hot plug-in/unplug and fast V<sub>IN</sub> steps, stray inductance in the power path can cause voltage ringing above the normal input DC value, which may exceed the absolute maximum supply rating. An input transient such as that caused by lightning can also put a severe transient peak voltage on the input rail. The following techniques are recommended to reduce the effect of transients:

- 1) Minimize stray inductance in the power path using wide traces and minimize loop area including the power traces and the return ground path.

- 2) Add a high-frequency (ceramic) bypass capacitor on the backplane as close as possible to the plugin connector (Figure 17).

- 3) Add a  $1k\Omega$  resistor in series with the MAX5936/ MAX5937's GND pin and a  $0.1\mu$ F capacitor from GND to VEE to limit transient current going into this pin.

### Appendix A

#### **GATE Cycles**

The power-up GATE cycle and the step GATE cycle are quite similar but have distinct differences. Understanding these differences may clarify application issues.

#### GATE Cycle During Power-Up

The power-up GATE cycle occurs during the initial power-up of the MAX5936/MAX5937 and the associated power MOSFET and load. The power-up GATE cycle can result in full enhancement or in a fault (all voltages are relative to  $V_{EE}$ ).

#### Power-Up to Full Enhancement:

- At the beginning of the power-up sequence to the start of the power-up GATE cycle, the GATE is held at V<sub>EE</sub>. Following a successful completion of the load-probe test, GATE is held at V<sub>EE</sub> for an additional 350µs and then is allowed to float for 650µs. At this point, the GATE begins to ramp with 52µA charging the gate of the power MOSFET. [GATE turn-on]

- When GATE reaches the gate threshold voltage of the power MOSFET, V<sub>OUT</sub> begins to ramp down toward VEE. [V<sub>OUT</sub> ramp]

- When V<sub>OUT</sub> ramps below 72% V<sub>CB</sub>, the GATE is rapidly pulled to full enhancement and the powerup GATE cycle is complete. 1.26ms after GATE is pulled to full enhancement, PGOOD will assert. [Full enhancement]

Figure 17. Protecting the MAX5936/MAX5937 Input from High-Voltage Transients

#### Power-Up to Fault Management:

- 1) Same as step 1 above. [GATE turn-on]

- 2) Same as step 2 above. [V<sub>OUT</sub> ramp]

- GATE ramps to 90% of full enhancement while VOUT remains above 72% V<sub>CB</sub>, at which point the GATE is rapidly pulled to V<sub>EE</sub> and fault management is initiated. [Fault management]

#### GATE Cycle During VIN Step

A step GATE cycle occurs only after a successful power-up GATE cycle to full enhancement occurs and as a result of a positive  $V_{IN}$  step (all voltages are relative to  $V_{EE}$ ).

#### Step to Full Enhancement:

- A VIN step occurs resulting in STEP\_MON rising above STEPTH before VOUT rises above VSC. [Step detection]

- 2) After a step is detected, VOUT rises above VSC in response to the step. When VOUT rises above VSC, GATE is immediately pulled to VEE, rapidly turning off the power MOSFET. GATE is held at VEE for 350µs to dampen any ringing. Once GATE is pulled to VEE, the gate cycle has begun and STEP\_MON can safely drop below STEPTH and successfully complete a step GATE cycle to full enhancement without initiating fault management. [GATE pulldown]

- Following the 350µs of GATE pulldown, GATE is allowed to float for 650µs. At this point, the GATE

begins to ramp with 52µA charging the gate of the power MOSFET. [GATE turn-on]

- 4) When GATE reaches the gate threshold voltage of the power MOSFET, VOUT begins to ramp down toward the new lower VEE. In the interval where GATE is below the MOSFET threshold, the MOSFET is off and VOUT will droop depending on the RC time constant of the load. [VOUT ramp]

- 5) When V<sub>OUT</sub> ramps below 72% V<sub>CB</sub>, the GATE pulls rapidly to full enhancement and the step GATE cycle is complete. If STEP\_MON remains above STEP<sub>TH</sub> when GATE has ramped to 90% of full enhancement and V<sub>OUT</sub> remains above 72% of V<sub>CB</sub>, GATE remains at 90% and will not be pulled to full enhancement. In this condition, if V<sub>OUT</sub> drops below 72% of V<sub>CB</sub> before STEP\_MON drops below STEP<sub>TH</sub>, GATE is rapidly pulled to full enhancement and the step GATE cycle is complete. PGOOD remains asserted throughout the step GATE cycle. [Full enhancement]

#### Step to Fault Management:

- 1) Same as step 1 above. [Step detection]

- 2) Same as step 2 above. [GATE pulldown]

- 3) Same as step 3 above. [GATE turn-on]

- 4) Same as step 4 above. [VOUT ramp]

- If STEP\_MON is below STEP<sub>TH</sub> when GATE ramps 5) to 90% of full enhancement and VOUT remains above 72% VCB. GATE is rapidly pulled to VEE. Fault management is initiated and PGOOD is deasserted. If STEP\_MON is above STEPTH when GATE ramps to 90% of full enhancement and VOUT remains above 72% of VCB, GATE remains at 90%. It will not be pulled to full enhancement nor will it be pulled to VEE. In this condition, if VOUT drops below 72% of VCB before STEP\_MON drops below STEPTH, GATE is rapidly pulled to full enhancement and a fault is avoided. Conversely, if STEP\_MON drops below STEPTH first, the GATE is rapidly pulled to VEE, fault management is initiated, and PGOOD is deasserted. [Fault management]

It should be emphasized that while STEP\_MON remains above STEP<sub>TH</sub> the current fault management is blocked. During this time it is possible for there to be multiple events involving V<sub>OUT</sub> rising above V<sub>SC</sub> then those falling below 75% V<sub>CB</sub>. In each of these events, when V<sub>OUT</sub> rises above V<sub>SC</sub>, a full GATE cycle is initiated where GATE is first pulled low then allowed to ramp up. Then finally, when V<sub>OUT</sub> conditions are met, it will be fully enhanced.

MAX5936/MAX5937

# -48V Hot-Swap Controllers with VIN Step Immunity and No RSENSE

#### **GATE Output**

GATE is a complex output structure and its condition at any moment is dependent on various timing sequences in response to multiple inputs. A diode to VEE prevents negative excursions. For positive excursions, the states are:

- 1) Power-off with 2V clamp.

- 2) 10 $\Omega$  pulldown to VEE.

- a. Continuous during startup delay and during fault conditions.

- b. Pulsed following detected step or OV condition.

- 3) Floating with 15V clamp. [Prior to GATE ramp]

- 4) 47µA current source with 15V clamp. [GATE ramp]

- 5) Pullup to internal 10V supply with 15V clamp. [Full enhancement]

### Appendix B

#### Step Monitor Component Selection Analysis

As mentioned previously in the Selecting Resistor and Capacitor for Step Monitor section, the AC response from V<sub>IN</sub> to V<sub>OUT</sub> is dependent on the parasitics of the load. This is especially true for the load capacitor in conjunction with the power MOSFET's R<sub>DS(ON)</sub>. The load capacitor (with parasitic ESR and LSR) and the power MOSFET's R<sub>DS(ON)</sub> can be modeled as a heavily damped second-order system. As such, this system functions as a bandpass filter from V<sub>IN</sub> to V<sub>OUT</sub> limiting the ability of V<sub>OUT</sub> to follow the V<sub>IN</sub> ramp. STEP\_MON lags the V<sub>IN</sub> ramp with a first-order RC response, while V<sub>OUT</sub> lags with an overdamped second-order response.

Given a positive  $V_{IN}$  ramp with ramp rate of dV/dt, the approximate response of  $V_{OUT}$  to  $V_{IN}$  is:

$$V_{OUT}(t) = (dV/dt) \times \tau_C \times (1 - e^{(-t/\tau L, eqv)}) + R_{DS(ON)} \times I_{LOAD}$$

(Equation 1)

where  $\tau_{C} = C_{LOAD} \times R_{DS(ON)}$ .

Equation 1 is a simplification for the overdamped second-order response of the load to a ramp input,  $\tau_C = C_{LOAD} \times R_{DS(ON)}$ , and corresponds to the ability of the load capacitor to transfer dV/dt current to the fully enhanced power MOSFET's R<sub>DS(ON)</sub>. The equivalent time constant of the load ( $\tau_{L,eqv}$ ) accounts for the parasitic series inductance and resistance of the capacitor and board interconnect. Determine  $\tau_{L,eqv}$  empirically with a few tests to characterize the load dynamic response to V<sub>IN</sub> ramps.

Similarly, the response of STEP\_MON to a V<sub>IN</sub> ramp is:  $V_{STEP_MON}(t) = (dV/dt) \times \tau_{STEP} \times (1-e^{(-t / \tau_{STEP})})$  $+ 10\mu A \times R_{STEP_MON}$  (Equation 2)

where  $\tau_{STEP} = R_{STEP}MON \times C_{STEP}MON$ .

For proper step detection, VSTEP\_MON must exceed STEPTH prior to VOUT reaching VSC or within 1.4ms of VOUT reaching VCB (or overall VIN ramp rates anticipated in the application). It is impossible to give a fixed set of design guidelines that rigidly apply over the wide array of applications that use the MAX5936/MAX5937. There are, however, limiting conditions and recommendations that should be observed.

One limiting condition that must be observed is to ensure that the STEP\_MON time constant,  $\tau_{STEP}$ , is not so low that at the lowest ramp rate, the anticipated STEPT<sub>H</sub> cannot be obtained. The product (dV/dt) ×  $\tau_{STEP}$  =  $\tau_{STEP_MON,MAX}$ , is the maximum differential voltage at STEP\_MON if the V<sub>IN</sub> ramp were to continue indefinitely. A related condition is setting the STEP\_MON voltage below STEPT<sub>H</sub> with adequate margin,  $\Delta V_{STEP_MON}$ , to accommodate the tolerance of both I<sub>STEP\_OS</sub> (±8%) and RSTEP\_MON. In determining  $\tau_{STEP_MON}$ , use the 9.2µA limit to ensure sufficient margin with worst-case I<sub>STEP</sub> OS.

The margin of V<sub>OUT</sub> (with respect to V<sub>SC</sub> and V<sub>CB</sub>) is set when V<sub>SC</sub> and V<sub>CB</sub> were selected from the three available ranges. This margin may be lower at one of the temperature extremes and if so, that value should be used in the following discussion. These margins will be called  $\Delta V_{CB}$  and  $\Delta V_{SC}$  and they represent the minimum V<sub>OUT</sub> excursion required to trip the respective fault. RSTEP\_MON is typically set to 100k $\Omega$  ±1%. This gives a  $\Delta V_{STEP}$ \_MON of 0.25V, a worst-case low of 0.16V, and a worst-case high of 0.37V. In finding  $\tau_{STEP}$ in the equation below, use  $\Delta V_{STEP}$ \_MON = 0.37V to ensure sufficient margin with worst-case ISTEP\_OS.

To set  $\tau_{STEP}$  to block all VCB and VSC faults for any ramp rate, find the ratio of  $\Delta V_{STEP\_MON}$  to  $\Delta V_{CB}$  and choose  $\tau_{STEP}$  so:

$\tau_{\text{STEP}} = 1.2 \times \tau_{\text{C}} \times \Delta V_{\text{STEP}}$ Mon /  $\Delta V_{\text{CB}}$

and since RSTEP\_MON =  $100k\Omega$ :

$C_{STEP}MON = \tau_{STEP} / R_{STEP}MON = \tau_{STEP} / 100 k\Omega$

After the first-pass component selection, if sufficient timing margin exists, it is possible but not necessary to lower R<sub>STEP</sub> below  $100k\Omega$  to reduce the sensitivity of STEP\_MON to V<sub>IN</sub> noise.

#### Verification of the Step Monitor Timing

It is prudent to verify conclusively that all circuit-breaker and short-circuit faults will be blocked for all ramp rates. To do this, some form of graphical analysis is recommended but first, find the value of  $\tau_{L,eqV}$  of the load by a series of ramp tests as indicated earlier. These tests include evaluating the load with a series of V<sub>IN</sub> ramps of increasing ramp rates and monitoring the rate of V<sub>OUT</sub> rise during the ramp. Each V<sub>IN</sub> ramp should have a constant slope. The V<sub>OUT</sub> response data must be taken only during the positive ramp. Data taken after V<sub>IN</sub> has leveled off at the new higher value must not be used.

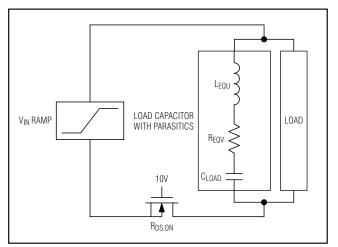

Figure 18 shows the load in parallel with the load capacitor, C<sub>LOAD</sub>, and the parallel connection in series with the power MOSFET, which is fully enhanced with  $V_{GS} = 10V$ . The objective is to determine  $\tau_{L,eqv}$  from the V<sub>OUT</sub> response.

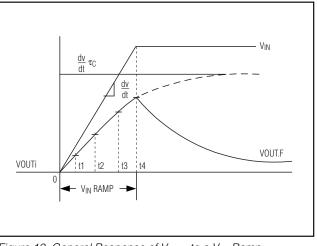

Figure 19 shows the general response of V<sub>OUT</sub> to a V<sub>IN</sub> ramp over time t. Equation 1 gives the response of V<sub>OUT</sub> to a ramp of dV/dt. The product (dV/dt) x  $\tau_{C} = \Delta V_{OUT}$ (max) or the maximum V<sub>OUT</sub> voltage differential if the V<sub>IN</sub> ramp were to continue indefinitely. The parameter of interest is  $\Delta V_{OUT}$  due to the ramp dV/dt, thus it is necessary to subtract the DC shift in V<sub>OUT</sub> due to the load resistance. For some loads, which are relatively independent of supply voltage, this may be insignificant.

#### $V_{OUT}(t) = V_{OUT}(t) - R_{DS(ON)} \times I_{LOAD}$

where  $I_{LOAD}$  is a function of the  $V_{OUT}$  level that should be determined separately with DC tests.

$\Delta V_{OUT}(t) / \left[ (dV/dt) \times \tau_C \right] = (1 - e^{(-t / \tau L, eqv)})$

If  $V_{OUT}(t)$  is measured at time t, then the equivalent time constant of the load is found from:

#### $\tau_{L,eqv} = -t / \ln(1 - \Delta V_{OUT} / [(dV/dt) \times \tau_C])$

As mentioned earlier, several measurements of  $\Delta V_{OUT}$  at times t1, t2, t3, and t4 should be made during the ramp. Each of these may result in slightly different values of  $\tau_{L,eqv}$  and all values should then be averaged. In making the measurements, the V<sub>IN</sub> ramp duration should be such that  $\Delta V_{OUT}$  reaches 2 or 3 times the selected  $\Delta V_{SC}$ . The ramp tests should include three ramp rates:  $\Delta V_{SC} / \tau_C$ , 2 x  $\Delta V_{SC} / \tau_C$  and 4 x  $\Delta V_{SC} / \tau_C$ . The values of  $\tau_{L,eqv}$  may vary over the range of slew rates due to measurement error, nonlinear dynamics in the load, and due to the fact that Equation 1 is a simplification from a higher order dynamic system. The resulting range of  $\tau_{L,eqv}$  values should be used to validate the performance of the final design.

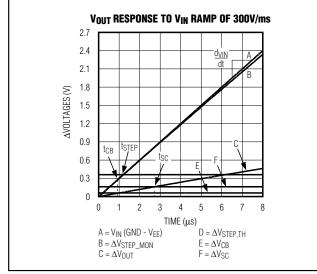

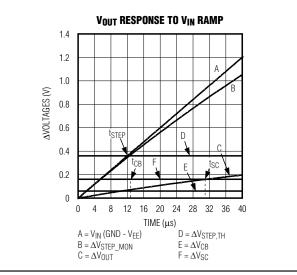

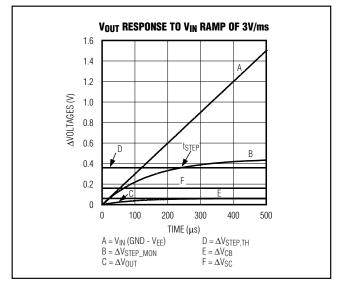

Having  $\tau_C$ ,  $\tau_{L,eqv}$ , RSTEP, and CSTEP in a graphical analysis using Equation 1 and Equation 2 can verify the step monitor function by displaying the relative timing of tCB, tSTEP, and tSC, which are the times when VCB, VSTEP\_MON, and VSC voltage thresholds are exceeded. A simple spreadsheet for this purpose can be supplied by Maxim upon request. Figures 20, 21, and 22 graphically verify a particular solution over 3 decades of VIN ramp rates. In addition, Figure 22 verifies that this solution will block all circuit-breaker and short-circuit faults for even the lowest VIN ramp that will cause VOUT to exceed VCB.

Figure 19. General Response of V<sub>OUT</sub> to a V<sub>IN</sub> Ramp

MAX5936/MAX5937

# -48V Hot-Swap Controllers with VIN Step Immunity and No RSENSE

Figure 20. VOUT Response to VIN Ramp of 300V/ms

### **Chip Information**

TRANSISTOR COUNT: 2320 PROCESS: BICMOS

Figure 21. VOUT Response to VIN Ramp of 30V/ms

Figure 22. VOUT Response to VIN Ramp of 3V/ms

| 3                 |

|-------------------|

| 0                 |

| 5                 |

| ¥.                |

|                   |

| 2                 |

| Σ                 |

| $\mathbf{\Sigma}$ |

| Ø                 |

| 2                 |

| ຼ                 |

| 5                 |

| ×                 |

| đ                 |

|                   |

|                   |

### **Timing Table**

### **Selector Guide**

| NAME                                                    | SYMBOL           | TYPICAL<br>TIME (s) |

|---------------------------------------------------------|------------------|---------------------|

| Power-Up Delay                                          | tondly           | 220m                |

| Load Probe Test Timeout                                 | tLP              | 220m                |

| Load Probe Retry Time                                   | tLP_OFF          | 3.5                 |

| PGOOD (PGOOD) Assertion<br>Delay Time                   | tpgood           | 1.26m               |

| Autoretry Delay                                         | <b>t</b> RETRY   | 3.5                 |

| Circuit-Breaker Glitch Rejection                        | tCB_DLY          | 1.4m                |

| UVLO Glitch Rejection                                   | t <sub>REJ</sub> | 1.5m                |

| GATE Pulldown Pulse Following<br>a V <sub>IN</sub> step | _                | 350µ                |

| GATE Low After a V <sub>IN</sub> Step,<br>Prior to Ramp | _                | 1m                  |

| PART      | CIRCUIT-<br>BREAKER<br>THRESHOLD<br>(mV) | FAULT<br>MANAGEMENT | PGOOD<br>ASSERTION |

|-----------|------------------------------------------|---------------------|--------------------|

| MAX5936LA | 100                                      | Latch               | Low                |

| MAX5936LB | 200                                      | Latch               | Low                |

| MAX5936LC | 400                                      | Latch               | Low                |

| MAX5936LN | No circuit<br>breaker                    | Latch               | Low                |

| MAX5936AA | 100                                      | Autoretry           | Low                |

| MAX5936AB | 200                                      | Autoretry           | Low                |

| MAX5936AC | 400                                      | Autoretry           | Low                |

| MAX5937LA | 100                                      | Latch               | High               |

| MAX5937LB | 200                                      | Latch               | High               |

| MAX5937LC | 400                                      | Latch               | High               |

| MAX5937LN | No circuit<br>breaker                    | Latch               | High               |

| MAX5937AA | 100                                      | Autoretry           | High               |

| MAX5937AB | 200                                      | Autoretry           | High               |

| MAX5937AC | 400                                      | Autoretry           | High               |

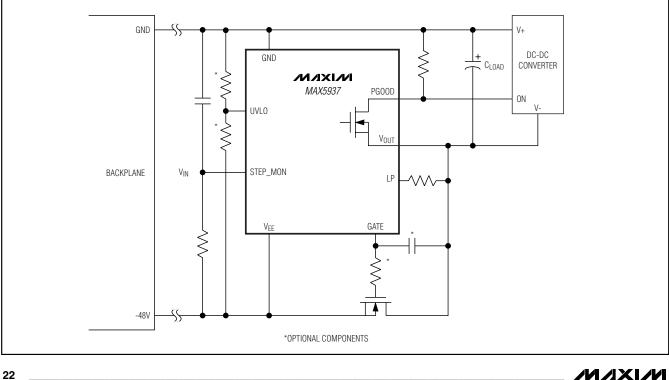

### **Typical Operating Circuit**

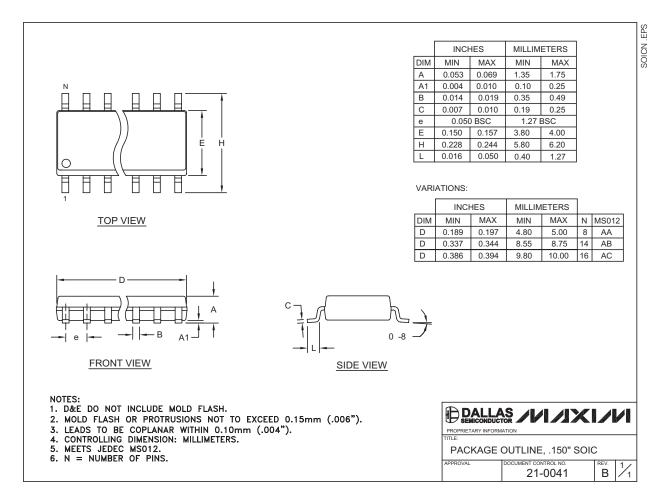

### \_Package Information

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to **www.maxim-ic.com/packages**.)

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

#### Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600 \_

© 2005 Maxim Integrated Products Printed USA MAXIM is a registered trademark of Maxim Integrated Products, Inc.