### 4V to 72V Input LDOs with Boost Preregulator

#### **General Description**

The MAX5092A/MAX5092B/MAX5093A/MAX5093B lowquiescent-current, low-dropout (LDO) regulators contain simple boost preregulators operating at a high frequency. The devices seamlessly provide a preset 3.3V (MAX5092A/MAX5093A) or 5V (MAX5092B/MAX5093B) LDO output voltage from a cold-crank through load-dump (3.5V to 80V) input voltage conditions. The MAX5092\_/ MAX5093\_ deliver up to 250mA with excellent load and line regulation. During normal operation, when the battery is healthy, the boost preregulator is completely turned off, reducing quiescent current to 65µA (typ). This makes the devices suitable for always-on power supplies.

The buck-boost operation achieved by this combination of LDO and boost preregulator offers the advantage of using a single off-the-shelf inductor in place of the multiplewinding custom magnetics needed in typical single-ended primary inductor converter (SEPIC) and transformerbased flyback topologies. The high operating frequency of the boost regulator significantly reduces component size. The MAX5092\_ integrates a blocking diode to further reduce the external component count. The boost preregulator output voltage is preset to 7V. Both LDO and boost output voltages are programmable using external resistors. The boost preregulator output voltage is adjustable up to 11V(MAX5092\_), or up to 12V (MAX5093\_). The LDO output voltage is adjustable from 1.5V to 9V (MAX5092\_) or from 1.5V to 10V (MAX5093\_).

The devices feature a shutdown mode with  $5\mu$ A (typ) shutdown current, a HOLD input to implement a self-holding circuit, and a power-on-reset output (RESET) with an externally programmable timeout period. Additional features include output overload, short-circuit, and thermal protection.

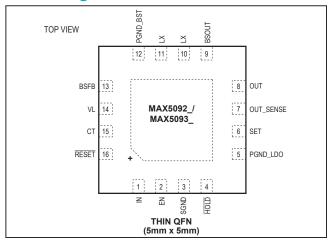

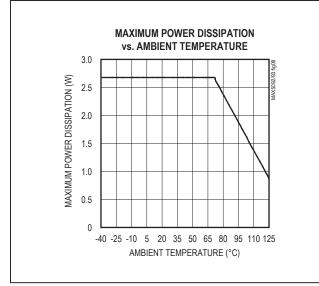

The MAX5092\_/MAX5093\_ are available in a thermally enhanced, 16-pin 5mm x 5mm thin QFN package and can dissipate up to 2.7W at  $+70^{\circ}$ C on a multilayer PC board (PCB).

#### **Applications**

Industrial

# Typical Operating Circuit and Selector Guide appear at end of data sheet.

#### **Features**

- Wide Operating Input Voltage Range: 3.5V to 72V with a 4V Startup Voltage

- LDO Output Regulates to 5V Seamlessly from an Input Voltage of 3.5V to 72V

- Up to 250mA Output Current

- Preset 3.3V, 5V, or Externally Programmable LDO Output Voltage from 1.5V to 9V (MAX5092\_) or from 1.5V to 10V (MAX5093\_)

- Preset 7V or Externally Programmable Boost Output Voltage Up to 11V (MAX5092\_) or Up to 12V (MAX5093\_)

- 65µA Quiescent Current in LDO Mode (V<sub>IN</sub> ≥ 8V) 5µA Shutdown Current

- Power-On Reset (RESET) with Programmable Timeout Period

- Output Short-Circuit and Thermal Protection

- TQFN Package Capable of Dissipating Up to 2.7W at +70°C

### **Ordering Information**

| PART         | TEMP RANGE      | PIN-PACKAGE |

|--------------|-----------------|-------------|

| MAX5092AATE+ | -40°C to +125°C | 16 TQFN-EP* |

| MAX5092BATE+ | -40°C to +125°C | 16 TQFN-EP* |

| MAX5093AATE+ | -40°C to +125°C | 16 TQFN-EP* |

| MAX5093BATE+ | -40°C to +125°C | 16 TQFN-EP* |

+Denotes a lead(Pb)-free/RoHS-compliant package. \*EP = Exposed pad.

### **Pin Configuration**

## 4V to 72V Input LDOs with Boost Preregulator

### **Absolute Maximum Ratings**

| IN, EN, LX, BSOUT to SGND               | -0.3V to +80V                     |

|-----------------------------------------|-----------------------------------|

| PGND_BST, PGND_LDO to SGND              | 0.3V to +0.3V                     |

| RESET, OUT, OUT_SENSE to SGND           | 0.3V to +12V                      |

| BSOUT to LX (MAX5092_)                  | 0.3V to +12V                      |

| VL, SET, BSFB, SGND                     | 0.3V to +6V                       |

| HOLD to SGND                            | 0.3V to (V <sub>OUT</sub> + 0.3V) |

| CT to SGND                              |                                   |

| OUT Current (IOUT) Short Circuit to PGI | ND_LDO,                           |

| (V <sub>IN</sub> ≤ 28V)                 |                                   |

| RESET Sinking Current                                 | 5mA             |

|-------------------------------------------------------|-----------------|

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |                 |

| Thin QFN (derate 33.3mW/°C                            |                 |

| above +70°C)                                          | 2666mW (Note 1) |

| Operating Temperature Range                           | 40°C to +125°C  |

| Maximum Junction Temperature                          | +150°C          |

| Storage Temperature Range                             | 60°C to +150°C  |

| Lead Temperature (soldering, 10s)                     | +300°C          |

Note 1: As per JEDEC Standard 51 (Multilayer Board).

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **Electrical Characteristics**

$(V_{IN} = V_{EN} = 14V, I_{OUT} = 1mA, C_{IN} = 47\mu$ F,  $C_{BSOUT} = 22\mu$ F,  $C_{OUT} = 10\mu$ F,  $C_{VL} = 1\mu$ F,  $T_A = T_J = -40^{\circ}$ C to +125°C, unless otherwise noted. See Figures 4–7 as applicable. Typical specifications are at  $T_A = +25^{\circ}$ C.) (Note 2)

| PARAMETER                                 | SYMBOL               | СО                                      | NDITIONS                                     | MIN  | TYP  | MAX  | UNITS |

|-------------------------------------------|----------------------|-----------------------------------------|----------------------------------------------|------|------|------|-------|

| INPUT SUPPLY                              |                      |                                         |                                              |      |      |      |       |

| Input Voltage Range                       | V <sub>IN</sub>      | (Note 3)                                |                                              | 4    |      | 72   | V     |

| Internal Input Undervoltage               | V <sub>UVLOF</sub>   | V <sub>IN</sub> falling                 |                                              | 3.0  | 3.2  | 3.4  | v     |

| Lockout                                   | VUVLOR               | V <sub>IN</sub> rising                  |                                              | 3.4  | 3.6  | 3.8  |       |

| Supply Current (Boost Converter           | IQ                   | LDO mode,<br>I <sub>OUT</sub> = 100µA   | T <sub>J</sub> = -40°C to +125°C<br>(Note 4) |      | 65   | 85   | μA    |

| Off)                                      |                      | LDO mode, I <sub>OUT</sub>              | = 250mA                                      |      | 70   | 100  |       |

| Supply Current (Boost Converter On)       | ١ <sub>S</sub>       | V <sub>IN</sub> = 5V                    |                                              |      | 0.4  | 1.0  | mA    |

| Shutdown Supply Current                   | I <sub>SHDN</sub>    | V <sub>EN</sub> ≤ +0.4V                 | T <sub>J</sub> = -40°C to +125°C<br>(Note 4) |      | 6    | 10   | μA    |

| BOOST CONVERTER                           |                      |                                         | ·                                            |      |      |      |       |

| Minimum BSOUT Output Current              | IBSOUT               | $V_{IN} = 4V$                           |                                              |      | 250  |      | mA    |

| Boost Converter Enable<br>Threshold       | V <sub>BST_EN</sub>  | V <sub>BSOUT</sub> – V <sub>OUT</sub> f | alling (Note 5)                              | 1.7  | 2.0  | 2.3  | V     |

| Boost Converter Disable<br>Threshold      | V <sub>BST_DIS</sub> | V <sub>BSOUT</sub> – V <sub>OUT</sub> r | ising (Note 5)                               | 2.2  | 2.5  | 2.8  | V     |

| Boost Converter Disable<br>Hysteresis     | V <sub>BST_HYS</sub> |                                         |                                              |      | 0.5  |      | V     |

| BSOUT Output Voltage                      | V <sub>BSOUT</sub>   | V <sub>IN</sub> = 4V, BSFB =            | SGND, V <sub>OUT</sub> = 5V                  |      | 7.00 |      | V     |

|                                           |                      | MAX5092_<br>MAX5093_                    |                                              |      | 11   |      |       |

| Maximum BSOUT Output Voltage              | VBSOUT(MAX)          |                                         |                                              | 12   |      |      |       |

| BSFB Regulation Voltage                   | V <sub>BSFB</sub>    |                                         |                                              | 1.18 | 1.24 | 1.30 | V     |

| BSFB Input Bias Current                   | I <sub>BSFB</sub>    |                                         |                                              |      |      | 100  | nA    |

| Boost Internal Switch<br>On-Resistance    | R <sub>DS(ON)</sub>  |                                         |                                              |      | 0.5  | 1.2  | Ω     |

| Boost Internal Switch Minimum<br>Off-Time | tOFF                 |                                         |                                              | 0.80 | 1    | 1.25 | μs    |

## 4V to 72V Input LDOs with Boost Preregulator

### **Electrical Characteristics (continued)**

$(V_{IN} = V_{EN} = 14V, I_{OUT} = 1mA, C_{IN} = 47\mu$ F,  $C_{BSOUT} = 22\mu$ F,  $C_{OUT} = 10\mu$ F,  $C_{VL} = 1\mu$ F,  $T_A = T_J = -40^{\circ}$ C to +125°C, unless otherwise noted. See Figures 4–7 as applicable. Typical specifications are at  $T_A = +25^{\circ}$ C.) (Note 2)

| PARAMETER                                | SYMBOL                                   | 0                                                                                       | CONDITIONS                                                                                  | MIN   | TYP   | MAX   | UNITS |

|------------------------------------------|------------------------------------------|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-------|-------|-------|-------|

| Boost Internal Switch Maximum<br>On-Time | t <sub>ON-max</sub>                      |                                                                                         |                                                                                             | 1.80  | 2.25  | 2.70  | μs    |

| Internal Switch Current Limit            | I <sub>LIM</sub>                         | Measured in st                                                                          | eady-state condition                                                                        | 1.5   |       | 3.0   | Α     |

| Boost Turn-On Response Time              |                                          | Time from V <sub>BS</sub><br>to switch on-tim                                           | <sub>OU</sub> T falling below regulation<br>ne                                              |       | 2     | 5     | μs    |

| Internal Diode Forward Voltage<br>Drop   | V <sub>F</sub>                           | MAX5092_only                                                                            | y, I <sub>F</sub> = 1A                                                                      |       | 0.95  |       | V     |

| LDO                                      |                                          |                                                                                         |                                                                                             |       |       |       |       |

| Guaranteed Output Current                | I <sub>OUT</sub>                         | V <sub>BSOUT</sub> - V <sub>OU</sub>                                                    | T = 2V (Note 6)                                                                             | 250   |       |       | mA    |

|                                          |                                          | SET = SGND,                                                                             | I <sub>OUT</sub> = 1mA                                                                      | 3.25  | 3.3   | 3.35  |       |

|                                          |                                          | MAX5092A/<br>MAX5093A                                                                   | 100µA ≤ I <sub>OUT</sub> ≤ 250mA                                                            | 3.2   | 3.3   | 3.4   |       |

| Output Voltage                           | V <sub>OUT</sub>                         | SET = SGND,<br>MAX5092B/                                                                | I <sub>OUT</sub> = 1mA                                                                      | 4.900 | 5     | 5.075 | V     |

|                                          |                                          | MAX5092B/<br>MAX5093B                                                                   | 100µA ≤ I <sub>OUT</sub> ≤ 250mA                                                            | 4.85  | 5     | 5.10  |       |

| Minimum Adjustable Output<br>Voltage     | V <sub>ADJMIN</sub>                      | Boost operation                                                                         | n, V <sub>IN</sub> = 4V, V <sub>BSOUT</sub> = 7V                                            |       | 1.5   |       | V     |

| Maximum Adjustable Output                | Vadjmax                                  | Boost<br>operation, V <sub>IN</sub><br>= 4V                                             | MAX5092_,<br>V <sub>BSOUT</sub> = 11V                                                       |       | 9     |       | - V   |

| Voltage                                  |                                          |                                                                                         | MAX5093_,<br>V <sub>BSOUT</sub> = 12V                                                       |       | 10    |       |       |

| Adjustable Output Voltage                | V <sub>ADJ</sub>                         | LDO operation, $V_{IN} \ge V_{BST_DIS}$<br>(boost converter off) (Note $\overline{7}$ ) |                                                                                             | 1.5   |       | 10.0  | V     |

| Dropout Voltage                          | ΔV <sub>DO</sub>                         | I <sub>OUT</sub> = 250mA (Note 8)                                                       |                                                                                             |       | 0.9   | 1.6   | V     |

| LDO Startup Response Time                |                                          |                                                                                         | Rising edge of $V_{BSOUT}$ to the rising edge of $V_{OUT}$ , $R_L = 500\Omega$ , SET = SGND |       | 200   |       | μs    |

|                                          |                                          | $7V \le V_{IN} \le$                                                                     | MAX5092A/MAX5093A                                                                           |       |       | 0.4   |       |

| Line Regulation                          | ΔV <sub>OUT</sub> /<br>ΔV <sub>IN</sub>  | 72V,                                                                                    | MAX5092B/MAX5093B                                                                           |       |       | 0.5   | mV/V  |

|                                          |                                          | $7V \le V_{IN} \le 28V, I_{LOAD} = 250 \text{mA}$                                       |                                                                                             |       | 1.6   |       |       |

| SET Reference Voltage                    | V <sub>SET</sub>                         |                                                                                         |                                                                                             | 1.205 | 1.235 | 1.265 | V     |

| SET Input Bias Current                   | I <sub>SET</sub>                         |                                                                                         |                                                                                             |       | 0.5   | 100   | nA    |

| Load Regulation                          | ΔV <sub>OUT</sub> /<br>ΔΙ <sub>ΟUT</sub> | I <sub>OUT</sub> = 1mA to                                                               | 250mA                                                                                       |       | 0.2   | 0.6   | mV/mA |

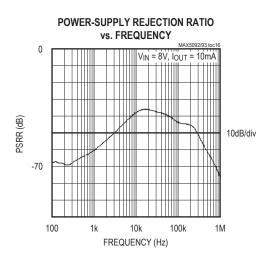

| Power-Supply Rejection Ratio             | ion Ratio PSRR —                         | f = 100Hz                                                                               | $I_{OUT} = 10mA,$<br>$V_{BSOUT(AC)} = 500mV_{P-P},$<br>$V_{OUT} = 5V$                       |       | 80    |       | 40    |

|                                          |                                          | f = 1MHz                                                                                | $I_{OUT} = 10mA,$<br>$V_{BSOUT(AC)} = 500mV_{P-P},$<br>$V_{OUT} = 5V$                       |       | 60    |       | dB    |

| Short-Circuit Current                    | I <sub>SC</sub>                          |                                                                                         |                                                                                             | 255   | 490   |       | mA    |

### 4V to 72V Input LDOs with Boost Preregulator

### **Electrical Characteristics (continued)**

$(V_{IN} = V_{EN} = 14V, I_{OUT} = 1mA, C_{IN} = 47\mu$ F,  $C_{BSOUT} = 22\mu$ F,  $C_{OUT} = 10\mu$ F,  $C_{VL} = 1\mu$ F,  $T_A = T_J = -40^{\circ}$ C to +125°C, unless otherwise noted. See Figures 4–7 as applicable. Typical specifications are at  $T_A = +25^{\circ}$ C.) (Note 2)

| PARAMETER                                  | SYMBOL                | CONDITIONS                                       | MIN                    | TYP  | MAX   | UNITS |

|--------------------------------------------|-----------------------|--------------------------------------------------|------------------------|------|-------|-------|

| ENABLE, HOLD and RESET                     |                       |                                                  |                        |      |       |       |

| EN High Input Threshold                    | ENH                   |                                                  | 2.4                    |      |       | V     |

| EN Low Input Threshold                     | ENL                   |                                                  |                        |      | 0.4   | V     |

| EN Input Bias Current                      | I <sub>EN</sub>       |                                                  |                        | 0.25 | 2     | μA    |

| HOLD Low Input Threshold                   | V <sub>IL</sub>       | Regulator on, EN transition from high to low     |                        |      | 0.4   | V     |

| HOLD Release Voltage                       | V <sub>IH</sub>       | EN = low                                         | V <sub>OUT</sub> - 0.4 |      |       | V     |

| HOLD Pullup Current                        | I <sub>HOLD</sub>     | Internally connected to OUT                      |                        | 4    |       | μA    |

| RESET Voltage Threshold                    | V <sub>RESET</sub>    | % of V <sub>OUT</sub> , V <sub>OUT</sub> falling | 87                     | 90   | 92    | %     |

| RESET Threshold Hysteresis                 | V <sub>RHYST</sub>    | % of V <sub>OUT</sub>                            |                        | 2    |       | %     |

| RESET Output Low Voltage                   | V <sub>RL</sub>       | I <sub>SINK</sub> = 1mA                          |                        |      | 0.4   | V     |

| RESET Output High Leakage<br>Current       | I <sub>RH</sub>       | V <sub>RESET</sub> = 5V                          |                        |      | 1     | μA    |

| RESET Output Minimum Timeout<br>Period     |                       | C <sub>CT</sub> not connected                    |                        | 25   |       | μs    |

| EN to RESET Minimum Timeout Delay          |                       | C <sub>CT</sub> not connected                    |                        | 260  |       | μs    |

| Delay Comparator Threshold (Rising)        | V <sub>CTTH</sub>     |                                                  | 1.205                  | 1.24 | 1.265 | V     |

| Delay Comparator Threshold<br>Hysteresis   | V <sub>CTTH-HYS</sub> |                                                  |                        | 100  |       | mV    |

| CT Charge Current                          | I <sub>CT-CHG</sub>   |                                                  | 1.5                    | 2    | 2.5   | μA    |

| CT Discharge Current                       | I <sub>CT-DIS</sub>   |                                                  |                        | 5    |       | mA    |

| Thermal Shutdown Temperature<br>Threshold  | T <sub>J(SHDN)</sub>  | Temperature rising                               |                        | +165 |       | °C    |

| Thermal Shutdown Temperature<br>Hysteresis | T <sub>J(HYST)</sub>  |                                                  |                        | 20   |       | °C    |

Note 2: Limits at -40°C are guaranteed by design and characterization; not production tested.

Note 3: Guaranteed minimum operating voltage is 3.5V on VIN falling only.

Note 4: Guaranteed by design and not production tested.

Note 5: The boost converter disable threshold (V<sub>BST\_DIS</sub>) is a static measurement. Internal comparator delay may cause a higher disable level.

**Note 6:** The continuous maximum output current from the LDO is guaranteed according to the maximum power dissipation imposed by the package thermal constraints.

**Note 7:** Maximum output adjustable value is conditioned by the maximum adjustable BSOUT Output Voltage Range minus the maximum dropout across the pass transistor.

Note 8: Dropout voltage is defined as (V<sub>BSOUT</sub> - V<sub>OUT</sub>) when V<sub>OUT</sub> is 2% below the value of V<sub>OUT</sub> for V<sub>BSOUT</sub> = V<sub>OUT</sub> + 2V.

### 4V to 72V Input LDOs with Boost Preregulator

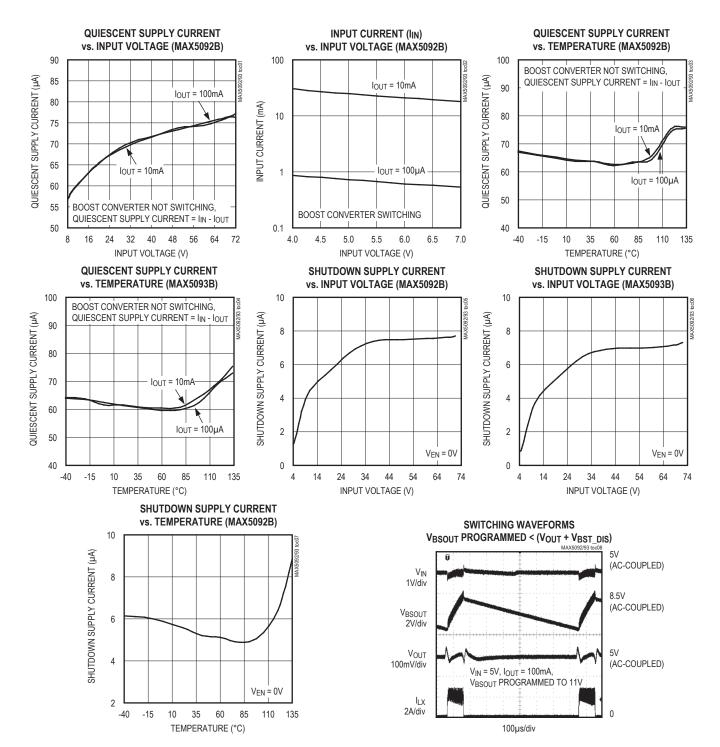

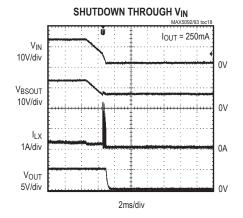

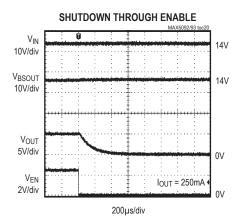

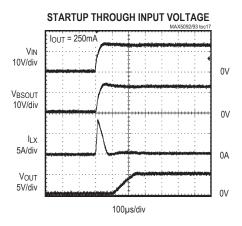

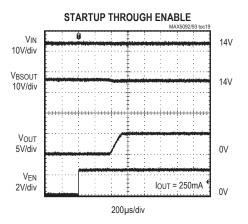

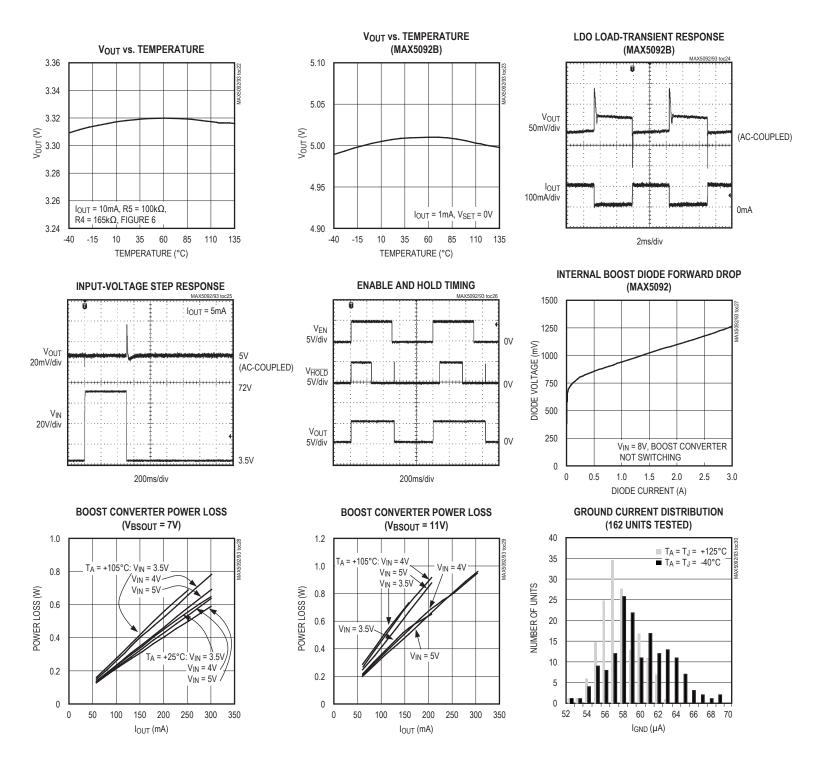

#### **Typical Operating Characteristics**

### 4V to 72V Input LDOs with Boost Preregulator

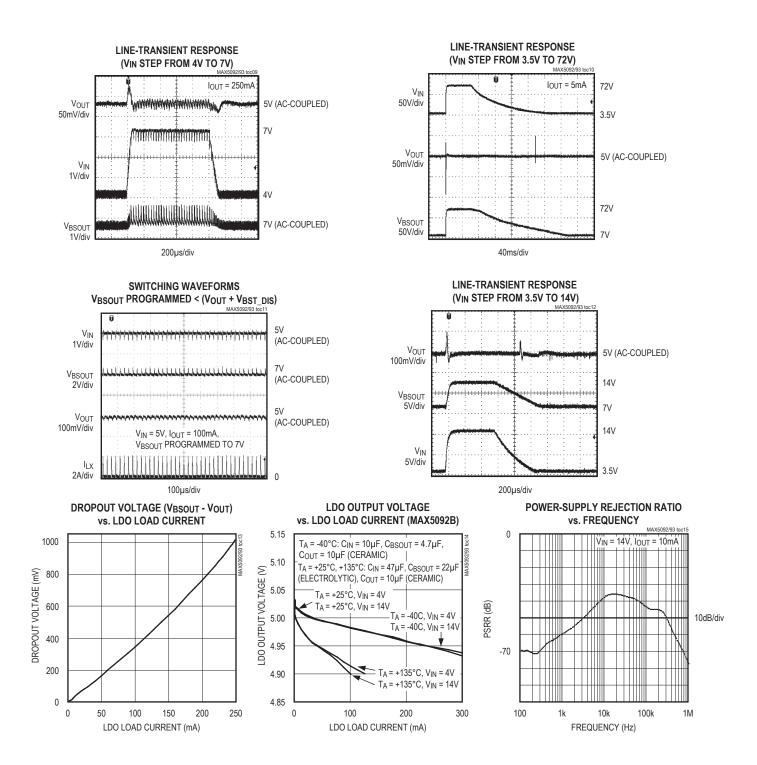

#### **Typical Operating Characteristics (continued)**

## 4V to 72V Input LDOs with Boost Preregulator

### **Typical Operating Characteristics (continued)**

### 4V to 72V Input LDOs with Boost Preregulator

### **Typical Operating Characteristics (continued)**

# 4V to 72V Input LDOs with Boost Preregulator

## **Pin Description**

| PIN    | NAME      | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | IN        | Input Supply Voltage. Bypass IN to the power ground plane with a 47 $\mu$ F (low-ESR) aluminum electrolytic capacitor in parallel with a 1 $\mu$ F ceramic capacitor placed as close to the IC as possible.                                                                                                                                                                                                                                                                                                                                                                              |

| 2      | EN        | Enable Input. Drive EN high to turn on the IC. Drive EN low to disable the IC. Connect EN directly to IN for always-on operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3      | SGND      | Signal Ground. Connect SGND to the signal ground plane and the exposed paddle. Connect the power ground and signal ground plane together at the negative terminal of the input capacitor(s).                                                                                                                                                                                                                                                                                                                                                                                             |

| 4      | HOLD      | Output Hold. When $\overline{\text{HOLD}}$ is forced low, the regulator stores the on-state of the output, allowing the regulator to remain enabled even if EN is pulled low. To shut down the regulator, release $\overline{\text{HOLD}}$ after EN is pulled low. If $\overline{\text{HOLD}}$ is unused, either connect $\overline{\text{HOLD}}$ to OUT or leave unconnected. $\overline{\text{HOLD}}$ is internally connected to OUT through a 4µA pullup current.                                                                                                                     |

| 5      | PGND_LDO  | LDO Power Ground. Connect PGND_LDO to the power ground plane. Connect the PGND_LDO ground and signal ground plane together.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 6      | SET       | Feedback Input for the LDO. Connect SET directly to SGND to set the output voltage of the LDO to the preset voltage of 3.3V (MAX5092A/MAX5093A) or 5V (MAX5092B/MAX5093B). Connect SET to the center tap of a resistor-divider connected between the LDO output and SGND to set the output voltage. $V_{SET}$ regulates to 1.24V when using an adjustable output.                                                                                                                                                                                                                        |

| 7      | OUT_SENSE | LDO Regulator Output Sense. Connect OUT_SENSE to OUT at the output capacitor near the load.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 8      | OUT       | LDO Regulator Output. Bypass OUT to the power ground plane with a 10 $\mu$ F ceramic capacitor. V <sub>OUT</sub> regulates to a preset voltage of 3.3V (MAX5092A/MAX5093A) or 5V (MAX5092B/MAX5093B), or is adjustable from 1.5V to 9V (MAX5902_) or 1.5V to 10V (MAX5093_).                                                                                                                                                                                                                                                                                                             |

| 9      | BSOUT     | Boost Regulator Output Voltage. Bypass BSOUT to the PGND_BST ground plane with a 22µF (low-ESR) aluminum electrolytic capacitor in parallel with a 1µF ceramic capacitor placed as close to the IC as possible. Connect BSFB directly to SGND to regulate the BOOST output to a fixed voltage of 7V for $V_{IN} \leq 7V$ . $V_{BSOUT}$ follows $V_{IN}$ for $V_{BSOUT} - V_{OUT} > 2.5V$ (typ). $V_{BSOUT}$ is programmable up to 11V (MAX5092_) or 12V (MAX5093_) by connecting BSFB to the center tap of an external resistor-divider connected between the BOOST output and PGND_BST. |

| 10, 11 | LX        | Inductor Connection to the Drain of the Internal Power MOSFET. Connect LX to the switched side of the inductor. Connect pins 10 and 11 together as close to the device as possible. For the MAX5093, also connect LX to the anode of the external Schottky diode.                                                                                                                                                                                                                                                                                                                        |

| 12     | PGND_BST  | Boost Regulator Power Ground. Connect PGND_BST to the power ground plane. Connect the PGND_BST ground plane and the signal ground plane together at the negative terminal of the input capacitor(s).                                                                                                                                                                                                                                                                                                                                                                                     |

| 13     | BSFB      | Feedback Input for the Boost Regulator. Connect BSFB directly to SGND to set the boost regulator output voltage to 7V. Connect BSFB to the center tap of an external resistor-divider connected between BSOUT and SGND to set the output voltage. $V_{BSFB}$ regulates to 1.24V when using an adjustable output.                                                                                                                                                                                                                                                                         |

| 14     | VL        | Internal Regulator Output for IC Supply. Bypass VL to SGND with a 1 $\mu$ F/6.3V ceramic capacitor placed as close to the IC as possible. V <sub>VL</sub> regulates to 5.5V with V <sub>BSOUT</sub> $\geq$ 5.5V.                                                                                                                                                                                                                                                                                                                                                                         |

| 15     | СТ        | RESET Timeout Programming Input. Connect a capacitor from CT to SGND to set the RESET timeout period. See the <i>CT Capacitor Selection</i> section.                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 16     | RESET     | $\begin{tabular}{l} \hline \hline RESET & Output. \hline RESET & is an open-drain output that goes high impedance when V_{OUT} exceeds 92\% of the output voltage threshold after a programmed time delay. \hline RESET pulls low immediately once V_{OUT} drops below 90\% of the regulated LDO output voltage. \\ \hline \hline \end{tabular}$                                                                                                                                                                                                                                         |

|        | EP        | Exposed Paddle. Connect to the signal ground plane (SGND). Connect to a large-signal ground plane for increased thermal performance.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

# 4V to 72V Input LDOs with Boost Preregulator

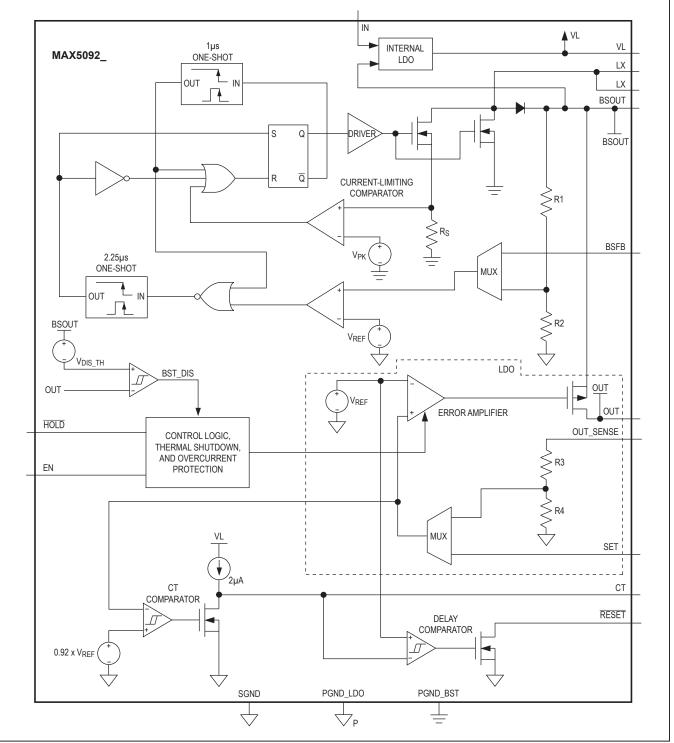

## **Functional Diagrams**

Figure 1. MAX5092\_ Functional Diagram

# 4V to 72V Input LDOs with Boost Preregulator

## **Functional Diagrams (continued)**

Figure 2. MAX5093\_ Functional Diagram

## 4V to 72V Input LDOs with Boost Preregulator

### **Detailed Description**

The MAX5092A/MAX5092B/MAX5093A/MAX5093B include a step-up, switch-mode DC-DC converter and a linear regulator to provide step-up/-down voltage conversion over a wide range of input voltages. This combination of an LDO and a boost converter offers the advantage of using a single off-the-shelf inductor in place of the multiple-winding custom magnetics needed in typical SEPIC or transformer-based flyback topologies. The boost preregulator is completely turned off during normal operation (V<sub>IN</sub> = 14V), reduces quiescent current to  $65\mu$ A (typ), and makes the devices suitable for always-on power supplies.

The devices have an internal UVLO threshold of 3.8V (max, V<sub>IN</sub> rising) that must be exceeded before the device is enabled. When V<sub>IN</sub> is above V<sub>UVLO</sub>, the internal boost converter starts switching and regulates V<sub>BSOUT</sub> to the programmed boost output voltage. The low quiescent-current LDO steps down V<sub>BSOUT</sub> to the programmed LDO output voltage. The LDO output is preset to 3.3V (MAX5092A/MAX5093A) or 5V (MAX5092B/MAX5093B). Both output voltages can be adjusted by using external resistor-dividers.

If (V<sub>BSOUT</sub> - V<sub>OUT</sub>) rises above 2.5V (typ), the boost converter is disabled, forcing V<sub>BSOUT</sub> to follow V<sub>IN</sub>. If V<sub>BSOUT</sub> - V<sub>OUT</sub> falls below 2V (typ), the boost converter starts switching and regulates V<sub>BSOUT</sub> to the programmed voltage. The boost converter regulates V<sub>BSOUT</sub> for V<sub>IN</sub> down to 3.5V, providing uninterrupted operation during low cold-crank voltages even if the programmed LDO output voltage is greater than V<sub>IN</sub> (but less than 9V). The boost converter turn-on response time is less than 10µs, making cold-crank input glitches transparent to the system even at full load.

The boost-converter output is followed by a high PSRR, low-quiescent-current LDO. The LDO rejects the switching noise present at BSOUT and provides a clean, regulated output voltage. The linear regulator uses an internal p-channel MOSFET pass element. Additional features include a power-on-reset function with an externally adjustable timeout, an enable (EN) input, and a hold (HOLD) regulator control input.

#### **Boost Converter**

The switch-mode converter uses a minimum off-time, maximum on-time pulse frequency modulation (PFM) control scheme. The internal MOSFET turns on whenever  $V_{BSOUT}$  falls below the regulation point determined by  $V_{BSFB}$  (see the *Setting the Boost Output Voltage* ( $V_{BSOUT}$ ) section). The MOSFET turns off when the

inductor current reaches the peak current limit (2.5A typ) or after 2.25 $\mu$ s maximum on-time, whichever occurs first. The MOSFET is held off for at least 1 $\mu$ s after the turn-on phase. A new switching cycle initiates once V<sub>BSOUT</sub> falls below the threshold. In this control scheme, switching frequency and output ripple are functions of load current and input voltage. No frequency compensation is needed in the PFM control scheme.

The output of the boost converter is preset to 7V and is adjustable by using external resistors. See the Setting the Boost Output Voltage  $V_{BSOUT}$  section.

If V<sub>BSOUT</sub> is programmed greater than (V<sub>OUT</sub> + V<sub>BST</sub> <sub>DIS</sub>), larger ripple is observed on BSOUT. The reason is as V<sub>BSOUT</sub> rises above V<sub>OUT</sub> + V<sub>BST</sub> <sub>DIS</sub>, the boost converter is disabled, causing V<sub>BSOUT</sub> to fall. As V<sub>BSOUT</sub> falls to V<sub>OUT</sub> + V<sub>BST</sub> <sub>EN</sub>, the boost converter turns back on, and V<sub>BSOUT</sub> rises. For the lowest V<sub>BSOUT</sub> ripple, program V<sub>BSOUT</sub> within the boost disable threshold. See the *Typical Operating Characteristics* for the Switching Waveforms.

Due to the integrated blocking diode in the MAX5092\_,  $V_{BSOUT}$  is limited to 11V. Use the MAX5093\_ for higher boost output voltages (or to reduce the power dissipation in to the package). The MAX5093\_ requires an external diode for the boost converter. Select the external diode according to the *Schottky Diode Selection (MAX5093\_)* section.

#### **Linear Regulator**

The MAX5092\_/MAX5093\_ contain an internal p-channel MOSFET used as the pass transistor for the LDO. The output of the boost regulator is connected to the source of the p-MOSFET. The LDO starts up 200 $\mu$ s after the boost regulator starts up. The LDO supplies up to 250mA with a typical dropout voltage of 0.9V. The maximum LDO output current is determined by the package power-dissipation limit as well as the internal current limit. The LDO is designed to be a low-quiescent-current type. During normal operation when the battery voltage is > 9V, the MAX5092\_/MAX5093\_ consume only 75 $\mu$ A (max) at +85°C and 100 $\mu$ A load.

The output voltage of the LDO is set using the SET input. Connect SET to SGND to use the factory-preset output voltage. Connect SET to the center of an external resistor-divider connected from OUT to SGND to program a different output voltage. See the *Setting the LDO Output Voltage* ( $V_{OUT}$ ) section.

#### Internal Regulator (VL)

An internal regulator (VL) is used to supply all internal low-voltage blocks. Bypass VL to SGND with a 1µF ceramic capacitor placed as close to the IC as possible. V<sub>VL</sub> regulates to 5.5V when V<sub>BSOUT</sub> is above 5.5V. V<sub>VL</sub> tracks the voltage at BSOUT when V<sub>BSOUT</sub> is below 5.5V.

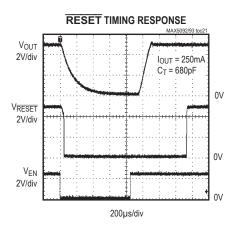

#### Power-On-Reset Output (RESET)

The MAX5092\_/MAX5093\_ contain an open-drain output (RESET) that indicates when the LDO output (V<sub>OUT</sub>) is out of regulation. If the output of the LDO falls below 90% of the nominal output voltage, RESET pulls low after a short delay. Once the output rises above 92% of the nominal output voltage, RESET goes high impedance after the programmed reset timeout period. Connect a 100k $\Omega$  pullup resistor from OUT to RESET. See the *CT Capacitor Selection* section for details on setting the RESET timeout period.

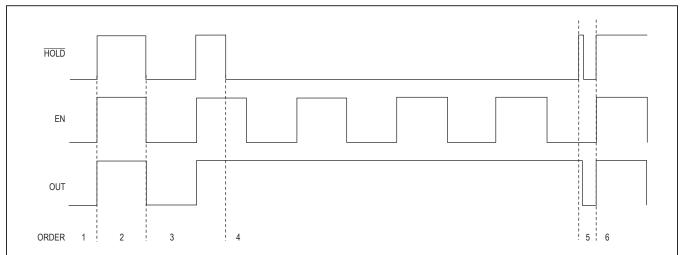

#### **Enable and Hold Inputs**

The MAX5092\_/MAX5093\_ utilize two logic inputs, EN (active-high) and HOLD (active low), to implement a selfholding circuit with no additional components. For example, an ignition switch drives EN high and the regulator turns on. If HOLD is then driven low, the regulator remains on even if EN goes low. As long as HOLD is forced low and remains low after initial regulator power-up, the regulator remains on. From this state, release HOLD (an internal current source connects HOLD to OUT), or connect HOLD to OUT to turn the regulator off. Drive EN low and HOLD high to place the IC into shutdown mode. Shutdown mode reduces supply current to 5µA. Figure 3 shows the timing diagram for the enable and hold functions. Table 1 shows the state of the regulator output with respect to the voltage level at EN and HOLD with reference to Figure 3. Connect HOLD to OUT or leave unconnected to disable the hold feature and use EN as a standard on/off control input.

Figure 3. Enable and Hold Timing Diagram

### Table 1. Truth Table for Enable and Hold Timing Diagram

| ORDER | EN   | HOLD     | OUT | COMMENTS                                                                                                                                 |

|-------|------|----------|-----|------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | Low  | х        | Off | Initial State. EN has a 500nA pulldown to GND. HOLD has an internal current source to OUT. HOLD follows OUT.                             |

| 2     | High | Released | On  | Regulator output is active when EN is pulled high. $\overline{\text{HOLD}}$ is in release state, and it follows OUT.                     |

| 3     | Low  | Released | Off | HOLD is in release state. OUT follows EN.                                                                                                |

| 4     | High | Low      | On  | HOLD is pulled low externally after OUT turns on. The regulator output is forced on regardless of the state of EN. A self-holding state. |

| 5     | Low  | Released | Off | HOLD is released after EN is pulled low. Output turns off.                                                                               |

| 5     | High | Х        | On  | Regulator enabled. Normal turn-on behavior. Regulator follows EN and HOLD follows OUT.                                                   |

# 4V to 72V Input LDOs with Boost Preregulator

### **Applications Information Diagrams**

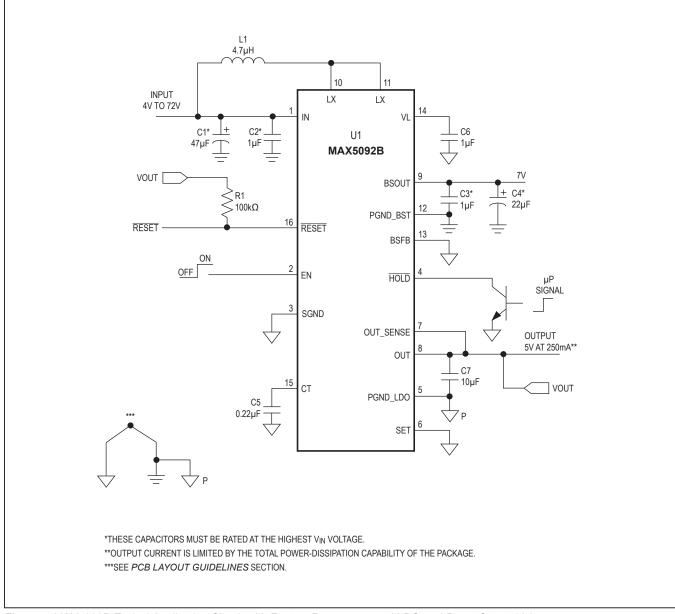

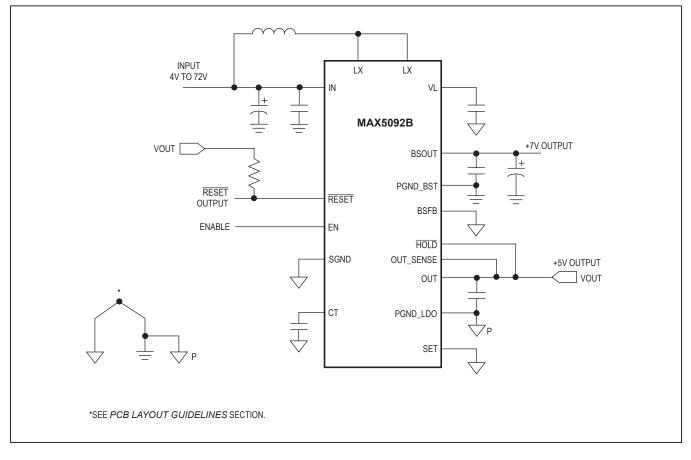

Figure 4. MAX5092B Typical Application Circuit with Factory Preprogrammed LDO and Boost Output Voltages

# 4V to 72V Input LDOs with Boost Preregulator

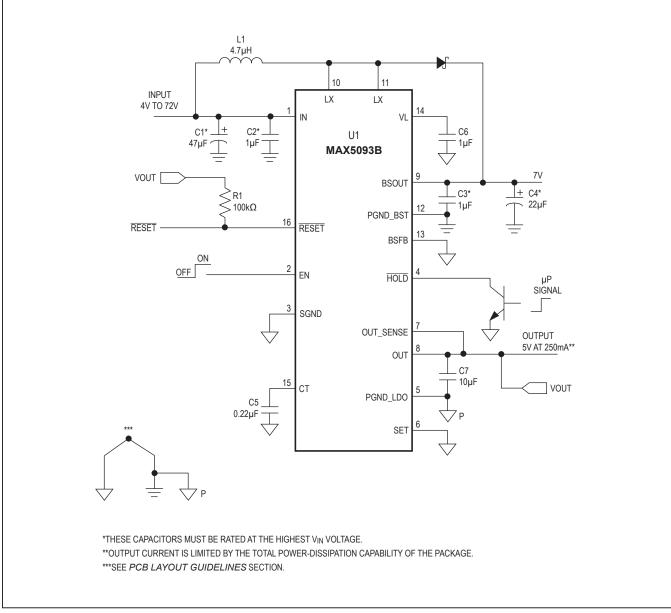

### **Applications Information Diagrams (continued)**

# 4V to 72V Input LDOs with Boost Preregulator

### **Applications Information Diagrams (continued)**

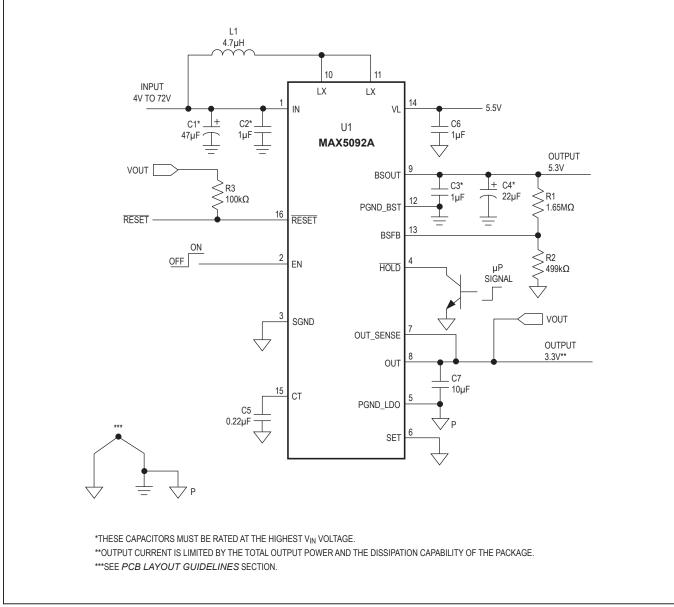

Figure 6. MAX5092A Typical Application Circuit with User-Programmed LDO and Boost Output Voltages

# 4V to 72V Input LDOs with Boost Preregulator

### **Applications Information Diagrams (continued)**

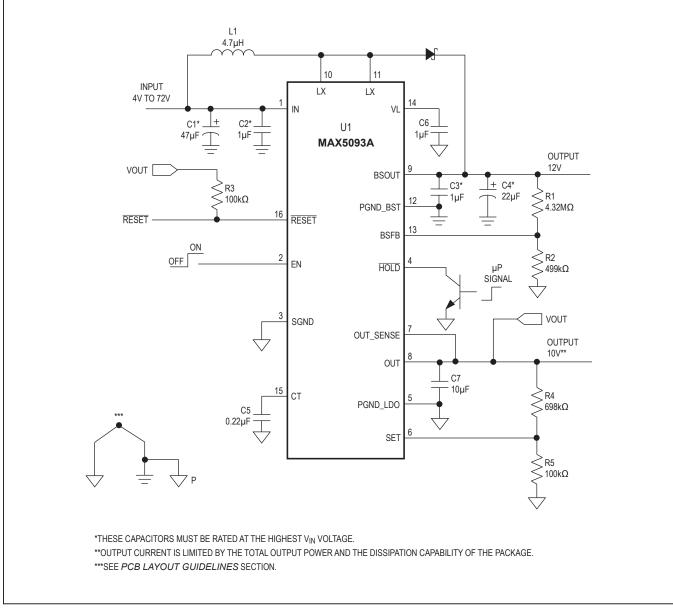

Figure 7. MAX5093A Typical Application Circuit with User-Programmable Boost Output Voltage and LDO Output Voltage

#### **Design Guidelines**

#### Input Capacitor (C<sub>IN</sub>) and Boost Capacitor (C<sub>BSOUT</sub>) Selection

The input current waveform of the boost converter is continuous, and usually does not demand high capacitance at its input. However, the MAX5092\_/MAX5093\_ boost converter is designed to fully turn on as soon as the input drops below a certain voltage in order to ride out coldcrank droops. This operation demands low input source impedance for proper operation. If the source (battery) is located far from the IC, high-capacity, low-ESR capacitors are recommended for CIN. The worst-case peak capacitor current could be as high as 3A. Use a  $47\mu$ F,  $100m\Omega$  low-ESR capacitor placed as close as possible to the input of the device. Note that the aluminum electrolytic capacitor ESR increases significantly at cold temperatures. In the cold temperature case, choose an electrolyte capacitor with ESR lower than 40mΩ or connect a low-ESR ceramic capacitor  $(10\mu F)$  in parallel with the electrolytic capacitor.

The boost converter output (BSOUT) is fed to the input of the internal 250mA LDO. The boost-converter output current waveform is discontinuous and requires highcapacity, low-ESR capacitors at BSOUT to ensure low V<sub>BSOUT</sub> ripple. During the on-time of the internal MOSFET, the BSOUT capacitor supplies 250mA current to the LDO input. During the off-time, the inductor dumps current into the output capacitor while supplying the output load current. The internal 250mA LDO is designed with high PSRR; however, high-frequency spikes may not be rejected by the LDO. Thus, high-value, low-ESR electrolytic capacitor. Use the following equation to calculate the required ESR (ESR<sub>BSOUT</sub>) of the BSOUT capacitor:

$$\mathsf{ESR}_{\mathsf{BSOUT}} = \frac{\Delta \mathsf{V}_{\mathsf{ESRBS}}}{\mathsf{I}_{\mathsf{LIM}} - \mathsf{I}_{\mathsf{OUT}}}$$

where  $\Delta V_{ESRBS}$  is 75% of total peak-to-peak ripple at BSOUT, I<sub>LIM</sub> is the internal switch current limit (3A max), and I<sub>OUT</sub> is the LDO output current. Use a 100m $\Omega$  or lower ESR electrolytic capacitor. Make sure the ESR at cold temperatures does not cause excessive ripple voltage. Alternately, use a 10µF ceramic capacitor in parallel with the electrolyte capacitor.

During the switch on-time, the BSOUT capacitor discharges while supplying  $I_{OUT}$ . The ripple caused by the capacitor discharge ( $\Delta V_{CBS}$ ) is estimated by using the following equation:

$$\Delta V_{CBS} = \frac{I_{OUT} \times 2.7 \times 10^{-6}}{C_{BSOUT}}$$

where  $I_{OUT}$  is the LDO output current and  $C_{BSOUT}$  is the BSOUT capacitance.

#### **Inductor Selection**

The control scheme of the MAX5092/MAX5093 permits flexibility in choosing an inductor value. Smaller inductance values typically offer smaller physical size for a given series resistance, allowing the smallest overall circuit dimensions. Circuits using larger inductance may provide higher efficiency and exhibit less ripple, but also may reduce the maximum output current. This occurs when the inductance is sufficiently large to prevent the LX current limit ( $I_{LIM}$ ) from being reached before the maximum on-time ( $t_{ON-MAX}$ ) expires.

For maximum output current, choose the inductor value so that the controller reaches the current limit before the maximum on-time is reached:

$$L \le \frac{V_{IN} \times t_{ON-MAX}}{I_{LIM}}$$

where  $t_{ON-MAX}$  is typically 2.25µs, and the current limit (I<sub>LIM</sub>) is a maximum of 3A (see the *Electrical Characteristics*). Choose an inductor with the maximum saturation current (I<sub>SAT</sub>) greater than 3A.

#### Setting the Boost Output Voltage (VBSOUT)

The MAX5092\_/MAX5093\_ feature Dual Mode™ operation for the internal boost converter output voltage. These devices operate in a preset output-voltage mode or an adjustable output-voltage mode. In preset mode, internal trimmed feedback resistors set V<sub>BSOUT</sub> to a fixed 7V. Select the preset mode by directly connecting BSFB to SGND (Figures 4 and 5). Ensure a low-impedance path between BSFB and SGND to limit the transient at BSFB to below 100mV. In adjustable mode, connect BSFB to the center tap of an external resistor-divider connected between BSOUT and SGND to program VBSOUT (Figures 6 and 7). Program (V<sub>BSOUT</sub> < V<sub>OUT</sub> + V<sub>BST DIS</sub>) for lower V<sub>BSOUT</sub> ripple. Note that the current drawn by the resistor-divider at BSOUT adds to the quiescent current and the shutdown current of the IC. Use the resistor-divider only if V<sub>BSOUT</sub> is required to be significantly different than 7V. Select  $499k\Omega$  or lower resistance value for the bottom resistor (R2) of the divider connected to SGND. The top resistor (R1) value is calculated as:

$$R1 = R2 \times \left(\frac{V_{BSOUT}}{V_{BSFB}} - 1\right)$$

where  $V_{BSFB}$  is the regulation voltage at BSFB (1.24V typ) and  $V_{BSOUT}$  is the desired output voltage for BSOUT.

#### Setting the LDO Output Voltage (VOUT)

The LDO output voltage is also Dual Mode (preset and adjustable). Preset mode is selected by connecting SET to SGND (Figures 4 and 5). In preset mode, V<sub>OUT</sub> regulates to 3.3V (MAX5092A/MAX5093A) or 5V (MAX5092B/MAX5093B) by internal trimmed feedback resistors. Adjustable mode is selected by connecting SET to the center tap of an external resistor-divider connected between OUT and SGND (Figures 6 and 7). Note that the current drawn by the resistor-divider at OUT adds to the quiescent current of the LDO. Use the resistor-divider only if V<sub>OUT</sub> is required to be significantly different than the preset voltage. Select 100k $\Omega$  or lower value for the bottom resistor (R5) of the divider connected to SGND. The top resistor (R4) value is calculated as:

$$R4 = R5 \times \left(\frac{V_{OUT}}{V_{SET}} - 1\right)$$

where  $V_{SET}$  is the regulation voltage at SET (1.24V typ) and  $V_{OUT}$  is the desired output voltage for the LDO output.

#### Schottky Diode Selection (MAX5093\_)

The MAX5093\_ requires an external diode connected between LX and BSOUT (Figures 5 and 7). Proper selection of an external diode can offer a lower forwardvoltage drop and a higher reverse-voltage handling capability. Since the high switching frequency of the IC demands a high-speed rectifier, Schottky diodes are recommended for most applications because of their fast recovery time and low forward-voltage drop. Ensure that the diode's peak current rating is greater than or equal to the peak current limit of internal boost converter MOSFET. A diode average forward current rating of at least 1A is recommended. Additionally, the diode reverse breakdown voltage must be greater than the worst-case load-dumpcondition voltage.

#### **CT** Capacitor Selection

The MAX5092\_/MAX5093\_ contain an open-drain poweron-reset output (RESET) that indicates when the LDO output voltage (V<sub>OUT</sub>) is out of regulation. When V<sub>OUT</sub> rises above 92% of the nominal output voltage, RESET goes high impedance after a user-programmable time delay. This time duration is programmable by a capacitor (C<sub>CT</sub>) from CT to SGND (Figures 4–7). For a chosen RESET active timeout period (t<sub>DELAY</sub>), calculate the required capacitor value as:

$$C_{CT} = \frac{2 \times 10^{-6} \times t_{DELAY}}{1.24}$$

When V<sub>OUT</sub> drops below 90% of the LDO output regulation voltage, a 5mA pulldown current from CT to SGND discharges C<sub>CT</sub>. The time required to discharge CT determines the delay necessary to pull RESET low. This delay provides glitch immunity to the RESET function. The glitch immunity delay is directly proportional to the CT capacitor and is approximately 70µs for a 0.1µF capacitor at CT.

Dual Mode is a trademark of Maxim Integrated Products, Inc.

## 4V to 72V Input LDOs with Boost Preregulator

Figure 8. MAX5092/MAX5093 Package Power Dissipation

#### Maximum Output Current (IOUT\_MAX)

The MAX5092\_/MAX5093\_ high input voltage (+72V max) provides up to 250mA of current from OUT. Package power-dissipation limits the amount of output current available for a given input/output voltage and ambient temperature. Figure 8 depicts the maximum power-dissipation curve for the devices. The graph assumes that the exposed metal pad of the IC package is soldered to the PCB copper according to the JEDEC 51 standard (multilayer board). Use Figure 8 to determine the allowable package dissipation for a given ambient temperature. Alternately, use the following formula to calculate the allowable package dissipation (P<sub>DISS</sub>) in watts:

For  $T_A \leq +70^{\circ}C$ :

$$P_{DISS} = 2.67$$

For  $+70^{\circ}C < T_{A} \le +125^{\circ}C$ :

where +70°C <  $T_A \le$  +125°C and 0.0333W/°C is the package thermal derating. After determining the allowable package dissipation, calculate the maximum output current ( $I_{OUT}$  MAX) using the following formula:

$$I_{OUT\_MAX} = \frac{P_{DISS} - P_{LOSS(BST)}}{V_{IN} - V_{OUT}}$$

where  $P_{DISS}$  is the allowable package power dissipation and  $P_{LOSS(BST)}$  is the boost converter power loss.  $\mathsf{P}_{DISS}$  includes the losses in the boost converter operation and the LDO itself. The boost converter loss  $\mathsf{P}_{LOSS(BST)}$ , depends on  $\mathsf{V}_{IN}, \mathsf{V}_{BSOUT},$  and  $\mathsf{I}_{OUT}.$  See the Boost Converter Power Loss graphs in the *Typical Operating Characteristics* to estimate the losses at a given  $\mathsf{V}_{IN}$  and  $\mathsf{V}_{BSOUT}$  at room temperature. At a higher ambient temperature of +105°C,  $\mathsf{P}_{LOSS(BST)}$  increases by up to 20% due to higher  $\mathsf{R}_{DS-ON}$  and switching losses of the internal boost converter MOSFET. (Note:  $\mathsf{I}_{OUT}\_MAX$  must be less than 250mA).

#### **PCB Layout Guidelines**

Good PCB layout and routing are required in highfrequency switching power supplies to achieve proper regulation and stability. It is strongly recommended that the evaluation kit PCB layouts be followed as closely as possible. Refer to the MAX5092 EV kit for an example layout. Follow these guidelines for good PCB layout:

- For SGND, use a large copper plane under the IC and solder it to the exposed paddle. To effectively use this copper area as a heat exchanger between the PCB and ambient, expose this copper area on the top and bottom side of the PCB. Do not make a direct connection from the EP copper plane to pin 3 (SGND) underneath the IC so as to minimize ground bounce.

- 2) Isolate the power components and high-current path from the sensitive analog circuit.

- Keep the high-current paths short, especially at the ground terminals. This practice is essential for stable, jitter-free operation.

- 4) Connect the return terminals of input capacitors and boost output capacitors to the PGND\_BST power ground plane. Connect the power ground (PGND\_ BST) and signal ground (SGND) planes together at the negative terminal of the input capacitors. Do not connect them anywhere else. Connect PGND\_LDO ground plane to SGND ground plane at a single point.

- 5) Ensure that the feedback connections are short and direct. Ensure a low-impedance path between BSFB and SGND to limit the transient at BSFB to 100mV.

- 6) Route high-speed switching nodes away from the sensitive analog areas. Use the internal PCB layer for SGND as an EMI shield to keep radiated noise away from the IC, feedback dividers, and bypass capacitors.

# 4V to 72V Input LDOs with Boost Preregulator

## Typical Operating Circuit

## 4V to 72V Input LDOs with Boost Preregulator

### **Selector Guide**

| PART         | PRESET LDO<br>OUTPUT (V) | ADJUSTABLE LDO<br>OUTPUT | PRESET BSOUT<br>OUTPUT (V) | ADJUSTABLE<br>BSOUT OUTPUT | BOOST DIODE |

|--------------|--------------------------|--------------------------|----------------------------|----------------------------|-------------|

| MAX5092AATE+ | 3.3                      | Yes                      | 7                          | Yes                        | Internal    |

| MAX5092BATE+ | 5                        | Yes                      | 7                          | Yes                        | Internal    |

| MAX5093AATE+ | 3.3                      | Yes                      | 7                          | Yes                        | External    |

| MAX5093BATE+ | 5                        | Yes                      | 7                          | Yes                        | External    |

### **Chip Information**

PROCESS: BICMOS

### **Package Information**

For the latest package outline information and land patterns (footprints), go to <u>www.maximintegrated.com/packages</u>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE<br>TYPE | PACKAGE<br>CODE | OUTLINE<br>NO. | LAND<br>PATTERN<br>NO. |

|-----------------|-----------------|----------------|------------------------|

| 16 TQFN-EP      | T1655+3         | <u>21-0140</u> | <u>90-0073</u>         |

## 4V to 72V Input LDOs with Boost Preregulator

### **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                                                                                                                                                                                                             |                            |

|--------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 0                  | 10/06            | Initial release                                                                                                                                                                                                         | —                          |

| 1                  | 1/08             | Updated Ordering Information and Electrical Characteristics table, added two Typical Operating Characteristics graphs, updated Functional Diagrams and Applications Information Diagrams, added boost converter details | 1–12, 14–17,<br>19, 22, 23 |

| 2                  | 10/14            | Removed automotive references from the <i>General Description</i> , <i>Applications</i> , <i>Detailed Description</i> , and <i>Enable and Hold Inputs</i> sections                                                      | 1, 12, 13                  |

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim Integrated's website at www.maximintegrated.com.

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.