#### General Description

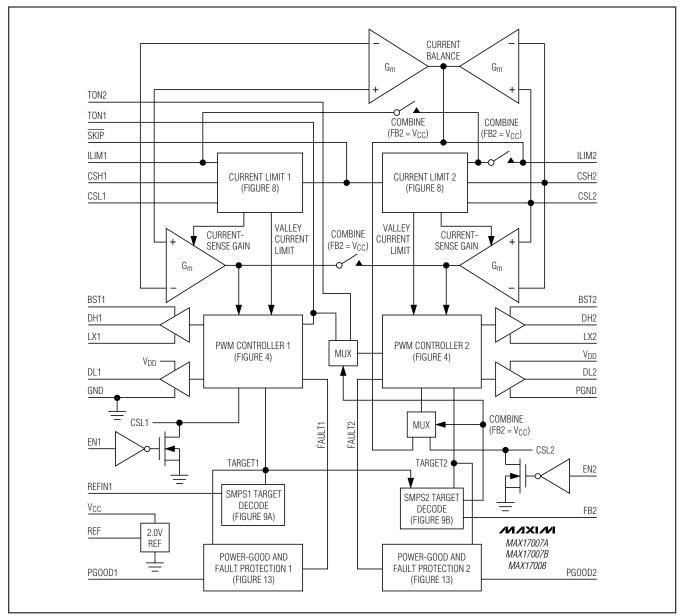

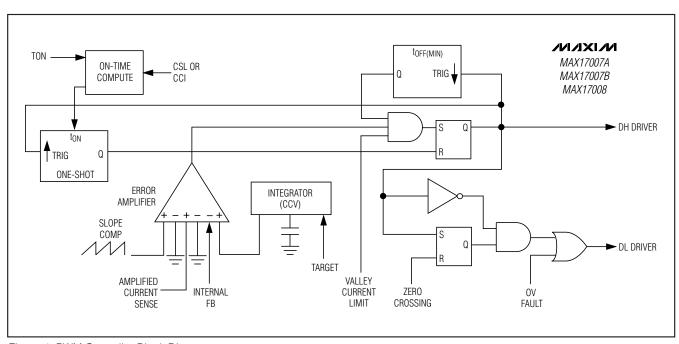

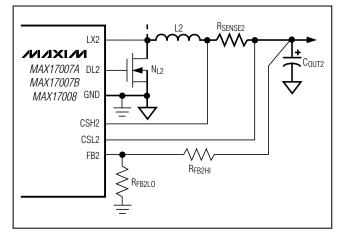

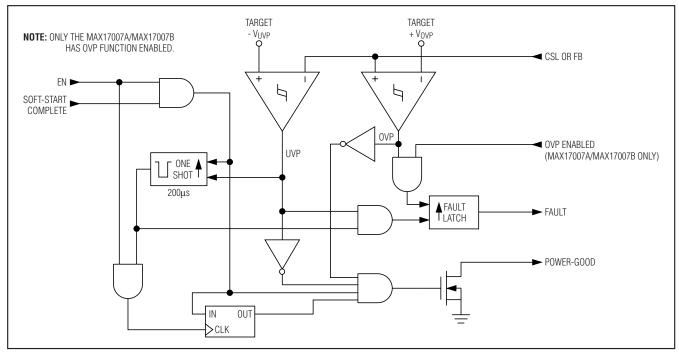

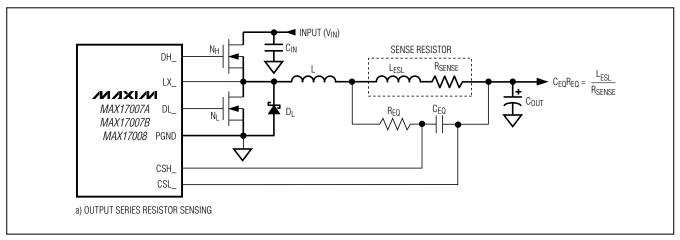

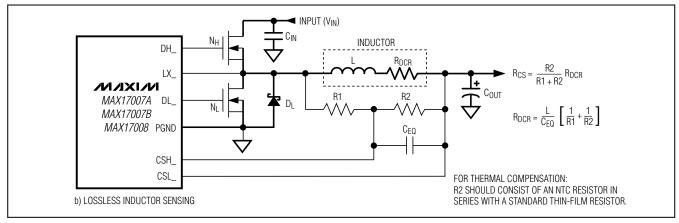

The MAX17007A/MAX17007B/MAX17008 are dual Quick-PWM<sup>™</sup> step-down controllers intended for general power generation in battery-powered systems. The two switched-mode power supplies (SMPSs) can also be combined to operate in a two-phase single-output mode. Constant on-time Quick-PWM operation provides fast response to load transients and handles wide input/output (I/O) voltage ratios with ease, while maintaining a relatively constant switching frequency. The switching frequency can be individually adjusted between 200kHz and 600kHz with external resistors. Differential output current sensing allows output sense-resistor sensing for an accurate current limit, or lossless inductor direct-current resistance (DCR) current sensing for lower power dissipation while maintaining 0.7% output accuracy. Overvoltage (MAX17007A/MAX17007B only), undervoltage protection, and accurate user-selectable current limits (15mV, 30mV, 45mV, and 60mV) ensure robust operations.

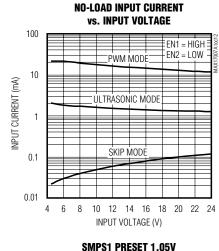

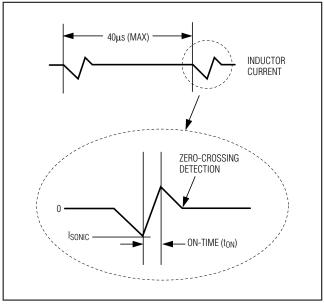

The SMPS outputs can operate in skip mode or in ultrasonic mode for improved light-load efficiency. The ultrasonic mode eliminates audible noises by maintaining a minimum switching frequency of 25kHz in pulseskipping mode.

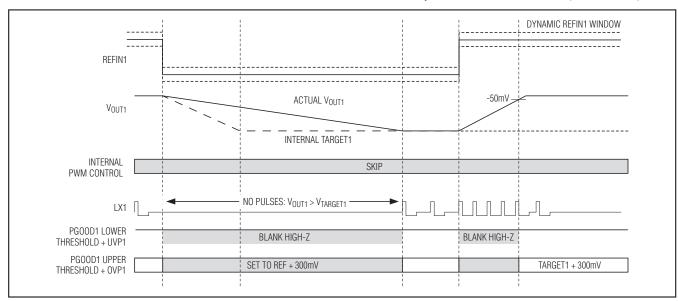

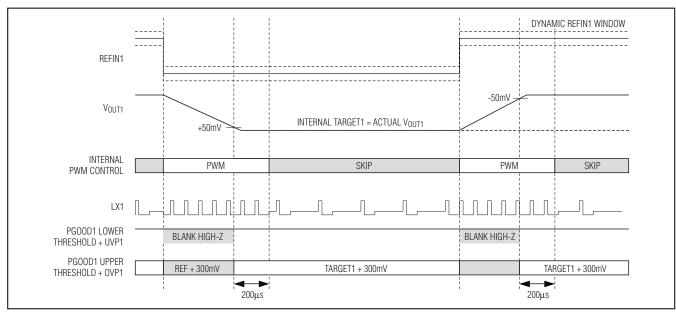

The output voltage of SMPS1 can be dynamically adjusted by changing the voltage at the REFIN1 pin. The device includes a 0.5% accurate reference output that can be used to set the REFIN1 voltage. An external 5V bias supply is required to power the internal circuitry and its gate drivers.

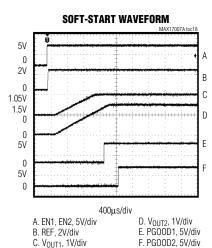

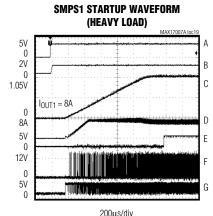

Independent on/off controls with well-defined logic thresholds and independent open-drain power-good outputs provide flexible system configurations. To prevent current surges at startup, the internal voltage target is slowly ramped up from zero to the final target with a slew rate of 1.3mV/µs for SMPS1 at CSL1 and 0.65mV/µs for SMPS2 at FB2. To prevent the output from ringing off below ground in shutdown, the internal voltage target is ramped down from its previous value to zero with the same respective slew rates. Integrated bootstrap switches eliminate the need for external bootstrap diodes.

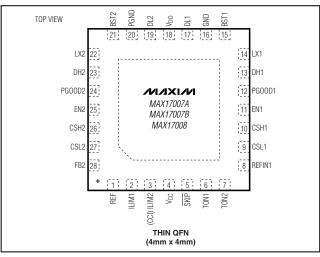

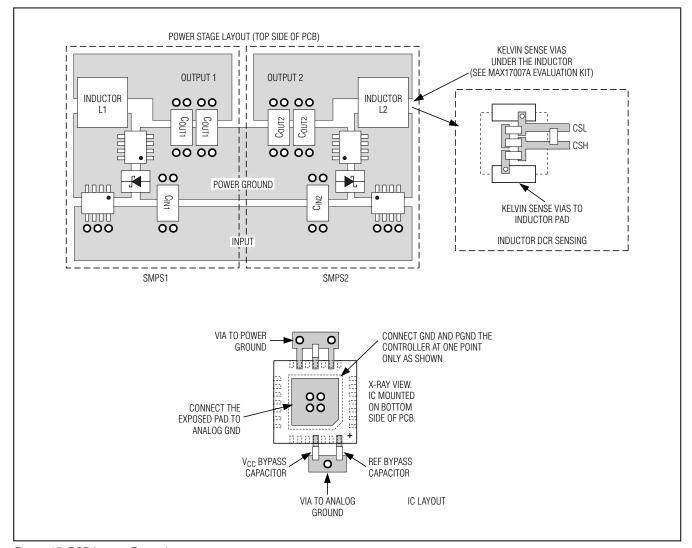

The MAX17007A/MAX17007B/MAX17008 are available in a space-saving, 28-pin, 4mm x 4mm, TQFN package with an exposed backside pad. The MAX17007B improves crosstalk performance over the MAX17007A.

#### **Applications**

Notebook Computers Low-Power I/O Supplies

**GPU Core Supplies** 2 to 4 Li+ Cells Battery-**Powered Devices**

Quick-PWM is a trademark of Maxim Integrated Products, Inc.

#### Features

- **Dual Quick-PWM with Fast Transient Response**

- **Automatic Dynamic REFIN1 Detection and** PGOOD1/Fault Blanking

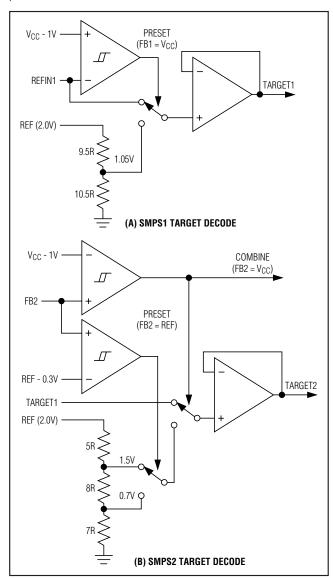

- ◆ Fixed and Adjustable Output Voltages ±0.7% Output Accuracy Over Line and Load OUT1: 0 to 2V Dynamic Output or Preset 1.05V OUT2: 0.7V to 2V Range or Preset 1.5V

- **♦** Resistor-Programmable Switching Frequency

- Integrated BST Switches

- ♦ Differential Current-Sense Inputs Low-Cost DCR Sensing or Accurate Current-**Sense Resistors Internally Coupled Current-Sense Compensation**

- **Combinable Mode Supports High-Current Dynamic Output Voltages**

- Selectable Forced-PWM, Pulse Skip, or Ultrasonic **Mode Operation**

- ◆ 26V Maximum Input Voltage Rating

- ♦ Independent Enable Inputs

- ♦ Independent Power-Good Outputs

- Overvoltage Protection (MAX17007A/MAX17007B Only)

- Undervoltage/Thermal Protection

- Voltage Soft-Start and Soft-Shutdown

#### **Ordering Information**

| PART          | TEMP RANGE      | PIN-PACKAGE |  |

|---------------|-----------------|-------------|--|

| MAX17007AGTI+ | -40°C to +105°C | 28 TQFN-EP* |  |

| MAX17007BGTI+ | -40°C to +105°C | 28 TQFN-EP* |  |

| MAX17008GTI+  | -40°C to +105°C | 28 TQFN-EP* |  |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package. \*EP = Exposed pad.

#### **Pin Configuration**

MIXIM

Maxim Integrated Products 1

#### **ABSOLUTE MAXIMUM RATINGS**

| BST1, BST2 to GND0.3V to +34V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | DL1 to GND0.3V to (V <sub>DD</sub> + 0.3V)            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| BST1, BST2 to V <sub>DD</sub> 0.3V to +28V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | DL2 to PGND0.3V to (V <sub>DD</sub> + 0.3V)           |

| TON1, TON2 to GND0.3V to +28V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | PGND to GND0.3V to + 0.3V                             |

| V <sub>DD</sub> to GND0.3V to +6V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | REF Short Circuit to GNDContinuous                    |

| V <sub>DD</sub> to V <sub>CC</sub> 0.3V to +0.3V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |

| LX1 to BST16V to +0.3V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 28-Pin TQFN T2844-1                                   |

| LX2 to BST26V to +0.3V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | (derate 20.8mW/°C above +70°C)1667mW                  |

| DH1 to LX10.3V to (V <sub>BST1</sub> + 0.3V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Extended Operating Temperature Range40°C to +105°C    |

| DH2 to LX20.3V to (V <sub>BST2</sub> + 0.3V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Junction Temperature+150°C                            |

| ILIM1, ILIM2, REF to GND0.3V to (V <sub>CC</sub> + 0.3V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Storage Temperature Range65°C to +150°C               |

| CSH1, CSH2, CSL1, CSL2, FB2, REFIN1 to GND0.3V to +6V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Lead Temperature (soldering, 10s)+300°C               |

| EN1, EN2, SKIP, PGOOD1, PGOOD2 to GND0.3V to +6V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Soldering Temperature+260°C                           |

| Observation and the second state of the second |                                                       |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{IN} = 12V, V_{DD} = V_{CC} = V_{EN1} = V_{EN2} = 5V, V_{REFIN1} = 2V, \overline{SKIP} = GND, T_A = 0 to +85^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .)

| PARAMETER                                                     | SYMBOL                                     | CONDITIONS                                                              |                                                           | MIN           | TYP               | MAX                   | UNITS |

|---------------------------------------------------------------|--------------------------------------------|-------------------------------------------------------------------------|-----------------------------------------------------------|---------------|-------------------|-----------------------|-------|

| PWM CONTROLLER                                                |                                            |                                                                         |                                                           |               |                   |                       |       |

| Input Voltage Range                                           | VIN                                        |                                                                         |                                                           | 4.5           |                   | 26                    | V     |

| Quiescent Supply Current (V <sub>DD</sub> , V <sub>CC</sub> ) | I <sub>DD</sub> + I <sub>CC</sub>          | Output forced abov<br>V <sub>EN1</sub> = V <sub>EN2</sub> = 5V          | ve regulation voltage,                                    |               | 1.7               | 2.5                   | mA    |

| Shutdown Supply Current (VDD, VCC)                            | I <sub>SHDN</sub>                          | EN1 = EN2 = GND                                                         | , T <sub>A</sub> = +25°C                                  |               | 0.1               | 5                     | μΑ    |

|                                                               |                                            | V <sub>IN</sub> = 12V,                                                  | $R_{TON1} = R_{TON2} =$<br>97.5k $\Omega$ (600kHz)        | 142<br>(-15%) | 174               | 194<br>(+15%)         |       |

| On-Time (Note 1)                                              | t <sub>ON1</sub> , t <sub>ON2</sub>        | VCSL1 = VCSL2 =<br>VCCI = 1.2V,<br>separate or                          | $R_{TON1} = R_{TON2} =$<br>200k $\Omega$ (300kHz)         | 305<br>(-10%) | 336               | 368<br>(+10%)         | ns    |

|                                                               | 1 '                                        | combined mode                                                           | RTON1 = RTON2 = $302.5$ k $\Omega$ (200kHz)               | 425<br>(-15%) | 500               | 575<br>(+15%)         |       |

| Minimum Off-Time                                              | toff(MIN)                                  | (Note 1)                                                                |                                                           |               | 250               | 400                   | ns    |

| TON1, TON2, Shutdown Supply Current                           | I <sub>TON1</sub> ,<br>I <sub>TON2</sub>   | EN1 = EN2 = GND<br>V <sub>DD</sub> = 0 or 5V, T <sub>A</sub> =          | , V <sub>TON1</sub> = V <sub>TON2</sub> = 26V,<br>= +25°C |               | 0.01              | 1                     | μΑ    |

| REFIN1 Voltage Range                                          | V <sub>REFIN1</sub>                        | (Note 2)                                                                |                                                           | 0             |                   | V <sub>REF</sub>      | V     |

| FB2 Regulation Voltage                                        | V <sub>FB2</sub>                           | Adjustable mode                                                         |                                                           |               | 0.7               |                       | V     |

| FB2 Input Voltage Range                                       |                                            | Preset mode                                                             |                                                           | 1.7           |                   | 2.3                   | V     |

| FB2 Combined-Mode Threshold                                   |                                            | Combined mode                                                           |                                                           | 3.8           | V <sub>CC</sub> - | V <sub>CC</sub> - 0.4 | V     |

| REFIN1 Dual Mode™<br>Switchover Threshold                     |                                            |                                                                         |                                                           | 3.8           | V <sub>CC</sub> - | V <sub>CC</sub> - 0.4 | V     |

| REFIN1, FB2 Bias Current                                      | I <sub>REFIN1</sub> ,<br>I <sub>FB2</sub>  | REFIN1 = 0.5V to 2V;<br>V <sub>FB2</sub> = 0.7V, T <sub>A</sub> = +25°C |                                                           | -0.1          |                   | +0.1                  | μΑ    |

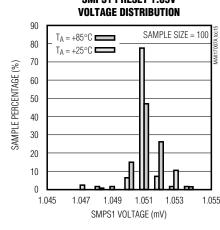

|                                                               | VCSL1                                      | Measured at CSL1, V <sub>IN</sub> = 2V to 26V, Sk                       |                                                           | 1.043         | 1.05              | 1.057                 | V     |

| SMPS1 Voltage Accuracy                                        | \/                                         | REFIN1 = 500mV,                                                         | T <sub>A</sub> = +25°C                                    | -12           |                   | +12                   |       |

|                                                               | V <sub>CSL1</sub> -<br>V <sub>REFIN1</sub> | SKIP = V <sub>CC</sub>                                                  | $T_A = 0$ °C to +85°C                                     | -20           |                   | +20                   | mV    |

|                                                               | *IILI IINI                                 | REFIN1 = 2V, SKIP                                                       | = VCC                                                     | -20           |                   | +20                   |       |

Dual Mode is a trademark of Maxim Integrated Products, Inc.

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN} = 12V, V_{DD} = V_{CC} = V_{EN1} = V_{EN2} = 5V, V_{REFIN1} = 2V, \overline{SKIP} = GND, T_A = 0 to +85°C$ , unless otherwise noted. Typical values are at  $T_A = +25°C$ .)

| PARAMETER                                                                                             | SYMBOL                                     | CONDITIONS                                                                                                                  | MIN                     | TYP   | MAX   | UNITS |

|-------------------------------------------------------------------------------------------------------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-------------------------|-------|-------|-------|

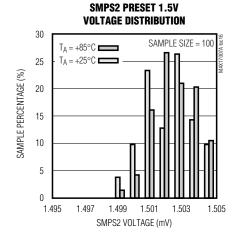

| SMPS2 Voltage Accuracy                                                                                | V <sub>CSL2</sub>                          | Measured at CSL2, FB2 = REF, V <sub>IN</sub> = 2V to 26V, <del>SKIP</del> = V <sub>CC</sub>                                 | 1.489                   | 1.5   | 1.511 | V     |

| Load Regulation Error                                                                                 |                                            | I <sub>LOAD</sub> = 0 to full load, SKIP = V <sub>CC</sub> (Note 3)                                                         |                         | 0.1   |       | %     |

| Line Regulation Error                                                                                 |                                            | V <sub>DD</sub> = 4.5V to 5.5V, V <sub>IN</sub> = 4.5V to 26V (Note 3)                                                      |                         | 0.25  |       | %     |

| CSL1 Soft-Start/-Stop Slew Rate                                                                       | SR <sub>SS1</sub>                          | Rising/falling edge on EN1                                                                                                  |                         | 1.25  |       | mV/μs |

| FB2 Soft-Start/-Stop Slew Rate                                                                        | SR <sub>SS2</sub>                          | Rising/falling edge on EN2                                                                                                  |                         | 0.63  |       | mV/μs |

| Dynamic REFIN1 Slew Rate                                                                              | SR <sub>DYN</sub>                          | Rising edge on REFIN1                                                                                                       |                         | 11.4  |       | mV/μs |

| INTERNAL REFERENCE                                                                                    |                                            |                                                                                                                             |                         |       |       |       |

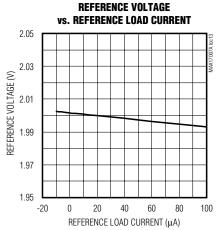

| Reference Voltage                                                                                     | V <sub>REF</sub>                           | $V_{DD} = 4.5V \text{ to } 5.5V$                                                                                            | 1.990                   | 2.000 | 2.010 | V     |

| Reference Lockout Voltage                                                                             | VREF(UVLO)                                 | Rising edge, hysteresis = 230mV                                                                                             |                         | 1.8   |       | V     |

| Reference Load Regulation                                                                             | (= -/                                      | I <sub>REF</sub> = -10μA to +100μA                                                                                          | 1.980                   |       | 2.015 | mV    |

| FAULT DETECTION                                                                                       | l                                          |                                                                                                                             |                         |       |       | ı     |

| SMPS1 Overvoltage Trip Threshold and PGOOD1 Upper                                                     | V <sub>O</sub> VP1,                        | With respect to the internal target voltage (error comparator threshold); rising edge; hysteresis = 50mV                    | 260                     | 300   | 340   | mV    |

| Threshold<br>(MAX17007A Only)                                                                         | VPG1_H                                     | Dynamic transition                                                                                                          | V <sub>REF</sub> + 0.30 |       | V     |       |

| (MAX17007A Offiy)                                                                                     |                                            | Minimum OVP threshold                                                                                                       |                         | 0.7   |       | V     |

| SMPS2 Adjustable Mode<br>Overvoltage Trip Threshold and<br>PGOOD2 Upper Threshold<br>(MAX17007A Only) | V <sub>OVP2</sub> ,<br>V <sub>PG2</sub> _H | With respect to the internal target voltage 0.7V (error comparator threshold); hysteresis = 50mV                            | 120                     | 150   | 180   | mV    |

| Output Overvoltage Fault<br>Propagation Delay<br>(MAX17007A Only)                                     | tovp                                       | CSL1/FB2 forced 25mV above trip threshold                                                                                   |                         | 5     |       | μs    |

| SMPS1 Undervoltage Protection<br>Trip Threshold and Lower<br>PGOOD1 Threshold                         | V <sub>UVP1</sub> ,<br>V <sub>PG1_L</sub>  | With respect to the internal target voltage (error comparator threshold); falling edge; hysteresis = 50mV                   | -240                    | -200  | -160  | mV    |

| SMPS2 Undervoltage Protection<br>Trip Threshold and Lower<br>PGOOD2 Threshold                         | V <sub>UVP2</sub> ,<br>V <sub>PG2_L</sub>  | With respect to the internal target voltage 0.7V (error comparator threshold); falling edge; hysteresis = 50mV              | -130                    | -100  | -70   | mV    |

| Output Undervoltage Fault<br>Propagation Delay                                                        | tuvp                                       | CSL1/FB2 forced 25mV below trip threshold                                                                                   | 90                      | 205   | 360   | μs    |

|                                                                                                       |                                            | UVP falling edge, 25mV overdrive                                                                                            |                         | 5     |       |       |

| PGOOD_ Propagation Delay                                                                              | tpgood                                     | OVP rising edge, 25mV overdrive                                                                                             |                         | 5     |       | μs    |

|                                                                                                       |                                            | Startup delay from regulation                                                                                               | 90                      | 205   | 360   |       |

| PGOOD_ Output Low Voltage                                                                             |                                            | I <sub>SINK</sub> = 3mA                                                                                                     |                         |       | 0.4   | V     |

| PGOOD_ Leakage Current                                                                                | I <sub>PGOOD</sub>                         | CSL1 = REFIN1, FB2 = 0.7V (PGOOD_high impedance), PGOOD_forced to 5V, T <sub>A</sub> = +25°C                                |                         |       | 1     | μA    |

| Dynamic REFIN1 Transition<br>Fault-Blanking Threshold                                                 |                                            | Fault blanking initiated; REFIN1 deviation from the internal target voltage (error comparator threshold); hysteresis = 10mV |                         | ±50   |       | mV    |

| Thermal-Shutdown Threshold                                                                            | TSHDN                                      | Hysteresis = 15°C (Note 3)                                                                                                  |                         | 160   |       | °C    |

| V <sub>CC</sub> Undervoltage Lockout<br>Threshold                                                     | V <sub>UVLO(VCC)</sub>                     | Rising edge, PWM disabled below this level, hysteresis = 100mV                                                              | 3.95                    | 4.20  | 4.45  | V     |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN} = 12V, V_{DD} = V_{CC} = V_{EN1} = V_{EN2} = 5V, V_{REFIN1} = 2V, \overline{SKIP} = GND, T_A = 0 to +85°C$ , unless otherwise noted. Typical values are at  $T_A = +25°C$ .)

| PARAMETER                                           | SYMBOL                   | CON                                                                                                                                                                                   | DITIONS                                      | MIN  | TYP                | MAX  | UNITS |

|-----------------------------------------------------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|------|--------------------|------|-------|

| CURRENT LIMIT                                       | •                        |                                                                                                                                                                                       |                                              | •    |                    |      | •     |

| Current Conce Innut Dongs                           |                          | CSH1, CSH2                                                                                                                                                                            |                                              | 0    |                    | 2.3  | V     |

| Current-Sense Input Range                           |                          | CSL1, CSL2                                                                                                                                                                            |                                              | 0    |                    | 2.3  | ] V   |

| Current-Sense Input (CSH_)<br>Leakage Current       |                          | CSH_ = GND or V <sub>CC</sub>                                                                                                                                                         | c, T <sub>A</sub> = +25°C                    | -0.2 |                    | +0.2 | μА    |

| Current-Sense Input (CSL_)<br>Leakage Current       |                          | CSL_= CSL_ = 2V,                                                                                                                                                                      | Γ <sub>A</sub> = +25°C                       |      |                    | 1    | μА    |

|                                                     |                          | Vcsh - Vcsl                                                                                                                                                                           | T <sub>A</sub> = +25°C                       | 28   | 30                 | 32   |       |

|                                                     |                          | ILIM1 = ILIM2 = RE                                                                                                                                                                    | $F T_A = 0$ °C to +85°C                      | 27   | 30                 | 33   | 1     |

| Current-Limit Threshold (Fixed)                     | VCSLIMIT                 | VCSH VCSL_, ILIM                                                                                                                                                                      | I = ILIM2 = V <sub>CC</sub>                  | 56   | 60                 | 64   | mV    |

|                                                     |                          | VCSH VCSL_, ILIM1                                                                                                                                                                     | = ILIM2 = OPEN                               | 42   | 45                 | 48   | ]     |

|                                                     |                          | VCSH VCSL_, ILIM                                                                                                                                                                      | = ILIM2 = GND                                | 13   | 15                 | 17   | ]     |

| Current-Limit Threshold (Negative)                  | VNEG                     | V <sub>CSH_</sub> - V <sub>CSL_</sub> , SKIP                                                                                                                                          | = VCC                                        |      | -1.2 x<br>VCSLIMIT |      | mV    |

| Current-Limit Threshold (Zero Crossing)             | Vzx                      | V <sub>CSH</sub> - V <sub>CSL</sub> , SKIP<br>ILIM1 = ILIM2 = RE                                                                                                                      |                                              |      | 1                  |      | mV    |

| Ultrasonic Frequency                                |                          | SKIP = open (3.3V); V <sub>CSL1</sub> = V <sub>REFIN1</sub> + 50mV;<br>V <sub>CSL2</sub> = V <sub>FB2</sub> + 50mV                                                                    |                                              | 20   |                    |      | kHz   |

| Ultrasonic Current-Limit                            | 7                        | 01/10                                                                                                                                                                                 | V <sub>CSL1</sub> = V <sub>REF1</sub> + 50mV | 22   | 33                 | 46   | .,,   |

| Threshold                                           |                          | SKIP = open (3.3V)                                                                                                                                                                    | V <sub>CSL2</sub> = V <sub>FB2</sub> + 50mV  | 18   | 30                 | 46   | - mV  |

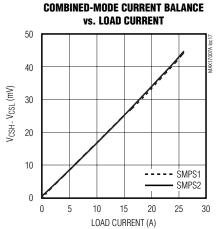

| Current-Balance Amplifier (GMI)<br>Offset           |                          | [V(CSH1,CSL1) - V(C                                                                                                                                                                   | SH2,CSL2)] at I <sub>CCI</sub> = 0           | -3   |                    | +3   | mV    |

| Current-Balance Amplifier (GMI)<br>Transconductance |                          | ΔI <sub>CCI</sub> /Δ[V(CSH1,CSL1) - V(CSH2,CSL2)];<br>V <sub>CCI</sub> = V <sub>CSL1</sub> = V <sub>CSL2</sub> = 0.5V to 2V, and<br>V(CSH_,CSL_) = -60.0mV to +60.0mV,<br>ILIM1 = GND |                                              |      | 180                |      | μS    |

| GATE DRIVERS                                        | •                        |                                                                                                                                                                                       |                                              |      |                    |      |       |

| DH1, DH2 Gate-Driver                                | Day.::-:::               | BST LX_ forced                                                                                                                                                                        | Low state (pulldown)                         |      | 1.7                | 4.0  |       |

| On-Resistance                                       | Ron(DH)                  | to 5V                                                                                                                                                                                 | High state (pullup)                          |      | 1.7                | 4.0  | Ω     |

| DL1, DL2 Gate-Driver                                | Danie                    | High state (pullup)                                                                                                                                                                   |                                              |      | 1.3                | 3.0  | 0     |

| On-Resistance                                       | RON(DL)                  | Low state (pulldown                                                                                                                                                                   | )                                            |      | 0.6                | 2.5  | Ω     |

| DH1, DH2 Gate-Driver<br>Source/Sink Current         | IDH                      | DH_ forced to 2.5V, BST LX_ forced to 5V                                                                                                                                              |                                              |      | 1.2                |      | А     |

| DL1, DL2 Gate-Driver<br>Source Current              | I <sub>DL</sub> (SOURCE) | DL_ forced to 2.5V                                                                                                                                                                    |                                              |      | 1                  |      | А     |

| DL1, DL2 Gate-Driver<br>Sink Current                | I <sub>DL(SINK)</sub>    | DL_ forced to 2.5V                                                                                                                                                                    |                                              |      | 2.4                |      | А     |

| Driver Proposation Delay                            |                          | DH_ low to DL high                                                                                                                                                                    |                                              | 10   | 25                 | 40   |       |

| Driver Propagation Delay                            |                          | DL_ low to DH high                                                                                                                                                                    |                                              | 15   | 30                 | 45   | ns    |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN} = 12V, V_{DD} = V_{CC} = V_{EN1} = V_{EN2} = 5V, V_{REFIN1} = 2V, \overline{SKIP} = GND, T_A = 0 to +85°C$ , unless otherwise noted. Typical values are at  $T_A = +25°C$ .)

| PARAMETER                          | SYMBOL             | CONE                                                                         | DITIONS     | MIN                   | TYP  | MAX  | UNITS |

|------------------------------------|--------------------|------------------------------------------------------------------------------|-------------|-----------------------|------|------|-------|

| DI Transition Time                 |                    | DL_ falling, C <sub>DL</sub> = 3r                                            | nF          | 10                    | 20   |      | ns    |

| DL_ Transition Time                |                    | DL_ rising, C <sub>DL</sub> = 3n                                             | F           | 10                    | 20   |      | 1115  |

| DLI Transition Time                |                    | DH_ falling, C <sub>DH</sub> = 3                                             | nF          | 10                    | 20   |      | 20    |

| DH_ Transition Time                |                    | DH_ rising, C <sub>DH</sub> = 3r                                             | nF          | 10                    | 20   |      | ns    |

| Internal BST_ Switch On-Resistance | R <sub>BST</sub> _ | I <sub>BST_</sub> = 10mA, V <sub>DD</sub> = 5V                               |             |                       | 6.5  | 11.0 | Ω     |

| INPUTS AND OUTPUTS                 |                    |                                                                              |             |                       |      |      | •     |

| EN1, EN2 Logic-Input Threshold     |                    | EN1, EN2 rising edge,<br>hysteresis = 300mV/600mV (min/max)                  |             | 1.20                  | 1.70 | 2.20 | V     |

| Logic-Input Current                |                    | EN1, EN2, T <sub>A</sub> = +25°                                              | C           | -0.5                  |      | +0.5 | μΑ    |

|                                    |                    |                                                                              | High (5V)   | V <sub>CC</sub> - 0.3 |      |      |       |

| Quad-Level Input-Logic Levels      |                    | SKIP, ILIM1, ILIM2                                                           | Open (3.3V) | 3.0                   |      | 3.6  | V     |

|                                    |                    |                                                                              | Ref (2.0V)  | 1.7                   |      | 2.3  | ]     |

|                                    |                    |                                                                              | Low (GND)   |                       |      | 0.4  |       |

| Quad-Level Logic-Input Current     |                    | SKIP, ILIM1, ILIM2 forced to GND or V <sub>CC</sub> , T <sub>A</sub> = +25°C |             | -2                    |      | +2   | μА    |

#### **ELECTRICAL CHARACTERISTICS**

$(V_{IN} = 12V, V_{DD} = V_{CC} = V_{EN1} = V_{EN2} = 5V, V_{REFIN1} = 2V, \overline{SKIP} = GND, T_A = -40^{\circ}C \text{ to } +105^{\circ}C, unless otherwise noted.) (Note 4)$

| PARAMETER                           | SYMBOL                                    | CON                                  | IDITIONS                                           | MIN  | MAX                   | UNITS |

|-------------------------------------|-------------------------------------------|--------------------------------------|----------------------------------------------------|------|-----------------------|-------|

| PWM CONTROLLER                      |                                           |                                      |                                                    |      |                       |       |

| Input Voltage Range                 | VIN                                       |                                      |                                                    | 4.5  | 26                    | V     |

| Quiescent Supply Current (VDD, VCC) | IDD + ICC                                 | Output forced above VEN1 = VEN2 = 5V | e regulation voltage,                              |      | 2.5                   | mA    |

|                                     |                                           | V <sub>IN</sub> = 12V,               | $R_{TON1} = R_{TON2} =$<br>97.5k $\Omega$ (600kHz) | 142  | 194                   |       |

| On-Time (Note 1)                    | t <sub>ON1</sub> ,<br>t <sub>ON2</sub>    | $V_{CCI} = 1.2V$ ,                   | $R_{TON1} = R_{TON2} =$<br>200k $\Omega$ (300kHz)  | 305  | 368                   | ns    |

|                                     |                                           | 1                                    | $R_{TON1} = R_{TON2} =$ 302.5k $\Omega$ (200kHz)   | 425  | 575                   |       |

| Minimum Off-Time                    | toff(MIN)                                 | (Note 1)                             |                                                    |      | 400                   | ns    |

| REFIN1 Voltage Range                | V <sub>REFIN1</sub>                       |                                      |                                                    | 0    | V <sub>REF</sub>      | V     |

| FB2 Input Voltage Range             |                                           | Preset mode                          |                                                    | 1.7  | 2.3                   | V     |

| FB2 Combined-Mode Threshold         |                                           | Combined mode                        |                                                    | 3.75 | V <sub>CC</sub> - 0.4 | V     |

| REFIN1, FB2 Bias Current            | I <sub>REFIN1</sub> ,<br>I <sub>FB2</sub> |                                      |                                                    | -0.1 | +0.1                  | μΑ    |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN} = 12V, V_{DD} = V_{CC} = V_{EN1} = V_{EN2} = 5V, V_{REFIN1} = 2V, \overline{SKIP} = GND, T_A = -40^{\circ}C \text{ to } +105^{\circ}C, unless otherwise noted.) (Note 4)$

| PARAMETER                                                                             | SYMBOL                                    | CONDITIONS                                                                                                    | MIN   | MAX                   | UNITS |

|---------------------------------------------------------------------------------------|-------------------------------------------|---------------------------------------------------------------------------------------------------------------|-------|-----------------------|-------|

| REFIN1 Dual-Mode<br>Switchover Threshold                                              |                                           |                                                                                                               | 3.75  | V <sub>CC</sub> - 0.4 | V     |

| SMPS1 Voltage Accuracy                                                                | VcsL1                                     | Measured at CSL1, REFIN1 = V <sub>CC</sub> ;<br>V <sub>IN</sub> = 2V to 26V, SKIP = V <sub>CC</sub> (Note 2)  | 1.039 | 1.061                 | V     |

| SMPS2 Voltage Accuracy                                                                | V <sub>CSL2</sub>                         | Measured at CSL2, FB2 = REF;<br>V <sub>IN</sub> = 2V to 26V, SKIP = V <sub>CC</sub> (Note 2)                  | 1.485 | 1.515                 | V     |

| INTERNAL REFERENCE                                                                    |                                           |                                                                                                               |       |                       |       |

| Reference Voltage                                                                     | VREF                                      | V <sub>DD</sub> = 4.5V to 5.5V                                                                                | 1.985 | 2.015                 | V     |

| FAULT DETECTION                                                                       |                                           |                                                                                                               |       |                       |       |

| SMPS1 Overvoltage Trip<br>Threshold and PGOOD1<br>Upper Threshold<br>(MAX17007A Only) | Vovp1,<br>VpG1_H                          | With respect to the internal target voltage (error comparator threshold); rising edge; hysteresis = 50mV      | 260   | 340                   | mV    |

| SMPS2 Overvoltage Trip<br>Threshold and PGOOD2<br>Upper Threshold<br>(MAX17007A Only) | V <sub>OVP2</sub> ,<br>V <sub>PG2</sub> H | With respect to the internal target voltage 0.7V (error comparator threshold); hysteresis = 50mV              | 120   | 180                   | mV    |

| SMPS1 Undervoltage Protection<br>Trip Threshold and Lower<br>PGOOD1 Threshold         | V <sub>UVP1</sub> ,<br>V <sub>PG1_L</sub> | With respect to the internal target voltage (error comparator threshold) falling edge; hysteresis = 50mV      | -240  | -160                  | mV    |

| SMPS2 Undervoltage Protection<br>Trip Threshold and Lower<br>PGOOD2 Threshold         | V <sub>UVP2</sub> ,<br>V <sub>PG2_L</sub> | With respect to the internal target voltage 0.7V (error comparator threshold) falling edge; hysteresis = 50mV | -130  | -70                   | mV    |

| Output Undervoltage Fault<br>Propagation Delay                                        | tuvp                                      | REFIN1/FB2 forced 25mV below trip threshold                                                                   | 90    | 360                   | μs    |

| PGOOD_ Propagation Delay                                                              | tpgood                                    | Startup delay from regulation                                                                                 | 90    | 360                   | μs    |

| PGOOD_ Output Low Voltage                                                             |                                           | I <sub>SINK</sub> = 3mA                                                                                       |       | 0.4                   | V     |

| V <sub>CC</sub> Undervoltage Lockout<br>Threshold                                     | Vuvlo(vcc)                                | Rising edge, PWM disabled below this level; hysteresis = 100mV                                                | 3.8   | 4.45                  | V     |

| CURRENT LIMIT                                                                         |                                           |                                                                                                               |       |                       |       |

| Current-Sense Input Range                                                             |                                           | CSH1, CSH2                                                                                                    | 0     | 2.3                   | V     |

| Current-Sense input Hange                                                             |                                           | CSL1, CSL2                                                                                                    | 0     | 2.3                   | v     |

| Current-Limit Threshold (Fixed)                                                       | VCSLIMIT                                  | VCSH VCSL_, ILIM1 = ILIM2 = REF                                                                               | 27    | 33                    | mV    |

| Ultrasonic Frequency                                                                  |                                           | SKIP = OPEN (3.3V);           VCSL1 = VREFIN1 + 50mV;           VCSL2 = VFB2 + 50mV                           | 18    |                       | kHz   |

| Ultrasonic Current-Limit                                                              |                                           | $\overline{\text{SKIP}} = \text{OPEN} (3.3V)$ $V_{\text{CSL1}} = V_{\text{REF1}} + 50\text{mV}$               | 22    | 46                    | mV    |

| Threshold                                                                             |                                           | $V_{CSL2} = V_{FB2} + 50 \text{mV}$                                                                           | 18    | 46                    | 111V  |

| Current-Balance Amplifier (GMI)<br>Offset                                             |                                           | [V(CSH1,CSL1) - V(CSH2,CSL2)] at I <sub>CCI</sub> = 0                                                         | -3    | +3                    | mV    |

6 \_\_\_\_\_\_ /N/XI/M

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN} = 12V, V_{DD} = V_{CC} = V_{EN1} = V_{EN2} = 5V, V_{REFIN1} = 2V, \overline{SKIP} = GND, T_A = -40^{\circ}C \text{ to } +105^{\circ}C, \text{ unless otherwise noted.})$  (Note 4)

| PARAMETER                          | SYMBOL             | COND                                           | ITIONS               | MIN                   | MAX  | UNITS |

|------------------------------------|--------------------|------------------------------------------------|----------------------|-----------------------|------|-------|

| GATE DRIVERS                       |                    |                                                |                      |                       |      |       |

| DH1, DH2 Gate-Driver               | Pon(pu)            | BST LX_ forced to                              | Low state (pulldown) |                       | 4.5  | Ω     |

| On-Resistance                      | Ron(DH)            | 5V                                             | High state (pullup)  |                       | 4.0  | 22    |

| DL1, DL2 Gate-Driver               | Dow/D/             | High state (pullup)                            |                      |                       | 3    | Ω     |

| On-Resistance                      | Ron(DL)            | Low state (pulldown)                           |                      |                       | 2.5  | 22    |

| Driver Propagation Delay           |                    | DH_ low to DL high                             |                      | 8                     | 42   | ns    |

| Driver Propagation Delay           |                    | DL_ low to DH high                             |                      | 12                    | 48   | 115   |

| Internal BST_ Switch On-Resistance | R <sub>BST</sub> _ | I <sub>BST_</sub> = 10mA, V <sub>DD</sub> = 5V |                      |                       | 12   | Ω     |

| INPUTS AND OUTPUTS                 |                    |                                                |                      |                       |      |       |

| EN1, EN2 Logic-Input Threshold     |                    | EN1, EN2 rising edge<br>hysteresis = 300mV/6   | ·                    | 1.20                  | 2.20 | V     |

|                                    |                    |                                                | High (5V)            | V <sub>CC</sub> - 0.3 |      |       |

| Quad-Level Input Logic Levels      |                    | SKIP, ILIM1, ILIM2                             | Open (3.3V)          | 3.0                   | 3.6  | V     |

|                                    |                    |                                                | Ref (2.0V)           | 1.7                   | 2.3  |       |

|                                    |                    |                                                | Low (GND)            |                       | 0.4  |       |

Note 1: On-time and off-time specifications are measured from 50% point to 50% point at the DH pin with LX = GND, V<sub>BST</sub> = 5V, and a 250pF capacitor connected from DH to LX. Actual in-circuit times might differ due to MOSFET switching speeds.

Note 2: The 0 to 0.5V range is guaranteed by design, not production tested.

Note 3: Not production tested.

**Note 4:** Specifications at T<sub>A</sub> = -40°C to +105°C are guaranteed by design, not production tested.

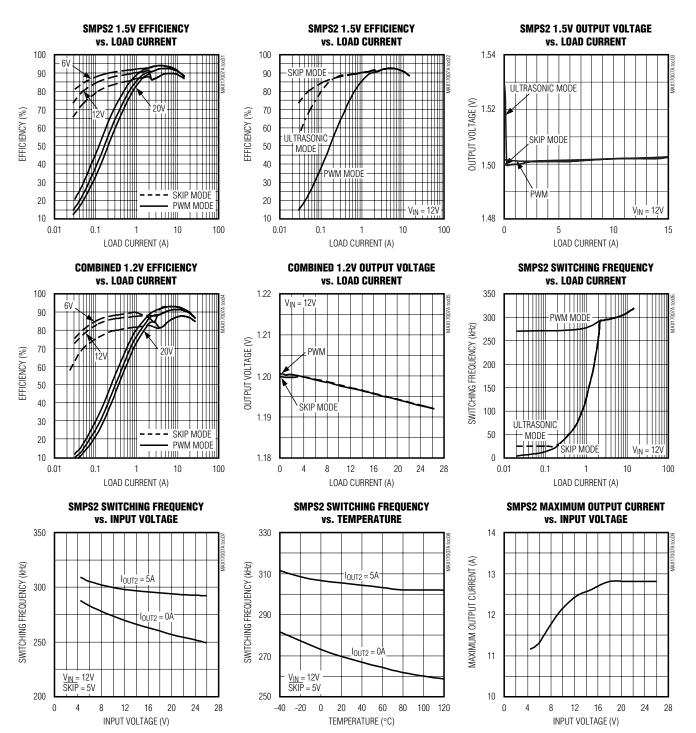

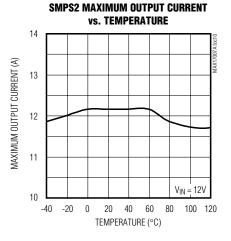

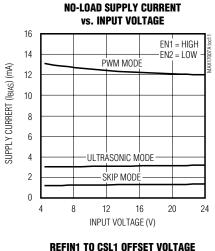

#### **Typical Operating Characteristics**

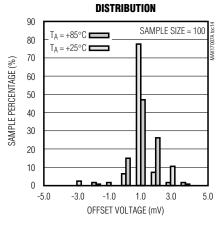

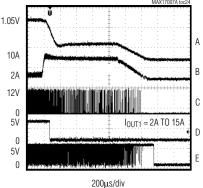

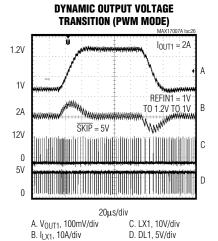

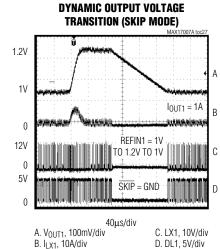

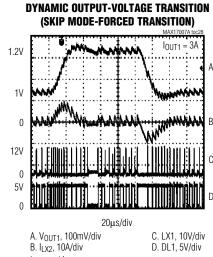

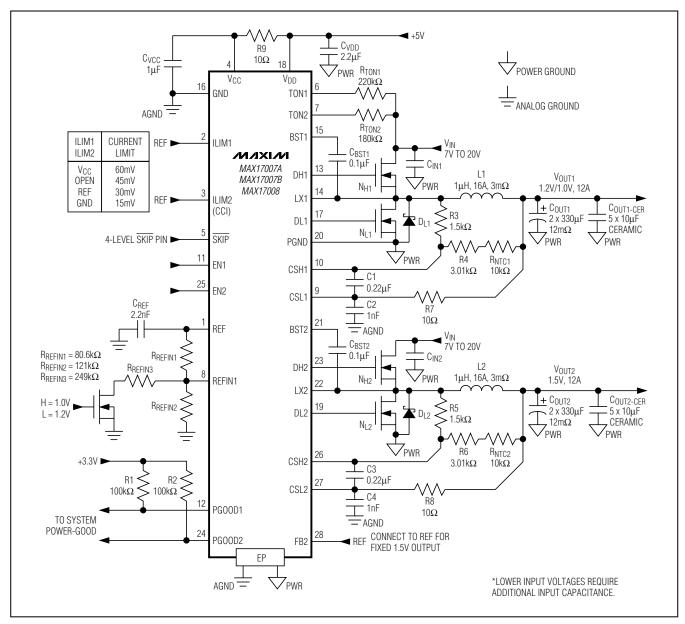

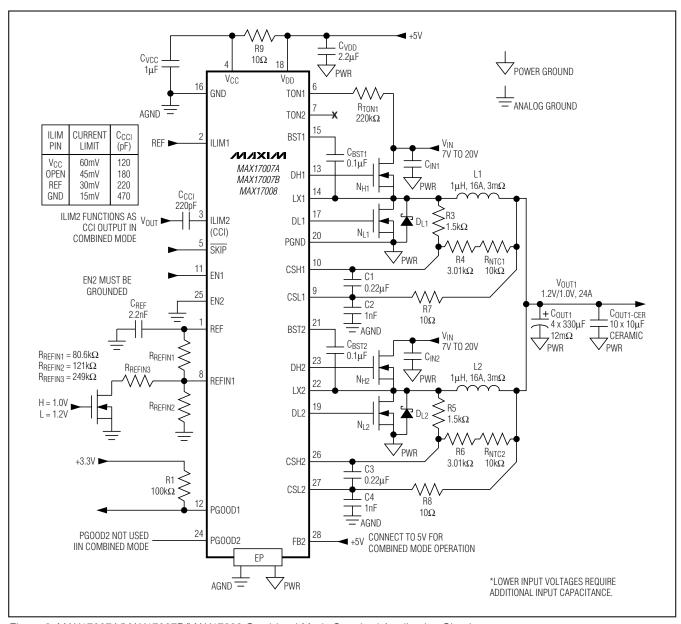

(Circuit of Figure 1, V<sub>IN</sub> = 12V, V<sub>DD</sub> = 5V, SKIP = GND, T<sub>A</sub> = +25°C, unless otherwise noted.)

#### Typical Operating Characteristics (continued)

(Circuit of Figure 1, V<sub>IN</sub> = 12V, V<sub>DD</sub> = 5V, SKIP = GND, T<sub>A</sub> = +25°C, unless otherwise noted.)

#### **Typical Operating Characteristics (continued)**

(Circuit of Figure 1,  $V_{IN} = 12V$ ,  $V_{DD} = 5V$ ,  $\overline{SKIP} = GND$ ,  $T_A = +25$ °C, unless otherwise noted.)

A. EN1, 5V/div E. PG00D1, 10V/div

B. REF, 2V/div F. LX1, 10V/div

C. V<sub>0UT1</sub>, 500mV/div G. DL1, 10V/div

D. I<sub>LX1</sub>, 10A/div

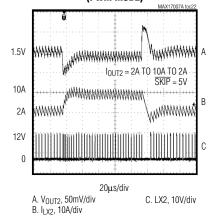

### SMPS2 LOAD-TRANSIENT RESPONSE (PWM MODE)

#### SMPS1 STARTUP WAVEFORM (LIGHT LOAD)

A. EN1, 5V/div E. PG00D1, 10V/div B. REF, 2V/div F. LX1, 10V/div C. V<sub>0UT1</sub>, 500mV/div G. DL1, 10V/div D. I<sub>LX1</sub>, 5A/div

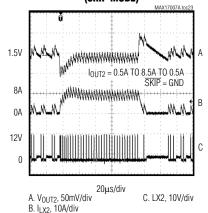

#### SMPS2 LOAD-TRANSIENT RESPONSE (SKIP MODE)

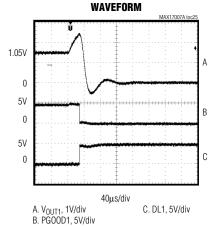

SMPS1 OUTPUT OVERVOLTAGE

# SMP\$1 SHUTDOWN WAVEFORM MAX17007A loc21 A A B C O O O 12V O 12V O SKIP = GND SV G G

A. EN1, 5V/div E. PG00D1, 10V/div B. REF, 5V/div F. LX1, 10V/div C. V<sub>0UT1</sub>, 500mV/div D. I<sub>LX1</sub>, 5A/div

#### SMPS1 OUTPUT OVERLOAD WAVEFORM

A. V<sub>OUT1</sub>, 500mV/div D. PG00D1, 5V/div B. I<sub>LX1</sub>, 10A/div E. DL1, 5V/div C. LX1, 10V/div

#### Typical Operating Characteristics (continued)

(Circuit of Figure 1, V<sub>IN</sub> = 12V, V<sub>DD</sub> = 5V, SKIP = GND, T<sub>A</sub> = +25°C, unless otherwise noted.)

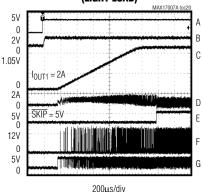

B. I<sub>LX2</sub>, 10A/div I<sub>OUT1</sub> = 1A REFIN1 = 1V TO 1.2V TO 1V SKIP = REF

#### **Pin Description**

| PIN | NAME           | FUN                                                                                                                               | ICTION                                                                                                                                                                                                                                                                                                                    |  |  |  |

|-----|----------------|-----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|