19-5132; Rev 1; 3/10

EVALUATION KIT AVAILABLE

# 76V, 300mW Boost Converter and Current Monitor for APD Bias Applications

## **General Description**

The MAX15059 constant-frequency pulse-width modulating (PWM) step-up DC-DC converter features an internal switch and a high-side current monitor with highspeed adjustable current limiting. This device is capable of generating output voltages up to 76V (300mW for the MAX15059A and 200mW for the MAX15059B) and provides current monitoring up to 4mA. The MAX15059 operates from 2.8V to 5.5V.

The constant-frequency (400kHz) current-mode PWM architecture provides low-noise-output voltage that is easy to filter. A high-voltage internal power MOSFET allows this device to boost output voltages up to 76V. Internal soft-start circuitry limits the input current when the boost converter starts. The MAX15059 features a shutdown mode to save power.

The MAX15059 includes a current monitor with more than three decades of dynamic range and monitors current ranging from 500nA to 4mA with high accuracy. Resistor-adjustable current limiting protects the APD from optical power transients. A clamp diode protects the monitor's output from overvoltage conditions. Other protection features include cycle-by-cycle current limiting of the boost converter switch, undervoltage lockout (UVLO), and thermal shutdown if the die temperature reaches +150°C.

The MAX15059 is available in a thermally enhanced, lead-free, 16-pin TQFN-EP package and operates over the -40°C to +85°C temperature range.

Avalanche Photodiode Biasing and Monitoring PIN Diode Bias Supply Low-Noise Varactor Diode Bias Supply FBON Modules GPON Modules

**Applications**

## **\_Features**

- ♦ Input Voltage Range: +2.8V to +5.5V

- Wide Output-Voltage Range from (VIN + 5V) to 76V

- Internal 1Ω (typ) 80V MOSFET

- Boost Converter Output Power: 300mW

- 200mW Version Available for Smaller Inductor

- Accurate ±5% (1:1 and 5:1) High-Side Current Monitor

- Resistor-Adjustable Ultra-Fast APD Current Limit (1µs Response Time)

- Open-Drain Current-Limit Indicator Flag

- ♦ 400kHz Fixed-Switching Frequency

- Constant PWM Frequency Provides Easy Filtering in Low-Noise Applications

- Internal Soft-Start

- ♦ 2µA (max) Shutdown Current

- ♦ -40°C to +85°C Temperature Range

- Small, Thermally Enhanced, 3mm x 3mm, Lead-Free, 16-Pin TQFN-EP Package

## **Ordering Information**

| PART          | MAXIMUM<br>POWER<br>(mW) | I <sub>APD</sub> :<br>Imout | PIN-<br>PACKAGE |

|---------------|--------------------------|-----------------------------|-----------------|

| MAX15059AETE+ | 300                      | 1:1                         | 16 TQFN-EP*     |

| MAX15059BETE+ | 200                      | 5:1                         | 16 TQFN-EP*     |

**Note:** All devices operate over the -40°C to +85°C temperature range.

+Denotes a lead(Pb)-free/RoHS-compliant package. \*EP = Exposed pad.

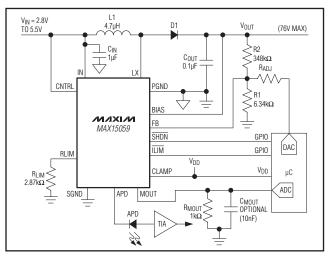

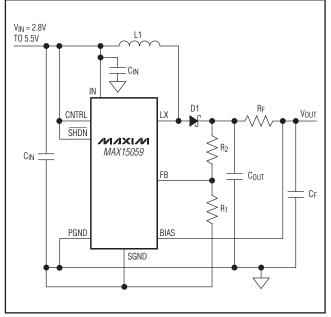

# \_Typical Operating Circuit

###

Maxim Integrated Products 1

res 5 76V

MAX15059

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-DataSheet4U.com or visit Maxim's website at www.maxim-ic.com.

# MAX15059

## **ABSOLUTE MAXIMUM RATINGS**

| IN, SHDN, FB, ILIM, RLIM, CNTRL to SGND0.3V to +6V    |

|-------------------------------------------------------|

| LX to PGND0.3V to +80V                                |

| BIAS to SGND0.3V to +79V                              |

| APD, CLAMP to SGND0.3V to (VBIAS + 0.3V)              |

| PGND to SGND0.3V to +0.3V                             |

| MOUT to SGND0.3V to (VCLAMP + 0.3V)                   |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |

| 16-Pin TQFN-EP (derate 20.8mW/°C                      |

| above +70°C)                                          |

| Junction-to-Case Thermal Resistance ( $\theta_{JC}$ ) (N | lote 1)         |

|----------------------------------------------------------|-----------------|

| 16-Pin TQFN-EP                                           | +7°C/W          |

| Junction-to-Ambient Thermal Resistance (0JA)             | ) (Note 1)      |

| 16-Pin TQFN-EP                                           | +48°C/W         |

| Operating Temperature Range                              | 40°C to +85°C   |

| Maximum Junction Temperature                             | +150°C          |

| Storage Temperature Range                                | -65°C to +150°C |

| Lead Temperature (soldering, 10s)                        | +300°C          |

| Soldering Temperature (reflow)                           | +260°C          |

Note 1: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a fourlayer board. For detailed information on package thermal considerations, refer to <u>www.maxim-ic.com/thermal-tutorial</u>.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **ELECTRICAL CHARACTERISTICS**

$(V_{IN} = V_{SHDN} = V_{CNTRL} = 3.3V, C_{IN} = 1\mu F, V_{PGND} = V_{SGND} = 0V, V_{BIAS} = 40V, LX = APD = CLAMP = \overline{ILIM}$  = unconnected, V<sub>MOUT</sub> = V<sub>RLIM</sub> = 0V, T<sub>A</sub> = -40°C to +85°C, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.) (Note 2)

| PARAMETER                              | SYMBOL     | CONDITIONS                                      | MIN     | TYP  | MAX    | UNITS |

|----------------------------------------|------------|-------------------------------------------------|---------|------|--------|-------|

| INPUT SUPPLY                           |            |                                                 | ·       |      |        |       |

| Supply Voltage Range                   | Vin        |                                                 | 2.8     |      | 5.5    | V     |

| Supply Current                         | ISUPPLY    | V <sub>FB</sub> = 1.4V, no switching            |         | 1    | 1.2    | mA    |

| Undervoltage-Lockout Threshold         | Vuvlo      | V <sub>IN</sub> rising                          | 2.475   | 2.6  | 2.775  | V     |

| Undervoltage-Lockout Hysteresis        | VUVLO_HYS  |                                                 |         | 200  |        | mV    |

| Shutdown Current                       | ISHDN      | VSHDN = 0V                                      |         |      | 2      | μA    |

| Shutdown BIAS Current                  | IBIAS_SHDN | $V_{BIAS} = 3.3V, V_{\overline{SHDN}} = 0V$     |         |      | 20     | μA    |

| BOOST CONVERTER                        |            |                                                 |         |      |        |       |

| Output-Voltage Adjustment<br>Range     |            |                                                 | VIN + 5 |      | 76     | V     |

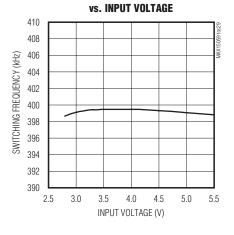

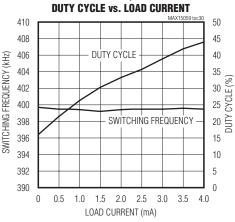

| Switching Frequency                    | fsw        | $V_{IN} = 5V$                                   | 380     | 400  | 420    | kHz   |

| Maximum Duty Cycle                     | DCLK       | $V_{IN} = 2.8V$                                 | 88      | 90   | 92     | %     |

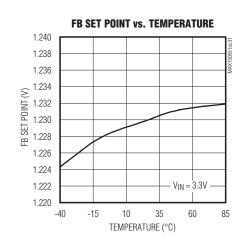

| FB Set-Point Voltage                   | VFB_SET    |                                                 | 1.2054  | 1.23 | 1.2546 | V     |

| FB Input-Bias Current                  | IFB        | $V_{FB} = V_{FB}_{SET}, T_A = +25^{\circ}C$     |         |      | 500    | nA    |

| Internal Switch On-Resistance          | Ron        | ILX = 100mA, VIN = 2.8V                         |         | 1    | 2      | Ω     |

| Peak Switch Current Limit              | hundred    | MAX15059A                                       | 1.1     | 1.2  | 1.3    | - A   |

| Peak Switch Current Limit              | ILIM_LX    | MAX15059B                                       | 0.825   | 0.9  | 0.975  |       |

| Peak Current-Limit Response            |            |                                                 |         | 100  |        | ns    |

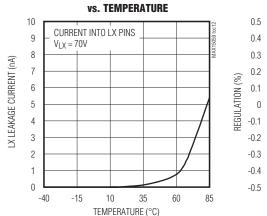

| LX Leakage Current                     |            | $V_{LX} = 76V, T_A = +25^{\circ}C$              |         |      | 1      | μA    |

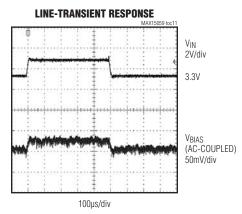

| Line Regulation                        |            | $2.8V \le V_{IN} \le 5.5V$ , $I_{LOAD} = 4.5mA$ |         | 0.2  |        | %     |

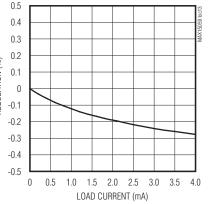

| Load Regulation                        |            | $0 \le I_{LOAD} \le 4.5 mA$                     |         | 1    |        | %     |

| Soft-Start Duration                    |            |                                                 |         | 8    |        | ms    |

| Soft-Start Steps                       |            |                                                 |         | 32   |        | Steps |

| CONTROL INPUT (CNTRL)                  |            |                                                 |         |      |        |       |

| Maximum Control Input Voltage<br>Range |            | FB set point is controlled to VCNTRL            |         | 1.2  |        | V     |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(VIN = VSHDN = VCNTRL = 3.3V, CIN = 1\muF, VPGND = VSGND = 0V, VBIAS = 40V, LX = APD = CLAMP = ILIM = unconnected, VMOUT = 0V, T_A = -40^{\circ}C to +85^{\circ}C$ , unless otherwise noted. Typical values are at T\_A = +25^{\circ}C.) (Note 2)

| PARAMETER                            | SYMBOL            | CONDITIONS                                                                                                                    |                          | MIN                        | ΤΥΡ  | MAX   | UNITS   |

|--------------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------|--------------------------|----------------------------|------|-------|---------|

| CNTRL-to-REF Transition<br>Threshold |                   | VFB = VREF above this voltage                                                                                                 |                          |                            | 1.3  |       | V       |

| CNTRL Input-Bias Current             |                   | VCNTRL = VFB_SET, TA = +25°                                                                                                   | °C                       |                            |      | 500   | nA      |

| CURRENT MONITOR                      |                   | ^<br>                                                                                                                         |                          |                            |      |       |         |

| Bias Voltage Range                   | VBIAS             |                                                                                                                               |                          | 10                         |      | 76    | V       |

|                                      |                   | L                                                                                                                             | MAX15059A                |                            | 150  | 250   |         |

|                                      | 1                 | $I_{APD} = 500nA$                                                                                                             | MAX15059B                |                            | 150  | 250   | - μΑ    |

| Bias Quiescent Current               | IBIAS             |                                                                                                                               | MAX15059A                |                            | 4    | 6     |         |

|                                      |                   | $I_{APD} = 2mA$                                                                                                               | MAX15059B                |                            | 3    | 4     | mA      |

| Voltage Drop                         | Vdrop             | IAPD = 2mA, VDROP = VBIAS -                                                                                                   | VAPD                     |                            | 2.7  | 3.5   | V       |

| Dynamic Output Resistance at<br>MOUT | RMOUT             | $R_{MOUT} = \Delta V_{MOUT} / \Delta I_{MOUT},$<br>$I_{APD} = 2.5 mA$                                                         | MAX15059A                |                            | 5    |       | GΩ      |

| APD Current-Step Response            |                   | Step load on IAPD = 20µA to 1                                                                                                 | mA                       |                            | 25   |       | ns      |

| MOUT Output Leakage                  |                   |                                                                                                                               |                          |                            | 1    |       | nA      |

| Output Clamp Voltage                 | Vmout -<br>Vclamp | Forward diode current = 500µ                                                                                                  | A                        | 0.45                       | 0.7  | 0.95  | V       |

| Output Clamp Leakage Current         |                   | VBIAS = VCLAMP = 76V                                                                                                          |                          |                            | 1    |       | nA      |

| MOUT Voltage Range                   | Vmout             | $10V \le V_{BIAS} \le 76V$ , $0 \le I_{APD} \le 1$ mA, CLAMP is unconnected                                                   |                          | V <sub>BIAS</sub> -<br>2.7 |      |       | V       |

|                                      | IMOUT/IAPD        | IAPD = 500nA                                                                                                                  | MAX15059A                | 0.95                       | 1    | 1.1   | – mA/mA |

|                                      |                   |                                                                                                                               | MAX15059B                | 0.19                       | 0.2  | 0.22  |         |

| Current Gain                         |                   | IAPD = 2mA                                                                                                                    | MAX15059A                | 0.965                      | 1    | 1.035 |         |

|                                      |                   |                                                                                                                               | MAX15059B                | 0.193                      | 0.2  | 0.207 |         |

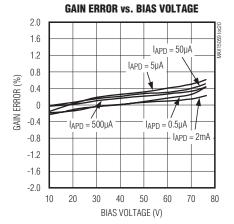

| Power Supply Paiastian Patia         | PSRR              | $(\Delta I_{MOUT}/I_{MOUT})/\Delta V_{BIAS},$<br>V <sub>BIAS</sub> = 10V to 76V and I <sub>APD</sub><br>= 5µA to 1mA (Note 3) | MAX15059A                | 35                         | 300  | 610   | ppm/V   |

| Power-Supply Rejection Ratio         |                   |                                                                                                                               | MAX15059B                | 35                         | 300  | 700   |         |

| APD Input Current Limit              | ILIM_APD          |                                                                                                                               |                          | 4                          | 4.6  | 5.2   | mA      |

| Current-Limit Adjustment Range       |                   | $9.75k\Omega \ge R_{LIM} \ge 0$                                                                                               |                          | 0.9                        |      | 5.2   | mA      |

| Power-Up Settling Time               | Sottling Time to  | I <sub>MOUT</sub> settles to within 0.1%, 10nF connected from APD to                                                          | I <sub>APD</sub> = 500nA |                            | 7.5  |       | ms      |

| Tower-op Setting Time                | ts                | ground                                                                                                                        | $I_{APD} = 2.5 mA$       |                            | 90   |       | μs      |

| LOGIC I/O                            |                   |                                                                                                                               |                          |                            |      |       |         |

| SHDN Input Voltage Low               | VIL               |                                                                                                                               |                          |                            |      | 0.8   | V       |

| SHDN Input Voltage High              | VIH               |                                                                                                                               |                          | 2.1                        |      |       | V       |

| ILIM Output Voltage Low              | Vol               | ILIM = 2mA                                                                                                                    |                          |                            |      | 0.1   | V       |

| ILIM Output Leakage Current          | Іон               | $T_A = +25^{\circ}C$                                                                                                          |                          |                            |      | 1     | μA      |

| THERMAL PROTECTION                   |                   |                                                                                                                               |                          |                            |      |       |         |

| Thermal-Shutdown Temperature         |                   | Temperature rising                                                                                                            |                          |                            | +150 |       | °C      |

| Thermal-Shutdown Hysteresis          |                   |                                                                                                                               |                          |                            | 15   |       | °C      |

**Note 2:** All MIN/MAX parameters are tested at  $T_A = +25^{\circ}C$ . Limits overtemperature are guaranteed by design.

Note 3: Guaranteed by design and not production tested.

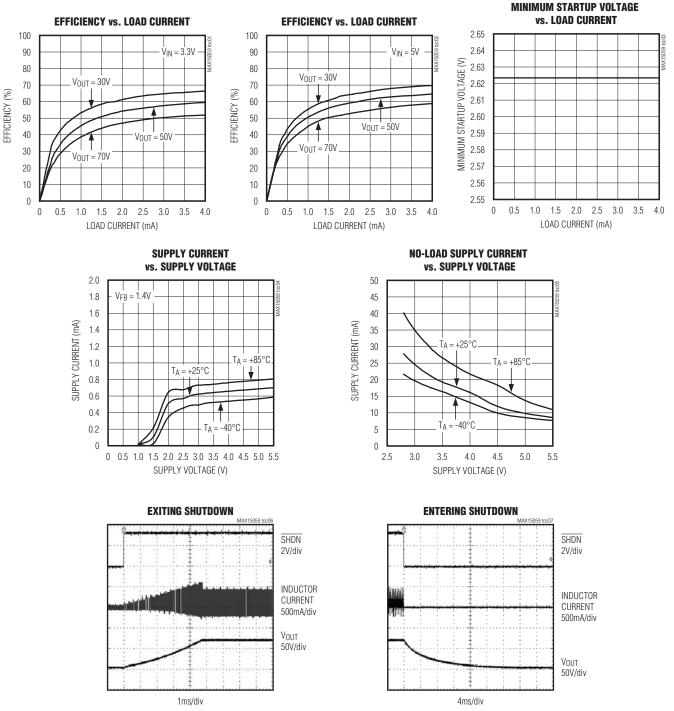

(VIN = 3.3V, V<sub>OUT</sub> = 70V,  $T_A$  = +25°C, unless otherwise noted.)

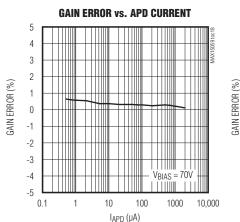

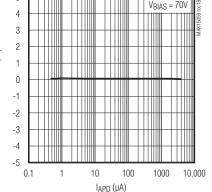

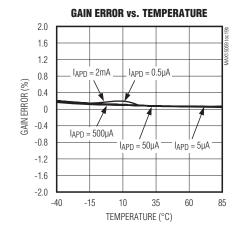

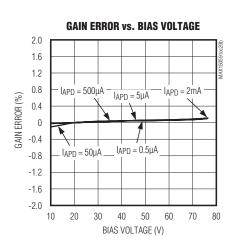

## **Typical Operating Characteristics**

$(V_{IN} = 3.3V, V_{OUT} = 70V, T_A = +25^{\circ}C, unless otherwise noted.)$

M/IXI/M

LX LEAKAGE CURRENT

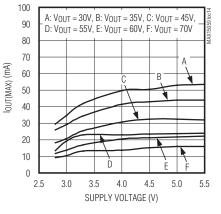

#### MAXIMUM LOAD CURRENT vs. SUPPLY VOLTAGE

#### **BIAS CURRENT vs. BIAS VOLTAGE BIAS CURRENT vs. APD CURRENT BIAS CURRENT vs. TEMPERATURE** 10 10 IAPD = 2mA BIAS CURRENT (mA) BIAS CURRENT (mA) 1 APD = 2m1 0.1 I<sub>APD</sub> = 500nA $I_{APD} = 500nA$ VRIAS = 70V 0.01 0.1 10 20 70 0 30 40 50 60 80 0.0001 0.001 0.01 0.1 10 -40 -15 10 35 60 85 1 BIAS VOLTAGE (V) APD CURRENT (mA) TEMPERATURE (°C) **GAIN ERROR vs. APD CURRENT GAIN ERROR vs. APD CURRENT GAIN ERROR vs. TEMPERATURE** 2.0 5 VBIAS = 70V 4 1.6 $I_{APD} = 0.5 \mu A$ 3 1.2 l<sub>APD</sub> = 5μÅ I<sub>APD</sub> = 50µA 2 0.8 GAIN ERROR (%)

#### -40 TEMPERATURE (°C)

0.4

0

-0.4

-0.8

-1.2

-16

-2.0

$I_{APD} = 500 \mu A$

-15

10

35

APD = 2mA

60

85

M/X/M www.DataSheet4U.com

**MAX15059**

10

1

0.1

0.01

BIAS CURRENT (mA)

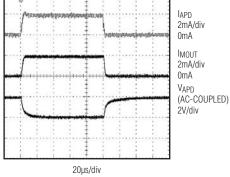

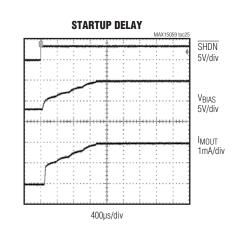

# **Typical Operating Characteristics (continued)**

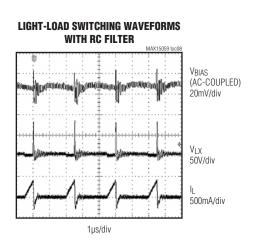

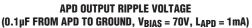

( $V_{IN} = 3.3V$ ,  $V_{OUT} = 70V$ ,  $T_A = +25^{\circ}C$ , unless otherwise noted.)

**Typical Operating Characteristics (continued)**

**APD TRANSIENT RESPONSE**

( $V_{IN} = 3.3V$ ,  $V_{OUT} = 70V$ ,  $T_A = +25^{\circ}C$ , unless otherwise noted.)

2ms/div

**STARTUP DELAY**

200µs/div

I<sub>MOUT</sub> 500nA/div

SHDN

5V/div

V<sub>BIAS</sub> 5V/div

I<sub>MOUT</sub> 500nA/div

$V_{BIAS} = 70V,$

$\begin{array}{l} V_{BIAS}=10V,\\ I_{APD}=500nA \end{array}$

IAPD = 500nA

Ŭ

STARTUP DELAY MAXISOB Inc23 SHDN SV/div VBIAS S0V/div VBIAS S0V/div MOUT MAUT MA

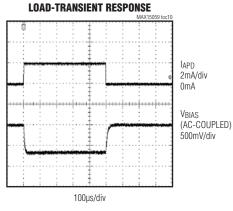

# MAX15059

SWITCHING FREQUENCY SHORT-CIRCUIT RESPONSE **VOLTAGE DROP vs. APD CURRENT** vs. TEMPERATURE 3.0 410  $R_{IIM} = 3.16 k\Omega$ 409 2.5 408 -40°C V<sub>APD</sub> 50V/div Ta = 407 2.0 FREQUENCY (kHz) VBIAS - VAPD (V) 406 МОЛТ 1.5 405 2mA/div 404 1.0  $T_{A} = +25$ 403 Ш Ta = +85°C 402 IILIM 0.5 5V/div 401 0 400 0.1 10 100 1000 10,000 -40 -15 2µs/div 1 10 35 60 85 I<sub>APD</sub> (µA) TEMPERATURE (°C)

$(V_{IN} = 3.3V, V_{OUT} = 70V, T_{A} = +25^{\circ}C, unless otherwise noted.)$

**Typical Operating Characteristics (continued)**

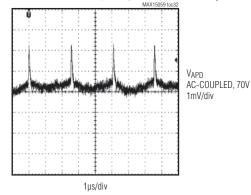

## Pin Configuration

## Pin Description

| PIN   | NAME  | FUNCTION                                                                                                                                                                                                                                                                                                       |

|-------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 16 | PGND  | Power Ground. Connect the negative terminals of the input and output capacitors to PGND. Connect PGND externally to SGND at a single point, typically at the return terminal of the output capacitor.                                                                                                          |

| 2     | IN    | Input-Supply Voltage. Bypass IN to PGND with a ceramic capacitor of 1µF minimum value.                                                                                                                                                                                                                         |

| 3     | SHDN  | Active-Low Shutdown Control Input. Apply a logic-low voltage to SHDN to shut down the device.<br>Connect SHDN to IN for normal operation. Ensure that V <sub>SHDN</sub> is not greater than the input voltage, VIN.<br>SHDN is internally pulled low. The converter is disabled when SHDN is left unconnected. |

| 4, 8  | SGND  | Signal Ground. Connect directly to the local ground plane. Connect SGND to PGND at a single point, typically near the return terminal of the output capacitor.                                                                                                                                                 |

| 5     | FB    | Feedback Regulation Input. Connect FB to the center tap of a resistive voltage-divider from the boost output to SGND to set the output voltage. The FB voltage regulates to 1.23V (typ) when VCNTRL is above 1.3V (typ) and to VCNTRL when VCNTRL is below 1.2V (typ).                                         |

| 6     | CNTRL | Control Input for Boost Converter Output-Voltage Programmability. CNTRL allows the feedback set-point voltage to be set externally by CNTRL when CNTRL is less than 1.2V. Pull CNTRL above 1.3V (typ) to use the internal 1.23V (typ) feedback set-point voltage.                                              |

| 7     | ILIM  | Open-Drain Current-Limit Indicator. ILIM asserts low when the APD current limit has been exceeded.                                                                                                                                                                                                             |

| 9     | RLIM  | Current-Limit Resistor Connection. Connect a resistor from RLIM to SGND to program the APD current-<br>limit threshold. When RLIM is connected to SGND, the current limit is set to 4.6mA.                                                                                                                     |

| 10    | MOUT  | Current-Monitor Output. For the MAX15059A, MOUT sources a current equal to IAPD. For the MAX15059B, MOUT sources a current equal to 1/5 of IAPD.                                                                                                                                                               |

| 11    | CLAMP | Clamp Voltage Input. CLAMP is the external potential used for voltage clamping of MOUT.                                                                                                                                                                                                                        |

## Pin Description (continued)

| PIN    | NAME | FUNCTION                                                                                                                                                                                                                            |

|--------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12     | APD  | Reference Current Output. APD provides the source current to the cathode of the photodiode.                                                                                                                                         |

| 13     | BIAS | Bias-Voltage Input. Connect BIAS to the boost converter output (VOUT) either directly or through a lowpass filter for ripple attenuation. BIAS provides the voltage bias for the current monitor and is the current source for APD. |

| 14, 15 | LX   | Drain of Internal 80V n-Channel DMOS. Connect inductor to LX. Minimize the trace area at LX to reduce switching-noise emission.                                                                                                     |

| _      | EP   | Exposed Paddle. Connect to a large copper plane at the SGND and PGND potential to improve thermal dissipation. Do not use as the only ground connection.                                                                            |

# **Functional Diagram**

#### Shutdown The MAX15059 features an active-low shutdown input (SHDN). Pull SHDN low or leave it unconnected to enter shutdown. During shutdown, the supply current drops to 2µA (max). The output remains connected to the input through the inductor and output rectifier, holding

**Current Limit**

(MOUT)

MAX15059

The current limit of the current monitor is programmable from 1mA to 4.6mA (typ). Connect RLIM to SGND to get a default current-limit threshold of 4.6mA or connect a resistor from RLIM to SGND to program the current-limit threshold below the default setting of 4.6mA. Calculate the value of the external resistor, RLIM, for a given current limit, ILIM, using the following equation:

$\mathsf{R}_{\mathsf{LIM}}(\mathsf{k}\Omega) = \left[ \left( \frac{1.23\mathsf{V}}{\mathsf{I}_{\mathsf{I}|\mathsf{IM}}(\mathsf{m}\mathsf{A})} \right) \times 10 - 2.67(\mathsf{k}\Omega) \right]$

CLAMP provides a means for diode clamping the volt-

age at MOUT; thus, VMOUT is limited to (VCLAMP + 0.6V).

CLAMP can be connected to either an external supply or

BIAS. Leave CLAMP unconnected if voltage clamping is

**Clamping the Monitor Output Voltage**

The devices operate in PWM mode using a fixedfrequency, current-mode operation. The current-mode frequency loop regulates the peak inductor current as a

function of the output-voltage error signal.

The current-mode PWM controller is intended for DCM operation. No internal slope compensation is added to the current signal.

#### tion approaches ideal cycle-by-cycle control over the **Detailed Description** output voltage since there is no conventional error amplifier in the feedback pa

76V, 300mW Boost Converter and Current

not required.

Monitor for APD Bias Applications

The MAX15059 constant-frequency, current-mode, PWM boost converters are intended for low-voltage systems that require a locally generated high voltage. These devices are capable of generating a low-noise, high output voltage required for PIN and varactor diode biasing. The MAX15059 operates from +2.8V to +5.5V.

The MAX15059 operates in discontinuous mode in order to reduce the switching noise caused by reverse recovery charge of the rectifier diode and eliminates the need for external compensation components. Other continuous-mode boost converters generate large voltage spikes at the output when the LX switch turns on because there is a conduction path between the output, diode, and switch to ground during the time needed for the diode to turn off and reverse its bias voltage. To reduce the output noise even further, the LX switch turns off by taking 10ns typically to transition from on to off. As a consequence, the positive slew rate of the LX node is reduced and the current from the inductor does not "force" the output voltage as hard as would be the case if the LX switch were to turn off faster.

The constant-frequency (400kHz) PWM architecture generates an output voltage ripple that is easy to filter. An 80V lateral DMOS device used as the internal power switch is ideal for boost converters with output voltages up to 76V. The MAX15059 can also be used in other topologies where the PWM switch is grounded, like SEPIC and flyback converters.

The MAX15059 includes a versatile current monitor intended for monitoring the APD, PIN, or varactor diode DC current in fiber and other applications. The MAX15059 features more than three decades of dynamic current ranging from 500nA to 4mA and provides an output current accurately proportional to the APD current at MOUT. MOUT output accuracy is ±10% from 500nA to 1mA and  $\pm 5\%$  from 1mA to 2mA.

The MAX15059 also features a shutdown logic input to disable the device and reduce its standby current to 2µA (max).

### **Fixed-Frequency PWM Controller**

The heart of the MAX15059 current-mode PWM controller is a BiCMOS multi-input comparator that simultaneously processes the output-error signal and switch current signal. The main PWM comparator uses direct summing, lacking a traditional error amplifier and its associated phase shift. The direct summing configura-

/VI/XI/VI

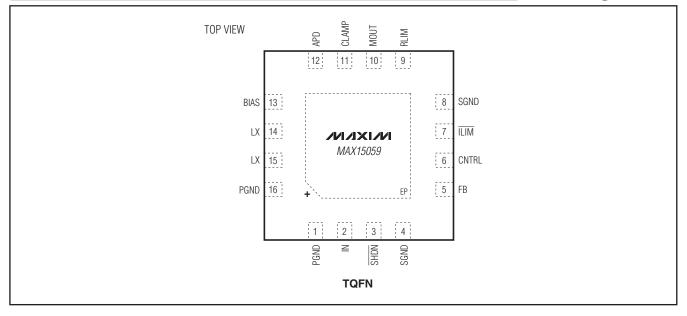

always-on operation. Adjusting the Feedback Set-Point/Reference Voltage Apply a voltage to the CNTRL input to set the feedback set-point reference voltage, VREF (see the Functional

the output voltage to one diode drop below IN when

the MAX15059 is in shutdown. Connect SHDN to IN for

Diagram). For VCNTRL > 1.3V, the internal 1.23V (typ) reference voltage is used as the feedback set point and for  $V_{CNTRL} < 1.2V$ , the CNTRL voltage is used as the reference voltage (VFB set equal to VCNTRL).

www.DataSheet4U.com

**AX15059**

# \_Design Procedure

#### Setting the Output Voltage

Set the MAX15059 output voltage by connecting a resistive divider from the output to FB to SGND (Figure 1). Select R<sub>1</sub> (FB to SGND resistor) between 5k $\Omega$  and 10k $\Omega$ . Calculate R<sub>2</sub> (V<sub>OUT</sub> to FB resistor) using the following equation:

$$R_{2} = R_{1} \left[ \left( \frac{V_{OUT}}{V_{REF}} \right) - 1 \right]$$

where V<sub>OUT</sub> can range from (V<sub>IN</sub> + 5V) to 76V. Apply a voltage to the CNTRL input to set the feedback set-point reference voltage, V<sub>REF</sub> (see the *Functional Diagram*). For V<sub>CNTRL</sub> > 1.3V, the internal 1.23 (typ) reference voltage is used as the feedback set point and for V<sub>CNTRL</sub> < 1.2V, V<sub>REF</sub> = V<sub>CNTRL</sub>. See the *Adjusting the Feedback Set-Point/Reference Voltage* section for more information on adjusting the feedback reference voltage, V<sub>REF</sub>.

#### **Determining Peak Inductor Current**

If the boost converter remains in the discontinuous mode of operation, then the approximate peak inductor current, ILPEAK (in A), is represented by the formula below:

$$I_{LPEAK} = \sqrt{\frac{2 \times t_{S} \times (V_{OUT} - V_{IN}MIN) \times I_{OUT}MAX}{\eta \times L}}$$

where ts is the switching period in  $\mu$ s, V<sub>OUT</sub> is the output voltage in volts, V<sub>IN\_MIN</sub> is the minimum input voltage in volts, I<sub>OUT\_MAX</sub> is the maximum output current in amps, L is the inductor value in  $\mu$ H, and  $\eta$  is the efficiency of the boost converter (see the *Typical Operating Characteristics*).

Figure 1. Adjustable Output Voltage

#### **Determining the Inductor Value**

Three key inductor parameters must be specified for operation with the MAX15059: inductance value (L), inductor saturation current (I<sub>SAT</sub>), and DC resistance (DCR). In general, the inductor should have a saturation current rating greater than the maximum peak switch current-limit value ( $I_{LIM_LX} = 1.3A$ ). DC series resistance (DCR) should be be low for reasonable efficiency.

Use the following formula to calculate the lower bound of the inductor value at different output voltages and output currents. This is the minimum inductance value for discontinuous mode operation for supplying full 300mW of output power:

$$L_{MIN}[\mu H] = \frac{2 \times t_{S} \times I_{OUT} \times (V_{OUT} - V_{IN}MIN)}{\eta \times I_{LIM}^{2}}$$

where VIN\_MIN, VOUT (both in volts), and IOUT (in amps) are typical values (so that efficiency is optimum for typical conditions), ts (in  $\mu$ s) is the period,  $\eta$  is the efficiency, and ILIM\_LX is the peak switch current in amps (see the *Electrical Characteristics* table).

Calculate the optimum value of L (LOPTIMUM) to ensure the full output power without reaching the boundary between continuous-conduction mode (CCM) and discontinuous-conduction mode (DCM) using the following formula:

$$L_{OPTIMUM}[\mu H] = \frac{L_{MAX}[\mu H]}{2.25}$$

where:

$$L_{MAX}[\mu H] = \frac{V_{IN}^{2} (V_{OUT} - V_{IN}MIN) \times t_{S} \times \eta}{2 \times I_{OUT} \times V_{OUT}^{2}}$$

For a design in which VIN = 3.3V, VOUT = 70V, IOUT = 3mA,  $\eta$  = 45%, ILIM\_LX = 1.2A, and ts = 2.5µs: LMAX = 27µH and LMIN = 1.5µH.

For a worse-case scenario in which V<sub>IN</sub> = 2.8V, V<sub>OUT</sub> = 70V, I<sub>OUT</sub> = 4mA,  $\eta$  = 43%, I<sub>LIM\_LX</sub> = 1.2A, and ts = 2.5µs: L<sub>MAX</sub> = 15µH and L<sub>MIN</sub> = 2.2µH.

The choice of  $4.7\mu$ H is reasonable given the worst-case scenario above. In general, the higher the inductance, the lower the switching noise. Load regulation is also better with higher inductance.

**MAX15059**

# 76V, 300mW Boost Converter and Current Monitor for APD Bias Applications

#### **Diode Selection**

The MAX15059's high switching frequency demands a high-speed rectifier. Schottky diodes are recommended for most applications because of their fast recovery time and low forward-voltage drop. Ensure that the diode's peak current rating is greater than the peak inductor current. Also, the diode breakdown voltage must be greater than VOUT.

#### **Output Filter Capacitor Selection**

For most applications, use a small output capacitor of 0.1µF or greater. To achieve low output ripple, a capacitor with low ESR, low ESL, and high capacitance value should be selected. If tantalum or electrolytic capacitors are used to achieve high capacitance values, always add a smaller ceramic capacitor in parallel to bypass the high-frequency components of the diode current. The higher ESR and ESL of electrolytic capacitors increase the output ripple and peak-to-peak transient voltage. Assuming the contribution from the ESR and capacitor discharge equals 50% (proportions may vary), calculate the output capacitance and ESR required for a specified ripple using the following equations:

$$C_{OUT}[\mu F] = \frac{I_{OUT}}{0.5 \times \Delta V_{OUT}} \left[ t_{S} - \frac{I_{LPEAK} \times L_{OPTIMUM}}{(V_{OUT} - V_{IN}MIN)} \right]$$

$$ESR[m\Omega] = \frac{0.5 \times \Delta V_{OUT}}{I_{OUT}}$$

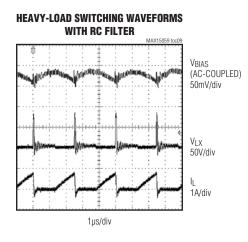

For very-low-output-ripple applications, the output of the boost converter can be followed by an RC filter to further reduce the ripple. Figure 2 shows a  $100\Omega$ ,  $0.1\mu$ F (RF CF) filter used to reduce the switching output ripple to 1mVP-P with a 0.1mA load or 1mVP-P with a 4mA load. The output voltage regulation resistive divider must remain connected to the diode/output capacitor node.

Use X7R ceramic capacitors for more stability over the full temperature range.

Figure 2. Typical Operating Circuit with RC Filter

#### **Input-Capacitor Selection**

Bypass IN to PGND with a  $1\mu$ F (min) ceramic capacitor. Depending on the supply source impedance, higher values may be needed. Make sure that the input capacitors are close enough to the IC to provide adequate decoupling at IN as well. If the layout cannot achieve this, add another 0.1 $\mu$ F ceramic capacitor between IN and PGND in the immediate vicinity of the IC. Bulk aluminum electrolytic capacitors may be needed to avoid chattering at low-input voltage. In case of aluminum electrolytic capacitors, calculate the capacitor value and ESR of the input capacitor using the following equations:

$$\begin{split} C_{IN}[\mu F] = & \frac{V_{OUT} \times I_{OUT}}{\eta \times V_{IN\_MIN} \times 0.5 \times \Delta V_{IN}} \Biggl[ t_S - \frac{I_{LPEAK} \times L_{OPTIMUM} \times V_{OUT}}{V_{IN\_MIN}(V_{OUT} - V_{IN\_MIN})} \Biggr] \\ & ESR[m\Omega] = \frac{0.5 \times \Delta V_{IN} \times \eta \times V_{IN\_MIN}}{V_{OUT} \times I_{OUT}} \end{split}$$

### Applications Information Using APD or PIN Photodiodes in Fiber Applications

When using the MAX15059 to monitor APD or PIN photodiode currents in fiber applications, several issues must be addressed. In applications where the photodiode must be fully depleted, keep track of voltages budgeted for each component with respect to the available supply voltage(s). The current monitors require as much as 3.5V between BIAS and APD, which must be considered part of the overall voltage budget.

Additional voltage margin can be created if a negative supply is used in place of a ground connection, as long as the overall voltage drop experienced by the MAX15059 is less than or equal to 76V. For this type of application, the MAX15059 is suggested so the output can be referenced to "true" ground and not the negative supply. The MAX15059's output current can be referenced as desired with either a resistor to ground or a transimpedance amplifier. Take care to ensure that output voltage excursions do not interfere with the required margin between BIAS and MOUT. In many fiber applications. MOUT is connected directly to an ADC that operates from a supply voltage that is less than the voltage at BIAS. Connecting the MAX15059's clamping diode output, CLAMP, to the ADC power supply helps avoid damage to the ADC. Without this protection, voltages can develop at MOUT that might destroy the ADC. This protection is less critical when MOUT is connected directly to subsequent transimpedance amplifiers (linear or logarithmic) that have low-impedance, near-groundreferenced inputs. If a transimpedance amp is used on the low side of the photodiode, its voltage drop must also be considered. Leakage from the clamping diode is most often insignificant over nominal operating conditions, but grows with temperature.

To maintain low levels of wideband noise, lowpass filtering the output signal is suggested in applications where only DC measurements are required. Connect the filter capacitor at MOUT. Determining the required filtering components is straightforward, as the MAX15059 exhibits a very high output impedance of  $5G\Omega$ . In some applications where pilot tones are used to identify specific fiber channels, higher bandwidths are desired at MOUT to detect these tones. Consider the minimum and maximum currents to be detected, then consult the frequency response and noise typical operating curves. If the minimum current is too small, insufficient bandwidth could result, while too high a current could result in excessive noise across the desired bandwidth.

#### **Layout Considerations**

Careful PCB layout is critical to achieve low switching losses and clean and stable operation. Protect sensitive analog grounds by using a star ground configuration. Connect SGND and PGND together close to the device at the return terminal of the output bypass capacitor. Do not connect them together anywhere else. Keep all PCB traces as short as possible to reduce stray capacitance, trace resistance, and radiated noise. Ensure that the feedback connection to FB is short and direct. Route high-speed switching nodes away from the sensitive analog areas. Use an internal PCB layer for SGND as an EMI shield to keep radiated noise away from the device, feedback dividers, and analog bypass capacitors. Refer to the MAX15059 Evaluation Kit data sheet for a layout example.

#### **Chip Information**

PROCESS: BICMOS

### **Package Information**

For the latest package outline information and land patterns, go to **www.maxim-ic.com/packages**. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE TYPE | PACKAGE CODE | DOCUMENT NO.   |

|--------------|--------------|----------------|

| 16 TQFN-EP   | T1633-4      | <u>21-0136</u> |

## **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                                        | PAGES<br>CHANGED |

|--------------------|------------------|----------------------------------------------------|------------------|

| 0                  | 1/10             | Initial release                                    | —                |

| 1                  | 3/10             | Replaced five TOCs, added three TOCs, updated text | 1, 2, 3, 5–8, 11 |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600 \_\_\_

© 2010 Maxim Integrated Products

Maxim is a registered trademark of Maxim Integrated Products, Inc. www.DataSheet4U.com

\_ 15