# Two Channel, 5kV<sub>RMS</sub> I<sup>2</sup>C Isolator

## **General Description**

The MAX14937 is a two-channel,  $5kV_{RMS}$   $I^2C$  digital isolator utilizing Maxim's proprietary process technology. For applications requiring  $2.75kV_{RMS}$  of isolation, see the MAX14933 data sheet. The device transfers digital signals between circuits with different power domains at ambient temperatures up to  $+125^{\circ}C$ .

The device offers two bidirectional, open-drain channels for applications, such as I<sup>2</sup>C, that require data to be transmitted in both directions on the same line. To prevent latch-up action, the A-side outputs comprise special buffers that regulate the logic-low voltage at 0.9V (max), and the input logic-low threshold is at least 50mV lower than the output logic-low voltage. The B side features conventional buffers that do not regulate logic-low output voltage.

The device features independent 2.25V to 5.5V supplies on each side of the isolator. The MAX14937 operates from DC to 1.7MHz and can be used in isolated  $I^2C$  busses with clock stretching.

The MAX14937 is available in a 16-pin, wide-body (10.3mm x 7.5mm) SOIC package, and is rated for operation at ambient temperatures of  $-40^{\circ}$ C to  $+125^{\circ}$ C.

## **Applications**

- I<sup>2</sup>C, SMBus, PMBus™ Interfaces

- Power Supplies

- Battery Management

- Instrumentation

#### **Benefits and Features**

- Robust Galvanic Isolation of Digital Signals

- Withstands 5kV<sub>RMS</sub> for 60s (V<sub>ISO</sub>)

- Continuously Withstands 848V<sub>RMS</sub> (V<sub>IOWM</sub>)

- 1200V<sub>PFAK</sub> Repetitive Peak Voltage (V<sub>IORM</sub>)

- Withstands ±10kV Surge per IEC 61000-4-5

- Interfaces Directly with Most Micros and FPGAs

- · Accepts 2.25V to 5.5V Supplies

- · Bidirectional Data Transfer from DC to 1.7MHz

- Low Power Consumption

- · 5.3mA per Channel Typical at 1.7MHz

#### **Safety Regulatory Approvals**

(See Safety Regulatory Approvals)

- UL According to UL1577

- · cUL According to CSA Bulletin 5A

- VDE 0884-10

Ordering Information appears at end of data sheet.

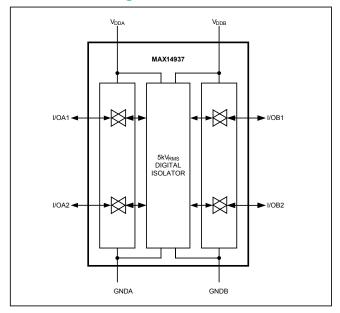

## **Functional Diagram**

PMBus is a trademark of SMIF, Inc.

## **Absolute Maximum Ratings**

| V <sub>DDA</sub> to GNDA0.3V to +      | 6V Continuous Power Dissipation (T <sub>A</sub> = +70°C) |

|----------------------------------------|----------------------------------------------------------|

| V <sub>DDB</sub> to GNDB0.3V to +      | 6V Wide SO (derate 14.1mW/°C above +70°C)1126.8mW        |

| I/OA_ to GNDA0.3V to +                 | 6V Operating Temperature Range40°C to +125°C             |

| I/OB_ to GNDB0.3V to +                 | 6V Maximum Junction Temperature+150°C                    |

| Short-Circuit Duration                 | Storage Temperature Range65°C to +150°C                  |

| (I/OA_ to GNDA, I/OB_ to GNDB)Continuo | bus Lead Temperature (soldering, 10s)+300°C              |

|                                        | Soldering Temperature (reflow)+260°C                     |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **Package Information**

#### 16 Wide SOIC

| Package Code                                              | W16M+8  |

|-----------------------------------------------------------|---------|

| Outline Number                                            | 21-0042 |

| Land Pattern Number                                       | 90-0107 |

| THERMAL RESISTANCE, FOUR-LAYER BOARD                      |         |

| Junction-to-Ambient Thermal Resistance (θ <sub>JA</sub> ) | 71°C/W  |

| Junction-to-Case Thermal Resistance $(\theta_{JC})$       | 23°C/W  |

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to www.maximintegrated.com/thermal-tutorial.

## **DC Electrical Characteristics**

$(V_{DDA}-V_{GNDA}=+2.25V\ to\ +5.5V,\ V_{DDB}-V_{GNDB}=+2.25V\ to\ +5.5V,\ T_{A}=-40^{\circ}C\ to\ +125^{\circ}C,\ unless\ otherwise\ noted.\ Typical\ values\ are\ at\ V_{DDA}-V_{GNDA}=+3.3V,\ V_{DDB}-V_{GNDB}=+3.3V,\ V_{GNDA}=V_{GNDB},\ T_{A}=+25^{\circ}C,\ unless\ otherwise\ noted.)\ (Notes\ 1\ and\ 2)$

| PARAMETER                                    | SYMBOL              | CONDITION                                                             | MIN                     | TYP                       | MAX | UNITS                     |      |

|----------------------------------------------|---------------------|-----------------------------------------------------------------------|-------------------------|---------------------------|-----|---------------------------|------|

| POWER SUPPLY                                 | •                   |                                                                       |                         | •                         |     |                           |      |

| On a mating at Community Valtages            | V <sub>DDA</sub>    | Relative to GNDA                                                      |                         | 2.25                      |     | 5.5                       | V    |

| Operating Supply Voltage                     | V <sub>DDB</sub>    | Relative to GNDB                                                      |                         | 2.25                      |     | 5.5                       | V    |

| Undervoltage-Lockout Threshold               | V <sub>UVLO</sub> _ | V <sub>DD</sub> rising                                                |                         | 1.7                       | 2.0 | 2.2                       | V    |

| Undervoltage-Lockout Threshold<br>Hysteresis | VUVLO_<br>HYST      |                                                                       |                         |                           | 85  |                           | mV   |

| Supply Current                               |                     | 0:1 4 11 1 1 10                                                       | V <sub>DDA</sub> = 5V   |                           | 6   | 9                         |      |

|                                              | IDDA                | Side A, all channels DC or 1.7MHz                                     | V <sub>DDA</sub> = 3.3V |                           | 6   | 9                         |      |

|                                              |                     | 1.71/11/12                                                            | V <sub>DDA</sub> = 2.5V |                           | 5.9 | 9                         |      |

|                                              |                     | Side B, all channels DC or 1.7MHz                                     | V <sub>DDB</sub> = 5V   |                           | 4.8 | 8                         | mA   |

|                                              | IDDB                |                                                                       | V <sub>DDB</sub> = 3.3V |                           | 4.8 | 8                         |      |

|                                              |                     |                                                                       | V <sub>DDB</sub> = 2.5V |                           | 4.7 | 8                         |      |

| Static Output Loading                        | II/OA_              | Side A                                                                |                         | 0.5                       |     | 3                         | mA   |

| Static Output Loading                        | II/OB_              | Side B                                                                |                         | 0.5                       |     | 30                        | IIIA |

| LOGIC INPUTS AND OUTPUTS                     |                     |                                                                       |                         |                           |     |                           |      |

|                                              |                     | V <sub>I/OA</sub> relative to GNDA                                    |                         | 0.7                       |     |                           |      |

| Input High Voltage                           | VIH                 | V <sub>I/OB</sub> _ relative to GNDB                                  |                         | 0.7 x<br>V <sub>DDB</sub> |     |                           | V    |

|                                              |                     | V <sub>I/OA</sub> relative to GNDA                                    |                         |                           |     | 0.5                       |      |

| Input Low Voltage                            | V <sub>IL</sub>     | V <sub>I/OB</sub> _ relative to GNDB                                  |                         |                           |     | 0.3 x<br>V <sub>DDB</sub> | V    |

| Input/Output Logic-Low Level Difference      | DV <sub>I/OL</sub>  | I <sub>/OA_</sub> (Note 3), V <sub>OL</sub> - V <sub>IL</sub>         | 50                      |                           |     | mV                        |      |

| Output Voltage Low                           |                     | V <sub>I/OA</sub> _ relative to GNDA, I <sub>I/OA</sub> _ = 3mA sink  |                         | 600                       |     | 900                       |      |

|                                              | V <sub>OL</sub>     | V <sub>I/OA</sub> relative to GNDA, I <sub>I/OA</sub> = 0.5mA sink    |                         | 600                       |     | 850                       | mV   |

|                                              |                     | V <sub>I/OB</sub> _ relative to GNDB, I <sub>I/OB</sub> _ = 30mA sink |                         |                           |     | 400                       |      |

| Leakage Current                              | ΙL                  | I/OA_ = V <sub>DDA</sub> , I/OB_ = V <sub>DDI</sub>                   | -1                      |                           | +1  | μA                        |      |

| Input Capacitance                            | C <sub>IN</sub>     | I/OA_, I/OB_, f = 1MHz                                                |                         |                           | 5   |                           | pF   |

# **Dynamic Characteristics**

$(V_{DDA} - V_{GNDA} = +2.25 V \text{ to } +5.5 V, V_{DDB} - V_{GNDB} = +2.25 V \text{ to } +5.5 V, T_{A} = -40 ^{\circ}\text{C} \text{ to } +125 ^{\circ}\text{C}, \text{ unless otherwise noted. Typical values are at } V_{DDA} - V_{GNDA} = +3.3 V, V_{DDB} - V_{GNDB} = +3.3 V, V_{GNDA} = V_{GNDB}, T_{A} = +25 ^{\circ}\text{C}, \text{ unless otherwise noted.)} \text{ (Note 4)}$

| PARAMETER                      | SYMBOL             |                                                                                                       | CONDITIONS                                                                                                  |  |    | MAX | UNITS |

|--------------------------------|--------------------|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|--|----|-----|-------|

| Common-Mode Transient Immunity | CMTI               | IN_ = GND_ or V <sub>D</sub>                                                                          | <sub>D_</sub> (Note 5)                                                                                      |  | 25 |     | kV/µs |

| Maximum Frequency              | f <sub>MAX</sub>   |                                                                                                       |                                                                                                             |  |    | 1.7 | MHz   |

|                                |                    |                                                                                                       | $4.5V \le V_{DDA}, V_{DDB} \le 5.5V,$ $C_{LA} = 40pF, R_A = 1.6kΩ,$ $C_{LB} = 400pF, R_B = 180Ω$            |  |    | 80  |       |

|                                | t <sub>FA</sub>    | I/OA_ = 0.9V <sub>DDA</sub><br>to 0.9V                                                                | $3.0V \le V_{DDA}, V_{DDB} \le 3.6V,$ $C_{LA} = 40pF, R_A = 1k\Omega,$ $C_{LB} = 400pF, R_B = 120\Omega$    |  |    | 65  |       |

| Fall Time (Figure 1)           |                    |                                                                                                       | $2.25V \le V_{DDA}, V_{DDB} \le 2.75V,$ $C_{LA} = 40pF, R_A = 810\Omega,$ $C_{LB} = 400pF, R_B = 91\Omega$  |  |    | 55  | ns    |

| Tail fille (Figure 1)          |                    |                                                                                                       | $4.5V \le V_{DDA}, V_{DDB} \le 5.5V,$ $C_{LA} = 40pF, R_A = 1.6kΩ,$ $C_{LB} = 400pF, R_B = 180Ω$            |  |    | 35  | 115   |

|                                |                    | I/OB_ = 0.9V <sub>DDB</sub><br>to 0.1V <sub>DDB</sub>                                                 | $3.0V \le V_{DDA}, V_{DDB} \le 3.6V,$ $C_{LA} = 40pF, R_A = 1k\Omega,$ $C_{LB} = 400pF, R_B = 120\Omega$    |  |    | 45  |       |

|                                |                    |                                                                                                       | $2.25V \le V_{DDA}, V_{DDB} \le 2.75V,$ $C_{LA} = 40pF, R_A = 810k\Omega,$ $C_{LB} = 400pF, R_B = 91\Omega$ |  |    | 75  |       |

|                                |                    |                                                                                                       | $4.5V \le V_{DDA}, V_{DDB} \le 5.5V,$ $C_{LA} = 0 pF, R_A = 1.6 k\Omega,$ $C_{LB} = 0 pF, R_B = 180 \Omega$ |  |    | 20  |       |

|                                | t <sub>PLHAB</sub> | I/OA_ = 0.5V <sub>DDA</sub><br>to I/OB_ =<br>0.7V <sub>DDB</sub>                                      | $3.0V \le V_{DDA}, V_{DDB} \le 3.6V,$ $C_{LA} = 0pF, R_A = 1k\Omega,$ $C_{LB} = 0pF, R_B = 120\Omega$       |  |    | 25  |       |

| Propagation Delay (Figure 1)   |                    |                                                                                                       | $2.25V \le V_{DDA}, V_{DDB} \le 2.75V,$ $C_{LA} = 0pF, R_A = 810\Omega,$ $C_{LB} = 0pF, R_B = 91\Omega$     |  |    | 35  |       |

|                                |                    |                                                                                                       | $4.5V \le V_{DDA}, V_{DDB} \le 5.5V,$ $C_{LA} = 0pF, R_A = 1.6kΩ,$ $C_{LB} = 0pF, R_B = 180Ω$               |  |    | 80  | ns    |

|                                | t <sub>PHLAB</sub> | $3.0V \le V_{DDA}, V_{DDB} \le 3.6V,$ $C_{LA} = 0pF, R_A = 1k\Omega,$ $C_{LB} = 0pF, R_B = 120\Omega$ |                                                                                                             |  | 95 |     |       |

|                                |                    |                                                                                                       | $2.25V \le V_{DDA}, V_{DDB} \le 2.75V,$ $C_{LA} = 0pF, R_A = 810\Omega,$ $C_{LB} = 0pF, R_B = 91\Omega$     |  |    | 110 |       |

## **Dynamic Characteristics (continued)**

$(V_{DDA} - V_{GNDA} = +2.25V \text{ to } +5.5V, V_{DDB} - V_{GNDB} = +2.25V \text{ to } +5.5V, T_A = -40^{\circ}\text{C} \text{ to } +125^{\circ}\text{C}, \text{ unless otherwise noted.}$  Typical values are at  $V_{DDA} - V_{GNDA} = +3.3V, V_{DDB} - V_{GNDB} = +3.3V, V_{GNDA} = V_{GNDB}, T_A = +25^{\circ}\text{C}, \text{ unless otherwise noted.}$  (Note 4)

| PARAMETER                    | SYMBOL                             |                                                                  | CONDITIONS                                                                                                      | MIN | TYP | MAX | UNITS |  |

|------------------------------|------------------------------------|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|--|

|                              |                                    |                                                                  | $4.5V \le V_{DDA}$ , $V_{DDB} \le 5.5V$ ,<br>$C_{LA} = 0$ pF, $R_A = 1.6$ kΩ,<br>$C_{LB} = 0$ pF, $R_B = 180$ Ω |     |     | 25  |       |  |

| Propagation Delay (Figure 1) | <sup>t</sup> PLHBA                 | I/OB_ = 0.5V <sub>DDB</sub><br>to I/OA_ =<br>0.7V <sub>DDA</sub> | $3.0V \le V_{DDA}, V_{DDB} \le 3.6V,$ $C_{LA} = 0pF, R_A = 1k\Omega,$ $C_{LB} = 0pF, R_B = 120\Omega$           |     |     | 25  |       |  |

|                              |                                    |                                                                  | $2.25V \le V_{DDA}, V_{DDB} \le 2.75V,$ $C_{LA} = 0pF, R_A = 810\Omega,$ $C_{LB} = 0pF, R_B = 91\Omega$         |     |     | 35  |       |  |

|                              |                                    |                                                                  | $4.5V \le V_{DDA}, V_{DDB} \le 5.5V,$ $C_{LA} = 0pF, R_A = 1.6k\Omega,$ $C_{LB} = 0pF, R_B = 180\Omega$         |     |     | 115 | ns    |  |

|                              |                                    | I/OB_ = 0.5V <sub>DDB</sub><br>to I/OA_ = 0.9V                   | $3.0V \le V_{DDA}, V_{DDB} \le 3.6V,$ $C_{LA} = 0pF, R_A = 1k\Omega,$ $C_{LB} = 0pF, R_B = 120\Omega$           |     |     | 115 |       |  |

|                              |                                    |                                                                  | $2.25V \le V_{DDA}, V_{DDB} \le 2.75V,$ $C_{LA} = 0pF, R_A = 810\Omega,$ $C_{LB} = 0pF, R_B = 91\Omega$         |     |     | 125 |       |  |

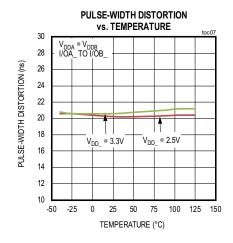

| Pulse-Width Distortion       |                                    |                                                                  | $4.5V \le V_{DDA}, V_{DDB} \le 5.5V$                                                                            |     |     | 65  |       |  |

|                              | PWD <sub>AB</sub>                  | tplhab - tphlab                                                  | $3.0V \le V_{DDA}, V_{DDB} \le 3.6V$                                                                            |     |     | 65  |       |  |

|                              |                                    |                                                                  | $2.25V \le V_{DDA}, V_{DDB} \le 2.75V$                                                                          |     |     | 80  | ns    |  |

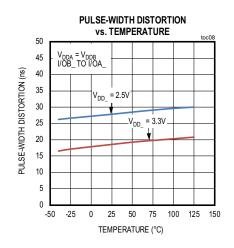

|                              |                                    |                                                                  | 4.5V ≤ V <sub>DDA</sub> , V <sub>DDB</sub> ≤ 5.5V                                                               |     |     | 95  |       |  |

|                              | PWD <sub>BA</sub>  t <sub>PL</sub> | t <sub>PLHBA</sub> - t <sub>PHLBA</sub>                          | $3.0V \le V_{DDA}, V_{DDB} \le 3.6V$                                                                            |     |     | 95  |       |  |

|                              |                                    |                                                                  | 2.25V ≤ V <sub>DDA</sub> , V <sub>DDB</sub> ≤ 2.75V                                                             |     |     | 100 |       |  |

#### **ESD Protection**

| PARAMETER | SYMBOL | CONDITIONS                 | MIN | TYP | MAX | UNITS |

|-----------|--------|----------------------------|-----|-----|-----|-------|

| ESD       |        | Human body model, all pins |     | ±4  |     | kV    |

- Note 1: All devices are 100% production tested at  $T_A = +125^{\circ}C$ . Specifications over temperature are guaranteed by design.

- **Note 2:** All currents into the device are positive; all currents out of the device are negative. All voltages are referenced to ground on the corresponding side of the device, unless otherwise noted.

- **Note 3:** This is the minimum difference between the output logic-low level and the input logic threshold. This ensures that there is no possibility of the part latching up the bus to which it is connected.

- Note 4: Not production tested. Guaranteed by design.

- Note 5: CMTI is the maximum sustainable common-mode voltage slew rate while maintaining operation. CMTI applies to both rising and falling common-mode voltage edges. Tested with the transient generator connected between GNDA and GNDB (V<sub>CM</sub> = 1000V).

### **Safety Regulatory Approvals**

#### UL

The MAX14937 is certified under UL1577. For more details, refer to file E351759.

Rated up to 5000V isolation voltage for single protection.

#### cUL (Equivalent to CSA notice 5A)

The MAX14937 is certified up to 5000V for single protection. For more details, refer to file 351759.

#### **VDE**

The MAX14937 is certified to DIN V VDE V 0884-10 (VDE V 0884-10): 2006-12. For details, see file ref. 5015017-4880-0001/217630/EC22/SCT. Basic Insulation, Maximum Transient Isolation Voltage 8400V, Maximum Working Voltage 848V

## **IEC Insulation Testing**

#### TUV

The MAX14937 is tested under TUV.

IEC60950-1: Up to 1200VP ( $848V_{RMS}$ ) working voltage for basic insulation.

IEC61010-1 (ed. 3): Up to 848V<sub>RMS</sub> working voltage for basic insulation. For details, see Technical Report number 095-72100581-100.

IEC60601-1 (ed. 3): For details see Technical Report number 095-72100581-200.

Basic insulation 1 MOOP, 1200V<sub>PK</sub> (848V<sub>RMS</sub>)

Withstand isolation voltage for 60s (Viso) 5000V<sub>RMS</sub>

#### **Insulation Characteristics**

| PARAMETER                                    | SYMBOL            | CONDITIONS                                                                 | VALUE              | UNITS            |

|----------------------------------------------|-------------------|----------------------------------------------------------------------------|--------------------|------------------|

| Partial Discharge Test Voltage               | V <sub>PR</sub>   | Method B1 = V <sub>IORM</sub> x 1.875<br>(t = 1s, partial discharge < 5pC) | 2250               | V <sub>P</sub>   |

| Maximum Repetitive Peak Isolation Voltage    | V <sub>IORM</sub> |                                                                            | 1200               | V <sub>P</sub>   |

| Maximum Working Isolation Voltage            | V <sub>IOWM</sub> |                                                                            | 848                | V <sub>RMS</sub> |

| Maximum Transient Isolation Voltage          | V <sub>IOTM</sub> | t = 1s                                                                     | 8400               | V <sub>P</sub>   |

| Maximum Withstand Isolation Voltage          | V <sub>ISO</sub>  | f <sub>SW</sub> = 60Hz, duration = 60s                                     | 5000               | V <sub>RMS</sub> |

| Maximum Surge Isolation Voltage              | V <sub>IOSM</sub> | Basic insulation 1.2/50µs pulse                                            | 10                 | kV               |

| Insulation Resistance                        | R <sub>S</sub>    | T <sub>A</sub> = +150°C<br>V <sub>IO</sub> = 500V                          | > 10 <sup>12</sup> | Ω                |

| Barrier Capacitance Input to Output (Note 6) | CIO               | f <sub>SW</sub> = 1MHz                                                     | 2                  | pF               |

| Minimum Creepage Distance                    | CPG               | Wide SOIC                                                                  | 8                  | mm               |

| Minimum Clearance Distance                   | CLR               | Wide SOIC                                                                  | 8                  | mm               |

| Internal Clearance                           |                   | Distance through insulation                                                | 0.015              | mm               |

| Comparative Tracking Resistance Index        | CTI               | Material Group II (IEC 60112)                                              | 575                |                  |

| Climatic Category                            |                   |                                                                            | 40/125/21          |                  |

| Pollution Degree (DIN VDE 0110, Table 1)     |                   |                                                                            | 2                  |                  |

Note 6: Capacitance is measured with all pins on side A and side B tied together

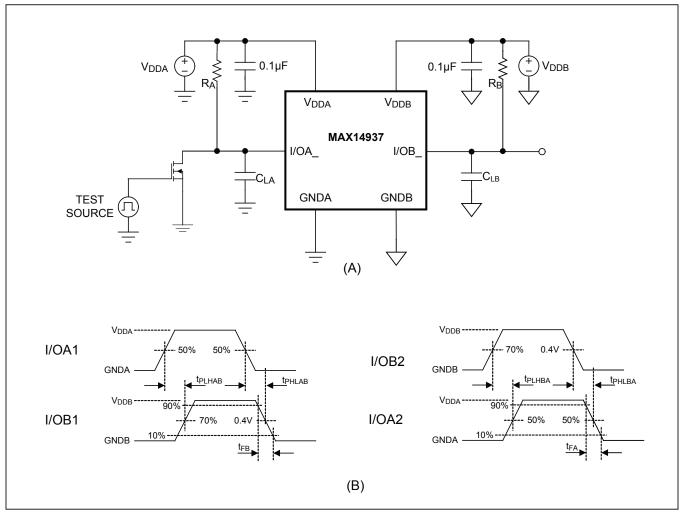

Figure 1. Test Circuit (A) and Timing Diagram (B)

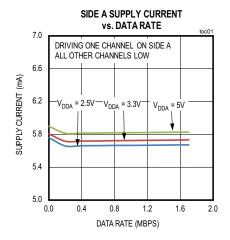

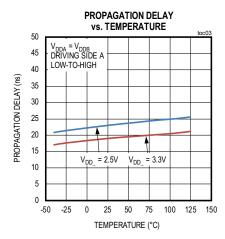

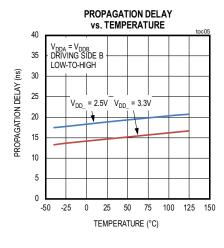

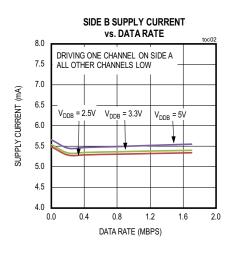

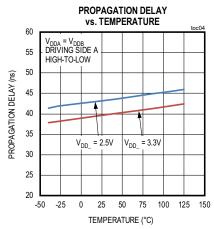

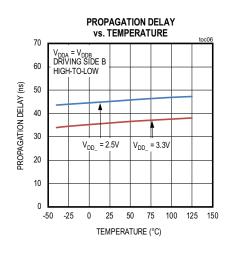

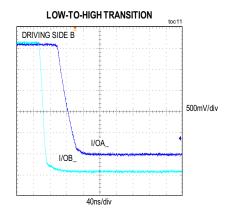

## **Typical Operating Characteristics**

$(V_{DDA} - V_{GNDA} = +3.3V, V_{DDB} - V_{GNDB} = +3.3V, V_{GNDA} = V_{GNDB}, T_A = +25$ °C, unless otherwise noted.)

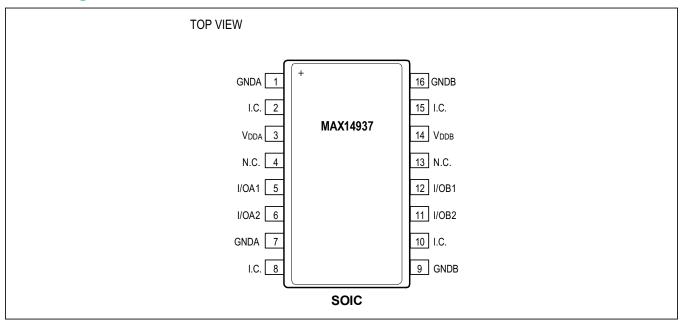

# **Pin Configuration**

# **Pin Description**

| PIN    | NAME             | FUNCTION                                                                                                           | VOLTAGE RELATIVE TO |

|--------|------------------|--------------------------------------------------------------------------------------------------------------------|---------------------|

| 1, 7   | GNDA             | Ground Reference For Side A. Ensure both pins 1 and 7 are connected to GNDA.                                       | _                   |

| 2, 8   | I.C.             | Internally Connected. Connect to GNDA or leave unconnected.                                                        | GNDA                |

| 3      | V <sub>DDA</sub> | Power Supply. Bypass $V_{\mbox{DDA}}$ with a 0.1 $\mu\mbox{F}$ ceramic capacitor as close as possible to the pin.  | GNDA                |

| 4, 13  | N.C.             | No Connection. Not internally connected.                                                                           | _                   |

| 5      | I/OA1            | Bidirectional Input/Output 1 On Side A. I/OA1 is translated to/from I/OB1 and is an open-drain output.             | GNDA                |

| 6      | I/OA2            | Bidirectional Input/Output 2 On Side A. I/OA2 is translated to/from I/OB2 and is an open-drain output.             | GNDA                |

| 9, 16  | GNDB             | Ground Reference For Side B.                                                                                       |                     |

| 10, 15 | I.C.             | Internally Connected. Connect to GNDB or leave unconnected.                                                        | GNDB                |

| 11     | I/OB2            | Bidirectional Input/Output 2 On Side B. I/OB2 is translated to/from I/OA2 and is an open-drain output.             | GNDB                |

| 12     | I/OB1            | Bidirectional Input/Output 1 On Side B. I/OB1 is translated to/from I/OA1 and is an open-drain output.             | GNDB                |

| 14     | V <sub>DDB</sub> | Power Supply. Bypass $V_{\mbox{DDB}}$ with a 0.1 $\mu \mbox{F}$ ceramic capacitor as close as possible to the pin. | GNDB                |

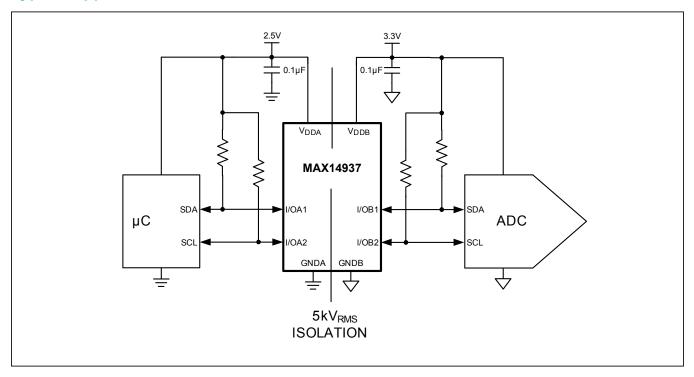

# **Typical Application Circuit**

## **Detailed Description**

The MAX14937 is a two-channel,  $5kV_{RMS}$   $I^2C$  isolator utilizing Maxim's proprietary process technology. For applications requiring  $2.75kV_{RMS}$  of isolation, refer to the MAX14933 data sheet. The MAX14937 transfers digital signals between circuits with different power domains at ambient temperatures up to  $+125^{\circ}C$ .

The device offers two bidirectional, open-drain channels for applications, such as I<sup>2</sup>C, that require data to be transmitted in both directions on the same line.

The device features independent 2.25V to 5.5V supplies on each side of the isolator. The device operates from DC to 1.7MHz and can be used in isolated I<sup>2</sup>C busses with clock stretching. The wide temperature range and high isolation voltage make the device ideal for use in harsh industrial environments.

#### **Digital Isolation**

The device provides galvanic isolation for digital signals that are transmitted between two ground domains. Up to  $1200V_{PEAK}$  of continuous isolation is supported as well as transient differences of up to  $5kV_{RMS}$  for up to 60s.

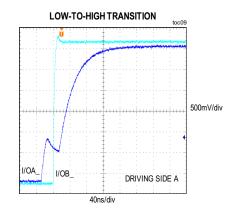

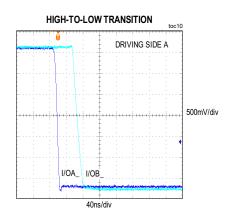

#### **Bidirectional Channels**

The device features two bidirectional channels that have open-drain outputs. The bidirectional channels do not require a direction control input. A logic-low on one side causes the corresponding pin on the other side to be pulled low while avoiding data latching within the device. I/OA1 and I/OA2 outputs comprise special buffers that regulate the logic-low voltage at approximately 0.7V. The input logic-low threshold ( $V_{IL}$ ) of I/OA1 and I/OA2 is at least 50mV lower than the output logic-low voltage of I/OA1 and I/OA2. This prevents an output logic-low on side A from being accepted as an input low and subsequently transmitted to side B; thus, preventing a latching action. I/OB1 and I/OB2 are conventional outputs that do not regulate the logic-low output voltage.

Due to their nature, the A-side output buffers of the MAX14937 cannot be connected together, or to a device with similar buffers or rise-time accelerators. The B-side output buffers of the MAX14937, instead can be connected together, or to any other bidirectional buffer or level translator.

The I/OA1, I/OA2, I/OB1, and I/OB2 pins have opendrain outputs, requiring pullup resistors to their respective supplies for logic-high outputs. The output low voltages are guaranteed for sink currents of up to 30mA for side B, and 3mA for side A (see the <u>DC Electrical Characteristics</u> table). The device supports I<sup>2</sup>C clock stretching.

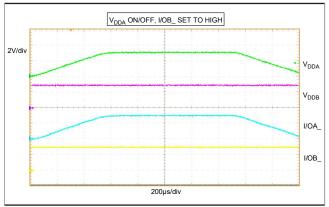

#### **Startup and Undervoltage Lockout**

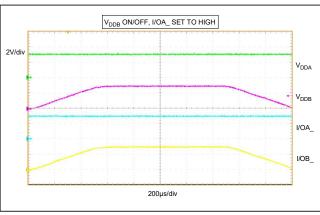

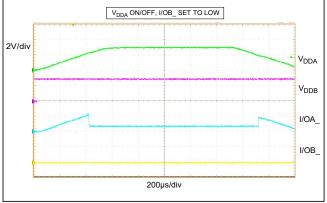

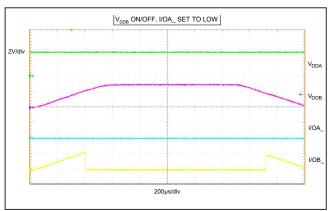

The  $V_{DDA}$  and  $V_{DDB}$  supplies are both internally monitored for undervoltage conditions. Undervoltage events can occur during power-up, power-down, or during normal operation due to a sagging supply voltage. When an undervoltage event is detected on either of the supplies, all bidirectional outputs become high-impedance and are pulled high by the external pullup resistor on the open-drain outputs (Table 1). Figure 2 through Figure 5 shows the behavior of the outputs during power-up and power-down.

## **Applications Information**

#### Effect of Continuous Isolation on Lifetime

High-voltage conditions cause insulation to degrade over time. Higher voltages result in faster degradation. Even the high-quality insulating material used in the device can degrade over long periods of time with a constant high voltage across the isolation barrier.

#### **Power-Supply Sequencing**

The MAX14937 does not require special power-supply sequencing. The logic levels are set independently on either side by  $V_{DDA}$  and  $V_{DDB}$ . Each supply can be present over the entire specified range regardless of the level or presence of the other supply.

#### **Power-Supply Decoupling**

To reduce ripple and the chance of introducing data errors, bypass  $V_{DDA}$  and  $V_{DDB}$  with  $0.1\mu F$  ceramic capacitors to GNDA and GNDB, respectively. Place the bypass capacitors as close as possible to the power-supply input.

#### Input/Output Capacitive Loads

For optimal performance, ensure that  $C_{LA} \le 40 pF$  and  $C_{LB} \le 400 pF$ .

**Table 1. Output Behavior During Undervoltage Conditions**

| V <sub>DDA</sub> | V <sub>DDB</sub> | V <sub>I/OA</sub> _ | V <sub>I/OB</sub> _ |

|------------------|------------------|---------------------|---------------------|

| Powered          | Powered          | 1                   | 1                   |

| Powered          | Powered          | 0                   | 0                   |

| Undervoltage     | Powered          | High-Z              | X                   |

| Powered          | Undervoltage     | X                   | High-Z              |

X = Don't care.

Figure 2. Undervoltage-Lockout Behavior (I/OB\_ Set High)

Figure 3. Undervoltage-Lockout Behavior (I/OA\_ Set High)

Figure 4. Undervoltage-Lockout Behavior (I/OB\_ Set Low)

Figure 5. Undervoltage-Lockout Behavior (I/OA\_ Set Low)

# **Ordering Information**

| PART         | TEMP RANGE      | PIN-PACKAGE  |

|--------------|-----------------|--------------|

| MAX14937AWE+ | -40°C to +125°C | 16 Wide SOIC |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

## **Chip Information**

PROCESS: BICMOS

## **Revision History**

| REVISION<br>NUMBER | REVISION DATE | DESCRIPTION                                                                                   | PAGES<br>CHANGED |

|--------------------|---------------|-----------------------------------------------------------------------------------------------|------------------|

| 0                  | 3/15          | Initial release                                                                               | _                |

| 1                  | 5/16          | Updated TUV information and added IEC Insulation Testing table                                | 1, 6             |

| 2                  | 1/17          | Removed VDE pending                                                                           | 6                |

| 3                  | 10/19         | Updated General Description and replaced the Bidirectional Channels sections; corrected typos | 1, 6, 12         |

For pricing, delivery, and ordering information, please visit Maxim Integrated's online storefront at https://www.maximintegrated.com/en/storefront/storefront.html.

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.