# 8-/4-Channel ADCs with Simultaneous T/Hs and Reference

#### **General Description**

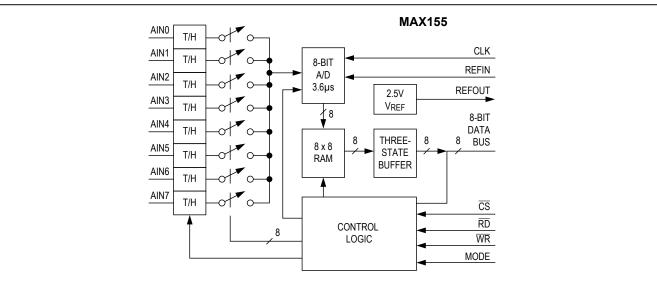

The MAX155/MAX156 are high-speed, 8-bit, multichannel analog-to-digital converters (ADCs) with simultaneous track/holds (T/Hs) to eliminate timing differences between input channel samples. The MAX155 has 8 analog input channels and the MAX156 has 4 analog input channels. Each channel has its own T/H, and all T/Hs sample at the same instant. The ADC converts a channel in 3.6µs and stores the result in an internal 8x8 RAM. The MAX155/ MAX156 also feature a 2.5V internal reference and power-down capability, providing a complete, sampling data-acquisition system.

When operating from a single +5V supply, the MAX155/ MAX156 perform either unipolar or bipolar, single-ended or differential conversions. For applications requiring wider dynamic range or bipolar conversions around ground, the  $V_{SS}$  supply pin may be connected to -5V.

Conversions are initiated with a pulse to the WR pin, and data is accessed from the ADC's RAM with a pulse to the RD pin. A bidirectional interface updates the channel configuration and provides output data. The ADC may also be wired for output-only operation. The MAX155 comes in 28-pin PDIP and wide SO packages, and the MAX156 comes in 24-pin narrow PDIP and 28-pin wide SO packages.

#### **Features**

- 8 Simultaneously Sampling Track/Hold Inputs

- 3.6µs Conversion Time Per Channel

- Unipolar or Bipolar Input Range

- Single-Ended or Differential Inputs

- Mixed Input Configurations Possible

- 2.5V Internal Reference

- Single +5V or Dual ±5V Supply Operation

#### Applications

- Phase-Sensitive Data Acquisition

- Vibration and Waveform Analysis

- DSP Analog Input

- AC Power Meters

- Portable Data Loggers

Ordering Information appears at end of data sheet.

For related parts and recommended products to use with this part, refer to <u>www.maximintegrated.com/MAX155.related</u>.

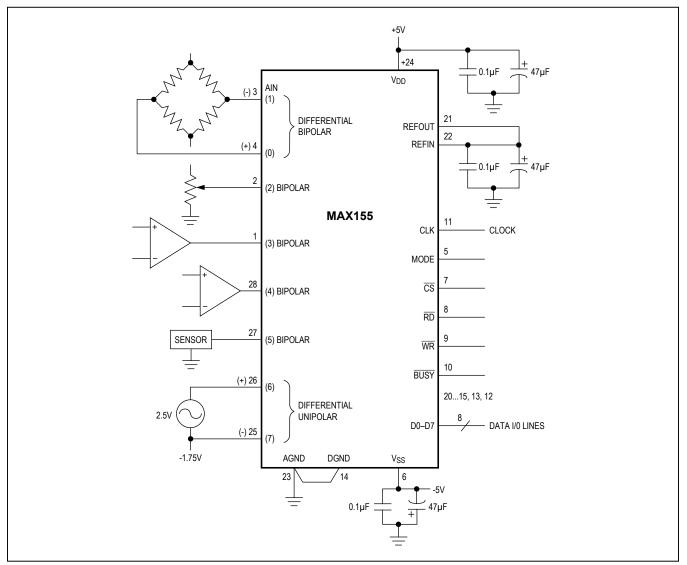

# Functional Diagram

# 8-/4-Channel ADCs with Simultaneous T/Hs and Reference

### **Absolute Maximum Ratings**

| V <sub>DD</sub> to AGND       |                                   |

|-------------------------------|-----------------------------------|

| V <sub>DD</sub> to DGND       |                                   |

| AGND to DGND                  | 0.3V, (V <sub>DD</sub> + 0.3V)    |

| V <sub>SS</sub> to AGND       | +0.3V, -6V                        |

| V <sub>SS</sub> to DGND       | +0.3V, -6V                        |

| CS, WR, RD, CLK, MODE to DGND | 0.3V, (V <sub>DD</sub> + 0 3V)    |

| BUSY, D0-D7 to DGND           | 0.3V, (V <sub>DD</sub> + 0 3V)    |

| REFOUT to AGND                | 0.3V, (V <sub>DD</sub> + 0 3V)    |

| REFIN to AGND                 | 0.3V, (V <sub>DD</sub> + 0 3V)    |

| AIN to AGND(V <sub>SS</sub>   | - 0.3V), (V <sub>DD</sub> + 0 3V) |

| Output Current (REFOUT)       |                                   |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |

|-------------------------------------------------------|

| 24-Pin PDIP (derate 8.7mW/°C above +70°C)696mW        |

| 28-Pin PDIP (derate 9.09mW/°C above +70°C)727mW       |

| 28-Pin Wide SO (derate 12.5mW/°C above +70°C)1000mW   |

| Operating Temperature Ranges:                         |

| MAX155/MAX156_C0°C to +70°C                           |

| MAX155/MAX156_E                                       |

| Storage Temperature Range65°C to +150°C               |

| Lead Temperature (soldering, 10s)+300°C               |

| Soldering Temperature (reflow)+260°C                  |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Electrical Characteristics**

$(V_{DD} = +5V, V_{REFIN} = +2.5V.$  External Reference,  $V_{AGND} = V_{DGND} = 0V$ ,  $V_{SS} = 0V$  or -5V,  $f_{CLK} = 5MHz$  external, Unipolar range single-ended mode,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.)

| PARAMETER                        | SYMBOL                    | CONDIT              | MIN           | TYP | MAX  | UNITS |       |

|----------------------------------|---------------------------|---------------------|---------------|-----|------|-------|-------|

| ACCURACY (Note 1)                |                           |                     |               |     |      |       |       |

| Resolution                       |                           |                     |               | 8   |      |       | Bits  |

| Integral Linearity Error         |                           | MAX15_A             |               |     |      | ±1⁄2  |       |

| Integral Linearity Error         |                           | MAX15_B             |               |     |      | ±1    | LSB   |

| No Missing Codes Resolution      |                           | Guaranteed monoto   | onic          | 8   |      |       | Bits  |

| Offect Error (Uninclor)          |                           | MAX15_A             |               |     |      | ±1⁄2  | LSB   |

| Offset Error (Unipolar)          |                           | MAX15_B             |               |     |      | ±1    |       |

| Offset Error (Bipolar)           |                           | MAX15_A             |               |     |      | ±1    |       |

|                                  |                           | MAX15_B             |               |     | ±2   | LSB   |       |

|                                  |                           | Unipolar            | MAX15_A       |     |      | ±1    | - LSB |

| Gain Error                       |                           | · ·                 | MAX15_B       |     |      | ±1    |       |

| Gain Endi                        |                           |                     | MAX15_A       |     |      | ±1    |       |

|                                  |                           | ырогаг              | MAX15_B       |     |      | ±2    |       |

| Channel-to-Channel Matching      |                           | MAX15_A             |               |     | ±1⁄2 |       | LSB   |

| Chame-to-Chame Matching          |                           | MAX15_B             |               | ±1  |      |       | LSD   |

| DYNAMIC PERFORMANCE (VIN =       | 50kHz, 2.5V <sub>P-</sub> | P sine wave sampled | l at 220ksps) |     |      |       |       |

| Signal-to-Noise and Distortion   | SINAD                     | MAX15_A             |               |     | 48   |       | dB    |

| Ratio                            | SINAD                     | MAX15_B             |               |     | 47   |       | uв    |

| Total Harmonic Distortion        | THD                       |                     |               |     | -60  |       | dB    |

| Spurious-Free Dynamic Range      | SFDR                      |                     |               |     | -62  |       | dB    |

| Small-Signal Bandwidth           |                           |                     |               |     | 4    |       | MHz   |

| Aperture Delay                   |                           |                     |               |     | 20   |       | ns    |

| Aperture Delay Matching (Note 2) |                           |                     |               |     |      | 4     | ns    |

# 8-/4-Channel ADCs with Simultaneous T/Hs and Reference

#### **Electrical Characteristics (continued)**

$(V_{DD} = +5V, V_{REFIN} = +2.5V.$  External Reference,  $V_{AGND} = V_{DGND} = 0V$ ,  $V_{SS} = 0V$  or -5V,  $f_{CLK} = 5MHz$  external, Unipolar range single-ended mode,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.)

| PARAMETER                                                 | SYMBOL           | L CONDITIONS                             |                                 |                             | TYP                | MAX                         | UNITS  |

|-----------------------------------------------------------|------------------|------------------------------------------|---------------------------------|-----------------------------|--------------------|-----------------------------|--------|

| ANALOG INPUT                                              |                  |                                          |                                 |                             |                    |                             | •      |

| Voltage Range, Unipolar, Single-<br>Ended                 |                  | AIN_(+) to AGND                          | AIN_(+) to AGND                 |                             |                    | V <sub>REF</sub>            |        |

| Unipolar Differential                                     |                  | AIN_(+) to AIN_(-                        | AIN_(+) to AIN_(-)              |                             |                    | V <sub>REF</sub>            |        |

| Bipolar, Single-Ended                                     |                  | AIN_(+) to AGND                          |                                 | -V <sub>REF</sub>           |                    | V <sub>REF</sub>            | V      |

| Bipolar, Differential                                     |                  | AIN_(+) to AIN_(-                        | )                               | -V <sub>REF</sub>           |                    | V <sub>REF</sub>            | ]      |

| Common-Mode Range                                         |                  | Differential mode                        |                                 | V <sub>SS</sub>             |                    | V <sub>DD</sub>             | 1      |

| DC Input Impedance                                        |                  | AIN = V <sub>DD</sub>                    |                                 | 10                          |                    |                             | MΩ     |

| REFERENCE INPUT                                           |                  |                                          |                                 | ·                           |                    |                             |        |

| REFIN Range (For Specified<br>Performance) (Note 2)       |                  |                                          |                                 | 2.375                       | 2.500              | 2.625                       | V      |

| I <sub>REF</sub>                                          |                  | V <sub>REFIN</sub> = 2.5V                |                                 |                             |                    | 1                           | mA     |

| REFERENCE OUTPUT ( $C_L = 4.7 \mu F$                      | )                |                                          |                                 |                             |                    |                             |        |

|                                                           |                  |                                          | T <sub>A</sub> = +25°C          | 2.44                        | 2.50               | 2.56                        |        |

| Output Voltage                                            |                  | I <sub>L</sub> = 0mA                     | $T_A = T_{MIN}$ to<br>$T_{MAX}$ | 2.38                        | 2.50               | 2.62                        | V      |

| Load Regulation                                           |                  | T <sub>A</sub> = +25°C, I <sub>OUT</sub> | = 0 to 10mA                     |                             |                    | -10                         | mV     |

| Power-Supply Sensitivity                                  |                  | T <sub>A</sub> = +25°C, V <sub>DD</sub>  | = 5V ±5%                        |                             | ±1                 | ±3                          | mV     |

| Temperature Drift                                         |                  |                                          |                                 |                             | ±100               |                             | ppm/°C |

| LOGIC INPUTS (Mode = Open Circ                            | uit)             |                                          |                                 | ·                           |                    |                             |        |

| CS, RD, WR, CLK, D0–D7 (When<br>Inputs) Input Low Voltage | V <sub>IL</sub>  |                                          |                                 |                             |                    | 0.8                         | V      |

| Input High Voltage                                        | V <sub>IH</sub>  |                                          |                                 | 2.4                         |                    |                             | V      |

| Input Current                                             | I <sub>IN</sub>  |                                          |                                 |                             |                    | ±10                         | μA     |

| Input Capacitance (Note 2)                                | C <sub>IN</sub>  |                                          |                                 |                             |                    | 15                          | pF     |

| MODE                                                      |                  |                                          |                                 | ·                           |                    |                             |        |

| Input Low Voltage                                         | V <sub>IL</sub>  |                                          |                                 |                             |                    | 0.5                         | V      |

| Input High Voltage                                        | V <sub>IH</sub>  |                                          |                                 | V <sub>DD</sub> -<br>0.5    |                    |                             | v      |

| Input Midlevel Voltage                                    | V <sub>MID</sub> |                                          |                                 | V <sub>DD</sub> /2<br>- 0.5 |                    | V <sub>DD</sub> /2<br>+ 0.5 | v      |

| Input Floating Voltage                                    | V <sub>FLT</sub> |                                          |                                 |                             | V <sub>DD</sub> /2 |                             | V      |

| Input Current                                             | I <sub>IN</sub>  |                                          |                                 | 1                           | ±50                | ±100                        | μA     |

# 8-/4-Channel ADCs with Simultaneous T/Hs and Reference

#### **Electrical Characteristics (continued)**

$(V_{DD} = +5V, V_{REFIN} = +2.5V.$  External Reference,  $V_{AGND} = V_{DGND} = 0V$ ,  $V_{SS} = 0V$  or -5V,  $f_{CLK} = 5MHz$  external, Unipolar range single-ended mode,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.)

| PARAMETER                                  | SYMBOL           | C                                    | MIN                                                                                                                     | TYP  | MAX  | UNITS |      |  |

|--------------------------------------------|------------------|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------|------|------|-------|------|--|

| LOGIC OUTPUTS                              |                  |                                      |                                                                                                                         |      |      |       |      |  |

| BUSY, D0–D7 Output Low Voltage             | V <sub>OL</sub>  | I <sub>OUT</sub> = 1.6m/             | A                                                                                                                       |      |      | 0.4   | V    |  |

| Output High Voltage                        | V <sub>OH</sub>  | l <sub>OUT</sub> = -360μ             | A                                                                                                                       | 4    |      |       | V    |  |

| D0–D7 Floating State Leakage               |                  |                                      |                                                                                                                         |      |      | ±10   | μA   |  |

| Floating State Output Capacitance (Note 2) | C <sub>OUT</sub> |                                      |                                                                                                                         |      |      | 15    | pF   |  |

| Conversion Time                            |                  | f <sub>CLK</sub> = 5MHz              | , single channel                                                                                                        | 3.6  |      | 3.8   | μs   |  |

| POWER REQUIREMENTS                         |                  |                                      |                                                                                                                         |      |      |       |      |  |

| Positive Power-Supply Voltage              | V <sub>DD</sub>  |                                      |                                                                                                                         | 4.75 |      | 5.25  | V    |  |

|                                            |                  | PD = 0                               | MAX155                                                                                                                  |      | 18   | 24    |      |  |

|                                            |                  | PD = 0                               | MAX156                                                                                                                  |      | 9    | 12    | - mA |  |

| Positive Power-Supply Current              | IDD              | PD = 1                               | CLK, $\overline{CS}$ , $\overline{WR}$ ,<br>RD = 0V or V <sub>DD</sub> ;<br>D <sub>OUT</sub> = 0V or<br>V <sub>DD</sub> |      | 25   | 100   | μΑ   |  |

| Negative Power-Supply Voltage              | V <sub>SS</sub>  |                                      | · · · ·                                                                                                                 | 0    |      | -5    | V    |  |

| Negative Dower Supply Current              | I                | PD = 0                               |                                                                                                                         |      | 2    | 50    |      |  |

| Negative Power-Supply Current              | I <sub>SS</sub>  | PD = 1                               |                                                                                                                         |      | 2    | 50    | - μΑ |  |

| Power-Supply Rejection (Change             |                  | V <sub>DD</sub> = 5V ±5              | %, V <sub>SS</sub> = 0V                                                                                                 |      | ±0.1 | ±0.25 |      |  |

| in Full-Scale Error)                       |                  | V <sub>DD</sub> = 5V, V <sub>S</sub> | <sub>3S</sub> = -5V ±5%                                                                                                 |      | ±0.1 |       | LSB  |  |

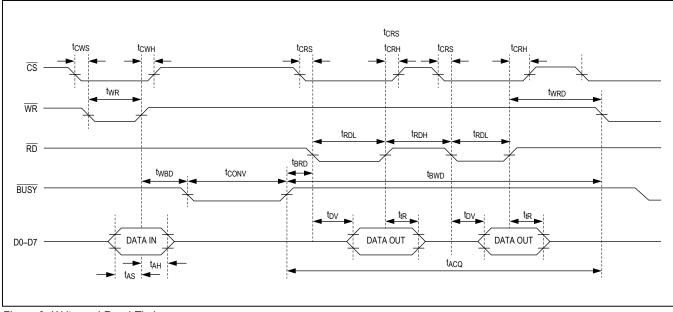

### TIMING CHARACTERISTICS (Note 3, Figures 1–7)

(V<sub>DD</sub> = +5V, V<sub>REFIN</sub> = +2.5V. External Reference, V<sub>AGND</sub> = V<sub>DGND</sub> = 0V, V<sub>SS</sub> = 0V or -5V, T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted.)

| PARAMETER                                                           | SYMBOL           | CONDITIONS | MIN | ТҮР | MAX  | UNITS |

|---------------------------------------------------------------------|------------------|------------|-----|-----|------|-------|

| CS to WR Setup Time                                                 | tcws             |            | 0   |     |      | ns    |

| $\overline{\text{CS}}$ to $\overline{\text{WR}}$ Hold Time          | t <sub>CWH</sub> |            | 0   |     |      | ns    |

| CS to RD Setup Time                                                 | t <sub>CRS</sub> |            | 0   |     |      | ns    |

| $\overline{\text{CS}}$ to $\overline{\text{RD}}$ Hold Time (Note 2) | t <sub>CRH</sub> |            | 0   |     |      | ns    |

| WR Low Pulse Width                                                  | t <sub>WR</sub>  | MAX15_C/E  | 100 |     | 2000 | ns    |

| RD Low Pulse Width                                                  | t <sub>RDL</sub> | MAX15_C/E  | 100 |     |      | ns    |

| RD High Pulse Width (Note 2)                                        | t <sub>RDH</sub> | MAX15_C/E  | 180 |     |      | ns    |

| WR to RD Delay (Note 2)                                             | t <sub>WRD</sub> | MAX15_C/E  | 280 |     |      | ns    |

| WR to BUSY Low Delay                                                | t <sub>WBD</sub> | MAX15_C/E  |     |     | 220  | ns    |

# 8-/4-Channel ADCs with Simultaneous T/Hs and Reference

### TIMING CHARACTERISTICS (Note 3, Figures 1-7) (continued)

(V<sub>DD</sub> = +5V, V<sub>REFIN</sub> = +2.5V. External Reference, V<sub>AGND</sub> = V<sub>DGND</sub> = 0V, V<sub>SS</sub> = 0V or -5V, T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted.)

| PARAMETER                                                                                                     | SYMBOL           | CONDITIONS | MIN | ТҮР | MAX | UNITS |

|---------------------------------------------------------------------------------------------------------------|------------------|------------|-----|-----|-----|-------|

| $\overline{\text{BUSY}}$ High to $\overline{\text{WR}}$ Delay (to update configuration register) (Notes 2, 3) | t <sub>BWD</sub> |            | 50  |     |     | ns    |

| CLK to WR Delay (Acquisition Time)<br>(Note 2)                                                                | tACQ             |            | 800 |     |     | ns    |

| BUSY High to RD Delay (Notes 2, 3)                                                                            | t <sub>BRD</sub> |            | 50  |     |     | ns    |

| Address-Setup Time                                                                                            | t <sub>AS</sub>  |            | 120 |     |     | ns    |

| Address-Hold Time                                                                                             | t <sub>AH</sub>  |            | 0   |     |     | ns    |

| RD to Data Valid (Note 4)                                                                                     | t <sub>DV</sub>  | MAX15_C/E  | 100 |     |     | ns    |

| RD to Data Three-State Output (Note 5)                                                                        | t <sub>TR</sub>  | MAX15_C/E  | 80  |     |     | ns    |

| CLK to BUSY Delay (Note 2)                                                                                    | t <sub>CB</sub>  |            |     | 100 | 300 | ns    |

| CLK Frequency                                                                                                 |                  |            | 0.5 |     | 5.0 | MHz   |

**Note 1:** V<sub>DD</sub> = +5V, V<sub>REFIN</sub> = +2.5V, V<sub>SS</sub> = 0V. Performance at ±5% power-supply tolerance is guaranteed by Power-Supply Rejection test.

Note 2: Guaranteed by design, not production tested.

**Note 3:** All input control signals are specified with  $t_r = t_f = 20$ ns (10% to 90% of +5V) and timed from a +1.6V voltage level. Output signals are timed from V<sub>OH</sub> and V<sub>OL</sub>.

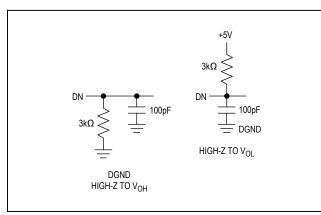

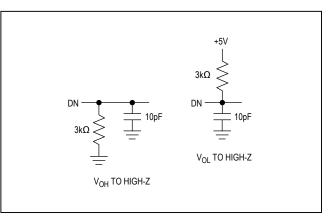

Note 4: t<sub>DV</sub> is the time required for an output to cross +0.8V or +2.4V measured with load circuit of Figure 1.

**Note 5:**  $t_{TR}$  is the time required for the data lines to change 0.5V, measured with load circuits of Figure 2.

Figure 1. Load Circuits for Data-Access Timing

Figure 2. Load Circuits for Three-State Output Timing

# 8-/4-Channel ADCs with Simultaneous T/Hs and Reference

Figure 3. Write and Read Timing

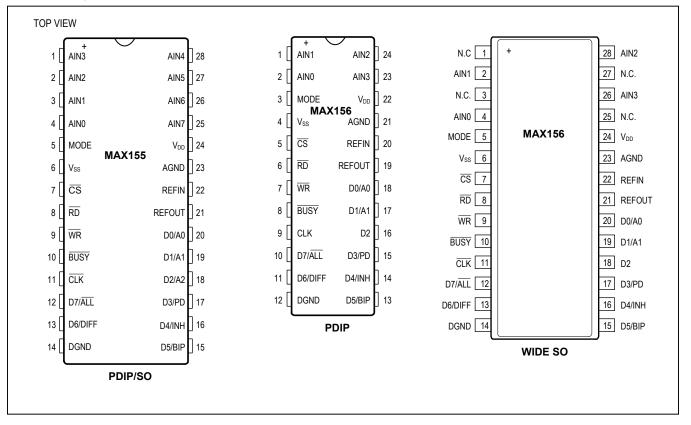

### **Pin Configuration**

# 8-/4-Channel ADCs with Simultaneous T/Hs and Reference

# **Pin Description**

| PIN     |      |                 |                 |                                                                                                                                                           |

|---------|------|-----------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX155  | МАХ  | (156            | NAME            | FUNCTION                                                                                                                                                  |

| PDIP/SO | PDIP | SO              |                 |                                                                                                                                                           |

| 1       | 23   | 26              | AIN3            | Sampling Analog Input, Channel 3                                                                                                                          |

| 2       | 24   | 28              | AIN2            | Sampling Analog Input, Channel 2                                                                                                                          |

| 3       | 1    | 2               | AIN1            | Sampling Analog Input, Channel 1                                                                                                                          |

| 4       | 2    | 4               | AIN0            | Sampling Analog Input, Channel 0                                                                                                                          |

| 5       | 3    | 5               | MODE            | Mode configures multiplexer and converter. See Table 4.                                                                                                   |

| 6       | 4    | 6               | V <sub>SS</sub> | Negative Supply. Power V <sub>SS</sub> with -5V for extended input range.                                                                                 |

| 7       | 5    | 7               | CS              | $\overrightarrow{CHIP}  \overrightarrow{SELECT} \text{ Input must be low for the ADC to recognize } \overrightarrow{RD}, \text{ or } \overrightarrow{WR}$ |

| 8       | 6    | 8               | RD              | READ Input reads data sequentially from RAM                                                                                                               |

| 9       | 7    | 9               | WR              | WRITE Input's rising edge initiates conversion and updates channel configuration register. Falling edge samples inputs.                                   |

| 10      | 8    | 10              | BUSY            | BUSY Output low when conversion is in progress                                                                                                            |

| 11      | 9    | 11              | CLK             | External Clock Input                                                                                                                                      |

| 12      | 10   | 12              | D7/ALL          | Three-State Data Output Bit 7 (MSB)/Sequential or Specific Conversion                                                                                     |

| 13      | 11   | 13              | D6/DIFF         | Three-State Data Output Bit 6/Single-Ended/Differential Select                                                                                            |

| 14      | 12   | 14              | DGND            | Digital Ground                                                                                                                                            |

| 15      | 13   | 15              | D5/BIP          | Three-State Data Output Bit 5/Unipolar/Bipolar Conversion                                                                                                 |

| 16      | 14   | 16              | D4/INH          | Three-State Data Output Bit 4/Inhibit Conversion Input                                                                                                    |

| 17      | 15   | 17              | D3/PD           | Three-State Data Output Bit 3/Power-Down Input                                                                                                            |

| 18      | 16   | 18              | D2/A2           | Three-State Data Output Bit 2/RAM Address Bit A2 (MAX155 Only)                                                                                            |

| 19      | 17   | 19              | D1/A1           | Three-State Data Output Bit 1/RAM Address Bit A1                                                                                                          |

| 20      | 18   | 20              | D0/A0           | Three-State Data Output Bit 0/RAM Address Bit A0                                                                                                          |

| 21      | 19   | 21              | REFOUT          | Reference Output, +2.5V                                                                                                                                   |

| 22      | 20   | 22              | REFIN           | Reference Input, +2.5 Normally                                                                                                                            |

| 23      | 21   | 23              | AGND            | Analog Ground                                                                                                                                             |

| 24      | 22   | 24              | V <sub>DD</sub> | Power-Supply Voltage, +5V Normally                                                                                                                        |

| 25–28   | _    | _               | AIN7-4          | Sampling Analog Input, Channels 7–4                                                                                                                       |

| _       | _    | 1, 3,<br>25, 27 | N.C.            | No Connection. No internal connection—pin unconnected.                                                                                                    |

# 8-/4-Channel ADCs with Simultaneous T/Hs and Reference

#### **Detailed Description**

#### **ADC Operation**

The MAX155/MAX156 contain a 3.6µs successive approximation ADC and 8/4 track-and-hold (T/H) inputs. When a conversion is started, all AIN inputs are simultaneously sampled. All channels sample whether or not they are selected for the conversion. Either a single-channel or multichannel conversion may be requested and channel configurations may be mixed, ADC results are then stored in an internal RAM.

In hard-wired mode (see the *Multiplexer and AID Configurations* section) multichannel conversions are initiated with one write operation. In input/output (I/O) mode, multichannel configurations are set up prior to the conversion by loading channel selections into the con-

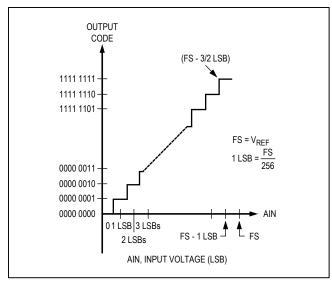

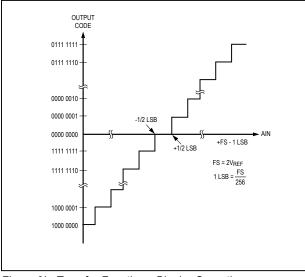

figuration register. This register also selects single-ended/ differential, unipolar/bipolar (Figure 9), power-down, and other functions. Each channel selection requires a separate write operation (i.e. 8 writes for 8 channels), but only after power-up. Once the desired channel arrangement is loaded, each subsequent write converts all selected channels without reconfiguring the multiplexer (mux). I/O mode requires more write operations, but provides more flexibility than hard-wired mode.

To access conversion results, successive  $\overline{RD}$  pulses automatically sence through RAM, beginning with channel 0. Each  $\overline{RD}$  pulse increments the RAM address counter, which resets to 0 when  $\overline{WR}$  goes low in multi channel conversions. An arbitrary RAM location may also be read by writing a 1 to INH while loading the RAM address (A0– A2), and then performing a read operation.

| PIN                     | NAME                                                                                                                    | FUNCTION                                                                                                                                                      |  |  |  |  |  |  |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| D0/A0<br>D1/A1<br>D2/A2 | 1 or 0                                                                                                                  | A0–A2 select a multiple channel for the configurations described below, or select a RAM address for reading with a subsequent $\overline{\text{RD}}$ .        |  |  |  |  |  |  |

|                         | 0                                                                                                                       | Normal ADC operation                                                                                                                                          |  |  |  |  |  |  |

| D3/PD                   | 1         Power-down reduces the power-supply current. Configuration data may be loaded a maintained during power-down. |                                                                                                                                                               |  |  |  |  |  |  |

|                         | 0                                                                                                                       | A conversion starts when WR goes high                                                                                                                         |  |  |  |  |  |  |

| D4/INH                  | 1                                                                                                                       | Inhibits the conversion when $\overline{WR}$ goes high. Allows mux configuration to be loaded and RAM locations to be accessed without starting a conversion. |  |  |  |  |  |  |

|                         | 0                                                                                                                       | Unipolar conversion (Figure 9a) for the channel specified by A0–A2. Input range = 0V to V <sub>REF</sub> .                                                    |  |  |  |  |  |  |

| D5/BIP**                | 1                                                                                                                       | Bipolar conversion (Figure 9b) for the channel specified by A0–A2. Input range = $\pm V_{REF}$ .                                                              |  |  |  |  |  |  |

|                         | 0                                                                                                                       | Single-ended configuration for the channel specified by A0–A2 as described in Table 2                                                                         |  |  |  |  |  |  |

| D6/DIFF**               | 1                                                                                                                       | Differential contiguration for the channel specified by A0–A2 as described in Table 2                                                                         |  |  |  |  |  |  |

|                         | 0                                                                                                                       | All previously configured channels are converted. Data is read with consecutive $\overline{RD}$ pulses, beginning with the lowest configured channel.         |  |  |  |  |  |  |

| D7/ALL                  | 1                                                                                                                       | Only the channel specified by A2–A0 is converted. A single $\overline{RD}$ pulse reads the result of that conversion.                                         |  |  |  |  |  |  |

#### Table 1. Multiplexer Configurations

•Configuration inputs are shared with data outputs D0-D7. The functions of D0-D7 are not described in this table.

••DIFF and BIP are not implemented on the current conversion, but go into effect on the following conversion.

# 8-/4-Channel ADCs with Simultaneous T/Hs and Reference

#### Multiplexer and A/D Configuration

A conversion is started with a  $\overline{WR}$  pulse. All channels sample on  $\overline{WR}$ 's falling edge. Mux configuration data is loaded on  $\overline{WR}$ 's rising edge. In I/O mode (MODE = Open Circuit), selections for channel number, single or multichannel conversion, unipolar or bipolar input, and singleended or differential input are made with A0-A2,  $\overline{ALL}$ , BIP, and DIFF (Table 1). These input pins are also shared with the RAM data outputs D0–D7. An alternate, simpler interface is provided by the hard-wired mode, which selects some general mux configurations without requiring ADC programming. Hard-wired connections of MODE and V<sub>SS</sub> select from 4 mux configurations as listed in Table 4 (see the *Hard-Wired Mode* section).

On the rising edge of  $\overline{\text{WR}}$ , the mux configuration register is updated; falling edge initiates sampling of all inputs. A channel selection can be implemented on the current conversion, but changes from unipolar to bipolar (with BIP) or from singleended to differential operation (with DIFF) do not go into effect until the following  $\overline{\text{WR}}$ . This can be overcome by writing to the configuration register while inhibiting the conversion (INH = 1), or by changing DIFF and BIP one conversion early, i.e. on the previous write.

#### Table 2. Single-Ended Channel Selection (MODE = Open Circuit)

|    | MUX AD | DRESS |      |   |   | SING | LE-ENDE | ENDED CHANNEL SELECTION |   |   |   |      |

|----|--------|-------|------|---|---|------|---------|-------------------------|---|---|---|------|

| A0 | A1     | A2    | DIFF | 0 | 1 | 2    | 3       | 4                       | 5 | 6 | 7 | AGND |

| 0  | 0      | 0     | 0    | + |   |      |         |                         |   |   |   | -    |

| 1  | 0      | 0     | 0    |   | + |      |         |                         |   |   |   | -    |

| 0  | 1      | 0     | 0    |   |   | +    |         |                         |   |   |   | -    |

| 1  | 1      | 0     | 0    |   |   |      | +       |                         |   |   |   | -    |

| 0  | 0      | 1     | 0    |   |   |      |         | +                       |   |   |   | -    |

| 1  | 0      | 1     | 0    |   |   |      |         |                         | + |   |   | -    |

| 0  | 1      | 1     | 0    |   |   |      |         |                         |   | + |   | -    |

| 1  | 1      | 1     | 0    |   |   |      |         |                         |   |   | + | -    |

Note: Shaded areas represent MAX156 operation.

#### Table 3. Differential Channel Selection (MODE = Open Circuit)

|    | MUX AD | DRESS |      |   |   | DIFFERE | NTIAL CH |   |   |   |   |

|----|--------|-------|------|---|---|---------|----------|---|---|---|---|

| A0 | A1     | A2    | DIFF | 0 | 1 | 2       | 3        | 4 | 5 | 6 | 7 |

| 0  | 0      | 0     | 1    | + | - |         |          |   |   |   |   |

| 0  | 1      | 0     | 1    |   |   | +       | -        |   |   |   |   |

| 0  | 0      | 1     | 1    |   |   |         |          | + | - |   |   |

| 0  | 1      | 1     | 1    |   |   |         |          |   |   | + | - |

| 1  | 0      | 0     | 1    | - | + |         |          |   |   |   |   |

| 1  | 1      | 0     | 1    |   |   | -       | +        |   |   |   |   |

| 1  | 0      | 1     | 1    |   |   |         |          | - | + |   |   |

| 1  | 1      | 1     | 1    |   |   |         |          |   |   | - | + |

Note: Shaded areas represent MAX156 operation.

# 8-/4-Channel ADCs with Simultaneous T/Hs and Reference

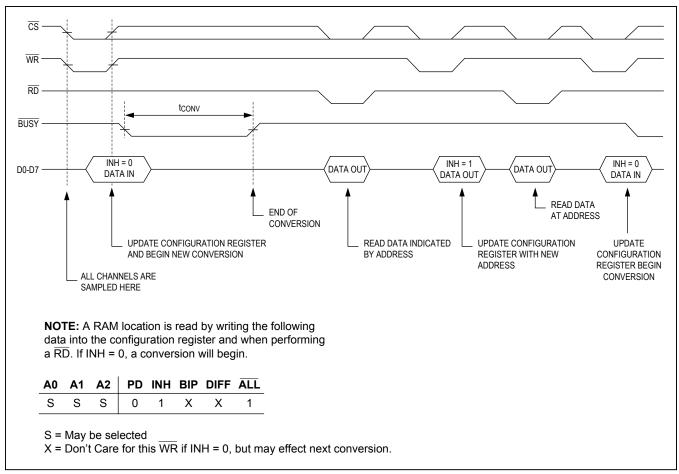

#### **Interface Timing**

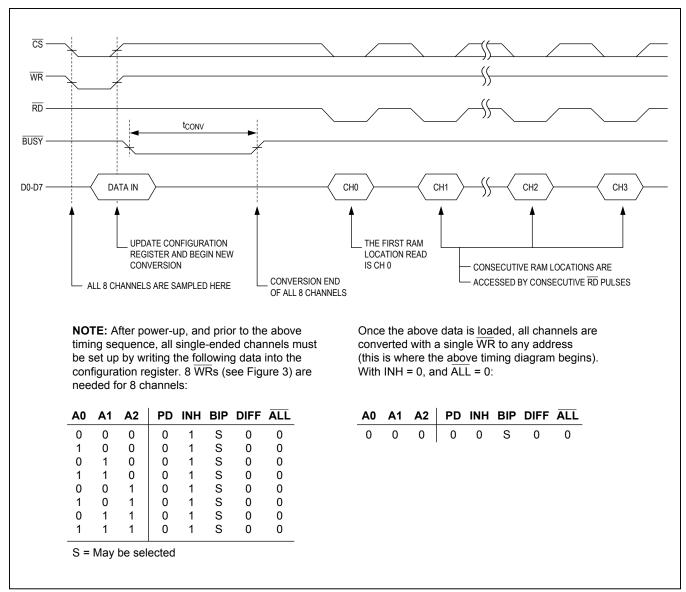

# Input/Output Mode, Multichannel Conversion Timing

I/O mode is selected when the MODE input is open circuit. In I/O mode, the mux configuration register determines the conversion type. The register is updated on the rising edge of  $\overline{WR}$ .

Table 1 lists all conversion options. For example, at D6/DIFF, a logic 0 or 1 selects a single-ended or differential conversion. Data is loaded into addressed locations in the configuration register with a series of  $\overline{WR}$  pulses. If INH is high while writing, no conversion takes place. A conversion is started by writing INH = 0 to the configuration register. When a change is made to the contents of the configuration register, a "dummy" conversion may be necessary. This is due to a built-in latency of one full conversion for unipolar/bipolar and single-ended/differential selections.

It is not necessary to update the configuration register before every conversion. A particular mux configuration must be loaded only once after power-up (but the configuration may require several writes to be loaded). A mux configuration is retained for successive conversions and during power-down (PD = 1) so that reconfiguring is unnecessary when the ADC returns to normal operation (PD = 0). Configuration and RAM data is lost only when power is removed from the ADC at V<sub>DD</sub>.

When updating the configuration register, INH should be high for all except the last  $\overline{WR}$  so the conversion is not started until the mux is set. On  $\overline{WR}$ 's falling edge, all input channels sample simultaneously. BUSY goes low at the beginning of the conversion, and channels are converted sequentially starting with the lowest selected channel. When BUSY goes high, conversion results are stored in RAM. At conversion end, a microprocessor ( $\mu$ P) can access the RAM contents with consecutive  $\overline{RD}$  pulses. The first accessed data is the lowest channel's result.

Subsequent  $\overline{\text{RD}}$  pulses access conversion results for the remaining channels.

The configuration data determines which RAM locations are sequentially read by consecutive  $\overline{RD}$  pulses, so new data should be placed in the configuration register only after a full  $\overline{RD}$  operation. It is not necessary to update the configuration register for every conversion. A new conversion is initiated with a  $\overline{WR}$  pulse (when INH = 0), regardless of the number of channe Is that have been read.

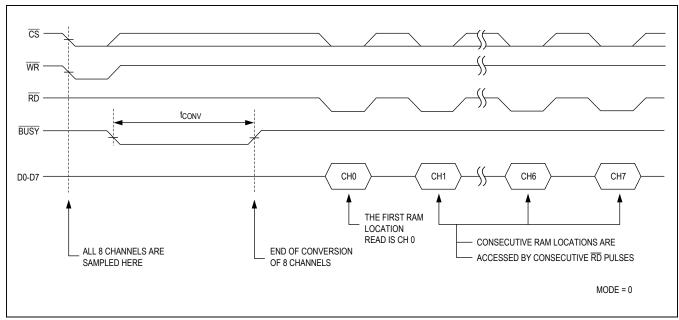

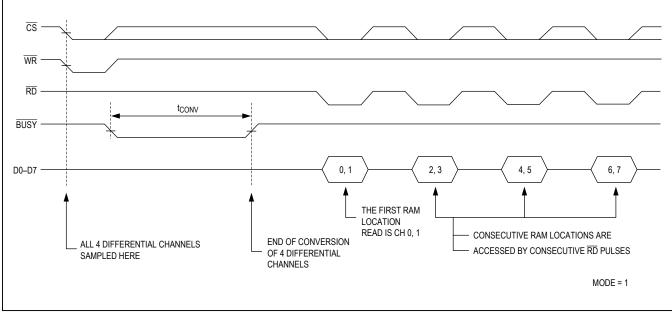

Figure 4a shows the MAX155 timing for an 8-channel unipolar configuration. 8 channels are configured and 8 consecutive  $\overline{RD}$  pulses access data. Figure 4b illustrates 4-channel differential conversion timing involving 4 sampled channels and 4  $\overline{RD}$  pulses. In cases where conflicting differential configurations are loaded, the last channel selected with DIFF = 1 will be the positive input of the differential channel.

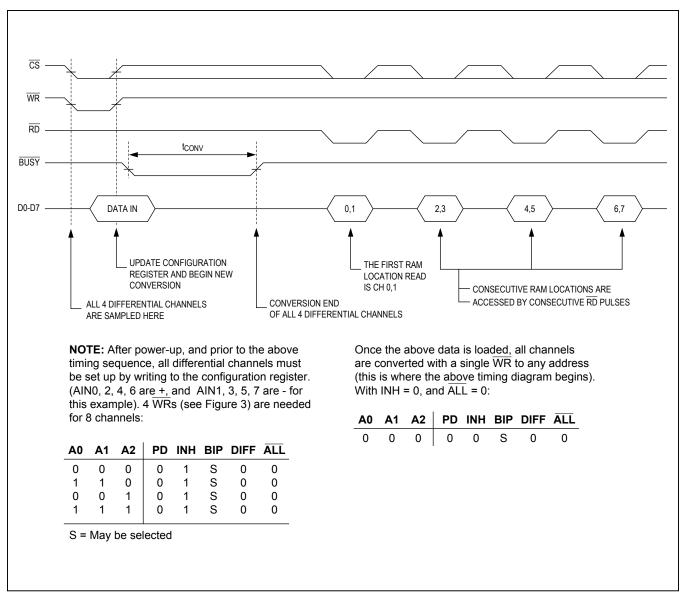

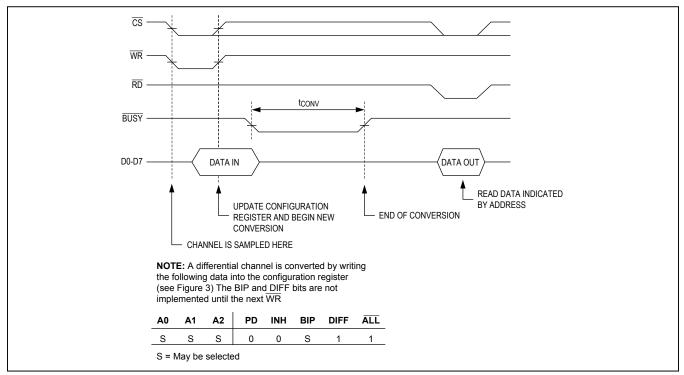

# Input/Output Mode, Single-Channel Conversion Timing

Figure 5a shows timing for a single-channel ( $\overline{ALL} = 1$ ), single-ended conversion; Figure 5b shows a differential conversion. With MODE floating, the configuration register is updated on the rising edge of WR. BUSY goes low at the beginning of the conversion and returns high when the channel designated by the configuration register has been converted. All channels are sampled on the falling edge of WR even if only a single channel has been requested. At conversion end, the  $\mu$ P can read the result for the selected channel with a single RD pulse. Subsequent RD pulses will access old conversion results remaining in other RAM locations. The next conversion is initiated with a WR pulse, regardless of the number of channels that have been read.

INH and A0–A2, in the configuration register, access locations in RAM. INH = 1 allows the RAM address pointer to be updated without starting a conversion. A READ pulse then reads the contents of the addressed location.

Figure 4a. Input/Output Mode Timing-Eight Single-Ended Conversions

Figure 4b. Input/Output Mode Timing–Four Differential Conversions

Figure 5a. Input/Output Mode Timing–Single-Channel, Single-Ended Conversion

Figure 5b. Input/Output Mode Timing–Single-Channel, Differential Conversion

# 8-/4-Channel ADCs with Simultaneous T/Hs and Reference

Figure 6. Input/Output Mode Timing–Reading Arbitrary RAM Locations

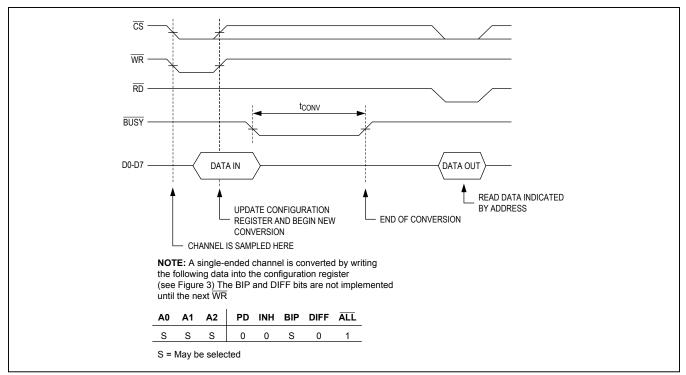

#### Hard-Wired Mode

For simpler applications, the MODE and V<sub>SS</sub> pins can be hard-wired to specify the type of conversion as outlined in Table 4. In this mode, the configuration register is not used, so input data on DO-D7 is ignored. For example, with MODE tied low, an 8-channel, single-ended conver sion begins with WR With MODE tied high, a 4-channel, differential conversion is init iated with WR. Again, the configuration register is not affected by the data present on 00-07. These conversions are otherwise identical to those shown in Figure 4.

#### **Analog Considerations**

#### **Internal Reference**

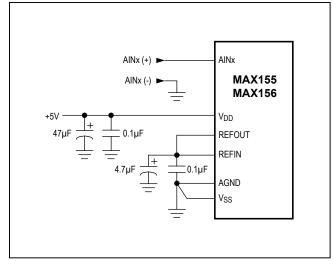

The internal 2.5V reference (REFOUT) must be bypassed to AGND (Figure 8a) with a 4.7 $\mu$ F electrolytic and a 0.1 $\mu$ F ceramic capacitor to ensure stability.

# Table 4. Hard-Wired Mode—MultiplexerSelections

| MODE            | V <sub>SS</sub> | CONVERSION TYPE                                                                |

|-----------------|-----------------|--------------------------------------------------------------------------------|

| OPEN<br>CIRCUIT | х               | Multiplexer configuration register determines conversion type. Not hard-wired. |

| 0               | AGND            | 8-Channel, Single-Ended, Unipolar<br>Conversion                                |

| 1               | AGND            | 4-Channel, Differential, Unipolar<br>Conversion                                |

| 0               | -5V             | 8-Channel, Single-Ended, Bipolar<br>Conversion                                 |

| 1               | -5V             | 4-Channel, Differential, Bipolar<br>Conversion                                 |

Figure 7a. Hard-Wired Mode Timing—Eight Single-Ended Conversions

Figure 7b. Hard-Wired Mode Timing—Eight Single-Ended Conversions

# 8-/4-Channel ADCs with Simultaneous T/Hs and Reference

Figure 8a. Internal Reference

#### **Extemal Reference**

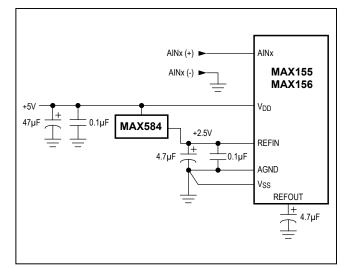

If an external voltage reference is used at REFIN, REFOUT must either be bypassed (Figure 8b) or disabled to prevent its output from oscillating and generating unwanted conversion noise elsewhere in the ADC. If component count is critical when using an external reference, REFOUT may be disabled by connecting it to V<sub>DD</sub>. In this case, the unused internal reference does not need a bypass cap. A disadvantage of tying REFOUT to V<sub>DD</sub> is that power-down current will be increased by about 250 $\mu$ A above the specification limits.

#### **Power-Down Mode**

The MAX155/MAX156 may be placed in a powered-down state by writing a 1 to the PD location in the configuration register (Table 1). The register may be updated while in this state (to change mux configurations or exit powerdown mode) and all register contents are retained; however no data can be read from RAM and no conversions can be started. The power-down command is implemented on  $\overline{WR}$ 's rising edge.

To minimize current drain, the MAX155/MAX156 internal reference is turned off during power-down. When returning to normal operation (PD = 0), up to 5ms may be needed to allow the reference to recharge its  $4.7\mu$ F bypass capacitor before a conversion is performed. If an external reference is used, and remains on during powerdown, a conversion can be started within 50µs after loading PD with a 0.

Figure 8b. External Reference, +2.5V Full Scale

#### Bypassing

A 47 $\mu$ F electrolytic and a 0.1 $\mu$ F ceramic capacitor should bypass V<sub>DD</sub> to AGND. If input signals below ground are expected, a negative supply is necessary. In that case, V<sub>SS</sub> should be bypassed to AGND with a 4.7 $\mu$ F and 0.1 $\mu$ F combination.

The internal reference requires a  $4.7\mu$ F and  $0.1\mu$ F combination. If an external voltage reference is used, bypass REFIN to AGND with a  $4.7\mu$ F capacitor close to the chip. When an external reference is used, REFOUT must still be either bypassed or connected to V<sub>DD</sub>.

#### **Track/Hold Amplifiers**

The MAX155/MAX156 T/H amplifiers' high input impedance usually requires no input buffering. All T/Hs sample simultaneously. For best results, the analog inputs should not exceed the power-supply rails ( $V_{DD}$ ,  $V_{SS}$ ) by more than 50mV.

The time required for the T/H to acquire an input signal for one channel is a function of how quickly the channel input capacitance is charged. If the source impedance of the input signal is high, acquisition takes longer, and more time must be allowed between conversions. Acquisition time is calculated by:

$t_{ACQ} = 8(R_S + R_{IN}) \times 4pF$  (but never less than 800ns)

where  $R_{IN}$  = 15k $\Omega$ , and  $R_S$  = source impedance of the ADC's input signal.

Figure 9a. Transfer Function—Unipolar Operation

Figure 9b. Transfer Function—Bipolar Operation

#### **Conversion Time**

Conversion time is calculated by:

#### $t_{CONV} = (9 \times N \times 2)/f_{CLK}$

where N is the number of channels converted. This includes one clock cycle of uncertainty. For a single channel and 5MHz clock, the conversion time is  $(9 \times 1 \times 2)/5$ MHz = 3.6µs. For the MAX155, the maximum conversion time for 8 channels is  $(9 \times 8 \times 2)/5$ MHz = 28.8µs. In the application example (Figure 10), six conversions are configured, and the conversion time is  $(9 \times 6 \times 2)/5$ MHz = 21.6µs.

# 8-/4-Channel ADCs with Simultaneous T/Hs and Reference

#### **Applications Information**

#### 9-Bit A/D Conversion

In I/O mode, a 9th bit of resolution can be created by performing two unipolar differential conversions with opposite input polarities (i.e., first with AIN0[+] and AIN1[-], then with AINO[-] and AIN1[+]). Only the A0 bit must be changed to reverse input channel polarity (Table 3). The sign reversal also occurs on the current write without a one conversion delay. For a differential input signal, one of the two conversions will read 0 while the other will contain an 8-bit result. The input polarity that provides the 8-bit result indicates the 9th (sign) bit. 4 channels can be measured this way. A major drawback of this technique is that many of the sampling features of the MAX155/MAX156 are defeated since two separate samples are needed

If only two 9-bit channels are needed, then two separate differential channels with reversed input polarities can be connected so that both input pairs sample at the same time. This way the simultaneoussampling advantages of the MAX155/MAX156 are retained.

#### **Typical I/O Mode Application**

The MAX155/MAX156 address and configuration inputs for this example were determined by selecting the desired channel configurations in Tables 2 and 3. Figure 10 illustrates the configuration outlined in Table 5.

| A2 | A1 | A0 | DIFF | BIP | FUNCTION                                 |  |

|----|----|----|------|-----|------------------------------------------|--|

| 0  | 0  | 1  | 1    | 1   | Channel (1, 0) Differential<br>Bipolar   |  |

| 0  | 1  | 0  | 0    | 0   | Channel 2 Single-Ended,<br>Unipolar      |  |

| 0  | 1  | 1  | 0    | 1   | Channel 3 Single-Ended,<br>Bipolar       |  |

| 1  | 0  | 0  | 0    | 1   | Channel 4 Single-Ended,<br>Bipolar       |  |

| 1  | 0  | 1  | 0    | 0   | Channel 5 Single-Ended,<br>Unipolar      |  |

| 1  | 1  | 0  | 1    | 0   | Channel (6. 7)<br>Differential, Unipolar |  |

#### **Table 5. Typical Multiplexer Configuration**

An A/D conversion in I/O mode involves the following steps:

Configure the mux by loading data into the configuration register based on selections from Table 2 and/or 3 (with INH = 1 and MODE = open circuit).

## 8-/4-Channel ADCs with Simultaneous T/Hs and Reference

For this example, 6 write operations (with each address and data setting in Table 5 above) load the mux after power-up.

Sample all selected channels with a WR pulse (and INH = 0), and update or rewrite any one location of the configuration register.

This write operation may be skipped by loading INH with a 0 on the last  $\overline{WR}$  of the above step. The conversion then starts on the 6th  $\overline{WR}$ . DIFF and SIP cannot be changed on the 6th  $\overline{WR}$  in the conversion is started at that time.

When the conversion starts, <u>BUSY</u> goes low while all selected channels are sequentially converted. Conversion results are stored in RAM and are ready to read when <u>BUSY</u> returns high.

- 3) Data is read from RAM with INH = L and consecutive RD strobes. Note that in the 6 channel configurations described in this example (Figure 10), 6 RD pulses access all available data, start with the differential channel (1, 0). Additional RD pulses loop around, accessing the lowest channel data again.

- 4) To start a new conversion cycle with the same mux configuration, repeat steps 2 and 3.

Figure 10. MAX155/MAX156 Typical Operating Circuit

# 8-/4-Channel ADCs with Simultaneous T/Hs and Reference

### **Ordering Information**

| PART        | TEMP RANGE     | PIN-<br>PACKAGE | ERROR<br>(LSBs) |

|-------------|----------------|-----------------|-----------------|

| MAX155ACPI+ | 0°C to +70°C   | 28 PDIP         | ±1⁄2            |

| MAX155BCPI+ | 0°C to +70°C   | 28 PDIP         | ±1              |

| MAX155ACWI+ | 0°C to +70°C   | 28 Wide SO      | ±1⁄2            |

| MAX155BCWI+ | 0°C to +70°C   | 28 Wide SO      | ±1              |

| MAX155BC/D  | 0°C to +70°C   | Dice*           | ±1              |

| MAX155AEPI+ | -40°C to +85°C | 28 PDIP         | ±1⁄2            |

| MAX155BEPI+ | -40°C to +85°C | 28 PDIP         | ±1              |

| MAX155AEWI+ | -40°C to +85°C | 28 Wide SO      | ±1⁄2            |

| MAX155BEWI+ | -40°C to +85°C | 28 Wide SO      | ±1              |

| MAX156ACNG+ | 0°C to +70°C   | 24 PDIP         | ±1⁄2            |

| MAX156BCNG+ | 0°C to +70°C   | 24 PDIP         | ±1              |

| MAX156ACWI+ | 0°C to +70°C   | 28 Wide SO      | ±1⁄2            |

| MAX156BCWI+ | 0°C to +70°C   | 28 Wide SO      | ±1              |

| MAX156BC/D  | 0°C to +70°C   | Dice*           | ±1              |

| MAX156AENG+ | -40°C to +85°C | 24 PDIP         | ±1⁄2            |

| MAX156BENG+ | -40°C to +85°C | 24 PDIP         | ±1              |

| MAX156AEWI+ | -40°C to +85°C | 28 Wide SO      | ±1⁄2            |

| MAX156BEWI+ | -40°C to +85°C | 28 Wide SO      | ±1              |

### **Package Information**

For the latest package outline information and land patterns (footprints), go to <u>www.maximintegrated.com/packages</u>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE<br>TYPE | PACKAGE<br>CODE | OUTLINE NO.    | LAND<br>PATTERN<br>NO. |  |

|-----------------|-----------------|----------------|------------------------|--|

| 24 PDIP         | N24+8           | <u>21-0043</u> | _                      |  |

| 28 PDIP         | P28+7           | <u>21-0044</u> | _                      |  |

| 28 Wide SO      | W28+3           | 21-0042        | <u>90-0109</u>         |  |

#### **Chip Information**

PROCESS: BICMOS

+Denotes a lead(Pb)-free/RoHS-compliant package.

\*Contact factory for dice specifications.

# 8-/4-Channel ADCs with Simultaneous T/Hs and Reference

### **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                                                   | PAGES<br>CHANGED |

|--------------------|------------------|---------------------------------------------------------------|------------------|

| 0                  | 11/91            | Initial release                                               | —                |

| 1                  | 6/94             | Revised Figure 9a                                             | 16               |

| 2                  | 1/12             | Removed military grade packages and updated stylistic changes | 1–5, 18–20       |

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim Integrated's website at www.maximintegrated.com.

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.