# **MAS9090B**

# **LOW VOLTAGE 14-BIT LINEAR CODEC**

- 14-bit linear analog to digital and digital to analog converters

- 8-bit A-law or  $\mu$ -law companded analog to digital and digital to analog converters

# **DESCRIPTION**

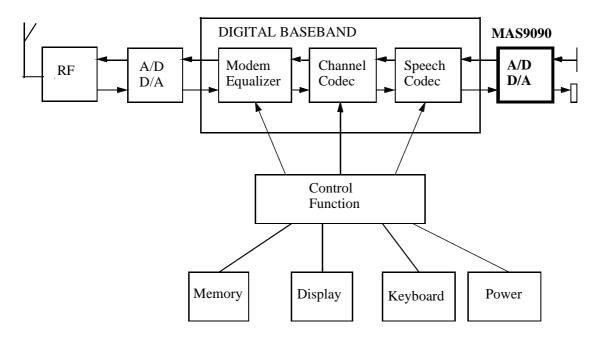

The MAS9090 is a high performance low power PCM CODEC and filter device tailored to implement the audio front-end functions required by the low voltage/low power consumption digital terminals.

### **FEATURES**

- Single 2.7-3.6 V Power supply

- -30°C to 85°C temperature operation range

- 11 mW operating power (typ. at 2.7V)

- 15 mW operating power (typ. at 3.0V)

- 27 mW operating power (typ. at 3.6V)

- Digital bandpass filters

- ±0.5 dB absolute gain accuracy (untrimmed)

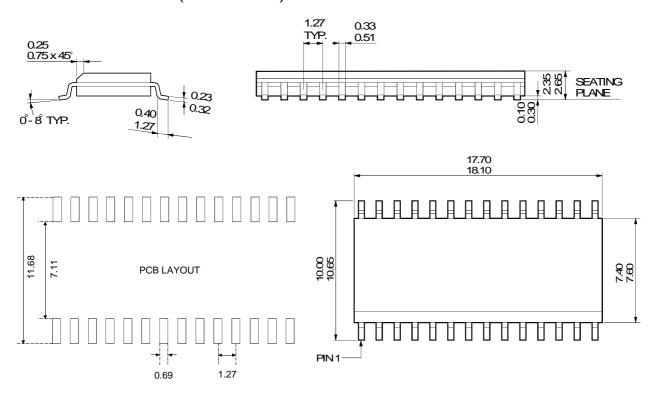

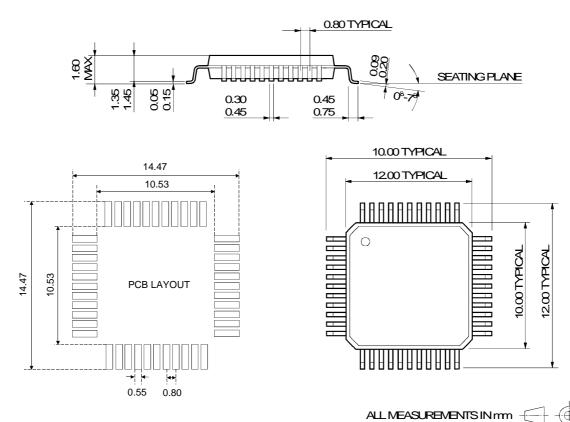

- 28-pin SO and 44-pin TQFP packages

- Pin compatible with ST5090 and ST5092

### **APPLICATIONS**

- GSM digital cellular telephones

- · Battery operated audio front-ends for DSPs

- ISDN Terminals

- CT2 and DECT digital cordless telephones

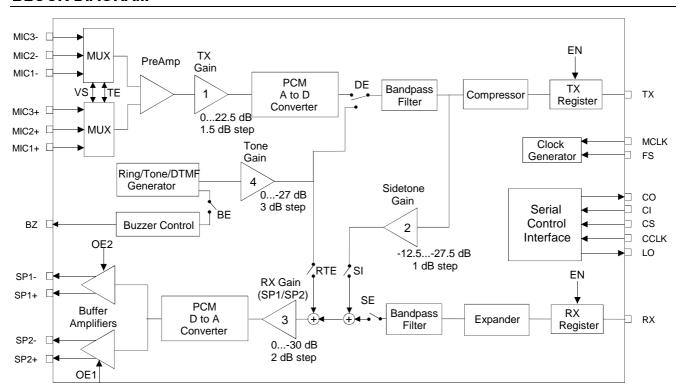

### **BLOCK DIAGRAM**

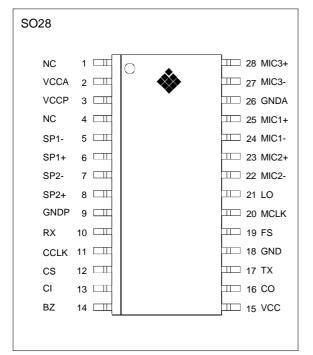

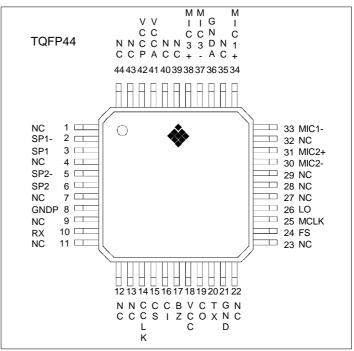

#### **PIN CONFIGURATION**

#### PIN DESCRIPTION

| Pin Name | Pin N | lumber                                                            | Туре | Function                                                                                                                        |

|----------|-------|-------------------------------------------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------|

| -        | SO28  | TQFP44                                                            |      |                                                                                                                                 |

|          | 1,4   | 1,4,7,9<br>11,12,13<br>22,23,27<br>28,29,32<br>35,39,40,<br>43,44 |      | No connection.                                                                                                                  |

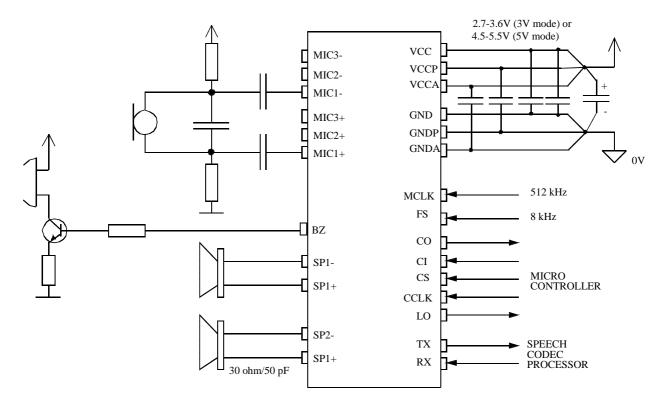

| VCCA     | 2     | 41                                                                | Р    | Positive power supply input for analog section.                                                                                 |

| VCCP     | 3     | 42                                                                | Р    | Positive power supply input for speaker amplifiers.                                                                             |

| SP1-     | 5     | 2                                                                 | AO   | Speaker 1 amplifier negative output.                                                                                            |

| SP1+     | 6     | 3                                                                 | AO   | Speaker 1 amplifier positive output.                                                                                            |

| SP2-     | 7     | 5                                                                 | AO   | Speaker 2 amplifier negative output.                                                                                            |

| SP2+     | 8     | 6                                                                 | AO   | Speaker 2 amplifier positive output.                                                                                            |

| GNDP     | 9     | 8                                                                 | G    | Speaker amplifiers.                                                                                                             |

| RX       | 10    | 10                                                                | DI   | Receive data input.                                                                                                             |

| CCLK     | 11    | 14                                                                | DI   | Control clock input. Shifts serially into CI and CO when CS is low. CCLK is asynchronous with other system clocks.              |

| CS       | 12    | 15                                                                | DI   | Chip select input.                                                                                                              |

| CI       | 13    | 16                                                                | DI   | Control data input.                                                                                                             |

| BZ       | 14    | 17                                                                | AO   | Buzzer driver output.                                                                                                           |

| VCC      | 15    | 18                                                                | Р    | Positive power supply input for the digital section. VCCA, VCCP AND VCC must be connected together.                             |

| CO       | 16    | 19                                                                | DO   | Control data output.                                                                                                            |

| TX       | 17    | 20                                                                | DO   | Transmit data output. Data is shifted out on this during the assigned transmit slots. Otherwise, TX is on high impedance state. |

| GND      | 18    | 21                                                                | G    | Ground for the digital section.                                                                                                 |

| FS       | 19    | 24                                                                | DI   | Frame sync input. This 8kHz signal defines the start of the TX and RX frames.                                                   |

### PIN DESCRIPTION

| Pin Name | Pin Nu | umber | Туре | Function                                        |

|----------|--------|-------|------|-------------------------------------------------|

| MCLK     | 20     | 25    | DI   | Master clock input. Must be 512, 1536, 2048 kHz |

| LO       | 21     | 26    | DO   | Value of bit DO of CR1.                         |

| MIC2-    | 22     | 30    | Al   | Negative differential input for MIC2.           |

| MIC2+    | 23     | 31    | Al   | Positive differential input for MIC2.           |

| MIC1-    | 24     | 33    | Al   | Negative differential input for MIC1.           |

| MIC1+    | 25     | 34    | Al   | Positive differential input for MIC1.           |

| GNDA     | 26     | 36    | G    | GNDA analog ground.                             |

| MIC3-    | 27     | 37    | Al   | Negative differential input for MIC3.           |

| MIC3+    | 28     | 38    | Al   | Positive differential input for MIC3.           |

### **ABSOLUTE MAXIMUM RATINGS**

| Parameter                     | Symbol          | Conditions             | N | /lin | Max                | Unit |

|-------------------------------|-----------------|------------------------|---|------|--------------------|------|

| Supply Voltage                | V <sub>CC</sub> |                        |   |      | 5.0                | V    |

| Voltage at MIC                |                 | V <sub>CC</sub> < 3.6V | - | -1   | V <sub>CC</sub> +1 | V    |

| Current at any digital output |                 |                        |   |      | 50                 | mA   |

| Voltage at any digital input  |                 | V <sub>CC</sub> < 3.6V | - | -1   | V <sub>CC</sub> +1 | V    |

| Storage Temperature           | Ts              |                        |   | 55   | +125               | ∘C   |

## RECOMMENDED OPERATION CONDITIONS

| Parameter             | Symbol   | Conditions       | Min | Тур | Max | Unit |

|-----------------------|----------|------------------|-----|-----|-----|------|

| Supply Voltage        | $V_{CC}$ | 3.0V mode (SV=0) | 2.7 | 3.0 | 3.6 | V    |

| Operating Temperature | $T_A$    |                  | -30 |     | +85 | ∘C   |

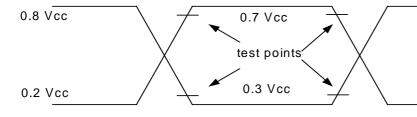

# AC, TESTING INPUT, OUTPUT WAVEFORM

AC testing: inputs are driven at 0.8Vcc for a logic '1' and 0.2Vcc for a logic '0'. Timing measurements are made at 0.7Vcc for a '1' and 0.3 Vcc for a '0'.

# **ELECTRICAL CHARACTERISTICS**

# ◆ Digital Inputs/Outputs

( $V_{CC}$  = 2.7-3.6V,  $T_A$  = -30°C to +85°C, unless otherwise specified)

| Parameter                        | Symbol | Conditions                                                                | Min                                          | Тур | Max                                      | Unit |

|----------------------------------|--------|---------------------------------------------------------------------------|----------------------------------------------|-----|------------------------------------------|------|

| Input low voltage                | VIL    | All digital inputs DC<br>All digital inputs AC                            |                                              |     | 0.3V <sub>CC</sub><br>0.2V <sub>CC</sub> | V    |

| Input high voltage               | VIH    | All digital inputs DC All digital inputs AC                               | 0.7V <sub>CC</sub><br>0.8V <sub>CC</sub>     |     |                                          | V    |

| Output low voltage               | VOL    | All digital outputs, IL = 10μA<br>All digital outputs, IL = 2mA           |                                              |     | 0.1<br>0.4                               | V    |

| Output high voltage              | VOH    | All digital outputs, IL = 10μA<br>All digital outputs, IL = 2mA           | V <sub>CC</sub> -0.1<br>V <sub>CC</sub> -0.4 |     |                                          | V    |

| Input low current                | IIL    | Any digital input,<br>GND < V <sub>IN</sub> < V <sub>IL</sub>             | -10                                          |     | 10                                       | μΑ   |

| Input high current               | IIH    | Any digital input,<br>V <sub>IH</sub> < V <sub>IN</sub> < V <sub>CC</sub> | -10                                          |     | 10                                       | μΑ   |

| Output current in high impedance | IOZ    | TX and CO                                                                 | -10                                          |     | 10                                       | μΑ   |

## ◆ Analog Inputs/Outputs

( $V_{CC} = 2.7-3.6V$ ,  $T_A = -30$ °C to +85°C, unless otherwise specified)

| Parameter                                     | Symbol            | Conditions                                                        | Min  | Тур | Max  | Unit |

|-----------------------------------------------|-------------------|-------------------------------------------------------------------|------|-----|------|------|

| Input leakage                                 | I <sub>MIC</sub>  | GND < V <sub>MIC</sub> < V <sub>CC</sub> (active mic)             | -100 | ±20 | +100 | μΑ   |

| Input resistance                              | R <sub>MIC</sub>  | GND < V <sub>MIC</sub> < V <sub>CC</sub>                          | 50   |     |      | kΩ   |

| Load resistance                               | R <sub>LSP1</sub> | SP1+ to SP1-                                                      | 30   |     |      | Ω    |

| Load capacitance                              | C <sub>LSP1</sub> | SP1+ to SP1-                                                      |      | 50  |      | nF   |

| Output resistance                             | R <sub>OSP1</sub> | Steady zero PCM code applied to RX, I = 1mA                       |      | 1.0 |      | Ω    |

| Differential offset voltage from SP1+ to SP1- | V <sub>OSP1</sub> | Alternating zero PCM code applied to RX, R <sub>L</sub> = 30 ohms | -100 | 0   | +100 | mV   |

| Load resistance                               | R <sub>LSP2</sub> | SP2+ to SP2-                                                      | 30   |     |      | Ω    |

| Load capacitance                              | C <sub>LSP2</sub> | SP2+ to SP2-                                                      |      | 50  |      | nF   |

| Input resistance                              | R <sub>MIC</sub>  | GND < V <sub>MIC</sub> < V <sub>CC</sub>                          | 50   |     |      | kΩ   |

| Output resistance                             | R <sub>OSP2</sub> | Steady zero PCM code applied to RX, I = 1mA                       |      | 1.0 |      | Ω    |

| Differential offset voltage from SP2+ to SP2- | V <sub>OSP2</sub> | Alternating zero PCM code applied to RX, R <sub>L</sub> = 30 ohms | -100 | 0   | +100 | mV   |

## **◆** Power Dissipation

(V<sub>CC</sub> = 2.7-3.6V,  $T_A$  = -30°C to +85°C, unless otherwise specified)

| Parameter                  | Symbol             | Conditions                         | Min | Тур  | Max | Unit |

|----------------------------|--------------------|------------------------------------|-----|------|-----|------|

| Power down current at 3.0V | I <sub>CC0</sub>   | CCLK, CI = 0.1V<br>CS = VCC - 0.1V |     | 0.08 | 10  | μΑ   |

| Power up current at 2.7V   | I <sub>CC1</sub>   | SP1 and SP2 not loaded             |     | 4    | 6   | mA   |

| Power up current at 3.0V   | I <sub>CC1</sub>   | SP1 and SP2 not loaded             |     | 5    | 8   | mA   |

| Power up current at 3.6V   | I <sub>CC1</sub>   | SP1 and SP2 not loaded             |     | 7.5  | 12  | mA   |

| SP1 short circuit current  | I <sub>SHORT</sub> |                                    |     | 130  |     | mA   |

# TIMING SPECIFICATIONS

# **◆ Master Clock Timing**

| Parameter                                            | Symbol            | Conditions                                       | Min | Тур                 | Max  | Unit |

|------------------------------------------------------|-------------------|--------------------------------------------------|-----|---------------------|------|------|

| Frequency of MCLK                                    | f <sub>MCLK</sub> | programmable                                     |     | 512<br>1536<br>2048 |      | kHz  |

| Period of MCLK high/low f <sub>MCK</sub> = 512       | t <sub>WHM</sub>  | Measured from V <sub>IH</sub> to V <sub>IH</sub> | 878 |                     | 1074 | ns   |

| Period of MCLK high<br>f <sub>MCK</sub> = 1536, 2048 | t <sub>WHM</sub>  | Measured from V <sub>IH</sub> to V <sub>IH</sub> | 80  |                     |      | ns   |

| Period of MCLK low<br>f <sub>MCK</sub> = 1536, 2048  | t <sub>WLM</sub>  | Measured from V <sub>IL</sub> to V <sub>IL</sub> | 80  |                     |      | ns   |

| Rise time of MCLK                                    | t <sub>RM</sub>   | Measured from V <sub>IL</sub> to V <sub>IH</sub> |     |                     | 30   | ns   |

| Fall time of MCLK                                    | t <sub>FM</sub>   | Measured from V <sub>IH</sub> to V <sub>IL</sub> |     |                     | 30   | ns   |

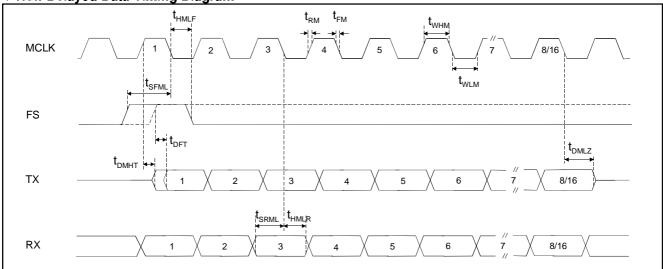

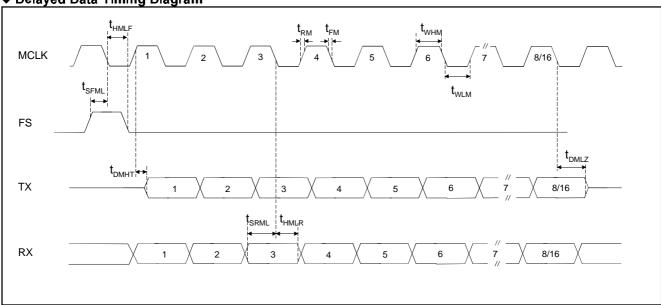

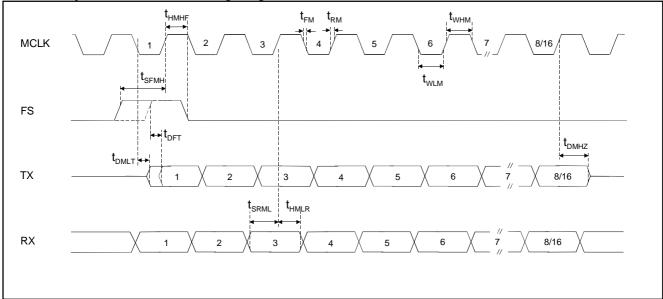

# ◆ PCM Interface Timing

| Parameter                               | Symbol            | Conditions                            | Min | Тур | Max | Unit |

|-----------------------------------------|-------------------|---------------------------------------|-----|-----|-----|------|

| Hold time, MCLK low to FS low           | t <sub>HMLF</sub> |                                       | 17  |     |     | ns   |

| Setup time, FS high to MCLK low         | t <sub>SFML</sub> |                                       | 30  |     |     | ns   |

| Delay time, MCLK high to valid TX data  | t <sub>DMHT</sub> | Load = 100pF                          |     |     | 100 | ns   |

| Delay time, MCLK low to TX disabled     | t <sub>DMLZ</sub> |                                       | 10  |     | 100 | ns   |

| Delay time, FS high to valid TX data    | t <sub>DFT</sub>  | Load = 100pF<br>non-delayed mode only |     |     | 100 | ns   |

| Setup time, RX data valid to MCLK low   | t <sub>SRML</sub> |                                       | 20  |     |     | ns   |

| Hold time, MCLK low to invalid RX data  | t <sub>HMLR</sub> |                                       | 10  |     |     | ns   |

| Hold time, MCLK high to FS low          | t <sub>HMHF</sub> |                                       | 30  |     |     | ns   |

| Setup time, FS high to MCLK high        | t <sub>SFMH</sub> |                                       | 30  |     |     | ns   |

| Delay time, MCLK low to valid TX data   | t <sub>DMLT</sub> | Load = 100pF                          |     |     | 100 | ns   |

| Delay time, MCLK high to TX disabled    | t <sub>DMHZ</sub> |                                       | 10  |     | 100 | ns   |

| Hold time, MCLK high to invalid RX data | t <sub>HMHR</sub> |                                       | 20  |     |     | ns   |

In companded mode the timing is applied to 8 bits instead of 16 bits.

# **TIMING SPECIFICATIONS**

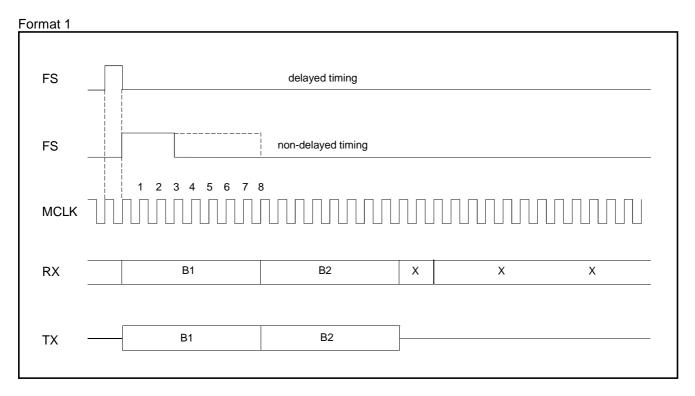

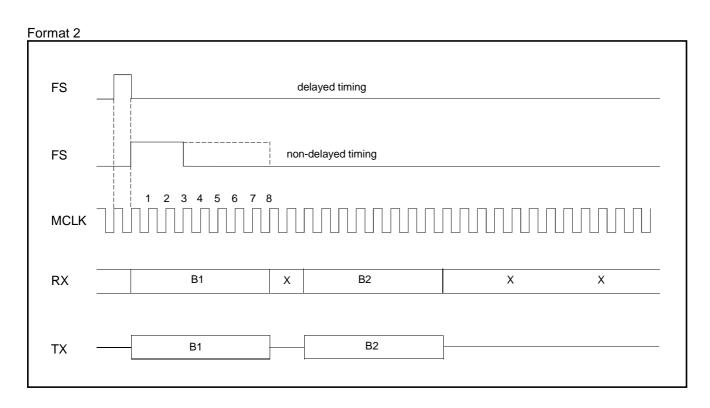

◆ Delayed Data Timing Diagram

In companded mode the timing is applied to 8 bits instead of 16 bits.

In companded mode the timing is applied to 8 bits instead of 16 bits.

# TIMING SPECIFICATIONS

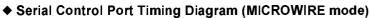

# ◆ Serial Control Port Timing

| Parameter                                                            | Symbol             | Conditions                                       | Min | Тур | Max   | Unit |

|----------------------------------------------------------------------|--------------------|--------------------------------------------------|-----|-----|-------|------|

| Frequency of CCLK                                                    | f <sub>CCLK</sub>  |                                                  |     |     | 2.048 | MHz  |

| Period of CCLK high                                                  | t <sub>WHC</sub>   | Measured from V <sub>IH</sub> to V <sub>IH</sub> | 160 |     |       | ns   |

| Period of CCLK low                                                   | t <sub>WLC</sub>   | Measured from V <sub>IL</sub> to V <sub>IL</sub> | 160 |     |       | ns   |

| Rise time of CCLK                                                    | t <sub>RC</sub>    | Measured from V <sub>IL</sub> to V <sub>IH</sub> |     |     | 50    | ns   |

| Fall time of CCLK                                                    | t <sub>FC</sub>    | Measured from V <sub>IH</sub> to V <sub>IL</sub> |     |     | 50    | ns   |

| Hold time, CCLK high to CS low                                       | t <sub>HCHS</sub>  |                                                  | 10  |     |       | ns   |

| Setup time, CS low to CCLK high                                      | t <sub>SSLCH</sub> |                                                  | 50  |     |       | ns   |

| Setup time, valid CI data to CCLK high                               | t <sub>SDCH</sub>  |                                                  | 50  |     |       | ns   |

| Hold time, CCLK high to invalid CI data                              | t <sub>HCHD</sub>  |                                                  | 50  |     |       | ns   |

| Delay time, CCLK low to valid CO data                                | t <sub>DCLD</sub>  | Load = 100 pF                                    |     |     | 80    | ns   |

| Delay time, CS low to valid CO data                                  | t <sub>DSD</sub>   |                                                  |     |     | 50    | ns   |

| Delay time, CS high or 8 <sup>th</sup> CCLK low to CO high impedance | t <sub>DSZ</sub>   |                                                  | 10  |     | 80    | ns   |

| Hold time, 8 <sup>th</sup> CCLK high to CS high                      | t <sub>H8CHS</sub> |                                                  | 100 |     |       | ns   |

| Setup time, CS high to CCLK high                                     | t <sub>SSHCH</sub> |                                                  | 100 |     |       | ns   |

### ◆ Absolute levels at MIC1/MIC2/MIC3

( $V_{CC}$  = 2.7-3.6V,  $T_A$  = -30°C to +85°C, unless otherwise specified)

| Parameter      | Conditions                               | Min | Тур   | Max | Unit       |

|----------------|------------------------------------------|-----|-------|-----|------------|

| 0 dBm0 level   | Transmit amps connected for 20 dB gain   |     | 49.26 |     | $mV_{RMS}$ |

| Overload level |                                          |     | 70.71 |     | $mV_{RMS}$ |

| 0 dBm0 level   | Transmit amps connected for 42.5 dB gain |     | 3.694 |     | $mV_{RMS}$ |

| Overload level |                                          |     | 5.302 |     | $mV_{RMS}$ |

## ◆ Absolute levels at SP1 / SP2 (differentially measured)

( $V_{CC}$  = 2.7-3.6V,  $T_A$  = -30°C to +85°C, unless otherwise specified)

| Parameter    | Conditions             | Min | Тур   | Max | Unit       |

|--------------|------------------------|-----|-------|-----|------------|

| 0 dBm0 level | Receive gains = 0 dB   |     | 1.965 |     | $V_{RMS}$  |

| 0 dBm0 level | Receive gains = -30 dB |     | 61.85 |     | $mV_{RMS}$ |

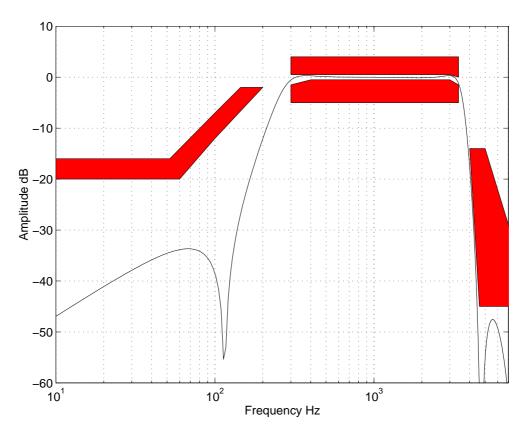

## ◆ Transmit path amplitude response

| Parameter                                                | Symbol    | (V <sub>CC</sub> = 2.7-3.6V, T                                                                                                                                            | Min                  | Тур               | Max               | Unit |

|----------------------------------------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-------------------|-------------------|------|

| Transmit gain absolute accuracy, HPT = 0 HPT = 1         | $G_XA$    | TX gain set to maximum, measure deviation of digital PCM code from ideal 0 dBm0 PCM code at TX                                                                            | -0.5<br>-0.4         | 0<br>0.1          | 0.5<br>0.6        | dB   |

| Transmit gain variation with programmed gain             | $G_{XAG}$ | Measure TX gain over the range (from max to min). Calculate the deviation from the programmed gain relative to $G_{XA}$ , i.e. $G_{XAG} = G_{actual} - G_{prog} - G_{XA}$ | -0.5                 |                   | 0.5               | dB   |

| Transmit gain variation with temperature                 | $G_{XAT}$ | Measured relative to $G_{XA}$<br>min. gain < $G_X$ < max. gain                                                                                                            | -0.1                 |                   | 0.1               | dB   |

| Transmit gain variation with supply                      | $G_{XAV}$ | Measured relative to $G_{XA}$<br>$G_X$ = maximum gain                                                                                                                     | -0.1                 |                   | 0.1               | dB   |

| Transmit gain variation with frequency                   | $G_{XAF}$ | Relative to 1.015625 kHz, multitone test technique used min. gain $< G_X < max$ . gain                                                                                    |                      |                   |                   |      |

| HPT=0                                                    |           | f = 60 Hz<br>f = 100 Hz<br>f = 200 Hz                                                                                                                                     |                      | -34<br>-36<br>-11 | -33<br>-35<br>-10 | dB   |

|                                                          |           | f = 300 Hz<br>f = 400 Hz to 3000 Hz                                                                                                                                       | -1.5<br>-0.5         | -0.7              | 0.5<br>0.5        |      |

|                                                          |           | f = 3400 Hz<br>f = 4000 Hz                                                                                                                                                | -1.5                 | -1.3<br>-17       | 0.0<br>-16        |      |

|                                                          |           | f = 4600 Hz<br>f = 8000 Hz                                                                                                                                                |                      | -62<br>-68        | -61<br>-67        |      |

| HPT=1                                                    |           | f = 60 Hz to 3000 Hz<br>f = 3000 to 8000 Hz, see HPT=0                                                                                                                    | -0.5                 |                   | 0.5               | dB   |

| Transmit gain variation with signal level                | $G_{XAL}$ | Sinusoidal test method reference level = -10 dBm0                                                                                                                         |                      |                   |                   |      |

|                                                          |           | $V_{MIC}$ = -40 dBm0 to +3.0 dBm0<br>$V_{MIC}$ = -50 dBm0 to -40 dBm0<br>$V_{MIC}$ = -55 dBm0 to -50 dBm0                                                                 | -0.5<br>-0.5<br>-1.2 |                   | 0.5<br>0.5<br>1.2 | dB   |

| Fone Generator gain G <sub>XTONE</sub> absolute accuracy |           | Measure deviation of digital PCM code from ideal 0dBm0 PCM code at TX                                                                                                     | -0.3                 |                   | 0.6               | dB   |

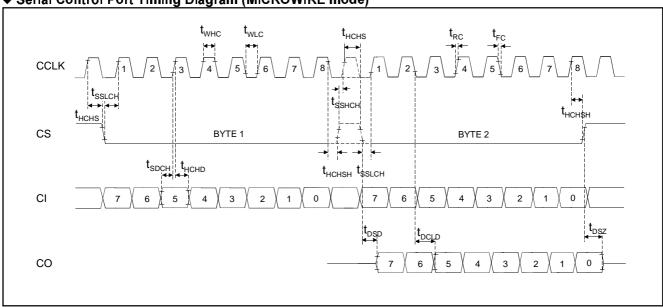

# ◆ Receive path amplitude response

( $V_{CC} = 2.7-3.6V$ ,  $T_A = -30$ °C to +85°C, unless otherwise specified)

| Parameter                                                | Symbol             | $(V_{CC} = 2.7-3.6V, I_A = $                                                                                                                                                                    | Min                  | Typ             | Max        | Unit |

|----------------------------------------------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----------------|------------|------|

| Receive gain absolute accuracy, HPX = 0                  | $G_{RA1}$          | RX gain programmed to maximum, apply -6dBm0 PCM code to RX,                                                                                                                                     | -0.5<br>-0.4         | 0               | 0.5<br>0.6 | dB   |

| HPX = 1  Receive gain absolute accuracy, HPX = 0 HPX = 1 | G <sub>RA2</sub>   | measure SP1+ to SP1- RX gain programmed to maximum, apply -6dBm0 PCM code to RX, measure SP2+ to SP2-                                                                                           | -0.4<br>-0.5<br>-0.4 | 0.1<br>0<br>0.1 | 0.5<br>0.6 | dB   |

| Receive gain variation with programmed gain              | G <sub>RAG1</sub>  | Measure SP1 gain over the range from maximum to minimum setting, calculate the deviation from the programmed gain relative to $G_{RA1}$ , i.e. $G_{RAG1} = G_{actual} - G_{prog} - G_{RA1}$     | -0.5                 | <b>3.</b> .     | 0.5        | dB   |

| Receive gain variation with programmed gain              | $G_{RAG2}$         | Measure SP2 gain over the range from maximum to minimum setting, calculate the deviation from the programmed gain relative to $G_{RA2}$ , i.e. $G_{RAG2} = G_{actual}$ - $G_{prog}$ - $G_{RA2}$ | -0.5                 |                 | 0.5        | dB   |

| Receive gain variation with temperature                  | $G_{RAT}$          | Measured relative to $G_{RA1}$ or $G_{RA2}$ min. gain < $G_R$ < max. gain                                                                                                                       | -0.1                 |                 | 0.1        | dB   |

| Receive gain variation with supply                       | G <sub>RAV</sub>   | Measured relative to $G_{RA1}$ or $G_{RA2}$ $G_R$ = maximum gain                                                                                                                                | -0.1                 |                 | 0.1        | dB   |

| Receive gain variation with frequency (SP1 and SP2)      | $G_RAF$            | Relative to 1.015625 kHz, multitone test technique used. min. gain < G <sub>R</sub> < max. gain.                                                                                                |                      |                 |            |      |

| HPR = 0                                                  |                    | f = 60 Hz                                                                                                                                                                                       |                      | -34             | -33        | dB   |

|                                                          |                    | f = 100 Hz                                                                                                                                                                                      |                      | -38             | -35        |      |

|                                                          |                    | f = 200 Hz                                                                                                                                                                                      |                      | -12             | -10        |      |

|                                                          |                    | f = 300 Hz                                                                                                                                                                                      | -1.5                 | -0.5            | 0.5        |      |

|                                                          |                    | f = 400 Hz to 3000 Hz                                                                                                                                                                           | -0.5                 |                 | 0.5        |      |

|                                                          |                    | f = 3400 Hz                                                                                                                                                                                     | -1.5                 | -1.3            | 0.0        |      |

|                                                          |                    | f = 4000 Hz                                                                                                                                                                                     |                      | -15             | -14        |      |

| HPR = 1                                                  |                    | f = 60 Hz to 3000 Hz<br>f = 3000 to 4000 Hz, see HPR=0                                                                                                                                          | -0.5                 |                 | 0.5        |      |

| Receive gain variation with signal level (SP1)           | G <sub>RAL1</sub>  | Sinusoidal test method, reference level = -10 dBm0                                                                                                                                              |                      |                 |            |      |

| 3 ( ,                                                    |                    | RX = -40  dBm0 to  -3  dBm0                                                                                                                                                                     | -0.5                 |                 | 0.5        | dB   |

|                                                          |                    | RX = -50 dBm0 to -40 dBm0                                                                                                                                                                       | -0.5                 |                 | 0.5        |      |

|                                                          |                    | RX = -55 dBm0 to -50 dBm0                                                                                                                                                                       | -1.2                 |                 | 1.2        |      |

| Receive gain variation with signal level (SP2)           | G <sub>RAL2</sub>  | Sinusoidal test method, reference level = -10 dBm0                                                                                                                                              |                      |                 |            |      |

|                                                          |                    | RX = -40 dBm0 to -3 dBm0                                                                                                                                                                        | -0.5                 |                 | 0.5        | dB   |

|                                                          |                    | RX = -50 dBm0 to -40 dBm0                                                                                                                                                                       | -0.5                 |                 | 0.5        |      |

|                                                          |                    | RX = -55 dBm0 to -50 dBm0                                                                                                                                                                       | -1.2                 |                 | 1.2        |      |

| Tone Generator gain absolute accuracy                    | G <sub>RTONE</sub> | Measure signal level at SP1                                                                                                                                                                     | -1                   |                 | 1          | dB   |

# ◆ Envelope delay distortion with frequency

( $V_{CC} = 2.7\text{-}3.6V$ ,  $T_A = -30^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise specified)

| Parameter          | Symbol    | (VCC = 2.7-3.6V, TA = -30- | Min | Тур | Max | Unit |

|--------------------|-----------|----------------------------|-----|-----|-----|------|

| TX delay, absolute | $D_{TXA}$ | f = 1600 Hz                |     | 800 |     | μs   |

| TX delay, relative | $D_{TXR}$ | f = 500 - 600 Hz           |     | 15  |     | μs   |

|                    |           | f = 600 - 800 Hz           |     | 20  |     |      |

|                    |           | f = 800 - 1000 Hz          |     | 5   |     |      |

|                    |           | f = 1000 - 1600 Hz         |     | -15 |     |      |

|                    |           | f = 1600 - 2600 Hz         |     | -40 |     |      |

|                    |           | f = 2600 - 2800 Hz         |     | -50 |     |      |

|                    |           | f = 2800 - 3000 Hz         |     | -50 |     |      |

| RX delay, absolute | $D_RXA$   | f = 1600 Hz                |     | 800 |     | μs   |

| RX delay, relative | $D_{RXR}$ | f = 500 - 600 Hz           |     | 15  |     | μs   |

|                    |           | f = 600 - 800 Hz           |     | 20  |     |      |

|                    |           | f = 800 - 1000 Hz          |     | 5   |     |      |

|                    |           | f = 1000 - 1600 Hz         |     | -15 |     |      |

|                    |           | f = 1600 - 2600 Hz         |     | -40 |     |      |

|                    |           | f = 2600 - 2800 Hz         |     | -50 |     |      |

|                    |           | f = 2800 - 3000 Hz         |     | -50 |     |      |

### **♦** Noise

( $V_{CC}$  = 2.7-3.6V,  $T_A$  = -30°C to +85°C, unless otherwise specified)

| Parameter                                                                      | Symbol             | Conditions                                                                                                                                                                              | Min | Тур        | Max  | Unit          |

|--------------------------------------------------------------------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------|------|---------------|

| TX noise, P weighted                                                           | $N_{TXP}$          | $V_{MIC} = 0V$ , DE = 0,<br>TX gain set to 15 dB                                                                                                                                        |     | -72*       | -68* | dBm0          |

| RX noise, A weighted<br>differential (SP+ to SP-)<br>single-ended (SP to GNDP) | N <sub>RXA</sub>   | Receive PCM code = positive zero SI = 0, RTE = 0, max. gain                                                                                                                             |     | 140*<br>80 | 190* | $\mu V_{RMS}$ |

| Noise, single frequency                                                        | N <sub>S</sub>     | MIC = 0V,<br>loop around measurement from<br>f = 0 Hz to 100 kHz                                                                                                                        |     | -76        | -50  | dBm0          |

| PSRR, TX                                                                       | PPSR <sub>TX</sub> | $\begin{aligned} &\text{MIC} = \text{OV} \\ &\text{V}_{\text{CC}} = 3.3 \text{V}_{\text{DC}} + 50 \text{ mV}_{\text{RMS}} \\ &\text{f} = 0 \text{ Hz to } 50 \text{ kHz} \end{aligned}$ | 30  | 44         |      | dB            |

| PSRR, RX                                                                       | PPSR <sub>RX</sub> | PCM code equals positive zero<br>$V_{CC} = 3.3 V_{DC} + 50 \text{ mV}_{RMS}$                                                                                                            |     |            |      |               |

|                                                                                |                    | f = 0 Hz to 4 kHz                                                                                                                                                                       | 30  | 54         |      | dB            |

|                                                                                |                    | f = 4  kHz to  50  kHz                                                                                                                                                                  | 30  |            |      |               |

| Spurious out-band signal at the output (relative to signal)                    | S <sub>os</sub>    | RX input set to -6 dBm0 PCM code, 300 Hz 3400 Hz input PCM code applied at RX                                                                                                           |     |            |      |               |

|                                                                                |                    | 4600 Hz - 5600 Hz                                                                                                                                                                       |     |            | -45  | dB            |

|                                                                                |                    | 5600 Hz - 7600 Hz                                                                                                                                                                       |     |            | -45  |               |

|                                                                                |                    | 7600 Hz - 8400 Hz                                                                                                                                                                       |     |            | -50  |               |

|                                                                                |                    | 8400 Hz - 20000 Hz                                                                                                                                                                      |     |            | -50  |               |

| Common mode rejection ratio                                                    | CMRR <sub>X</sub>  | MIC = -6dBm0, max. gain                                                                                                                                                                 |     | -74        | -45  | dB            |

| Tone generator noise                                                           | N <sub>TONE</sub>  | DTMF frequencies, TX/SP output                                                                                                                                                          |     | -36        | -28  | dBm0          |

<sup>\*</sup>Limit is used to speed up automatic testing. True value is less.

## **◆** Distortion

$(V_{CC} = 2.7-3.6V, T_A = -30^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise specified})$

| Parameter                                   | Symbol                | Conditions                     |     | in | Тур | Max | Unit |

|---------------------------------------------|-----------------------|--------------------------------|-----|----|-----|-----|------|

| Signal to total distortion TX               | $S_{TDTX}$            | Sinusoidal test method (Linear |     |    | •   |     |      |

| (up to 35 dB gain)                          |                       | 300 Hz to 3400 Hz weighting).  |     |    |     |     |      |

| Typical values measured                     |                       | Level = 0 dBm0                 | 56  |    | 64  |     | dB   |

| with 35 dB gain                             |                       | Level = -6 dBm0                | 5   | 0  | 60  |     |      |

|                                             |                       | Level = -10 dBm0               | 4   | 8  | 57  |     |      |

|                                             |                       | Level = -20 dBm0               | 4   | 3  | 53  |     |      |

|                                             |                       | Level = -30 dBm0               | 3   | 8  | 44  |     |      |

|                                             |                       | Level = -45 dBm0               | 2   | 4  | 29  |     |      |

|                                             |                       | Level = -55 dBm0               | 1   | 5  | 19  |     |      |

| Single frequency distortion                 | $S_{DTX}$             | 0 dBm0 input signal            |     |    | -70 | -56 | dB   |

| transmit                                    |                       |                                |     |    |     |     |      |

| Signal to total distortion                  | S <sub>TDSP1</sub>    | Sinusoidal test method (Linear |     |    |     |     |      |

| SP1/SP2                                     | $S_{TDSP2}$           | 300 Hz to 3400 Hz weighting).  |     |    |     |     |      |

| (up to 20 dB attenuation)                   |                       | Load is 1000 or 30 Ω.          | 4   |    |     | 1   |      |

|                                             |                       | Level = -6 dBm0                | 45* | 50 | 60  |     | dB   |

|                                             |                       | Level = -10 dBm0               | 45* | 48 | 60  |     |      |

|                                             |                       | Level = -20 dBm0               | 42* | 43 | 55  |     |      |

|                                             |                       | Level = -30 dBm0               | 35* | 38 | 50  |     |      |

|                                             |                       | Level = -45 dBm0               | 24* | 24 | 40  |     |      |

|                                             |                       | Level = -55 dBm0               | 15* | 15 | 28  |     |      |

| Single frequency distortion receive SP1/SP2 | $S_{DSP1} \ S_{DSP2}$ | -6 dBm0 input signal           |     |    | -62 | -45 | dB   |

| Signal to distortion of tone                | S <sub>TONE</sub>     | DTMF frequencies               | 2   | 8  | 42  |     | dB   |

| generator signals                           | FIONE                 | Linear 300 Hz to 3400 Hz       |     |    |     |     |      |

|                                             |                       | weighting.                     |     |    |     |     |      |

| Intermodulation                             | IMD                   | Loop around measurement        |     |    | -61 | -46 | dB   |

|                                             |                       | voltage at MIC = -10 dBm0 to - |     |    |     |     |      |

|                                             |                       | 27 dBm0, 2 frequencies in the  |     |    |     |     |      |

|                                             |                       | range 300 Hz to 3400 Hz        |     |    |     |     |      |

<sup>\*</sup>max. load (30 $\Omega$ ) and min. Vcc (2.7V) and max. temperature

### **◆** Crosstalk

( $V_{CC}$  = 2.7-3.6V,  $T_A$  = -30°C to +85°C, unless otherwise specified)

| Parameter           | Symbol             | Conditions                                                              | Min | Тур | Max | Unit |

|---------------------|--------------------|-------------------------------------------------------------------------|-----|-----|-----|------|

| Transmit to receive | C <sub>TX-RX</sub> | Transmit level = 0 dBm0<br>f = 300 Hz to 3400 Hz<br>RX = quiet PCM code |     | -82 | -65 | dB   |

| Receive to transmit | C <sub>RX-TX</sub> | Receive level = -6 dBm0<br>f = 300 Hz to 3400 Hz<br>MIC = 0V            |     | -75 | -60 | dB   |

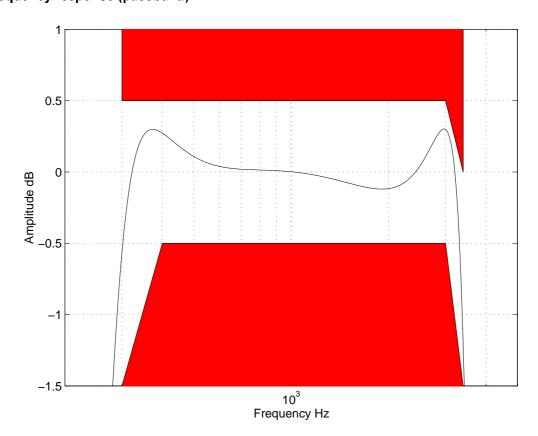

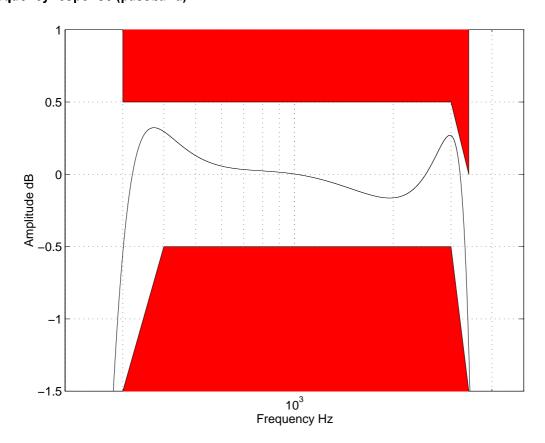

# ♦ RX frequency response

# ◆ RX frequency response (passband)

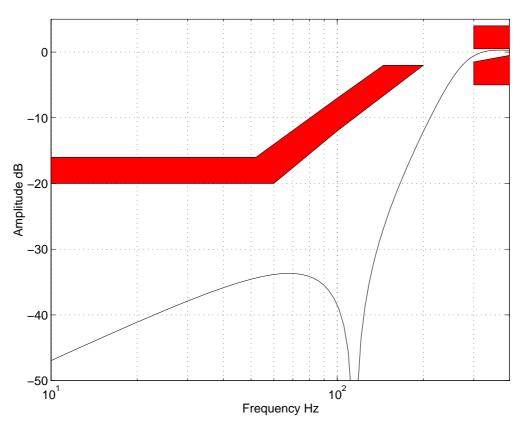

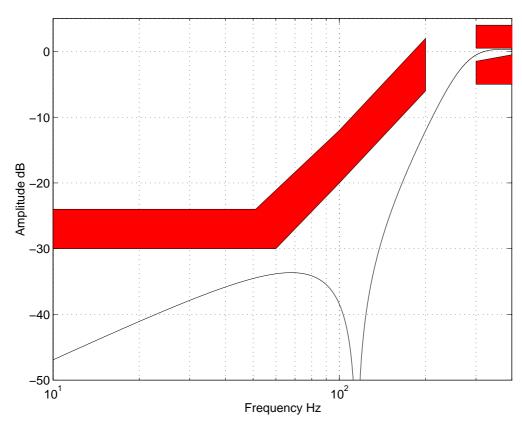

# ◆ RX frequency response (stopband low)

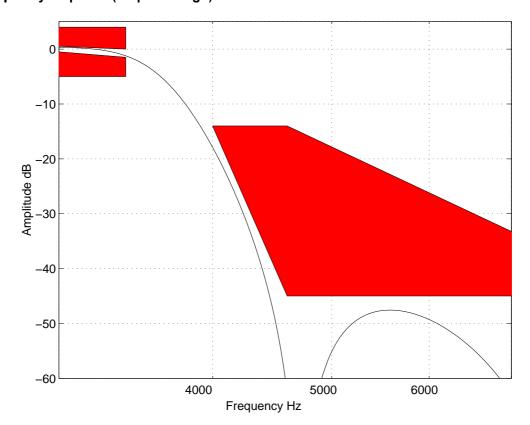

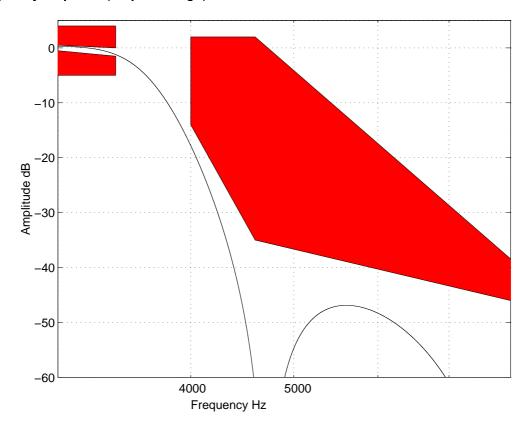

# ◆ RX frequency response (stopband high)

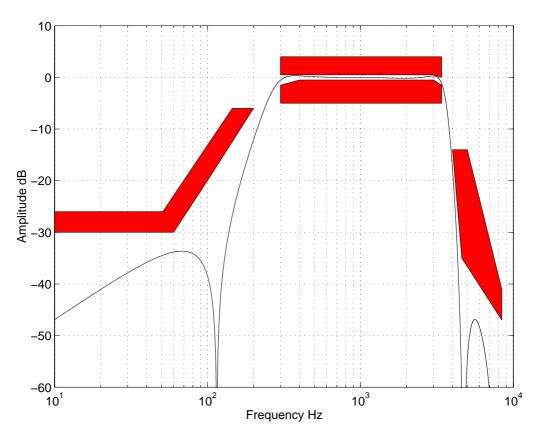

# **♦TX** frequency response

# **◆TX** frequency response (passband)

# ◆TX frequency response (stopband low)

# ◆TX frequency response (stopband high)

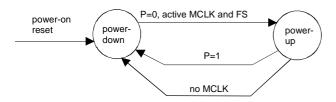

#### **◆** Operating Modes

When power is first applied, power-on reset circuit initializes control and data registers of MAS9090 and puts it into a power-down state. During power-down state, control registers retain their initial state until they are written via the serial interface. Master clock (MCLK) can be inactive.

The power up/down control is accomplished by changing the P-bit of the address byte of the serial interface ("0" means active and "1" power-down) or by stopping the master clock.

#### ◆ Control Interface

Control information or data is written into or readback from the internal registers of MAS9090 via the serial control port. Serial control port consists of control output CO, control input CI, chip select CS-and control clock CCLK and supports the MICROWIRE<sup>TM\*</sup>) communication protocol. All control instructions, except the single byte power up/down command require two bytes of data.

To shift the data into MAS9090, CCLK must be pulsed eight times (CS is low). Data on the CI input is shifted into the serial input register on the rising edges of CCLK pulses. After 8 bit address data is shifted in, the content of the shift register is decoded and may indicate that 8 bit control word will follow. Control word may start immediately after the address byte or after a single CS pulse. It is not mandatory for the CS signal to return high in between the address and the data. After the second byte is shifted in, the CS signal must return to a high state.

The same process takes place for reading-back status information during the next CS low state. CS will remain low for eight CCLK pulses. The data is shifted out on the CO output from the serial output register on the falling edges of CCLK. When CS is high, the CO pin is in a high impedance state, which enables CO pins of other devices to be multiplexed together.

#### ◆ Digital Data Interface

Digital data is shifted in/out from RX/TX using master clock (MCLK) and Frame Sync (FS) signals. FS determines the beginning of frame and its duration can vary from single cycle of MCLK to squarewave.

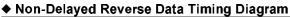

Three different modes between FS and the first time slot of a data frame can be used: non-delayed normal data timing, non-delayed reverse data timing and delayed data timing. These modes are set with bits DM0 and DM1 of control register CR1.

In non-delayed timing modes the first time slot begins coincident with the rising edge of the FS. In delayed timing mode the FS must be active at least one half cycle of MCLK before the beginning of the first time slot.

Bit EN of control register CR1 enables the voice data transfer on TX and RX pins. Data is shifted out from TX output on the rising edge of MCLK and shifted into RX on falling edge of MCLK on assigned time slot. In non-delayed reverse mode the data is shifted with different edge of MCLK (on falling edge from TX and on rising edge into RX). TX output is in tristate condition during non selected time slots. The TX output transmits 8 bits of encoded data (A-law or  $\mu$ -law) or 16 bits (14 effective bits, 2 LSB bits zero) of linear data when compressor is bypassed.

Two time slots (B1 and B2) can be used in two formats: in Format 1, time slot B1 corresponds to eight MCLK cycles starting immediately after the rising edge of FS and time slot B2 starts immediately after the B1 is ended. A two-bit space is left after B2 for insertion of possible D channel data. The position of this two-bit data is changed in Format 2 to the center of time slots B1 and B2. The data format is selected by bit FF in control register CR0 and time slots B1 and B2 are selected by bit TS in control register CR1.

#### ◆ Control Channel Access to PCM Interface

When companded code is selected it is possible to access the selected time slot (B1 or B2) by writing data bytes to internal registers CR2 and CR3. The byte written to CR3 is transmitted from TX with the following frame in place of PCM data if bit MX (3) of CR1 is selected. To implement a continuous data flow from interface to B channel a control byte has to be sent on each PCM frame.

The byte written into CR2 is sent through the receive audio path (RX) if bit MR (4) of CR1 is selected. CR2 can also be used to read the RX input. In order to implement a continuous data flow from B channel to the interface, register CR2 has to be read at each PCM frame.

\*) Trade Mark of National Semiconductor

#### **♦ TX Audio Path**

Analog front end provides three identical differential inputs (MIC1, MIC2, MIC3) for capacitive connection of microphones or auxiliary audio circuits. Desired input signal is selected with bits VS and TE (6 and 7) of register CR4 and forwarded to a low noise preamplifier.

Preamplifier has 16.1 dB gain and its output is fed to the programmable gain amplifier which provides an additional gain from 0 to 22.5 dB in 1.5 dB steps. Gain is controlled with bits 4-7 of register CR5.

An active RC anti alias filter is used to prevent signal folding during the sampling. Accurate analog to digital conversion is done by using a sigma-delta modulator followed by a decimation filter.

Digital multiplexer (bit DE (0) in CR 7) is used to select the input of a digital bandpass filter (300-3400 Hz). The input can be taken from the output of the decimator or from an internal ring/tone generator. The bandpass filter output contains hard clipping saturation logic for signals exceeding overload level (+3.14 dB). Highpass part of the bandpass filter can be bypassed with bit HPT of register CR10.

Output data can be compressed by using CCITT A-law or  $\mu$ 255-law coding. The compression code is selected with bits CM (5), MA (4) and IA (3) of register CR0.

#### ◆ RX Audio Path

Received signal is transferred into RX register in 8 bit encoded format or in 16 bit linear format. The data is expanded by using A-law or  $\mu\text{-law}$  signal encoding according to CCITT A and  $\mu255$  laws. The expansion code is selected with bits CM (5), MA (4) and IA (3) of register CR0. Signal is then passed through a bandpass filter (bandpass 300-3400 Hz). The high pass section of the filter can be bypassed with bit HPR of register CR4.

The input signal of RX gain3 is controlled with bits SI (5), RTE (2) and SE (0) of register CR4. Bit SI activates the transmit side tone signal, bit RTE activates the ring/tone generator and bit SE activates the received signal to be summed to the gain input. RX gain3 can be programmed with bits 4-7 of register CR6 from 0 dB to -30 dB with -2dB steps. It contains also hard-clipping saturation logic.

After gain adjustment the signal is fed to a digital sigma-delta modulator followed by a switched capacitor (SC) reconstruction filter and a continuous time smoothing filter. Filtered analog signal can be directed to a speaker amplifier (SP1) or to an extra analog output amplifier (SP2) with bits OE1 (4) and OE2 (3) of register CR4. Gains can be set with register CR6 in the range of 0 to -30 dB in -2 dB steps.

Differential analog outputs (SP1, SP2) are capable of directly driving output load of 30  $\Omega$  with power level up to 66mW. Also ceramic receivers up to 50nF can be used. Power up transient noise suppression is used in both outputs.

## ◆ Ring and tone generator

Ring/tone generator is able to generate one or two sinewave or squarewave frequencies (including DTMF tones) to the transmit (TX) receive (RX) or buzzer paths. Generated frequencies can be programmed with registers CR8 and CR9. One of the three frequency ranges can be selected with bits DFT and HFT of register CR10. Output signal level of the tone generator can be selected from 0 to -27 dB with -3dB steps with bits 4-7 of register CR7.

Single ended BZ output is used to drive a buzzer by using an external bipolar transistor with pulse width modulated (PWM) squarewave signal f1 (CR8). This PWM signal can also be amplitude modulated with signal f2 (CR9). Maximum load for BZ is 5 k $\Omega$  and 50pF. Implementation of tone generator is fully digital. Therefore no amplitude or frequency response variations (at TX output) over temperature, power supply or from unit to unit exist.

# ◆ Digital Interface Format

## **◆** Registers

Register Map

| Register |   |   | Ad | dres | s B | yte |   |   | 1/0   |                           | Data Byte |           |          |            |             |           |     |

|----------|---|---|----|------|-----|-----|---|---|-------|---------------------------|-----------|-----------|----------|------------|-------------|-----------|-----|

| <u>-</u> | 7 | 6 | 5  | 4    | 3   | 2   | 1 | 0 |       | 7                         | 6         | 5         | 4        | 3          | 2           | 1         | 0   |

| Power    | Р | Χ | Х  | Х    | Х   | Х   | 0 | Х |       |                           |           |           |          |            |             |           |     |

| CR0      | Р | 0 | 0  | 0    | 0   | 0   | 1 | Х | Write | F1                        | F0        | CM        | MA       | IA         | FF          | B7        | DL  |

|          | Р | 0 | 0  | 0    | 0   | 1   | 1 | Х | Read  |                           |           |           |          |            |             |           |     |

| CR1      | Р | 0 | 0  | 0    | 1   | 0   | 1 | Х | Write | DM1                       | DM0       | DO        | MR       | MX         | EN          | TS        | SV  |

|          | Р | 0 | 0  | 0    | 1   | 1   | 1 | Х | Read  |                           |           |           |          |            |             |           |     |

| CR2      | Р | 0 | 0  | 1    | 0   | 0   | 1 | Х | Write |                           |           |           | Input d  | lata [0:7] |             |           |     |

|          | Р | 0 | 0  | 1    | 0   | 1   | 1 | Х | Read  |                           |           |           |          |            |             |           |     |

| CR3      | Р | 0 | 0  | 1    | 1   | 0   | 1 | Х | Write |                           |           |           | Output   | data [0:7  | ]           |           |     |

|          | Р | 0 | 0  | 1    | 1   | 1   | 1 | Х | Read  |                           |           |           |          |            |             |           |     |

| CR4      | Р | 0 | 1  | 0    | 0   | 0   | 1 | Х | Write | VS                        | TE        | SI        | OE1      | OE2        | RTE         | HPR       | SE  |

|          | Р | 0 | 1  | 0    | 0   | 1   | 1 | Х | Read  |                           |           |           |          |            |             |           |     |

| CR5      | Р | 0 | 1  | 0    | 1   | 0   | 1 | Х | Write |                           | TX gai    | n [4:7]   |          |            | Side tone   | gain [0:3 | ]   |

|          | Р | 0 | 1  | 0    | 1   | 1   | 1 | Х | Read  |                           |           |           |          |            |             |           |     |

| CR6      | Р | 0 | 1  | 1    | 0   | 0   | 1 | Х | Write |                           | SP1 ga    | in [4:7]  |          |            | SP2 ga      | in [0:3]  |     |

|          | Р | 0 | 1  | 1    | 0   | 1   | 1 | Χ | Read  |                           |           |           |          |            |             |           |     |

| CR7      | Р | 0 | 1  | 1    | 1   | 0   | 1 | Х | Write |                           | Tone ga   | ain [4:7] |          | F1         | F2          | SN        | DE  |

|          | Р | 0 | 1  | 1    | 1   | 1   | 1 | Х | Read  |                           |           |           |          |            |             |           |     |

| CR8      | Р | 1 | 0  | 0    | 0   | 0   | 1 | Х | Write |                           |           | Binary v  | vord use | d for cald | culating f1 |           |     |

|          | Р | 1 | 0  | 0    | 0   | 1   | 1 | Х | Read  |                           |           |           |          |            |             |           |     |

| CR9      | Р | 1 | 0  | 0    | 1   | 0   | 1 | Х | Write |                           |           | Binary v  | vord use | d for cald | culating f2 |           |     |

|          | Р | 1 | 0  | 0    | 1   | 1   | 1 | Х | Read  |                           |           |           |          |            |             |           |     |

| CR10     | Р | 1 | 0  | 1    | 0   | 0   | 1 | Х | Write | POR                       | SCA       | HPT       | EXT      | LI         | LO          | DFT       | HFT |

|          | Р | 1 | 0  | 1    | 0   | 1   | 1 | Х | Read  |                           |           |           |          |            |             |           |     |

| CR11     | Р | 1 | 0  | 1    | 1   | 0   | 1 | Χ | Write |                           |           |           |          |            |             |           |     |

|          | Р | 1 | 0  | 1    | 1   | 1   | 1 | Χ | Read  |                           |           |           |          |            |             |           |     |

| CR14     | Χ | X | Х  | Х    | Х   | Х   | Χ | Х |       | For testing purposes only |           |           |          |            |             |           |     |

#### Address byte bits:

- Bit 0 reserved for future extensions

- Bit 1 indicates the presence of a second byte. If cleared indicates single byte power up/down command

- Bit 2 is write/read select bit

- Bits 6 to 3 contain the address of register

- Registers CR12, CR13, CR15 are not accessible

- MSB bit (bit 7) of the address and data byte is always clocked first into or out from CI and CO pins

- Bit 7 'P' controls the power up/down state of the chip. P = 1 means power down

#### Data bits:

- All registers are cleared during power on reset or by writing to bit POR of CR10

- Default value for all bits is zero.

Notice the difference between power down and POR. Registers can be written in both power down/up states and they retain their values in power down. Both data and control registers are cleared when POR bit (in CR10) is written high or during power on reset (i.e. Vcc transition from 0 volts to 3-5 volts).

**Control register CR0**

| 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  | Function                             |      |

|----|----|----|----|----|----|----|----|--------------------------------------|------|

| F1 | F0 | CM | MA | IA | FF | B7 | DL |                                      |      |

| 0  | 0  |    |    |    |    |    |    | MCLK = 512 kHz                       | *    |

| 0  | 1  |    |    |    |    |    |    | MCLK = 1536 kHz                      |      |

| 1  | 0  |    |    |    |    |    |    | MCLK = 2048 kHz                      |      |

| 1  | 1  |    |    |    |    |    |    | Not implemented                      |      |

|    |    | 0  |    |    |    |    |    | Linear code                          | *    |

|    |    |    | 0  | 0  |    |    |    | 2's complement                       | *    |

|    |    |    | 0  | 1  |    |    |    | sign and magnitude                   |      |

|    |    |    | 1  | 0  |    |    |    | 2's complement                       |      |

|    |    |    | 1  | 1  |    |    |    | 1's complement                       |      |

|    |    | 1  |    |    |    |    |    | Companded code                       |      |

|    |    |    | 0  | 0  |    |    |    | μ-Law: CCITT D3-D4                   |      |

|    |    |    | 0  | 1  |    |    |    | μ-Law: bare coding                   |      |

|    |    |    | 1  | 0  |    |    |    | A-Law: including even bit inversions |      |

|    |    |    | 1  | 1  |    |    |    | A-Law: bare coding                   |      |

|    |    |    |    |    | 0  |    |    | B1 and B2 consecutive                | (1)* |

|    |    |    |    |    | 1  |    |    | B1 and B2 separated                  | (1)  |

|    |    |    |    |    |    | 0  |    | 8-bit time slot                      | (1)* |

|    |    |    |    |    |    | 1  |    | 7-bit time slot                      | (1)  |

|    |    |    |    |    |    |    | 0  | Normal operation (default)           | *    |

|    |    |    |    |    |    |    | 1  | Digital loop back (TX and RX muted)  |      |

Control register CR1

| 7   | 6   | 5  | 4  | 3  | 2  | 1  | 0  | Function                        |      |

|-----|-----|----|----|----|----|----|----|---------------------------------|------|

| TM1 | TM0 | DO | MR | MX | EN | TS | sv |                                 |      |

| 0   | Х   |    |    |    |    |    |    | Delayed data timing             | *    |

| 1   | 0   |    |    |    |    |    |    | Non-delayed normal data timing  |      |

| 1   | 1   |    |    |    |    |    |    | Non-delayed reverse data timing |      |

|     |     | 0  |    |    |    |    |    | LO latch set to 1               | *    |

|     |     | 1  |    |    |    |    |    | LO latch set to 0               |      |

|     |     |    | 0  |    |    |    |    | RX connected to RX path         | *    |

|     |     |    | 1  |    |    |    |    | CR2 connected to RX path        | (1)  |

|     |     |    |    | 0  |    |    |    | TX path connected to TX         | *    |

|     |     |    |    | 1  |    |    |    | CR3 connected to TX             | (1)  |

|     |     |    |    |    | 0  |    |    | Voice data transfer disable     | *    |

|     |     |    |    |    | 1  |    |    | Voice data transfer enable      |      |

|     |     |    |    |    |    | 0  |    | B1 channel selected             | (1)* |

|     |     |    |    |    |    | 1  |    | B2 channel selected             | (1)  |

|     |     |    |    |    |    |    | 0  | 2.7-3.6V power supply *         |      |

|     |     |    |    |    |    |    | 1  | Not allowed                     |      |

significant in companded mode only state at power on initialization (1)

**Control register CR2**

| 7   | 6  | 5  | 4  | 3  | 2  | 1  | 0  | Function                                            |

|-----|----|----|----|----|----|----|----|-----------------------------------------------------|

| d7  | d6 | d5 | d4 | d3 | d2 | d1 | d0 |                                                     |

| msb |    |    |    |    |    |    |    | Data sent to RX path or data received from RX input |

**Control register CR3**

| 7   | 6  | 5  | 4  | 3  | 2  | 1  | 0  | Function            |

|-----|----|----|----|----|----|----|----|---------------------|

| d7  | d6 | d5 | d4 | d3 | d2 | d1 | d0 |                     |

| msb |    |    |    |    |    |    |    | TX data transmitted |

Control register CR4

| 7  | registe<br>6 | 5  | 4   | 3   | 2   | 1   | 0  | Function                         |   |

|----|--------------|----|-----|-----|-----|-----|----|----------------------------------|---|

| VS | TE           | SI | OE1 | OE2 | RTE | HPR | SE | , anotion                        |   |

| 0  | 0            |    |     |     |     |     |    | TX input muted                   | * |

| 0  | 1            |    |     |     |     |     |    | MIC1 selected                    |   |

| 1  | 0            |    |     |     |     |     |    | MIC2 selected                    |   |

| 1  | 1            |    |     |     |     |     |    | MIC3 selected                    |   |

|    |              | 0  |     |     |     |     |    | Internal side tone disabled      | * |

|    |              | 1  |     |     |     |     |    | Internal side tone enabled       |   |

|    |              |    | 0   | 0   |     |     |    | RX output muted                  | * |

|    |              |    | 0   | 1   |     |     |    | SP1 output selected              |   |

|    |              |    | 1   | 0   |     |     |    | SP2 output selected              |   |

|    |              |    | 1   | 1   |     |     |    | NOT ALLOWED                      |   |

|    |              |    |     |     | 0   |     |    | Ring/Tone to SP1 or SP2 disabled | * |

|    |              |    |     |     | 1   |     |    | Ring/Tone to SP1 or SP2 enabled  |   |

|    |              |    |     |     |     | 0   |    | Receive HP filter enabled        | * |

|    |              |    |     |     |     | 1   |    | Receive HP filter disabled       |   |

|    |              |    |     |     |     |     | 0  | RX signal to SP1 or SP2 disabled | * |

|    |              |    |     |     |     |     | 1  | RX signal to SP1 or SP2 enabled  |   |

Control register CR5

| 7 | 6    | 5    | 4 | 3 | 2      | 1       | 0 | Function        |  |

|---|------|------|---|---|--------|---------|---|-----------------|--|

|   | TX ( | Gain |   |   | Sideto | ne Gain |   |                 |  |

| 0 | 0    | 0    | 0 |   |        |         |   | 0 dB gain *     |  |

| 0 | 0    | 0    | 1 |   |        |         |   | 1.5 dB gain     |  |

| - | -    | -    | - |   |        |         |   | in 1.5 dB steps |  |

| 1 | 1    | 1    | 1 |   |        |         |   | 22.5 dB gain    |  |

|   |      |      |   | 0 | 0      | 0       | 0 | -12.5 dB gain * |  |

|   |      |      |   | 0 | 0      | 0       | 1 | -13.5 dB gain   |  |

|   |      |      |   | - | -      | -       | - | in 1 dB steps   |  |

|   |      |      |   | 1 | 1      | 1       | 1 | -27.5 dB gain   |  |

<sup>\*</sup> state at power on initialization

Control register CR6

| 7 | 6                                    | 5 | 4 | 3 | 3 2 1 0 Function |   |   |                |  |

|---|--------------------------------------|---|---|---|------------------|---|---|----------------|--|

|   | Earpiece Gain Extra Gain (SP1) (SP2) |   |   |   |                  |   |   |                |  |

| 0 | 0                                    | 0 | 0 |   |                  |   |   | 0 dB gain *    |  |

| 0 | 0                                    | 0 | 1 |   |                  |   |   | -2 dB gain     |  |

| - | -                                    | - | - |   |                  |   |   | in -2 dB steps |  |

| 1 | 1                                    | 1 | 1 |   |                  |   |   | -30 dB gain    |  |

|   |                                      |   |   | 0 | 0                | 0 | 0 | 0 dB gain *    |  |

|   |                                      |   |   | 0 | 0                | 0 | 1 | -2 dB gain     |  |

|   |                                      |   |   | - | -                | - | - | in -2 dB steps |  |

|   |                                      |   |   | 1 | 1                | 1 | 1 | -30 dB gain    |  |

**Control register CR7**

| Contro | <u>Ji regi</u> | Ster C | 171 |    |    |    |    |                  |               |               |            |  |  |  |

|--------|----------------|--------|-----|----|----|----|----|------------------|---------------|---------------|------------|--|--|--|

| 7      | 6              | 5      | 4   | 3  | 2  | 1  | 0  |                  | F             | unction       |            |  |  |  |

|        | Tone           | gain   |     | f1 | f2 | SN | DE | Attenuation      | f1 dBm0       | f2 dBm0       | f1+f2 dBm0 |  |  |  |

| 0      | 0              | 0      | 0   |    |    |    |    | 0 dB gain *      | 1.20 (2)      | -0.87 (2)     | -1.81 (2)  |  |  |  |

| 0      | 0              | 0      | 1   |    |    |    |    | -3 dB            |               |               |            |  |  |  |

| 0      | 0              | 1      | 0   |    |    |    |    | -6 dB            |               |               |            |  |  |  |

| 0      | 0              | 1      | 1   |    |    |    |    | -9 dB            |               |               |            |  |  |  |

| 0      | 1              | 0      | 0   |    |    |    |    | -12 dB           |               |               |            |  |  |  |

| 0      | 1              | 0      | 1   |    |    |    |    | -15 dB           |               |               |            |  |  |  |

| 0      | 1              | 1      | 0   |    |    |    |    | -18 dB           |               |               |            |  |  |  |

| 0      | 1              | 1      | 1   |    |    |    |    | -21 dB           |               |               |            |  |  |  |

| 1      | Х              | X      | 0   |    |    |    |    | -24 dB           |               |               |            |  |  |  |

| 1      | Χ              | Х      | 1   |    |    |    |    | -27 dB           | -25.80        | -27.87        | -28.81     |  |  |  |

|        |                |        |     | 0  | 0  |    |    | f1 and f2 muted  |               |               | *          |  |  |  |

|        |                |        |     | 0  | 1  |    |    | f2 selected      |               |               |            |  |  |  |

|        |                |        |     | 1  | 0  |    |    | f1 selected      |               |               |            |  |  |  |

|        |                |        |     | 1  | 1  |    |    | f1 and f2 in sum | med mode      |               |            |  |  |  |

|        |                |        |     |    |    | 0  |    | Squarewave sign  | nal selected  |               | *          |  |  |  |

|        |                |        |     |    |    | 1  |    | Sinewave signal  | selected      |               |            |  |  |  |

|        |                |        |     |    |    |    | 0  | Normal operation | n             |               | *          |  |  |  |

|        |                |        |     |    |    |    | 1  | Tone/Ring gene   | rator connect | ted to TX pat | h          |  |  |  |

**Control register CR8**

| 7   | 6  | 5  | 4  | 3  | 2  | 1               | 0  | Function        |

|-----|----|----|----|----|----|-----------------|----|-----------------|

| d7  | d6 | D5 | d4 | d3 | d2 | d1              | d0 |                 |

| msb |    |    |    |    |    | f1 control word |    | f1 control word |

Control register CR9

| Contro | Ji i egisi | CI OIL |    |    |    |    |    |                 |

|--------|------------|--------|----|----|----|----|----|-----------------|

| 7      | 6          | 5      | 4  | 3  | 2  | 1  | 0  | Function        |

| d7     | d6         | d5     | d4 | d3 | d2 | d1 | d0 |                 |

| msb    |            |        |    |    |    |    |    | f2 control word |

- (2) values are calculated from TX output, levels on RX are 6 dB smaller

- X don't care

- \* state at power on initialization

Control register CR10

| 7   | 6   | 5   | 4   | 3  | 2  | 1   | 0   | Function                                      |

|-----|-----|-----|-----|----|----|-----|-----|-----------------------------------------------|

| POR | SCA | HPT | EXT | L1 | L0 | DFT | HFT | , anoton                                      |

| 0   |     |     |     |    |    |     |     | Normal operation *                            |

| 1   |     |     |     |    |    |     |     | Set power-on-reset initialization             |

|     | 0   |     |     |    |    |     |     | Normal operation *                            |

|     | 1   |     |     |    |    |     |     | Scan. Cl is input, DX is output. For device   |

|     |     |     |     |    |    |     |     | testing.                                      |

|     |     | 0   |     |    |    |     |     | Normal operation *                            |

|     |     | 1   |     |    |    |     |     | Bypass TX highpass filter                     |

|     |     |     | 0   |    |    |     |     | Normal operation *                            |

|     |     |     | 1   |    |    |     |     | Read 2-bit input to the decimator. For device |

|     |     |     |     |    |    |     |     | testing (CI and DR)                           |

|     |     |     |     | 0  |    |     |     | Normal operation *                            |

|     |     |     |     | 1  |    |     |     | Loop from expander to compressor              |

|     |     |     |     |    | 0  |     |     | Normal operation *                            |

|     |     |     |     |    | 1  |     |     | Loop from TX to Rx                            |

|     |     |     |     |    |    | 0   | 0   | Standard frequency tone range *               |

|     |     |     |     |    |    | 0   | 1   | Halved frequency tone range                   |

|     |     |     |     |    |    | 1   | 0   | Double frequency tone range                   |

|     |     |     |     |    |    | 1   | 1   | Forbidden                                     |

Control register CR11

| 7  | 6 | 5   | 4   | 3   | 2   | 1   | 0   | Function                                     |

|----|---|-----|-----|-----|-----|-----|-----|----------------------------------------------|

| BE | В | BZ5 | BZ4 | BZ3 | BZ2 | BZ1 | BZ0 |                                              |

| 0  |   |     |     |     |     |     |     | Buzzer Output disabled (set to 0) *          |

| 1  |   |     |     |     |     |     |     | Buzzer output enabled                        |

|    | 0 |     |     |     |     |     |     | Duty cycle is relative to width of logic 1 * |

|    | 1 |     |     |     |     |     |     | Duty cycle is relative to width of logic 0   |

| 1  |   | msb |     |     |     |     |     | Duty cycle control word                      |

Control register CR14 (for testing purposes only)

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   | Fi                        | unction             |

|-----|-----|-----|-----|-----|-----|-----|-----|---------------------------|---------------------|

| AM2 | AM1 | AM0 | DM2 | DM1 | DM0 | MUX | EDX |                           |                     |

|     |     |     |     |     |     |     |     | rxtest pin                | Txtest pin          |

| 0   | 0   | 0   |     |     |     |     |     | VSA                       | VSA                 |

| 0   | 0   | 1   |     |     |     |     |     | Anti-image filter         | Gain amplifier      |

| 0   | 1   | 0   |     |     |     |     |     | DAC output                | VSA                 |

| 0   | 1   | 1   |     |     |     |     |     | RX pos. reference         | Anti-image filter   |