Operation Temperature Condition -40° C~95° C

## **DDR4 SDRAM**

## 32M x 16 Bit x 8 Banks DDR4 SDRAM

### Feature

- Power supply

- VDD = VDDQ = 1.2V ± 5%

- VPP = 2.375V to 2.75V

- 8 internal banks

- 2 groups of 4 banks each (x16)

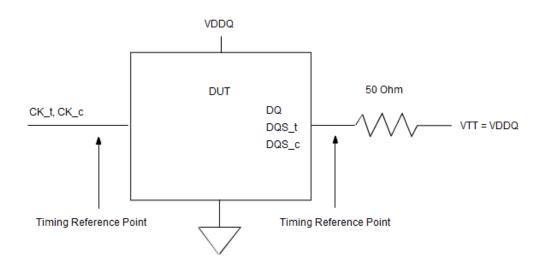

- Differential clock inputs (CK\_t and CK\_c)

Distinguished differential clock and cK\_c)

- Bi-directional differential data strobe (DQS\_t and DQS\_c)

- Asynchronous reset is supported (RESET\_n)

- ZQ calibration for Output driver by compare to external reference resistance (RZQ 240 ohm ±1%)

- Nominal, park and dynamic On-die Termination (ODT)

- DLL aligns DQ and DQS transitions with CK transitions

- Commands entered on each positive CK edge

- CAS Latency (CL): 9, 11, 12, 13, 14, 15, 16, 18, 19, 20, 21, 22, 23 and 24 supported

- Additive Latency (AL) 0, CL-1, and CL-2 supported

- Burst Length (BL): 8 and 4 with on the fly supported

- CAS Write Latency (CWL): 9, 10, 11, 12, 14, 16, 18 and 20 supported

- Refresh cycles

- Average refresh period

- 7.8µs at -40°C  $\leq$  T<sub>C</sub>  $\leq$  +85°C

- 3.9µs at +85°C <  $T_C \le$  +95°C

- Fine granularity refresh is supported

- Adjustable internal generation VREFDQ

- Pseudo Open Drain (POD) interface for data input/output

- Driver strength selected by MRS

- The high-speed data transfer by the 8 bits prefetch

- Temperature Controlled Refresh (TCR) mode is supported

- Low Power Auto Self Refresh (LPASR) mode is supported

- Self-refresh abort is supported

- Programmable preamble is supported

- Write leveling is supported

- Command/Address latency (CAL) is supported

- Multipurpose register READ and WRITE capability

- Command Address (CA) Parity for command/address signal error detect and inform it to controller

- Write Cyclic Redundancy Code (CRC) for DQ error detect and inform it to controller during high-speed operation

- Data Bus Inversion (DBI) for Improve the power consumption and signal integrity of the memory interface (x16 product only)

- Data Mask (DM) for write data

- Per DRAM Addressability (PDA) for each DRAM can be set a different mode register value individually and has individual adjustment.

- Gear down mode (1/2 and 1/4 rate) is supported

- PPR and sPPR is supported

- Connectivity test (x16 only)

- Maximum power down mode for the lowest power consumption with no internal refresh activity

- JEDEC JESD-79-4 compliant

- Operating case temperature range: T<sub>C</sub> = -40°C to +95°C

### **Ordering Information**

| Product ID         | Max Freq. | VDD  | Data Rate (CL-tRCD-tRP) | Package     | Comments |

|--------------------|-----------|------|-------------------------|-------------|----------|

| M16U4G16256A-QLBIG | 1600MHz   | 1.2V | DDR4- 3200 (24-24-24)   | 96 ball BGA | Pb-free  |

| M16U4G16256A-KJBIG | 1333MHz   | 1.2V | DDR4- 2666 (19-19-19)   | 96 ball BGA | Pb-free  |

| M16U4G16256A-HHBIG | 1200MHz   | 1.2V | DDR4- 2400 (17-17-17)   | 96 ball BGA | Pb-free  |

Operation Temperature Condition -40° C~95° C

## **DDR4 SDRAM Addressing**

| 256 Mb x16 |

|------------|

| 2          |

| BG0        |

| 4          |

| BA0 – BA1  |

| A0 – A14   |

| A0 – A9    |

| 2КВ        |

|            |

Note:

1.

Page size is per bank, calculated as follows: Page size =  $2^{\text{COLBITS}} \times \text{ORG/8}$ , where COLBIT = the number of column address bits and ORG = the number of DQ bits.

Operation Temperature Condition -40° C~95° C

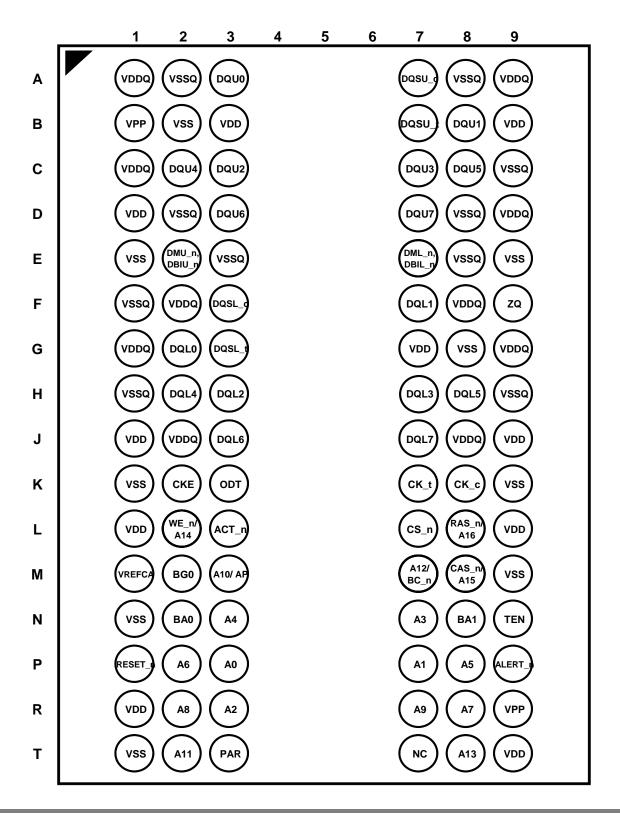

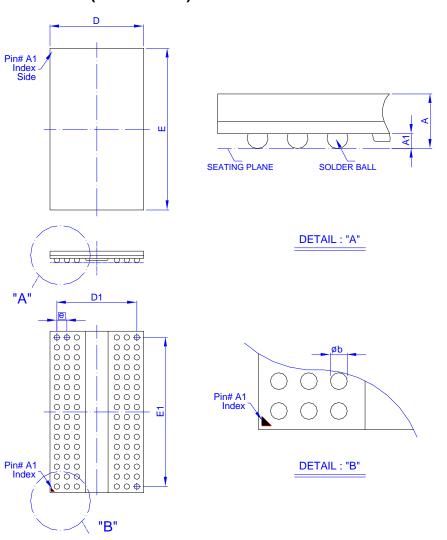

## Ball Configuration – 96 balls BGA Package

< TOP View> See the balls through the package

Elite Semiconductor Microelectronics Technology Inc

## Operation Temperature Condition -40° C~95° C

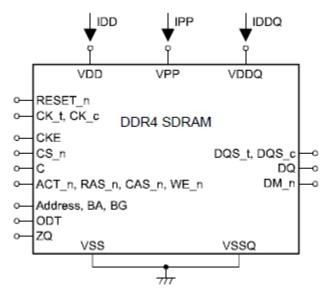

## Input / Output Functional Description

| Symbol                                          | Туре         | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------------------------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CK_t, CK_c                                      | Input        | Clock: CK_t and CK_c are differential clock inputs. All address and control input signals are sampled on the crossing of the positive edge of CK_t and negative edge of CK_c.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| CKE                                             | Input        | Clock Enable: CKE HIGH activates, and CKE Low deactivates, internal clock signals and device input buffers and output drivers. Taking CKE Low provides Precharge Power-Down and Self-Refresh operation (all banks idle), or Active Power-Down (row Active in any bank). CKE is synchronous for Self-Refresh exit. After VREFCA and Internal DQ Vref have become stable during the power on and initialization sequence, they must be maintained during all operations (including Self-Refresh). CKE must be maintained high throughout read and write accesses. Input buffers, excluding CK_t,CK_cODT and CKE are disabled during power-down. Input buffers, excluding CKE, are disabled during Self-Refresh. |

| CS_n                                            | Input        | Chip Select: All commands are masked when CS_n is registered HIGH. CS_n provides for<br>external Rank selection on systems with multiple Ranks. CS_n is considered part of the<br>command code.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| ODT                                             | Input        | On Die Termination: ODT (registered HIGH) enables RTT_NOM termination resistance internal to the DDR4 SDRAM. When enabled, ODT is only applied to each DQ, DQS_t, DQS_c and DM_n/DBI_n/ TDQS_t, NU/TDQS_c (When TDQS is enabled via Mode Register A11=1 in MR1) signal for x8 configurations. For x16 configuration ODT is applied to each DQ, DQSU_t, DQSU_t, DQSL_t, DQSL_c, DMU_n, and DML_n signal. The ODT pin will be ignored if MR1 is programmed to disable RTT_NOM.                                                                                                                                                                                                                                  |

| ACT_n                                           | Input        | Activation Command Input : ACT_n defines the Activation command being entered along with CS_n. The input into RAS_n, CAS_n/A15 and WE_n/A14 will be considered as Row Address A15 and A14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| RAS_n, CAS_n/A15,<br>WE_n/A14                   | Input        | Command Inputs: RAS_n, CAS_n/A15 and WE_n/A14 (along with CS_n) define the command being entered. Those pins have multi function. For example, for activation with ACT_n Low, those are Addressing like A15, A14 but for non-activation command with ACT_n High, those are Command pins for Read, Write and other command defined in command truth table                                                                                                                                                                                                                                                                                                                                                      |

| DM_n/DBI_n<br>(DMU_n/DBIU_n),<br>(DML_n/DBIL_n) | Input/Output | Input Data Mask and Data Bus Inversion: DM_n is an input mask signal for write data.<br>Input data is masked when DM_n is sampled LOW coincident with that input data during a<br>Write access. DM_nis sampled on both edges of DQS. DM is muxed with DBI function by<br>Mode Register A10,A11,A12 setting in MR5. For x8 device, the function of DM or TDQS is<br>enabled by Mode Register A11 setting in MR1. DBI_n is an input/output identifying<br>whether to store/output the true or inverted data. If DBI_n is LOW, the data will be stored/<br>output after inversion inside the DDR4 SDRAM and not inverted if DBI_n is HIGH.                                                                       |

| BG0 - BG1                                       | Input        | Bank Group Inputs : BG0 - BG1 define to which bank group an Active, Read, Write or Precharge command is being applied. BG0 also determines which mode register is to be accessed during a MRS cycle. x4/8 have BG0 and BG1 but x16 has only BG0                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| BA0 - BA1                                       | Input        | Bank Address Inputs: BA0 - BA1 define to which bank an Active, Read, Write or Precharge command is being applied. Bank address also determines which mode register is to be accessed during a MRS cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

## Operation Temperature Condition -40° C~95° C

| Symbol                                             | Туре           | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|----------------------------------------------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| A0 - A15                                           | Input          | Address Inputs: Provide the row address for ACTIVATE Commands and the column address for Read/ Write commands to select one location out of the memory array in the respective bank. (A10/AP,A12/ BC_n, RAS_n, CAS_n/A15 and WE_n/A14 have additional functions, see other rows.The address inputs also provide the op-code during Mode Register Setcommands.                                                                                                                                                                                                                 |  |  |

| A10 / AP                                           | Input          | Auto-precharge: A10 is sampled during Read/Write commands to determine whether<br>Autoprecharge should be performed to the accessed bank after the Read/Write operation<br>(HIGH: Autoprecharge; LOW: no Autoprecharge).A10 is sampled during a Precharge<br>command to determine whether thePrecharge applies to one bank (A10 LOW) or all banks<br>(A10 HIGH). If only one bank is to be precharged, the bank is selected by bank addresses.                                                                                                                                |  |  |

| A12 / BC_n                                         | Input          | Burst Chop: A12 / BC_n is sampled during Read and Write commands to determine if burst chop (on-the-fly) will be performed. (HIGH, no burst chop; LOW: burst chopped). See command truth table for details.                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| RESET_n                                            | Input          | Active Low Asynchronous Reset: Reset is active when RESET_n is LOW, and inactive when RESET_n is HIGH. RESET_n must be HIGH during normal operation. RESET_n is a CMOS rail to rail signal with DC high and low at 80% and 20% of VDD.                                                                                                                                                                                                                                                                                                                                        |  |  |

| DQ                                                 | Input / Output | Data Input/ Output: Bi-directional data bus. If CRC is enabled via Mode register then CRC code is added at the end of Data Burst. Any DQ from DQ0~DQ3 may indicate the internal Vref level during test via Mode Register Setting MR4 A4=High. During this mode, RTT value should be set to Hi-Z. Refer to vendor specific datasheets to determine which DQ is used.                                                                                                                                                                                                           |  |  |

| DQS_t, DQS_c,<br>DQSU_t, DQSU_c,<br>DQSL_t, DQSL_c | Input / Output | Data Strobe: output with read data, input with write data. Edge-aligned with read data, centered in write data. For the x16, DQSL corresponds to the data on DQL0-DQL7; DQSU corresponds to the data on DQU0-DQU7. The data strobe DQS_t, DQSL_t and DQSU_t are paired with differential signals DQS_c, DQSL_c and DQSU_c, respectively, to provide differential pair signaling to the system during reads and writes. DDR4 SDRAM supports differential data strobe only and does not support single-ended.                                                                   |  |  |

| PAR                                                | Input          | Command and Address Parity Input : DDR4 Supports Even Parity check in DRAMs with MR setting. Once it's enabled via Register in MR5, then DRAM calculates Parity withACT_n,RAS_n,CAS_n/A15,WE_n/ A14,BG0-BG1,BA0-BA1,A15-A0. Input parity should maintain at the rising edge of the clock and at the same time with command & address with CS_n LOW                                                                                                                                                                                                                            |  |  |

| ALERT_n                                            | Input/Output   | Alert : It has multi functions such as CRC error flag , Command and Address Parity error flag as Output signal. If there is error in CRC, then Alert_n goes LOW for the period time interval and goes back HIGH. If there is error in Command Address Parity Check, then Alert_n goes LOW for relatively long period until on going DRAM internal recovery transaction to complete. During Connectivity Test mode, this pin works as input. Using this signal or not is dependent on system. In case of not connected as Signal, ALERT_n Pin must be bounded to VDD on board. |  |  |

| TEN                                                | Input          | Connectivity Test Mode Enable : Required on x16 devices and optional input on x4/x8 with densities equal to or greater than 8Gb. HIGH in this pin will enable Connectivity Test Mode operation along with other pins. It is a CMOS rail to rail signal with AC high and low at 80% and 20% of VDD. Using this signal or not is dependent on System. This pin may be DRAM internally pulled low through a weak pull-down resistor to $V_{SS}$ .                                                                                                                                |  |  |

| NC                                                 |                | No Connect: No internal electrical connection is present.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| VDDQ                                               | Supply         | DQ Power Supply: 1.2 V +/- 0.06 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| VSSQ                                               | Supply         | DQ Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

Elite Semiconductor Microelectronics Technology Inc

Operation Temperature Condition -40° C~95° C

| VDD                                                                                                                                         | Supply | Power Supply: 1.2 V +/- 0.06 V                               |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------|--------|--------------------------------------------------------------|--|--|

| VSS                                                                                                                                         | Supply | Ground                                                       |  |  |

| VPP                                                                                                                                         | Supply | DRAM Activating Power Supply: 2.5V ( 2.375V min , 2.75V max) |  |  |

| VREFCA                                                                                                                                      | Supply | Reference voltage for CA                                     |  |  |

| ZQ                                                                                                                                          | Supply | Reference Pin for ZQ calibration                             |  |  |

| Note: Input only pins (BG0-BG1, BA0-BA1, A0-A15, ACT_n, RAS_n, CAS_n/A15, W E_n/A14, CS_n, CKE, ODT, and RESET_n) do not supplytermination. |        |                                                              |  |  |

Operation Temperature Condition -40° C~95° C

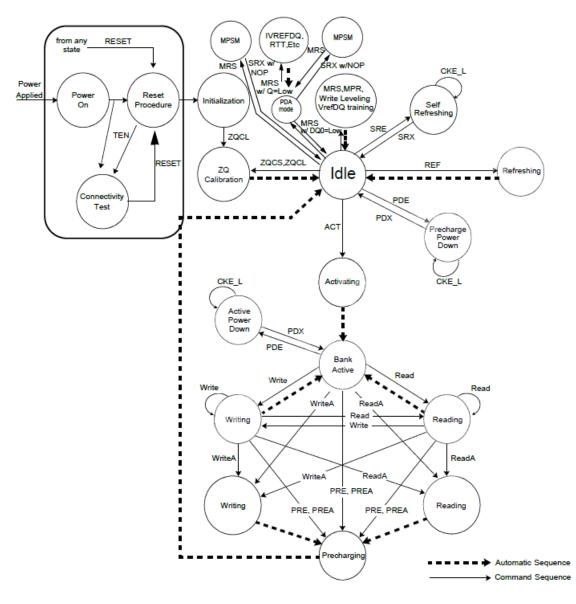

## Simplified State Diagram

### **State Diagram Command Definitions**

| Abbreviation | Function                     | Abbreviation | Function                 | Abbreviation | Function                  |

|--------------|------------------------------|--------------|--------------------------|--------------|---------------------------|

| ACT          | Active                       | Read         | RD, RDS4, RDS8           | PDE          | Enter Power-down          |

| PRE          | Precharge                    | Read A       | RDA, RDAS4,<br>RDAS8     | PDX          | Exit Power-down           |

| PREA         | Precharge All                | Write        | WR, WRS4, WRS8           | SRE          | Self-Refresh entry        |

| MRS          | Mode Register Set            | Write A      | WRA, WRAS4,<br>WRAS8     | SRX          | Self-Refresh exit         |

| REF          | Refresh                      | RESET_n      | Start RESET<br>Procedure | MPR          | Multi-Purpose<br>Register |

| TEN          | Boundary Scan Mode<br>Enable | -            | -                        | -            | -                         |

### Operation Temperature Condition -40° C~95° C

### **Basic Functionality**

The DDR4 SDRAM is a high-speed dynamic random-access memory internally configured as sixteen-banks, 4 bank group with 4 banks for each bank group for x4/x8 and eight-banks, 2 bank group with 4 banks for each bankgroup for x16 DRAM. The DDR4 SDRAM uses a 8n prefetch architecture to achieve high-speed operation. The 8n prefetch architecture is combined with an interface designed to transfer two data words per clock cycle at the I/O pins. A single read or write operation for the DDR4 SDRAM consists of a single 8n-bit wide, four clock data transfer at the internal DRAM core and eight corresponding n-bit wide, one-half clock cycle data transfers at the I/O pins.

Read and write operation to the DDR4 SDRAM are burst oriented, start at a selected location, and continue for a burst length of eight or a 'chopped' burst of four in a programmed sequence. Operation begins with the registration of an ACTIVATE Command, which is then followed by a Read or Write command. The address bits registered coincident with the ACTIVATE Command are used to select the bank and row to be activated (BG0-BG1 in x4/8 and BG0 in x16 select the bankgroup; BA0-BA1 select the bank; A0-A17 select the row; refer to "DDR4 SDRAM Addressing" for specific requirements). The address bits registered coincident with the Read or Write command are used to select the starting column location for the burst operation, determine if the auto precharge command is to be issued (via A10), and select BC4 or BL8 mode 'on the fly' (via A12) if enabled in the mode register.

Prior to normal operation, the DDR4 SDRAM must be powered up and initialized in a predefined manner.

The following sections provide detailed information covering device reset and initialization, register definition, command descriptions, and device operation.

### **RESET and Initialization Procedure**

For power-up and reset initialization, in order to prevent DRAM from functioning improperly default values for the following MR settings need to be defined.

Gear down mode (MR3 A[3]) : 0 = 1/2 Rate Per DRAM Addressability (MR3 A[4]) : 0 = Disable Max Power Saving Mode (MR4 A[1]) : 0 = Disable CS to Command/Address Latency (MR4 A[8:6]) : 000 = Disable CA Parity Latency Mode (MR5 A[2:0]) : 000 = Disable Hard Post Package Repair mode (MR4 A[13]) : 0 = Disable Soft Post Package Repair mode (MR4 A[5]) : 0 = Disable

Operation Temperature Condition -40° C~95° C

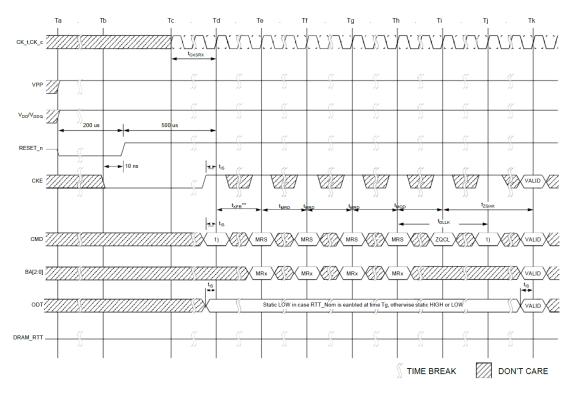

### **Power-up Initialization sequence**

The Following sequence is required for POWER UP and Initialization

Apply power (RESET\_n and TEN are recommended to be maintained below 0.2 x VDD, all other inputs may be undefined). RESET\_n needs to be maintained below 0.2 x VDD for minimum 200µs with stable power and TEN needs to be maintained below 0.2 x VDD for minimum 700us with stable power. CKE is pulled "Low" anytime before RESET\_n being de-asserted (min. time 10ns). The power voltage ramp time between 300mV to VDD<sub>min</sub> must be no greater than 200ms; and during the ramp, VDD ≥ VDDQ and (VDD-VDDQ) <0.3 Volts. VPP must ramp at the same time or earlier than VDD and VPP must be equal to or higher than VDD at all times.

- VDD and VDDQ are driven from a single power converter output, AND

- The voltage levels on all pins other than VDD, VDDQ, VSS, VSSQ must be less than or equal to VDDQ and VDD on one side and must be larger than or equal to VSSQ and VSS on the other side. In addition, VTT is limited to 0.76 V max once power ramp is finished, AND

- VrefCA tracks VDD/2.

- OR

- Apply VDD without any slope reversal before or at the same time as VDDQ

- Apply VDDQ without any slope reversal before or at the same time as VTT & VrefCA.

- Apply VPP without any slope reversal before or at the same time as VDD.

- The voltage levels on all pins other than VDD, VDDQ, VSS, VSSQ must be less than or equal to VDDQ and VDD on one side and must be larger than or equal to VSSQ and VSS on the other side.

- 2. After RESET\_n is de-asserted, wait for another 500us until CKE becomes active. During this time, the DRAM will start internal initialization; this will be done independently of external clocks.

- 3. Clock (CK\_t, CK\_c) need to be started and stabilized for at least 10ns or 5tCK (which is larger) before CKE goes active. Since CKE is a synchronous signal, the corresponding setup time to clock (tIS) must be met. Also a Deselect command must be registered (with tIS set up time to clock) at clock edge Td. Once the CKE registered "High" after Reset, CKE needs to be continuously registered "High" until the initialization sequence is finished, including expiration of tDLLK and tZQ<sub>init</sub>.

- 4. The DDR4 SDRAM keeps its on-die termination in high-impedance state as long as RESET\_n is asserted. Further, the SDRAM keeps its on-die termination in high impedance state after RESET\_n deassertion until CKE is registered HIGH. The ODT input signal may be in undefined state until tIS before CKE is registered HIGH. When CKE is registered HIGH, the ODT input signal may be statically held at either LOW or HIGH. If RTT\_NOM is to be enabled in MR1 the ODT input signal must be statically held LOW. In all cases, the ODT input signal remains static until the power up initialization sequence is finished, including the expiration of tDLLK and tZQ<sub>init</sub>.

- 5. After CKE is being registered high, wait minimum of Reset CKE Exit time, tXPR, before issuing the first MRS command to load mode register. (tXPR=Max(tXS, 5nCK)]

- 6. Issue MRS Command to to load MR3 with all application settings( To issue MRS command to MR3, provide " Low" to BG0, "High" to BA1, BA0)

- 7. Issue MRS command to load MR6 with all application settings (To issue MRS command to MR6, provide "Low" to BA0, "High" to BG0, BA1)

- 8. Issue MRS command to load MR5 with all application settings (To issue MRS command to MR5, provide "Low" to BA1, "High" to BG0, BA0)

- 9. Issue MRS command to load MR4 with all application settings (To issue MRS command to MR4, provide "Low" to BA1, BA0, "High" to BG0)

- 10. Issue MRS command to load MR2 with all application settings (To issue MRS command to MR2, provide "Low" to BG0, BA0, "High" to BA1)

- 11. Issue MRS command to load MR1 with all application settings (To issue MRS command to MR1, provide "Low" to BG0, BA1, "High" to BA0).

- 12. Issue MRS command to load MR0 with all application settings (To issue MRS command to MR0, provide "Low" to BG0, BA1, BA0)

- 13. Issue ZQCL command to starting ZQ calibration

- 14. Wait for both tDLLK and tZQ init completed

- 15. The DDR4 SDRAM is now ready for read/Write training (include Vref training and Write leveling).

Operation Temperature Condition -40° C~95° C

#### **RESET\_n and Initialization Sequence at Power- on Ramping**

#### Note:

- 1. From time point "Td" until "Tk", DES commands must be applied between MRS and ZQCL commands.

- 2. MRS Commands must be issued to all Mode Registers that have defined settings.

### VDD Slew rate at Power-up Initialization Sequence

#### **VDD Slew Rate**

| Symbol              | Min   | Max | Unit              |

|---------------------|-------|-----|-------------------|

| VDD_sl <sup>a</sup> | 0.004 | 600 | V/ms <sup>b</sup> |

| VDD_ona             |       | 200 | ms <sup>c</sup>   |

a. Measurement made between 300mv and 80% VDD minimum.

b. 20 MHz bandlimited measurement.

c. Maximum time to ramp VDD from 300 mv to VDD minimum.

Operation Temperature Condition -40° C~95° C

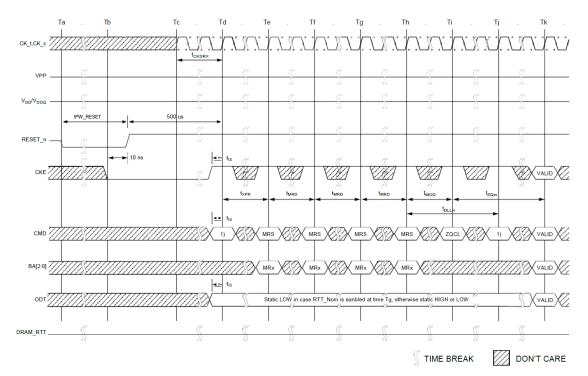

### **Reset Initialization with Stable Power**

The following sequence is required for RESET at no power interruption initialization.

- 1. Asserted RESET\_n below 0.2 \* VDD anytime when reset is needed (all other inputs may be undefined). RESET\_n needs to be maintained for minimum tPW\_RESET. CKE is pulled "LOW" before RESET\_n being de-asserted (min. time 10 ns).

- 2. Follow steps 2 to 10 in "Power-up Initialization Sequence".

- 3. The Reset sequence is now completed, DDR4 SDRAM is ready for Read/Write training (include Vref training and Write leveling)

Reset Procedure at Power Stable

#### Note:

- 1. From time point 'Td' until 'Tk', DES commands must be applied between MRS and ZQCL commands

- 2. MRS Commands must be issued to all Mode Registers that have defined settings.

Operation Temperature Condition -40° C~95° C

## **Register Definition**

### Programming the mode registers

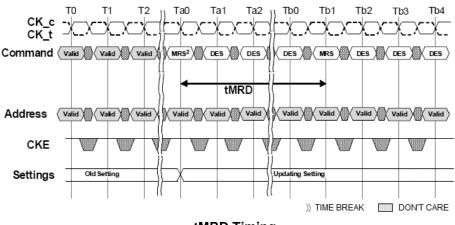

For application flexibility, various functions, features, and modes are programmable in seven Mode Registers, provided by the DDR4 SDRAM, as user defined variables and they must be programmed via a Mode Register Set (MRS) command. The mode registers are divided into various fields depending on the functionality and/or modes. As not all the Mode Registers (MR#) have default values defined, contents of Mode Registers must be initialized and/or re-initialized, i. e. written, after power up and/or reset for proper operation. Also the contents of the Mode Registers can be altered by re-executing the MRS command during normal operation. When programming the mode registers, even if the user chooses to modify only a sub-set of the MRS fields, all address fields within the accessed mode register must be redefined when the MRS command is issued. MRS command and DLL Reset do not affect array contents, which means these commands can be executed any time after power-up without affecting the array contents. MRS Commands can be issued only when DRAM is at idle state. The mode register set command cycle time, tMRD is required to complete the write operation to the mode register and is the minimum time required between two MRS commands.

#### Note:

- 1. This timing diagram shows C/A Parity Latency mode is "Disable" case.

- 2. List of MRS commands exception that do not apply to tMRD

- Gear down mode

- C/A Parity Latency mode

- CS to Command/Address Latency mode

- Per DRAM Addressability mode

- VrefDQ training Value, VrefDQ Training mode and VrefDQ training Range

Some of the Mode Register setting affect to address/command/control input functionality. These case, next MRS command can be allowed when the function updating by current MRS command completed.

The MRS commands that do not apply tMRD timing to next MRS command are listed in Note 2 of tMRD Timing figure.

These MRS command input cases have unique MR setting procedure, so refer to individual function description.

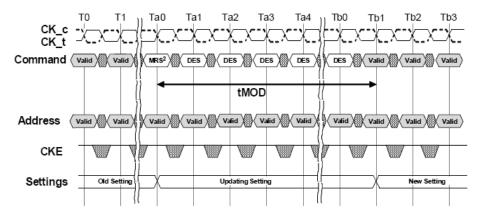

The most MRS command to Non-MRS command delay, tMOD, is required for the DRAM to update the features, and is the minimum time required from an MRS command to a non-MRS command excluding DES shown in tMOD Timing figure.

Operation Temperature Condition -40° C~95° C

### tMOD Timing

#### Note:

- 1. This timing diagram shows CA Parity Latency mode is "Disable" case.

- 2. List of MRS commands exception that do not apply to tMOD

- DLL Enable, DLL Reset

- VrefDQ training Value, internal Vref Monitor, VrefDQ Training mode and VrefDQ training Range

- Gear down mode

- Per DRAM addressability mode

- Maximum power saving mode

- CA Parity mode

Some of the mode register setting cases, function updating takes longer than tMOD. The MRS commands that do not apply tMOD timing to next valid command excluding DES is listed in Note 2 of tMOD Timing figure. These MRS command input cases have unique MR setting procedure, so refer to individual function description.

Operation Temperature Condition -40° C~95° C

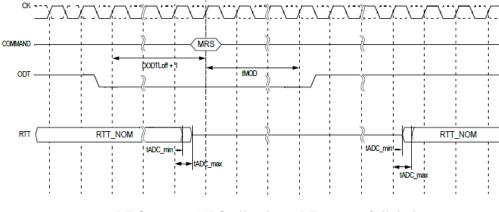

#### ODT Status at MRS affecting ODT turn-on/off timing

#### Note:

- 1. This timing diagram shows CA Parity Latency mode is "Disable" case.

- When an MRS command mentioned in this note affects RTT\_NOM turn on timings, RTT\_NOM turn off timings and RTT\_NOM value, this means the MR register value changes. The ODT signal should set to be low for at least DODTLoff +1 clock before their affecting MRS command is issued and remain low until tMOD expires. The following MR registers affects RTT\_NOM turn on timings, RTT\_NOM turn off timings and RTT\_NOM value and it requires ODT to be low when an MRS command change the MR register value. If there are no change the MR register value that correspond to commands mentioned in this note, then ODT signal is not require to be low.

- DLL control for precharge power down

- Additive latency and CAS read latency

- DLL enable and disable

- CAS write latency

- CA Parity mode

- Gear Down mode

- RTT\_NOM

The mode register contents can be changed using the same command and timing requirements during normal operation as long as the DRAM is in idle state, i.e., all banks are in the precharged state with tRP satisfied, all data bursts are completed and CKE is high prior to writing into the mode register. For MRS command, If RTT\_Nom function is intended to change (enable to disable and vice versa) or already enabled in DRAM MR, ODT signal must be registered Low ensuring RTT\_NOM is in an off state prior to MRS command affecting RTT\_NOM turn-on and off timing. Refer to note2 of ODT Status at MRS affecting ODT turn-on/off timing figure for this type of MRS. The ODT signal may be registered high after tMOD has expired. ODT signal is a don't care during MRS command if DRAM RTT\_Nom function is disabled in the mode register prior and after an MRS command.

Operation Temperature Condition -40° C~95° C

## **Mode Register**

#### MR0

| Address                   | Operating Mode             | Description                                                                                                                                          |  |  |

|---------------------------|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| BG1                       | RFU                        | 0 = must be programmed to 0 during MRS                                                                                                               |  |  |

| BG0, BA1:BA0              | MR Select                  | $000 = MR0$ $100 = MR4$ $001 = MR1$ $101 = MR5$ $010 = MR2$ $110 = MR6$ $011 = MR3$ $111 = RCW^1$                                                    |  |  |

| A17                       | RFU                        | 0 = must be programmed to 0 during MRS                                                                                                               |  |  |

| A13 <sup>5</sup> , A11:A9 | WR and RTP <sup>2, 3</sup> | Write Recovery and Read to Precharge for auto precharge (see Write Recovery and Read to Precharge (cycles) table)                                    |  |  |

| A8                        | DLL Reset                  | 0 = NO 1 = Yes                                                                                                                                       |  |  |

| A7                        | ТМ                         | 0 = Normal 1 = Test                                                                                                                                  |  |  |

| A12, A6:A4,A2             | CAS Latency <sup>4</sup>   | (see CAS Latency table)                                                                                                                              |  |  |

| A3                        | Read Burst Type            | 0 = Sequential 1 = Interleave                                                                                                                        |  |  |

| A1:A0                     | Burst Length               | 00 = 8 (Fixed) Abbreviated BL8MRS<br>01 = BC4 or 8 (on the fly) Abbreviated BC4OTF or BL8OTF<br>10 = BC4 (Fixed) Abbreviated BC4MRS<br>11 = Reserved |  |  |

#### Note:

- 1. Reserved for Register control word setting. DRAM ignores MR command with BG0, BA1;BA0=111 and doesn't respond. When RFU MR code setting is inputted, DRAM operation is not defined.

- WR (write recovery for autoprecharge)min in clock cycles is calculated following rounding algorithm defined. The WR value in the mode register must be programmed to be equal or larger than WRmin. The programmed WR value is used with tRP to determine tDAL.

- 3. The table shows the encodings for Write Recovery and internal Read command to Precharge command delay. For actual Write recovery timing, please refer to AC timing table.

- 4. The table only shows the encodings for a given Cas Latency. For actual supported Cas Latency, please refer to speedbin tables for each frequency. Cas Latency controlled by A12 is optional for 4Gb device.

- 5. A13 for WR and RTP setting is optional for 4Gb.

Operation Temperature Condition -40° C~95° C

| A13 | A11 | A10 | A9 | WR       | RTP      |

|-----|-----|-----|----|----------|----------|

| 0   | 0   | 0   | 0  | 10       | 5        |

| 0   | 0   | 0   | 1  | 12       | 6        |

| 0   | 0   | 1   | 0  | 14       | 7        |

| 0   | 0   | 1   | 1  | 16       | 8        |

| 0   | 1   | 0   | 0  | 18       | 9        |

| 0   | 1   | 0   | 1  | 20       | 10       |

| 0   | 1   | 1   | 0  | 22       | 11       |

| 0   | 1   | 1   | 1  | 24       | 12       |

| 1   | 0   | 0   | 0  | 26       | 13       |

| 1   | 0   | 0   | 1  | Reserved | Reserved |

| 1   | 0   | 1   | 0  | Reserved | Reserved |

| 1   | 0   | 1   | 1  | Reserved | Reserved |

| 1   | 1   | 0   | 0  | Reserved | Reserved |

| 1   | 1   | 0   | 1  | Reserved | Reserved |

| 1   | 1   | 1   | 0  | Reserved | Reserved |

| 1   | 1   | 1   | 1  | Reserved | Reserved |

### Write Recovery and Read to Precharge (cycles)

Operation Temperature Condition -40° C~95° C

### **CAS Latency**

| A12 | A6 | A5 | A4 | A2 | CAS Latency               |

|-----|----|----|----|----|---------------------------|

| 0   | 0  | 0  | 0  | 0  | 9                         |

| 0   | 0  | 0  | 0  | 1  | 10                        |

| 0   | 0  | 0  | 1  | 0  | 11                        |

| 0   | 0  | 0  | 1  | 1  | 12                        |

| 0   | 0  | 1  | 0  | 0  | 13                        |

| 0   | 0  | 1  | 0  | 1  | 14                        |

| 0   | 0  | 1  | 1  | 0  | 15                        |

| 0   | 0  | 1  | 1  | 1  | 16                        |

| 0   | 1  | 0  | 0  | 0  | 18                        |

| 0   | 1  | 0  | 0  | 1  | 20                        |

| 0   | 1  | 0  | 1  | 0  | 22                        |

| 0   | 1  | 0  | 1  | 1  | 24                        |

| 0   | 1  | 1  | 0  | 0  | 23                        |

| 0   | 1  | 1  | 0  | 1  | 17                        |

| 0   | 1  | 1  | 1  | 0  | 19                        |

| 0   | 1  | 1  | 1  | 1  | 21                        |

| 1   | 0  | 0  | 0  | 0  | 25                        |

| 1   | 0  | 0  | 0  | 1  | 26                        |

| 1   | 0  | 0  | 1  | 0  | 27 ( only 3DS available ) |

| 1   | 0  | 0  | 1  | 1  | 28                        |

| 1   | 0  | 1  | 0  | 0  | reserved for 29           |

| 1   | 0  | 1  | 0  | 1  | 30                        |

| 1   | 0  | 1  | 1  | 0  | reserved for 31           |

| 1   | 0  | 1  | 1  | 1  | 32                        |

| 1   | 1  | 0  | 0  | 0  | reserved                  |

### Operation Temperature Condition -40° C~95° C

#### Mode Register 1

| Address      | Operating Mode                  | Description                                                                                                                                                                          |  |

|--------------|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| BG1          | RFU                             | 0 = must be programmed to 0 during MRS                                                                                                                                               |  |

| BG0, BA1:BA0 | MR Select                       | $000 = MR0$ $100 = MR4$ $001 = MR1$ $101 = MR5$ $010 = MR2$ $110 = MR6$ $011 = MR3$ $111 = RCW^3$                                                                                    |  |

| A17          | RFU                             | 0 = must be programmed to 0 during MRS                                                                                                                                               |  |

| A13, A6, A5  | Rx CTLE control                 | 000 = Vendor Optimized Setting (default)001 = vendor defined010 = vendor defined011 = vendor defined100 = vendor defined101 = vendor defined110 = vendor defined111 = vendor defined |  |

| A12          | Qoff <sup>1</sup>               | 0 = Output buffer enabled<br>1 = Output buffer disabled                                                                                                                              |  |

| A11          | TDQS enable                     | 0 = Disable 1 = Enable                                                                                                                                                               |  |

| A10, A9, A8  | RTT_NOM                         | (see RTT_NOM table)                                                                                                                                                                  |  |

| A7           | Write Leveling Enable           | 0 = Disable 1 = Enable                                                                                                                                                               |  |

| A4, A3       | Additive Latency                | 00 = 0(AL disabled)         10 = CL-2           01 = CL-1         11 = Reserved                                                                                                      |  |

| A2, A1       | Output Driver Impedance Control | (see Output Driver Impedance Control table)                                                                                                                                          |  |

| A0           | DLL Enable                      | 0 = Disable <sup>2</sup> 1 = Enable                                                                                                                                                  |  |

Note:

1. Outputs disabled - DQs, DQS\_ts, DQS\_cs.

2. States reversed to "0 as Disable" with respect to DDR4.

3. Reserved for Register control word setting .DRAM ignores MR command with BG0,BA1;BA0=111 and doesn't respond. When RFU MR code setting is inputted, DRAM operation is not defined.

Operation Temperature Condition -40° C~95° C

### RTT\_NOM

| A10 | A9 | A8 | RTT_NOM         |

|-----|----|----|-----------------|

| 0   | 0  | 0  | RTT_NOM Disable |

| 0   | 0  | 1  | RZQ/4           |

| 0   | 1  | 0  | RZQ/2           |

| 0   | 1  | 1  | RZQ/6           |

| 1   | 0  | 0  | RZQ/1           |

| 1   | 0  | 1  | RZQ/5           |

| 1   | 1  | 0  | RZQ/3           |

| 1   | 1  | 1  | RZQ/7           |

### **Output Driver Impedance Control**

| A2 | A1 | Output Driver Impedance Control |

|----|----|---------------------------------|

| 0  | 0  | RZQ/7                           |

| 0  | 1  | RZQ/5                           |

| 1  | 0  | Reserved                        |

| 1  | 1  | Reserved                        |

Operation Temperature Condition -40 C~95 C

#### Mode Register 2

| Address      | Operating Mode                       | Description                                                                                                                                                                                                                                          |

|--------------|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BG1          | RFU                                  | 0 = must be programmed to 0 during MRS                                                                                                                                                                                                               |

| BG0, BA1:BA0 | MR Select                            | $000 = MR0$ $100 = MR4$ $001 = MR1$ $101 = MR5$ $010 = MR2$ $110 = MR6$ $011 = MR3$ $111 = RCW^1$                                                                                                                                                    |

| A17          | RFU                                  | 0 = must be programmed to 0 during MRS                                                                                                                                                                                                               |

| A13          | RFU                                  | 0 = must be programmed to 0 during MRS                                                                                                                                                                                                               |

| A12          | Write CRC                            | 0 = Disable 1 = Enable                                                                                                                                                                                                                               |

| A11, A10:A9  | RTT_WR                               | (see RTT_WR table)                                                                                                                                                                                                                                   |

| A8, A2       | RFU                                  | 0 = must be programmed to 0 during MRS                                                                                                                                                                                                               |

| A7:A6        | Low Power Auto Self Refresh (LP ASR) | <ul> <li>00 = Manual Mode (Normal Operaing Temperature Range)</li> <li>01 = Manual Mode (Reduced Operating Temperature Range)</li> <li>10 = Manual Mode (Extended Operating Temperature Range)</li> <li>11 = ASR Mode (Auto Self Refresh)</li> </ul> |

| A5:A3        | CAS Write Latency(CWL)               | see CWL (CAS Write Latency) table)                                                                                                                                                                                                                   |

| A1:A0        | RFU                                  | 0 = must be programmed to 0 during MRS                                                                                                                                                                                                               |

#### Note:

1. Reserved for Register control word setting .DRAM ignores MR command with BG0,BA1;BA0=111 and doesn't respond. When RFU MR code setting is inputted, DRAM operation is not defined.

Operation Temperature Condition -40°C~95°C

### RTT\_WR

| A11 | A10 | A9 | RTT_WR          |

|-----|-----|----|-----------------|

| 0   | 0   | 0  | Dynamic ODT Off |

| 0   | 0   | 1  | RZQ/2           |

| 0   | 1   | 0  | RZQ/1           |

| 0   | 1   | 1  | Hi-Z            |

| 1   | 0   | 0  | RZQ/3           |

| 1   | 0   | 1  | Reserved        |

| 1   | 1   | 0  | Reserved        |

| 1   | 1   | 1  | Reserved        |

#### **CWL (CAS Write Latency)**

| A5 | 5 A4 A3 CWL |   | • • | a Rate in MT/s<br>rite Preamble | Operating Data Rate in MT/s<br>for 2 tCK Write Preamble <sup>1</sup> |             |             |  |

|----|-------------|---|-----|---------------------------------|----------------------------------------------------------------------|-------------|-------------|--|

|    |             |   |     | 1st Set                         | 2nd Set                                                              | 1st Set     | 2nd Set     |  |

| 0  | 0           | 0 | 9   | 1600                            |                                                                      |             |             |  |

| 0  | 0           | 1 | 10  | 1866                            |                                                                      |             |             |  |

| 0  | 1           | 0 | 11  | 2133                            | 1600                                                                 |             |             |  |

| 0  | 1           | 1 | 12  | 2400                            | 1866                                                                 |             |             |  |

| 1  | 0           | 0 | 14  | 2666                            | 2133                                                                 | 2400        |             |  |

| 1  | 0           | 1 | 16  | 2933/ 3200                      | 2400                                                                 | 2666        | 2400        |  |

| 1  | 1           | 0 | 18  |                                 | 2666                                                                 | 2933 / 3200 | 2666        |  |

| 1  | 1           | 1 | 20  |                                 | 2933 / 3200                                                          |             | 2933 / 3200 |  |

#### Note:

1. The 2 tCK Write Preamble is valid for DDR4-2400/2666/2933/3200 Speed Grade. For the 2nd Set of 2 tCK Write Preamble, no additional CWL is needed.

Operation Temperature Condition -40 C~95 C

#### Mode Register 3

| Address      | Operating Mode                                | Description                                                                                       |

|--------------|-----------------------------------------------|---------------------------------------------------------------------------------------------------|

| BG1          | RFU                                           | 0 = must be programmed to 0 during MRS                                                            |

| BG0, BA1:BA0 | MR Select                                     | $000 = MR0$ $100 = MR4$ $001 = MR1$ $101 = MR5$ $010 = MR2$ $110 = MR6$ $011 = MR3$ $111 = RCW^1$ |

| A17          | RFU                                           | 0 = must be programmed to 0 during MRS                                                            |

| A13          | RFU                                           | 0 = must be programmed to 0 during MRS                                                            |

| A12:A11      | MPR Read Format                               | 00 = Serial10 = Staggered01 = Parallel11 = Reserved                                               |

| A10:A9       | Write CMD Latency when CRC and DM are enabled | see Write Command Latency when CRC and DM are both enabled table                                  |

| A8, A6       | Fine Granularity Refresh Mode                 | see Fine Granularity Refresh Mode table                                                           |

| A5           | Temperature sensor readout                    | 0 = Disable 1 = Enable                                                                            |

| A4           | Per DRAM Addressability                       | 0 = Disable 1 = Enable                                                                            |

| A3           | Geardown Mode                                 | 0 = 1/2 Rate 1 = 1/4 Rate                                                                         |

| A2           | MPR Operation                                 | 0 = Normal 1 = Dataflow from/to MPR                                                               |

| A1:A0        | MPR page Selection                            | 00 = Page010 = Page201 = Page 111 = Page3(see MPR Data Format table)                              |

#### Note:

1. Reserved for Register control word setting. DRAM ignores MR command with BG0,BA1;BA0=111 and doesn't respond. When RFU MR code setting is inputted, DRAM operation is not defined.

Operation Temperature Condition -40° C~95° C

| A8 | A7 | A6 | Fine Granularity Refresh |

|----|----|----|--------------------------|

| 0  | 0  | 0  | Normal (Fixed 1x)        |

| 0  | 0  | 1  | Fixed 2x                 |

| 0  | 1  | 0  | Fixed 4x                 |

| 0  | 1  | 1  | Reserved                 |

| 1  | 0  | 0  | Reserved                 |

| 1  | 0  | 1  | Enable on the fly 2x     |

| 1  | 1  | 0  | Enable on the fly 4x     |

| 1  | 1  | 1  | Reserved                 |

### Fine Granularity Refresh Mode

#### MR3 A<10:9> Write Command Latency when CRC and DM are both enabled

| A10 | A9 | CRC+DM Write Command Latency | Operating Data Rate |

|-----|----|------------------------------|---------------------|

| 0   | 0  | 4nCK                         | 1600                |

| 0   | 1  | 5nCK                         | 1866,2133,2400,2666 |

| 1   | 0  | 6nCK                         | 2933,3200           |

| 1   | 1  | RFU                          | RFU                 |

Note:

1. Write Command latency when CRC and DM are both enabled:

2. At less than or equal to 1600 then 4nCK; neither 5nCK nor 6nCK

3. At greater than 1600 and less than or equal to 2666 then 5nCK; neither 4nCK nor 6nCK

4. At greater than 2666 and less than or equal to 3200 then 6nCK; neither 4nCK nor 5nCK

Operation Temperature Condition -40° C~95° C

### MPR page0 (Training Pattern)

#### **MPR Data Format**

| Address | MPR Location | [7] | [6] | [5] | [4] | [3] | [2] | [1] | [0] | Note                       |

|---------|--------------|-----|-----|-----|-----|-----|-----|-----|-----|----------------------------|

| BA1:BA0 | 00 = MPR0    | 0   | 1   | 0   | 1   | 0   | 1   | 0   | 1   | Deed/                      |

|         | 01 = MPR1    | 0   | 0   | 1   | 1   | 0   | 0   | 1   | 1   | Read/<br>Write<br>(default |

|         | 10 = MPR2    | 0   | 0   | 0   | 0   | 1   | 1   | 1   | 1   |                            |

|         | 11 = MPR3    | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | value)                     |

#### MPR page1 (CA Parity Error Log)

| Address | MPR Location | [7]             | [6]             | [5]                            | [4]      | [3]      | [2]   | [1]   | [0]           | Note         |

|---------|--------------|-----------------|-----------------|--------------------------------|----------|----------|-------|-------|---------------|--------------|

|         | 00 = MPR0    | A[7]            | A[6]            | A[5]                           | A[4]     | A[3]     | A[2]  | A[1]  | A[0]          |              |

|         | 01 = MPR1    | CAS_n/<br>A15   | WE_n/<br>A14    | A[13]                          | A[12]    | A[11]    | A[10] | A[9]  | A[8]          |              |

| BA1:BA0 | 10 = MPR2    | PAR             | ACT_n           | BG[1]                          | BG[0]    | BA[1]    | BA[0] | A[17] | RAS_n/<br>A16 | Read<br>only |

|         |              | CRC             | Parity          | CA Parity Latency <sup>4</sup> |          |          |       |       |               | Uniy         |

|         | 11 = MPR3    | Error<br>Status | Error<br>Status | MR5.A[2]                       | MR5.A[1] | MR5.A[0] | C[2]  | C[1]  | C[0]          |              |

#### Note:

1. MPR used for C/A parity error log readout is enabled by setting A[2] in MR3

2. For higher density of DRAM, where A[17] is not used, MPR2[1] should be treated as don't care.

3. If a device is used in monolithic application, where C[2:0] are not used, then MPR3[2:0] should be treated as don't care.

4. MPR3 bit 0~2 (CA parity latency) reflects the latest programmed CA parity latency values.

Operation Temperature Condition -40° C~95° C

### MPR page2 (MRS Readout)

| Address | MPR<br>Location | [7]                      | [6]     | [5]                                                                                         | [4] | [3]      | [2] | [1]            | [0]   | Note |  |

|---------|-----------------|--------------------------|---------|---------------------------------------------------------------------------------------------|-----|----------|-----|----------------|-------|------|--|

|         | 00 = MPR0       | hPPR                     | sPPR    | sPPR         RTT_WR         Temperature<br>Sensor Status         CRC<br>Write         Rtt_V |     |          |     |                |       |      |  |

|         |                 | _                        | _       | MR2                                                                                         | _   | —        | MR2 | Ν              | 1R2   |      |  |

|         |                 |                          |         | A11                                                                                         |     | —        | A12 | A10            | A9    |      |  |

|         | 01 = MPR1       | Vref DQ<br>Trng<br>range |         | Vref DQ Trng range Geardwn Enable                                                           |     |          |     |                |       |      |  |

|         |                 | MR6                      | MR6     |                                                                                             |     |          |     |                | MR3   | Read |  |

| BA1:BA0 |                 | A6                       | A5      | A4                                                                                          | A3  | A2       | A1  | A0             | A3    | only |  |

|         |                 |                          | C       | CAS Latency                                                                                 |     |          | CA  | S Write La     | tency |      |  |

|         | 10 = MPR2       |                          |         | MR0                                                                                         |     |          |     | MR2            |       |      |  |

|         |                 | A6                       | A5      | A4                                                                                          | A2  | A12      | A5  | A4             | A3    |      |  |

|         |                 |                          | Rtt_Nom |                                                                                             |     | Rtt_Park |     | Driver Impedan |       |      |  |

|         | 11 = MPR3       |                          | MR1     |                                                                                             |     | MR5      |     | MR1            |       |      |  |

|         |                 | A10                      | A9      | A6                                                                                          | A8  | A7       | A6  | A2             | A1    |      |  |

MR bit for Temperature Sensor Readout

MR3 bit A5=1: DRAM updates the temperature sensor status to MPR Page 2 (MPR0 bits A4:A3). Temperature data is guaranteed by the DRAM to be no more than 32ms old at the time of MPR Read of the Temperature Sensor Status bits.

MR3 bit A5=0: DRAM disables updates to the temperature sensor status in MPR Page 2(MPR0-bit A4:A3)

| MPR0 bit A4 | MPR0 bit A3 | Refresh Rate Range          |  |  |  |  |

|-------------|-------------|-----------------------------|--|--|--|--|

| 0           | 0           | Sub 1X refresh ( > tREFI)   |  |  |  |  |

| 0           | 1           | 1X refresh rate(= tREFI)    |  |  |  |  |

| 1           | 0           | 2X refresh rate(1/2* tREFI) |  |  |  |  |

| 1           | 1           | rsvd                        |  |  |  |  |

### MPR page3 (Vendor use only)<sup>1</sup>

| Address  | MPR Location | [7] | [6]            | [5] | [4] | [3] | [2] | [1] | [0] | Note |  |  |  |

|----------|--------------|-----|----------------|-----|-----|-----|-----|-----|-----|------|--|--|--|

|          | 00 = MPR0    |     | don't care     |     |     |     |     |     |     |      |  |  |  |

| BA1:BA0  | 01 = MPR1    |     | don't care     |     |     |     |     |     |     |      |  |  |  |

| DA I.DAU | 10 = MPR2    |     | don't care     |     |     |     |     |     |     |      |  |  |  |

|          | 11 = MPR3    |     | don't care MAC |     |     |     |     |     |     |      |  |  |  |

Note:

1. MPR page3 is specifically assigned to DRAM. Actual encoding method is vendor specific.

Operation Temperature Condition -40° C~95° C

#### Mode Register 4

| Address      | Operating Mode                          | Description                                                                 |                                                                                    |  |

|--------------|-----------------------------------------|-----------------------------------------------------------------------------|------------------------------------------------------------------------------------|--|

| BG1          | RFU                                     | 0 = must be programmed to 0 during MRS                                      |                                                                                    |  |

| BG0, BA1:BA0 | MR Select                               | 000 = MR0<br>001 = MR1<br>010 = MR2<br>011 = MR3                            | 100 = MR4<br>101 = MR5<br>110 = MR6<br>$111 = RCW^{1}$                             |  |

| A17          | RFU                                     | 0 = must be programmed to                                                   | 0 during MRS                                                                       |  |

| A13          | hPPR                                    | 0 = Disable                                                                 | 1 = Enable                                                                         |  |

| A12          | Write Preamble                          | 0 = 1 nCK                                                                   | 1 = 2 nCK                                                                          |  |

| A11          | Read Preamble                           | 0 = 1 nCK                                                                   | 1 = 2 nCK                                                                          |  |

| A10          | Read Preamble Training Mode             | 0 = Disable                                                                 | 1 = Enable                                                                         |  |

| A9           | Self Refresh Abort                      | 0 = Disable                                                                 | 1 = Enable                                                                         |  |

| A8:A6        | CS to CMD/ADDR Latency Mode<br>(cycles) | 000 = Disable<br>001 = 3<br>010 = 4<br>011 = 5<br>(see CS to CMD / ADDR Lat | 100 = 6<br>101 = 8<br>110 = Reserved<br>111 = Reserved<br>ency Mode Setting table) |  |

| A5           | sPPR                                    | 0 = Disable                                                                 | 1 = Enable                                                                         |  |

| A4           | Internal Vref Monitor                   | 0 = Disable                                                                 | 1 = Enable                                                                         |  |

| A3           | Temperature Controlled Refresh Mode     | 0 = Disable                                                                 | 1 = Enable                                                                         |  |

| A2           | Temperature Controlled Refresh Range    | 0 = Normal                                                                  | 1 = Extended                                                                       |  |

| A1           | Maximum Power Down Mode                 | 0 = Disable                                                                 | 1 = Enable                                                                         |  |

| A0           | RFU                                     | 0 = must be programmed to                                                   | 0 during MRS                                                                       |  |

Note:

1. Reserved for Register control word setting .DRAM ignores MR command with BG0,BA1;BA0=111 and doesn't respond. When RFU MR code setting is inputted, DRAM operation is not defined.

CS to CMD / ADDR Latency Mode Setting

| A8 | A7 | A6 | CAL      |  |

|----|----|----|----------|--|

| 0  | 0  | 0  | Disable  |  |

| 0  | 0  | 1  | 3        |  |

| 0  | 1  | 0  | 4        |  |

| 0  | 1  | 1  | 5        |  |

| 1  | 0  | 0  | 6        |  |

| 1  | 0  | 1  | 8        |  |

| 1  | 1  | 0  | Reserved |  |

| 1  | 1  | 1  | Reserved |  |

Operation Temperature Condition -40° C~95° C

#### Mode Register 5

| Address      | Operating Mode                          | Description                                                                                       |

|--------------|-----------------------------------------|---------------------------------------------------------------------------------------------------|

| BG1          | RFU                                     | 0 = must be programmed to 0 during MRS                                                            |

| BG0, BA1:BA0 | MR Select                               | $000 = MR0$ $100 = MR4$ $001 = MR1$ $101 = MR5$ $010 = MR2$ $110 = MR6$ $011 = MR3$ $111 = RCW^1$ |

| A17          | RFU                                     | 0 = must be programmed to 0 during MRS                                                            |

| A13          | RFU                                     | 0 = must be programmed to 0 during MRS                                                            |

| A12          | Read DBI                                | 0 = Disable 1 = Enable                                                                            |

| A11          | Write DBI                               | 0 = Disable 1 = Enable                                                                            |

| A10          | Data Mask                               | 0 = Disable 1 = Enable                                                                            |

| A9           | CA parity Persistent                    | 0 = Disable 1 = Enable                                                                            |

| A8:A6        | RTT_PARK                                | see RTT_PARK table                                                                                |

| A5           | ODT Input Buffer during Power Down mode | 0 = ODT input buffer is activated<br>1 = ODT input buffer is deactivated                          |

| A4           | C/A Parity Error Status                 | 0 = Clear 1 = Error                                                                               |

| A3           | CRC Error Clear                         | 0 = Clear 1 = Error                                                                               |

| A2:A0        | C/A Parity Latency Mode                 | see the table of C/A Parity Latency Mode table                                                    |

#### Note:

1. Reserved for Register control word setting .DRAM ignores MR command with BG0,BA1;BA0=111 and doesn't respond. When RFU MR code setting is inputted, DRAM operation is not defined.

2. When RTT\_NOM Disable is set in MR1, A5 of MR5 will be ignored.

Operation Temperature Condition -40°C~95°C

#### RTT\_PARK

| A8 | A7 | A6 | RTT_PARK         |

|----|----|----|------------------|

| 0  | 0  | 0  | RTT_PARK Disable |

| 0  | 0  | 1  | RZQ/4            |

| 0  | 1  | 0  | RZQ/2            |

| 0  | 1  | 1  | RZQ/6            |

| 1  | 0  | 0  | RZQ/1            |

| 1  | 0  | 1  | RZQ/5            |

| 1  | 1  | 0  | RZQ/3            |

| 1  | 1  | 1  | RZQ/7            |

### C/A Parity Latency Mode

| A2 | A1 | A0 | PL       | Speed Bin      |

|----|----|----|----------|----------------|

| 0  | 0  | 0  | Disable  | —              |

| 0  | 0  | 1  | 4        | 1600,1866,2133 |

| 0  | 1  | 0  | 5        | 2400, 2666     |

| 0  | 1  | 1  | 6        | 2933, 3200     |

| 1  | 0  | 0  | 8        | RFU            |

| 1  | 0  | 1  | Reserved | —              |

| 1  | 1  | 0  | Reserved | —              |

| 1  | 1  | 1  | Reserved | —              |

#### Note:

1. Parity latency must be programmed according to timing parameters by speed grade table

Operation Temperature Condition -40° C~95° C

#### MR6

| Address      | Operating Mode         | Description                                                                                       |  |  |

|--------------|------------------------|---------------------------------------------------------------------------------------------------|--|--|

| BG1          | RFU                    | 0 = must be programmed to 0 during MRS                                                            |  |  |

| BG0, BA1:BA0 | MR Select              | $000 = MR0$ $100 = MR4$ $001 = MR1$ $101 = MR5$ $010 = MR2$ $110 = MR6$ $011 = MR3$ $111 = RCW^1$ |  |  |

| A17          | RFU                    | 0 = must be programmed to 0 during MRS                                                            |  |  |

| A13, A9, A8  | RFU                    | 0 = must be programmed to 0 during MRS                                                            |  |  |

| A12:A10      | tCCD_L                 | (see the table of "tCCD_L and tDLLK")                                                             |  |  |

| A7           | VrefDQ Training Enable | 0 = Disable (Normal operation Mode)<br>1 = Enable (Training Mode)                                 |  |  |

| A6           | VrefDQ Training Range  | (see the table of "VrefDQ Training: Range")                                                       |  |  |

| A5:A0        | VrefDQ Training Value  | (see the table of "VrefDQ Training: Values")                                                      |  |  |

Note:

1. Reserved for Register control word setting. DRAM ignores MR command with BG0, BA1; BA0=111 and doesn't respond.

| A12 | A11 | A10 | tCCD_L.min (nCK) <sup>1</sup> | tDLLKmin (nCK) <sup>1</sup> | Note                                             |

|-----|-----|-----|-------------------------------|-----------------------------|--------------------------------------------------|

| 0   | 0   | 0   | 4                             |                             | Data rate≦1333Mbps                               |

| 0   | 0   | 1   | 5                             | 597                         | 1333Mbps < Data rate≦1866Mbps<br>(1600/1866Mbps) |

| 0   | 1   | 0   | 6                             | 768                         | 1866Mbps < Data rate≦2400Mbps<br>(2133/2400Mbps) |

| 0   | 1   | 1   | 7                             | 4004                        | 2400Mbps < Data rate≦2666Mbps<br>(2666Mbps)      |

| 1   | 0   | 0   | 8                             | 1024                        | 2666Mbps < Data rate≦3200Mbps<br>(2933/3200Mbps) |

| 1   | 0   | 1   |                               |                             | _                                                |

| 1   | 1   | 0   | Reserved                      | _                           | _                                                |

| 1   | 1   | 1   |                               |                             | _                                                |

#### tCCD\_L and tDLLK

Note:

1. tCCD\_L/tDLLK should be programmed according to the value defined in AC parameter table per operating frequency

### VrefDQ Training: Range

| A6 | VrefDQ Range |

|----|--------------|

| 0  | Range 1      |

| 1  | Range 2      |

**ESMT**

# M16U4G16256A

Operation Temperature Condition -40° C~95° C

| A5:A0   | Range1 | Range2 | A5:A0             | Range1   | Range2   |

|---------|--------|--------|-------------------|----------|----------|

| 00 0000 | 60.00% | 45.00% | 01 1010           | 76.90%   | 61.90%   |

| 00 0001 | 60.65% | 45.65% | 01 1011           | 77.55%   | 62.55%   |

| 00 0010 | 61.30% | 46.30% | 01 1100           | 78.20%   | 63.20%   |

| 00 0011 | 61.95% | 46.95% | 01 1101           | 78.85%   | 63.85%   |

| 00 0100 | 62.60% | 47.60% | 01 1110           | 79.50%   | 64.50%   |

| 00 0101 | 63.25% | 48.25% | 01 1111           | 80.15%   | 65.15%   |

| 00 0110 | 63.90% | 48.90% | 10 0000           | 80.80%   | 65.80%   |

| 00 0111 | 64.55% | 49.55% | 10 0001           | 81.45%   | 66.45%   |

| 00 1000 | 65.20% | 50.20% | 10 0010           | 82.10%   | 67.10%   |

| 00 1001 | 65.85% | 50.85% | 10 0011           | 82.75%   | 67.75%   |

| 00 1010 | 66.50% | 51.50% | 10 0100           | 83.40%   | 68.40%   |