Ordering number : EN\*A1990 Preliminary

## SANYO Semiconductors **DATA SHEET**

An ON Semiconductor Company

# LV23411V — For Home Stereo Systems FM/AM Tuner IC

#### Overview

The LV23411V is single chip tuner IC, and FM/AM radio is able to be realized with few external parts.

#### **Functions**

- FM tuner

- AM tuner

- MPX Stereo Decoder

- Tuning system

#### **Features**

- No alignments necessary

- Reduction of external component counts

- Large audio output signal is available for home stereo systems

- Worldwide FM band support (64 to 108MHz)

- Worldwide AM band support (520 to 1710kHz)

- Soft-mute, Stereo-blend function

- LV23411 corresponds to Europe Immunity standard (EN55020-S1)

- I<sup>2</sup>C control interface

- Any and all SANYO Semiconductor Co.,Ltd. products described or contained herein are, with regard to "standard application", intended for the use as general electronics equipment. The products mentioned herein shall not be intended for use for any "special application" (medical equipment whose purpose is to sustain life, aerospace instrument, nuclear control device, burning appliances, transportation machine, traffic signal system, safety equipment etc.) that shall require extremely high level of reliability and can directly threaten human lives in case of failure or malfunction of the product or may cause harm to human bodies, nor shall they grant any guarantee thereof. If you should intend to use our products for new introduction or other application different from current conditions on the usage of automotive device, communication device, office equipment, industrial equipment etc., please consult with us about usage condition (temperature, operation time etc.) prior to the intended use. If there is no consultation or inquiry before the intended use, our customer shall be solely responsible for the use.

- Specifications of any and all SANYO Semiconductor Co.,Ltd. products described or contained herein stipulate the performance, characteristics, and functions of the described products in the independent state, and are not guarantees of the performance, characteristics, and functions of the described products as mounted in the customer's products or equipment. To verify symptoms and states that cannot be evaluated in an independent device, the customer should always evaluate and test devices mounted in the customer's products or equipment.

#### **Specifications**

#### **Absolute Maximum Ratings** at Ta = 25°C, GND1 = GND2 = GND3 = GND4 = GND5 = 0V

| Parameter                   | Symbol                | Conditions   | Ratings     | Unit |

|-----------------------------|-----------------------|--------------|-------------|------|

| Maximum supply voltage      | V <sub>CC</sub> max   |              | 10.0        | V    |

| Digital output voltage      | V <sub>O</sub> max    | SDA          | 3.6         | V    |

| Digital input voltage       | V <sub>IN</sub> 1 max | SDA, SCL     | 3.6         | V    |

|                             | V <sub>IN</sub> 2 max | CLK IN       | 3.6         | V    |

| Allowable power dissipation | Pd max                | Ta ≤ 70°C *1 | 450         | mW   |

| Operating temperature       | Topr                  |              | -20 to +70  | °C   |

| Storage temperature         | Tstg                  |              | -40 to +125 | °C   |

<sup>\*1 :</sup> Mounted on a specified board. Board size is 114.3mm × 76.1mm × 1.6mm, glass epoxy.

## $\textbf{Operating Conditions} \ \ \text{at Ta} = \underline{25^{\circ}\text{C}}, \ \underline{GND1} = \underline{GND2} = \underline{GND3} = \underline{GND4} = \underline{GND5} = \underline{0V}$

| Parameter                      | Symbol             | Conditions                       | Ratings    | Unit |

|--------------------------------|--------------------|----------------------------------|------------|------|

| Recommended supply voltage     | V <sub>CC</sub>    |                                  | 9.0        | V    |

| Operating supply voltage Range | V <sub>CC</sub> op | Register 1Eh bit 1 (LEVSHIF) = 0 | 4.5 to 6.5 | V    |

| * Note                         |                    | Register 1Eh bit 1 (LEVSHIF) = 1 | 8.5 to 9.5 | V    |

<sup>\*</sup> Note : supply the stabilized voltage.

#### Interface Conditions at Ta = -20 to +70°C, GND1 = GND2 = GND3 = GND4 = GND5 = 0V

| Parameter                  | Symbol            | Symbol Conditions |      | Unit   |      |       |

|----------------------------|-------------------|-------------------|------|--------|------|-------|

| Falametei                  | Symbol            | Conditions        | min  | typ    | max  | Offic |

| High level input voltage   | V <sub>IH</sub> 1 | SDA, SCL          | 2.3  |        | 3.5  | ٧     |

|                            | V <sub>IH</sub> 2 | CLK IN            | 2.3  |        | 3.5  | V     |

| Low level input voltage    | V <sub>IL</sub> 1 | SDA, SCL          | 0    |        | 0.5  | V     |

|                            | V <sub>IL</sub> 2 | CLK IN            | 0    |        | 0.3  | V     |

| Output voltage             | VO                | SDA               | 0    |        | 3.5  | V     |

| Crystal frequency          | fin               | CLK IN            |      | 32.768 |      | kHz   |

| Crystal frequency accuracy | faccuracy         |                   | -100 |        | +100 | ppm   |

#### **Operating Characteristics** at $Ta = 25^{\circ}C$ , $V_{CC} = 9.0V$ , with the designated circuit.

| Doromotor                      | Cumb of            | Symbol Conditions                                                                     |              | Llmit       |      |       |  |

|--------------------------------|--------------------|---------------------------------------------------------------------------------------|--------------|-------------|------|-------|--|

| Parameter                      | Symbol             | Symbol                                                                                |              | typ         | max  | Unit  |  |

| MONO : 75kHz dev               |                    | dBμV, fm = 1kHz, De-emphasis = 50μs, IF = 225KHz,                                     | , BW = 45%   |             |      |       |  |

| STEREO: L+R = 67.5kHz dev, Pil |                    | Discours A. F. Ch                                                                     | 0.4.         |             |      |       |  |

| Current drain                  | $I_{CC}$ FM        | Pin 9 output, Audio filter = IHF-BP F, Soft mute = off No input                       | ,Sort stereo | = OII<br>40 | 45   | mA    |  |

|                                | - 00               | '                                                                                     | 33           |             |      |       |  |

| 30dB S/N sensitivity           | SN30               | S/N = 30dB input level                                                                |              | 10          | 15   | dBμV  |  |

| Signal-to-noise ratio          | SNR                | MONO                                                                                  | 62           | 70          |      | dB    |  |

| Total harmonic distortion      | THD                | MONO                                                                                  |              | 0.5         | 1.5  | %     |  |

|                                | THD-ST             | STEREO                                                                                |              | 0.5         | 2.5  | %     |  |

| Demodulation output            | V <sub>O</sub> 3   | MONO                                                                                  | 518          | 775         | 1160 | mVrms |  |

| SD operation level             | SD                 | FS = 4                                                                                | 17           | 25          | 33   | dBμV  |  |

| Mute attenuation               | Mute               | MONO                                                                                  | 60           | 75          |      | dB    |  |

| Stereo separation              | Sep                | Pin 10 output/Pin 9 output                                                            | 20           | 35          |      | dB    |  |

| Carrier leak                   | CL                 | STEREO SNR, Audio filter = OFF                                                        | 30           | 40          |      | dB    |  |

| Stereo on level                | ST-ON              | L+R = 67.5kHz dev, Pilot level                                                        |              | 3.0         | 6.5  | %     |  |

|                                |                    | = 400Hz, mod = 30% IF = 53KHz, BW = 50%<br>Pin 9 output, Audio filter = 15kHz LPF OFF |              |             |      |       |  |

| Current drain                  | I <sub>CC</sub> AM | No input                                                                              | 30           | 35          | 40   | mA    |  |

| 20dB S/N sensitivity           | SN20               | S/N = 20dB input level                                                                |              | 48          | 65   | dΒμV  |  |

| Signal-to-noise ratio          | SNR                |                                                                                       | 42           | 50          |      | dB    |  |

| Total harmonic distortion      | THD                |                                                                                       |              | 0.8         | 2.8  | %     |  |

| Demodulation output            | V <sub>O</sub> 2   |                                                                                       | 122          | 173         | 245  | mVrms |  |

| SD operation level             | SD                 | FS = 4                                                                                | 46           | 54          | 64   | dBμV  |  |

| Mute attenuation               | Mute               | 15kHz LPF ON                                                                          | 50           | 65          |      | dB    |  |

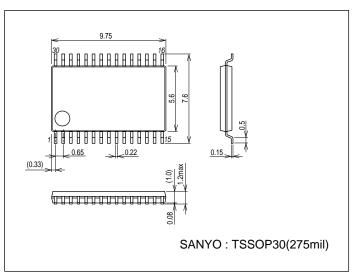

## **Package Dimensions**

unit: mm (typ)

3259

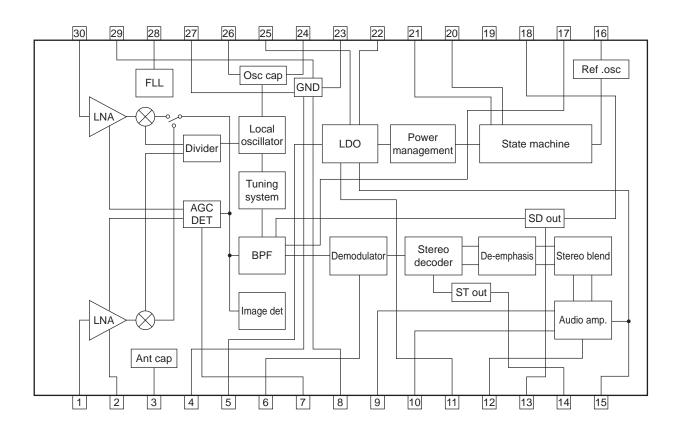

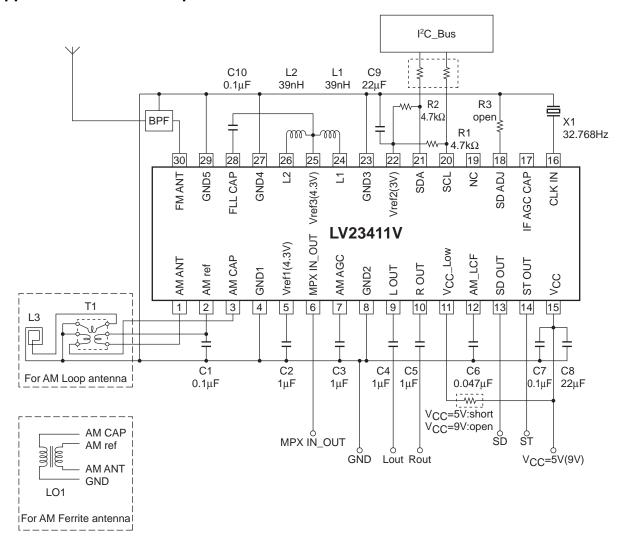

## **Block Diagram**

Pin descriptions

|     | acscriptic           | ,,,, |                                                  |                                                                                                                         |                |

|-----|----------------------|------|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|----------------|

| Pin | Pin name             | I/O  | Descriptions                                     | Remarks                                                                                                                 | DC voltage     |

| 1   | AM-ANT               | 1    | AM antenna input                                 | Connect to pin2 through Matching coil or Ferrite antenna.                                                               | -              |

| 2   | AM-REF               | 0    | Reference voltage for AM part                    | Connect to pin1 through Matching coil or Ferrite antenna.                                                               | 2.2V           |

| 3   | AM-CAP               | I    | AM capacitor bank                                | Exteranal inductor (recommendation value) is connected between this pin and GND.                                        | -              |

| 4   | GND1                 | -    | AM antenna GND                                   | Connected to GND                                                                                                        | 0V             |

| 5   | VREF1                | 0    | Reference voltage for analog                     | Capacitor of 1µF is connected between this pin and GND.                                                                 | 4.3V           |

| 6   | MPX IN_OUT           | 0    | Demodulato output                                | When RDS used, LC72725 is applicable                                                                                    | 2.5V           |

| 7   | AM RF-AGC            | 0    | AM RF AGC output                                 | Capacitor of 1µF is connected between this pin and GND.                                                                 | -              |

| 8   | GND2                 | -    | Analog GND                                       | Connected to GND                                                                                                        | 0V             |

| 9   | L-OUT                | 0    | Audio Lch output                                 | According to the V <sub>CC</sub> _application, Reference Output_level setting is cangeable by Register Bit.             | 2.6V<br>(3.7V) |

| 10  | R-OUT                | 0    | Audio Rch output                                 | Register 1Eh bit 1 (LEVSHIF) =1: Register 1Eh bit 1 (LEVSHIF) =0:                                                       |                |

| 11  | V <sub>CC</sub> -Low | -    | Voltage supply pin at low voltage operation mode | When using V <sub>CC</sub> < 6V, Connect to Pin15 directly                                                              | -              |

| 12  | AM LCF               | 0    | AM low_cut filter                                | Capacitor of 0.047uF is connected between this pin and GND.                                                             | 2.2V           |

| 13  | SD-OUT               | 0    | SD indicator output                              | Active low output                                                                                                       | 3.0V<br>(0.1V) |

| 14  | ST-OUT               | 0    | ST indicator output                              | Active low output                                                                                                       | 3.0V<br>(0.1V) |

| 15  | Vcc                  | -    | Voltage supply pin                               |                                                                                                                         | -              |

| 16  | CLK_IN               | I    | Reference clock input                            | 32.768kHz crystal connected to GND.  It is Also applicable to input directly clock signals ( square wave GND_reference) | -              |

| 17  | IF AGC CAP           | -    | IF-AGC monitor point (test)                      | Open                                                                                                                    | -              |

| 18  | SD-ADJ               | -    | Adjustment for SD on level                       | Incase of changing SD on level, put Resistor between this pin and GND.                                                  | -              |

| 19  | NC                   | ı    |                                                  |                                                                                                                         | -              |

| 20  | SCL                  | I    | I <sup>2</sup> C interface CLK input             |                                                                                                                         | -              |

| 21  | SDA                  | I/O  | I <sup>2</sup> C interface Data input/output     |                                                                                                                         | -              |

| 22  | VREF2                | 0    | Output voltage pin for V <sub>DD</sub>           | V <sub>DD</sub> output_pin of 3.0V. This pin is applicable to supply the current other IC up to 10mA.                   | 3.0V           |

| 23  | GND3                 | -    | Digital GND for control part                     |                                                                                                                         | 0V             |

| 24  | L1                   | -    | Local oscillator                                 | 39nH connected to pin 25                                                                                                | -              |

| 25  | VREF3                | 0    | Reference voltage for local OSC part             |                                                                                                                         | 5.0V           |

| 26  | L2                   | -    | Local oscillator                                 | 39nH connected to pin 25                                                                                                | -              |

| 27  | GND4                 | -    | Analog GND for OSC part                          | Connected to GND                                                                                                        | 0V             |

| 28  | FLL-CAP              | -    | Oscillator tuning voltage output                 | Capacitor of $0.1\mu F$ is connected between this pin and GND.                                                          | -              |

| 29  | GND5                 | -    | Analog GND for FMRF part                         | Connected to GND                                                                                                        | 0V             |

| 30  | FM-ANT               | I    | FM antenna input 1                               | Input impedance is $75\Omega$                                                                                           | 0.8V           |

Pin internal circuit description

| Pin No. | Pin name       | Pin voltage (V)                   | Description                                                                                        | Internal equivalent circuit |

|---------|----------------|-----------------------------------|----------------------------------------------------------------------------------------------------|-----------------------------|

| 1       | AM-ANT         | 2.2                               | AM antenna input pin. The AM antenna coil is connected between pins 40 and this pin. $R=100\Omega$ |                             |

| 2       | AM-REF         | 2.2                               | Reference voltage pin for AM. VAM-REF = 2.2V                                                       | 2.2V<br>Regulator           |

| 3       | AM-CAP         | -                                 | Tuning pinl for AM. (AM Capacitor Bank)                                                            | CAP-BANK  3                 |

| 4       | GND1           | 0                                 | GND pin for Analogue AM_FE part.                                                                   |                             |

| 5       | VREF1          | 4.3                               | Analogue part (tuner) reference bias terminal.  VREF1 = 4.3V                                       | 4.3V<br>Regulator           |

| 6       | MPX IN_OUT     | 2.5                               | FM demodulation output /input for MPX. $R=100\Omega$                                               | (9)                         |

| 7       | AM RF-AGC      | -                                 | Pin for AM_RF AGC. $R1 = 2M\Omega$ $R2 = 5k\Omega$ $R3 = 250\Omega$ $R4 = 1k\Omega$                | R2\$ R4 R4 W                |

| 8       | GND2           | 0                                 | GND pin for Analogue tuner part.                                                                   |                             |

| 9 10    | L-OUT<br>R-OUT | 2.6<br>(3.7V when<br>LEVSHIF = 1) | L-ch (R-ch) output pin. $R = 100\Omega$ $R_{OUT} = 150\Omega$                                      | (15)<br>(10)<br>(10)<br>(9) |

Continued on next page.

| continuea | rom | preceding | page. |

|-----------|-----|-----------|-------|

|           |     |           |       |

| Pin No. | from preceding page.  Pin name | Pin voltage (V)        | Description                                                                                                                                                                                                | Internal equivalent circuit                  |

|---------|--------------------------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| 11      | V <sub>CC</sub> -Low           |                        | $\begin{tabular}{ll} Description \\ \hline when using with $V_{CC}$ < 6.0V, 11Pin-15 Pin is \\ \hline \end{tabular}$                                                                                       | Internal equivalent circuit                  |

| 12      | AM LCF                         | 2.2                    | shorted.  Terminal for AM Low-cut Filter.                                                                                                                                                                  | 5V<br>Regulator<br>4.3V<br>Regulator         |

| 12      | AW EOI                         | 2.2                    | R1 = $250\Omega$<br>R2 = $100k\Omega$<br>R3 = $100k\Omega$<br>R4 = $50k\Omega$<br>R5 = $50k\Omega$                                                                                                         | 12 R1 R2 R2 R5 R5                            |

| 13      | SD-OUT                         | 3.0<br>(less than 0.1) | SD indicator output pin.<br>Active Low output.<br>$R = 100k\Omega$                                                                                                                                         | 22)<br>R \$<br>SD<br>SW                      |

| 14      | ST-OUT                         | 3.0<br>(less than 0.1) | FM stereo indicator output pin Active Low output $R = 100 k \Omega$                                                                                                                                        | R\$ R\$ ST SW                                |

| 15      | Vcc                            | Vcc                    | Analogue part power supply pin. When using 8.5 to 9.5V, set to Register 1Eh Bit 1 (LEVSHIF) = 1 When using with $V_{CC}$ < 6.5V, set to Register 1Eh Bit 1 (LEVSHIF) = 0 And 11Pin-15Pin must be shorted " |                                              |

| 16      | CLK_IN                         | 2.1<br>(OSC mode)      | For internal reference clock.<br>32.768kHz crystal connected to GND. It is Also applicable to input directly clock signals ( square wave GND_reference)<br>R = $100\Omega$                                 | R Crystal oscillator                         |

| 17      | IF AGC CAP                     | -                      | This pin is for test. Open $R1=1.5k\Omega,R2=1k\Omega,R3=500\Omega$                                                                                                                                        | R1 R2 R3 W W W W W W W W W W W W W W W W W W |

| 18      | SD-ADJ                         | -                      | Open normally. Adjust pin for SD sensitivity with to $k\Omega$ resistor connected to GND                                                                                                                   | COMP 18                                      |

Continued on next page.

Continued from preceding page.

| Continucu | from preceding page. |                 | 1                                                                                                                                                                  |                             |

|-----------|----------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| Pin No.   | Pin name             | Pin voltage (V) | Description                                                                                                                                                        | Internal equivalent circuit |

| 19        | NC                   | -               |                                                                                                                                                                    |                             |

| 20        | SCL                  | -               | Digital interface CLK line. $R = 1k\Omega$                                                                                                                         | 20 R SCL                    |

| 21        | SDA                  |                 | Digital interface DATA line. (Interactive data communication line.) Require pull_up resistor 3.3k to 10k between this pin and Vref2 ( $V_{DD}$ ). R = 250 $\Omega$ | data data                   |

| 22        | VREF2                | 3               | Reference voltage output pin for Logic part.  Vref2 = 3V                                                                                                           | 15) Regulator 22            |

| 23        | GND3                 | 0               | GND pin for digital part (Control part).                                                                                                                           |                             |

| 24<br>26  | L1<br>L2             | 5               | OSC coil of 39nH to be connected between this pin and pin 25.                                                                                                      | 24 26 CAP BANK BANK         |

| 25        | VREF3                | 5               | Reference voltage pin for local oscillation circuit.                                                                                                               | 5V<br>Regulator             |

| 27        | GND4                 | 0               | GND pin for local oscillation circuit.                                                                                                                             |                             |

| 28        | FLL-CAP              | -               | LPF pi n for controlled FLL internally. $R = 80k\Omega$                                                                                                            | 28                          |

| 29        | GND5                 | 0               | GND pin for local oscillation circuit.                                                                                                                             |                             |

Continued on next page.

Continued from preceding page.

| Pin No. | Pin name | Pin voltage (V) | Description                                            | Internal equivalent circuit |

|---------|----------|-----------------|--------------------------------------------------------|-----------------------------|

| 30      | FM-ANT   | 0.8             | FM antenna input pin FM. $R=1.5k\Omega$ $Rin=75\Omega$ | 30<br>R<br>29               |

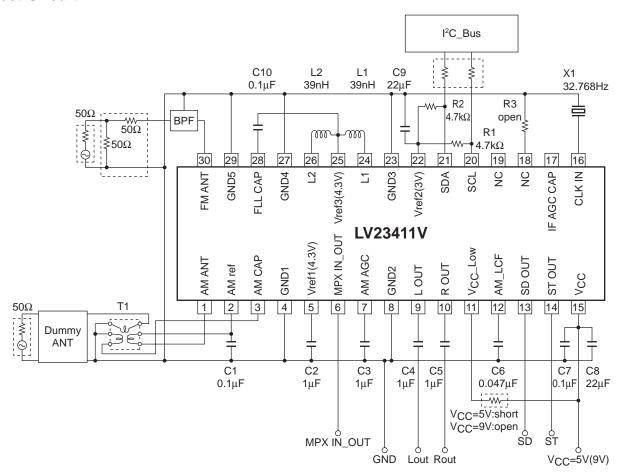

**Used parts**

| Used parts |                         |           |           |                   |          |

|------------|-------------------------|-----------|-----------|-------------------|----------|

| Component  | Parameter               | Value     | Tolerance | Туре              | Supplier |

| L1         | Local Osc Coil          | 39nH      | 5%        | LL2012-FHL39NJ    | TOKO     |

| L2         | Local Osc Coil          | 39nH      | 5%        | LL2012-FHL39NJ    | TOKO     |

| L3         | AM Loop antenna         | 18.1μH    | 5%        | 4910-CSL18R1JN1   | SAGAMI   |

| T1         | AM RF matching          | 250μΗ     | -         | A90326057         | COILS    |

|            |                         |           |           | #7003RNS-A1109YZS | TOKO     |

| C1         | Ripple Filter           | 1μF       |           |                   |          |

| C2         | AM RF AGC Capacitor     | 1μF       |           |                   |          |

| C3         | Coupling Capacitor      | 1μF       |           |                   |          |

| C4         | Coupling Capacitor      | 1μF       |           |                   |          |

| C5         | Supply Bypass Capacitor | 0.1μF     |           |                   |          |

| C6         | Supply Bypass Capacitor | 22μF      |           |                   |          |

| C7         | AM Low-cut Filter       | 0.1μF     |           |                   |          |

| C8         | Supply Bypass Capacitor | 22μF      |           |                   |          |

| C9         | Osc Filter              | 0.1μF     |           |                   |          |

| C10        | Ripple Filter           | 0.1μF     |           |                   |          |

| R1         | Pulled-up Resistor      | 4.7kΩ     |           |                   |          |

| R2         | Pulled-up Resistor      | 4.7kΩ     |           |                   |          |

| R3         | SD Adjust Resistor      | to kΩ     |           |                   |          |

| BPF        | FM ANT BPF              | -         | -         | GFMB7             | SOSHIN   |

| X1         | Crystal                 | 32.768kHz | 100ppm    | DT-26             | KDS      |

| LO1        | AM Ferrite antenna      | 260μΗ     | TBD       | -                 | -        |

|            |                         |           |           |                   |          |

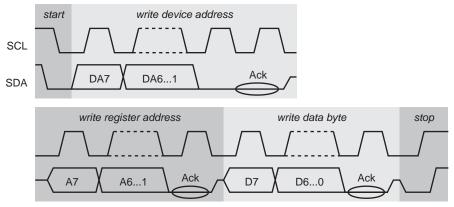

#### **Format of Bus Transfers**

Bus transfers are primarily based on the I<sup>2</sup>C primitives

- Start condition

- Repeated start condition

- Stop condition

- Byte write

- Byte read

Start, restart, and stop conditions are specified as shown in Table 1 below.

Fig. 1 the I<sup>2</sup>C start, repeated start and stop conditions.

For details, like timing, etc., refer to specifications of I<sup>2</sup>C.

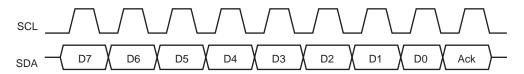

#### 8-bit write

8-bit data is sent from the master microcomputer to LV23411.

Data bit consists of MSB first and LSB last.

Data transmission is latched at the rising edge of SCL in synchronization with the SCL clock generated at the master IC. Do not change data while SCL remains HIGH.

LV23411 outputs the ACK bit between eighth and ninth falling edges of SCL

Fig. 2 Signal pattern of the I<sup>2</sup>C byte write

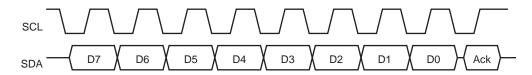

Read is of the same form as write, only except that the data direction is opposite. Eight data bits are sent from LV23411 to the master while Ack is sent from the master to LV23411.

Fig. 3 Signal pattern of the I<sup>2</sup>C byte read

The serial clock SCL is supplied from the master side. It is essential that data bit is output from LV23411 in synchronization with the falling edge while the master side performs latching at the rising edge.

LV23411 latches ACK at the rising edge.

The sequence to write data D into the register A of LV23411 is shown below.

- Start condition

- write the device address (C0h)

- write the register address, A

- write the target data, D

- stop condition

Fig. 4 Register write through I<sup>2</sup>C

When one or more data has been provided for writing, only the first data is allowed to be written.

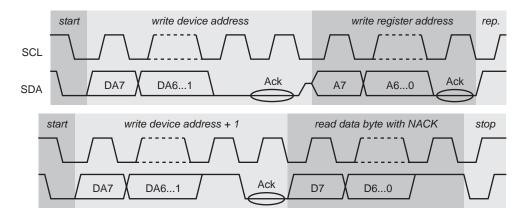

#### Read sequence

- start condition

- write the device address (C0h)

- write the register address, A

- repeated start condition (or stop + start in a single master network)

- write the device address + 1 (C1h)

- read the register contents D, transmit NACK (no more data to be read)

- stop condition

Fig. 5 Register read through I<sup>2</sup>C

#### Interrupt Pin INT

LV23411 has the dedicated interrupt output pin. For the active level to the host, either LOW or HIGH can be selected. The INT output pin is kept floating while the PWRAD bit is cleared during initialization.

Therefore, to avoid influence on the CPU side during initialization, it is recommended to secure the non-active state by means of the pull-up or pull-down resistor.

This enables direct INT output connection to non-masking interruption of the host CPU.

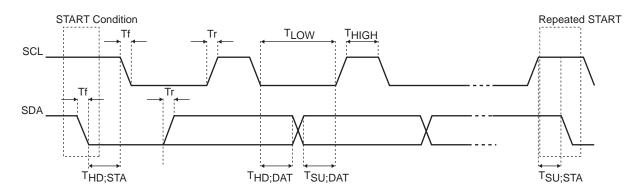

## Digital interface specification (interface specification : reference)

(1). Characteristics of SDA and SCL bus line relative to the I<sup>2</sup>C bus interface

| Bernatus                                         | 0                     | Standar | d-mode | High_Spe |     |      |

|--------------------------------------------------|-----------------------|---------|--------|----------|-----|------|

| Parameter                                        | Symbol                | min     | max    | min      | max | unit |

| SCL clock frequency                              | F <sub>SCL</sub>      | 0       | 100    | 0        | 400 | kHz  |

| Fall time of both SDA and SCL                    | Tf                    |         | 300    | 20+0.1Cb | 300 | ns   |

| Rise time of both SDA and SCL                    | Tr                    |         | 1000   | 20+0.1Cb | 300 | ns   |

| High time of SCL                                 | T <sub>HIGH</sub>     | 4.0     |        | 0.6      |     | μs   |

| Low time of SCL                                  | T <sub>LOW</sub>      | 4.7     |        | 1.3      |     | μs   |

| Hold time of STAT condition                      | T <sub>HD</sub> ; STA | 4.0     |        | 0.6      |     | μs   |

| Hold time of Data                                | T <sub>HD</sub> ; DAT | 0       | 3.45   | 0        | 0.9 | μs   |

| Set-up time of STAT condition                    | T <sub>SU</sub> ; STA | 4.7     |        | 0.6      |     | μs   |

| Set-up time of STOP condition                    | T <sub>SU</sub> ; STO | 4.0     |        | 0.6      |     | μs   |

| Set-up time of Data                              | T <sub>SU</sub> ; DAT | 250     |        | 100      |     | ns   |

| Bus free time between a STOP and START condition | T <sub>BUF</sub>      | 4.7     |        | 1.3      |     | μs   |

| Capacitivie load for each bus line               | Cb                    |         | 400    |          | 400 | pF   |

<sup>\*</sup>Cb = Total capacitance of one bus line

#### Description of the Register of LV23411V

## Register 00h - CHIP\_ID - Chip identify register (Read-Only)

| 7               | 6                                                             | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|-----------------|---------------------------------------------------------------|---|---|---|---|---|---|--|--|--|

| ID[7:0]         |                                                               |   |   |   |   |   |   |  |  |  |

|                 | : ID[7:0] : 8-bit Chip ID<br>LV243411 : 1Bh                   |   |   |   |   |   |   |  |  |  |

| Note : To abort | Note: To abort the command, write any value in this register. |   |   |   |   |   |   |  |  |  |

#### Register 01h - CHIP\_REV - Chip Revision identify register (Read-Only)

| 7             | 6                                                             | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |  |

|---------------|---------------------------------------------------------------|---|---|---|---|---|---|--|--|--|--|

| Revision[7:0] |                                                               |   |   |   |   |   |   |  |  |  |  |

| Bit 7-0:      | Bit 7-0: ID[7:0]: 8-bit Chip Revision                         |   |   |   |   |   |   |  |  |  |  |

|               | ES1:00h                                                       |   |   |   |   |   |   |  |  |  |  |

| Note: To abor | Note: To abort the command, write any value in this register. |   |   |   |   |   |   |  |  |  |  |

#### Register 02h - RADIO\_STAT - Radio station status (Read-Only)

| 7        | 6                                                                                                                                                                                                                                                                                                      | 5                                           | 4                | 3       | 2 | 1 | 0     |  |  |  |  |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|------------------|---------|---|---|-------|--|--|--|--|

| IM_STAT  | IM_FS[1:0]                                                                                                                                                                                                                                                                                             |                                             | MO_ST            | FS[2:0] |   |   | TUNED |  |  |  |  |

| Bit 7 :  | IM_STAT : State of Image-station avoidance  0 = Normal (Possible to write)  1 = The Image-station avoidance is being processed (Impossible to write)  Note :  This bit works only at Register14h_bit7 (IM_EVAS) is set to "1".  The writing processing to LV23411 is prohibited when this bit is "1".  |                                             |                  |         |   |   |       |  |  |  |  |

| Bit 6-5: | IM_FS: Image-signal Fieldstrength 0: No image-signal 1: There are weak Image-signal that level is less -10dB or more weaker than desire's 2: The level of the image –signal is around 0 - 10dB compared with desire's 3: The level of the image-signal is +10dB or more stronger than that of desire's |                                             |                  |         |   |   |       |  |  |  |  |

| Bit 4:   | MO_ST: Mono/Stereo indicator 0 = Forced monaural 1 = Normal (Receiving in stereo mode)                                                                                                                                                                                                                 |                                             |                  |         |   |   |       |  |  |  |  |

| Bit 3-1: | FS[2:0]: Fieldstr<br>0: FS < 10 dBµ <sup>V</sup><br>1: FS = 10 - 20 d<br>2: FS = 20 - 30 d<br>                                                                                                                                                                                                         | V<br>dBµV<br>dBµV                           |                  |         |   |   |       |  |  |  |  |

| Bit 0 :  | 1. PW_RA<br>2. Tuning                                                                                                                                                                                                                                                                                  | tuning command<br>cleared under 3<br>aD = 0 | conditions as be | low.    |   |   |       |  |  |  |  |

|                 |                               |                                                | LV23              | 3411V          |             |     |      |

|-----------------|-------------------------------|------------------------------------------------|-------------------|----------------|-------------|-----|------|

| Register 04h    | - TNPL - Tur                  | ne position lo                                 | w (Read-Only)     |                |             |     |      |

| 7               | 6                             | 5                                              | 4                 | 3              | 2           | 1   | 0    |

| TUNEPOS[7:0     | )]                            |                                                |                   |                |             |     |      |

| Bit 7-0:        | TUNEPOS[7:0]                  | ] : Current RF F                               | Frequency (Low 8) | bit)           |             |     |      |

| Pagistar 05h    | - TNIDH ST/                   | NT - Tune nos                                  | sition high/statu | ıs (Poad-Only  | <b>(</b> )  |     |      |

| 7               | 6                             | 1                                              | 4                 |                | 1           | T 1 | Ιο Ι |

| ERROR[1:0]      | O                             | 5 TUNEPOS[1                                    |                   | 3              | 2           | 1   | 0    |

| Bit 7-6:        | ERROR[1:0]:                   | _                                              | 12.6]             |                |             |     |      |

| Bit 7-0.        | ERROR[1:0]                    | Error code                                     | Remark            |                |             |     |      |

|                 | 0                             |                                                | OK, Command e     | end (No Error) |             |     |      |

|                 | 1                             |                                                | DAC Limit Error   |                |             |     |      |

|                 | 2                             |                                                | Command forced    |                |             |     |      |

|                 | 3                             |                                                | Command busy      |                |             |     |      |

| Bit 5:0 :       | TUNEPOS[13:                   | 8] : Current RF                                | Frequency (High : | 5 bit)         |             |     |      |

| <u> </u>        |                               | <u>- · · · · · · · · · · · · · · · · · · ·</u> | . , , ,           | *              |             |     |      |

| Register 06h    | - COUNT L                     | - Counter lov                                  | v (Read-Only)     |                |             |     |      |

| 7               | 6                             | 5                                              | 4                 | 3              | 2           | 1   | 0    |

| COUNT[7:0]      | <u> </u>                      | 1                                              |                   | 1 -            | _1 -        | 1 - |      |

| Bit 7-0:        | COUNT[7:0] :                  | Counter value (                                | Low 8 bit)        |                |             |     |      |

|                 |                               |                                                | , ,               |                |             |     |      |

| Register 07h    | - COUNT H                     | - Counter Hi                                   | gh (Read-Only)    | )              |             |     |      |

| 7               | 6                             | 5                                              | 4                 | 3              | 2           | 1   | 0    |

| COUNT[15:8]     | 1 -                           |                                                | <u>'</u>          | 1 3            | 1 2         | 1 * |      |

| Bit 7-0 :       | COUNT[15:8]                   | : Counter value                                | (High 8 bit)      |                |             |     |      |

| 210.7.0.1       | 000111[1010]                  | · counter variae                               | (Ingh o on)       |                |             |     |      |

| Register 08h    | - IF OSC - D                  | DAC for IF OS                                  | SC (Read/Write    | .)             |             |     |      |

| 7               | 6                             | 5                                              | 4                 | 3              | 2           | 1   | 0    |

| IFOSC[7:0]      | 1 0                           | 1 3                                            |                   | 1 3            | 1 -         | 1 1 | 1 0  |

| Bit 7-0:        | IFOSC[7:0] : IF               | F Oscillator DA                                | C                 |                |             |     |      |

| 1 210 7 0 1     | 11 000[/.0] . 11              |                                                |                   |                |             |     |      |

| Register 09h    | - IFRW-DAC                    | for IF - Filter                                | Band width (R     | ead/Write)     |             |     |      |

| 7               | 6                             | 5                                              | 4                 | 3              | 2           | 1   | 0    |

| IFBW[7:0]       | J                             | ] ]                                            |                   | 1 3            |             | 1   | 1 0  |

| Bit 7-0:        | IFBW[7:0] : IF-               | -Filter Band wid                               | dth DAC           |                |             |     |      |

|                 | · = · · [ · · · · · ] · · · · | Zuna Wi                                        |                   |                |             |     |      |

| Register 0Rh    | - STERFO                      | OSC - DAC f                                    | or Stereo Deco    | der OSC (Re    | ad/Write)   |     |      |

| 7               | 6                             | 5                                              | 4                 | 3              | 2           | 1   | 0    |

| SDOSC[7:0]      | <u> </u>                      | 1 -                                            | <u> </u>          | 1 ~            | <u>1 ~ </u> | 1 * | 1 "  |

| Bit 7-0:        | SDOSC[7:0] · S                | Stereo Decoder                                 | Oscillator DAC    |                |             |     |      |

| Bit / O.        | 52050[7.0].1                  | Stereo Becouer                                 | Osemator Brie     |                |             |     |      |

| Register OCh    | - RE OSC -                    | DAC for RE                                     | OSC (Read/Wi      | rito)          |             |     |      |

| 7               | 6                             | 5                                              | 4                 | 3              | 2           | 1   | 0    |

| RFCAP[7:0]      | 0                             | 3                                              | 4                 | 3              | 2           | 1   | 10   |

| Bit 7-0:        | RFOSC[7:0] : I                | PE Oscillator D                                | A.C.              |                |             |     |      |

| Dit /-U .       | KI USC[/:U] : I               | A. Oscillator Di                               | AC .              |                |             |     |      |

| Pagistar ADA    | DECAD F                       | DE Can bank                                    | (Pand/Mrita)      |                |             |     |      |

|                 |                               |                                                | (Read/Write)      | La             | T 2         |     | 10   |

| 7<br>DECADI7.01 | 6                             | 5                                              | 4                 | 3              | 2           | 1   | 0    |

| RFCAP[7:0]      | DECADIZ OLI                   | OF On-iller C                                  | omanita: De 1     |                |             |     |      |

| Bit 7-0:        | RFCAP[7:0] : I                | Kr Oscillator Ca                               | apacitor-Bank     |                |             |     |      |

#### Register 0Eh - AMCAP1 - AM - ANT Cap bank1 (Read/Write)

| 7                                                | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|--------------------------------------------------|---|---|---|---|---|---|---|--|--|

| AMCAP[7:0]                                       |   |   |   |   |   |   |   |  |  |

| Bit 7-0 : AMCAP[7:0] : AM Antenna Capacitor-Bank |   |   |   |   |   |   |   |  |  |

Note:

The AM antenna capacitor bank is composed of 12 bits.

High 4 bit is arranged at "AMCTRL" register.

#### Register 0Fh - AMCTRL - AM Station Control (Read/Write)

| 7          | 6 | 5 | 4      | 3      | 2      | 1     | 0     |

|------------|---|---|--------|--------|--------|-------|-------|

| AMDIV[2:0] |   |   | AM_CAL | ACAP11 | ACAP10 | ACAP9 | ACAP8 |

Bit 7-5: AMDIV[2:0]: AM Clock Divider Bit 7: AM\_CD2: AM Clock Divider bit 2. Bit 6: AM\_CD1: AM Clock Divider bit 1. Bit 5: AM\_CD0: AM Clock Divider bit 0.

Note: The AM\_CD[2:0] is used to decrease frequency from FM - band to AM - band.

Please set AM\_CD to "0" at FM mode.

| AM_CD[2:0] | Divide-Rate | AM-RF frequency (In kHz) |

|------------|-------------|--------------------------|

| 0,1        | Divider OFF | 0 (FM mode)              |

| 2          | 224         | 338 - 483                |

| 3          | 160         | 474 - 676                |

| 4          | 112         | 676 - 966                |

| 5          | 80          | 947 - 1353               |

| 6          | 64          | 1183 - 1692              |

| 7          | 48          | 1578 - 2256              |

Bit 4: NA (Fixed to "0")

Bit 3-0: AMCAP[11:8]: AM Antenna Capacitor-Bank

Bit 3: AMCAP\_bit 11 Bit 2: AMCAP\_bit 10 AMCAP\_bit 9 Bit 1: Bit 0: AMCAP\_bit 8

#### Register 10h - DO\_REF\_CLK\_CNF - DO output mode and reference clock configuration (Read/Write)

| 7                                                                   | 6                                        | 5  | 4                  | 3              | 2             | 1   | 0 |  |  |  |  |

|---------------------------------------------------------------------|------------------------------------------|----|--------------------|----------------|---------------|-----|---|--|--|--|--|

| IPOL                                                                | DO_SEL[1:0]                              |    | EXT_CLK_CF         | )]             |               |     |   |  |  |  |  |

| Bit 7-5:                                                            | NA (Fixed to "0                          | ") |                    |                |               |     |   |  |  |  |  |

| Bit 4-3:                                                            | EXT_CLK_CFG[1:0]: External Clock Setting |    |                    |                |               |     |   |  |  |  |  |

|                                                                     | EXT_CLK_CFG[1:0] Reference clock         |    |                    |                |               |     |   |  |  |  |  |

|                                                                     | 00                                       | •  | Off                |                |               |     |   |  |  |  |  |

|                                                                     | 01                                       | (  | Oscillator clock s | ource (Externa | al Clock sour | ce) |   |  |  |  |  |

|                                                                     | 10                                       | 3  | 32768Hz crystal    | oscillator     |               |     |   |  |  |  |  |

|                                                                     | 11 No use                                |    |                    |                |               |     |   |  |  |  |  |

| Bit 2-0 : FS_S[2:0] : SD (Station Detector) operation level setting |                                          |    |                    |                |               |     |   |  |  |  |  |

#### Register 11h - IF\_SEL - IF frequency selection (Read/Write)

| 7       | 6         | 5         | 4 | 3         | 2 | 1 | 0 |

|---------|-----------|-----------|---|-----------|---|---|---|

| FLL_MOD | AMIF[2:0] | AMIF[2:0] |   | FMIF[3:0] |   |   |   |

Bit 7:

FLL\_MOD: FLL operation mode 0 : Smoothing Filter = OFF

1 : Smoothing Filter = ON

Bit 6-4: AMIF[2:0]: IF frequency setting at AM mode

|                 | AMIF[2:0]                                                                                               |  |  |  |  |  |  |  |  |  |  |  |

|-----------------|---------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|--|

| 0 1 2 3 4 5 6 7 |                                                                                                         |  |  |  |  |  |  |  |  |  |  |  |

| 20kHz           | 20kHz         31kHz         42kHz         53kHz         64kHz         75kHz         86kHz         97kHz |  |  |  |  |  |  |  |  |  |  |  |

#### Bit 3-0: FMIF[3:0]: IF frequency setting at FM mode (kHz)

| SE_AM | RF_SEL |       | FMIF[3:0] |       |       |       |       |       |       |       |       |       |       |       |       |       |       |

|-------|--------|-------|-----------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

|       |        | 0     | 1         | 2     | 3     | 4     | 5     | 6     | 7     | 8     | 9     | 10    | 11    | 12    | 13    | 14    | 15    |

| 0     | 0      | 112.5 | 125       | 137.5 | 150   | 162.5 | 175   | 187.5 | 212.5 | 225   | 237.5 | 250   | 262.5 | 275   | 287.5 | 312.5 | 325   |

| 0     | 1      | 112.5 | 127.5     | 142.5 | 157.5 | 157.5 | 172.5 | 187.5 | 202.5 | 217.5 | 232.5 | 247.5 | 262.5 | 277.5 | 292.5 | 307.5 | 322.5 |

#### Register 12h - REF\_CLK\_MOD - Slope correction (Read/Write)

| 7           | 6                                                | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |  |  |

|-------------|--------------------------------------------------|---|---|---|---|---|---|--|--|--|--|--|

| REFMOD[7:0] |                                                  |   |   |   |   |   |   |  |  |  |  |  |

| Bit 7-0:    | Bit 7-0: REFMOD[7:0]: Reference clock collection |   |   |   |   |   |   |  |  |  |  |  |

## Register 13h - SM\_CTRL - Statemachine control (Read/Write)

| 7          | 6                                                                                                                      | 5                | 4                   | 3                 | 2                 | 1                  | 0             |  |  |  |  |  |

|------------|------------------------------------------------------------------------------------------------------------------------|------------------|---------------------|-------------------|-------------------|--------------------|---------------|--|--|--|--|--|

| FLL_ON     | CLKS_SE[2:0]                                                                                                           | ]                |                     | nSD_PM            | nIF_PM            | CM_SE[1:0]         |               |  |  |  |  |  |

| Bit 7:     | FLL_ON : FLL                                                                                                           | control          |                     | •                 | •                 | •                  |               |  |  |  |  |  |

|            | 0 = FLL OFF                                                                                                            |                  |                     |                   |                   |                    |               |  |  |  |  |  |

|            | 1 = FLL ON                                                                                                             |                  |                     |                   |                   |                    |               |  |  |  |  |  |

|            |                                                                                                                        |                  |                     |                   |                   |                    |               |  |  |  |  |  |

| Bit 6-4 :  | Bit 6-4: CLKS_SE: Clock source selection                                                                               |                  |                     |                   |                   |                    |               |  |  |  |  |  |

|            | 0 = No select 1 = Stereo Decoder Oscillator is selected                                                                |                  |                     |                   |                   |                    |               |  |  |  |  |  |

|            |                                                                                                                        |                  | selected            |                   |                   |                    |               |  |  |  |  |  |

|            | 2 = IF Oscillator<br>3 = AM Antenna                                                                                    |                  | lootod              |                   |                   |                    |               |  |  |  |  |  |

|            | 4 = FM RF Osci                                                                                                         |                  |                     |                   |                   |                    |               |  |  |  |  |  |

|            | 5 = AM RF Osci                                                                                                         |                  |                     |                   |                   |                    |               |  |  |  |  |  |

|            | 6 - 7 = No select                                                                                                      |                  | •                   |                   |                   |                    |               |  |  |  |  |  |

|            | 0 7 = 110 select                                                                                                       | •                |                     |                   |                   |                    |               |  |  |  |  |  |

| Note : Bit | [6-4] set oscillato                                                                                                    | or source.       |                     |                   |                   |                    |               |  |  |  |  |  |

|            | ect arbitrary clock                                                                                                    |                  | ning or calibration | ns or measure.    |                   |                    |               |  |  |  |  |  |

|            |                                                                                                                        |                  |                     |                   |                   |                    |               |  |  |  |  |  |

| Bit 3:     | nSD_PM : Stere                                                                                                         |                  | mute                |                   |                   |                    |               |  |  |  |  |  |

|            | 0 = SD PLL Off                                                                                                         |                  |                     |                   |                   |                    |               |  |  |  |  |  |

|            | 1 = SD PLL On                                                                                                          | (Normal operati  | on)                 |                   |                   |                    |               |  |  |  |  |  |

| Bit 2:     | nIF_PM : IF PLI                                                                                                        | Lmuta            |                     |                   |                   |                    |               |  |  |  |  |  |

| Bit 2.     | 0 = IF PLL Off (                                                                                                       |                  |                     |                   |                   |                    |               |  |  |  |  |  |

|            | 1 = IF PLL On (I                                                                                                       |                  | m)                  |                   |                   |                    |               |  |  |  |  |  |

|            | I - II I LL OII (I                                                                                                     | rtormar operatio | ,                   |                   |                   |                    |               |  |  |  |  |  |

| Bit 1-0:   | CM_SE : Comm                                                                                                           | and mode select  | tion                |                   |                   |                    |               |  |  |  |  |  |

|            | 0 = No command                                                                                                         | d                |                     |                   |                   |                    |               |  |  |  |  |  |

|            | 1 = Measure mod                                                                                                        | de               |                     |                   |                   |                    |               |  |  |  |  |  |

|            | 2 = Calibration r                                                                                                      | node             |                     |                   |                   |                    |               |  |  |  |  |  |

|            | 3 = Radio tuning                                                                                                       | g (RF frequency  | tuning) mode        |                   |                   |                    |               |  |  |  |  |  |

| )          |                                                                                                                        |                  |                     |                   |                   |                    |               |  |  |  |  |  |

|            | is bit used to selec                                                                                                   |                  |                     |                   |                   |                    |               |  |  |  |  |  |

|            | ect the arbitrary co                                                                                                   |                  |                     | T /TT             |                   |                    |               |  |  |  |  |  |

| 1 ne       | command is exec                                                                                                        | cuted by setting | TARGET_VAL_         | _L/H.             |                   |                    |               |  |  |  |  |  |

| Command    | l execution time :                                                                                                     |                  |                     |                   |                   |                    |               |  |  |  |  |  |

| Commune    | SD calibration = 540ms                                                                                                 |                  |                     |                   |                   |                    |               |  |  |  |  |  |

|            | IF calibration = 134ms                                                                                                 |                  |                     |                   |                   |                    |               |  |  |  |  |  |

|            | RF (FM) tuning = 105ms                                                                                                 |                  |                     |                   |                   |                    |               |  |  |  |  |  |

|            | RF (AM) tuning = $158$ ms                                                                                              |                  |                     |                   |                   |                    |               |  |  |  |  |  |

|            |                                                                                                                        |                  |                     |                   |                   |                    |               |  |  |  |  |  |

|            | Note: Please wait the time provided for the above-mentioned before all processing including reading the register after |                  |                     |                   |                   |                    |               |  |  |  |  |  |

|            |                                                                                                                        | -                | r the above-menti   | oned before all p | rocessing includi | ing reading the re | egister after |  |  |  |  |  |

|            | having executed                                                                                                        | the command.     |                     |                   |                   |                    |               |  |  |  |  |  |

#### Register 14h - REF\_CLK\_PRS - Reference clock pre-scaler (Read/Write)

| 7         | 6                       | 5                                                           | 4                | 3        | 2 | 1 | 0 |  |  |  |  |

|-----------|-------------------------|-------------------------------------------------------------|------------------|----------|---|---|---|--|--|--|--|

| IM_EVAS   | Reserved                | d WAIT_SEL AM_FINE REFPRE[3:0]                              |                  |          |   |   |   |  |  |  |  |

| Bit 7:    | IM_EVAS : Ima           | ge signal avoida                                            | nce function ON  | /OFF     |   |   |   |  |  |  |  |

|           | 0 = OFF                 | -                                                           |                  |          |   |   |   |  |  |  |  |

|           | 1 = ON (Recomi          | 1 = ON (Recommend)                                          |                  |          |   |   |   |  |  |  |  |

| Bit 6:    | Reserved : Fixed to "0" |                                                             |                  |          |   |   |   |  |  |  |  |

| Bit 5:    |                         | WAIT_SEL : Selection mute release standby time after tuning |                  |          |   |   |   |  |  |  |  |

|           | 0 = 8ms wait            |                                                             |                  |          |   |   |   |  |  |  |  |

|           | 1 = 4ms wait            |                                                             |                  |          |   |   |   |  |  |  |  |

| Bit 4 :   | AM_FINE : Sele          | ection AM_ANT                                               | adjustment stand | dby time |   |   |   |  |  |  |  |

|           | 0 = No wait whe         | n DAC value is                                              | changed          | •        |   |   |   |  |  |  |  |

|           | 1 = 2ms wait wh         | en DAC value is                                             | changed          |          |   |   |   |  |  |  |  |

| Bit 3-0 : | REFPRE[3:0] : I         | Reference Clock                                             | pre- scaler      |          |   |   |   |  |  |  |  |

|           | 0 = 1 : 1               |                                                             |                  |          |   |   |   |  |  |  |  |

|           | 1 = 1 : 2               |                                                             |                  |          |   |   |   |  |  |  |  |

|           | 2 = 1 : 4               |                                                             |                  |          |   |   |   |  |  |  |  |

|           |                         |                                                             |                  |          |   |   |   |  |  |  |  |

|           | 15 = 1 : 32768          |                                                             |                  |          |   |   |   |  |  |  |  |

#### Register 15h - REF\_CLK\_DIV - Reference clock divider (Read/Write)

| 7           | 6                                                                     | 5   | 4       | 3 | 2 | 1 | 0 |

|-------------|-----------------------------------------------------------------------|-----|---------|---|---|---|---|

| REFDIV[7:0] |                                                                       |     |         |   |   |   |   |

| Bit 7-0:    | REFDIV[7:0] : I 0 : Divide rate = 1 : Divide rate = 255 : Divide rate | 1 2 | Divider |   |   |   |   |

## Register 16h - TARGET\_VAL\_L - Target Value Low Register (Read/Write)

| •                                                 |                                                     | _ |   | • , | , |   |   |  |

|---------------------------------------------------|-----------------------------------------------------|---|---|-----|---|---|---|--|

| 7                                                 | 6                                                   | 5 | 4 | 3   | 2 | 1 | 0 |  |

| TARGET[7:0]                                       |                                                     |   |   |     |   |   |   |  |

| Bit 7-0: TARGET[7:0]: Target frequency low 8 bit: |                                                     |   |   |     |   |   |   |  |

| Tuni                                              | Tuning frequency or Calibration frequency: low byte |   |   |     |   |   |   |  |

#### Register 17h - TARGET\_VAL\_H - Target Value High Register (Read/Write)

| 7                                                    | 6                                                                                                                                                                    | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|---|---|---|---|--|--|--|

| TARGET[15:8]                                         |                                                                                                                                                                      |   |   |   |   |   |   |  |  |  |

| Bit 7-0:                                             | Bit 7-0: TARGET[15:8]: Target frequency high 8 bit:                                                                                                                  |   |   |   |   |   |   |  |  |  |

| Tuning frequency or Calibration frequency: high byte |                                                                                                                                                                      |   |   |   |   |   |   |  |  |  |

| *                                                    | With radio power ON, lower eight bits of the target frequency are set. Then, set higher eight bits of the target frequency to this register. The command is executed |   |   |   |   |   |   |  |  |  |

TUNEPOS and TARGET :

- AM mode : 1kHz span - FM mode : 10kHz span

#### Register 18h - RADIO\_CTRL1 - Radio control 1 (Read/Write)

| 7       | 6     | 5           | 4 | 3    | 2        | 1 | 0       |

|---------|-------|-------------|---|------|----------|---|---------|

| IQC_CTR | IFPOL | OSC_LEV[1:0 | ] | DEEM | VOL[1:0] |   | EN_AMHC |

Bit 7: IQC\_CTR: I/Q phase change

0 = Normal mode (Upper heterodyne)

1 = I/Q phase change : for image signal avoidance (Lower heterodyne)

Note: Usually, no-need to change

Bit 6: IF pole change by State Machine

0 = The IF frequency is added to local frequency (Normal) 1 = The IF frequency is subtracted from local frequency

Note: Usually, no-need to change

Bit 5-4: OSC\_LEV[1:0]: RF-OSC oscillation level setting

0 = minimum level 3 = maximum level

Note: 3dB steps, Level = 2 is recommended

Bit 3: DEEM: De-emphasis setting

$0 = 50\mu s$ : Korea China, Europe, Japan

$1 = 75\mu s : USA$

Bit 2-1: VOL[1:0]: Volume setting

0 = minimum (VOL0)

• • • • • •

3 = maximum (VOL3)

Bit 0: EN\_AMHC: AM High-cut Filter ON/OFF

0 = AM HCF OFF 1 = AM HCF ON

#### Register 19h - RADIO\_CTRL2 - Radio control 2 (Read/Write)

| 7         | 6                                                                                              | 5                                                        | 4        | 3          | 2          | 1      | 0        |  |  |  |

|-----------|------------------------------------------------------------------------------------------------|----------------------------------------------------------|----------|------------|------------|--------|----------|--|--|--|

| Reserved  | Reserved                                                                                       | EN_AMM                                                   | Reserved | IF_AGC_LEV | RF_AGC_LEV | 7[1:0] | EN_RFAGC |  |  |  |

| Bit 7 :   | Reserved : Fixed                                                                               | l to "0"                                                 |          |            |            |        |          |  |  |  |

| Bit 6:    | Reserved: Fixed to "1"                                                                         |                                                          |          |            |            |        |          |  |  |  |

| Bit 5:    | 0 = AM mute Ol                                                                                 | EN_AMM : AM Mute ON/OFF  0 = AM mute OFF  1 = AM mute ON |          |            |            |        |          |  |  |  |

| Bit 4 :   | Reserved : Fixed                                                                               | l to "0"                                                 |          |            |            |        |          |  |  |  |

| Bit 3:    | IF_AGC_LEV:<br>0 = AGC slow m<br>1 = AGC first m                                               | node                                                     | Control  |            |            |        |          |  |  |  |

| Bit 2-1 : | RF_AGC_LEV[1:0]: RF-AGC Level Control 0 = AGC slow mode 1 = AGC normal mode 3 = AGC first mode |                                                          |          |            |            |        |          |  |  |  |

| Bit 0 :   | EN_RFAGC : RF-AGC ON/OFF<br>0 = AGC OFF<br>1 = AGC ON (Normal)                                 |                                                          |          |            |            |        |          |  |  |  |

## Register 1Ah - RADIO\_CTRL3 - Radio control 3 (Read/Write)

| 7         | 6                                                                                 | 5                                                                               | 4            | 3               | 2      | 1         | 0     |  |  |  |

|-----------|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------|--------------|-----------------|--------|-----------|-------|--|--|--|

| DEEM_100  | NA                                                                                |                                                                                 | IF_AGC_CAP   | AM_WIDE_A       | GC_OFF | AM_WIDE_A | GC_ON |  |  |  |

| Bit 7:    | $0 = 0 \mu s$ (Default                                                            | DEEM_100 : Additional De-emphasis (100 $\mu$ s) 0 = 0 $\mu$ s (Default setting) |              |                 |        |           |       |  |  |  |

|           | $1 = 100\mu s$ (DEE)                                                              | $\mathbf{M} = 1:75\mu\mathbf{S})$                                               |              |                 |        |           |       |  |  |  |

| Bit 6:    | NA                                                                                | NA                                                                              |              |                 |        |           |       |  |  |  |